# **FEATURES**

- 3.3 Volt  $V_{DD}$  power supply with a range of 2.7V to 3.6V

- I/O Voltage range supports wide +1.65 to +3.6 Volt interfaces

- Fast 45 ns read/write cycle

- SRAM compatible timing

- Unlimited read & write endurance

- Data always non-volatile for >20-years at temperature

- All products meet MSL-3 moisture sensitivity level

- RoHS-compliant small footprint BGA package

# **BENEFITS**

- One memory replaces FLASH, SRAM, EEPROM and BBSRAM in systems for simpler, more efficient designs

- Improves reliability by replacing battery-backed SRAM

# INTRODUCTION

The **MRODL08B** is a dual power supply 1,048,576-bit magnetoresistive random access memory (MRAM) device organized as 131,072 words of 8 bits. It supports I/O voltages from +1.65 to +3.6 volts. The MRODL08B offers SRAM compatible 45ns read/write timing with unlimited endurance. Data is always non-volatile for greater than 20-years. Data is automatically protected on power loss by low-voltage inhibit circuitry to prevent writes with voltage out of specification. The MRODL08B is the ideal memory solution for applications that must permanently store and retrieve critical data and programs quickly.

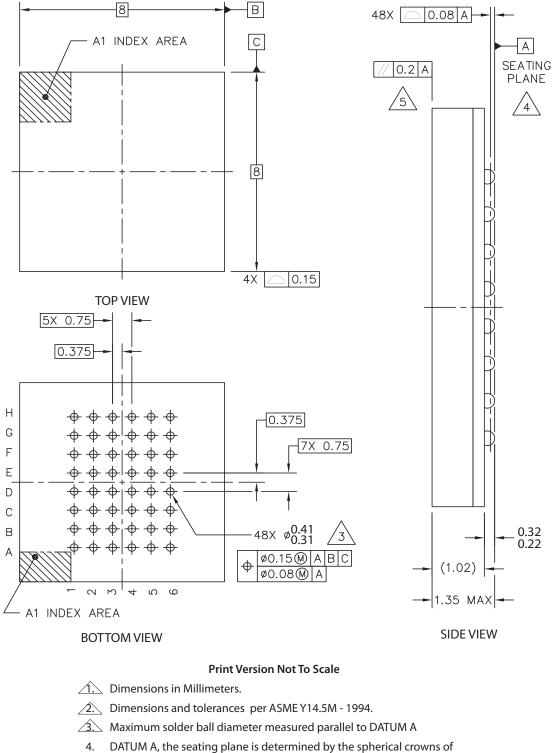

The **MRODL08B** is available in small footprint 8 mm x 8 mm, 48-pin ball grid array (BGA) package with 0.75 mm ball centers.

The **MRODL08B** provides highly reliable data storage over a wide range of temperatures. The product is offered with commercial temperature (0 to +70 °C).

# CONTENTS

| 1. DEVICE PIN ASSIGNMENT     | . 2  |

|------------------------------|------|

| 2. ELECTRICAL SPECIFICATIONS | 4    |

| 3. TIMING SPECIFICATIONS     | 8    |

| 4. ORDERING INFORMATION      | 13   |

| 5. MECHANICAL DRAWING        | 14   |

| 6. REVISION HISTORY          | . 15 |

| How to Reach Us              | . 15 |

# MRODLO8B Dual Supply 128K x 8 MRAM

# **1. DEVICE PIN ASSIGNMENT**

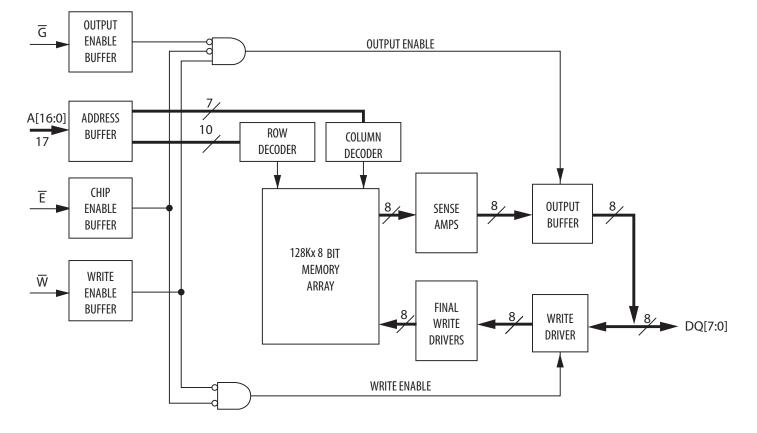

#### Figure 1.1 Block Diagram

| Signal Name      | Function                                                         |

|------------------|------------------------------------------------------------------|

| A                | Address Input                                                    |

| Ē                | Chip Enable                                                      |

| W                | Write Enable                                                     |

| G                | Output Enable                                                    |

| DQ               | Data I/O                                                         |

| V <sub>DD</sub>  | Power Supply                                                     |

| V <sub>DDQ</sub> | I/O Power Supply                                                 |

| V <sub>ss</sub>  | Ground                                                           |

| DC               | Do Not Connect                                                   |

| NC               | No Connection, Ball D3, H1, H6, G2 Reserved for Future Expansion |

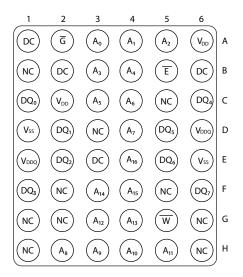

#### Figure 1.2 Pin Diagrams for Available Packages (Top View)

#### 48 Pin FBGA

#### **Table 1.2 Operating Modes**

| Ē | $\overline{\mathbf{G}}^{1}$ | $\overline{\mathbf{W}}^{1}$ | Mode            | V <sub>DD</sub> Current             | <b>DQ[7:0]</b> <sup>2</sup> |

|---|-----------------------------|-----------------------------|-----------------|-------------------------------------|-----------------------------|

| Н | Х                           | Х                           | Not selected    | Ι <sub>SB1</sub> , Ι <sub>SB2</sub> | Hi-Z                        |

| L | Н                           | Н                           | Output disabled | I <sub>DDR</sub>                    | Hi-Z                        |

| L | L                           | Н                           | Byte Read       | I <sub>DDR</sub>                    | D <sub>Out</sub>            |

| L | Х                           | L                           | Byte Write      | I <sub>DDW</sub>                    | D <sub>in</sub>             |

<sup>1</sup> H = high, L = low, X = don't care

<sup>2</sup> Hi-Z = high impedance

# **2. ELECTRICAL SPECIFICATIONS**

#### **Absolute Maximum Ratings**

This device contains circuitry to protect the inputs against damage caused by high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage greater than maximum rated voltages to these high-impedance (Hi-Z) circuits.

The device also contains protection against external magnetic fields. Precautions should be taken to avoid application of any magnetic field more intense than the maximum field intensity specified in the maximum ratings.

| Parameter                                     | Symbol                 | Value             | Unit |

|-----------------------------------------------|------------------------|-------------------|------|

| Core Supply voltage <sup>2</sup>              | V <sub>DD</sub>        | -0.5 to 4.0       | V    |

| I/O Power Supply voltage <sup>2</sup>         | V <sub>DDQ</sub>       | -0.5 to 4.0       | V    |

|                                               | V <sub>IN</sub>        | -0.5 to +4.0 or   |      |

| Voltage on any pin <sup>2</sup>               |                        | $V_{DDQ} + 0.5$   | V    |

|                                               |                        | whichever is less |      |

| Output current per pin                        | I <sub>OUT</sub>       | ±20               | mA   |

| Package power dissipation <sup>3</sup>        | P <sub>D</sub>         | 0.600             | W    |

| Temperature under bias                        | T <sub>BIAS</sub>      | -10 to 85         | °C   |

| Storage Temperature                           | T <sub>stg</sub>       | -55 to 150        | °C   |

| Lead temperature during solder (3 minute max) | T <sub>Lead</sub>      | 260               | °C   |

| Maximum magnetic field during write           | H <sub>max_write</sub> | 2000              | A/m  |

| Maximum magnetic field during read or standby | H <sub>max_read</sub>  | 8000              | A/m  |

#### Table 2.1 Absolute Maximum Ratings<sup>1</sup>

<sup>1</sup> Permanent device damage may occur if absolute maximum ratings are exceeded. Functional operation should be restricted to recommended operating conditions. Exposure to excessive voltages or magnetic fields could affect device reliability.

<sup>2</sup> All voltages are referenced to V<sub>ss</sub>.

<sup>3</sup> Power dissipation capability depends on package characteristics and use environment.

| Parameter                                        | Symbol             | Min               | Typical | Max                 | Unit |  |  |

|--------------------------------------------------|--------------------|-------------------|---------|---------------------|------|--|--|

| Core Power supply voltage                        | $V_{_{DD}}$        | 2.7 <sup>1</sup>  | 3.3     | 3.6                 | V    |  |  |

| I/O Power supply voltage                         | V <sub>DDQ</sub>   | 1.65 <sup>1</sup> | -       | 3.6                 | V    |  |  |

| Write inhibit voltage V <sub>DD</sub>            | $V_{WIDD}$         | 2.3               | 2.5     | 2.7 <sup>1</sup>    | V    |  |  |

| Write inhibit voltage V <sub>DDQ</sub>           | V <sub>WIDDQ</sub> | 1.2               | 1.4     | 1.65 <sup>1</sup>   | V    |  |  |

| Input high voltage (V <sub>DDQ</sub> =1.65-2.2V) | V <sub>IH</sub>    | 1.4               | -       | $V_{DDQ} + 0.2^{2}$ | V    |  |  |

| Input high voltage (V <sub>DDQ</sub> =2.2-2.7V)  | V <sub>IH</sub>    | 1.8               | -       | $V_{DDQ} + 0.2^{2}$ | V    |  |  |

| Input high voltage (V <sub>DDQ</sub> =2.7-3.6V)  | V <sub>IH</sub>    | 2.2               | -       | $V_{DDQ} + 0.2^{2}$ | V    |  |  |

| Input low voltage (V <sub>DDQ</sub> =1.65-2.2V)  | V <sub>IL</sub>    | -0.2 <sup>3</sup> | -       | 0.4                 | V    |  |  |

| Input low voltage (V <sub>DDQ</sub> =2.2-2.7V)   | V <sub>IL</sub>    | -0.2 <sup>3</sup> | -       | 0.6                 | V    |  |  |

| Input low voltage (V <sub>DDQ</sub> =2.7-3.6V)   | V <sub>IL</sub>    | -0.2 <sup>3</sup> | -       | 0.8                 | V    |  |  |

| Access Time                                      | T <sub>A</sub>     | 0                 |         | 70                  | °C   |  |  |

#### **Table 2.2 Operating Conditions**

Notes:

- 1.  $V_{DDQ} \leq V_{DD}$ . Write inhibit occurs when either  $V_{DD}$  or  $V_{DDQ}$  drops below its write inhibit voltage. There is a 2 ms startup time once  $V_{DD}$  exceeds  $V_{DD}$  (min). See Power Up and Power Down Sequencing.

- 2.  $V_{IH}(max) = V_{DDQ} + 0.2 \text{ V DC}$ ;  $V_{IH}(max) = V_{DDQ} + 0.5 \text{ V AC}$  (pulse width  $\leq 20 \text{ ns}$ ) for  $I \leq 20.0 \text{ mA}$ .

- 3.  $V_{IL}(min) = -0.2 \text{ V DC}$ ;  $V_{IL}(min) = -2.0 \text{ V AC}$  (pulse width  $\leq 20 \text{ ns}$ ) for  $I \leq 20.0 \text{ mA}$ .

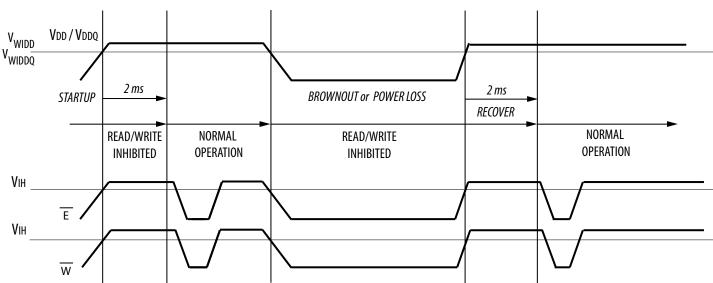

#### Power Up and Power Down Sequencing

#### Initial Power Up

The MRAM is protected from write operations whenever  $V_{DD}$  is less than  $V_{WDD}$ . Upon power up  $V_{DD}$  must go above 3.0V, and a 2 ms startup time must be observed before read or write operations can start. This time allows memory power supplies to stabilize.

#### Power Loss or Brownout

During power loss or brownout where  $V_{DD}$  goes below  $V_{WIDD}$  writes are inhibited. To return to normal operation and exit Write Inhibit,  $V_{DD}$  must go above 3.0V, and a 2 ms startup time must be observed. Once powered up,  $V_{DD}$  minimum can go as low as 2.7V.

#### Chip Enable and Write Enable

The  $\overline{E}$  and  $\overline{W}$  control signals should track  $V_{DD}$  on power up to  $V_{DD}$  - 0.2 V or  $V_{IH}$  (whichever is lower) and remain high for the startup time. In most systems, this means that these signals should be pulled up with a resistor so that signal remains high if the driving signal is Hi-Z during power up. Any logic that drives  $\overline{E}$  and  $\overline{W}$ should hold the signals high with a power-on reset signal for longer than the startup time.

| Parameter                                                   | Symbol              | Min | Typical | Мах | Unit |

|-------------------------------------------------------------|---------------------|-----|---------|-----|------|

| Input leakage current                                       | l <sub>lkg(l)</sub> | -   | -       | ±1  | μΑ   |

| Output leakage current                                      | l <sub>lkg(O)</sub> | -   | -       | ±1  | μΑ   |

| Output low voltage (V <sub>DDQ</sub> =1.65-2.2V@ 0.1mA)     | V <sub>ol</sub>     | -   | -       | 0.2 | V    |

| Output low voltage (V <sub>DDQ</sub> =2.2-2.7V@ 0.1mA)      | V <sub>ol</sub>     | -   | -       | 0.4 | V    |

| Output low voltage (V <sub>DDQ</sub> =2.7-3.6V@ 2.1 mA)     | V <sub>ol</sub>     | -   | -       | 0.4 | V    |

| Output high voltage (V <sub>DDQ</sub> =1.65-2.2V@ - 0.1 mA) | V <sub>OH</sub>     | 1.4 | -       | -   | V    |

| Output high voltage (V <sub>DDQ</sub> =2.2-2.7V@ -0.1 mA)   | V <sub>oh</sub>     | 2   | -       | -   | V    |

| Output high voltage (V <sub>DDQ</sub> =2.7-3.6V@ -1.0 mA)   | V <sub>OH</sub>     | 2.4 | -       | -   | V    |

#### **Table 2.3 DC Characteristics**

## **Table 2.4 Power Supply Characteristics**

| Parameter                                                                                                                                                                          | Symbol           | Typical | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|-----|------|

| AC active supply current - read modes <sup>1</sup><br>(I <sub>OUT</sub> = 0 mA, V <sub>DD</sub> = max)                                                                             | I <sub>DDR</sub> | 25      | 30  | mA   |

| AC active supply current - write modes <sup>1</sup><br>(V <sub>DD</sub> = max)                                                                                                     | I <sub>DDW</sub> | 55      | 65  | mA   |

| AC active operating current<br>$(V_{DDQ} = V_{H} = 3.6V, V_{IL} = 0V)$<br><i>input transitions &lt;2ns, no output load</i>                                                         | I <sub>DDQ</sub> | 0.50    | 2   | mA   |

| AC standby current<br>$(V_{DD} = \max, \overline{E} = V_{H})$<br><i>no other restrictions on other inputs</i>                                                                      | I <sub>SB1</sub> | 6       | 8   | mA   |

| CMOS standby current<br>$(\overline{E} \ge V_{DD} - 0.2 \text{ V and } V_{In} \le V_{SS} + 0.2 \text{ V or } \ge V_{DDQ} - 0.2 \text{ V})$<br>$(V_{DD} = \max, f = 0 \text{ MHz})$ | I <sub>SB2</sub> | 5       | 7   | mA   |

<sup>1</sup> All active current measurements are measured with one address transition per cycle and at minimum cycle time.

# **3. TIMING SPECIFICATIONS**

Table 3.1 Capacitance<sup>1</sup>

| Parameter                 | Symbol           | Typical | Max | Unit |

|---------------------------|------------------|---------|-----|------|

| Address input capacitance | C <sub>In</sub>  | -       | 6   | рF   |

| Control input capacitance | C <sub>In</sub>  | -       | 6   | рF   |

| Input/Output capacitance  | C <sub>I/O</sub> | -       | 8   | рF   |

$^{1}$  f = 1.0 MHz, VDDQ=VDDQ(typ), T<sub>A</sub> = 25 °C, periodically sampled rather than 100% tested.

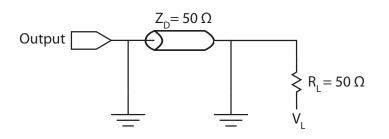

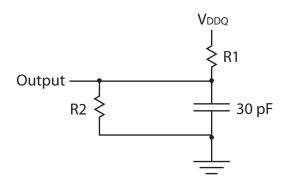

#### **Table 3.2 AC Measurement Conditions**

| Parameter                                                                 | V <sub>DDQ</sub> =1.8 | V <sub>DDQ</sub> =2.5 | V <sub>DDQ</sub> =3.3 | Unit |

|---------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|------|

| Logic input timing measurement reference level                            | 0.8                   | 0.8                   | 0.8                   | V    |

| Logic output timing measurement reference level                           | 0.8                   | 0.8                   | 0.8                   | V    |

| Logic input pulse levels                                                  | 0 or 1.8              | 0 or 2.5              | 0 or 3.3              | V    |

| Output load voltage (VL) for low & high impedance parameters (Figure 3.1) | 0.8                   | 1.2                   | 1.75                  | V    |

| Output load resistor (R1) for all other timing                            | 13,500                | 16,600                | 1,103                 | Ω    |

| Output load resistor (R2) for all other timing                            | 10,800                | 15,400                | 1,554                 | Ω    |

## Figure 3.1 Output Load Test Low and High

#### Figure 3.2 Output Load Test All Others

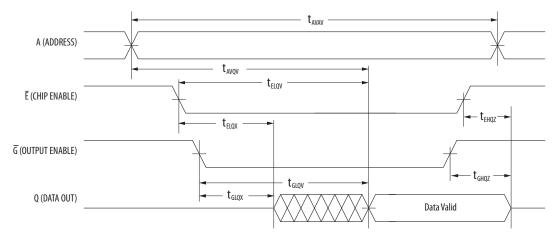

#### Read Mode

| Parameter                                       | Symbol            | Min | Max | Unit |  |  |  |  |

|-------------------------------------------------|-------------------|-----|-----|------|--|--|--|--|

| Read cycle time                                 | t <sub>AVAV</sub> | 45  | -   | ns   |  |  |  |  |

| Address access time                             | t <sub>AVQV</sub> | -   | 45  | ns   |  |  |  |  |

| Enable access time <sup>2</sup>                 | t <sub>ELQV</sub> | -   | 45  | ns   |  |  |  |  |

| Output enable access time                       | t <sub>GLQV</sub> | -   | 20  | ns   |  |  |  |  |

| Output hold from address change                 | t <sub>AXQX</sub> | 3   | -   | ns   |  |  |  |  |

| Enable low to output active <sup>3</sup>        | t <sub>ELQX</sub> | 3   | -   | ns   |  |  |  |  |

| Output enable low to output active <sup>3</sup> | t <sub>GLQX</sub> | 0   | -   | ns   |  |  |  |  |

| Enable high to output Hi-Z <sup>3</sup>         | t <sub>EHQZ</sub> | 0   | 15  | ns   |  |  |  |  |

| Output enable high to output Hi-Z <sup>3</sup>  | t <sub>GHQZ</sub> | 0   | 15  | ns   |  |  |  |  |

#### Table 3.3 Read Cycle Timing<sup>1</sup>

<sup>1</sup> W is high for read cycle. Power supplies must be properly grounded and decoupled, and bus contention conditions must be minimized or eliminated during read or write cycles.

<sup>2</sup> Addresses valid before or at the same time  $\overline{E}$  goes low.

$^3$  This parameter is sampled and not 100% tested. Transition is measured ±200 mV from the steady-state voltage.

# A (ADDRESS)

#### Figure 3.3A Read Cycle 1

NOTE: Device is continuously selected ( $\overline{E} \leq V_{\mu}, \overline{G} \leq V_{\mu}$ )

#### Figure 3.3B Read Cycle 2

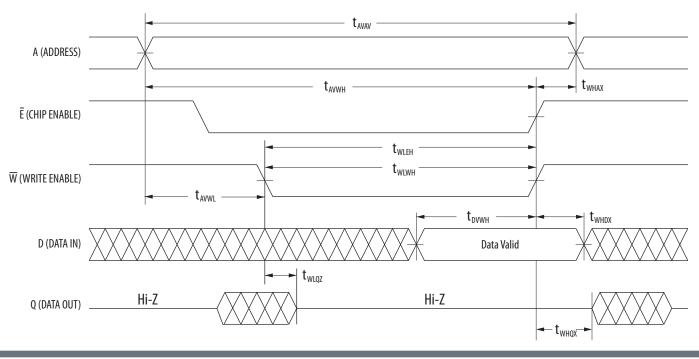

| Table 3.4 Write Cycle Timing 1 (W Controlled)' |                                        |     |     |      |  |  |  |  |

|------------------------------------------------|----------------------------------------|-----|-----|------|--|--|--|--|

| Parameter                                      | Symbol                                 | Min | Мах | Unit |  |  |  |  |

| Write cycle time <sup>2</sup>                  | t <sub>AVAV</sub>                      | 45  | -   | ns   |  |  |  |  |

| Address set-up time                            | t <sub>AVWL</sub>                      | 0   | -   | ns   |  |  |  |  |

| Address valid to end of write (G high)         | t <sub>AVWH</sub>                      | 25  | -   | ns   |  |  |  |  |

| Address valid to end of write (G low)          | t <sub>AVWH</sub>                      | 25  | -   | ns   |  |  |  |  |

| Write pulse width (G high)                     | t <sub>wlwh</sub><br>t <sub>wleh</sub> | 20  | -   | ns   |  |  |  |  |

| -<br>Write pulse width (G low)                 | t <sub>wlwh</sub><br>t <sub>wleh</sub> | 20  | -   | ns   |  |  |  |  |

| Data valid to end of write                     | t <sub>DVWH</sub>                      | 15  | -   | ns   |  |  |  |  |

| Data hold time                                 | t <sub>whdx</sub>                      | 0   | -   | ns   |  |  |  |  |

| Write low to data Hi-Z <sup>3</sup>            | t <sub>wLQZ</sub>                      | 0   | 15  | ns   |  |  |  |  |

| Write high to output active <sup>3</sup>       | t <sub>whox</sub>                      | 3   | -   | ns   |  |  |  |  |

| Write recovery time                            | t <sub>whax</sub>                      | 12  | -   | ns   |  |  |  |  |

Table 3.4 Write Cycle Timing 1 ( $\overline{\mathbf{W}}$  Controlled)<sup>1</sup>

<sup>1</sup> All writes occur during the overlap of E low and W low. Power supplies must be properly grounded and decoupled and bus contention conditions must be minimized or eliminated during read and write cycles. If G goes low at the same time or after W goes low, the output will remain in a high impedance state. After W or E has been brought high, the signal must remain in steady-state high for a minimum of 2 ns. The minimum time between E being asserted low in one cycle to E being asserted low in a subsequent cycle is the same as the minimum cycle time allowed for the device.

<sup>2</sup> All write cycle timings are referenced from the last valid address to the first transition address.

<sup>3</sup> This parameter is sampled and not 100% tested. Transition is measured ±200 mV from the steady-state voltage. At any given voltage or temperature,  $t_{wLOZ}(max) < t_{wHOX}(min)$

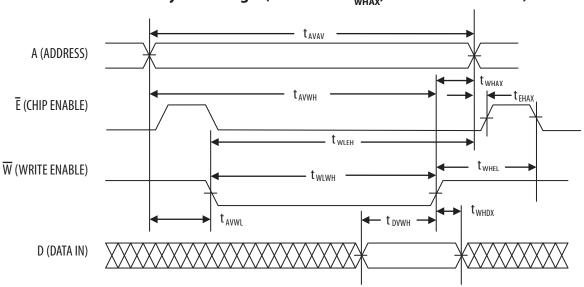

# Figure 3.4 Write Cycle Timing 1 ( $\overline{W}$ Controlled)

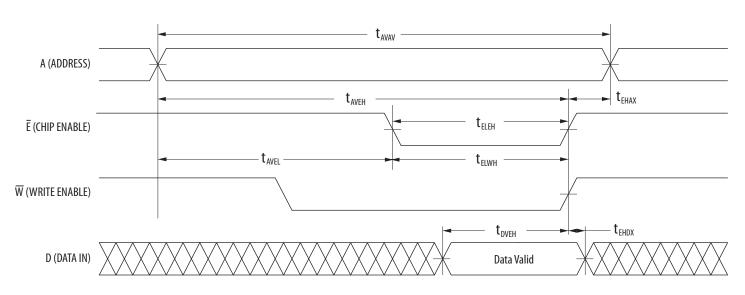

| Table 3.5 Write Cycle Timing 2 (E Controlled)'        |                                        |                      |     |      |  |  |

|-------------------------------------------------------|----------------------------------------|----------------------|-----|------|--|--|

| Parameter                                             | Symbol                                 | Min                  | Мах | Unit |  |  |

| Write cycle time <sup>2</sup>                         | t <sub>AVAV</sub>                      | 45                   | -   | ns   |  |  |

| Address set-up time                                   | t <sub>AVEL</sub>                      | 0                    | -   | ns   |  |  |

| Address valid to end of write (G high)                | t <sub>AVEH</sub>                      | 25                   | -   | ns   |  |  |

| Address valid to end of write ( $\overline{G}$ low)   | t <sub>AVEH</sub>                      | t <sub>AVEH</sub> 25 |     | ns   |  |  |

| Enable to end of write ( $\overline{G}$ high)         | t <sub>elen</sub><br>t <sub>elwn</sub> | 20                   | -   | ns   |  |  |

| Enable to end of write $(\overline{G} \text{ low})^3$ | t <sub>elen</sub><br>t <sub>elwn</sub> | 20                   | -   | ns   |  |  |

| Data valid to end of write                            | t <sub>DVEH</sub>                      | 15                   | -   | ns   |  |  |

| Data hold time                                        | t <sub>eHDX</sub>                      | 0                    | -   | ns   |  |  |

| Write recovery time                                   | t <sub>ehax</sub>                      | 12                   | -   | ns   |  |  |

All writes occur during the overlap of  $\overline{E}$  low and  $\overline{W}$  low. Power supplies must be properly grounded and decoupled and bus contention conditions must be minimized or eliminated during read and write cycles. If  $\overline{G}$  goes low at the same time or after  $\overline{W}$  goes low, the output will remain in a high impedance state. After  $\overline{W}$  or  $\overline{E}$  has been brought high, the signal must remain in steady-state high for a minimum of 2 ns. The minimum time between  $\overline{E}$  being asserted low in one cycle to  $\overline{E}$  being asserted low in a subsequent cycle is the same as the minimum cycle time allowed for the device.

<sup>2</sup> All write cycle timings are referenced from the last valid address to the first transition address.

<sup>3</sup> If  $\overline{E}$  goes low at the same time or after  $\overline{W}$  goes low, the output will remain in a high-impedance state. If  $\overline{E}$  goes high at the same time or before  $\overline{W}$  goes high, the output will remain in a high-impedance state.

# Figure 3.5 Write Cycle Timing 2 ( $\overline{E}$ Controlled)

# Table 3.6 Write Cycle Timing 3 (Shortened $t_{WHAX}$ , $\overline{W}$ and $\overline{E}$ Controlled)<sup>1</sup>

| Parameter                                  | Symbol                                 | Min | Мах | Unit |

|--------------------------------------------|----------------------------------------|-----|-----|------|

| Write cycle time <sup>2</sup>              | t <sub>AVAV</sub>                      | 45  | -   | ns   |

| Address set-up time —                      | t <sub>AVWL</sub>                      | 0   | -   | ns   |

| Address valid to end of write (G high)     | t <sub>avwh</sub>                      | 25  | -   | ns   |

| Address valid to end of write (G low)      | t <sub>avwh</sub>                      | 25  | -   | ns   |

| Write pulse width                          | t <sub>wlwh</sub><br>t <sub>wleh</sub> | 20  | -   | ns   |

| Data valid to end of write                 | t <sub>DVWH</sub>                      | 15  | -   | ns   |

| Data hold time                             | t <sub>whdx</sub>                      | 0   | -   | ns   |

| Enable recovery time                       | t <sub>ehax</sub>                      | -2  | -   | ns   |

| Write recovery time <sup>3</sup>           | t <sub>whax</sub>                      | 6   | -   | ns   |

| Write to enable recovery time <sup>3</sup> | t <sub>whel</sub>                      | 12  | -   | ns   |

<sup>1</sup> All writes occur during the overlap of E low and W low. Power supplies must be properly grounded and decoupled and bus contention conditions must be minimized or eliminated during read and write cycles. If G goes low at the same time or after W goes low, the output will remain in a high impedance state. After W or E has been brought high, the signal must remain in steady-state high for a minimum of 2 ns. The minimum time between E being asserted low in one cycle to E being asserted low in a subsequent cycle is the same as the minimum cycle time allowed for the device.

<sup>2</sup> All write cycle timings are referenced from the last valid address to the first transition address.

<sup>3</sup> If  $\overline{E}$  goes low at the same time or after  $\overline{W}$  goes low, the output will remain in a high-impedance state. If  $\overline{E}$  goes high at the same time or before  $\overline{W}$  goes high, the output will remain in a high-impedance state.

Table 3.6 Write Cycle Timing 3 (Shortened  $t_{WHAX}$ ,  $\overline{W}$  and  $\overline{E}$  Controlled)

# **4. ORDERING INFORMATION**

| MR | 0 | DL | 08 | В |                  | MA                              | 45 | R |            |                                |             |                            |

|----|---|----|----|---|------------------|---------------------------------|----|---|------------|--------------------------------|-------------|----------------------------|

|    |   |    |    |   |                  |                                 |    |   |            |                                | Carrier     | (Blank=Tray,R=Tape & Reel) |

|    |   |    |    |   |                  |                                 |    |   |            |                                | Speed       | (45 = 45  ns)              |

|    |   |    |    |   |                  |                                 |    |   |            | Package                        | (MA = FBGA) |                            |

|    |   |    |    |   | Temperature Rang | e (Blank= 0 to $+70 \degree$ C) |    |   |            |                                |             |                            |

|    |   |    |    |   | Revision         | (B = Revision)                  |    |   |            |                                |             |                            |

|    |   |    |    |   |                  |                                 |    |   | Data Width | (08 = 8-Bit)                   |             |                            |

|    |   |    |    |   |                  |                                 |    |   | Туре       | (DL= Dual Supply Low Voltage)  |             |                            |

|    |   |    |    |   |                  |                                 |    |   | Density    | (0 = 1Mb)                      |             |                            |

|    |   |    |    |   |                  |                                 |    |   | Part Type  | (MR = Magnetoresistive<br>RAM) |             |                            |

# Figure 4.1 Part Numbering System

# Table 4.1 Available Parts

| Part Number   | Description                                  | Temperature |

|---------------|----------------------------------------------|-------------|

| MR0DL08BMA45  | Dual Supply 128x8 MRAM 48-BGA                | Commercial  |

| MR0DL08BMA45R | Dual Supply 128x8 MRAM 48-BGA<br>Tape & Reel | Commercial  |

- DATUM A, the seating plane is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement shall exclude any effect of mark on top surface of package.

# **6. REVISION HISTORY**

| Revision | Date           | Description of Change                          |

|----------|----------------|------------------------------------------------|

| 1        | Nov 19, 2013   | Initial Data Sheet Release                     |

| 1.1      | May 19, 2015   | Revised contact information.                   |

| 1.2      | June 11, 2015  | Corrected Japan Sales Office telephone number. |

| 1.3      | March 22, 2018 | Updated Contact Us table                       |

Home Page: www.everspin.com

#### **World Wide Information Request**

#### WW Headquarters - Chandler, AZ

5670 W. Chandler Blvd., Suite 100 Chandler, Arizona 85224 Tel: +1-877-480-MRAM (6726) Local Tel: +1-480-347-1111 Fax: +1-480-347-1175 support@everspin.com

**Europe, Middle East and Africa** Everspin Europe Support <u>support.europe@everspin.com</u>

#### Japan

Everspin Japan Support support.japan@everspin.com

#### **Asia Pacific**

Everspin Asia Support support.asia@everspin.com

#### Filename:

EST02629\_MR0DL08B\_Datasheet\_Rev1.3032218<sup>trademarks</sup> of Everspin Technologies, Inc.

# **HOW TO CONTACT US**

#### **Everspin Technologies, Inc.**

Information in this document is provided solely to enable system and software implementers to use Everspin Technologies products. There are no express or implied licenses granted hereunder to design or fabricate any integrated circuit or circuits based on the information in this document. Everspin Technologies reserves the right to make changes without further notice to any products herein. Everspin makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Everspin Technologies assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters, which may be provided in Everspin Technologies data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters including "Typicals" must be validated for each customer application by customer's technical experts. Everspin Technologies does not convey any license under its patent rights nor the rights of others. Everspin Technologies products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Everspin Technologies product could create a situation where personal injury or death may occur. Should Buyer purchase or use Everspin Technologies products for any such unintended or unauthorized application, Buyer shall indemnify and hold Everspin Technologies and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Everspin Technologies was negligent regarding the design or manufacture of the part. Everspin<sup>™</sup> and the Everspin logo are

All other product or service names are the property of their respective owners. Copyright © Everspin Technologies, Inc. 2018

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for MRAM category:

Click to view products by Everspin manufacturer:

Other Similar products are found below :

AS3016316-035nX0IBCY AS3032316-035nX0IBCY MR25H256ACDF AS3004316-035nX0ITAY EMD4E001G16G2-150CAS2 MR0A16AYS35 MR25H40MDF MR25H256CDF MR25H40CDF MR25H10CDF MR25H256ACDFR MR2A08AYS35 MR4A08BCYS35 MR4A16BCYS35 MR0D08BMA45R MR4A08BMA35 MR4A08BCMA35 AS1016204-0108X0PWAY AS3004204-0054X0IWAY AS3001204-0054X0IWAY AS3004204-0054X0PWAY MR10Q010SC M3032316045NX0IBCY AS1016204-0108X0PSAY AS3004204-0054X0PSAY AS3004204-0054X0ISAY AS3004204-0108X0PSAY AS3001204-0054X0ISAY MR10Q010CMB MR25H256AMDF MR25H128AMDF MR25H128ACDF MR0A08BMA35 MR0DL08BMA45 MR10Q010VSC MR256A08BMA35 MR25H10MDF MR25H256MDF MR25H40VDF MR2A08ACMA35 MR2A08AMA35 MR2A16AMA35 MR5A16AYS35 MR5A16ACYS35 MR3A16AYS35 MR4A08BUYS45 MR4A08BYS35 MR4A16BCMA35 MR4A16BUYS45 MR5A16AMA35