# FORESEE eMMC FSEIASLD-xxG Datasheet

Version: 1.1

2019.01.04

LONGSYS ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Longsys Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or other-wise.

Longsys products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

For updates or additional information about Longsys products, contact your nearest Longsys office.

All brand names, trademarks and registered trademarks belong to their respective owners.

© 2018 Shenzhen Longsys Electronics Co., Ltd. All rights reserved.

#### **Revision History:**

|   | Rev. | Date       | Changes                     | Remark      |

|---|------|------------|-----------------------------|-------------|

| F | 1.0  | 2018/08/13 | Basic spec and architecture | Preliminary |

|   | 1.1  | 2019/01/04 | Revise some descriptions    |             |

#### CONTENTS

| 1. Ini<br>1       | roduction                           |  |  |  |  |

|-------------------|-------------------------------------|--|--|--|--|

| 2. Pro<br>1       | duct List                           |  |  |  |  |

| 3. Fea<br>1       | . Features                          |  |  |  |  |

| 2                 | nctional Description                |  |  |  |  |

| -                 | duct Specifications                 |  |  |  |  |

| 3                 |                                     |  |  |  |  |

| 5.                | Performance                         |  |  |  |  |

| 5.                | <ul><li>Power Consumption</li></ul> |  |  |  |  |

| 6. Pir<br>4       | Assignments                         |  |  |  |  |

| 6.                | Ball Array view<br>4                |  |  |  |  |

| <b>7. Us</b><br>6 | age Overview                        |  |  |  |  |

| 7.                | General description                 |  |  |  |  |

| 7.3               | Partition Management                |  |  |  |  |

| 7.                | 8 Automatic Sleep Mode              |  |  |  |  |

| 7.4               | Sleep (CMD5)                        |  |  |  |  |

## FORESEE®

|           | 7.5         | H/W Reset operation9       |

|-----------|-------------|----------------------------|

|           | 7.6         | High-speed mode selection9 |

|           | 7.7         | Bus width selection        |

|           | 7.8         | Partition configuration    |

|           | 7.9         | CID register               |

|           |             | CSD register               |

|           | 7.11        | Extended CSD register      |

|           |             | OCR Register               |

|           |             | Field firmware update(FFU) |

|           |             | S.M.A.R.T. Health Report   |

|           | Pack<br>25  | age Dimension              |

|           | Conno<br>26 | ection Guide               |

|           | 9.1<br>26   | Schematic Diagram          |

| 10.<br>27 | Pro         | cessing Guide              |

|           |             |                            |

#### 1. Introduction

FORESEE eMMC is an embedded storage solution designed in the BGA package. The FORESEE eMMC consists of NAND flash and eMMC controller. The controller could manage the interface protocols, wear-leveling, bad block management and ECC.

FORESEE eMMC has high performance at a competitive cost, high quality and low power consumption, and eMMC is compatible with JEDEC standard eMMC 5.1 specifications.

#### 2. Product List

| Density | Part Number   | NAND Flash Type | Capacity | Package Size(mm) | Package Type |

|---------|---------------|-----------------|----------|------------------|--------------|

| 32GB    | FSEIASLD-32G  | 256Gb x1        | 28.8GB   | 11.5x13x1.0      | 153FBGA      |

| 64GB    | FSEIASLD-64G  | 256Gb x2        | 57.6GB   | 11.5x13x1.0      | 153FBGA      |

| 128GB   | FSEIASLD-128G | 256Gb x4        | 115.2GB  | 11.5x13x1.2      | 153FBGA      |

#### 3. Features

#### > eMMC5.1 specification compatibility

(Backward compatible to eMMC4.41/4.5/5.0)

#### Bus mode

- Data bus width: 1 bit (default), 4 bits, 8 bits

- Data transfer rate: up to 400MB/s (HS400)

- MMC I/F Clock frequency : 0~200MHz

#### > Operating voltage range

- Vcc(NAND) : 2.7 3.6V

- Vccq(Controller) : 1.7 1.95V / 2.7 3.6V

- > Temperature

- Operation (-25°C ~ +85°C)

- Storage without operation (-40°C  $\sim$  +85°C)

- > Sudden-Power-Loss safeguard

- > Hardware ECC engine

- Unique firmware backup mechanism

- Global-wear-leveling >

#### Supported features. -

- HS400, HS200

- Partitioning, RPMB

- Boot feature, boot partition

- HW Reset/SW Reset

- Discard, Trim, Erase, Sanitize

- Background operations, HPI

- Enhanced reliable write

- S.M.A.R.T. Health Report

- Command queuing

- FFU

- Sleep / awake

- > Others

- Compliance with the RoHS Directive

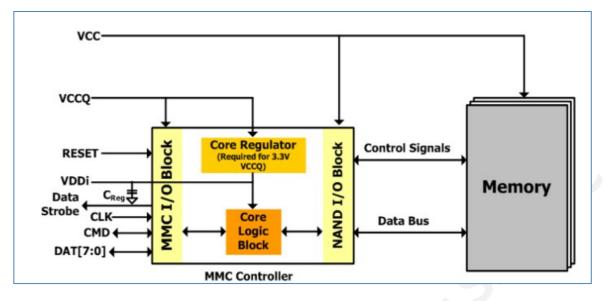

4. Functional Description

FORESEE eMMC with powerful L2P (Logical to Physical) NAND Flash management algorithm provides unique functions:

- > Host independence from details of operating NAND flash

- > Internal ECC to correct defect in NAND flash

## FORESEE®

Sudden-Power-Loss safeguard

To prevent from data loss, a mechanism named Sudden-Power-Loss safeguard is added in the eMMC. In the case of sudden power-failure, the eMMC would work properly after power cycling.

Global-wear-leveling

To achieve the best stability and device endurance, this eMMC equips the Global Wear Leveling algorithm. It ensures that not only normal area, but also the frequently accessed area, such as FAT, would be programmed and erased evenly.

IDA(Initial Data Acceleration)

The eMMC prevents the pre-burned data from data-loss with IDA, in case of our customer had preburned data to eMMC, before the eMMC being SMT.

Cache

The eMMC enhanced the data written performance with Cache, with which our customer would get more endurance and reliability.

> DEVICE TYPE

| Bit | Device Type                                                 | Supportability |

|-----|-------------------------------------------------------------|----------------|

| 7   | HS400 Dual Data Rate eMMC at 200 MHz – 1.2 V I/O            | Not support    |

| 6   | HS400 Dual Data Rate eMMC at 200 MHz – 1.8 V I/O            | Support        |

| 5   | HS200 Single Data Rate eMMC at 200 MHz - 1.2 V I/O          | Not support    |

| 4   | HS200 Single Data Rate eMMC at 200 MHz - 1.8 V I/O          | Support        |

| 3   | High-Speed Dual Data Rate eMMC at 52 MHz - 1.2 V I/O        | Not support    |

| 2   | High-Speed Dual Data Rate eMMC at 52 MHz - 1.8 V or 3 V I/O | Support        |

| 1   | High-Speed eMMC at 52 MHz - at rated device voltage(s)      | Support        |

| 0   | High-Speed eMMC at 26 MHz - at rated device voltage(s)      | Support        |

#### 5. Product Specifications

#### 5.1 Performance

| Part Number   | Write         | Read          |

|---------------|---------------|---------------|

| FSEIASLD-32G  | Up to 120MB/s | Up to 220MB/s |

| FSEIASLD-64G  | Up to 145MB/s | Up to 230MB/s |

| FSEIASLD-128G | Up to 150MB/s | Up to 230MB/s |

- Test Condition: Bus width x8, 200MHz DDR, 512KB data transfer, w/o file system overhead, measured on internal board

- Test tool: uBOOT (Without O/S)

- Chunk size: 1MB,

- Test area: 100MB/ Full-range of LBA.

#### **5.2 Power Consumption**

5.2.1 Active power consumption during operation

| Part Number   | Icc   | Iccq  |

|---------------|-------|-------|

| FSEIASLD-32G  | 100mA | 150mA |

| FSEIASLD-64G  | 120mA | 150mA |

| FSEIASLD-128G | 150mA | 150mA |

- Power Measurement conditions: Bus configuration =x8 @200MHz DDR, 23°C.

- Vcc:3.3V & Vccq: 1.8V.

- The measurement for max RMS current is the average RMS current consumption over a period of 100ms.

#### 5.2.2 Low power mode (stand-by)

| Part Number   | Icc   | Iccq  |

|---------------|-------|-------|

| FSEIASLD-32G  | 70uA  | 150uA |

| FSEIASLD-64G  | 100uA | 160uA |

| FSEIASLD-128G | 130uA | 160uA |

- Power Measurement conditions: Bus configuration =x8 @200MHz DDR, 23°C.

- Standby: Nand Vcc & Controller Vccq power supply is switched on.

- The measurement for max RMS current is the average RMS current consumption over a period of 100ms.

#### 5.2.3 Low power mode (sleep)

| Part Number   | Icc | Iccq  |

|---------------|-----|-------|

| FSEIASLD-32G  | 0   | 150uA |

| FSEIASLD-64G  | 0   | 160uA |

| FSEIASLD-128G | 0   | 160uA |

- Power Measurement conditions: Bus configuration =x8 @200MHz DDR, 23°C.

- Sleep: Nand Vcc power supply is switched off (Controller Vccq on)

- The measurement for max RMS current is the average RMS current consumption over a period of 100ms.

#### 6. Pin Assignments

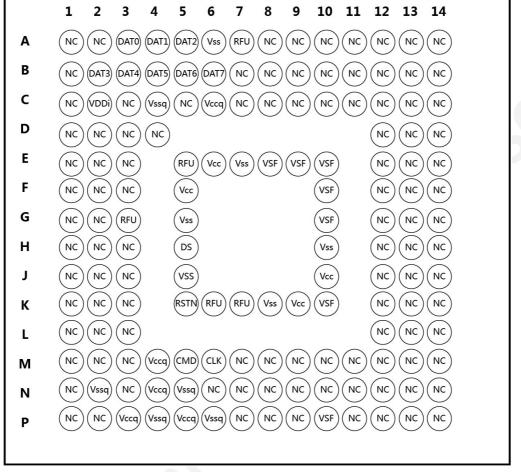

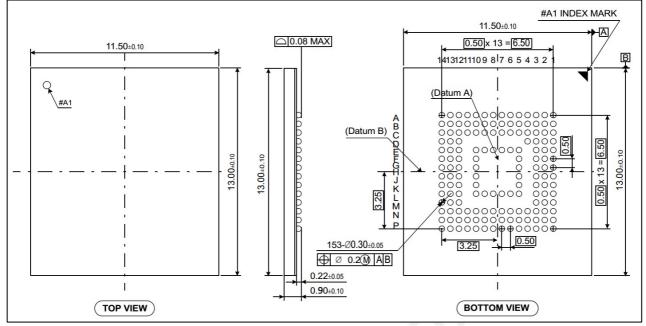

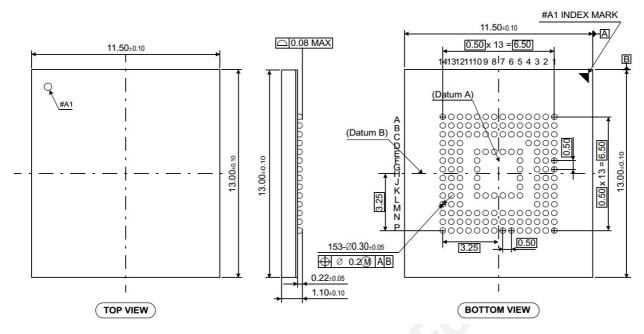

#### 6.1 Ball Array view

FBGA153 - Ball Array (Top View through package)

#### 6.2 Ball Array view

| Signal           | Description                                                                                                                                                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLOCK<br>(CLK)   | Each cycle of the clock directs a transfer on the command line and on the data lines.                                                                                                                                                                                                                                             |

| COMMAND<br>(CMD) | This signal is a bidirectional command channel used for device initialization and<br>command transfer.<br>The CMD Signal has 2 operation modes: open drain, for initialization, and push-<br>pull, for command transfer.<br>Commands are sent from the host to the device, and responses are sent from the<br>device to the host. |

|                     | These are bidirectional data signal. The DAT signals operate in push-pull mode.                                                                                                                                                                                                                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | By default, after power-up or RESET, only DAT0 is used for data transfer. The                                                                                                                                                                                                                                                                                         |

|                     | controller can configure a wider data bus for data transfer wither using DAT                                                                                                                                                                                                                                                                                          |

| DATA                | [3:0](4bit mode)or DAT[7:0](8bit mode).                                                                                                                                                                                                                                                                                                                               |

| DATA<br>(DAT0-DAT7) | Includes internal pull-up resistors for data lines DAT[7:1].Immediately after<br>entering the 4-bit mode, the device disconnects the internal pull-up resistors on<br>the DAT1 and DAT2 lines.(The DAT3 line internal pull-up is left connected.)Upon<br>entering the 8bit mode, the device disconnects the internal pull-up on the DAT1,<br>DAT2, and DAT[7:4]lines. |

|                     | Newly assigned pin for HS400 mode. Data Strobe is generated from e.MMC to host.                                                                                                                                                                                                                                                                                       |

| Data Strobe         | In HS400 mode, read data and CRC response are synchronized with Data Strobe.                                                                                                                                                                                                                                                                                          |

| (DS)                |                                                                                                                                                                                                                                                                                                                                                                       |

| RESET               |                                                                                                                                                                                                                                                                                                                                                                       |

| (RSTN)              | Hardware Reset Input                                                                                                                                                                                                                                                                                                                                                  |

| Vccq                | Vccq is the power supply line for host interface, have two power mode: High power mode:2.7V~3.6V; Lower power mode:1.7V~1.95V                                                                                                                                                                                                                                         |

| Vcc                 | Vcc is the power supply line for internal flash memory, its power voltage range is:2.7V~3.6V                                                                                                                                                                                                                                                                          |

| VDDi                | VDDi is internal power node, not the power supply. Connect 1uF capacitor VDDi to ground                                                                                                                                                                                                                                                                               |

| Vss,Vssq            | Ground lines.                                                                                                                                                                                                                                                                                                                                                         |

#### Note:

NC: No Connect, shall be connected to ground or left floating.

RFU: Reserved for Future Use, must be left floating for future use.

VSF: Vendor Specific Function, must be left floating.

#### 7. Usage Overview 7.1 General description

The eMMC can be operated in 1, 4, or 8-bit mode. NAND flash memory is managed by a controller inside, which manages ECC, wear leveling and bad block management. The eMMC provides easy integration with the host process that all flash management hassles are invisible to the host.

#### 7.2 Partition Management

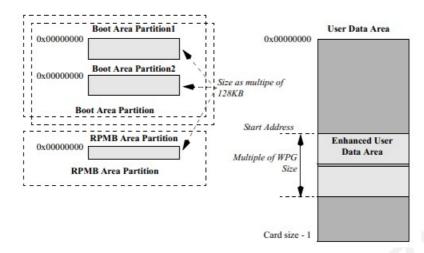

The embedded device offers also the possibility of configuring by the host additional split local memory partitions with independent addressable space starting from logical address 0x00000000 for different usage models. Default size of each Boot Area Partition is 4096 KB and can be changed by Vendor Command as multiple of 128KB. Boot area partition size is calculated as ( 128KB \* BOOT\_SIZE\_MULTI ) The size of Boot Area Partition 1 and 2 cannot be set independently and is set as same value Boot area partition which is enhanced partition. Therefore memory block area scan is classified as follows:

- Factory configuration supplies boot partitions.

- > The RPMB partition is 4MB.

- The host is free to configure one segment in the User Data Area to be implemented as enhanced storage media, and to specify its starting location and size in terms of Write Protect Groups. The attributes of this Enhanced User Data Area can be programmed only once during the device lifecycle (one-time programmable).

- Up to four General Purpose Area Partitions can be configured to store user data or sensitive data, or for other host usage models. The size of these partitions is a multiple of the write protect group. Size and attributes can be programmed once in device life-cycle (one-time programmable). Each of the General Purpose Area Partitions can be implemented with enhanced technological features.

Partitions and user data area configuration

(The size of RPMB area partition is 4MB)

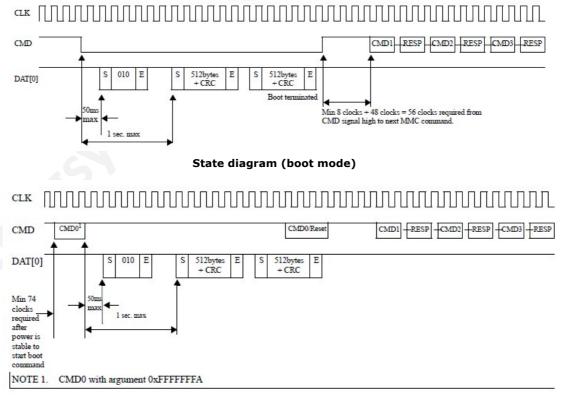

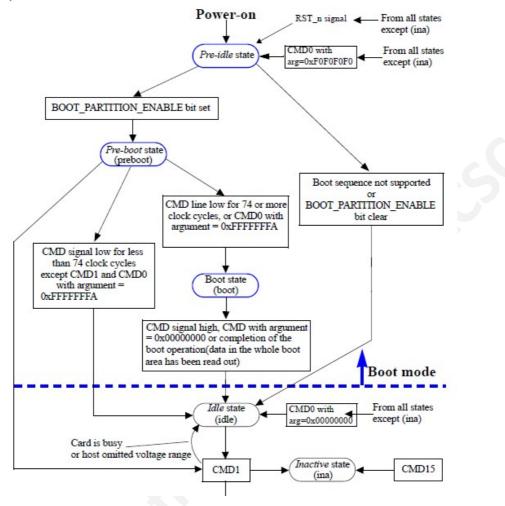

In boot operation mode, the master can read boot data from the slave (device) by keeping CMD line low or sending CMD0 with argument + 0xFFFFFFA, before issuing CMD1. The data can be read from either boot area or user area depending on register setting.

| Timing Factor       | Value   |

|---------------------|---------|

| Boot ACK Time       | < 50 ms |

| Boot Data Time      | < 1 s   |

| Initialization Time | < 1 s   |

State diagram (alternative boot mode)

State diagram (boot mode)\*

#### 7.3 Automatic Sleep Mode

If host does not issue any command during certain duration **(1s)**, after previously issued command is completed, the device enters "Power Saving mode" to reduce power consumption. At this time, commands arriving at the device while it is in power saving mode will be serviced in normal fashion. The below table explains the condition to enter and exit Auto Power Saving Mode

#### 7.4 Sleep (CMD5)

A card may be switched between a Sleep state and a Standby state by SLEEP/AWAKE (CMD5). In the Sleep state the power consumption of the memory device is minimized. In this state the memory device reacts only to the commands RESET (CMD0 with argument of either 0x00000000 or 0xF0F0F0F0 or H/W reset) and SLEEP/AWAKE (CMD5). All the other commands are ignored by the memory device. The timeout for state transitions between Standby state and Sleep state is defined in the EXT\_CSD register S\_A\_timeout. The maximum current consumptions during the Sleep state are defined in the EXT\_CSD registers S\_A\_VCC and S\_A\_VCCQ. Sleep command: The bit 15 as set to 1 in SLEEP/ AWAKE (CMD5) argument. A wake command: The bit 15 as set to 0 in SLEEP/AWAKE (CMD5) argument.

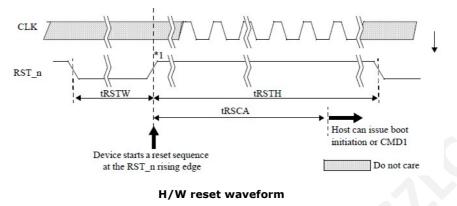

#### 7.5 H/W Reset operation

Device will detect the rising edge of RST\_n signal to trigger internal reset sequence

#### 7.6 High-speed mode selection

After the host verifies that the card complies with version 4.0, or higher, of this standard, it has to enable the high speed mode timing in the card, before changing the clock frequency to a frequency higher than 20MHz. For the host to change to a higher clock frequency, it has to enable the high speed interface timing. The host uses the SWITCH command to write 0x01 to the HS\_TIMING byte, in the Modes segment of the EXT\_CSD register.

#### 7.7 Bus width selection

After the host has verified the functional pins on the bus it should change the bus width configuration accordingly, using the SWITCH command. The bus width configuration is changed by writing to the BUS\_WIDTH byte in the Modes Segment of the EXT\_CSD register (using the SWITCH command to do so). After power-on, or software reset, the contents of the BUS\_WIDTH byte is 0x00.

| Model         | Area/Partition   | Size<br>(GB) | Size<br>(MB) | Size<br>(Sector) | Size (Byte)  | Size (Hex,<br>Byte) |

|---------------|------------------|--------------|--------------|------------------|--------------|---------------------|

| 6             | User             | 28.8GB       | 29600        | 60620800         | 31037849600  | 73A000000           |

|               | Boot Partition 1 | -            | 4            | 8192             | 4194304      | 400000              |

| FSEIASLD-32G  | Boot Partition 2 | -            | 4            | 8192             | 4194304      | 400000              |

|               | RPMB             | -            | 4            | 8192             | 4194304      | 400000              |

|               | User             | 57.6GB       | 59000        | 120832000        | 61865984000  | E67800000           |

|               | Boot Partition 1 | -            | 4            | 8192             | 4194304      | 400000              |

| FSEIASLD-64G  | Boot Partition 2 | -            | 4            | 8192             | 4194304      | 400000              |

|               | RPMB             | -            | 4            | 8192             | 4194304      | 400000              |

| FSEIASLD-128G | User             | 115.2GB      | 118000       | 241664000        | 123731968000 | 1CCF000000          |

#### 7.8 Partition configuration

| Boot Partition 1 | - | 4 | 8192 | 4194304 | 400000 |

|------------------|---|---|------|---------|--------|

| Boot Partition 2 | - | 4 | 8192 | 4194304 | 400000 |

| RPMB             | - | 4 | 8192 | 4194304 | 400000 |

| ·                |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

|                  |   |   |      |         |        |

#### 7.9 CID register

The Card Identification (CID) register is 128 bits wide. It contains the card identification information used during the card identification phase (protocol). Every individual flash or I/O card shall have an unique identification number. Every type of ROM cards (defined by content) shall have a unique identification number. The structure of the CID register is defined in the following sections.

| l               | Name            | Field | Width | CID-slice | CID Value      | Remark         |        |

|-----------------|-----------------|-------|-------|-----------|----------------|----------------|--------|

| Manu            | Manufacturer ID |       | 8     | [127:120] | 88h            |                |        |

| Re              | eserved         | -     | 6     | [119:114] |                |                |        |

| Ca              | ard/BGA         | CBX   | 2     | [113:112] | 01h            | BGA            |        |

| OEM/A           | pplication ID   | OID   | 8     | [111:104] | 03h            | 2              |        |

|                 | FSEIASLD-32G    |       |       |           |                | 0x534C44333247 | SLD32G |

| Product<br>name | FSEIASLD-64G    | PNM   | 48    | [103:56]  | 0x534C44363447 | SLD64G         |        |

| nume            | FSEIASLD-128G   |       |       |           | 0x534c44313238 | SLD128         |        |

| Produ           | ict revision    | PRV   | 8     | [55:48]   |                |                |        |

| Product         | serial number   | PSN   | 32    | [47:16]   |                | Not Fixed      |        |

| Manufa          | cturing date    | MDT   | 8     | [15:8]    |                | Not Fixed      |        |

| CRC7            | checksum        | CRC   | 7     | [7:1]     |                | Not Fixed      |        |

| Not use         | ed, always `1'  | -     | 1     | [0:0]     |                |                |        |

#### 7.10 CSD register

The Card-Specific Data (CSD) register provides information on how to access the card contents. The CSD defines the data format, error correction type, maximum data access time, data transfer speed, whether the DSR register can be used etc. The programmable part of the register (entries marked by W or E, see below) can be changed by CMD27. The type of the CSD Registry entries coded as follows:

| Name                                             | Field              | Width | Cell Type | CSD-slice |

|--------------------------------------------------|--------------------|-------|-----------|-----------|

| CSD structure                                    | CSD_STRUCTURE      | 2     | R         | [127:126] |

| System specification version                     | SPEC_VERS          | 4     | R         | [125:122] |

| Reserved                                         | -                  | 2     | R         | [121:120] |

| Data read access-time 1                          | ТААС               | 8     | R         | [119:112] |

| Data read access-time 2 in CLK cycles (NSAC*100) | NSAC               | 8     | R         | [111:104] |

| Max. bus clock frequency                         | TRAN_SPEED         | 8     | R         | [103:96]  |

| Card command classes                             | ССС                | 12    | R         | [95:84]   |

| Max. read data block length                      | READ_BL_LEN        | 4     | R         | [83:80]   |

| Partial blocks for read allowed                  | READ_BL_PARTIAL    | 1     | R         | [79:79]   |

| Write block misalignment                         | WRITE_BLK_MISALIGN | 1     | R         | [78:78]   |

| Read block misalignment                          | READ_BLK_MISALIGN  | 1     | R         | [77:77]   |

| FORESEE®                        |       |                |          |       |               |   | F         | Rev. 1.1<br>SEIASLD-xxG |

|---------------------------------|-------|----------------|----------|-------|---------------|---|-----------|-------------------------|

| Name Fie                        | ld    | Size           | Туре     |       | lice<br>ytes] | V | alue      | Description             |

| DSR implemented                 | DSF   | R_IMP          |          |       | 1             |   | R         | [76:76]                 |

| Reserved                        | -     |                |          |       | 2             |   | R         | [75:74]                 |

| Device size                     | C_5   | SIZE           |          |       | 12            |   | R         | [73:62]                 |

| Max. read current @VDDmin       | VDI   | D_R_CU         | RR_MIN   |       | 3             |   | R         | [61:59]                 |

| Max. read current @VDD max      | VDI   | D_R_CU         | RR_MAX   |       | 3             |   | R         | [58:56]                 |

| Max. write current $@V_{DD}min$ | VDI   | D_W_CU         | RR_MIN   |       | 3             |   | R         | [55:53]                 |

| Max. write current @VDD max     | VDI   | D_W_CU         | RR_MAX   |       | 3             |   | R         | [52:50]                 |

| Name                            |       | Fi             | eld      |       | Widt          | h | Cell Type | e CSD-slice             |

| Device size multiplier          | C_9   | SIZE_MU        | LT       |       | 3             |   | R         | [49:47]                 |

| Erase group size                | ERA   | SE_GRP         | _SIZE    |       | 5             |   | R         | [46:42]                 |

| Erase group size multiplier     | ERA   | ERASE_GRP_MULT |          | 5     |               | R | [41:37]   |                         |

| Write protect group size        | WP_   | WP_GRP_SIZE    |          |       | 5 R           |   | [36:32]   |                         |

| Write protect group enable      | WP_   | _GRP_M         | ULT      |       | 1             |   | R         | [31:31]                 |

| Manufacturer default ECC        | DEF   | AULT_E         | СС       |       | 2             |   | R         | [30:29]                 |

| Write speed factor              | R2V   | V_FACTO        | DR       |       | 3             |   | R         | [28:26]                 |

| Max. write data block length    | WR    | ITE_BL_        | LEN      |       | 4 R           |   | [25:22]   |                         |

| Partial blocks for write allowe | d WR  | ITE_BL_        | PARTIAL  |       | 1             |   | R         | [21:21]                 |

| Reserved                        | -     |                | 0        |       | 4             |   | R         | [20:17]                 |

| Content protection application  | n COI | NTENT_P        | PROT_APP |       | 1             |   | R         | [16:16]                 |

| File format group               | FIL   | E_FORM         | AT_GRP   |       | 1             |   | R/W       | [15:15]                 |

| Copy flag(OTP)                  | СОГ   | ργ             |          |       | 1             |   | R/W       | [14:14]                 |

| Permanent write protection      | PER   | M_WRIT         | E_PROTE  | СТ    | 1             |   | R/W       | [13:13]                 |

| Temporary write protection      | TM    | P_WRITE        | _PROTECT | Г     | 1             |   | R/W/E     | [12:12]                 |

| File format                     | FILI  | E_FORM         | MAT      |       | 2             |   | R/W       | [11:10]                 |

| ECC code                        | ECO   | CC 2 R/W/E     |          | [9:8] |               |   |           |                         |

| CRC                             | CRO   | 2              |          |       | 7             |   | R/W/E     | [7:1]                   |

| Not used, always '1'            | -     |                |          |       | 1             |   | -         | [0:0]                   |

#### 7.11 Extended CSD register

The Extended CSD register defines the card properties and selected modes. It is 512 bytes long. The most significant 320 bytes are the Properties segment, which defines the card capabilities and cannot be modified by the host. The lower 192 bytes are the Modes segment, which defines the configuration the card is working in. These modes can be changed by the host by means of the SWITCH command.

| Max packed<br>write<br>command                 | MAX_PACKED_WRITES          | 1 | R | [500] | 3Fh |                        |

|------------------------------------------------|----------------------------|---|---|-------|-----|------------------------|

| Data Tag<br>Support                            | DATA_TAD_SUPPORT           | 1 | R | [499] | 1h  | 3                      |

| Tag Unit Size                                  | TAG_UNIT_SIZE              | 1 | R | [498] | 3h  |                        |

| Tag Resource<br>Size                           | TAG_RES_SIZE               | 1 | R | [497] | 0h  |                        |

| Context<br>management<br>capabilities          | CONTEXT_CAPABITILIT<br>IES | 1 | R | [496] | 5h  |                        |

| Large Unit size                                | LARGE_UNIT_SIZE_M1         | 1 | R | [495] | 7h  | Large Unit size<br>8MB |

| Extended<br>partitions<br>attribute<br>support | EXT_SUPPORT                | 1 | R | [494] | 3h  |                        |

| Name                                | Field            | Size | Туре | Slice<br>[bytes] | Value | Description        |

|-------------------------------------|------------------|------|------|------------------|-------|--------------------|

| Reserved                            |                  | 6    | -    | [511:50<br>6]    | -     |                    |

| Extended<br>security error          | EXT_SECURITU_ERR | 1    | R    | [505]            | 0     |                    |

| Supported<br>Command<br>Sets        | S_CMD_SET        | 1    | R    | [504]            | 1h    |                    |

| HPI Features                        | HPI_FEATURES     | 1    | R    | [503]            | 1h    |                    |

| Background<br>operations<br>support | BKOPS_SUPPORT    | 1    | R    | [502]            | 1h    | BKOPS<br>supported |

| Max packed<br>read<br>command       | MAX_PACKED_READS | 1    | R    | [501]            | 3Fh   |                    |

| <b>FORESEE</b> <sup>®</sup> |  |

|-----------------------------|--|

|-----------------------------|--|

|                                          |                                      |      |      | Slice         |       | rseiasld-xxg |

|------------------------------------------|--------------------------------------|------|------|---------------|-------|--------------|

| Name                                     | Field                                | Size | Туре | [bytes]       | Value | Description  |

|                                          |                                      |      |      |               |       |              |

| Supported<br>modes                       | SUPPORTED_MODES                      | 1    | R    | [493]         | 3h    |              |

| FFU features                             | FFU_FEATURES                         | 1    | R    | [492]         | 0h    |              |

| Operation<br>codes timeout               | OPERATION_CODE_TI<br>MEOUT           | 1    | R    | [491]         | 0h    |              |

| FFU Argument                             | FFU_ARG                              | 4    | R    | [490:487]     | 0h    |              |

| Barrier support                          | BARRIER_SUPPORT                      | 1    | R    | [486]         | 0h    | 5            |

|                                          | Reserved                             | 177  | -    | [485:309]     | -     |              |

| CMDQ support                             | CMDQ_SUPPORT                         | 1    | W/R  | [308]         | 1h    |              |

| CMDQ depth                               | CMDQ_DEPTH                           | 1    | W/R  | [307]         | 1Fh   |              |

|                                          | Reserved                             | 1    | -    | [306]         | 0     |              |

| Number of<br>received<br>sectors         | NUMBER_OF_RECEIVE<br>D_SECTORS       | 4    | R    | [305:30<br>2] | Oh    |              |

| Vendor<br>proprietary<br>health report   | VENDOR_PROPRIETARY<br>_HEALTH_REPORT | 1    | R    | [301:27<br>0] | Oh    |              |

| Device life time<br>estimation<br>type B | DEVICE_LIFE_TIME_ES<br>T_TYP_B       | 1    | R    | [269]         | 1h    |              |

|                                          |                                      |      |      |               |       |              |

| FORESEE |

|---------|

|---------|

|                                                 |                                |      |      |                  |        | -SEIASLD-XXG                                      |

|-------------------------------------------------|--------------------------------|------|------|------------------|--------|---------------------------------------------------|

| Name                                            | Field                          | Size | Туре | Slice<br>[bytes] | Value  | Description                                       |

|                                                 |                                |      |      |                  |        |                                                   |

| Device life time<br>estimation<br>type A        | DEVICE_LIFE_TIME_ES<br>T_TYP_A | 1    | R    | [268]            | 1h     |                                                   |

| Pre EOL<br>information                          | PRE_EOL_INFO                   | 1    | R    | [267]            | 1h     | 6                                                 |

| Optimal read size                               | OPTIMAL_READ_SIZE              | 1    | R    | [266]            | 0h     | S                                                 |

| Optimal write size                              | OPTIMAL_WRITE _SIZE            | 1    | R    | [265]            | 20h    |                                                   |

| Optimal trim<br>unit size                       | OPTIMAL_TRIM_UNIT_<br>SIZE     | 1    | R    | [264]            | 1h     |                                                   |

| Device version                                  | DEVICE_VERSION                 | 2    | R    | [263:262]        | 0h     |                                                   |

| Firmware<br>version                             | FIRMWARE_VERSION               | 8    | R    | [261:254]        | -      | FW Patch Ver.                                     |

| Power class<br>for200MHz,<br>DDR at<br>VCC=3.6V | PWR_CL_DDR_200_36<br>0         | 1    | R    | [253]            | 0h     |                                                   |

| Cache size                                      | CACHE_SIZE                     | 4    | R    | [252:24<br>9]    | 10000h |                                                   |

| Generic CMD6<br>timeout                         | GENERIC_CMD6_TIME              | 1    | R    | [248]            | Ah     | Generic CMD6<br>timeout 100ms                     |

| Power-off<br>notification(lo<br>ng) timeout     | POWER_OFF_LONG_TI<br>ME        | 1    | R    | [247]            | 3Ch    | Power off<br>notification(long<br>) timeout 600ms |

| Background<br>operations<br>status              | BKOPS_STATUS                   | 1    | R    | [246]            | 0h     | No operations<br>required                         |

| Number of<br>correctly<br>programmed<br>sectors | CORRECTLY_PRG_SECT<br>ORS_NUM  | 4    | R    | [245:242]        | 0h     |                                                   |

## FORESEE®

|                                                                        |                         |      |      |                  |       | -SEIASLD-XXG                                                           |

|------------------------------------------------------------------------|-------------------------|------|------|------------------|-------|------------------------------------------------------------------------|

| Name                                                                   | Field                   | Size | Туре | Slice<br>[bytes] | Value | Description                                                            |

| Power class for<br>52Mhz,DDR at<br>3.6V                                | PWR_CL_DDR_52_360       | 1    | R    | [239]            | 0h    | rms 100 mA,<br>peak 200 mA                                             |

| Power class for<br>52Mhz,DDR at<br>1.95V                               | PWR_CL_DDR_52_195       | 1    | R    | [238]            | 0h    | rms 65 mA, peak<br>130 mA                                              |

| Power class for<br>200Mhz at<br>VCCQ=1.95V,<br>VCC=3.6V                | PWR_CL_200_195          | 1    | R    | [237]            | 0h    |                                                                        |

| Power class for<br>200Mhz at<br>VCCQ=1.3V,<br>VCC=3.6V                 | PWR_CL_200_360          | 1    | R    | [236]            | Oh    |                                                                        |

| Minimum<br>write<br>performance<br>for 8bit at<br>52MHz in DDR<br>mode | MIN_PERF_DDR_W_8<br>_52 | 1    | R    | [235]            | 0h    | For cards not<br>reaching the 4.8<br>MB/s value<br>Only support<br>SDR |

| Minimum read<br>performance<br>for 8bit at<br>52MHz in DDR<br>mode     | MIN_PERF_DDR_R_8_<br>52 | 1    | R    | [234]            | 0h    | For cards not<br>reaching the<br>4.8MB/s value                         |

| I                                                                      | Reserved                | 1    | -    | [233]            | -     |                                                                        |

| TRIM<br>Multiplier                                                     | TRIM_MULT               | 1    | R    | [232]            | 5h    | trim time out<br>1.5s                                                  |

| First<br>Initialization<br>time after<br>partitioning                  | INI_TIMEOUT_AP          | 1    | R    | [241]            | 1Eh   | initial time out<br>3s                                                 |

| Cache<br>Flushing Policy                                               | CACHE_FLUSH_POLIC<br>Y  | 1    | R    | [240]            | 0h    |                                                                        |

| Name                             | Field                   | Size | Туре | Slice<br>[bytes] | Value | Description                                                                                                                                                                                                                                                    |

|----------------------------------|-------------------------|------|------|------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Secure feature<br>support        | SEC_FEATURE_SUPPO<br>RT | 1    | R    | [231]            | 55h   | <ol> <li>Support the secure and insecure trim operations.</li> <li>Support the automatic secure purge operation on retired defective portions of the array.</li> <li>Secure purge operations are supported.</li> <li>Support the sanitize operation</li> </ol> |

| Secure Erase<br>Multiplier       | SEC_ERASE_MULT          | 1    | R    | [230]            | 1Bh   | secure erase<br>time out 40.5s                                                                                                                                                                                                                                 |

| Secure TRIM<br>Multiplier        | SEC_TRIM_MULT           | 1    | R    | [229]            | 11h   | secure trim time<br>out 25.5s                                                                                                                                                                                                                                  |

| Boot<br>Information              | BOOT_INFO               | 1    | R    | [228]            | 7h    | <ol> <li>Support high<br/>speed timing<br/>boot.</li> <li>Support dual<br/>data rate<br/>during boot</li> <li>Support<br/>alternative<br/>boot method</li> </ol>                                                                                               |

|                                  | Reserved                | 1    | -    | [227]            | -     |                                                                                                                                                                                                                                                                |

| Boot partition size              | BOOT_SIZE_MULTI         | 1    | R    | [226]            | 20h   | boot partition<br>4096KB                                                                                                                                                                                                                                       |

| Access size                      | ACC_SIZE                | 1    | R    | [225]            | 6h    | super page<br>16KB                                                                                                                                                                                                                                             |

| High-capacity<br>Erase unit size | HC_ERASE_GROUP_SI<br>ZE | 1    | R    | [224]            | 1h    | hc erase group<br>size 512KB                                                                                                                                                                                                                                   |

| FO | RES | EE |

|----|-----|----|

|    |     |    |

|                                                       |                                            |      |      | 1                |       | -SEIASLD-XXG                                  |

|-------------------------------------------------------|--------------------------------------------|------|------|------------------|-------|-----------------------------------------------|

| Name                                                  | Field                                      | Size | Туре | Slice<br>[bytes] | Value | Description                                   |

| High-capacity<br>Erase time out                       | ERASE_TIMEOU_MULT                          | 1    | R    | [223]            | 5h    | hc erase time<br>out 1.5s                     |

| Reliable write sector count                           | REL_WR_SEC_C                               | 1    | R    | [222]            | 1h    | 1 sector                                      |

| High-capacity<br>write protect<br>group size          | HC_WP_GRP_SIZE                             | 1    | R    | [221]            | 8h    | hc wp group size<br>4096KB                    |

| Sleep<br>current(VCC)                                 | S_C_VCC                                    | 1    | R    | [220]            | 7h    | 128µA                                         |

| Sleep<br>current[VCCQ<br>]                            | S_C_VCCQ                                   | 1    | R    | [219]            | 7h    | 128µA                                         |

| Production<br>state<br>awareness<br>timeout           | PRODUCTION_STATE_<br>AWARENESS_TIMEOU<br>T | 1    | R    | [218]            | Oh    | Not defined                                   |

| Sleep/Awake<br>time out                               | S_A_TIMEOUT                                | 1    | R    | [217]            | 16h   | Sleep/Awake<br>timeout<br>419.43ms            |

| Sleep<br>Notification<br>Time out                     | SLEEP_NOTIFICATION<br>_TIME                | 1    | R    | [216]            | 10h   | Sleep<br>Notification<br>Time out<br>655.36ms |

| Sector count                                          | SEC_COUNT                                  | 4    | R    | [215:212]        | -     | depend on<br>density                          |

| Secure Write<br>Protection<br>Mode                    | SECURE_WP_INFO                             | 1    |      | [211]            | 1h    |                                               |

| Minimum<br>Write<br>Performance<br>for 8bit<br>@52MHz | MIN_PERF_W_8_52                            | 1    | R    | [210]            | 0h    |                                               |

|                                                                        |                          |      |      |                  |       | -SEIASLD-XXG               |

|------------------------------------------------------------------------|--------------------------|------|------|------------------|-------|----------------------------|

| Name                                                                   | Field                    | Size | Туре | Slice<br>[bytes] | Value | Description                |

| Minimum<br>Read<br>Performance<br>for 8bit<br>@52MHz                   | MIN_PERF_R_8_52          | 1    | R    | [209]            | 0h    |                            |

| Minimum Write<br>Performance<br>for 4bit<br>@52MHz or<br>8bit @26MHz   | MIN_PERF_W_8_26_4<br>_52 | 1    | R    | [208]            | 0h    | S                          |

| Minimum<br>Read<br>Performance<br>for 4bit<br>@52MHz or<br>8bit @26MHz | MIN_PERF_R_8_26_4_<br>52 | 1    | R    | [207]            | Oh    |                            |

| Minimum<br>Write<br>Performance<br>for 4bit<br>@26MHz                  | MIN_PERF_W_4_26          | 1    | R    | [206]            | 0h    |                            |

| Minimum<br>Read<br>Performance<br>for 4bit<br>@26MHz                   | MIN_PERF_R_4_26          | 1    | R    | [205]            | 0h    |                            |

|                                                                        | Reserved                 | 1    | -    | [204]            | -     |                            |

| Power Class<br>for 26MHz<br>@3.6V                                      | PWR_CL_26_360            | 1    | R    | [203]            | Oh    | rms 100 mA,<br>peak 200 mA |

| Power Class<br>for 52MHz<br>@3.6V                                      | PWR_CL_52_360            | 1    | R    | [202]            | 0h    | rms 100 mA,<br>peak 200 mA |

| Power Class<br>for 26MHz<br>@1.95V                                     | PWR_CL_26_195            | 1    | R    | [201]            | 0h    | rms 65 mA,<br>peak 130 mA  |

|   |  | _ | R |

|---|--|---|---|

|   |  |   |   |

| Г |  |   |   |

|                                    | JEE                       |      |             |                  |       | FSEIASLD-xx(                          |

|------------------------------------|---------------------------|------|-------------|------------------|-------|---------------------------------------|

| Name                               | Field                     | Size | Туре        | Slice<br>[bytes] | Value | Description                           |

| Power Class<br>for 52MHz<br>@1.95V | PWR_CL_52_195             | 1    | R           | [200]            | Oh    | rms 65 mA,<br>peak 130 mA             |

| Partition<br>switching<br>timing   | PARTITION_SWITCH_T<br>IME | 1    | R           | [199]            | Ah    | Partition swite<br>time out 100ms     |

| Out-of-interru<br>pt busy timing   | OUT_OF_INTERRUPT_T<br>IME | 1    | R           | [198]            | 5h    | HPI time out<br>50ms                  |

| I/O Driver<br>Strength             | DRIVER_STRENGTH           | 1    | R           | [197]            | 1h    |                                       |

| Card Type                          | CARD_TYPE                 | 1    | R           | [196]            | 57h   | HS400 DDR<br>eMMC@200Mhz<br>-1.8V I/O |

|                                    | Reserved                  | 1    | -           | [195]            | 9 -   |                                       |

| CSD Structure<br>Version           | CSD_STRUCTURE             | 1    | R           | [194]            | 2h    | CSD version No<br>1.2                 |

|                                    | Reserved                  | 1    |             | [193]            | -     |                                       |

| Extended CSD<br>Revision           | EXT_CSD_REV               | 1    | R           | [192]            | 8h    | Revision 1.8 (fo<br>MMC v5. 1)        |

| Command Set                        | CMD_SET                   | 1    | R/W/E<br>_P | [191]            | 0h    |                                       |

|                                    | Reserved                  | 1    | -           | [190]            | -     |                                       |

| Command set revision               | CMD_SET_REV               | 1    | R           | [189]            | 0h    |                                       |

|                                    | Reserved                  | 1    | -           | [188]            | -     |                                       |

| Power class                        | POWER_CLASS               | 1    | R/W/E<br>_P | [187]            | 0h    |                                       |

|                                    | Reserved                  | 1    | -           | [186]            | -     |                                       |

| High Speed<br>Interface<br>Timing  | HS_TIMING                 | 1    | R/W/E<br>_P | [185]            | Oh    |                                       |

| Strobe<br>Support                  | STROBE_SUPPORT            | 1    | R           | [184]            | 1h    |                                       |

| Bus Width<br>Mode                  | BUS_WIDTH                 | 1    | W/E_P       | [183]            | 0h    |                                       |

|                                    | Reserved                  | 1    | -           | [182]            | -     |                                       |

| FORESEE | FO | R | ES | R |

|---------|----|---|----|---|

|---------|----|---|----|---|

| Name                                            | Field            | Size | Туре                 | Slice<br>[bytes] | Value | Description |

|-------------------------------------------------|------------------|------|----------------------|------------------|-------|-------------|

|                                                 |                  |      |                      |                  | _     |             |

| Erased<br>memory range                          | ERASE_MEM_CONT   | 1    | R                    | [181]            | 0h    |             |

|                                                 | Reserved         | 1    | -                    | [180]            | -     |             |

| Partition<br>Configuration                      | PARTITION_CONFIG | 1    | R/W/E<br>R/W/E<br>_P | [179]            | Oh    |             |

| Boot config<br>protection                       | BOOT_CONFIG_PROT | 1    | R/W<br>R/W/C<br>_P   | [178]            | Oh    | S           |

| Boot bus<br>width1                              | BOOT_BUS_WIDTH   | 1    | R/W/E                | [177]            | 0h    |             |

|                                                 | Reserved         | 1    | -                    | [176]            |       |             |

| High-density<br>erase group<br>definition       | ERASE_GROUP_DEF  | 1    | R/W/E<br>_P          | [175]            | Oh    |             |

| Boot write<br>protection<br>status<br>registers | BOOT_WP_STATUS   | 1    | R                    | [174]            | Oh    |             |

| Boot area<br>write protect<br>register          | BOOT_WP          | 1    | R/W<br>R/W/C<br>_P   | [173]            | 0h    |             |

|                                             | Reserved       | 1 | -                                 | [172] | -   |                     |

|---------------------------------------------|----------------|---|-----------------------------------|-------|-----|---------------------|

| User area<br>write protect<br>register      | USER_WP        | 1 | R/W<br>R/W/C<br>_P<br>R/W/E<br>_P | [171] | 0h  |                     |

|                                             | Reserved       | 1 | -                                 | [170] | -   |                     |

| FW<br>Configuration                         | FW_CONFIG      | 1 | R/W                               | [169] | 0h  |                     |

| RPMB Size                                   | RPMB_SIZE_MULT | 1 | R                                 | [168] | 20h | RPMB size is<br>4MB |

| Write<br>reliability<br>setting<br>register | WR_REL_SET     | 1 | R/W                               | [167] | 1Fh |                     |

|                                                 | _              |      |             |                  |       | SEIASLD-XXG                                                |

|-------------------------------------------------|----------------|------|-------------|------------------|-------|------------------------------------------------------------|

| Name                                            | Field          | Size | Туре        | Slice<br>[bytes] | Value | Description                                                |

| Write<br>reliability<br>parameter<br>register   | WR_REL_PARAM   | 1    | R           | [166]            | 15h   | Support the<br>enhanced<br>definition of<br>reliable write |

| Start Sanitize operation                        | SANITIZE_START | 1    | W/E_P       | [165]            | 0h    |                                                            |

| Manually start<br>background<br>operations      | BKOPS_START    | 1    | W/E_P       | [164]            | 0h    | 3                                                          |

| Enable<br>background<br>operations<br>handshake | BKOPS_EN       | 1    | R/W         | [163]            | 0h    |                                                            |

| H/W reset<br>function                           | RST_n_FUNCTION | 1    | R/W         | [162]            | Oh    |                                                            |

| HPI<br>management                               | HPI_MGMT       | 1    | R/W/E<br>_P | [161]            | 0h    |                                                            |

| Partitioning<br>support   | PARTITIONING_SUPP<br>ORT         | 1 | R   | [160]         | 7h   | <ol> <li>Enhanced<br/>technological<br/>features in<br/>partitions and<br/>user data area.</li> <li>Device<br/>supports<br/>partitioning<br/>features</li> <li>Device can<br/>have extended<br/>partition<br/>attribute</li> </ol> |

|---------------------------|----------------------------------|---|-----|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Max Enhanced<br>Area Size | MAX_ENH_SIZE_MULT                | 3 | R   | [159:15<br>7] | 100h |                                                                                                                                                                                                                                    |

| Partitions<br>attribute   | PARTITIONS_ATTRIBU<br>TE         | 1 | R/W | [156]         | 0h   |                                                                                                                                                                                                                                    |

| Partitions<br>setting     | PARTITIONS_SETTING<br>_COMPLETED | 1 | R/W | [155]         | 0h   |                                                                                                                                                                                                                                    |

Rev. 1.1 FSEIA<u>SLD-xxG</u>

|                                              |                                 |      |                                            |                  |       | FSEIASLD-xxG |  |

|----------------------------------------------|---------------------------------|------|--------------------------------------------|------------------|-------|--------------|--|

| Name                                         | Field                           | Size | Туре                                       | Slice<br>[bytes] | Value | Description  |  |

| General<br>Purpose<br>Partition Size         | GP_SIZE_MULT                    | 12   | R/W                                        | [154:14<br>3]    | 0h    |              |  |

| Enhanced<br>User Data<br>Area Size           | ENH_SIZE_MULT                   | 3    | R/W                                        | [142:14<br>0]    | 0h    |              |  |

| Enhanced<br>User Data<br>Start Address       | ENH_START_ADDR                  | 4    | R/W                                        | [139:13<br>6]    | Oh    | 6            |  |

|                                              | Reserved                        | 1    | -                                          | [135]            | -     |              |  |

| Secure Bad<br>Block<br>Management<br>Mode    | SEC_BAD_BLK_MGMN<br>T           | 1    | R/W                                        | [134]            | Oh    |              |  |

| Production<br>state<br>awareness             | PRODUCTION_STATE_<br>AWARENESS  | 1    | R/W/E                                      | [133]            | 0h    |              |  |

| Package Case<br>Temperature is<br>controlled | TCASE_SUPPORT                   | 1    | W/E_P                                      | [132]            | Oh    |              |  |

| Periodic<br>Wake-up                          | PERIODIC_WAKEUP                 | 1    | R/W/E                                      | [131]            | 0h    |              |  |

| Program<br>CID/CSD in<br>DDR mode<br>support | PROGRAM_CID_CSD_<br>DDR_SUPPORT | 1    | R                                          | [130]            | 1h    |              |  |

|                                              | Reserved                        | 2    | -                                          | [129:12<br>8]    | -     |              |  |

| Vendor<br>specific field                     | VENDOR_SPECIFIC_FI<br>ELD       | 64   | <vend<br>or<br/>specfic<br/>&gt;</vend<br> | [127:64]         | Oh    |              |  |

| Native sector size                           | NATIVE_SECTOR_SIZ<br>E          | 1    | R                                          | [63]             | 0h    |              |  |

|           |    | R |

|-----------|----|---|

|           | EC |   |

| <b>FU</b> |    |   |

|                                                                   |                              |      |             |                  |       | SLIASLD-XXG |

|-------------------------------------------------------------------|------------------------------|------|-------------|------------------|-------|-------------|

| Name                                                              | Field                        | Size | Туре        | Slice<br>[bytes] | Value | Description |

| Sector size emulation                                             | USE_NATIVE_SECTOR            | 1    | R/W         | [62]             | 0h    |             |

| Sector size                                                       | DATA_SECTOR_SIZE             | 1    | R           | [61]             | 0h    |             |

| 1st initialization<br>after disabling<br>sector size<br>emulation | INI_TIMEOUT_EMU              | 1    | R           | [60]             | 0h    | S           |

| Class 6<br>commands<br>control                                    | CLASS_6_CTRL                 | 1    | R/W/E<br>_P | [59]             | 0h    |             |

| Number of<br>addressed<br>group to be<br>Released                 | DYNCAP_NEEDED                | 1    | R           | [58]             | Oh    |             |

| Exception<br>events control                                       | EXCEPTION_EVENTS_<br>CTRL    | 2    | R/W/E<br>_P | [57:56]          | 0h    |             |

| Exception<br>events status                                        | EXCEPTION_EVENTS_<br>STATUS  | 2    | R           | [55:54]          | 0h    |             |

| Extended<br>Partitions<br>Attribute                               | EXT_PARTITIONS_ATT<br>RIBUTE | 2    | R/W         | [53:52]          | 0h    |             |

| Context configuration                                             | CONTEXT_CONF                 | 15   | R/W/E<br>_P | [51:37]          | 0h    |             |

| Packed<br>command<br>status                                       | PACKED_COMMAND_S<br>TATUS    | 1    | R           | [36]             | Oh    |             |

| Packed<br>command<br>failure index                                | PACKED_FAILURE_IN<br>DEX     | 1    | R           | [35]             | 0h    |             |

Notes: 1. R= Read-only

R/W=One-Time Programmable and readable

R/W/E=Multiple writable with value kept after a power cycle, assertion of the RST\_n signal, and any CMD0 reset, and readable

TBD=To Be Defined.

### FORESEE®

|                                          |                                            |      |             |                  |       | FSEIASLD-xxG |

|------------------------------------------|--------------------------------------------|------|-------------|------------------|-------|--------------|

| Name                                     | Field                                      | Size | Туре        | Slice<br>[bytes] | Value | Description  |

| Power Off<br>Notification                | POWER_OFF_NOTIFIC<br>ATION                 | 1    | R/W/E<br>_P | [34]             | 0h    |              |

| Control to turn<br>the Cache<br>ON/OFF   | ON/OFF CACHE_CTRL                          | 1    | R/W/E<br>_P | [33]             | Oh    |              |

| Flushing of the cache                    | FLUSH_CACHE                                | 1    | W/E_P       | [32]             | 0h    | 6            |

| Control to turn<br>the Barrier<br>ON/OFF | ON/OFF<br>BARRIER_CTRL                     | 1    | R/W         | [31]             | 0h    | 6            |

| Mode config                              | MODE_CONFIG                                | 1    | R/W/E<br>_P | [30]             | 0h    |              |

| Mode<br>operation<br>codes               | MODE_OPERATION_C<br>ODES                   | 1    | W/E_P       | [29]             | Oh    |              |

| F                                        | Reserved                                   | 2    | -           | [28:27]          | -     |              |

| FFU status                               | FFU_STATUS                                 | 1    | R           | [26]             | 0h    |              |

| Pre loading<br>data size                 | PRE_LOADING_DATA_<br>SIZE                  | 4    | R/W/E<br>_P | [25:22]          | 0h    |              |

| Max pre<br>loading data<br>size          | MAX_PRE_LOADING_<br>DATA_SIZE              | 4    | R           | [21:18]          | -     |              |

| Product state<br>awareness<br>enablement | PRODUCT_STATE_AW<br>ARENESS_ENABLEME<br>NT | 1    | R/W/E<br>&R | [17]             | Oh    |              |

| Secure<br>Removal Type                   | SECURE_REMOVAL_TY<br>PE                    | 1    | R/W&<br>R   | [16]             | 9h    |              |

| Command<br>Queue Mode<br>Enable          | CMDQ_MODE_EN                               | 1    | R/W/E<br>_P | [15]             | 0h    |              |

| F                                        | Reserved                                   | 15   | -           | [14:0]           | -     |              |

2. Reserved bits should be read as 0.

#### 7.12 OCR Register

The 32-bit operation conditions register stores the VCCQ voltage profile of the eMMC. In addition, this register includes a status information bit. This status bit is set if the eMMC power up procedure has been finished. The OCR register shall be implemented by eMMC.

| OCR bit | VCCQ voltage window         | eMMC                                 |

|---------|-----------------------------|--------------------------------------|

| [6:0]   | Reserved                    | 000 0000b                            |

| [7]     | 1.7-1.95                    | 1b                                   |

| [14:8]  | 2.0-2.6                     | 000 0000b                            |

| [23:15] | 2.7-3.6                     | 1 1111 1111b                         |

| [28:24] | Reserved                    | 000 0000b                            |

| [30:29] | Access Mode                 | 00b (byte mode)/10b (sector<br>mode) |

| [31]    | power up status bit (busy)* |                                      |

**Note\*:** This bit is set to LOW if the eMMC has not finished the power up routine. The supported voltage range is coded as shown in table.

#### 7.13 Field firmware update(FFU)

To download a new firmware, the controller requires instruction sequence following JEDEC standard. Longsys eMMC only supports Manual mode (MODE\_OPERATION\_CODES is not supported). For more details, refer to the App note.

| Operation                      | CMD                        | Remark                                                                                                                                                          |

|--------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set block length 512B          | CMD16, arg :<br>0x00000200 |                                                                                                                                                                 |

| Enter FFU mode                 | CMD6, arg : 0x031E0100     |                                                                                                                                                                 |

| Send FW to<br>device(Download) | CMD25, arg :<br>0x0000000  | Sending CMD25 is followed by sending FW data ,The whole data should be sent by one CMD25                                                                        |

| CMD12 : Stop                   | CMD12, arg :<br>0x00000000 |                                                                                                                                                                 |

| CMD6 : Exit FFU mode           | CMD6, arg : 0x031E0000     |                                                                                                                                                                 |

| HW Reset/Power cycle           |                            | CMD0 Reset is not support                                                                                                                                       |

| Re-Init to trans state         | CMD0, CMD1                 |                                                                                                                                                                 |

| Check if FFU is succeeded      | CMD8, arg : 0x00000000     | Check EXT_CSD[26] : FFU_SUCCESS<br>If FFU_SUCCESS is 0, FFU is succeeded, otherwise<br>FFU is failed.<br>Do not verify data with CMD17/CMD18 while FFU<br>mode. |

#### Longsys eMMC (FSEIASLD-xxG) Field F/W update flow - CMD sequence

#### SUPPORTED\_MODE[493] (Read Only)

BIT[0] : '0' FFU is not supported by the device.

'1' FFU is supported by the device.

BIT[1]: '0' Vendor specific mode (VSM) is not supported by the device.

#### `1' Vendor specific mode is supported by the device.

| Bit      | Field    | Supportability |

|----------|----------|----------------|

| Bit[7:2] | Reserved | -              |

| Bit[1]   | VSM      | Not support    |

| Bit[0]   | FFU      | Support        |

#### FFU\_FEATURE[492] (Read Only)

BIT[0] : `0' Device does not support MODE\_OPERATION\_CODES field (Manual mode) `1' Device supports MODE\_OPERATION\_CODES field (Auto mode)

| Bit      | Field                          | Supportability |

|----------|--------------------------------|----------------|

| Bit[7:1] | Reserved                       | 5              |

| Bit[0]   | SUPPORTED_MODE_OPERATION_CODES | Not support    |

#### FFU\_ARG[490-487] (Read Only)

Using this field the device reports to the host which value the host should set as an argument for read and write commands in FFU mode.

#### FW\_CONFIG[169] (R/W)

BIT[0] : Update disable

0x0 : FW updates enabled

0x1 : FW update disabled permanently

| Bit      | Field          | Supportability           |

|----------|----------------|--------------------------|

| Bit[7:1] | Reserved       | -                        |

| Bit[0]   | Update disable | FW updates enabled (0x0) |

#### FFU\_STATUS[26] (R/W/E\_P)

Using this field the device reports to the host the state of FFU process

| Value       | Description                      |

|-------------|----------------------------------|

| 0x13 ~ 0xFF | Reserved                         |

| 0x12        | Error in downloading<br>Firmware |

| 0x11        | Firmware install error           |

| 0x10        | General error                    |

| 0x01 ~ 0x0F | Reserved                         |

| 0×00        | Success                          |

#### OPERATION\_CODES\_TIMEOUT[491](Read Only)

Maximum timeout for the SWITCH command when setting a value to the MODE\_OPERATION\_CODES field. The register is set to '0', because the controller doesn't support MODE\_OPERATION\_CODES.

| Value       | Description                            | Timeout value |

|-------------|----------------------------------------|---------------|

| 0x01 ~ 0x17 | MODE_OPERATION_CODES_TIMEOUT = 100us x | (Not defined) |

|             | 20PERATION_CODES_TIMEOUT               |               |

| 0x18 ~ 0xFF | Reserved                               | - (           |

#### MODE\_OPERATION\_CODES[29] (W/E\_P)

The host sets the operation to be performed at the selected mode, in case MODE\_CONFIGS is set to FFU\_MODE,MODE\_OPERATION\_CODES could have the following values :

| Value        | Description |

|--------------|-------------|

| 0x01         | FFU_INSTALL |

| 0x02         | FFU_ABORT   |

| 0x00, others | Reserved    |

#### 7.14 S.M.A.R.T. Health Report

S.M.A.R.T. is a monitoring system that detects and reports on various indicators of eMMC reliability(Including original bad blocks, increased bad blocks, power-up number, power-loss counts and etc), with the intent of enabling the anticipation of hardware failures. We may be able to use recorded S.M.A.R.T. data to discover where the faults lie, ensure how to solve the problems and prevent them from recurring in future eMMC designs (For details, please refer to app note).

Page 28

11.5mm x 13.0mm x 1.0mm Package Dimension

11.5mm x 13.0mm x 1.2mm Package Dimension

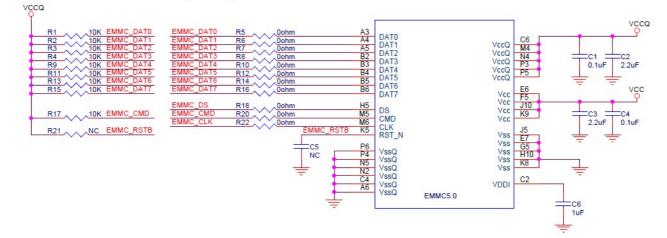

#### 9 Connection Guide 9.1 Schematic Diagram

- > Coupling capacitor should be connected with VCC/VCCQ and VSS as closely as possible.

- > The resistance on the CLK line is highly recommended ( $0\Omega$  by default).  $0\Omega \sim 100\Omega$  is also available.