#### ... scale Semiconductor

Data Sheet: Technical Data

Document Number: MMA52xxKW Rev. 11, 08/2012

**√RoHS**

# Xtrinsic MMA52xxKW PSI5 Inertial Sensor

The MMA52xxKW family, a SafeAssure solution, includes the AKLV27 and PSI5 Version 1.3 compatible overdamped X-axis satellite accelerometers.

#### **Features**

- ±60g to ±480g Full-Scale Range

- Selectable 400 Hz, 3 Pole, or 4 pole Low-Pass Filter

- Single Pole High Pass Filter with Fast Startup and Output Rate Limiting

- PSI5 Version 1.3 Compatible

- PSI5-P10P-500/3L Compatible

- Programmable Time Slots with 0.5 μs Resolution

- Selectable Baud Rate: 125 kBaud or 190.5 kBaud

- Selectable Data Length: 8 or 10 bits

- Selectable Error Detection: Even Parity, or 3-bit CRC

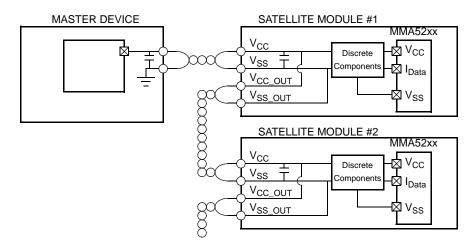

- Optional Daisy Chain with External Low-Side Switch

- Two-Wire Programming Mode

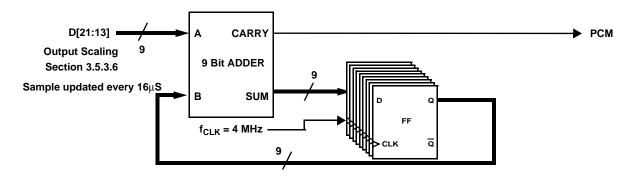

- 16 μs Internal Sample Rate, with Interpolation to 1 μs

- Pb-Free 16-Pin QFN, 6 by 6 Package

- Qualified AECQ100, Revision G, Grade 1 (-40°C to +125°C) (http://www.aecouncil.com/)

#### **Typical Applications**

· Airbag Front and Side Crash Detection

|             | OR   | DERING INFO | RMATION |             |

|-------------|------|-------------|---------|-------------|

| Device      | Axis | Range       | Package | Shipping    |

| MMA5206KW   | Х    | 60g         | 2086-01 | Tubes       |

| MMA5212KW   | Х    | 120g        | 2086-01 | Tubes       |

| MMA5224KW   | Х    | 240g        | 2086-01 | Tubes       |

| MMA5248KW   | Х    | 480g        | 2086-01 | Tubes       |

| MMA5206KWR2 | Х    | 60g         | 2086-01 | Tape & Reel |

| MMA5212KWR2 | Х    | 120g        | 2086-01 | Tape & Reel |

| MMA5224KWR2 | Х    | 240g        | 2086-01 | Tape & Reel |

| MMA5248KWR2 | Х    | 480g        | 2086-01 | Tape & Reel |

For user register array programming, please consult your Freescale representative.

## MMA52xxKW

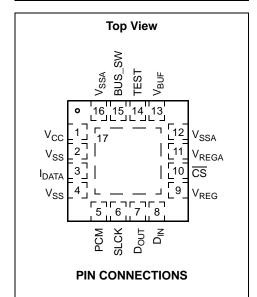

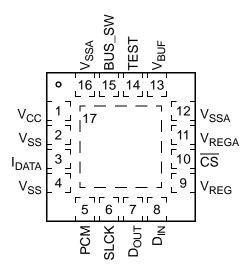

## **Bottom View**

16-PIN QFN CASE 2086-01

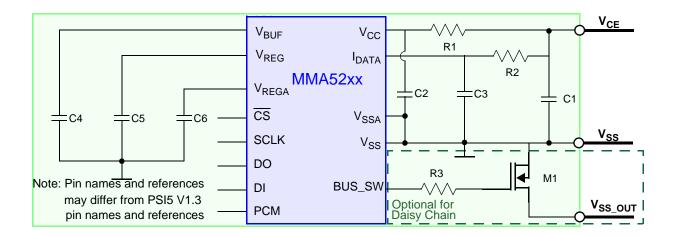

## **Application Diagram**

Figure 1. Application Diagram

|            |                  | External Component Recomme    | endations                                                  |

|------------|------------------|-------------------------------|------------------------------------------------------------|

| Ref Des    | Туре             | Description                   | Purpose                                                    |

| C1         | Ceramic          | 2.2 nF, 10%, 50V minimum, X7R | V <sub>CC</sub> Power Supply Decoupling and Signal Damping |

| C3         | Ceramic          | 470 pF, 10%, 50V minimum, X7R | I <sub>DATA</sub> Filtering and Signal Damping             |

| C2         | Ceramic          | 15 nF, 10%, 50V minimum, X7R  | V <sub>CC</sub> Power Supply Decoupling                    |

| C4, C5, C6 | Ceramic          | 1 μF, 10%, 10V minimum, X7R   | Voltage Regulator Output Capacitor(s)                      |

| R1         | General Purpose  | 82Ω, 5%, 200 PPM              | V <sub>CC</sub> Filtering and Signal Damping               |

| R2         | General Purpose  | 27Ω, 5%, 200 PPM              | I <sub>DATA</sub> Filtering and Signal Damping             |

| R3         | General Purpose  | 20 kΩ, 5%, 200 PPM            | Gate Resistor for External Low-Side Daisy Chain FET        |

| M1         | N-Channel MOSFET | _                             | Low-Side Daisy Chain Transistor                            |

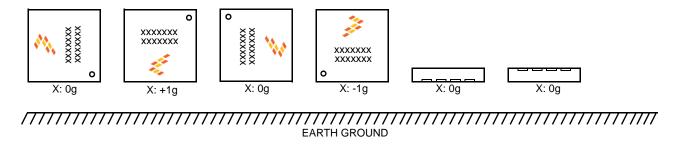

#### **Device Orientation**

Figure 2. Device Orientation Diagram

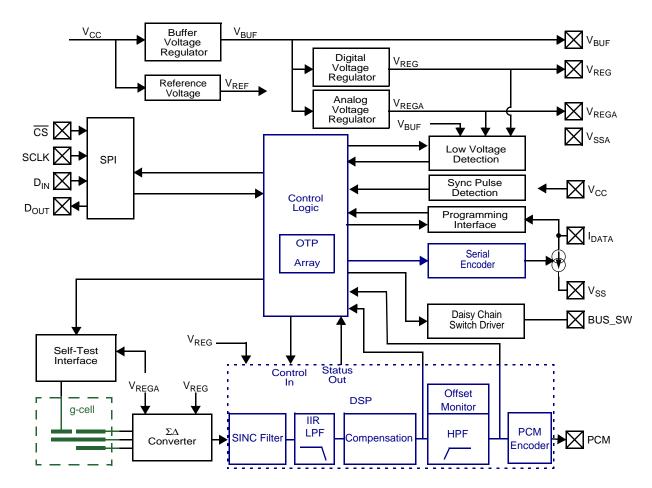

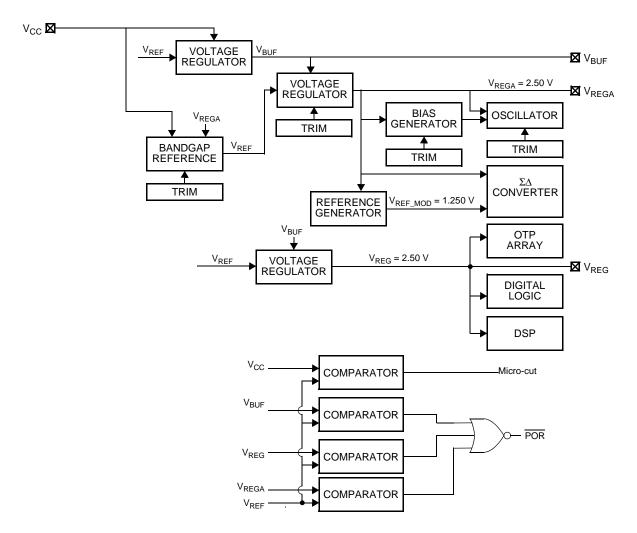

## **Internal Block Diagram**

Figure 3. Block Diagram

## 1 Pin Connections

Figure 4. Top View, 16-Pin QFN Package

**Table 1. Pin Description**

| Pin | Pin               | Formal Name              | Definition                                                                                                                                                                                                                                                                                                                         |

|-----|-------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Name              |                          |                                                                                                                                                                                                                                                                                                                                    |

| 1   | V <sub>CC</sub>   | Supply                   | This pin is connected to the PSI5 power and data line through a resistor and supplies power to the device. An external capacitor must be connected between this pin and $V_{SS}$ . Reference Figure 1.                                                                                                                             |

| 2   | V <sub>SS</sub>   | Digital GND              | This pin is the power supply return node for the digital circuitry.                                                                                                                                                                                                                                                                |

| 3   | I <sub>DATA</sub> | Response<br>Current      | This pin is connected to the PSI5 power and data line through a resistor and modulates the response current for PSI5 communication. Reference Figure 1.                                                                                                                                                                            |

| 4   | V <sub>SS</sub>   | Digital GND              | This pin is the power supply return node for the digital circuitry.                                                                                                                                                                                                                                                                |

| 5   | PCM               | PCM<br>Output            | This pin provides a 4 MHz PCM signal proportional to the acceleration data for test purposes. The output can be enabled via OTP. Reference Section 3.5.3.7. If unused, this pin must be left unconnected.                                                                                                                          |

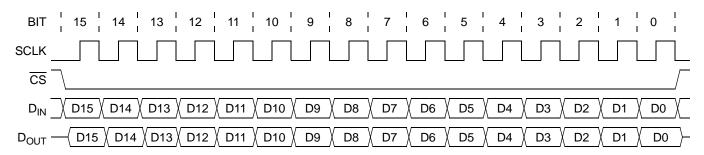

| 6   | SCLK              | SPI Clock                | This input pin provides the serial clock to the SPI port for test purposes. An internal pulldown device is connected to this pin. This pin must be grounded or left unconnected in the application.                                                                                                                                |

| 7   | D <sub>OUT</sub>  | SPI Data Out             | This pin functions as the serial data output from the SPI port for test purposes. This pin must be left unconnected in the application.                                                                                                                                                                                            |

| 8   | D <sub>IN</sub>   | SPI Data In              | This pin functions as the serial data input to the SPI port for test purposes. An internal pulldown device is connected to this pin. This pin must be grounded or left unconnected in the application.                                                                                                                             |

| 9   | V <sub>REG</sub>  | Digital<br>Supply        | This pin is connected to the power supply for the internal digital circuitry. An external capacitor must be connected between this pin and $V_{SS}$ . Reference Figure 1.                                                                                                                                                          |

| 10  | CS                | Chip Select              | This input pin provides the chip select to the SPI port for test purposes. An internal pullup device is connected to this pin. This pin must be left unconnected in the application.                                                                                                                                               |

| 11  | V <sub>REGA</sub> | Analog<br>Supply         | This pin is connected to the power supply for the internal analog circuitry. An external capacitor must be connected between this pin and $V_{SSA}$ . Reference Figure 1.                                                                                                                                                          |

| 12  | VSSA              | Analog GND               | This pin is the power supply return node for the analog circuitry.                                                                                                                                                                                                                                                                 |

| 13  | V <sub>BUF</sub>  | Power<br>Supply          | This pin is connected to a buffer regulator for the internal circuitry. The buffer regulator supplies both the analog ( $V_{REGA}$ ) and digital ( $V_{REG}$ ) supplies to provide immunity from EMC and supply dropouts on $V_{CC}$ . An external capacitor must be connected between this pin and $V_{SS}$ . Reference Figure 1. |

| 14  | TEST              | Test Pin                 | This pin is must be grounded or left unconnected in the application.                                                                                                                                                                                                                                                               |

| 15  | BUS_SW            | Bus Switch<br>Gate Drive | This pin is the drive for a low-side daisy chain switch. When daisy chain mode is enabled, this pin is connected to the gate of an n-channel FET which connects V <sub>SS</sub> to V <sub>SS_OUT</sub> . Reference Figure 1. If unused, this pin must be left unconnected.                                                         |

| 16  | VSSA              | Analog GND               | This pin is the power supply return node for the analog circuitry.                                                                                                                                                                                                                                                                 |

| 17  | PAD               | Die Attach Pad           | This pin is the die attach flag, and is internally connected to VSS. Reference Section 7 for die attach pad connection details.                                                                                                                                                                                                    |

|     | Corner<br>Pads    | Corner Pads              | The corner pads are internally connected to V <sub>SS</sub> .                                                                                                                                                                                                                                                                      |

## **2 Electrical Characteristics**

## 2.1 Maximum Ratings

Maximum ratings are the extreme limits to which the device can be exposed without permanently damaging it.

| #                   | Rating                                                                                                                                                                                                                        | Symbol                                                              | Value                           | Unit        |                          |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------|-------------|--------------------------|

| 1<br>2<br>3         | Supply Voltage ( $V_{CC}$ , $I_{DATA}$ )<br>Reverse Current $\leq$ 160 mA, $t \leq$ 80 ms<br>Continuous<br>Transient ( $<$ 10 $\mu$ s)                                                                                        | V <sub>CC_REV</sub><br>V <sub>CC_MAX</sub><br>V <sub>CC_TRANS</sub> | -0.7<br>+20.0<br>+25.0          | V<br>V<br>V | (3)<br>(3)<br>(9)        |

| 4                   | V <sub>BUF,</sub> Test, BUS_SW                                                                                                                                                                                                |                                                                     | -0.3 to +4.2                    | V           | (3)                      |

| 5                   | $V_{REGA}$ , $V_{REGA}$ , $SCLK$ , $\overline{CS}$ , $D_{IN}$ , $D_{OUT}$ , $PCM$                                                                                                                                             |                                                                     | -0.3 to +3.0                    | V           | (3)                      |

| 6                   | owered Shock (six sides, 0.5 ms duration)  gpms ±2000                                                                                                                                                                         |                                                                     | ±2000                           | g           | (3)                      |

| 7                   | Unpowered Shock (six sides, 0.5 ms duration)                                                                                                                                                                                  | g <sub>shock</sub> ±2500                                            |                                 | g           | (3)                      |

| 8                   | Drop Shock (to concrete, tile or steel surface, 10 drops, any orientation)                                                                                                                                                    | h <sub>DROP</sub>                                                   | 1.2                             | m           | (5)                      |

| 9<br>10<br>11<br>12 | Electrostatic Discharge (per AEC-Q100)<br>External Pins ( $V_{CC}$ , $I_{DATA}$ , $V_{SS}$ , $V_{SSA}$ ), HBM (100 pF, 1.5 k $\Omega$ )<br>HBM (100 pF, 1.5 k $\Omega$ )<br>CDM (R = 0 $\Omega$ )<br>MM (200 pF, 0 $\Omega$ ) | Vesd<br>Vesd<br>Vesd<br>Vesd                                        | ±4000<br>±2000<br>±1500<br>±200 | V<br>V<br>V | (5)<br>(5)<br>(5)<br>(5) |

| 13<br>14            | Temperature Range<br>Storage<br>Junction                                                                                                                                                                                      | T <sub>stg</sub> -40 to +125<br>T <sub>J</sub> -40 to +150          |                                 | °C<br>°C    | (3)<br>(9)               |

| 15                  | Thermal Resistance                                                                                                                                                                                                            | $\theta_{JC}$                                                       | 2.5                             | °C/W        | (9, 14)                  |

## 2.2 Operating Range

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \, T_L \leq T_A \leq T_H, \, \Delta T \leq 25 \, \, \text{K/min, unless otherwise specified.}$

| #        | Characteristic                                                                                    | Symbol                                | Min                                            | Тур | Max                                      | Units    |            |

|----------|---------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------|-----|------------------------------------------|----------|------------|

| 16<br>17 | Supply Voltage                                                                                    | V <sub>CC</sub><br>V <sub>CC_UV</sub> | V <sub>L</sub><br>4.2<br>V <sub>VCC_UV_F</sub> | _   | V <sub>H</sub><br>17.0<br>V <sub>L</sub> | V<br>V   | (1)<br>(9) |

| 18       | Programming Voltage (I <sub>DATA</sub> ≤ 85 mA)<br>Applied to I <sub>DATA</sub> , V <sub>CC</sub> | V <sub>PP</sub>                       | 14.0                                           | _   | _                                        | V        | (3)        |

| 19<br>20 | Operating Temperature Range                                                                       | T <sub>A</sub><br>T <sub>A</sub>      | T <sub>L</sub><br>-40<br>-40                   |     | T <sub>H</sub><br>+105<br>+125           | °C<br>°C | (1)<br>(3) |

# 2.3 Electrical Characteristics - Supply and I/O $V_L \leq (V_{CC} - V_{SS}) \leq V_H, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 25 \ \text{K/min, unless otherwise specified.}$

| #                    | Characteristic                                                                                                                                      | Symbol                                                                                                | Min                          | Тур                                  | Max                            | Units       |                                      |

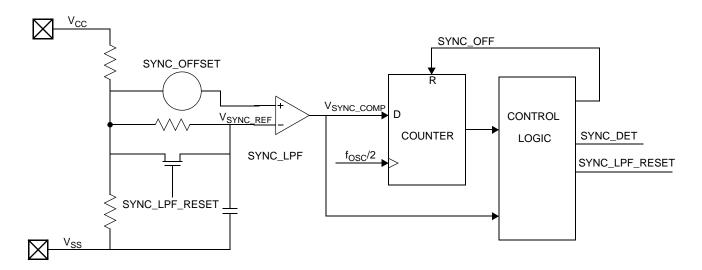

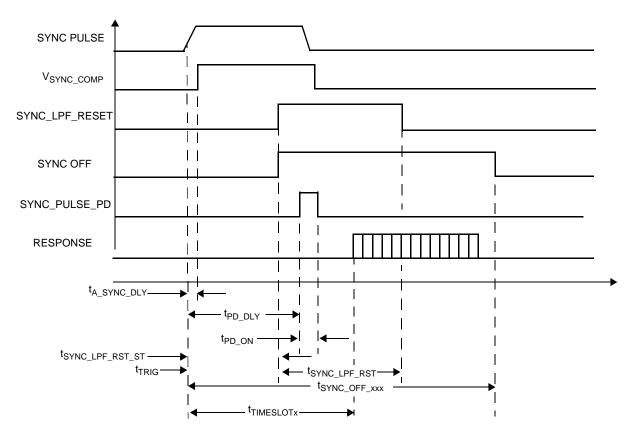

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------|--------------------------------|-------------|--------------------------------------|

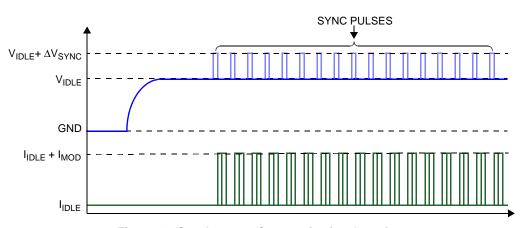

| 21                   | Quiescent Supply Current *                                                                                                                          | I <sub>IDLE</sub>                                                                                     | 4.0                          | _                                    | 8.0                            | mA          | (1)                                  |

| 22                   | Modulation Supply Current *                                                                                                                         | I <sub>MOD</sub>                                                                                      | I <sub>IDLE</sub> + 22.0     | I <sub>IDLE</sub> + 26.0             | I <sub>IDLE</sub> + 30.0       | mA          | (1)                                  |

| 23                   | Inrush Current (Power On until V <sub>BUF</sub> , V <sub>REG</sub> , V <sub>REGA</sub> Stable)                                                      | I <sub>INRUSH</sub>                                                                                   | _                            | _                                    | 30                             | mA          | (3)                                  |

| 24<br>25<br>26       | Internally Regulated Voltages  VBUF VREG VREGA  *                                                                                                   | V <sub>BUF</sub><br>V <sub>REG</sub><br>V <sub>REGA</sub>                                             | 3.60<br>2.425<br>2.425       | 3.80<br>2.50<br>2.50                 | 4.00<br>2.575<br>2.575         | V<br>V<br>V | (1)<br>(1)<br>(1)                    |

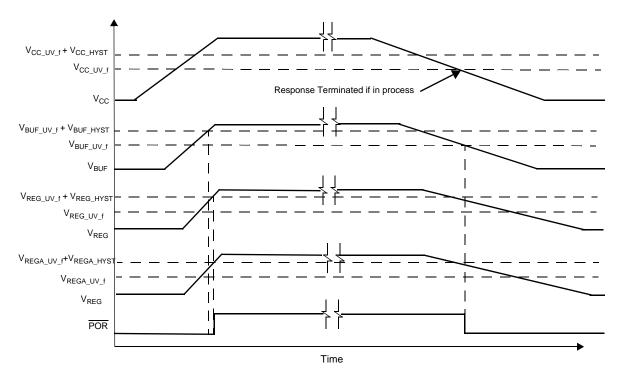

| 27<br>28<br>29<br>30 | Low Voltage Detection Threshold  V <sub>CC</sub> Falling  V <sub>BUF</sub> Falling  V <sub>REG</sub> Falling  V <sub>REGA</sub> Falling  Hysteresis | V <sub>VCC_UV_</sub> F<br>V <sub>BUF_UV_</sub> F<br>V <sub>REG_UV_</sub> F<br>V <sub>REGA_UV_</sub> F | 3.40<br>2.95<br>2.15<br>2.15 | 3.70<br>3.15<br>2.25<br>2.25         | 4.0<br>3.35<br>2.35<br>2.35    | V<br>V<br>V | (3, 6)<br>(3, 6)<br>(3, 6)<br>(3, 6) |

| 31<br>32<br>33<br>34 | V <sub>CC</sub> V <sub>BUF</sub> V <sub>REG</sub> V <sub>REGA</sub>                                                                                 | V <sub>CC_HYST</sub> V <sub>BUF_HYST</sub> V <sub>REG_HYST</sub> V <sub>REGA_HYST</sub>               | 0.10<br>0.05<br>0.05<br>0.05 | 0.25<br>0.10<br>0.10<br>0.10         | 0.40<br>0.15<br>0.15<br>0.15   | V<br>V<br>V | (3)<br>(3)<br>(3)<br>(3)             |

| 35<br>36             | External Capacitor (V <sub>BUF</sub> , V <sub>REG</sub> , V <sub>REGA</sub> ) Capacitance ESR (including interconnect resistance)                   | ESR                                                                                                   | 500<br>0                     | 1000<br>—                            | 1500<br>200                    | nF<br>mΩ    | (9)<br>(9)                           |

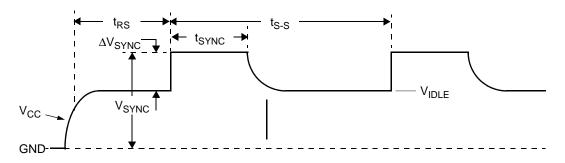

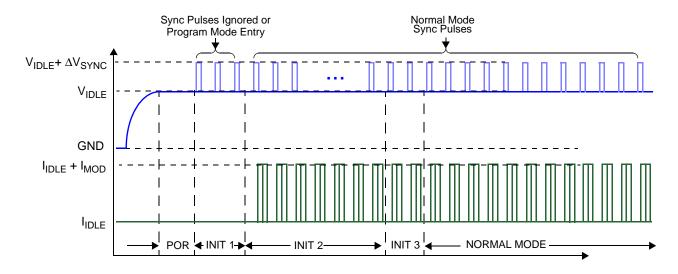

| 37<br>38             | Synchronization Pulse (Figure 5)  V <sub>IDLE</sub> Voltage Range *  DC Sync Pulse Detection Threshold *                                            | VIDLE<br>ΔV <sub>SYNC</sub>                                                                           | —<br>V <sub>IDLE</sub> +1.4  | —<br>V <sub>IDLE</sub> +2.0          | 15.4<br>V <sub>IDLE</sub> +2.6 | V           | (3, 11, (3, 6)                       |

| 39                   | Sync Pulse Pulldown Current                                                                                                                         | I <sub>SYNC_PD</sub>                                                                                  | _                            | I <sub>MOD</sub> - I <sub>IDLE</sub> | _                              | mA          | (3)                                  |

| 40                   | Output High Voltage (DO)<br>I <sub>Load</sub> = 100 μA                                                                                              | V <sub>OH</sub>                                                                                       | V <sub>REG</sub> - 0.1       | _                                    | _                              | V           | (9)                                  |

| 41                   | Output Low Voltage (DO) I <sub>Load</sub> = 100 μA                                                                                                  | V <sub>OL</sub>                                                                                       | _                            | _                                    | 0.1                            | V           | (9)                                  |

| 42                   | Input High Voltage<br>CS, SCLK, DI                                                                                                                  | $V_{IH}$                                                                                              | 0.7 * V <sub>REG</sub>       | _                                    | _                              | V           | (9)                                  |

| 43                   | Input Low Voltage CS, SCLK, DI                                                                                                                      | V <sub>IL</sub>                                                                                       | _                            | _                                    | 0.3 * V <sub>REG</sub>         | V           | (9)                                  |

| 44<br>45             | Input Current High (at $V_{IH}$ ) (DI) Low (at $V_{IL}$ ) (CS)                                                                                      | I <sub>IH</sub><br>I <sub>IL</sub>                                                                    | -100<br>10                   | _<br>_                               | -10<br>100                     | μA<br>μA    | (9)<br>(9)                           |

| 46                   | Pulldown Resistance (SCLK)                                                                                                                          | R <sub>PD</sub>                                                                                       | 20                           | æ                                    | 100                            | kΩ          | (9)                                  |

| 47                   | BUS_SW Output High Voltage (BUS_SW) I <sub>Load</sub> = 100 μA                                                                                      | V <sub>BUS_SW_OH</sub>                                                                                | 3.15                         | _                                    | V <sub>BUF</sub>               | V           | (9)                                  |

| 48                   | Output Low Voltage (BUS_SW) I <sub>Load</sub> = 100 μA                                                                                              | V <sub>BUS_SW_OL</sub>                                                                                | 0.0                          | _                                    | 0.45                           | V           | (9)                                  |

| 49                   | Daisy Chain Addressing Mode Sync Pulse Period                                                                                                       |                                                                                                       | _                            | t <sub>S-S_PM_L</sub>                | _                              | s           | (7)                                  |

| 50                   | Bus Switch Output Activation Time (C = 50 pF) From last bit of "SetAdr" Response to 80% of V <sub>BUS_SW_OH</sub>                                   | tBUS_SW                                                                                               |                              | _                                    | 300                            | μs          | (7)                                  |

| 51                   | Sync Pulse Blanking Time after "SetAdr" Command Received From last bit of "SetAdr" Response                                                         | t <sub>DC_BLANKING</sub>                                                                              |                              | 200000 / f <sub>OSC</sub>            |                                | s           | (7)                                  |

## 2.4 Electrical Characteristics - Sensor And Signal Chain

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 25 \ \text{K/min, unless otherwise specified}.$

| #                                | Characteristic                                                                                                                                                                                                                                                                                                                                                                                  | Symbol                                                                     | Min                        | Тур              | Max                        | Units                            |                                        |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------|------------------|----------------------------|----------------------------------|----------------------------------------|

| 52<br>53<br>54<br>55             | Sensitivity (10-bit output @ 100 Hz, referenced to 0 Hz)  ±60g Range  ±120g Range  ±240g Range  ±480g Range  *  Total Sensitivity Error (including non-linearity)                                                                                                                                                                                                                               | SENS<br>SENS<br>SENS<br>SENS                                               | _<br>_<br>_<br>_           | 8<br>4<br>2<br>1 | _<br>_<br>_<br>_           | LSB/g<br>LSB/g<br>LSB/g<br>LSB/g | (1)<br>(1)<br>(1)<br>(1)               |

| 56<br>57<br>58<br>59<br>60<br>61 | $ \begin{array}{l} T_A = 25^{\circ}C,  \leq \pm 240g & * \\ T_L \leq T_A \leq T_H,  \leq \pm 240g,  V_{VCC\_UV\_F} \leq V_{CC} \leq V_L \\ T_A = 25^{\circ}C,  > \pm 240g & * \\ T_L \leq T_A \leq T_H,  \leq \pm 240g,  V_{VCC\_UV\_F} \leq V_{CC} \leq V_L \\ T_A = 25^{\circ}C,  > \pm 240g & * \\ T_L \leq T_A \leq T_H,  > \pm 240g,  V_{VCC\_UV\_F} \leq V_{CC} \leq V_L \\ \end{array} $ | ΔSENS_240<br>ΔSENS_240<br>ΔSENS_240<br>ΔSENS_480<br>ΔSENS_480<br>ΔSENS_480 | -5<br>-7<br>-7<br>-5<br>-7 | _<br>_<br>_<br>_ | +5<br>+7<br>+7<br>+5<br>+7 | %<br>%<br>%<br>%<br>%            | (1)<br>(1)<br>(9)<br>(1)<br>(1)<br>(9) |

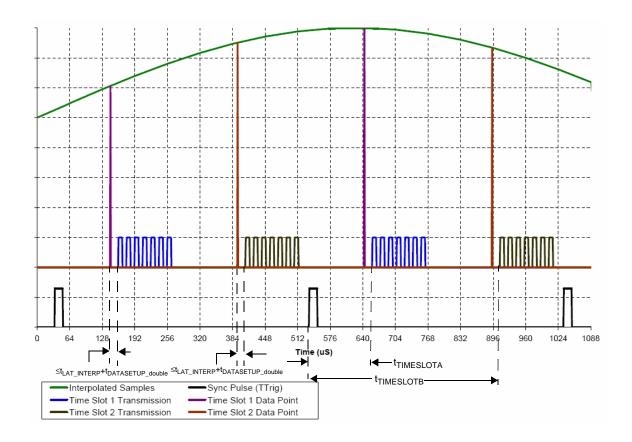

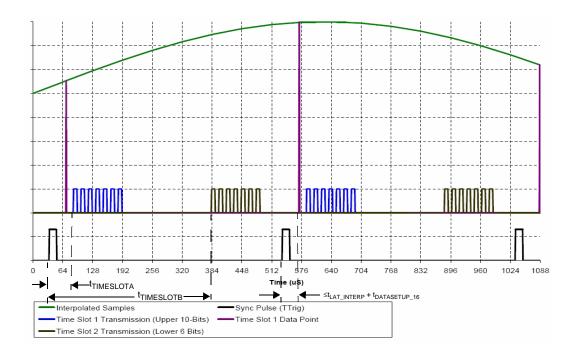

| 62<br>63                         | Digital Offset Before Offset Cancellation 10-bit 10-bit, $T_L \le T_A \le T_H$ , $V_{VCC\_UV\_F} \le V_{CC} \le V_L$                                                                                                                                                                                                                                                                            | OFF <sub>10Bit</sub><br>OFF <sub>10Bit</sub>                               | -52<br>-52                 | 0                | +52<br>+52                 | LSB<br>LSB                       | (1)<br>(9)                             |

| 64<br>65                         | Digital Offset After Offset Cancellation 10-bit, 0.3 Hz HPF or 0.1 Hz HPF 10-bit, 0.04 Hz HPF *                                                                                                                                                                                                                                                                                                 | OFF <sub>10Bit</sub><br>OFF <sub>10Bit</sub>                               | -1<br>-2                   | 0                | +1<br>+2                   | LSB<br>LSB                       | (1)<br>(9)                             |

| 66                               | Continuous Offset Monitor Limit<br>10-bit output, before compensation                                                                                                                                                                                                                                                                                                                           | OFF <sub>MON</sub>                                                         | -66                        | _                | +66                        | LSB                              | (3)                                    |

| 67                               | Range of Output (10-bit Mode)<br>Acceleration                                                                                                                                                                                                                                                                                                                                                   | RANGE                                                                      | -480                       | _                | +480                       | LSB                              | (3)                                    |

| 68<br>69                         | Cross-Axis Sensitivity Z-axis to X-axis Y-axis to X-axis *                                                                                                                                                                                                                                                                                                                                      | V <sub>ZX</sub><br>V <sub>YX</sub>                                         | -5<br>-5                   | _                | +5<br>+5                   | %<br>%                           | (3)<br>(3)                             |

| 70                               | System Output Noise Peak (10-bit Mode, 1 Hz - 1 kHz, All Ranges) *                                                                                                                                                                                                                                                                                                                              | n <sub>Peak</sub>                                                          | -4                         | _                | +4                         | LSB                              | (3)                                    |

| 71                               | System Output Noise RMS (10-bit mode, 1 Hz - 1 kHz, All Ranges) *                                                                                                                                                                                                                                                                                                                               | n <sub>RMS</sub>                                                           | _                          | _                | +1.0                       | LSB                              | (3)                                    |

| 72<br>73                         | Non-linearity 10-bit output, ≤ ±240g 10-bit output, > ±240g                                                                                                                                                                                                                                                                                                                                     | NL <sub>OUT_240g</sub><br>NL <sub>OUT_480g</sub>                           | -2<br>-2                   | _                | +2<br>+2                   | %<br>%                           | (3)                                    |

#### 2.5 Electrical Characteristics - Self-Test and Overload

$V_L \le (V_{CC} - V_{SS}) \le V_H$ ,  $T_L \le T_A \le T_H$ ,  $\Delta T \le 25$  K/min, unless otherwise specified.

| #                    | Characteristic                                                                                                                                       | Symbol                                                      | Min                  | Тур              | Max                      | Units                    |    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|------------------|--------------------------|--------------------------|----|

| 74<br>75<br>76<br>77 | 10-Bit Output During Active Self-Test (T <sub>L</sub> ≤ T <sub>A</sub> ≤ T <sub>H</sub> )<br>±60g Range<br>±120g Range<br>±240g Range<br>±480g Range | * 9ST10_60X<br>* 9ST10_120X<br>* 9ST10_240X<br>* 9ST10_480X | 120<br>40<br>56<br>8 | _<br>_<br>_<br>_ | 280<br>160<br>184<br>112 | LSB<br>LSB<br>LSB<br>LSB | () |

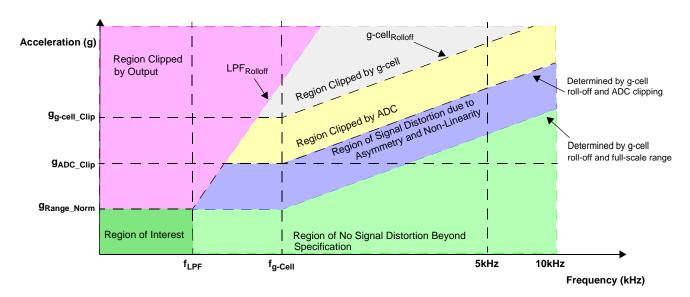

| 78                   | Acceleration (without hitting internal g-cell stops) ±60g Range Positive/Negative                                                                    | g <sub>g-cell_Clip60X</sub>                                 | 400                  | 456              | 500                      | g                        | (  |

| 79                   | Acceleration (without hitting internal g-cell stops)<br>±120g Range Positive/Negative                                                                | g <sub>g-cell_Clip120X</sub>                                | 400                  | 456              | 500                      | g                        |    |

| 80                   | Acceleration (without hitting internal g-cell stops) ±240g Range Positive/Negative                                                                   | gg-cell_Clip240X                                            | 1750                 | 2065             | 2300                     | g                        |    |

| 81                   | Acceleration (without hitting internal g-cell stops) ±480g Range Positive/Negative                                                                   | gg-cell_Clip480X                                            | 1750                 | 2065             | 2300                     | g                        |    |

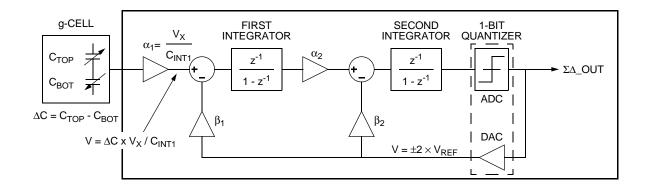

| 82                   | ΣΔ and Sinc Filter Clipping Limit<br>±60g Range Positive/Negative                                                                                    | 9ADC_Clip60X                                                | 191                  | 210              | 233                      | g                        |    |

| 83                   | ΣΔ and Sinc Filter Clipping Limit<br>±120g Range Positive/Negative                                                                                   | 9ADC_Clip120X                                               | 353                  | 380              | 410                      | g                        |    |

| 84                   | ΣΔ and Sinc Filter Clipping Limit<br>±240g Range Positive/Negative                                                                                   | 9ADC_Clip240X                                               | 928                  | 1055             | 1218                     | g                        |    |

| 85                   | ΣΔ and Sinc Filter Clipping Limit<br>±480g Range Positive/Negative                                                                                   | 9ADC_Clip480X                                               | 1690                 | 1879             | 2106                     | g                        |    |

## 2.6 Dynamic Electrical Characteristics - PSI5

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 25 \ \text{K/min, unless otherwise specified}$

| #                                                                                       | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Symbol                                                                                                                                                         | Min                                                                                              | Тур                                                                                                                                                                                                                                     | Max                                                                                              | Units                                          |                                                                                                                |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

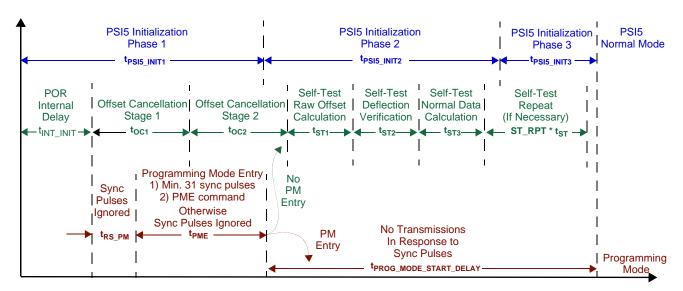

| 86<br>87<br>88<br>89<br>90<br>91<br>92<br>93<br>94<br>95<br>96<br>97<br>98<br>99<br>100 | Initialization Timing Phase 1 Phase 2 (10-Bit, Synchronous Mode, k = 4) Phase 2 (8-Bit, Synchronous Mode, k = 8) Phase 2 (10-Bit, Asynchronous Mode 0, k = 8) Phase 2 (10-Bit, Asynchronous Mode 0, k = 16) Phase 3 (10-Bit, Synchronous Mode, ST_RPT = 0) Phase 3 (8-Bit, Synchronous Mode, ST_RPT = 0) Phase 3 (10-Bit, Asynchronous Mode 0, ST_RPT = 0) Phase 3 (8-Bit, Asynchronous Mode 0, ST_RPT = 0) Phase 3 (8-Bit, Asynchronous Mode 0, ST_RPT = 0) Offset Cancellation Stage 1 Operating Time Offset Cancellation Stage 2 Operating Time Self-Test Stage 1 Operating Time Self-Test Stage 2 Operating Time Self-Test Stage 3 Operating Time Self-Test Repetitions Programming Mode Entry Window | †PSI5_INIT1 †PSI6_INIT2_10s †PSI5_INIT2_8s †PSI5_INIT2_8a0 †PSI5_INIT3_10s †PSI5_INIT3_10s †PSI5_INIT3_8s †PSI5_INIT3_8a0 †CC1 †CC2 †ST1 †ST2 †ST3 ST_RPT †PME |                                                                                                  | 532000 / fosc<br>256 * ts-s<br>288 * ts-s<br>512 * tasync<br>576 * tasync<br>2 * ts-s<br>2 * ts-s<br>19 * tasync<br>320000 / fosc<br>128000 / fosc<br>128000 / fosc<br>128000 / fosc<br>128000 / fosc<br>128000 / fosc<br>128000 / fosc |                                                                                                  | 5 5 5 5 5 5 5 5 5 5 5 5 5                      | (7)<br>(7)<br>(7)<br>(7)<br>(7, 12)<br>(7, 12)<br>(7, 12)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7, 12)<br>(7) |

| 102<br>103<br>104<br>105<br>106<br>107<br>108<br>109<br>110<br>111<br>112<br>113        | Synchronization Pulse (Figure 5, Figure 28 and Figure 32) Reset to first sync pulse (Program Mode Entry) Reset to first sync pulse (Normal Mode) Sync Pulse Period Sync Pulse Width Sync Pulse Reference LPF time constant Sync Pulse Reference Discharge Start Time Sync Pulse Reference Discharge Activation Time Sync Pulse Detection Disable Time (BLANKTIME = 0) Analog Delay of Sync Pulse Detection Sync Pulse Pulldown Function Delay Time Sync Pulse Pulldown Function Activate Time Sync Pulse Detection Jitter                                                                                                                                                                                 | trs_pm trs ts-s ts-s ts-ync_lpf tsync_lpf_rst_st tsync_lpf_rst tsync_off_500 ta_sync_dly tpd_oly tpd_on tsync_jit                                              | 58 tpsi5_init1 tsync_off 9 120                                                                   | 280<br>66 / f <sub>OSC</sub><br>616 / f <sub>OSC</sub><br>1810 / f <sub>OSC</sub><br>74 / f <sub>OSC</sub><br>64 / f <sub>OSC</sub>                                                                                                     |                                                                                                  | тs<br>s<br>µs<br>µs<br>иs<br>s<br>s<br>ns<br>s | (7)<br>(7)<br>(7)<br>(7)<br>(9)<br>(7)<br>(7)<br>(9)<br>(7)<br>(7)<br>(7)                                      |

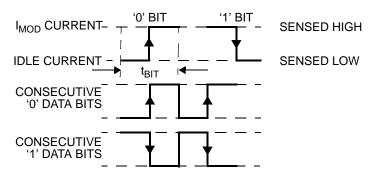

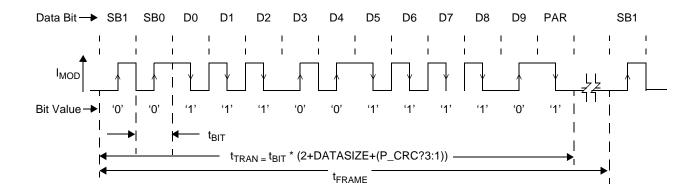

| 114<br>115                                                                              | Data Transmission Single Bit Time (PSI5 Low Bit Rate) Data Transmission Single Bit Time (PSI5 High Bit Rate) *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>BIT_LOW</sub>                                                                                                                                           | 7.6000<br>4.9875                                                                                 | 8.0000<br>5.2500                                                                                                                                                                                                                        | 8.4000<br>5.5125                                                                                 | μs<br>μs                                       | (7)<br>(7)                                                                                                     |

| 116<br>117                                                                              | Modulation Current (20% to 80% of I <sub>MOD</sub> - I <sub>IDLE</sub> )<br>Rise Time<br>Fall Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <sup>t</sup> RISE<br><sup>t</sup> FALL                                                                                                                         | 324<br>324                                                                                       | 463<br>463                                                                                                                                                                                                                              | 602<br>602                                                                                       | ns<br>ns                                       | (3)<br>(3)                                                                                                     |

| 118<br>119                                                                              | Position of bit transition (PSI5 Low Baud Rate)  * Position of bit transition (PSI5 High Baud Rate)  *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <sup>t</sup> Bittrans_LowBaud<br><sup>t</sup> Bittrans_HighBaud                                                                                                | 49<br>47                                                                                         | 50<br>æ                                                                                                                                                                                                                                 | 51<br>53                                                                                         | %<br>%                                         | (7)<br>(7)                                                                                                     |

| 120                                                                                     | Asynchronous Response Time *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>ASYNC</sub>                                                                                                                                             | _                                                                                                | 912 / f <sub>OSC</sub>                                                                                                                                                                                                                  | æ                                                                                                | s                                              | (7)                                                                                                            |

| 121<br>122<br>123<br>124<br>125<br>126<br>127<br>128                                    | Time Slots  Minimum Programmed Time Slot (TIMESLOTx = 0x001)  Maximum Programmed Time Slot (TIMESLOTx = 0x3FF)  Default Time Slot (TIMESLOTx = 0x000)  Time Slot Resolution  Sync Pulse to Daisy Chain Default Time Slot 1  Sync Pulse to Daisy Chain Default Time Slot 2  Sync Pulse to Daisy Chain Default Time Slot 3  Sync Pulse to Daisy Chain Programming Time Slot                                                                                                                                                                                                                                                                                                                                 | tTIMESLOTX_MIN tTIMESLOTX_MAX tTIMESLOT_DFLT tTIMESLOT_DC1 tTIMESLOT_DC1 tTIMESLOT_DC2 tTIMESLOT_DC3 tTIMESLOT_DCP                                             | -<br>-<br>-<br>-<br>-<br>-<br>-                                                                  | 2/f <sub>OSC</sub><br>2046/f <sub>OSC</sub><br>186/f <sub>OSC</sub><br>2/f <sub>OSC</sub><br>186/f <sub>OSC</sub><br>768/f <sub>OSC</sub><br>1400/f <sub>OSC</sub>                                                                      |                                                                                                  | s<br>s<br>s/LSB<br>s<br>s<br>s                 | (7, 9)<br>(3, 7)<br>(3, 7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)                                                  |

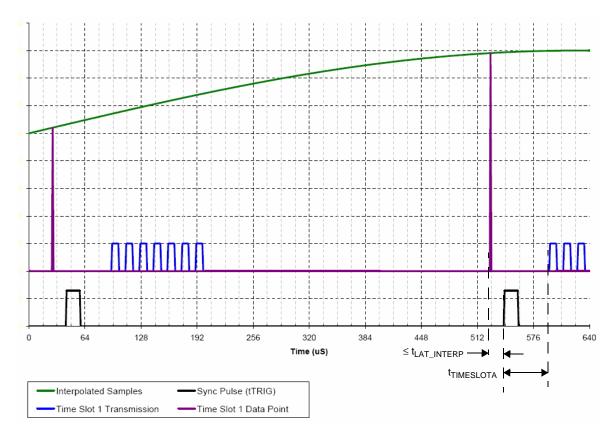

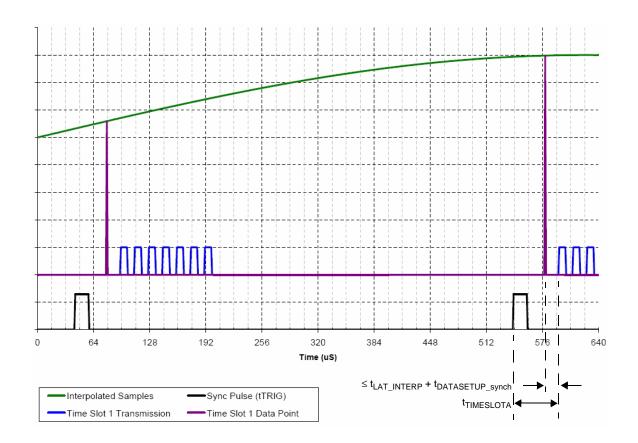

| 129<br>130                                                                              | Data Interpolation Latency (Figure 35, Figure 36) Data Setup Time - Synchronous Mode (Figure 36) Data Setup Time - Double Sample Rate Mode (Figure 37) Data Setup Time - 16-bit Resolution Mode (Figure 39)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | tLAT_INTERP tDATASETUP_synch tDATASETUP_double tDATASETUP_16                                                                                                   | 64 / f <sub>OSC</sub><br>48 / f <sub>OSC</sub><br>48 / f <sub>OSC</sub><br>48 / f <sub>OSC</sub> | _<br>_<br>_<br>_                                                                                                                                                                                                                        | 65 / f <sub>OSC</sub><br>56 / f <sub>OSC</sub><br>60 / f <sub>OSC</sub><br>60 / f <sub>OSC</sub> | \$<br>\$<br>\$<br>\$                           | (7)<br>(7)<br>(7)<br>(7)                                                                                       |

| 131<br>132<br>133<br>134<br>135                                                         | Programming Mode Timing Programming Mode Sync Pulse Period Programming Mode Command Timeout OTP Write Command to V <sub>CC</sub> = V <sub>PP</sub> OTP Write CMD Response to OTP programming start Time to program the OTP User Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ts-s_pm_l<br>tpm_timeout<br>tprog_hold<br>tprog_delay<br>tprog_array                                                                                           | 495<br>—<br>—<br>—<br>—<br>70                                                                    | 500<br>4 * t <sub>S-S_PM</sub><br>—<br>—                                                                                                                                                                                                | 505<br>—<br>20<br>40<br>—                                                                        | μs<br>μs<br>μs<br>ms<br>ms                     | (7)<br>(7)<br>(7)<br>(7)<br>(7)                                                                                |

## 2.7 Dynamic Electrical Characteristics - Signal Chain $V_L \leq (V_{CC} - V_{SS}) \leq V_H, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 25 \ \text{K/min, unless otherwise specified}$

| #                                                                                              | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Symbol                                                                                                                       | Min                              | Тур                                                                                                                                                        | Max                              | Units                                                                  |                                                                |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------|

| 136                                                                                            | Internal Oscillator Frequency *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | fosc                                                                                                                         | 3.80                             | 4                                                                                                                                                          | 4.20                             | MHz                                                                    | (1                                                             |

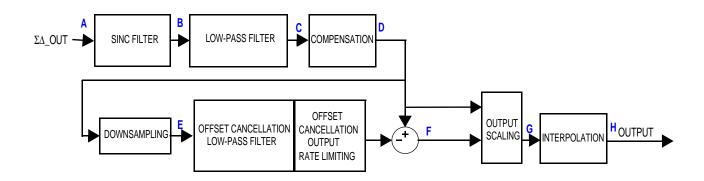

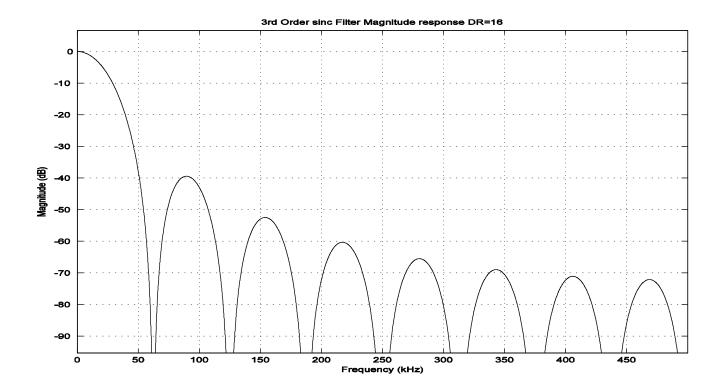

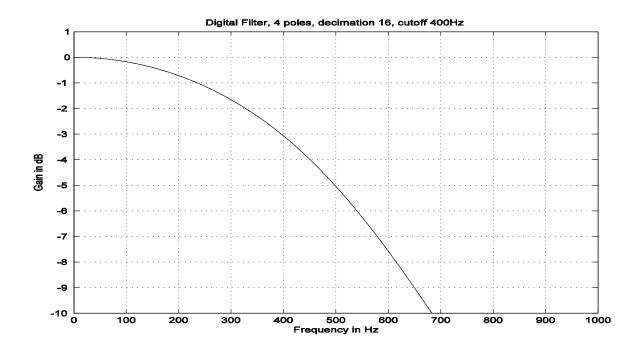

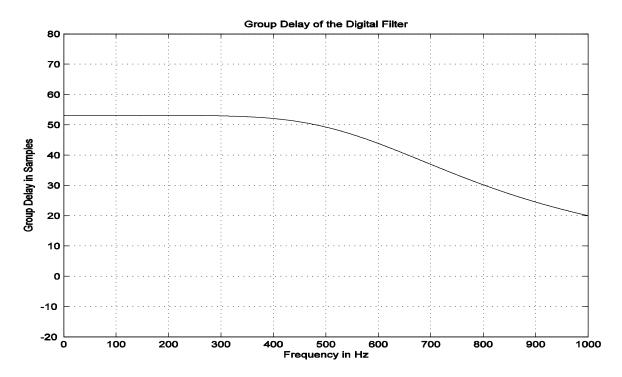

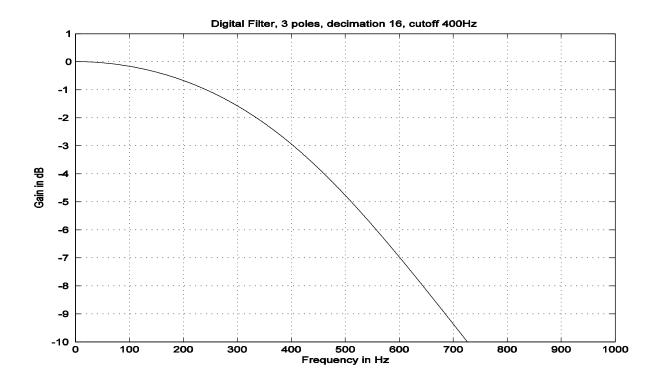

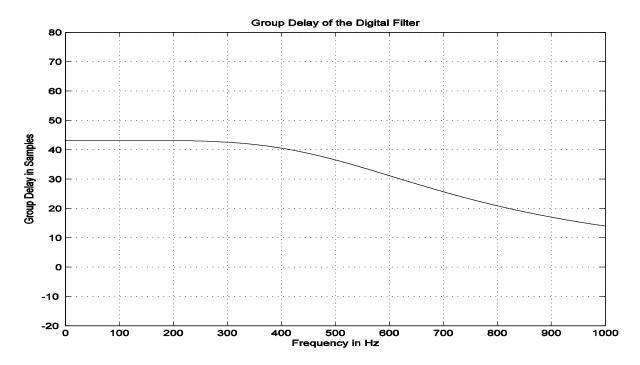

| 137<br>138<br>139<br>140                                                                       | DSP Low-Pass Filter (Note15) Cutoff frequency LPF0 (referenced to 0 Hz) Filter Order LPF0 Cutoff frequency LPF1 (referenced to 0 Hz) Filter Order LPF1  *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | f <sub>C_LPF0</sub> O <sub>LPF0</sub> f <sub>C_LPF1</sub> O <sub>LPF1</sub>                                                  | _<br>_<br>_<br>_                 | 400<br>3<br>400<br>4                                                                                                                                       | <br><br>                         | Hz<br>1<br>Hz<br>1                                                     | (7<br>(7<br>(7<br>(7                                           |

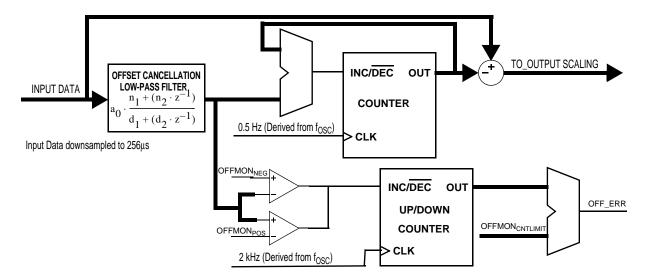

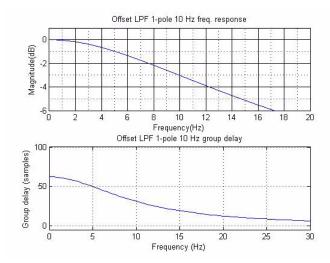

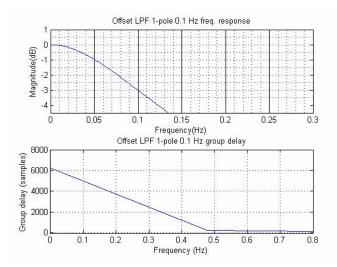

| 141<br>142<br>143<br>144<br>145<br>146<br>147<br>148<br>149<br>150<br>151<br>152<br>153<br>154 | DSP Offset Cancellation Low-Pass Filter (Note 15) Offset Cancellation Low-Pass Filter Input Sample Rate Stage 1 Cutoff frequency, Startup Phase 1 Stage 1 Filter Order, Startup Phase 1 Stage 2 Cutoff frequency, Startup Phase 1 Stage 2 Filter Order, Startup Phase 1 Stage 2 Filter Order, Startup Phase 1 Cutoff frequency, Option 0 Filter Order, Option 0 Offset Cancellation Output Update Rate (8-Bit Mode) Offset Cancellation Output Step Size (8-Bit Mode) Offset Cancellation Output Update Rate (10-Bit Mode) Offset Cancellation Output Step Size (10-Bit Mode) Offset Monitor Update Frequency Offset Monitor Count Limit Offset Monitor Counter Size | toc_sampleRate fc_OC10 OOC10 fc_OC03 OOC03 fc_OC0 OOC0 toffRate_8 OFF Step_8 toffRate_10 OFFStep_10 OFFMONOSC OFFMONCNTLIMIT |                                  | 256<br>10.0<br>1<br>0.300<br>1<br>0.100<br>1<br>f <sub>OSC</sub> / 2e6<br>0.125<br>f <sub>OSC</sub> / 2e6<br>0.5<br>f <sub>OSC</sub> /2000<br>4096<br>8192 |                                  | μs<br>Hz<br>1<br>Hz<br>1<br>Hz<br>1<br>s<br>LSB<br>s<br>LSB<br>Hz<br>1 | (7<br>(7<br>(7<br>(7<br>(7<br>(7<br>(7<br>(7<br>(7<br>(7<br>(7 |

| 155<br>156<br>157<br>158                                                                       | Sensing Element Natural Frequency ±60g ±120g ±240g ±480g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | f <sub>gcell_</sub> X60<br>f <sub>gcell_</sub> X120<br>f <sub>gcell_</sub> X240<br>f <sub>gcell_</sub> X480                  | 12651<br>12651<br>26000<br>26000 | _<br>_<br>_<br>_                                                                                                                                           | 13871<br>13871<br>28700<br>28700 | Hz<br>Hz<br>Hz<br>Hz                                                   | (9<br>(9<br>(9                                                 |

| 159<br>160<br>161<br>162                                                                       | Sensing Element Rolloff Frequency (-3 db) ±60g ±120g ±240g ±480g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | fgcell_X60<br>fgcell_X120<br>fgcell_X240<br>fgcell_X480                                                                      | 938<br>938<br>3952<br>3952       | _<br>_<br>_<br>_                                                                                                                                           | 2592<br>2592<br>14370<br>14370   | Hz<br>Hz<br>Hz<br>Hz                                                   | (9<br>(9<br>(9                                                 |

| 163<br>164<br>165<br>166                                                                       | Sensing Element Damping Ratio ±60g ±120g ±240g ±480g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ζgcell_X60<br>Śgcell_X120<br>Śgcell_X240<br>Śgcell_X480                                                                      | 2.760<br>2.760<br>1.260<br>1.260 | _<br>_<br>_<br>_                                                                                                                                           | 6.770<br>6.770<br>3.602<br>3.602 | _<br>_<br>_<br>_                                                       | (9<br>(9<br>(9                                                 |

| 167<br>168<br>169<br>170                                                                       | Sensing Element Delay (@100 Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | fgcell_delay_X60<br>fgcell_delay_X120<br>fgcell_delay_X240<br>fgcell_delay_X480                                              | 63<br>63<br>13<br>13             | _<br>_<br>_<br>_                                                                                                                                           | 170<br>170<br>40<br>40           | μs<br>μs<br>μs<br>μs                                                   | (9<br>(9<br>(9                                                 |

| 171                                                                                            | Package Resonance Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f <sub>Package</sub>                                                                                                         | 100                              | _                                                                                                                                                          | _                                | kHz                                                                    | (9                                                             |

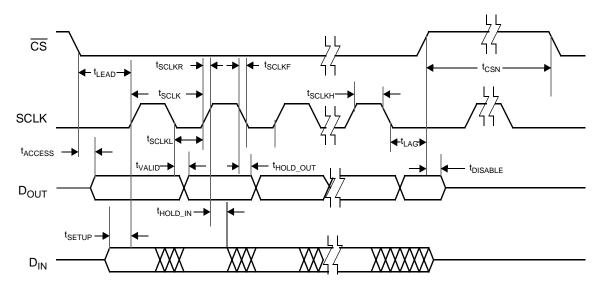

## 2.8 Dynamic Electrical Characteristics - Supply and SPI

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \ T_L \leq T_A \leq T_H, \ \Delta T \leq 25 \ \text{K/min, unless otherwise specified}$

| #                                                                                              | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Symbol                                                                                                     | Min                                                   | Тур                                                                                | Max                                       | Units                                    |                                                                    |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------|--------------------------------------------------------------------|

| 172                                                                                            | Quiescent Current Settling Time (Power Applied to Iq = I <sub>IDLE</sub> ± 2mA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>SET</sub>                                                                                           | _                                                     | _                                                                                  | 5                                         | ms                                       | (3)                                                                |

| 173                                                                                            | Reset Recovery Internal Delay (After internal POR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t <sub>INT_INIT</sub>                                                                                      | _                                                     | 16000 / f <sub>OSC</sub>                                                           | _                                         | s                                        | (7)                                                                |

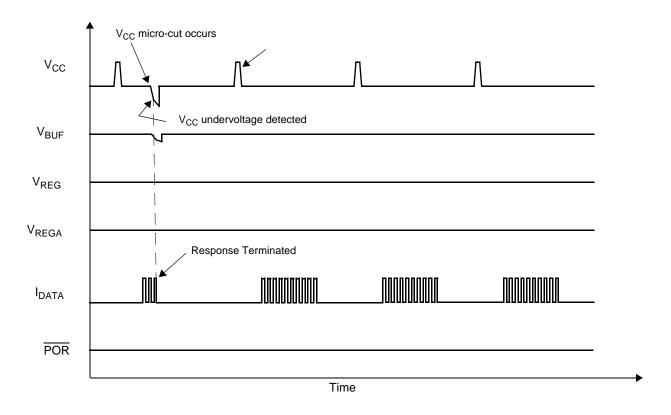

| 174<br>175<br>176                                                                              | $\begin{array}{l} V_{CC} \ \text{Micro-cut} \ (C_{BUF} = C_{REG} = C_{REGA} = 1 \ \mu F) \\ \text{Survival Time} \ (V_{CC} \ \text{disconnect without Reset, } C_{BUF} = C_{REG} = C_{REGA} = 700 \ \text{nF}) \\ \text{Survival Time} \ (V_{CC} \ \text{disconnect without Reset, } C_{BUF} = C_{REG} = C_{REGA} = 1 \ \mu F) \\ \text{Reset Time} \ (V_{CC} \ \text{disconnect above which Reset is guaranteed}) \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | tvcc_MICROCUTmin<br>tvcc_MICROCUT<br>tvcc_RESET                                                            | 30<br>50                                              | _<br>_<br>_                                                                        | <br>1000                                  | μs<br>μs<br>μs                           | (3)<br>(3)<br>(3)                                                  |

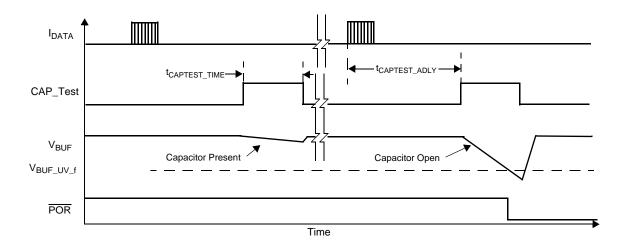

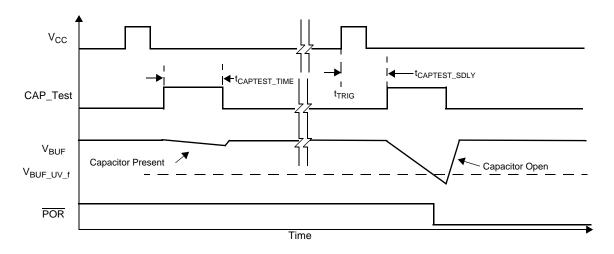

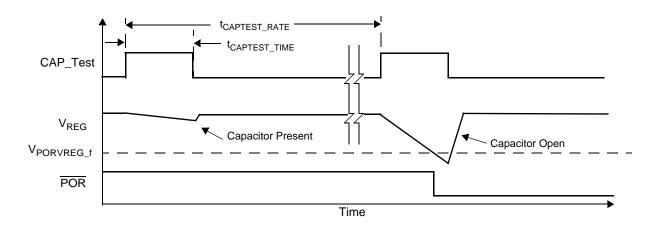

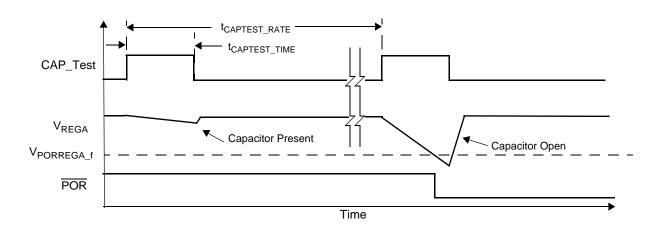

| 177<br>178<br>179<br>180                                                                       | V <sub>BUF</sub> , Capacitor Monitor Disconnect Time (Figure 10) POR to first Capacitor Test Disconnect Disconnect Time (Figure 10) Disconnect Delay, Asynchronous Mode (Figure 10) Disconnect Delay, Synchronous Mode (Figure 11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | tPOR_CAPTEST tCAPTEST_TIME tCAPTEST_ADLY tCAPTEST_SDLY                                                     |                                                       | 12000 / f <sub>OSC</sub><br>1.5<br>688 / f <sub>OSC</sub><br>72 / f <sub>OSC</sub> | <br>5.0<br><br>                           | s<br>µs<br>s                             | (7)<br>(7)<br>(7)<br>(7)                                           |