# MPC860 PowerQUICC Family Hardware Specifications

This hardware specification contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications for the MPC860 family.

To locate published errata or updates for this document, see the MPC860 product summary page on the website listed on the back cover of this document or contact your local Freescale sales office.

#### Contents

| 1.  | Overview                                    |

|-----|---------------------------------------------|

| 2.  | Features                                    |

| 3.  | Maximum Tolerated Ratings 7                 |

| 4.  | Thermal Characteristics 8                   |

| 5.  | Power Dissipation                           |

| 6.  | DC Characteristics                          |

| 7.  | Thermal Calculation and Measurement 12      |

| 8.  | Layout Practices                            |

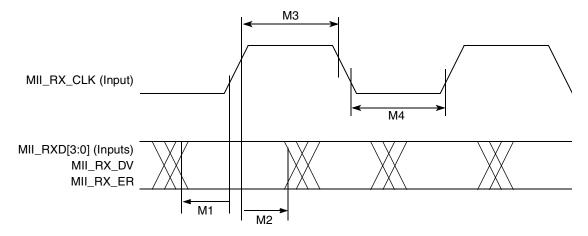

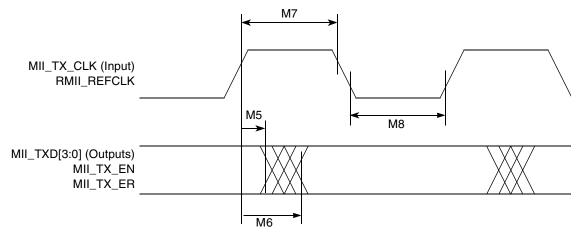

| 9.  | Bus Signal Timing                           |

| 10. | IEEE 1149.1 Electrical Specifications       |

| 11. | CPM Electrical Characteristics              |

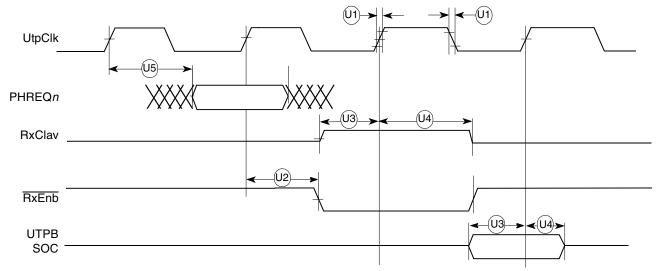

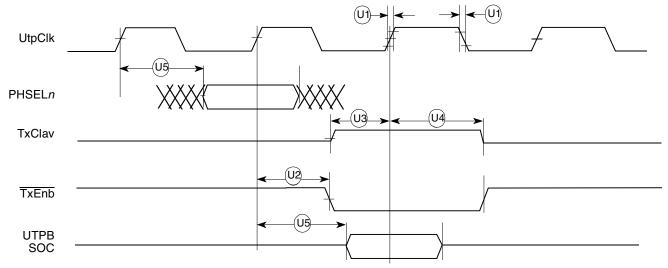

| 12. | UTOPIA AC Electrical Specifications 65      |

| 13. | FEC Electrical Characteristics              |

| 14. | Mechanical Data and Ordering Information 70 |

| 15. | Document Revision History                   |

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

## 1 Overview

The MPC860 power quad integrated communications controller (PowerQUICC<sup>TM</sup>) is a versatile one-chip integrated microprocessor and peripheral combination designed for a variety of controller applications. It particularly excels in communications and networking systems. The PowerQUICC unit is referred to as the MPC860 in this hardware specification.

The MPC860 implements Power Architecture<sup>TM</sup> technology and contains a superset of Freescale's MC68360 quad integrated communications controller (QUICC), referred to here as the QUICC, RISC communications processor module (CPM). The CPU on the MPC860 is a 32-bit core built on Power Architecture technology that incorporates memory management units (MMUs) and instruction and data caches.. The CPM from the MC68360 QUICC has been enhanced by the addition of the inter-integrated controller (I<sup>2</sup>C) channel. The memory controller has been enhanced, enabling the MPC860 to support any type of memory, including high-performance memories and new types of DRAMs. A PCMCIA socket controller supports up to two sockets. A real-time clock has also been integrated.

Table 1 shows the functionality supported by the MPC860 family.

|          | Cache (              | (Kbytes)   | Ethe    | ernet  |     |     |                        |

|----------|----------------------|------------|---------|--------|-----|-----|------------------------|

| Part     | Instruction<br>Cache | Data Cache | 10T     | 10/100 | ATM | scc | Reference <sup>1</sup> |

| MPC860DE | 4                    | 4          | Up to 2 | _      | _   | 2   | 1                      |

| MPC860DT | 4                    | 4          | Up to 2 | 1      | Yes | 2   | 1                      |

| MPC860DP | 16                   | 8          | Up to 2 | 1      | Yes | 2   | 1                      |

| MPC860EN | 4                    | 4          | Up to 4 | _      | _   | 4   | 1                      |

| MPC860SR | 4                    | 4          | Up to 4 | _      | Yes | 4   | 1                      |

| MPC860T  | 4                    | 4          | Up to 4 | 1      | Yes | 4   | 1                      |

| MPC860P  | 16                   | 8          | Up to 4 | 1      | Yes | 4   | 1                      |

| MPC855T  | 4                    | 4          | 1       | 1      | Yes | 1   | 2                      |

**Table 1. MPC860 Family Functionality**

Supporting documentation for these devices refers to the following:

<sup>1.</sup> MPC860 PowerQUICC Family User's Manual (MPC860UM, Rev. 3)

<sup>2.</sup> MPC855T User's Manual (MPC855TUM, Rev. 1)

3

## 2 Features

The following list summarizes the key MPC860 features:

- Embedded single-issue, 32-bit core (implementing the Power Architecture technology) with thirty-two 32-bit general-purpose registers (GPRs)

- The core performs branch prediction with conditional prefetch without conditional execution.

- 4- or 8-Kbyte data cache and 4- or 16-Kbyte instruction cache (see Table 1)

- 16-Kbyte instruction caches are four-way, set-associative with 256 sets; 4-Kbyte instruction caches are two-way, set-associative with 128 sets.

- 8-Kbyte data caches are two-way, set-associative with 256 sets; 4-Kbyte data caches are two-way, set-associative with 128 sets.

- Cache coherency for both instruction and data caches is maintained on 128-bit (4-word) cache blocks.

- Caches are physically addressed, implement a least recently used (LRU) replacement algorithm, and are lockable on a cache block basis.

- MMUs with 32-entry TLB, fully-associative instruction, and data TLBs

- MMUs support multiple page sizes of 4-, 16-, and 512-Kbytes, and 8-Mbytes; 16 virtual address spaces and 16 protection groups

- Advanced on-chip-emulation debug mode

- Up to 32-bit data bus (dynamic bus sizing for 8, 16, and 32 bits)

- 32 address lines

- Operates at up to 80 MHz

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank.

- Up to 15 wait states programmable per memory bank

- Glueless interface to DRAM, SIMMS, SRAM, EPROM, Flash EPROM, and other memory devices

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, and one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbytes to 256 Mbytes)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers or two 32-bit timers

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture.

#### **Features**

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Low-power stop mode

- Clock synthesizer

- Decrementer, time base, and real-time clock (RTC)

- Reset controller

- IEEE 1149.1<sup>TM</sup> Std. test access port (JTAG)

- Interrupts

- Seven external interrupt request (IRQ) lines

- 12 port pins with interrupt capability

- 23 internal interrupt sources

- Programmable priority between SCCs

- Programmable highest priority request

- 10/100 Mbps Ethernet support, fully compliant with the IEEE 802.3u® Standard (not available when using ATM over UTOPIA interface)

- ATM support compliant with ATM forum UNI 4.0 specification

- Cell processing up to 50–70 Mbps at 50-MHz system clock

- Cell multiplexing/demultiplexing

- Support of AAL5 and AAL0 protocols on a per-VC basis. AAL0 support enables OAM and software implementation of other protocols.

- ATM pace control (APC) scheduler, providing direct support for constant bit rate (CBR) and unspecified bit rate (UBR) and providing control mechanisms enabling software support of available bit rate (ABR)

- Physical interface support for UTOPIA (10/100-Mbps is not supported with this interface) and byte-aligned serial (for example, T1/E1/ADSL)

- UTOPIA-mode ATM supports level-1 master with cell-level handshake, multi-PHY (up to four physical layer devices), connection to 25-, 51-, or 155-Mbps framers, and UTOPIA/system clock ratios of 1/2 or 1/3.

- Serial-mode ATM connection supports transmission convergence (TC) function for T1/E1/ADSL lines, cell delineation, cell payload scrambling/descrambling, automatic idle/unassigned cell insertion/stripping, header error control (HEC) generation, checking, and statistics.

- Communications processor module (CPM)

- RISC communications processor (CP)

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

5

- Up to 8 Kbytes of dual-port RAM

- 16 serial DMA (SDMA) channels

- Three parallel I/O registers with open-drain capability

- Four baud-rate generators (BRGs)

- Independent (can be tied to any SCC or SMC)

- Allows changes during operation

- Autobaud support option

- Four serial communications controllers (SCCs)

- Ethernet/IEEE 802.3® standard optional on SCC1–4, supporting full 10-Mbps operation (available only on specially programmed devices)

- HDLC/SDLC (all channels supported at 2 Mbps)

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support point-to-point protocol (PPP)

- AppleTalk

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Binary synchronous communication (BISYNC)

- Totally transparent (bit streams)

- Totally transparent (frame-based with optional cyclic redundancy check (CRC))

- Two SMCs (serial management channels)

- UART

- Transparent

- General circuit interface (GCI) controller

- Can be connected to the time-division multiplexed (TDM) channels

- One SPI (serial peripheral interface)

- Supports master and slave modes

- Supports multimaster operation on the same bus

- One I<sup>2</sup>C (inter-integrated circuit) port

- Supports master and slave modes

- Multiple-master environment support

- Time-slot assigner (TSA)

- Allows SCCs and SMCs to run in multiplexed and/or non-multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame synchronization, and clocking

#### **Features**

- Allows dynamic changes

- Can be internally connected to six serial channels (four SCCs and two SMCs)

- Parallel interface port (PIP)

- Centronics interface support

- Supports fast connection between compatible ports on the MPC860 or the MC68360

- PCMCIA interface

- Master (socket) interface, release 2.1 compliant

- Supports two independent PCMCIA sockets

- Supports eight memory or I/O windows

- Low power support

- Full on—all units fully powered

- Doze—core functional units disabled except time base decrementer, PLL, memory controller, RTC, and CPM in low-power standby

- Sleep—all units disabled except RTC and PIT, PLL active for fast wake up

- Deep sleep—all units disabled including PLL except RTC and PIT

- Power down mode—all units powered down except PLL, RTC, PIT, time base, and decrementer

- Debug interface

- Eight comparators: four operate on instruction address, two operate on data address, and two operate on data

- Supports conditions:  $= \neq < >$

- Each watchpoint can generate a break-point internally.

- 3.3-V operation with 5-V TTL compatibility except EXTAL and EXTCLK

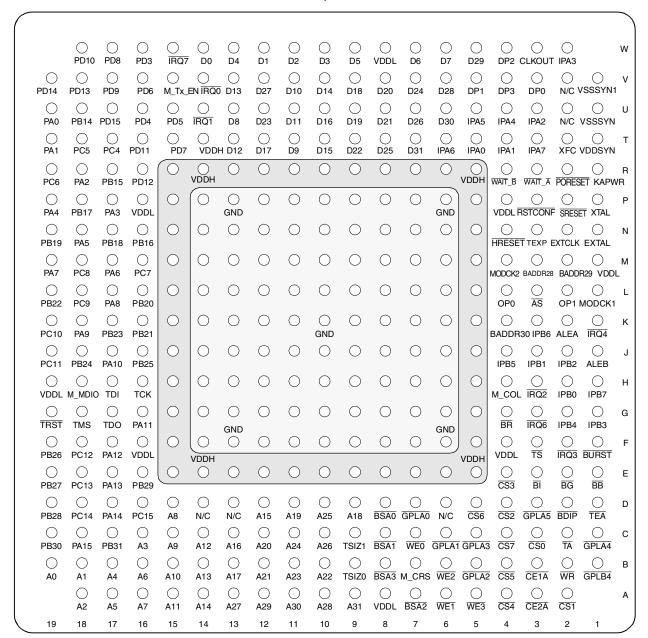

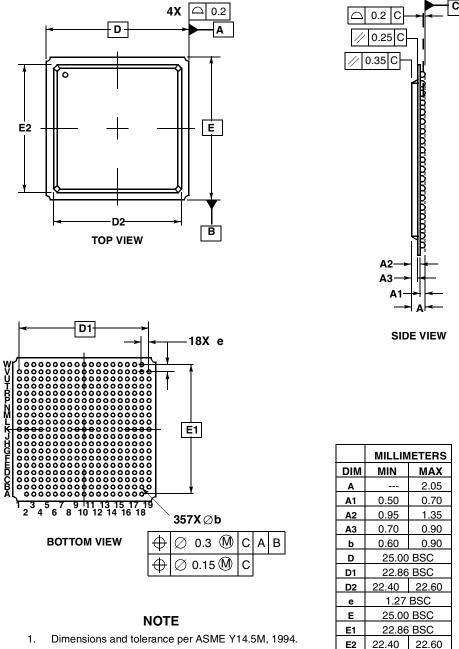

- 357-pin ball grid array (BGA) package

# 3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC860. Table 2 provides the maximum ratings.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or V<sub>DD</sub>).

**Table 2. Maximum Tolerated Ratings**

(GND = 0 V)

| Rating                              | Symbol              | Value                         | Unit |

|-------------------------------------|---------------------|-------------------------------|------|

| Supply voltage <sup>1</sup>         | V <sub>DDH</sub>    | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDL</sub>    | -0.3 to 4.0                   | V    |

|                                     | KAPWR               | -0.3 to 4.0                   | V    |

|                                     | V <sub>DDSYN</sub>  | -0.3 to 4.0                   | V    |

| Input voltage <sup>2</sup>          | V <sub>in</sub>     | GND – 0.3 to V <sub>DDH</sub> | V    |

| Temperature <sup>3</sup> (standard) | T <sub>A(min)</sub> | 0                             | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Temperature <sup>3</sup> (extended) | T <sub>A(min)</sub> | -40                           | °C   |

|                                     | T <sub>j(max)</sub> | 95                            | °C   |

| Storage temperature range           | T <sub>stg</sub>    | -55 to 150                    | °C   |

<sup>&</sup>lt;sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

Functional operating conditions are provided with the DC electrical specifications in Table 6. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device.

**Caution**: All inputs that tolerate 5 V cannot be more than 2.5 V greater than the supply voltage. This restriction applies to power-up and normal operation (that is, if the MPC860 is unpowered, voltage greater than 2.5 V must not be applied to its inputs).

<sup>&</sup>lt;sup>3</sup> Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as junction temperature, T<sub>i</sub>.

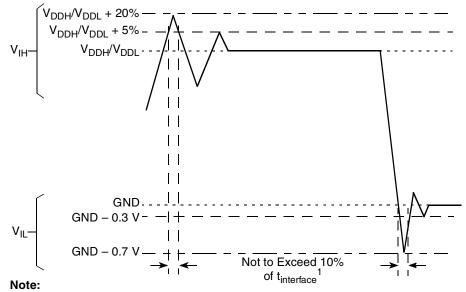

Figure 1 shows the undershoot and overshoot voltages at the interface of the MPC860.

1.  $t_{\text{interface}}$  refers to the clock period associated with the bus clock interface.

Figure 1. Undershoot/Overshoot Voltage for  $V_{DDH}$  and  $V_{DDL}$

## 4 Thermal Characteristics

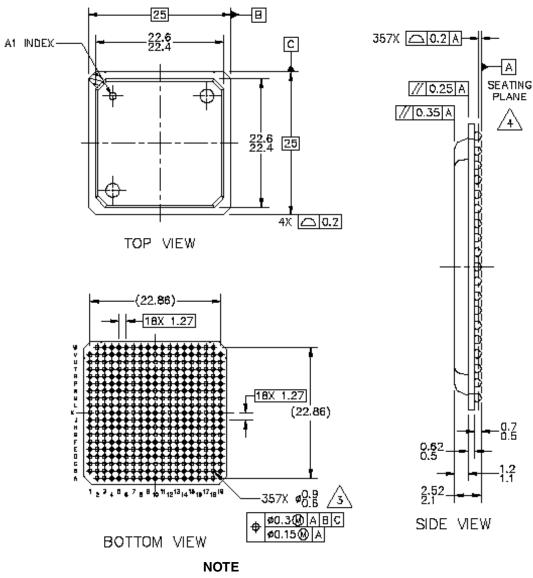

**Table 3. Package Description**

| Package Designator | Package Code (Case No.) | Package Description     |

|--------------------|-------------------------|-------------------------|

| ZP                 | 5050 (1103-01)          | PBGA 357 25*25*0.9P1.27 |

| ZQ/VR              | 5058 (1103D-02)         | PBGA 357 25*25*1.2P1.27 |

Table 4 shows the thermal characteristics for the MPC860.

Table 4. MPC860 Thermal Resistance Data

| Rating                                              | Env                  | ironment                | Symbol                         | ZP<br>MPC860P | ZQ / VR<br>MPC860P | Unit |

|-----------------------------------------------------|----------------------|-------------------------|--------------------------------|---------------|--------------------|------|

| Mold Compound Thicknes                              | s                    |                         |                                | 0.85          | 1.15               | mm   |

| Junction-to-ambient <sup>1</sup> Natural convection |                      | Single-layer board (1s) | $R_{\theta JA}^2$              | 34            | 34                 | •C/W |

|                                                     |                      | Four-layer board (2s2p) | R <sub>0JMA</sub> <sup>3</sup> | 22            | 22                 |      |

|                                                     | Airflow (200 ft/min) | Single-layer board (1s) | R <sub>0JMA</sub> <sup>3</sup> | 27            | 27                 |      |

|                                                     |                      | Four-layer board (2s2p) | R <sub>0JMA</sub> <sup>3</sup> | 18            | 18                 |      |

| Junction-to-board 4                                 |                      |                         | $R_{\theta JB}$                | 14            | 13                 |      |

| Junction-to-case 5                                  |                      |                         | $R_{\theta JC}$                | 6             | 8                  |      |

| Junction-to-package top <sup>6</sup>                | Natural convection   |                         | $\Psi_{JT}$                    | 2             | 2                  |      |

Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

$<sup>^2\,</sup>$  Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

<sup>&</sup>lt;sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>&</sup>lt;sup>4</sup> Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature. For exposed pad packages where the pad would be expected to be soldered, junction-to-case thermal resistance is a simulated value from the junction to the exposed pad without contact resistance.

<sup>&</sup>lt;sup>6</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2.

**Power Dissipation**

# 5 Power Dissipation

Table 5 provides power dissipation information. The modes are 1:1, where CPU and bus speeds are equal, and 2:1, where CPU frequency is twice the bus speed.

Table 5. Power Dissipation (P<sub>D</sub>)

| Die Revision   | Frequency (MHz) | Typical <sup>1</sup> | Maximum <sup>2</sup> | Unit |

|----------------|-----------------|----------------------|----------------------|------|

| D.4 (1:1 mode) | 50              | 656                  | 735                  | mW   |

| (1:1 mode)     | 66              | TBD                  | TBD                  | mW   |

| D.4            | 66              | 722                  | 762                  | mW   |

| (2:1 mode)     | 80              | 851                  | 909                  | mW   |

Typical power dissipation is measured at 3.3 V.

#### **NOTE**

Values in Table 5 represent  $V_{DDL}$ -based power dissipation and do not include I/O power dissipation over  $V_{DDH}$ . I/O power dissipation varies widely by application due to buffer current, depending on external circuitry.

## 6 DC Characteristics

Table 6 provides the DC electrical characteristics for the MPC860.

**Table 6. DC Electrical Specifications**

| Characteristic                                                                                | Symbol                                                                  | Min                    | Max                    | Unit |  |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------|------------------------|------|--|

| Operating voltage at 40 MHz or less                                                           | V <sub>DDH</sub> , V <sub>DDL</sub> , V <sub>DDSYN</sub>                | 3.0                    | 3.6                    | V    |  |

|                                                                                               | KAPWR<br>(power-down mode)                                              | 2.0                    | 3.6                    | V    |  |

|                                                                                               | KAPWR (all other operating modes) V <sub>DDH</sub> = 0.4 V <sub>D</sub> |                        |                        |      |  |

| Operating voltage greater than 40 MHz                                                         | V <sub>DDH</sub> , V <sub>DDL</sub> , KAPWR,<br>V <sub>DDSYN</sub>      | 3.135                  | 3.465                  | V    |  |

|                                                                                               | KAPWR<br>(power-down mode)                                              | 2.0                    | 3.6                    | V    |  |

|                                                                                               | KAPWR (all other operating modes)                                       | V <sub>DDH</sub> – 0.4 | V <sub>DDH</sub>       | ٧    |  |

| Input high voltage (all inputs except EXTAL and EXTCLK)                                       | V <sub>IH</sub>                                                         | 2.0                    | 5.5                    | V    |  |

| Input low voltage <sup>1</sup>                                                                | V <sub>IL</sub>                                                         | GND                    | 0.8                    | V    |  |

| EXTAL, EXTCLK input high voltage                                                              | V <sub>IHC</sub>                                                        | $0.7 \times (V_{DDH})$ | V <sub>DDH</sub> + 0.3 | V    |  |

| Input leakage current, $V_{in}$ = 5.5 V (except TMS, $\overline{TRST}$ , DSCK, and DSDI pins) | l <sub>in</sub>                                                         | _                      | 100                    | μΑ   |  |

<sup>&</sup>lt;sup>2</sup> Maximum power dissipation is measured at 3.5 V.

**Table 6. DC Electrical Specifications (continued)**

| Characteristic                                                                                                                                                                                                                                                                                            | Symbol          | Min | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|------|

| Input leakage current, $V_{in}$ = 3.6 V (except TMS, $\overline{TRST}$ , DSCK, and DSDI pins)                                                                                                                                                                                                             | l <sub>In</sub> | _   | 10  | μΑ   |

| Input leakage current, V <sub>in</sub> = 0 V (except TMS, TRST, DSCK, and DSDI pins)                                                                                                                                                                                                                      | I <sub>In</sub> | _   | 10  | μΑ   |

| Input capacitance <sup>2</sup>                                                                                                                                                                                                                                                                            | C <sub>in</sub> | _   | 20  | pF   |

| Output high voltage, $I_{OH} = -2.0$ mA, $V_{DDH} = 3.0$ V (except XTAL, XFC, and open-drain pins)                                                                                                                                                                                                        | V <sub>OH</sub> | 2.4 | _   | V    |

| Output low voltage $I_{OL} = 2.0 \text{ mA, CLKOUT}$ $I_{OL} = 3.2 \text{ mA}^3$ $I_{OL} = 5.3 \text{ mA}^4$ $I_{OL} = 7.0 \text{ mA, TXD1/PA14, TXD2/PA12}$ $I_{OL} = 8.9 \text{ mA, } \overline{TS}, \overline{TA}, \overline{TEA}, \overline{BI}, \overline{BB}, \overline{HRESET}, \overline{SRESET}$ | V <sub>OL</sub> | _   | 0.5 | V    |

$<sup>^{1}</sup>$  V<sub>IL</sub>(max) for the I<sup>2</sup>C interface is 0.8 V rather than the 1.5 V as specified in the I<sup>2</sup>C standard.

<sup>&</sup>lt;sup>2</sup> Input capacitance is periodically sampled.

<sup>3</sup> A(0:31), TSIZ0/REG, TSIZ1, D(0:31), DP(0:3)/IRQ(3:6), RD/WR, BURST, RSV/IRQ2, IP\_B(0:1)/IWP(0:1)/VFLS(0:1), IP\_B2/IOIS16\_B/AT2, IP\_B3/IWP2/VF2, IP\_B4/LWP0/VF0, IP\_B5/LWP1/VF1, IP\_B6/DSDI/AT0, IP\_B7/PTR/AT3, RXD1/PA15, RXD2/PA13, L1TXDB/PA11, L1RXDB/PA10, L1TXDA/PA9, L1RXDA/PA8, TIN1/L1RCLKA/BRGO1/CLK1/PA7, BRGCLK1/TOUT1/CLK2/PA6, TIN2/L1TCLKA/BRGO2/CLK3/PA5, TOUT2/CLK4/PA4, TIN3/BRGO3/CLK5/PA3, BRGCLK2/L1RCLKB/TOUT3/CLK6/PA2, TIN4/BRGO4/CLK7/PA1, L1TCLKB/TOUT4/CLK8/PA0, REJCT1/SPISEL/PB31, SPICLK/PB30,SPIMOSI/PB29, BRGO4/SPIMISO/PB28, BRGO1/I2CSDA/PB27, BRGO2/I2CSCL/PB26, SMTXD1/PB25, SMRXD1/PB24, SMSYN1/SDACK1/PB23, SMSYN2/SDACK2/PB22, SMTXD2/L1CLKOB/PB21, SMRXD2/L1CLKOA/PB20, L1ST1/RTS1/PB19, L1ST2/RTS2/PB18, L1ST3/L1RQB/PB17, L1ST4/L1RQA/PB16, BRGO3/PB15, RSTRT1/PB14, L1ST1/RTS1/DREQ0/PC15, L1ST2/RTS2/DREQ1/PC14, L1ST3/L1RQB/PC13, L1ST4/L1RQA/PC12, CTS1/PC11, TGATE1/CD1/PC10, CTS2/PC9, TGATE2/CD2/PC8, SDACK2/L1TSYNCB/PC7, L1RSYNCB/PC6, SDACK1/L1TSYNCA/PC5, L1RSYNCA/PC4, PD15, PD14, PD13, PD12, PD11, PD10, PD9, PD8, PD5, PD6, PD7, PD4, PD3, MII\_MDC, MII\_TX\_ER, MII\_EN, MII\_MDIO, and MII\_TXD[0:3]

BDIP/GPL\_B(5), BR, BG, FRZ/IRQ6, CS(0:5), CS(6)/CE(1)\_B, CS(7)/CE(2)\_B, WE0/BS\_B0/IORD, WE1/BS\_B1/IOWR, WE2/BS\_B2/PCOE, WE3/BS\_B3/PCWE, BS\_A(0:3), GPL\_A0/GPL\_B0, OE/GPL\_A1/GPL\_B1, GPL\_A(2:3)/GPL\_B(2:3)/CS(2:3), UPWAITA/GPL\_A4, UPWAITB/GPL\_B4, GPL\_A5, ALE\_A, CE1\_A, CE2\_A, ALE\_B/DSCK/AT1, OP(0:1), OP2/MODCK1/STS, OP3/MODCK2/DSDO, and BADDR(28:30)

## 7 Thermal Calculation and Measurement

For the following discussions,  $P_D = (V_{DD} \times I_{DD}) + PI/O$ , where PI/O is the power dissipation of the I/O drivers.

#### 7.1 Estimation with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>I</sub>, in °C can be obtained from the equation:

$$T_I = T_A + (R_{\theta IA} \times P_D)$$

where:

$T_A$  = ambient temperature (°C)

$R_{\theta JA}$  = package junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in package

The junction-to-ambient thermal resistance is an industry standard value which provides a quick and easy estimation of thermal performance. However, the answer is only an estimate; test cases have demonstrated that errors of a factor of two (in the quantity  $T_I - T_A$ ) are possible.

## 7.2 Estimation with Junction-to-Case Thermal Resistance

Historically, the thermal resistance has frequently been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$$R_{\theta IA} = R_{\theta IC} + R_{\theta CA}$$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user adjusts the thermal environment to affect the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the airflow around the device, add a heat sink, change the mounting arrangement on the printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device. This thermal model is most useful for ceramic packages with heat sinks where some 90% of the heat flows through the case and the heat sink to the ambient environment. For most packages, a better model is required.

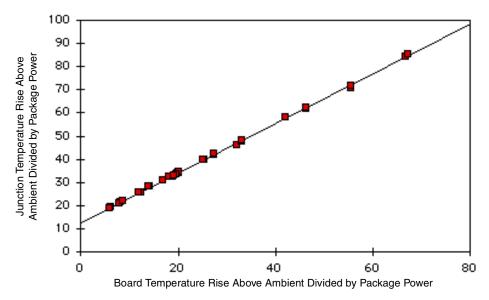

## 7.3 Estimation with Junction-to-Board Thermal Resistance

A simple package thermal model which has demonstrated reasonable accuracy (about 20%) is a two-resistor model consisting of a junction-to-board and a junction-to-case thermal resistance. The junction-to-case thermal resistance covers the situation where a heat sink is used or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed-circuit board. It has been observed that the thermal performance of most plastic packages, especially PBGA packages, is strongly dependent on the board temperature; see Figure 2.

Figure 2. Effect of Board Temperature Rise on Thermal Behavior

If the board temperature is known, an estimate of the junction temperature in the environment can be made using the following equation:

$$T_J = T_B + (R_{\theta JB} \times P_D)$$

where:

$R_{\theta JB}$  = junction-to-board thermal resistance (°C/W)

$T_B$  = board temperature (°C)

$P_D$  = power dissipation in package

If the board temperature is known and the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. For this method to work, the board and board mounting must be similar to the test board used to determine the junction-to-board thermal resistance, namely a 2s2p (board with a power and a ground plane) and by attaching the thermal balls to the ground plane.

#### 7.4 **Estimation Using Simulation**

When the board temperature is not known, a thermal simulation of the application is needed. The simple two-resistor model can be used with the thermal simulation of the application [2], or a more accurate and complex model of the package can be used in the thermal simulation.

#### **Experimental Determination** 7.5

To determine the junction temperature of the device in the application after prototypes are available, the thermal characterization parameter  $(\Psi_{IT})$  can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_{J} = T_{T} + (\Psi_{JT} \times P_{D})$$

#### **Layout Practices**

where:

$\Psi_{IT}$  = thermal characterization parameter

$T_T$  = thermocouple temperature on top of package

$P_D$  = power dissipation in package

The thermal characterization parameter is measured per JEDEC JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

#### 7.6 References

Semiconductor Equipment and Materials International (415) 964-5111

805 East Middlefield Rd. Mountain View, CA 94043

MIL-SPEC and EIA/JESD (JEDEC) Specifications 800-854-7179 or (Available from Global Engineering Documents) 303-397-7956

JEDEC Specifications http://www.jedec.org

1. C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

2. B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 8 Layout Practices

Each  $V_{DD}$  pin on the MPC860 should be provided with a low-impedance path to the board's supply. Each GND pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on the chip. The  $V_{DD}$  power supply should be bypassed to ground using at least four  $0.1~\mu F$ -bypass capacitors located as close as possible to the four sides of the package. The capacitor leads and associated printed circuit traces connecting to chip  $V_{DD}$  and GND should be kept to less than half an inch per capacitor lead. A four-layer board employing two inner layers as  $V_{CC}$  and GND planes is recommended.

All output pins on the MPC860 have fast rise and fall times. Printed circuit (PC) trace interconnection length should be minimized in order to minimize undershoot and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of 6 inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the  $V_{\rm CC}$  and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins.

# 9 Bus Signal Timing

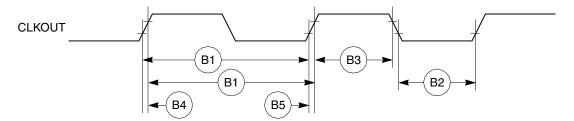

Table 7 provides the bus operation timing for the MPC860 at 33, 40, 50, and 66 MHz.

The maximum bus speed supported by the MPC860 is 66 MHz. Higher-speed parts must be operated in half-speed bus mode (for example, an MPC860 used at 80 MHz must be configured for a 40-MHz bus).

The timing for the MPC860 bus shown assumes a 50-pF load for maximum delays and a 0-pF load for minimum delays.

**Table 7. Bus Operation Timings**

| Norma            | Charastaristis                                                                                                          | 33 1  | ИHz   | 40 [  | MHz   | 50 I  | ИНz   | IHz 66 MHz |       |      |

|------------------|-------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|------------|-------|------|

| Num              | Characteristic                                                                                                          | Min   | Max   | Min   | Max   | Min   | Max   | Min        | Max   | Unit |

| B1               | CLKOUT period                                                                                                           | 30.30 | 30.30 | 25.00 | 30.30 | 20.00 | 30.30 | 15.15      | 30.30 | ns   |

| B1a              | EXTCLK to CLKOUT phase skew (EXTCLK > 15 MHz and MF <= 2)                                                               | -0.90 | 0.90  | -0.90 | 0.90  | -0.90 | 0.90  | -0.90      | 0.90  | ns   |

| B1b              | EXTCLK to CLKOUT phase skew (EXTCLK > 10 MHz and MF < 10)                                                               | -2.30 | 2.30  | -2.30 | 2.30  | -2.30 | 2.30  | -2.30      | 2.30  | ns   |

| B1c              | CLKOUT phase jitter (EXTCLK > 15 MHz and MF <= 2) <sup>1</sup>                                                          | -0.60 | 0.60  | -0.60 | 0.60  | -0.60 | 0.60  | -0.60      | 0.60  | ns   |

| B1d              | CLKOUT phase jitter <sup>1</sup>                                                                                        | -2.00 | 2.00  | -2.00 | 2.00  | -2.00 | 2.00  | -2.00      | 2.00  | ns   |

| B1e              | CLKOUT frequency jitter (MF < 10) <sup>1</sup>                                                                          | _     | 0.50  | _     | 0.50  | _     | 0.50  | _          | 0.50  | %    |

| B1f              | CLKOUT frequency jitter (10 < MF < 500) <sup>1</sup>                                                                    | _     | 2.00  | _     | 2.00  | _     | 2.00  | _          | 2.00  | %    |

| B1g              | CLKOUT frequency jitter (MF > 500) <sup>1</sup>                                                                         | _     | 3.00  | _     | 3.00  | _     | 3.00  | _          | 3.00  | %    |

| B1h              | Frequency jitter on EXTCLK <sup>2</sup>                                                                                 | _     | 0.50  | _     | 0.50  | _     | 0.50  | _          | 0.50  | %    |

| B2               | CLKOUT pulse width low                                                                                                  | 12.12 | _     | 10.00 | _     | 8.00  | _     | 6.06       | _     | ns   |

| В3               | CLKOUT width high                                                                                                       | 12.12 | _     | 10.00 | _     | 8.00  | _     | 6.06       | _     | ns   |

| B4               | CLKOUT rise time <sup>3</sup>                                                                                           | _     | 4.00  | _     | 4.00  | _     | 4.00  | _          | 4.00  | ns   |

| B5 <sup>33</sup> | CLKOUT fall time <sup>3</sup>                                                                                           | _     | 4.00  | _     | 4.00  | _     | 4.00  | _          | 4.00  | ns   |

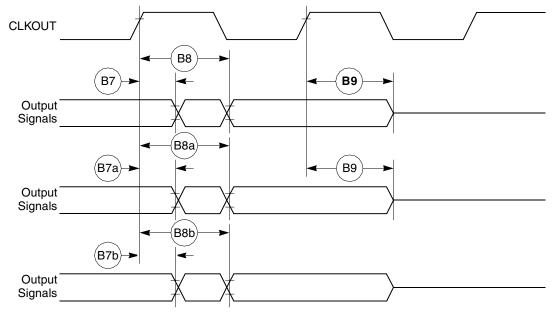

| В7               | CLKOUT to A(0:31), BADDR(28:30),<br>RD/WR, BURST, D(0:31), DP(0:3) invalid                                              | 7.58  | _     | 6.25  | _     | 5.00  | _     | 3.80       | _     | ns   |

| В7а              | CLKOUT to TSIZ(0:1), REG, RSV, AT(0:3), BDIP, PTR invalid                                                               | 7.58  |       | 6.25  | _     | 5.00  | _     | 3.80       | _     | ns   |

| B7b              | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , FRZ, VFLS(0:1), VF(0:2) IWP(0:2), LWP(0:1), $\overline{STS}$ invalid $^4$ | 7.58  | _     | 6.25  | _     | 5.00  | _     | 3.80       | _     | ns   |

| B8               | CLKOUT to A(0:31), BADDR(28:30)<br>RD/WR, BURST, D(0:31), DP(0:3) valid                                                 | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80       | 10.04 | ns   |

| B8a              | CLKOUT to TSIZ(0:1), REG, RSV, AT(0:3) BDIP, PTR valid                                                                  | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80       | 10.04 | ns   |

| B8b              | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , VFLS(0:1), VF(0:2), IWP(0:2), FRZ, LWP(0:1), $\overline{STS}$ valid $^4$  | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80       | 10.04 | ns   |

**Table 7. Bus Operation Timings (continued)**

| Num  | Characteristic                                                                                                  | 33 I  | ИНz   | 40 I  | MHz   | 50 I  | ИHz   | 66 MHz |       | Unit |

|------|-----------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                  | Min   | Max   | Min   | Max   | Min   | Max   | Min    | Max   | Unit |

| B9   | CLKOUT to A(0:31), BADDR(28:30),<br>RD/WR, BURST, D(0:31), DP(0:3),<br>TSIZ(0:1), REG, RSV, AT(0:3), PTR High-Z | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80   | 10.04 | ns   |

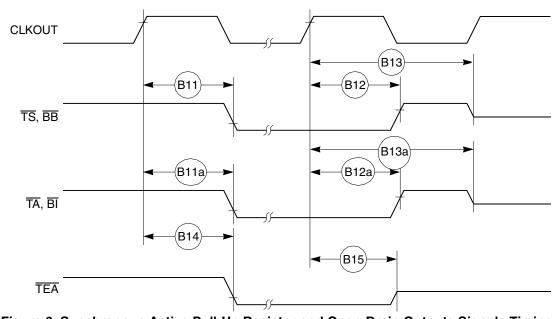

| B11  | CLKOUT to TS, BB assertion                                                                                      | 7.58  | 13.58 | 6.25  | 12.25 | 5.00  | 11.00 | 3.80   | 11.29 | ns   |

| B11a | CLKOUT to TA, BI assertion (when driven by the memory controller or PCMCIA interface)                           | 2.50  | 9.25  | 2.50  | 9.25  | 2.50  | 9.25  | 2.50   | 9.75  | ns   |

| B12  | CLKOUT to TS, BB negation                                                                                       | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80   | 8.54  | ns   |

| B12a | CLKOUT to TA, BI negation (when driven by the memory controller or PCMCIA interface)                            | 2.50  | 11.00 | 2.50  | 11.00 | 2.50  | 11.00 | 2.50   | 9.00  | ns   |

| B13  | CLKOUT to TS, BB High-Z                                                                                         | 7.58  | 21.58 | 6.25  | 20.25 | 5.00  | 19.00 | 3.80   | 14.04 | ns   |

| B13a | CLKOUT to TA, BI High-Z (when driven by the memory controller or PCMCIA interface)                              | 2.50  | 15.00 | 2.50  | 15.00 | 2.50  | 15.00 | 2.50   | 15.00 | ns   |

| B14  | CLKOUT to TEA assertion                                                                                         | 2.50  | 10.00 | 2.50  | 10.00 | 2.50  | 10.00 | 2.50   | 9.00  | ns   |

| B15  | CLKOUT to TEA High-Z                                                                                            | 2.50  | 15.00 | 2.50  | 15.00 | 2.50  | 15.00 | 2.50   | 15.00 | ns   |

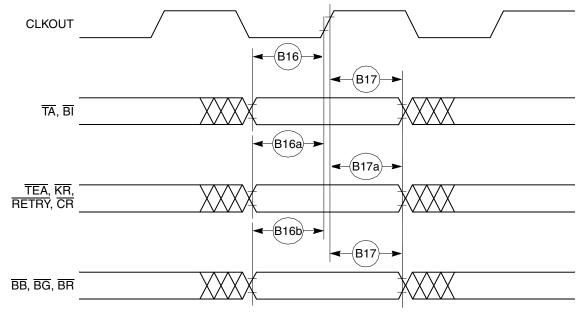

| B16  | TA, BI valid to CLKOUT (setup time)                                                                             | 9.75  | _     | 9.75  | _     | 9.75  | _     | 6.00   | _     | ns   |

| B16a | TEA, KR, RETRY, CR valid to CLKOUT (setup time)                                                                 | 10.00 | _     | 10.00 | _     | 10.00 | _     | 4.50   | _     | ns   |

| B16b | $\overline{BB}, \overline{BG}, \overline{BR},$ valid to CLKOUT (setup time) $^5$                                | 8.50  | _     | 8.50  | _     | 8.50  | _     | 4.00   | _     | ns   |

| B17  | CLKOUT to TA, TEA, BI, BB, BG, BR valid (hold time)                                                             | 1.00  | _     | 1.00  | _     | 1.00  | _     | 2.00   | _     | ns   |

| B17a | CLKOUT to KR, RETRY, CR valid (hold time)                                                                       | 2.00  | _     | 2.00  | _     | 2.00  | _     | 2.00   | _     | ns   |

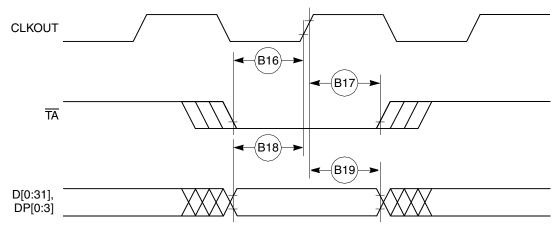

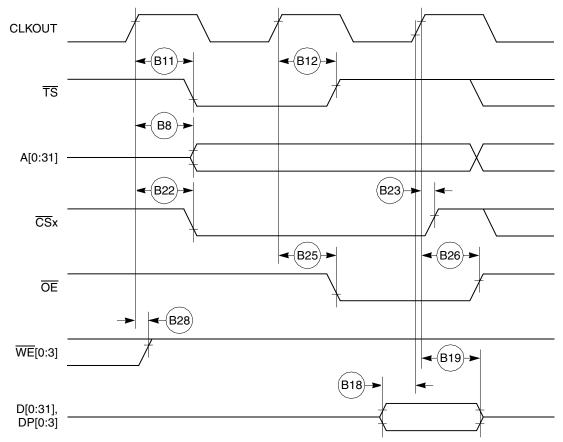

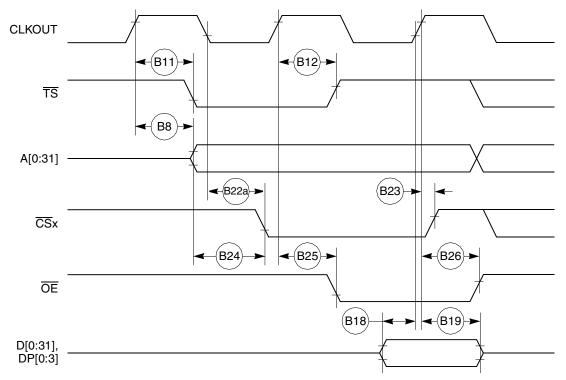

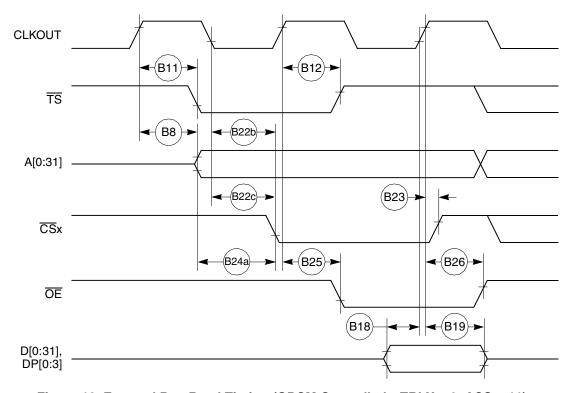

| B18  | D(0:31), DP(0:3) valid to CLKOUT rising edge (setup time) <sup>6</sup>                                          | 6.00  | _     | 6.00  | _     | 6.00  | _     | 6.00   | _     | ns   |

| B19  | CLKOUT rising edge to D(0:31), DP(0:3) valid (hold time) <sup>6</sup>                                           | 1.00  | _     | 1.00  | _     | 1.00  | _     | 2.00   | _     | ns   |

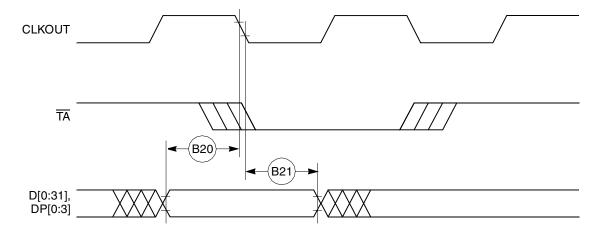

| B20  | D(0:31), DP(0:3) valid to CLKOUT falling edge (setup time) <sup>7</sup>                                         | 4.00  | _     | 4.00  | _     | 4.00  | _     | 4.00   | _     | ns   |

| B21  | CLKOUT falling edge to D(0:31), DP(0:3) valid (hold time) <sup>7</sup>                                          | 2.00  | _     | 2.00  | _     | 2.00  | _     | 2.00   | _     | ns   |

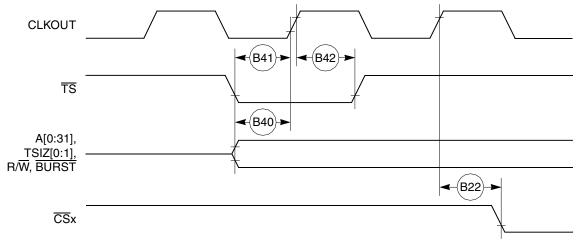

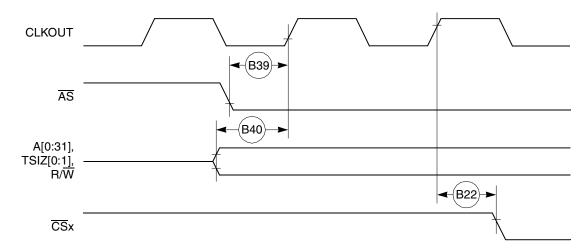

| B22  | CLKOUT rising edge to $\overline{\text{CS}}$ asserted GPCM ACS = 00                                             | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80   | 10.04 | ns   |

| B22a | CLKOUT falling edge to $\overline{\text{CS}}$ asserted GPCM ACS = 10, TRLX = 0                                  | _     | 8.00  | _     | 8.00  | _     | 8.00  | _      | 8.00  | ns   |

| B22b | CLKOUT falling edge to $\overline{\text{CS}}$ asserted GPCM ACS = 11, TRLX = 0, EBDF = 0                        | 7.58  | 14.33 | 6.25  | 13.00 | 5.00  | 11.75 | 3.80   | 10.54 | ns   |

| B22c | CLKOUT falling edge to $\overline{\text{CS}}$ asserted GPCM ACS = 11, TRLX = 0, EBDF = 1                        | 10.86 | 17.99 | 8.88  | 16.00 | 7.00  | 14.13 | 5.18   | 12.31 | ns   |

MPC860 PowerQUICC Family Hardware Specifications, Rev. 9

**Table 7. Bus Operation Timings (continued)**

| Ni   | Charactariatia                                                                                                                        | 33 1  | MHz 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit  |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-------|--------|-------|--------|-------|-------|------|

| Num  | Characteristic                                                                                                                        | Min   | Max        | Min   | Max    | Min   | Max    | Min   | Max   | Unit |

| B23  | CLKOUT rising edge to $\overline{\text{CS}}$ negated GPCM read access, GPCM write access ACS = 00, TRLX = 0, and CSNT = 0             | 2.00  | 8.00       | 2.00  | 8.00   | 2.00  | 8.00   | 2.00  | 8.00  | ns   |

| B24  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 10, TRLX = 0                                                          | 5.58  | _          | 4.25  | _      | 3.00  | _      | 1.79  | _     | ns   |

| B24a | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 11, TRLX = 0                                                          | 13.15 | _          | 10.50 | _      | 8.00  | _      | 5.58  |       | ns   |

| B25  | CLKOUT rising edge to $\overline{OE}$ , $\overline{WE}$ (0:3) asserted                                                                | _     | 9.00       | _     | 9.00   | _     | 9.00   | _     | 9.00  | ns   |

| B26  | CLKOUT rising edge to OE negated                                                                                                      | 2.00  | 9.00       | 2.00  | 9.00   | 2.00  | 9.00   | 2.00  | 9.00  | ns   |

| B27  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 10, TRLX = 1                                                          | 35.88 | _          | 29.25 | _      | 23.00 | _      | 16.94 | _     | ns   |

| B27a | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted GPCM ACS = 11, TRLX = 1                                                          | 43.45 | _          | 35.50 | _      | 28.00 | _      | 20.73 | _     | ns   |

| B28  | CLKOUT rising edge to $\overline{\text{WE}}(0:3)$ negated GPCM write access CSNT = 0                                                  | _     | 9.00       | _     | 9.00   | _     | 9.00   | _     | 9.00  | ns   |

| B28a | CLKOUT falling edge to $\overline{WE}(0:3)$ negated GPCM write access TRLX = 0, 1, CSNT = 1, EBDF = 0                                 | 7.58  | 14.33      | 6.25  | 13.00  | 5.00  | 11.75  | 3.80  | 10.54 | ns   |

| B28b | CLKOUT falling edge to $\overline{CS}$ negated GPCM write access TRLX = 0, 1, CSNT = 1, ACS = 10, or ACS = 11, EBDF = 0               | _     | 14.33      | _     | 13.00  | _     | 11.75  | _     | 10.54 | ns   |

| B28c | CLKOUT falling edge to $\overline{WE}(0:3)$ negated GPCM write access TRLX = 0, 1, CSNT = 1 write access TRLX = 0, CSNT = 1, EBDF = 1 | 10.86 | 17.99      | 8.88  | 16.00  | 7.00  | 14.13  | 5.18  | 12.31 | ns   |

| B28d | CLKOUT falling edge to $\overline{CS}$ negated GPCM write access TRLX = 0, 1, CSNT = 1, ACS = 10, or ACS = 11, EBDF = 1               | _     | 17.99      | _     | 16.00  | _     | 14.13  | _     | 12.31 | ns   |

| B29  | WE(0:3) negated to D(0:31), DP(0:3) High-Z<br>GPCM write access CSNT = 0, EBDF = 0                                                    | 5.58  | _          | 4.25  | _      | 3.00  | _      | 1.79  | _     | ns   |

| B29a | WE(0:3) negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>EBDF = 0                                      | 13.15 | _          | 10.5  | _      | 8.00  | _      | 5.58  | _     | ns   |

| B29b | CS negated to D(0:31), DP(0:3), High-Z<br>GPCM write access, ACS = 00, TRLX = 0, 1,<br>and CSNT = 0                                   | 5.58  |            | 4.25  |        | 3.00  | _      | 1.79  |       | ns   |

| B29c | CS negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 0                    | 13.15 | _          | 10.5  | _      | 8.00  | _      | 5.58  |       | ns   |

**Table 7. Bus Operation Timings (continued)**

| N    | Observatoristis                                                                                                                                                                                             | 33 1  | ИНz  | 40 I  | ИHz  | 50 I  | ИHz  | 66 MHz |      | 11!4 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|-------|------|--------|------|------|

| Num  | Characteristic                                                                                                                                                                                              | Min   | Max  | Min   | Max  | Min   | Max  | Min    | Max  | Unit |

| B29d | WE(0:3) negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>EBDF = 0                                                                                                            | 43.45 | _    | 35.5  | _    | 28.00 | _    | 20.73  | _    | ns   |

| B29e | CS negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 0                                                                                          | 43.45 |      | 35.5  |      | 28.00 |      | 29.73  |      | ns   |

| B29f | WE(0:3) negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>EBDF = 1                                                                                                            | 8.86  |      | 6.88  | 1    | 5.00  | 1    | 3.18   | 1    | ns   |

| B29g | CS negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                                                                                          | 8.86  | _    | 6.88  |      | 5.00  |      | 3.18   |      | ns   |

| B29h | WE(0:3) negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>EBDF = 1                                                                                                            | 38.67 | _    | 31.38 |      | 24.50 |      | 17.83  |      | ns   |

| B29i | CS negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>ACS = 10, or ACS = 11, EBDF = 1                                                                                          | 38.67 | _    | 31.38 |      | 24.50 |      | 17.83  |      | ns   |

| B30  | CS, WE(0:3) negated to A(0:31), BADDR(28:30) invalid GPCM write access <sup>8</sup>                                                                                                                         | 5.58  | _    | 4.25  | _    | 3.00  | _    | 1.79   | _    | ns   |

| B30a | WE(0:3) negated to A(0:31), BADDR(28:30) invalid GPCM, write access, TRLX = 0, CSNT = 1, CS negated to A(0:31) invalid GPCM write access, TRLX = 0, CSNT = 1 ACS = 10, or ACS = 11, EBDF = 0                | 13.15 | _    | 10.50 |      | 8.00  |      | 5.58   |      | ns   |

| B30b | WE(0:3) negated to A(0:31), invalid GPCM BADDR(28:30) invalid GPCM write access, TRLX = 1, CSNT = 1. CS negated to A(0:31), Invalid GPCM, write access, TRLX = 1, CSNT = 1, ACS = 10, or ACS = 11, EBDF = 0 | 43.45 | _    | 35.50 | _    | 28.00 | _    | 20.73  | _    | ns   |

| B30c | WE(0:3) negated to A(0:31), BADDR(28:30) invalid GPCM write access, TRLX = 0, CSNT = 1. CS negated to A(0:31) invalid GPCM write access, TRLX = 0, CSNT = 1, ACS = 10, ACS = 11, EBDF = 1                   | 8.36  |      | 6.38  | 1    | 4.50  | 1    | 2.68   | 1    | ns   |

| B30d | WE(0:3) negated to A(0:31), BADDR(28:30) invalid GPCM write access, TRLX = 1, CSNT = 1. CS negated to A(0:31) invalid GPCM write access TRLX = 1, CSNT = 1, ACS = 10, or ACS = 11, EBDF = 1                 | 38.67 | _    | 31.38 | _    | 24.50 | _    | 17.83  | _    | ns   |

| B31  | CLKOUT falling edge to CS valid—as requested by control bit CST4 in the corresponding word in UPM                                                                                                           | 1.50  | 6.00 | 1.50  | 6.00 | 1.50  | 6.00 | 1.50   | 6.00 | ns   |

**Table 7. Bus Operation Timings (continued)**

| NI   | Characteristic                                                                                                                       | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit  |

|------|--------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|-------|

| Num  |                                                                                                                                      | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Oiiii |

| B31a | CLKOUT falling edge to CS valid—as requested by control bit CST1 in the corresponding word in UPM                                    | 7.58   | 14.33 | 6.25   | 13.00 | 5.00   | 11.75 | 3.80   | 10.54 | ns    |

| B31b | CLKOUT rising edge to CS valid—as requested by control bit CST2 in the corresponding word in UPM                                     | 1.50   | 8.00  | 1.50   | 8.00  | 1.50   | 8.00  | 1.50   | 8.00  | ns    |

| B31c | CLKOUT rising edge to CS valid—as requested by control bit CST3 in the corresponding word in UPM                                     | 7.58   | 14.33 | 6.25   | 13.00 | 5.00   | 11.75 | 3.80   | 10.04 | ns    |

| B31d | CLKOUT falling edge to $\overline{\text{CS}}$ valid—as requested by control bit CST1 in the corresponding word in UPM, EBDF = 1      | 13.26  | 17.99 | 11.28  | 16.00 | 9.40   | 14.13 | 7.58   | 12.31 | ns    |

| B32  | CLKOUT falling edge to BS valid—as requested by control bit BST4 in the corresponding word in UPM                                    | 1.50   | 6.00  | 1.50   | 6.00  | 1.50   | 6.00  | 1.50   | 6.00  | ns    |

| B32a | CLKOUT falling edge to BS valid—as requested by control bit BST1 in the corresponding word in UPM, EBDF = 0                          | 7.58   | 14.33 | 6.25   | 13.00 | 5.00   | 11.75 | 3.80   | 10.54 | ns    |

| B32b | CLKOUT rising edge to BS valid—as requested by control bit BST2 in the corresponding word in UPM                                     | 1.50   | 8.00  | 1.50   | 8.00  | 1.50   | 8.00  | 1.50   | 8.00  | ns    |

| B32c | CLKOUT rising edge to BS valid—as requested by control bit BST3 in the corresponding word in UPM                                     | 7.58   | 14.33 | 6.25   | 13.00 | 5.00   | 11.75 | 3.80   | 10.54 | ns    |

| B32d | CLKOUT falling edge to BS valid—as requested by control bit BST1 in the corresponding word in UPM, EBDF = 1                          | 13.26  | 17.99 | 11.28  | 16.00 | 9.40   | 14.13 | 7.58   | 12.31 | ns    |

| B33  | CLKOUT falling edge to GPL valid—as requested by control bit GxT4 in the corresponding word in UPM                                   | 1.50   | 6.00  | 1.50   | 6.00  | 1.50   | 6.00  | 1.50   | 6.00  | ns    |

| B33a | CLKOUT rising edge to GPL valid—as requested by control bit GxT3 in the corresponding word in UPM                                    | 7.58   | 14.33 | 6.25   | 13.00 | 5.00   | 11.75 | 3.80   | 10.54 | ns    |

| B34  | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{CS}}$ valid—as requested by control bit CST4 in the corresponding word in UPM | 5.58   |       | 4.25   | _     | 3.00   | _     | 1.79   |       | ns    |

| B34a | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{CS}}$ valid—as requested by control bit CST1 in the corresponding word in UPM | 13.15  | _     | 10.50  | _     | 8.00   | _     | 5.58   |       | ns    |

| B34b | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{CS}}$ valid—as requested by control bit CST2 in the corresponding word in UPM | 20.73  | _     | 16.75  | _     | 13.00  | _     | 9.36   | _     | ns    |

**Table 7. Bus Operation Timings (continued)**

| Num  | Characteristic                                                                                                                | 33 MHz |     | 40 MHz |     | 50 MHz |     | 66 MHz |     | l lmit |

|------|-------------------------------------------------------------------------------------------------------------------------------|--------|-----|--------|-----|--------|-----|--------|-----|--------|

| Num  |                                                                                                                               | Min    | Max | Min    | Max | Min    | Max | Min    | Max | Unit   |

| B35  | A(0:31), BADDR(28:30) to $\overline{\text{CS}}$ valid—as requested by control bit BST4 in the corresponding word in UPM       | 5.58   | _   | 4.25   | _   | 3.00   | _   | 1.79   | _   | ns     |

| B35a | A(0:31), BADDR(28:30), and D(0:31) to $\overline{BS}$ valid—as requested by control bit BST1 in the corresponding word in UPM | 13.15  | _   | 10.50  | _   | 8.00   | _   | 5.58   | _   | ns     |

| B35b | A(0:31), BADDR(28:30), and D(0:31) to $\overline{BS}$ valid—as requested by control bit BST2 in the corresponding word in UPM | 20.73  | _   | 16.75  | _   | 13.00  | _   | 9.36   | _   | ns     |

| B36  | A(0:31), BADDR(28:30), and D(0:31) to GPL valid—as requested by control bit GxT4 in the corresponding word in UPM             | 5.58   | _   | 4.25   | _   | 3.00   | _   | 1.79   | _   | ns     |

| B37  | UPWAIT valid to CLKOUT falling edge <sup>9</sup>                                                                              | 6.00   | _   | 6.00   | _   | 6.00   | _   | 6.00   | _   | ns     |

| B38  | CLKOUT falling edge to UPWAIT valid <sup>9</sup>                                                                              | 1.00   | _   | 1.00   | _   | 1.00   | _   | 1.00   | _   | ns     |

| B39  | AS valid to CLKOUT rising edge <sup>10</sup>                                                                                  | 7.00   | _   | 7.00   | _   | 7.00   | _   | 7.00   | _   | ns     |

| B40  | A(0:31), TSIZ(0:1), RD/WR, BURST, valid to CLKOUT rising edge                                                                 | 7.00   | _   | 7.00   | _   | 7.00   | _   | 7.00   | _   | ns     |

| B41  | TS valid to CLKOUT rising edge (setup time)                                                                                   | 7.00   | _   | 7.00   | _   | 7.00   | _   | 7.00   | _   | ns     |

| B42  | CLKOUT rising edge to TS valid (hold time)                                                                                    | 2.00   | _   | 2.00   | _   | 2.00   | _   | 2.00   | _   | ns     |

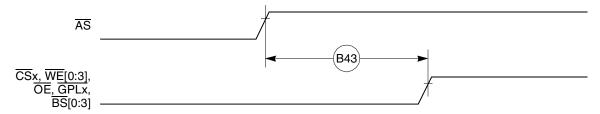

| B43  | AS negation to memory controller signals negation                                                                             | _      | TBD | _      | TBD | _      | TBD | _      | TBD | ns     |

<sup>1</sup> Phase and frequency jitter performance results are only valid if the input jitter is less than the prescribed value.

<sup>&</sup>lt;sup>2</sup> If the rate of change of the frequency of EXTAL is slow (that is, it does not jump between the minimum and maximum values in one cycle) or the frequency of the jitter is fast (that is, it does not stay at an extreme value for a long time) then the maximum allowed jitter on EXTAL can be up to 2%.

<sup>&</sup>lt;sup>3</sup> The timings specified in B4 and B5 are based on full strength clock.

<sup>&</sup>lt;sup>4</sup> The timing for  $\overline{BR}$  output is relevant when the MPC860 is selected to work with external bus arbiter. The timing for  $\overline{BG}$  output is relevant when the MPC860 is selected to work with internal bus arbiter.

<sup>&</sup>lt;sup>5</sup> The timing required for  $\overline{BR}$  input is relevant when the MPC860 is selected to work with internal bus arbiter. The timing for  $\overline{BG}$  input is relevant when the MPC860 is selected to work with external bus arbiter.

<sup>&</sup>lt;sup>6</sup> The D(0:31) and DP(0:3) input timings B18 and B19 refer to the rising edge of the CLKOUT in which the TA input signal is asserted.

The D(0:31) and DP(0:3) input timings B20 and B21 refer to the falling edge of the CLKOUT. This timing is valid only for read accesses controlled by chip-selects under control of the UPM in the memory controller, for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

<sup>&</sup>lt;sup>8</sup> The timing B30 refers to  $\overline{CS}$  when ACS = 00 and to  $\overline{WE}$ (0:3) when CSNT = 0.

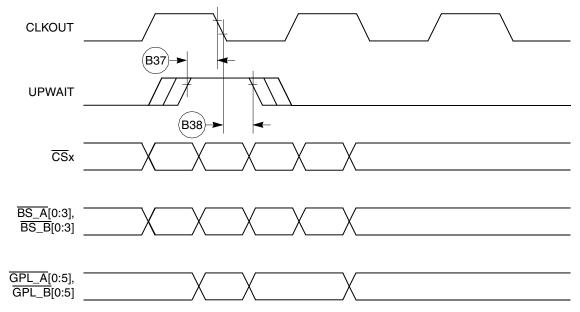

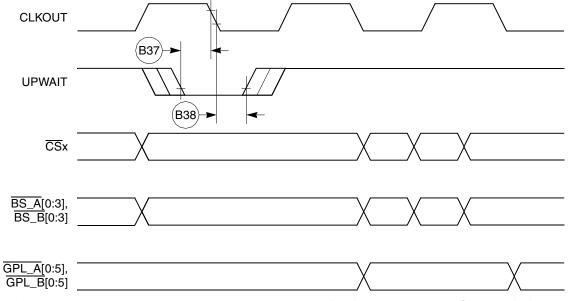

<sup>&</sup>lt;sup>9</sup> The signal UPWAIT is considered asynchronous to the CLKOUT and synchronized internally. The timings specified in B37 and B38 are specified to enable the freeze of the UPM output signals as described in Figure 18.

<sup>&</sup>lt;sup>10</sup> The  $\overline{\text{AS}}$  signal is considered asynchronous to the CLKOUT. The timing B39 is specified in order to allow the behavior specified in Figure 21.

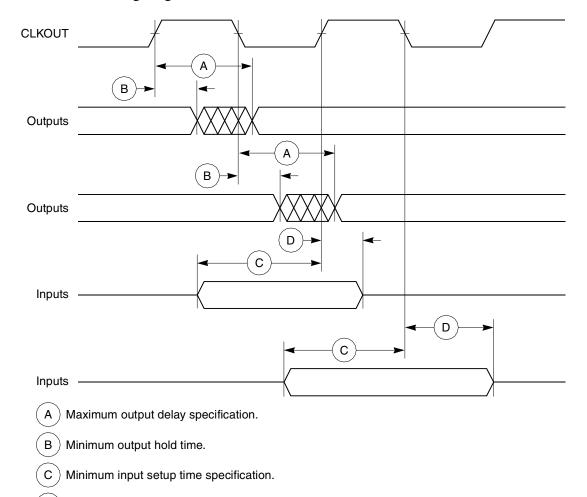

Figure 3 is the control timing diagram.

Figure 3. Control Timing

Figure 4 provides the timing for the external clock.

Minimum input hold time specification.

Figure 4. External Clock Timing

Figure 5 provides the timing for the synchronous output signals.

Figure 5. Synchronous Output Signals Timing

Figure 6 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 6. Synchronous Active Pull-Up Resistor and Open-Drain Outputs Signals Timing

Figure 7 provides the timing for the synchronous input signals.

Figure 7. Synchronous Input Signals Timing

Figure 8 provides normal case timing for input data. It also applies to normal read accesses under the control of the UPM in the memory controller.

Figure 8. Input Data Timing in Normal Case

MPC860 PowerQUICC Family Hardware Specifications, Rev. 9 Freescale Semiconductor 23

#### **Bus Signal Timing**

Figure 9 provides the timing for the input data controlled by the UPM for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

Figure 9. Input Data Timing when Controlled by UPM in the Memory Controller and DLT3 = 1

Figure 10 through Figure 13 provide the timing for the external bus read controlled by various GPCM factors.

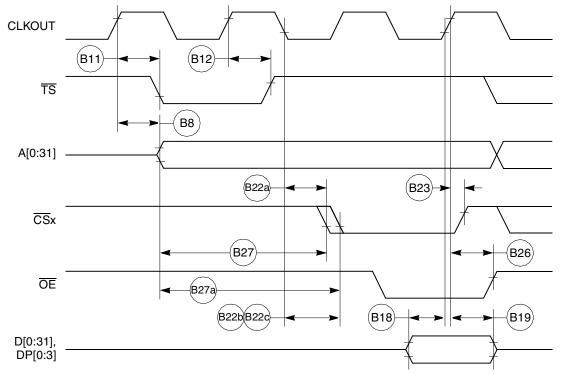

Figure 10. External Bus Read Timing (GPCM Controlled—ACS = 00)

MPC860 PowerQUICC Family Hardware Specifications, Rev. 9

Figure 11. External Bus Read Timing (GPCM Controlled—TRLX = 0, ACS = 10)

Figure 12. External Bus Read Timing (GPCM Controlled—TRLX = 0, ACS = 11)

#### **Bus Signal Timing**

Figure 13. External Bus Read Timing (GPCM Controlled—TRLX = 0 or 1, ACS = 10, ACS = 11)

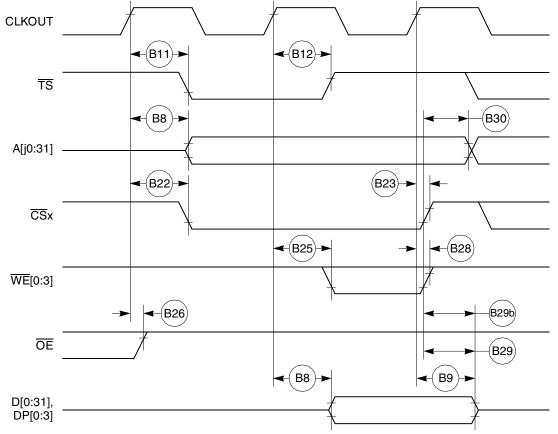

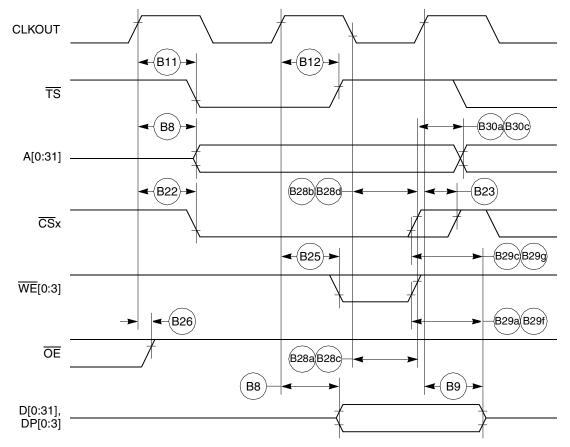

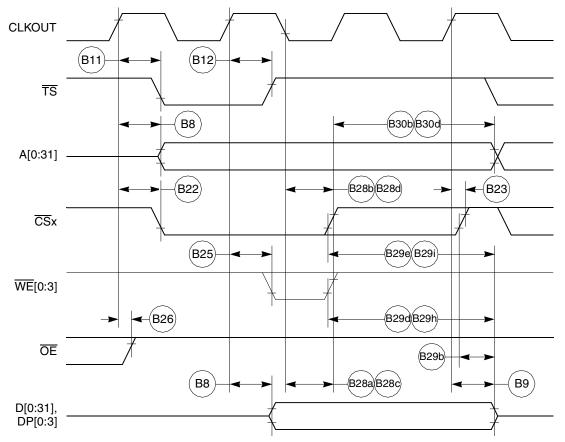

Figure 14 through Figure 16 provide the timing for the external bus write controlled by various GPCM factors.

Figure 14. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 0)

Figure 15. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 1)

Figure 16. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 1)

Figure 17 provides the timing for the external bus controlled by the UPM.

Figure 17. External Bus Timing (UPM Controlled Signals)

Figure 18 provides the timing for the asynchronous asserted UPWAIT signal controlled by the UPM.

Figure 18. Asynchronous UPWAIT Asserted Detection in UPM Handled Cycles Timing

Figure 19 provides the timing for the asynchronous negated UPWAIT signal controlled by the UPM.

Figure 19. Asynchronous UPWAIT Negated Detection in UPM Handled Cycles Timing

MPC860 PowerQUICC Family Hardware Specifications, Rev. 9 Freescale Semiconductor 31

Figure 20 provides the timing for the synchronous external master access controlled by the GPCM.

Figure 20. Synchronous External Master Access Timing (GPCM Handled ACS = 00)

Figure 21 provides the timing for the asynchronous external master memory access controlled by the GPCM.

Figure 21. Asynchronous External Master Memory Access Timing (GPCM Controlled—ACS = 00)

Figure 22 provides the timing for the asynchronous external master control signals negation.

Figure 22. Asynchronous External Master—Control Signals Negation Timing

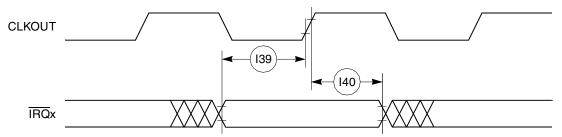

Table 8 provides interrupt timing for the MPC860.

**Table 8. Interrupt Timing**

| Num | Characteristic <sup>1</sup>                   | All Freq                  | I I m i A |      |

|-----|-----------------------------------------------|---------------------------|-----------|------|

|     | Characteristic                                | Min                       | Max       | Unit |

| 139 | IRQx valid to CLKOUT rising edge (setup time) | 6.00                      | _         | ns   |

| 140 | IRQx hold time after CLKOUT                   | 2.00                      | _         | ns   |

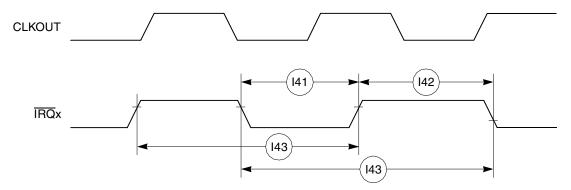

| I41 | IRQx pulse width low                          | 3.00                      | _         | ns   |

| 142 | IRQx pulse width high                         | 3.00                      | _         | ns   |

| 143 | ĪRQx edge-to-edge time                        | 4 × T <sub>CLOCKOUT</sub> | _         | _    |

The timings I39 and I40 describe the testing conditions under which the IRQ lines are tested when being defined as level-sensitive. The IRQ lines are synchronized internally and do not have to be asserted or negated with reference to the CLKOUT.

Figure 23 provides the interrupt detection timing for the external level-sensitive lines.

Figure 23. Interrupt Detection Timing for External Level Sensitive Lines

Figure 24 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 24. Interrupt Detection Timing for External Edge Sensitive Lines

The timings I41, I42, and I43 are specified to allow the correct function of the IRQ lines detection circuitry and have no direct relation with the total system interrupt latency that the MPC860 is able to support.

#### **Bus Signal Timing**

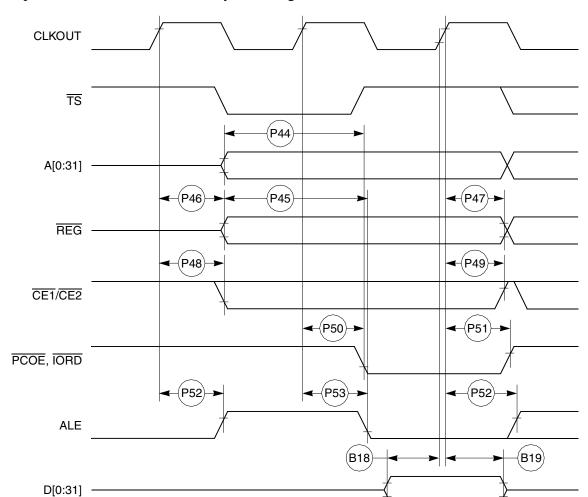

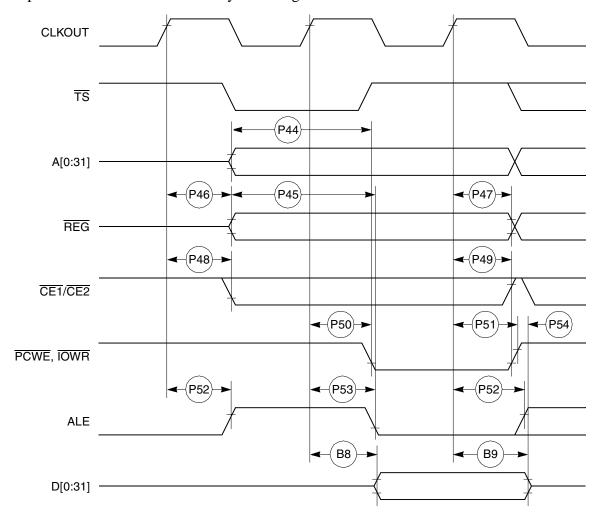

Table 9 shows the PCMCIA timing for the MPC860.

**Table 9. PCMCIA Timing**

| Num | Characteristic                                             | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit |

|-----|------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

|     |                                                            | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Jill |

| P44 | A(0:31), REG valid to PCMCIA Strobe asserted <sup>1</sup>  | 20.73  | _     | 16.75  | _     | 13.00  | _     | 9.36   | _     | ns   |

| P45 | A(0:31), REG valid to ALE negation <sup>1</sup>            | 28.30  | _     | 23.00  | _     | 18.00  | _     | 13.15  | _     | ns   |

| P46 | CLKOUT to REG valid                                        | 7.58   | 15.58 | 6.25   | 14.25 | 5.00   | 13.00 | 3.79   | 11.84 | ns   |

| P47 | CLKOUT to REG invalid                                      | 8.58   | _     | 7.25   | _     | 6.00   | _     | 4.84   | _     | ns   |

| P48 | CLKOUT to CE1, CE2 asserted                                | 7.58   | 15.58 | 6.25   | 14.25 | 5.00   | 13.00 | 3.79   | 11.84 | ns   |

| P49 | CLKOUT to CE1, CE2 negated                                 | 7.58   | 15.58 | 6.25   | 14.25 | 5.00   | 13.00 | 3.79   | 11.84 | ns   |

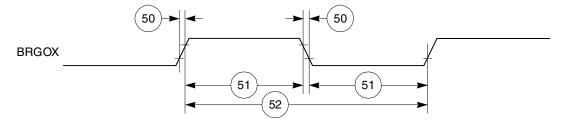

| P50 | CLKOUT to PCOE, IORD, PCWE, IOWR assert time               | _      | 11.00 |        | 11.00 | _      | 11.00 | _      | 11.00 | ns   |

| P51 | CLKOUT to PCOE, IORD, PCWE, IOWR negate time               | 2.00   | 11.00 | 2.00   | 11.00 | 2.00   | 11.00 | 2.00   | 11.00 | ns   |

| P52 | CLKOUT to ALE assert time                                  | 7.58   | 15.58 | 6.25   | 14.25 | 5.00   | 13.00 | 3.79   | 10.04 | ns   |

| P53 | CLKOUT to ALE negate time                                  | _      | 15.58 |        | 14.25 | _      | 13.00 | _      | 11.84 | ns   |

| P54 | PCWE, IOWR negated to D(0:31) invalid <sup>1</sup>         | 5.58   | _     | 4.25   | _     | 3.00   | _     | 1.79   | _     | ns   |

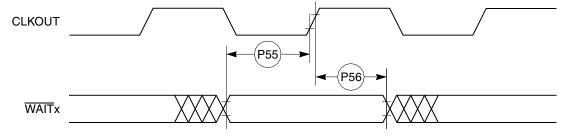

| P55 | WAITA and WAITB valid to CLKOUT rising edge <sup>1</sup>   | 8.00   | _     | 8.00   | _     | 8.00   | _     | 8.00   | _     | ns   |

| P56 | CLKOUT rising edge to WAITA and WAITB invalid <sup>1</sup> | 2.00   | _     | 2.00   | _     | 2.00   | _     | 2.00   | _     | ns   |

<sup>1</sup> PSST = 1. Otherwise add PSST times cycle time.

These synchronous timings define when the WAITx signals are detected in order to freeze (or relieve) the PCMCIA current cycle. The WAITx assertion will be effective only if it is detected 2 cycles before the PSL timer expiration. See Chapter 16, "PCMCIA Interface," in the MPC860 PowerQUICC<sup>TM</sup> Family User's Manual.

PSHT = 0. Otherwise add PSHT times cycle time.

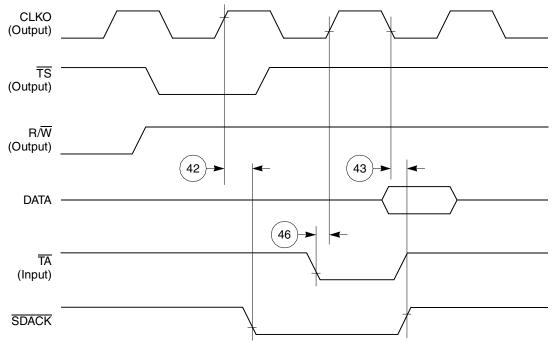

Figure 25 provides the PCMCIA access cycle timing for the external bus read.

Figure 25. PCMCIA Access Cycle Timing External Bus Read

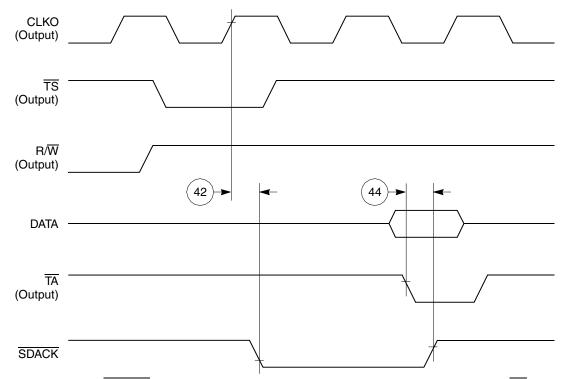

Figure 26 provides the PCMCIA access cycle timing for the external bus write.

Figure 26. PCMCIA Access Cycle Timing External Bus Write

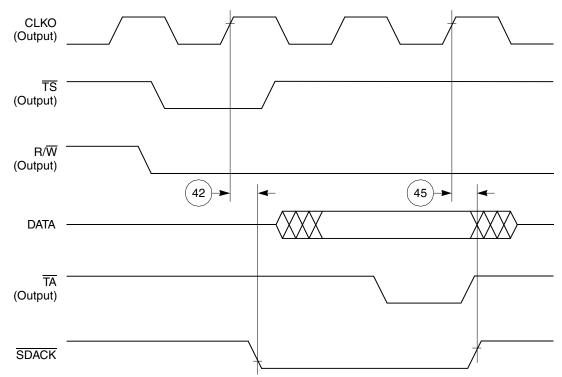

Figure 27 provides the PCMCIA WAIT signal detection timing.

Figure 27. PCMCIA WAIT Signal Detection Timing

MPC860 PowerQUICC Family Hardware Specifications, Rev. 9

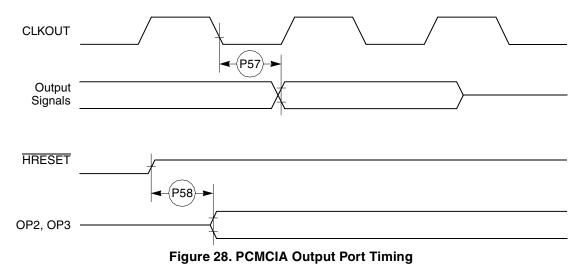

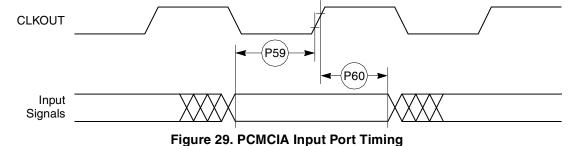

Table 10 shows the PCMCIA port timing for the MPC860.

**Table 10. PCMCIA Port Timing**

| Num | Characteristic —                         | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit  |

|-----|------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|-------|

| Num |                                          | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Offic |

| P57 | CLKOUT to OPx valid                      | _      | 19.00 | _      | 19.00 | _      | 19.00 | _      | 19.00 | ns    |

| P58 | HRESET negated to OPx drive <sup>1</sup> | 25.73  | _     | 21.75  | _     | 18.00  | _     | 14.36  | _     | ns    |

| P59 | IP_Xx valid to CLKOUT rising edge        | 5.00   | _     | 5.00   |       | 5.00   |       | 5.00   |       | ns    |

| P60 | CLKOUT rising edge to IP_Xx invalid      | 1.00   | _     | 1.00   | _     | 1.00   | _     | 1.00   | _     | ns    |

<sup>&</sup>lt;sup>1</sup> OP2 and OP3 only.

Figure 28 provides the PCMCIA output port timing for the MPC860.

Figure 29 provides the PCMCIA output port timing for the MPC860.

MPC860 PowerQUICC Family Hardware Specifications, Rev. 9

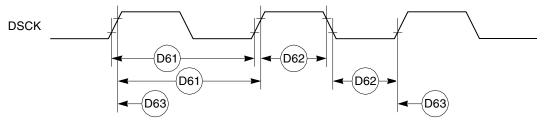

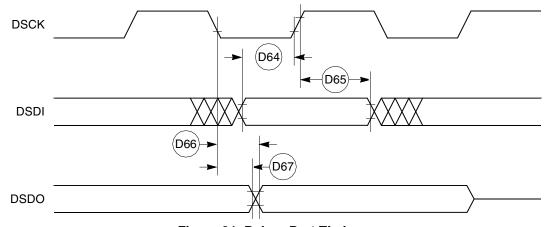

Table 11 shows the debug port timing for the MPC860.

**Table 11. Debug Port Timing**

| Num | Characteristic              | All Frequencies              |       | Unit  |

|-----|-----------------------------|------------------------------|-------|-------|

| Num | Characteristic              | Min                          | Max   | Oilit |

| P61 | DSCK cycle time             | 3 × T <sub>CLOCKOUT</sub>    | _     | _     |

| P62 | DSCK clock pulse width      | 1.25 × T <sub>CLOCKOUT</sub> | _     | _     |

| P63 | DSCK rise and fall times    | 0.00                         | 3.00  | ns    |

| P64 | DSDI input data setup time  | 8.00                         | _     | ns    |

| P65 | DSDI data hold time         | 5.00                         | _     | ns    |

| P66 | DSCK low to DSDO data valid | 0.00                         | 15.00 | ns    |

| P67 | DSCK low to DSDO invalid    | 0.00                         | 2.00  | ns    |

Figure 30 provides the input timing for the debug port clock.

Figure 30. Debug Port Clock Input Timing

Figure 31 provides the timing for the debug port.

Figure 31. Debug Port Timings

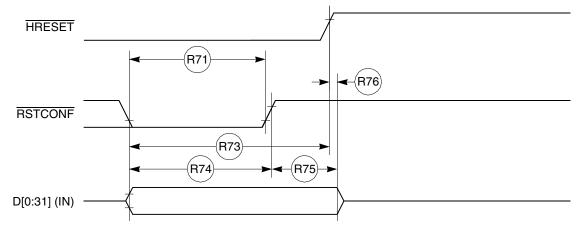

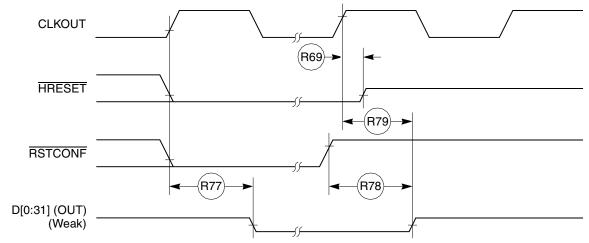

Table 12 shows the reset timing for the MPC860.

Table 12. Reset Timing

|     | Characteristic                                                                       | 33 N   | 1Hz   | 40 MHz |       | 50 N   | ИHz   | 66 MHz |       |      |

|-----|--------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

| Num |                                                                                      | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| R69 | CLKOUT to HRESET high impedance                                                      | _      | 20.00 | _      | 20.00 | _      | 20.00 | _      | 20.00 | ns   |

| R70 | CLKOUT to SRESET high impedance                                                      | _      | 20.00 | _      | 20.00 | _      | 20.00 | _      | 20.00 | ns   |

| R71 | RSTCONF pulse width                                                                  | 515.15 | _     | 425.00 |       | 340.00 | _     | 257.58 | _     | ns   |

| R72 | _                                                                                    | _      | _     | _      | _     | _      | _     | _      | _     |      |

| R73 | Configuration data to HRESET rising edge setup time                                  | 504.55 | _     | 425.00 | _     | 350.00 | _     | 277.27 | _     | ns   |

| R74 | Configuration data to RSTCONF rising edge setup time                                 | 350.00 | _     | 350.00 | _     | 350.00 | _     | 350.00 | _     | ns   |

| R75 | Configuration data hold time after RSTCONF negation                                  | 0.00   | _     | 0.00   | _     | 0.00   | _     | 0.00   | _     | ns   |

| R76 | Configuration data hold time after HRESET negation                                   | 0.00   | _     | 0.00   | _     | 0.00   | _     | 0.00   | _     | ns   |

| R77 | HRESET and RSTCONF asserted to data out drive                                        | _      | 25.00 |        | 25.00 | _      | 25.00 | _      | 25.00 | ns   |

| R78 | RSTCONF negated to data out high impedance                                           | _      | 25.00 | _      | 25.00 | _      | 25.00 | _      | 25.00 | ns   |

| R79 | CLKOUT of last rising edge before chip three-state HRESET to data out high impedance | _      | 25.00 | _      | 25.00 | _      | 25.00 | _      | 25.00 | ns   |

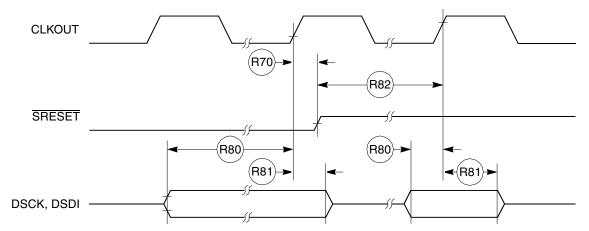

| R80 | DSDI, DSCK setup                                                                     | 90.91  | _     | 75.00  | _     | 60.00  | _     | 45.45  | _     | ns   |

| R81 | DSDI, DSCK hold time                                                                 | 0.00   | _     | 0.00   | _     | 0.00   | _     | 0.00   | _     | ns   |

| R82 | SRESET negated to CLKOUT rising edge for DSDI and DSCK sample                        | 242.42 | _     | 200.00 | _     | 160.00 | _     | 121.21 | _     | ns   |

### **Bus Signal Timing**

Figure 32 shows the reset timing for the data bus configuration.

Figure 32. Reset Timing—Configuration from Data Bus

Figure 33 provides the reset timing for the data bus weak drive during configuration.

Figure 33. Reset Timing—Data Bus Weak Drive During Configuration

Figure 34 provides the reset timing for the debug port configuration.

Figure 34. Reset Timing—Debug Port Configuration

# 10 IEEE 1149.1 Electrical Specifications

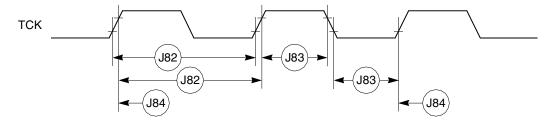

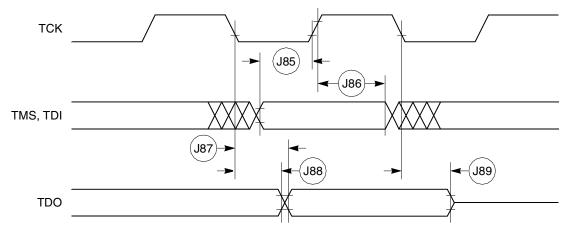

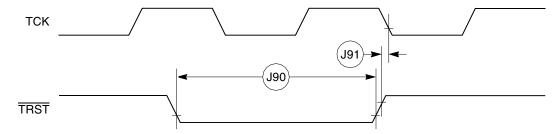

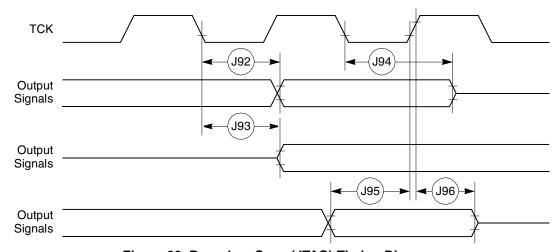

Table 13 provides the JTAG timings for the MPC860 shown in Figure 35 through Figure 38.

| Table | 13. | JTAG | Timing |

|-------|-----|------|--------|

|-------|-----|------|--------|

| Ni  | Characteristic                                         | All Frequencies |       | I I m i a |

|-----|--------------------------------------------------------|-----------------|-------|-----------|

| Num | Characteristic                                         | Min             | Max   | Unit      |

| J82 | TCK cycle time                                         | 100.00          | _     | ns        |

| J83 | TCK clock pulse width measured at 1.5 V                | 40.00           | _     | ns        |

| J84 | TCK rise and fall times                                | 0.00            | 10.00 | ns        |

| J85 | TMS, TDI data setup time                               | 5.00            | _     | ns        |

| J86 | TMS, TDI data hold time                                | 25.00           | _     | ns        |

| J87 | TCK low to TDO data valid                              | _               | 27.00 | ns        |

| J88 | TCK low to TDO data invalid                            | 0.00            | _     | ns        |

| J89 | TCK low to TDO high impedance                          | _               | 20.00 | ns        |

| J90 | TRST assert time                                       | 100.00          | _     | ns        |

| J91 | TRST setup time to TCK low                             | 40.00           | _     | ns        |

| J92 | TCK falling edge to output valid                       | _               | 50.00 | ns        |

| J93 | TCK falling edge to output valid out of high impedance | _               | 50.00 | ns        |

| J94 | TCK falling edge to output high impedance              | _               | 50.00 | ns        |

| J95 | Boundary scan input valid to TCK rising edge           | 50.00           | _     | ns        |

| J96 | TCK rising edge to boundary scan input invalid         | 50.00           | _     | ns        |

Figure 35. JTAG Test Clock Input Timing

Figure 36. JTAG Test Access Port Timing Diagram

Figure 37. JTAG TRST Timing Diagram

Figure 38. Boundary Scan (JTAG) Timing Diagram

MPC860 PowerQUICC Family Hardware Specifications, Rev. 9

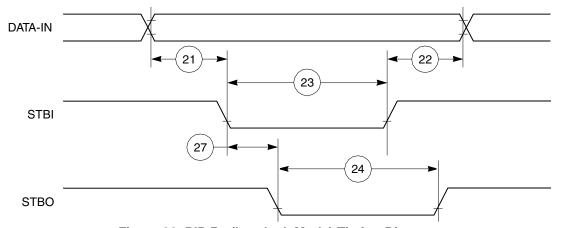

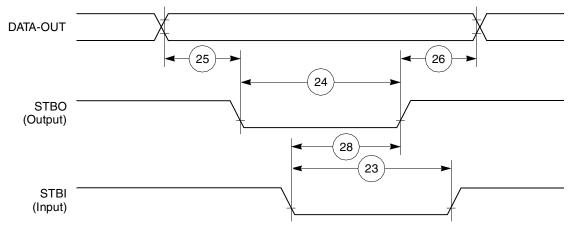

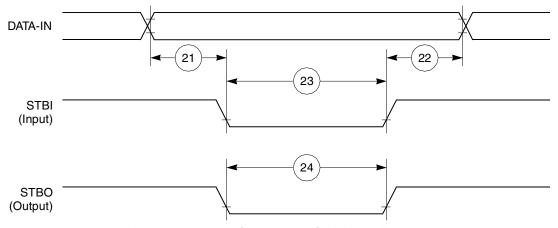

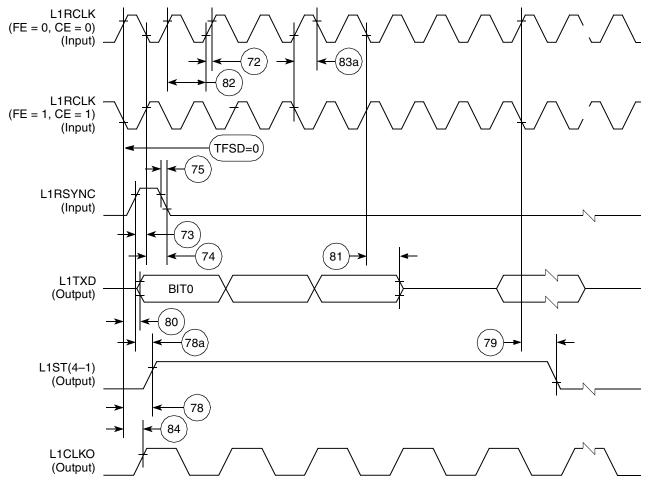

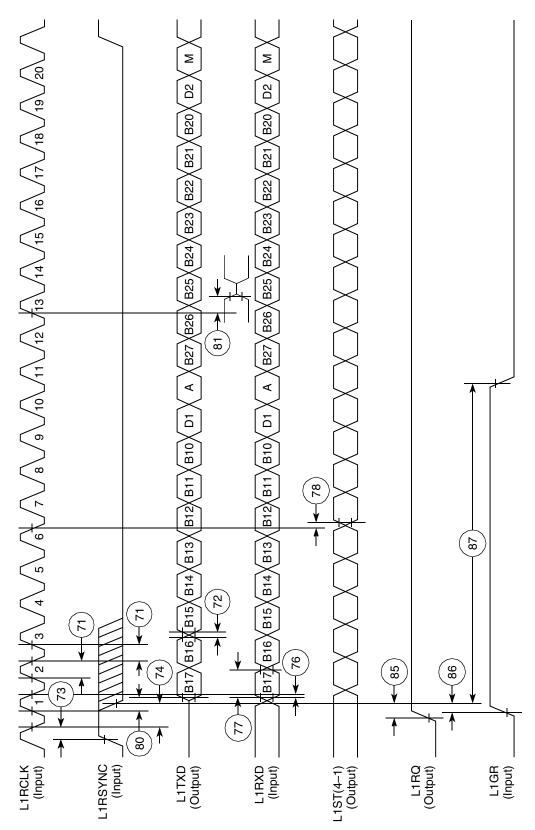

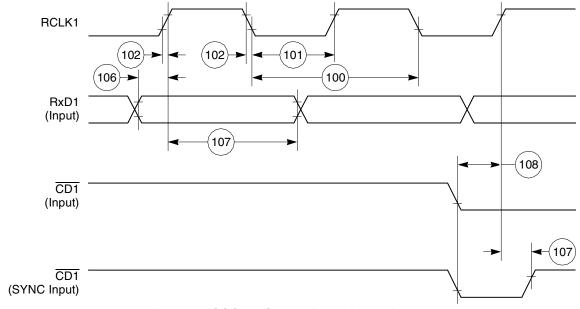

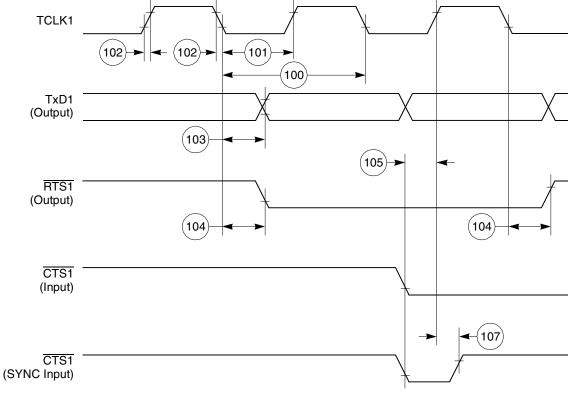

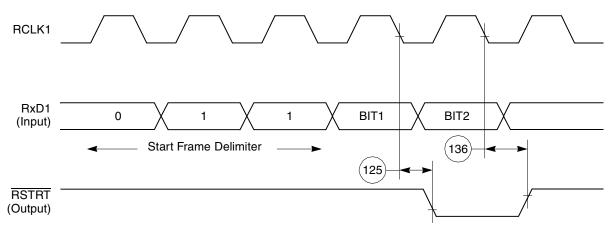

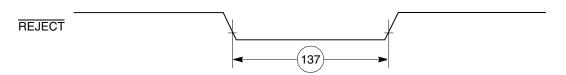

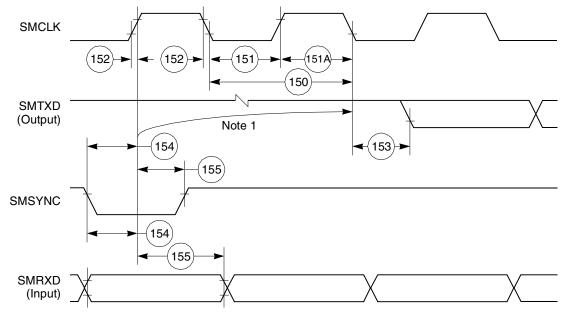

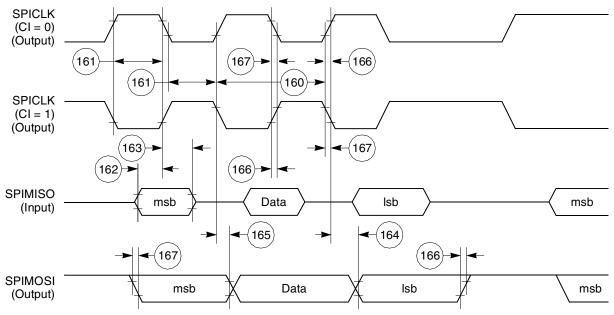

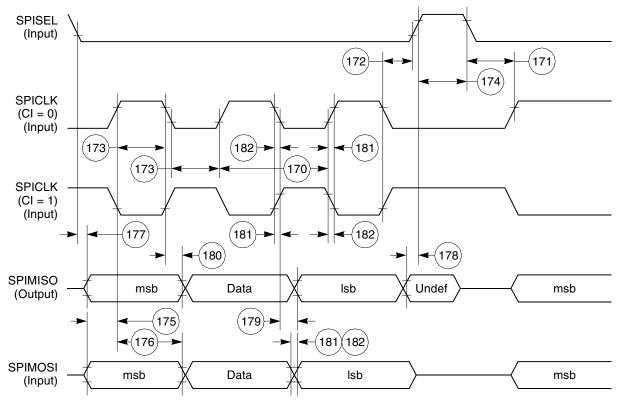

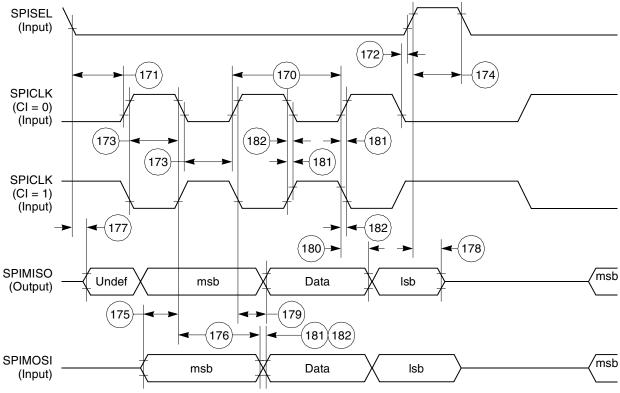

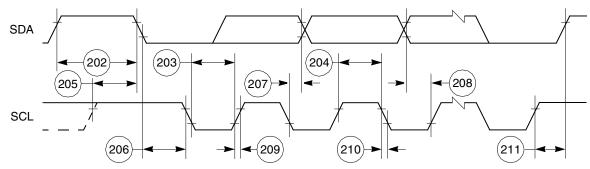

### 11 CPM Electrical Characteristics

This section provides the AC and DC electrical specifications for the communications processor module (CPM) of the MPC860.

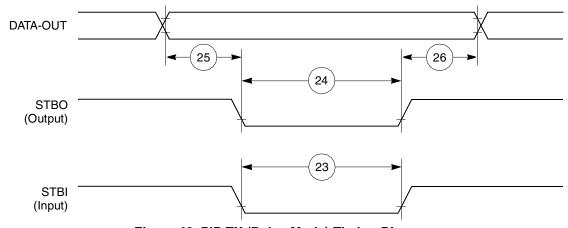

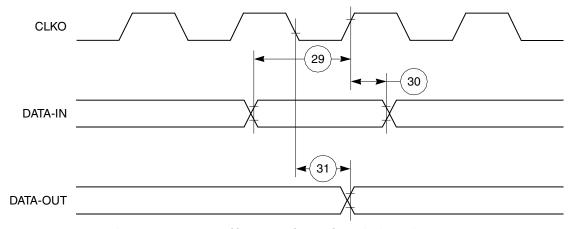

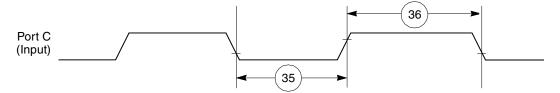

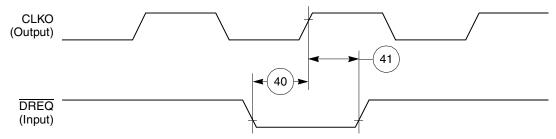

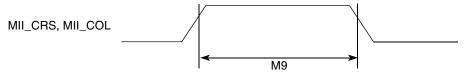

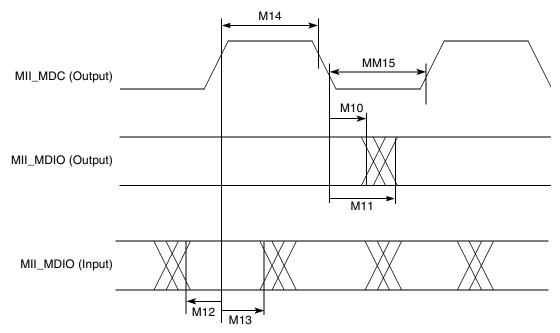

### 11.1 PIP/PIO AC Electrical Specifications