# Freescale Semiconductor Data Sheet

Document Number: MSC8144

Rev. 16, 5/2010

## **MSC8144**

## **Quad Core Digital Signal Processor**

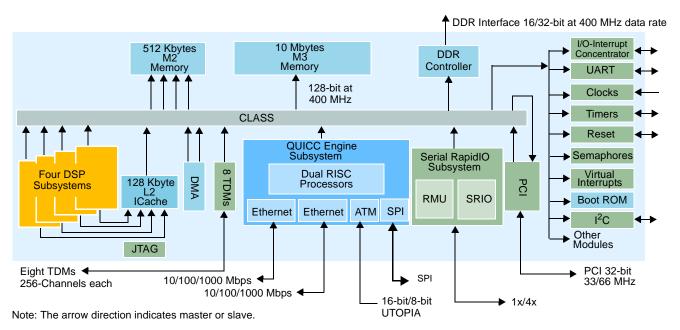

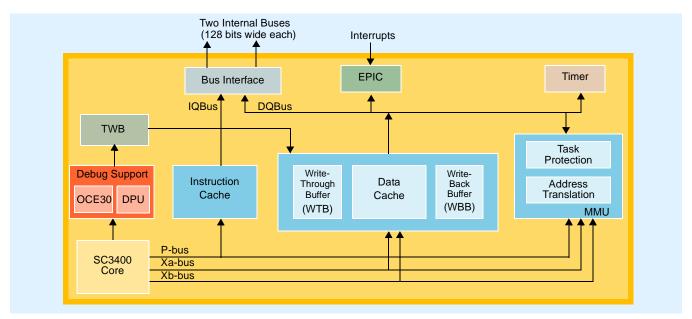

- Four StarCore<sup>®</sup> SC3400 DSP subsystems, each with an SC3400 DSP core, 16 Kbyte L1 instruction cache, 32 Kbyte L1 data cache, memory management unit (MMU), extended programmable interrupt controller (EPIC), two general-purpose 32-bit timers, debug and profiling support, and low-power Wait and Stop processing modes.

- Chip-level arbitration and system (CLASS) that provides full fabric non-blocking arbitration between the processing elements and other initiators and the M2 memory, DDR SRAM controller, device configuration control and status registers, and other targets.

- 128 Kbyte L2 shared instruction cache.

- 512 Kbyte M2 memory for critical data and temporary data buffering.

- 10 Mbyte 128-bit wide M3 memory.

- 96 Kbyte boot ROM.

- Three input clocks (shared, global, and differential).

- Four PLLs (system, core, global, and serial RapidIO).

- DDR controller with up to a 200 MHz clock (400 MHz data rate), 16/32 bit data bus, supporting up to 1 Gbyte in up to two banks and support for DDR1 and DDR2.

- DMA controller with 16 bidirectional channels with up to 1024 buffer descriptors, and programmable priority, buffer, and multiplexing configuration.

- Up to eight independent TDM modules with programmable word size (2, 4, 8, or 16-bit), hardware-base A-law/μ-law conversion, up to 128 Mbps data rate for all channels, with glueless interface to E1 or T1 framers, and can interface with H-MVIP/H.110 devices, TSI, and codecs such as AC-97.

- QUICC Engine<sup>TM</sup> technology subsystem with dual RISC processors, 48 Kbyte multi-master RAM, 48 Kbyte instruction RAM, supporting three communication controllers with one ATM and two Gigabit Ethernet interfaces, to offload scheduling tasks from the DSP cores.

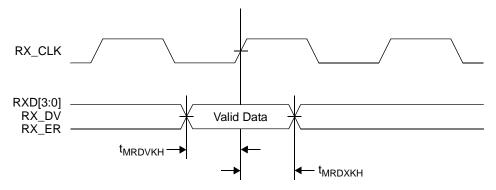

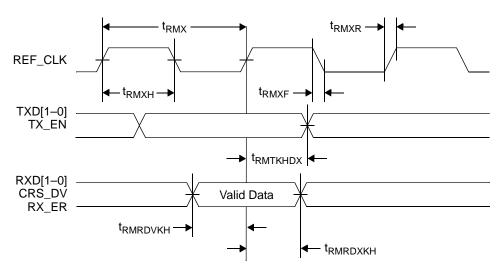

- The two Ethernet controllers support 10/100/1000 Mbps operations via MII/RMII/SMII/RGMII/SGMII and the SGMII protocol using a 4-pin SerDes interface at 1000 Mbps data rate only.

- The ATM controller supports UTOPIA level II 8/16 bits at 25/50 MHz in UTOPIA/POS mode with adaptation layer support AAL0, AAL2, and AAL5.

- PCI designed to comply with the PCI specification revision 2.2 at 33 MHz or 66 MHz with access to all PCI address spaces.

- Serial RapidIO® 1x/4x endpoint corresponds to Specification 1.2

of the RapidIO trade association, and supports read, write,

messages, doorbells, and maintenance accesses in inbound mode,

and messages and doorbells in outbound mode.

- I/O interrupt concentrator consolidates all chip maskable interrupt and non-maskable interrupt sources and routes them to <del>INT\_OUT</del>, NMI\_OUT, and the cores.

- UART that permits full-duplex operation with a bit rate of up to 6.25 Mbps.

- Serial peripheral interface (SPI).

- Four timer modules, each with four configurable 16-bit timers.

- Four software watchdog timer (SWT) modules.

- Up to 32 general-purpose input/output (GPIO) ports, 16 of which can be configured as maskable interrupt inputs.

- I<sup>2</sup>C interface that allows booting from EEPROM devices.

- Eight programmable hardware semaphores.

- Thirty two virtual maskable interrupts and one virtual NMI that can be generated by a simple write access.

- Optional booting via serial RapidIO port, PCI, I<sup>2</sup>C, SPI, or Ethernet interfaces.

**Note:** This document supports mask set M31H.

# **Table of Contents**

| 4   | Din Assignments and Depart States                                                   | Figure 42 Transmitter Output Compliance Mode                                              | 46   |

|-----|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|

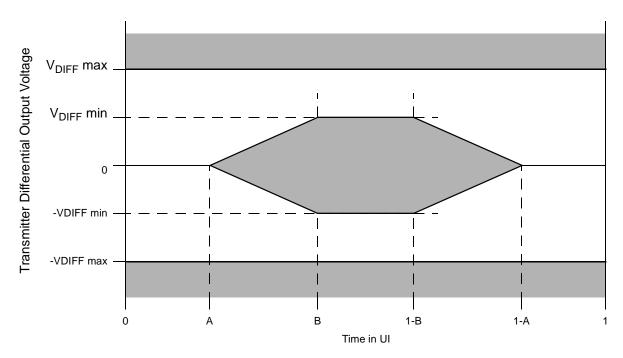

| 1   | Pin Assignments and Reset States                                                    | Figure 12.Transmitter Output Compliance Mask                                              |      |

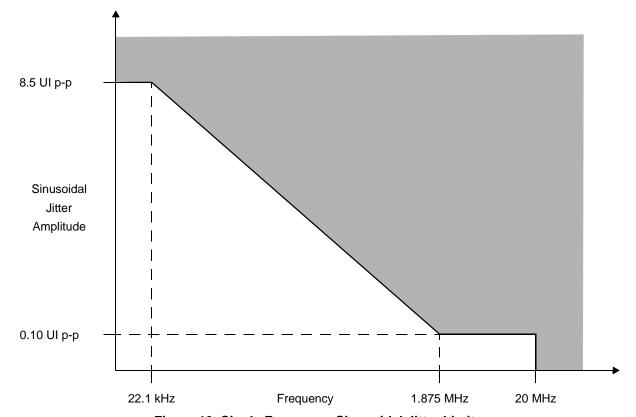

|     | 1.1 FC-PBGA Ball Layout Diagrams                                                    | Figure 13.Single Frequency Sinusoidal Jitter Limits                                       |      |

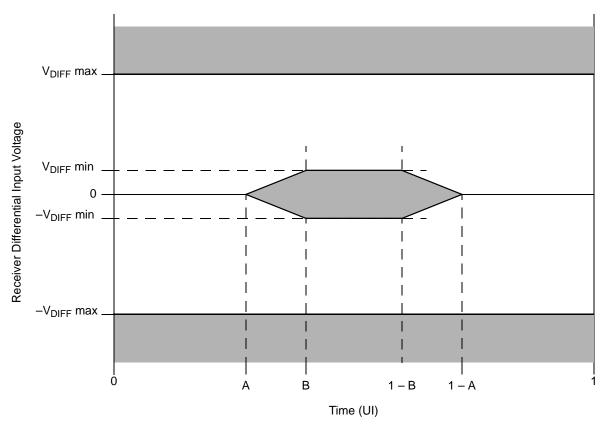

|     | 1.2 Signal List By Ball Location                                                    | Figure 14. Receiver Input Compliance Mask                                                 |      |

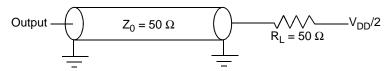

| 2   | Electrical Characteristics                                                          | Figure 15.PCI AC Test Load                                                                |      |

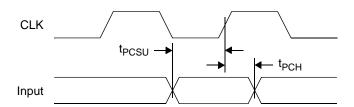

|     | 2.1 Maximum Ratings                                                                 | Figure 16.PCI Input AC Timing Measurement Conditions                                      |      |

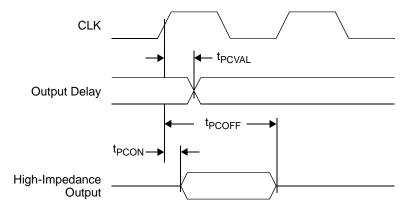

|     | 2.2 Recommended Operating Conditions27                                              | Figure 17.PCI Output AC Timing Measurement Condition                                      |      |

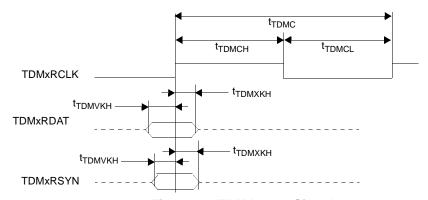

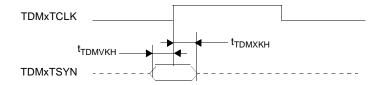

|     | 2.3 Default Output Driver Characteristics                                           | Figure 18.TDM Inputs Signals                                                              | . 52 |

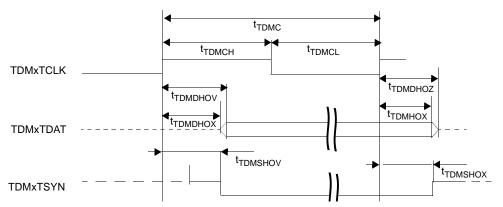

|     | 2.4 Thermal Characteristics                                                         | Figure 20.TDM Output Signals                                                              |      |

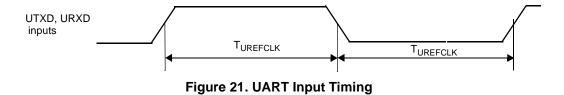

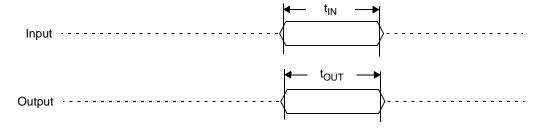

|     | 2.5 DC Electrical Characteristics                                                   | Figure 21.UART Input Timing                                                               | . 53 |

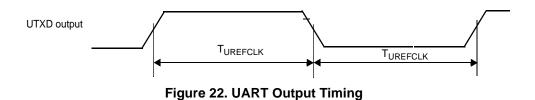

|     | 2.6 AC Timings                                                                      | Figure 22.UART Output Timing                                                              | . 53 |

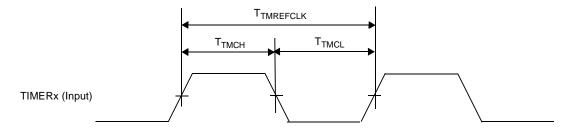

| 3   | Hardware Design Considerations64                                                    | Figure 23.Timer Timing                                                                    | . 54 |

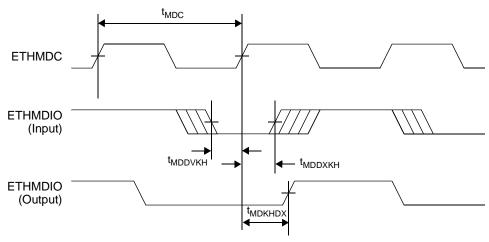

|     | 3.1 Start-up Sequencing Recommendations                                             | Figure 24.MII Management Interface Timing                                                 | . 55 |

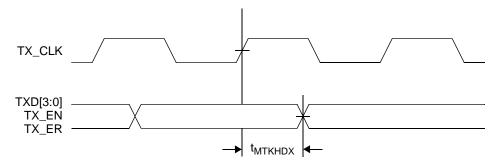

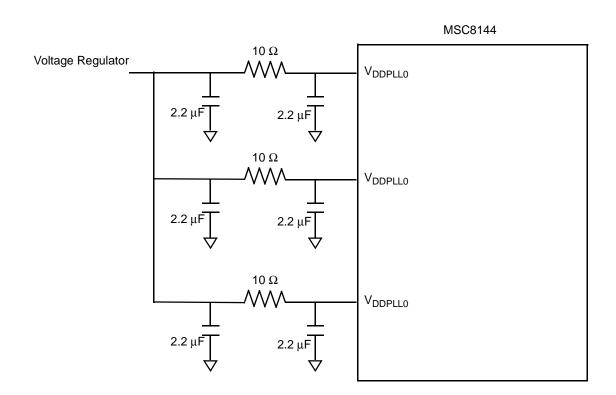

|     | 3.2 Power Supply Design Considerations66                                            | Figure 25.MII Transmit AC Timing                                                          | . 55 |

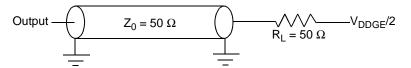

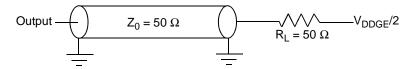

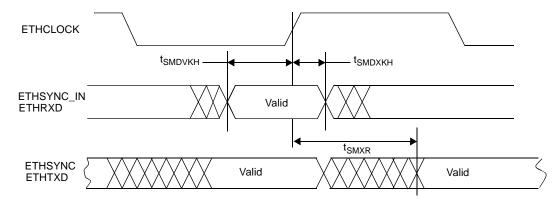

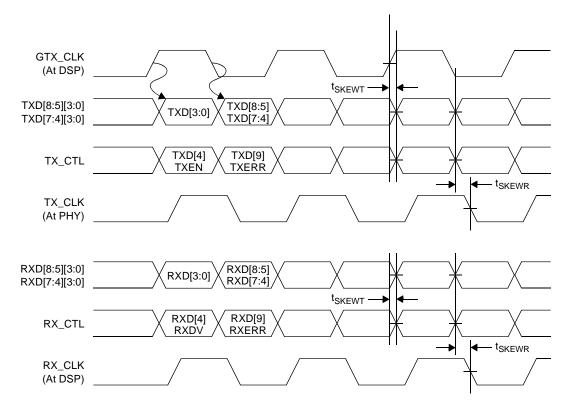

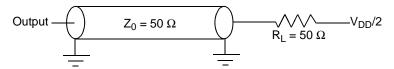

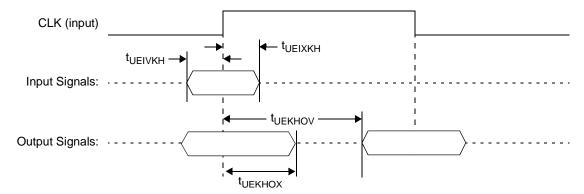

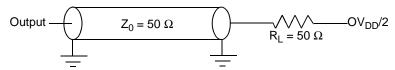

|     | 3.3 Clock and Timing Signal Board Layout Considerations 67                          | Figure 26.AC Test Load                                                                    |      |

|     | 3.4 Connectivity Guidelines                                                         | Figure 27.MII Receive AC Timing                                                           |      |

| 4   | Ordering Information                                                                | Figure 28.RMII Transmit and Receive AC Timing                                             |      |

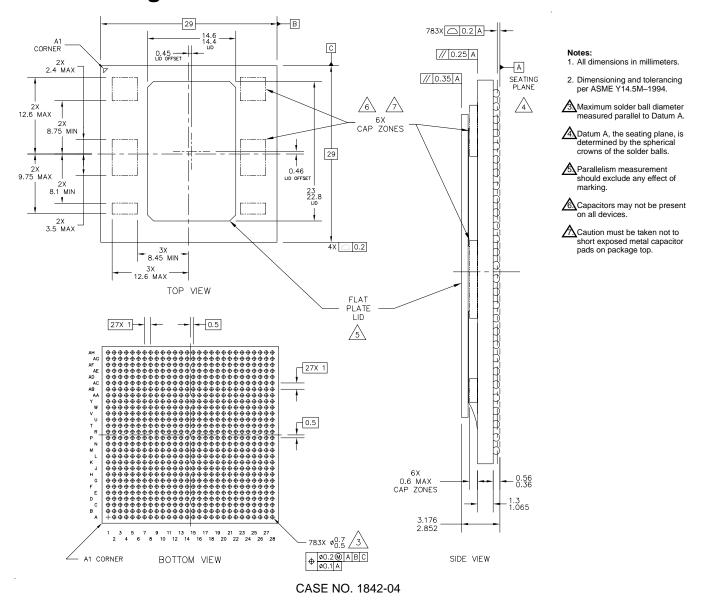

| 5   | Package Information77                                                               | Figure 29.AC Test Load                                                                    |      |

| 6   | Product Documentation                                                               | Figure 30.SMII Mode Signal Timing                                                         |      |

| 7   | Revision History                                                                    | Figure 31.RGMII AC Timing and Multiplexing                                                |      |

|     | •                                                                                   | Figure 32.ATM/UTOPIA/POS AC Test Load                                                     |      |

| Li  | st of Figures                                                                       | Figure 33.ATM/UTOPIAPOS AC Timing (External Clock)                                        |      |

| Fig | jure 1. MSC8144 Block Diagram                                                       | Figure 34.SPI AC Test Load                                                                |      |

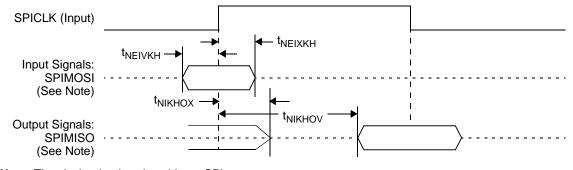

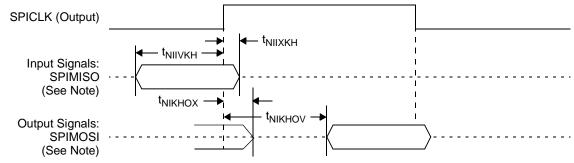

|     | jure 2. StarCore SC3400 DSP Core Subsystem Block Diagram 3                          | Figure 35.SPI AC Timing in Slave Mode (External Clock)                                    |      |

|     | jure 3. MSC8144 FC-PBGA Package, Top View 4                                         | Figure 36.SPI AC Timing in Master Mode (Internal Clock)                                   |      |

|     | jure 4. MSC8144 FC-PBGA Package, Bottom View 5                                      | Figure 37.Asynchronous Signal Timing                                                      |      |

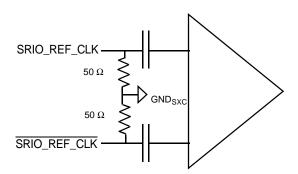

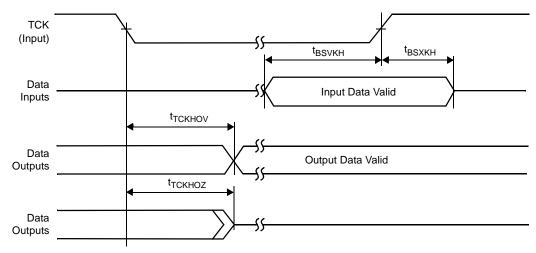

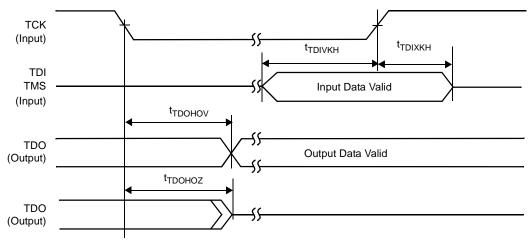

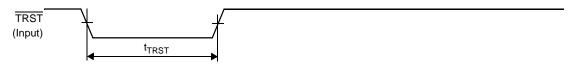

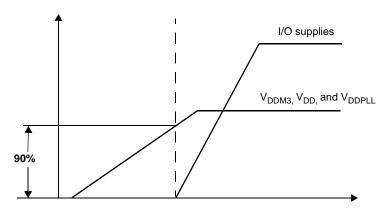

|     | jure 5. SerDes Reference Clocks Input Stage                                         | Figure 38.Test Clock Input Timing                                                         |      |

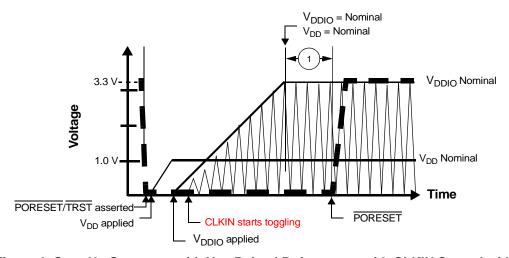

|     | pure 6. Start-Up Sequence with V <sub>DD</sub> Raised Before V <sub>DDIO</sub> with |                                                                                           |      |

|     | CLKIN Started with V <sub>DDIO</sub>                                                | Figure 39.Boundary Scan (JTAG) Timing                                                     |      |

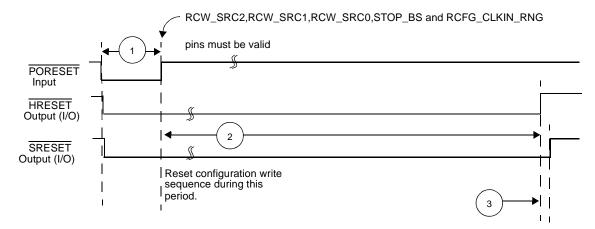

| Fic | gure 7. Timing for a Reset Configuration Write                                      | Figure 44 TRST Timing                                                                     |      |

|     | gure 8. Timing for a Reset Configuration Write                                      | Figure 41.TRST Timing                                                                     |      |

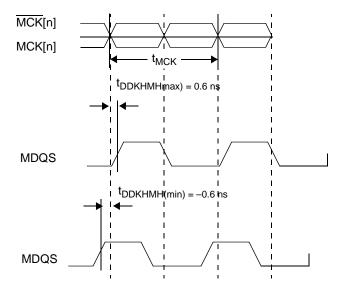

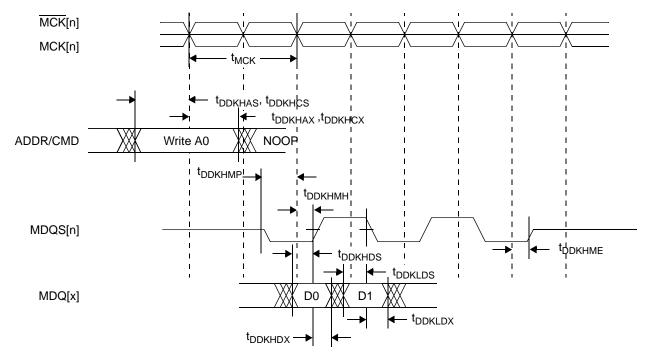

| Fig | jure 9. DDR SDRAM Output Timing                                                     | Figure 42.V <sub>DDM3</sub> , V <sub>DDM3IO</sub> and V <sub>25M3</sub> Power-on Sequence |      |

|     |                                                                                     | Figure 44.MSC8144 Mechanical Information, 783-ball FC-PBGA                                |      |

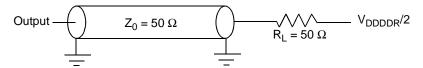

|     | gure 10.DDR AC Test Load                                                            | Package                                                                                   | . 77 |

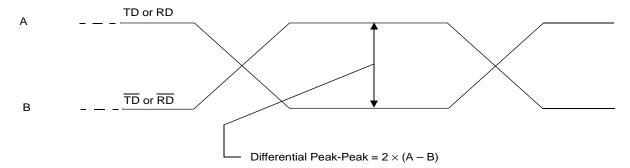

| ΗIQ | jure 11. Differential V <sub>PP</sub> of Transmitter or Receiver 42                 |                                                                                           |      |

Figure 1. MSC8144 Block Diagram

Figure 2. StarCore SC3400 DSP Core Subsystem Block Diagram

AF AG AH

# 1 Pin Assignments and Reset States

This section includes diagrams of the MSC8144 package ball grid array layouts and tables showing how the pinouts are allocated for the package.

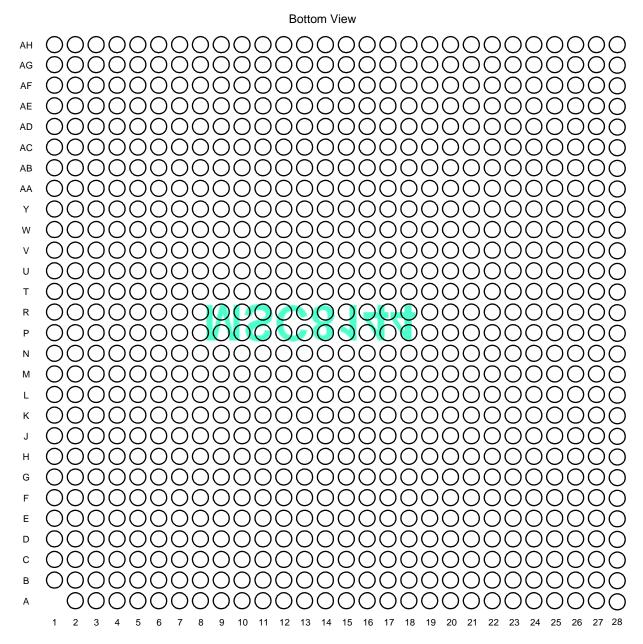

# 1.1 FC-PBGA Ball Layout Diagrams

Top and bottom views of the FC-PBGA package are shown in Figure 3 and Figure 4 with their ball location index numbers.

Top View 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 Α В С D Е F G Н J Κ L Μ Ν Р R Т U ٧ W Υ AA AB AC ΑD ΑE

Figure 3. MSC8144 FC-PBGA Package, Top View

Figure 4. MSC8144 FC-PBGA Package, Bottom View

# 1.2 Signal List By Ball Location

Table 1 presents the signal list sorted by ball number. The functionality of multi-functional (multiplexed) pins is separated for each mode. When designing a board, make sure that the reference supply for each signal is appropriately considered. The specified reference supply must be tied to the voltage level specified in this document if any of the related signal functions are used (active).

Table 1. Signal List by Ball Number

|                |                            | Power-               | abic 1. |           |           | O Multiple |            | de <sup>2</sup> |              |         |                       |

|----------------|----------------------------|----------------------|---------|-----------|-----------|------------|------------|-----------------|--------------|---------|-----------------------|

| Ball<br>Number | Signal Name                | On<br>Reset<br>Value | 0 (000) | 1 (001)   | 2 (010)   | 3 (011)    | 4 (100)    | 5 (101)         | 6 (110)      | 7 (111) | Ref.<br>Supply        |

| A2             | GND                        |                      |         |           |           |            |            |                 |              |         | GND                   |

| А3             | GE2_RX_ER/PCI_AD31         |                      |         | Ethei     | net 2     |            | PCI        |                 | Ethernet 2   |         | V <sub>DDGE2</sub>    |

| A4             | $V_{DDGE2}$                |                      |         |           |           |            |            |                 |              |         | V <sub>DDGE2</sub>    |

| A5             | GE2_RX_DV/PCI_AD30         |                      |         | Ethei     | net 2     |            | PCI        |                 | Ethernet 2   |         | V <sub>DDGE2</sub>    |

| A6             | GE2_TD0/PCI_CBE0           |                      |         | Ethei     | net 2     |            | PCI        |                 | Ethernet 2   |         | V <sub>DDGE2</sub>    |

| A7             | SRIO_IMP_CAL_RX            |                      |         |           |           |            |            |                 |              |         | V <sub>DDSXC</sub>    |

| A8             | Reserved <sup>1</sup>      |                      |         |           |           |            |            |                 |              |         | _                     |

| A9             | Reserved <sup>1</sup>      |                      |         |           |           |            |            |                 |              |         | _                     |

| A10            | Reserved <sup>1</sup>      |                      |         |           |           |            |            |                 |              |         | _                     |

| A11            | Reserved <sup>1</sup>      |                      |         |           |           |            |            |                 |              |         | _                     |

| A12            | SRIO_RXD0                  |                      |         |           |           |            |            |                 |              |         | V <sub>DDSXC</sub>    |

| A13            | V <sub>DDSXC</sub>         |                      |         |           |           |            |            |                 |              |         | V <sub>DDSXC</sub>    |

| A14            | SRIO_RXD1                  |                      |         |           |           |            |            |                 |              |         | V <sub>DDSXC</sub>    |

| A15            | $V_{\text{DDSXC}}$         |                      |         |           |           |            |            |                 |              |         | V <sub>DDSXC</sub>    |

| A16            | SRIO_REF_CLK               |                      |         |           |           |            |            |                 |              |         | V <sub>DDSXC</sub>    |

| A17            | V <sub>DDRIOPLL</sub>      |                      |         |           |           |            |            |                 |              |         | GND <sub>RIOPLL</sub> |

| A18            | GND <sub>SXC</sub>         |                      |         |           |           |            |            |                 |              |         | GND <sub>SXC</sub>    |

| A19            | SRIO_RXD2/<br>GE1_SGMII_RX |                      | SG      | MII suppo | rt on SER | DES is en  | abled by F | Reset Con       | figuration W | /ord    | V <sub>DDSXC</sub>    |

| A20            | V <sub>DDSXC</sub>         |                      |         |           |           |            |            |                 |              |         | V <sub>DDSXC</sub>    |

| A21            | SRIO_RXD3/<br>GE2_SGMII_RX |                      | SG      | MII suppo | rt on SER | DES is en  | abled by f | Reset Con       | figuration W | /ord    | V <sub>DDSXC</sub>    |

| A22            | V <sub>DDSXC</sub>         |                      |         |           |           |            |            |                 |              |         | V <sub>DDSXC</sub>    |

| A23            | SRIO_IMP_CAL_TX            |                      |         |           |           |            |            |                 |              |         | V <sub>DDSXP</sub>    |

| A24            | MDQ28                      |                      |         |           |           |            |            |                 |              |         | V <sub>DDDDR</sub>    |

| A25            | MDQ29                      |                      |         |           |           |            |            |                 |              |         | V <sub>DDDDR</sub>    |

| A26            | MDQ30                      |                      |         |           |           |            |            |                 |              |         | $V_{DDDDR}$           |

| A27            | MDQ31                      |                      |         |           |           |            |            |                 |              |         | $V_{DDDDR}$           |

| A28            | MDQS3                      |                      |         |           |           |            |            |                 |              |         | $V_{DDDDR}$           |

| B1             | Reserved <sup>1</sup>      |                      |         |           |           |            |            |                 |              |         | _                     |

| B2             | GE2_TD1/PCI_CBE1           |                      |         | Ethei     | net 2     |            | PCI        |                 | Ethernet 2   |         | V <sub>DDGE2</sub>    |

| В3             | GE2_TX_EN/PCI_CBE2         |                      |         | Ethei     | net 2     |            | PCI        |                 | Ethernet 2   |         | V <sub>DDGE2</sub>    |

| B4             | GE_MDIO                    |                      |         |           |           | Eth        | ernet      |                 |              |         | V <sub>DDGE2</sub>    |

| B5             | GND                        |                      |         |           |           |            |            |                 |              |         | GND                   |

| В6             | GE_MDC                     |                      |         |           |           | Eth        | ernet      |                 |              |         | V <sub>DDGE2</sub>    |

| B7             | GND <sub>SXC</sub>         |                      |         |           |           |            |            |                 |              |         | GND <sub>SXC</sub>    |

| B8             | Reserved <sup>1</sup>      |                      |         |           |           |            |            |                 |              |         | _                     |

| В9             | Reserved <sup>1</sup>      |                      |         |           |           |            |            |                 |              |         | _                     |

Table 1. Signal List by Ball Number (continued)

|                |                                      | Power-               |         |           | I/        | O Multipl | exing Mo   | de <sup>2</sup> |              |         |                       |

|----------------|--------------------------------------|----------------------|---------|-----------|-----------|-----------|------------|-----------------|--------------|---------|-----------------------|

| Ball<br>Number | Signal Name                          | On<br>Reset<br>Value | 0 (000) | 1 (001)   | 2 (010)   | 3 (011)   | 4 (100)    | 5 (101)         | 6 (110)      | 7 (111) | Ref.<br>Supply        |

| B10            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                     |

| B11            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                     |

| B12            | SRIO_RXD0                            |                      |         |           |           |           |            |                 |              |         | V <sub>DDSXC</sub>    |

| B13            | GND <sub>SXC</sub>                   |                      |         |           |           |           |            |                 |              |         | GND <sub>SXC</sub>    |

| B14            | SRIO_RXD1                            |                      |         |           |           |           |            |                 |              |         | V <sub>DDSXC</sub>    |

| B15            | GND <sub>SXC</sub>                   |                      |         |           |           |           |            |                 |              |         | GND <sub>SXC</sub>    |

| B16            | SRIO_REF_CLK                         |                      |         |           |           |           |            |                 |              |         | V <sub>DDSXC</sub>    |

| B17            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                     |

| B18            | V <sub>DDSXC</sub>                   |                      |         |           |           |           |            |                 |              |         | V <sub>DDSXC</sub>    |

| B19            | SRIO_RXD2/<br>GE1_SGMII_RX           |                      | SG      | MII suppo | rt on SER | DES is en | abled by I | Reset Con       | figuration V | Vord    | V <sub>DDSXC</sub>    |

| B20            | GND <sub>SXC</sub>                   |                      |         |           |           |           |            |                 |              |         | GND <sub>SXC</sub>    |

| B21            | SRIO_RXD3/<br>GE2_SGMII_RX           |                      | SG      | MII suppo | rt on SER | DES is en | abled by F | Reset Con       | figuration V | Vord    | V <sub>DDSXC</sub>    |

| B22            | GND <sub>SXC</sub>                   |                      |         |           |           |           |            |                 |              |         | GND <sub>SXC</sub>    |

| B23            | GND <sub>SXP</sub>                   |                      |         |           |           |           |            |                 |              |         | GND <sub>SXP</sub>    |

| B24            | MDQ27                                |                      |         |           |           |           |            |                 |              |         | V <sub>DDDDR</sub>    |

| B25            | $V_{DDDDR}$                          |                      |         |           |           |           |            |                 |              |         | V <sub>DDDDR</sub>    |

| B26            | GND                                  |                      |         |           |           |           |            |                 |              |         | GND                   |

| B27            | $V_{DDDDR}$                          |                      |         |           |           |           |            |                 |              |         | V <sub>DDDDR</sub>    |

| B28            | MDQS3                                |                      |         |           |           |           |            |                 |              |         | V <sub>DDDDR</sub>    |

| C1             | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                     |

| C2             | GE2_RX_CLK/PCI_AD29                  |                      |         | Ethe      | net 2     |           | PCI        |                 | Ethernet 2   | 1       | V <sub>DDGE2</sub>    |

| C3             | $V_{DDGE2}$                          |                      |         |           |           |           |            |                 |              |         | V <sub>DDGE2</sub>    |

| C4             | TDM7RSYN/GE2_TD2/<br>PCI_AD2/UTP_TER |                      | TE      | DM        |           | PCI       | •          | Ethe            | ernet 2      | UTOPIA  | V <sub>DDGE2</sub>    |

| C5             | TDM7RCLK/GE2_RD2/<br>PCI_AD0/UTP_RVL |                      | TC      | OM        |           | PCI       |            | Ethe            | ernet 2      | UTOPIA  | V <sub>DDGE2</sub>    |

| C6             | $V_{DDGE2}$                          |                      |         |           |           |           |            |                 |              |         | V <sub>DDGE2</sub>    |

| C7             | GE2_RD0/PCI_AD27                     |                      |         | Ethe      | net 2     |           | PCI        |                 | Ethernet 2   | 1       | V <sub>DDGE2</sub>    |

| C8             | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                     |

| C9             | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                     |

| C10            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                     |

| C11            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                     |

| C12            | $V_{\text{DDSXP}}$                   |                      |         |           |           |           |            |                 |              |         | $V_{DDSXP}$           |

| C13            | SRIO_TXD0                            |                      |         |           |           |           |            |                 |              |         | V <sub>DDSXP</sub>    |

| C14            | $V_{\text{DDSXP}}$                   |                      |         |           |           |           |            |                 |              |         | $V_{DDSXP}$           |

| C15            | SRIO_TXD1                            |                      |         |           |           |           |            |                 |              |         | V <sub>DDSXP</sub>    |

| C16            | GND <sub>SXC</sub>                   |                      |         |           |           |           |            |                 |              |         | GND <sub>SXC</sub>    |

| C17            | GND <sub>RIOPLL</sub>                |                      |         |           |           |           |            |                 |              |         | GND <sub>RIOPLL</sub> |

| C18            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                     |

| C19            | $V_{DDSXP}$                          |                      |         |           |           |           |            |                 |              |         | V <sub>DDSXP</sub>    |

| C20            | SRIO_TXD2/GE1_SGMII_T                |                      | SG      | MII suppo | rt on SER | DES is en | abled by I | Reset Con       | figuration V | Vord    | V <sub>DDSXP</sub>    |

Table 1. Signal List by Ball Number (continued)

|                |                                      | Power-               |         |           | I/        | O Multipl | exing Mo   | de <sup>2</sup> |              |         |                    |

|----------------|--------------------------------------|----------------------|---------|-----------|-----------|-----------|------------|-----------------|--------------|---------|--------------------|

| Ball<br>Number | Signal Name                          | On<br>Reset<br>Value | 0 (000) | 1 (001)   | 2 (010)   | 3 (011)   | 4 (100)    | 5 (101)         | 6 (110)      | 7 (111) | Ref.<br>Supply     |

| C21            | $V_{\text{DDSXP}}$                   |                      |         |           |           |           |            |                 |              |         | V <sub>DDSXP</sub> |

| C22            | SRIO_TXD3/GE2_SGMII_T                |                      | SG      | MII suppo | rt on SER | DES is en | abled by I | Reset Cor       | figuration W | /ord    | V <sub>DDSXP</sub> |

| C23            | V <sub>DDSXP</sub>                   |                      |         |           |           |           |            |                 |              |         | $V_{\rm DDSXP}$    |

| C24            | MDQ26                                |                      |         |           |           |           |            |                 |              |         | $V_{DDDDR}$        |

| C25            | MDQ25                                |                      |         |           |           |           |            |                 |              |         | $V_{DDDDR}$        |

| C26            | MDM3                                 |                      |         |           |           |           |            |                 |              |         | V <sub>DDDDR</sub> |

| C27            | GND                                  |                      |         |           |           |           |            |                 |              |         | GND                |

| C28            | MDQ24                                |                      |         |           |           |           |            |                 |              |         | $V_{DDDDR}$        |

| D1             | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                  |

| D2             | GE2_RD1/PCI_AD28                     |                      |         | Ethe      | rnet 2    |           | PCI        |                 | Ethernet 2   |         | V <sub>DDGE2</sub> |

| D3             | GND                                  |                      |         |           |           |           |            |                 |              |         | GND                |

| D4             | TDM7TDAT/GE2_TD3/<br>PCI_AD3/UTP_TMD |                      | TE      | M         |           | PCI       | •          | Ethe            | ernet 2      | UTOPIA  | V <sub>DDGE2</sub> |

| D5             | TDM7RDAT/GE2_RD3/<br>PCI_AD1/UTP_STA |                      | TE      | M         |           | PCI       |            | Ethe            | ernet 2      | UTOPIA  | V <sub>DDGE2</sub> |

| D6             | GE1_RD0/UTP_RD2/<br>PCI_CBE2         |                      | UTOPIA  | Ethe      | rnet 1    | PCI       | UTC        | DPIA            | Ethernet 1   | UTOPIA  | V <sub>DDGE1</sub> |

| D7             | TDM7TCLK/GE2_TCK/<br>PCI_IDS/UTP_RER |                      | TE      | M         |           | PCI       | ·          | Ethe            | ernet 2      | UTOPIA  | V <sub>DDGE2</sub> |

| D8             | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                  |

| D9             | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                  |

| D10            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                  |

| D11            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                  |

| D12            | GND <sub>SXP</sub>                   |                      |         |           |           |           |            |                 |              |         | GND <sub>SXP</sub> |

| D13            | SRIO_TXD0                            |                      |         |           |           |           |            |                 |              |         | $V_{DDSXP}$        |

| D14            | GND <sub>SXP</sub>                   |                      |         |           |           |           |            |                 |              |         | GND <sub>SXP</sub> |

| D15            | SRIO_TXD1                            |                      |         |           |           |           |            |                 |              |         | V <sub>DDSXP</sub> |

| D16            | V <sub>DDSXC</sub>                   |                      |         |           |           |           |            |                 |              |         | V <sub>DDSXC</sub> |

| D17            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                  |

| D18            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | _                  |

| D19            | GND <sub>SXP</sub>                   |                      |         |           |           |           |            |                 |              |         | GND <sub>SXP</sub> |

| D20            | SRIO_TXD2/GE1_SGMII_T                |                      | SG      | MII suppo | rt on SER | DES is en | abled by f | Reset Cor       | figuration W | /ord    | V <sub>DDSXP</sub> |

| D21            | GND <sub>SXP</sub>                   |                      |         |           |           |           |            |                 |              |         | GND <sub>SXP</sub> |

| D22            | SRIO_TXD3/GE2_SGMII_T                |                      | SG      | MII suppo | rt on SER | DES is en | abled by F | Reset Cor       | figuration W | /ord    | V <sub>DDSXP</sub> |

| D23            | GND <sub>SXP</sub>                   |                      |         |           |           |           |            |                 |              |         | GND <sub>SXP</sub> |

| D24            | MDQ23                                |                      |         |           |           |           |            |                 |              |         | V <sub>DDDDR</sub> |

| D25            | $V_{DDDDR}$                          |                      |         |           |           |           |            |                 |              |         | V <sub>DDDDR</sub> |

| D26            | MDQ22                                |                      |         |           |           |           |            |                 |              |         | V <sub>DDDDR</sub> |

| D27            | MDQ21                                |                      |         |           |           |           |            |                 |              |         | V <sub>DDDDR</sub> |

| D28            | MDQS2                                |                      |         |           |           |           |            |                 |              |         | V <sub>DDDDR</sub> |

| E1             | Reserved <sup>1</sup>                |                      |         |           |           |           |            |                 |              |         | —<br>DDDDK         |

Table 1. Signal List by Ball Number (continued)

|            |                                                    | Power-         | On Reset 0 (000) 1 (001) 2 (010) 3 (011) 4 (100) 5 (101) 6 (110) 7 (111) St |         |         |          |              |           |            |         |                           |

|------------|----------------------------------------------------|----------------|-----------------------------------------------------------------------------|---------|---------|----------|--------------|-----------|------------|---------|---------------------------|

| Ball       | Signal Name                                        | On             |                                                                             |         | ı,      | - munipi | CAINING IVIO | ue        | 1          |         | Ref.                      |

| Number     | Signal Name                                        | Reset<br>Value | 0 (000)                                                                     | 1 (001) | 2 (010) | 3 (011)  | 4 (100)      | 5 (101)   | 6 (110)    | 7 (111) | Supply                    |

| E2         | GE1_RX_CLK/UTP_RD6/<br>PCI_PAR                     |                | UTOPIA                                                                      | Ethe    | net 1   | PCI      | UTC          | PIA       | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub>        |

| E3         | GE1_RD2/UTP_RD4/<br>PCI_FRAME                      |                | UTOPIA                                                                      | Ethe    | net 1   | PCI      | UTC          | PIA       | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub>        |

| E4         | GE1_RD1/UTP_RD3/<br>PCI_CBE3                       |                | UTOPIA                                                                      | Ethe    | rnet 1  | PCI      | UTC          | PIA       | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub>        |

| E5         | GE1_RD3/UTP_RD5/<br>PCI_IRDY                       |                | UTOPIA                                                                      | Ethe    | rnet 1  | PCI      | UTC          | PIA       | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub>        |

| E6         | V <sub>DDGE1</sub>                                 |                |                                                                             |         |         |          |              |           |            |         | V <sub>DDGE1</sub>        |

| E7         | GE1_TX_EN/UTP_TD6/<br>PCI_CBE0                     |                | UTOPIA                                                                      | Ethe    | rnet 1  | PCI      | UTC          | PIA       | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub>        |

| E8         | Reserved <sup>1</sup>                              |                |                                                                             |         |         |          |              |           |            |         | _                         |

| E9         | Reserved <sup>1</sup>                              |                |                                                                             |         |         |          |              |           |            |         | _                         |

| E10        | GND                                                |                |                                                                             |         |         |          |              |           |            |         | GND                       |

| E11        | $V_{DD}$                                           |                |                                                                             |         |         |          |              |           |            |         | V <sub>DD</sub>           |

| E12        | GND                                                |                |                                                                             |         |         |          |              |           |            |         | GND                       |

| E13        | $V_{DD}$                                           |                |                                                                             |         |         |          |              |           |            |         | V <sub>DD</sub>           |

| E14        | GND                                                |                |                                                                             |         |         |          |              |           |            |         | GND                       |

| E15        | $V_{DD}$                                           |                |                                                                             |         |         |          |              |           |            |         | V <sub>DD</sub>           |

| E16        | GND                                                |                |                                                                             |         |         |          |              |           |            |         | GND                       |

| E17        | $V_{DD}$                                           |                |                                                                             |         |         |          |              |           |            |         | V <sub>DD</sub>           |

| E18        | GND                                                |                |                                                                             |         |         |          |              |           |            |         | GND                       |

| E19        | V <sub>DD</sub>                                    |                |                                                                             |         |         |          |              |           |            |         | V <sub>DD</sub>           |

| E20        | GND                                                |                |                                                                             |         |         |          |              |           |            |         | GND                       |

| E21        | V <sub>DD</sub>                                    |                |                                                                             |         |         |          |              |           |            |         | V <sub>DD</sub>           |

| E22        | GND                                                |                |                                                                             |         |         |          |              |           |            |         | GND                       |

| E23        |                                                    |                |                                                                             |         |         |          |              |           |            |         |                           |

| E24        | V <sub>DDDDR</sub><br>MDQ20                        |                |                                                                             |         |         |          |              |           |            |         | V <sub>DDDDR</sub>        |

| E24<br>E25 | GND                                                |                |                                                                             |         |         |          |              |           |            |         | V <sub>DDDDR</sub><br>GND |

|            |                                                    |                |                                                                             |         |         |          |              |           |            |         |                           |

| E26        | V <sub>DDDDR</sub>                                 |                |                                                                             |         |         |          |              |           |            |         | V <sub>DDDDR</sub>        |

| E27        | GND                                                |                |                                                                             |         |         |          |              |           |            |         | GND                       |

| E28        | MDQS2                                              |                |                                                                             |         |         |          |              |           |            |         | $V_{DDDDR}$               |

| F1<br>F2   | Reserved <sup>1</sup> GE1_TX_CLK/UTP_RD0/ PCI_AD31 |                | UTOPIA                                                                      | Ethe    | rnet 1  | PCI      | UTC          | )<br>PIA  | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub>        |

| F3         | V <sub>DDGE1</sub>                                 |                |                                                                             |         |         |          |              |           |            |         | V <sub>DDGE1</sub>        |

| F4         | GE1_TD3/UTP_TD5/                                   |                | UTOPIA                                                                      | Ethe    | net 1   | PCI      | LITC         | l<br>)PIA | Ethernet 1 | LITOPIA |                           |

|            | PCI_AD30                                           |                |                                                                             |         |         |          |              |           |            |         | V <sub>DDGE1</sub>        |

| F5         | GE1_TD1/UTP_TD3/<br>PCI_AD28                       |                | UTOPIA                                                                      | Ethe    | rnet 1  | PCI      | UIC          | PIA       | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub>        |

| F6         | GND                                                | 1              | ļ                                                                           |         |         |          |              |           |            |         | GND                       |

| F7         | GE1_TD0/UTP_TD2/<br>PCI_AD27                       |                | UTOPIA                                                                      | Ethe    | rnet 1  | PCI      | UTC          | PIA       | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub>        |

| F8         | V <sub>DDGE1</sub>                                 |                |                                                                             |         |         |          |              |           |            |         | $V_{DDGE1}$               |

| F9         | GND                                                |                |                                                                             |         |         |          |              |           |            |         | GND                       |

Table 1. Signal List by Ball Number (continued)

|                |                                | Power-               |         |         | V       | O Multipl | exing Mo | de <sup>2</sup> |            |         |                    |

|----------------|--------------------------------|----------------------|---------|---------|---------|-----------|----------|-----------------|------------|---------|--------------------|

| Ball<br>Number | Signal Name                    | On<br>Reset<br>Value | 0 (000) | 1 (001) | 2 (010) | 3 (011)   | 4 (100)  | 5 (101)         | 6 (110)    | 7 (111) | Ref.<br>Supply     |

| F10            | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| F11            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| F12            | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| F13            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| F14            | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| F15            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| F16            | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| F17            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| F18            | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| F19            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| F20            | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | $V_{DD}$           |

| F21            | Reserved <sup>1</sup>          |                      |         |         |         |           |          |                 |            |         | _                  |

| F22            | $V_{DDDDR}$                    |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| F23            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| F24            | MDQ19                          |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| F25            | MDQ18                          |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| F26            | MDM2                           |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| F27            | MDQ17                          |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| F28            | MDQ16                          |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| G1             | Reserved <sup>1</sup>          |                      |         |         |         |           |          |                 |            |         | —                  |

| G2             | SRESET <sup>4</sup>            |                      |         |         |         |           |          |                 |            |         | V <sub>DDIO</sub>  |

| G3             | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| G4             | PORESET <sup>4</sup>           |                      |         |         |         |           |          |                 |            |         | V <sub>DDIO</sub>  |

| G5             | GE1_COL/UTP_RD1                |                      | UTOPIA  | Ethe    | rnet 1  |           | UTOPIA   | l               | Ethernet 1 | UTOPIA  | V <sub>DDIO</sub>  |

| G6             | GE1_TD2/UTP_TD4/<br>PCI_AD29   |                      | UTOPIA  |         | rnet 1  | PCI       | 1        | PIA             | Ethernet 1 |         | V <sub>DDGE1</sub> |

| G7             | GE1_RX_DV/UTP_RD7              |                      | UTOPIA  | Ethe    | rnet 1  |           | UTOPIA   |                 | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| G8             | GE1_TX_ER/UTP_TD7/<br>PCI_CBE1 |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | PIA             | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| G9             | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| G10            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| G11            | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | $V_{DD}$           |

| G12            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| G13            | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| G14            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| G15            | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | $V_{DD}$           |

| G16            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| G17            | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | $V_{DD}$           |

| G18            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| G19            | $V_{DD}$                       |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| G20            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

| G21            | Reserved <sup>1</sup>          | _                    |         |         |         |           |          |                 |            |         | _                  |

| G22            | GND                            |                      |         |         |         |           |          |                 |            |         | GND                |

Table 1. Signal List by Ball Number (continued)

|                |                                                    | Power-               |              |               | I/      | O Multipl | exing Mo | de <sup>2</sup> |          |         |                    |

|----------------|----------------------------------------------------|----------------------|--------------|---------------|---------|-----------|----------|-----------------|----------|---------|--------------------|

| Ball<br>Number | Signal Name                                        | On<br>Reset<br>Value | 0 (000)      | 1 (001)       | 2 (010) | 3 (011)   | 4 (100)  | 5 (101)         | 6 (110)  | 7 (111) | Ref.<br>Supply     |

| G23            | MBA1                                               |                      |              |               |         |           |          |                 |          |         | V <sub>DDDDR</sub> |

| G24            | MA3                                                |                      |              |               |         |           |          |                 |          |         | V <sub>DDDDR</sub> |

| G25            | MA8                                                |                      |              |               |         |           |          |                 |          |         | V <sub>DDDDR</sub> |

| G26            | $V_{DDDDR}$                                        |                      |              |               |         |           |          |                 |          |         | $V_{DDDDR}$        |

| G27            | GND                                                |                      |              |               |         |           |          |                 |          |         | GND                |

| G28            | MCK0                                               |                      |              |               |         |           |          |                 |          |         | $V_{DDDDR}$        |

| H1             | Reserved <sup>1</sup>                              |                      |              |               |         |           |          |                 |          |         |                    |

| H2             | CLKIN                                              |                      |              |               |         |           |          |                 |          |         | $V_{DDIO}$         |

| НЗ             | HRESET                                             |                      |              |               |         |           |          |                 |          |         | $V_{DDIO}$         |

| H4             | PCI_CLK_IN                                         |                      |              |               |         |           |          |                 |          |         | $V_{DDIO}$         |

| H5             | NMI                                                |                      |              |               |         |           |          |                 |          |         | $V_{DDIO}$         |

| H6             | URXD/GPIO14/IRQ8/<br>RC_LDF <sup>3, 6</sup>        | RC_LDF               |              |               | UA      | RT/GPIO   | /IRQ     |                 |          |         | $V_{DDIO}$         |

| H7             | GE1_RX_ER/PCI_AD6/<br>GPIO25/IRQ15 <sup>3, 6</sup> |                      | GPIO/<br>IRQ | Ethernet<br>1 |         | PCI       |          | GPIO/<br>IRQ    | Ether    | net 1   | $V_{DDIO}$         |

| Н8             | GE1_CRS/PCI_AD5                                    |                      | PCI          | Ethernet<br>1 |         | Р         | CI       | l               | Ether    | net 1   | V <sub>DDIO</sub>  |

| H9             | GND                                                |                      |              |               |         |           |          |                 |          |         | GND                |

| H10            | $V_{DD}$                                           |                      |              |               |         |           |          |                 |          |         | V <sub>DD</sub>    |

| H11            | GND                                                |                      |              |               |         |           |          |                 |          |         | GND                |

| H12            | $V_{DD}$                                           |                      |              |               |         |           |          |                 |          |         | V <sub>DD</sub>    |

| H13            | GND                                                |                      |              |               |         |           |          |                 |          |         | GND                |

| H14            | $V_{DD}$                                           |                      |              |               |         |           |          |                 |          |         | V <sub>DD</sub>    |

| H15            | $V_{DD}$                                           |                      |              |               |         |           |          |                 |          |         | V <sub>DD</sub>    |

| H16            | V <sub>DD</sub>                                    |                      |              |               |         |           |          |                 |          |         | V <sub>DD</sub>    |

| H17            | GND                                                |                      |              |               |         |           |          |                 |          |         | GND                |

| H18            | $V_{DD}$                                           |                      |              |               |         |           |          |                 |          |         | V <sub>DD</sub>    |

| H19            | GND                                                |                      |              |               |         |           |          |                 |          |         | GND                |

| H20            | $V_{DD}$                                           |                      |              |               |         |           |          |                 |          |         | $V_{DD}$           |

| H21            | $V_{DD}$                                           |                      |              |               |         |           |          |                 |          |         | V <sub>DD</sub>    |

| H22            | V <sub>DDDDR</sub>                                 |                      |              |               |         |           |          |                 |          |         | V <sub>DDDDR</sub> |

| H23            | MBA0                                               |                      |              |               |         |           |          |                 |          |         | V <sub>DDDDR</sub> |

| H24            | MA15                                               |                      |              |               |         |           |          |                 |          |         | V <sub>DDDDR</sub> |

| H25            | $V_{DDDDR}$                                        |                      |              |               |         |           |          |                 |          |         | V <sub>DDDDR</sub> |

| H26            | MA9                                                |                      |              |               |         |           |          | 1               |          |         | V <sub>DDDDR</sub> |

| H27            | MA7                                                |                      |              |               |         |           |          |                 |          |         | V <sub>DDDDR</sub> |

| H28            | MCK0                                               |                      |              |               |         |           |          |                 |          |         | V <sub>DDDDR</sub> |

| J1             | Reserved <sup>1</sup>                              |                      |              |               |         |           |          |                 |          |         | — DDDDK            |

| J2             | GND                                                |                      |              |               |         |           |          |                 |          |         | GND                |

| J3             | V <sub>DDIO</sub>                                  |                      |              |               |         |           |          |                 |          |         | V <sub>DDIO</sub>  |

| J4             | STOP_BS                                            |                      |              |               |         |           |          |                 |          |         | V <sub>DDIO</sub>  |

| J5             | NMI_OUT <sup>4</sup>                               |                      |              |               |         |           |          |                 |          |         | V <sub>DDIO</sub>  |

| J6             | INT_OUT <sup>4</sup>                               |                      |              |               |         |           |          |                 |          |         | V <sub>DDIO</sub>  |

| J7             | SDA/GPIO27 <sup>3, 4, 6</sup>                      |                      |              | ı             | i       | I2C/GPI0  | )        | 1               | <u> </u> |         | V <sub>DDIO</sub>  |

Table 1. Signal List by Ball Number (continued)

|                |                       | Power-               | On      |         |         |         |         |         |         |         |                      |

|----------------|-----------------------|----------------------|---------|---------|---------|---------|---------|---------|---------|---------|----------------------|

| Ball<br>Number | Signal Name           | On<br>Reset<br>Value | 0 (000) | 1 (001) | 2 (010) | 3 (011) | 4 (100) | 5 (101) | 6 (110) | 7 (111) | Ref.<br>Supply       |

| J8             | $V_{DDIO}$            |                      |         |         |         |         |         |         |         |         | V <sub>DDIO</sub>    |

| J9             | $V_{DD}$              |                      |         |         |         |         |         |         |         |         | V <sub>DD</sub>      |

| J10            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J11            | $V_{DD}$              |                      |         |         |         |         |         |         |         |         | $V_{DD}$             |

| J12            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J13            | $V_{DD}$              |                      |         |         |         |         |         |         |         |         | V <sub>DD</sub>      |

| J14            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J15            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J16            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J17            | $V_{DD}$              |                      |         |         |         |         |         |         |         |         | $V_{DD}$             |

| J18            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J19            | $V_{DD}$              |                      |         |         |         |         |         |         |         |         | $V_{DD}$             |

| J20            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J21            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J22            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J23            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J24            | V <sub>DDDDR</sub>    |                      |         |         |         |         |         |         |         |         | V <sub>DDDDR</sub>   |

| J25            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J26            | V <sub>DDDDR</sub>    |                      |         |         |         |         |         |         |         |         | V <sub>DDDDR</sub>   |

| J27            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| J28            | $V_{DDDDR}$           |                      |         |         |         |         |         |         |         |         | V <sub>DDDDR</sub>   |

| K1             | Reserved <sup>1</sup> |                      |         |         |         |         |         |         |         |         | - DDDDK              |

| K2             | Reserved <sup>1</sup> |                      |         |         |         |         |         |         |         |         | _                    |

| K3             | Reserved <sup>1</sup> |                      |         |         |         |         |         |         |         |         | _                    |

| K4             | Reserved <sup>1</sup> |                      |         |         |         |         |         |         |         |         | _                    |

| K5             | V <sub>DDPLL2A</sub>  |                      |         |         |         |         |         |         |         |         | V <sub>DDPLL2A</sub> |

| K6             | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| K7             | V <sub>DDPLL0A</sub>  |                      |         |         |         |         |         |         |         |         | V <sub>DDPLL0A</sub> |

| K8             | V <sub>DDPLL1A</sub>  |                      |         |         |         |         |         |         |         |         | V <sub>DDPLL1A</sub> |

| K9             | V <sub>DD</sub>       |                      |         |         |         |         |         |         |         |         | V <sub>DD</sub>      |

| K10            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| K11            | V <sub>DD</sub>       |                      |         |         |         |         |         |         |         |         | V <sub>DD</sub>      |

| K12            | GND                   |                      |         |         |         |         |         |         |         |         | GND                  |

| K13            | V <sub>DD</sub>       |                      |         |         |         |         |         |         |         |         | V <sub>DD</sub>      |

| K14            | V <sub>DD</sub>       |                      |         |         |         |         |         |         |         |         | V <sub>DD</sub>      |

| K15            |                       |                      |         |         |         |         |         |         |         |         |                      |

| K16            | V <sub>DD</sub>       |                      |         |         |         |         |         |         |         |         | V <sub>DD</sub>      |

|                | V <sub>DD</sub>       |                      | -       |         |         |         |         | 1       |         |         | V <sub>DD</sub>      |

| K17            | V <sub>DD</sub>       |                      | -       |         |         |         |         | -       |         |         | V <sub>DD</sub>      |

| K18            | GND                   |                      | -       |         |         |         |         |         |         |         | GND                  |

| K19            | V <sub>DD</sub>       |                      | 1       |         |         |         |         | 1       |         |         | V <sub>DD</sub>      |

| K20            | GND                   |                      | 1       |         |         |         |         | -       |         |         | GND                  |

| K21            | V <sub>DD</sub>       |                      | -       |         |         |         |         | 1       |         |         | V <sub>DD</sub>      |

| K22            | $V_{DDDDR}$           |                      | ]       |         |         |         |         | 1       |         |         | $V_{DDDDR}$          |

Table 1. Signal List by Ball Number (continued)

|                |                                                  | Power-               | on      |         |              |                   |          |                   |            |         |                   |

|----------------|--------------------------------------------------|----------------------|---------|---------|--------------|-------------------|----------|-------------------|------------|---------|-------------------|

| Ball<br>Number | Signal Name                                      | On<br>Reset<br>Value | 0 (000) | 1 (001) | 2 (010)      | 3 (011)           | 4 (100)  | 5 (101)           | 6 (110)    | 7 (111) | Ref.<br>Supply    |

| K23            | MBA2                                             |                      |         |         |              |                   |          |                   |            |         | $V_{DDDDR}$       |

| K24            | MA10                                             |                      |         |         |              |                   |          |                   |            |         | $V_{DDDDR}$       |

| K25            | MA12                                             |                      |         |         |              |                   |          |                   |            |         | $V_{DDDDR}$       |

| K26            | MA14                                             |                      |         |         |              |                   |          |                   |            |         | $V_{DDDDR}$       |

| K27            | MA4                                              |                      |         |         |              |                   |          |                   |            |         | $V_{DDDDR}$       |

| K28            | $MV_{REF}$                                       |                      |         |         |              |                   |          |                   |            |         | $V_{DDDDR}$       |

| L1             | Reserved <sup>1</sup>                            |                      |         |         |              |                   |          |                   |            |         | _                 |

| L2             | CLKOUT                                           |                      |         |         |              |                   |          |                   |            |         | $V_{DDIO}$        |

| L3             | TMR1/UTP_IR/PCI_CBE3/<br>GPIO17 <sup>3, 6</sup>  |                      | UTC     | OPIA    | TMR/<br>GPIO | UTOPIA            | PCI      |                   | UTOPIA     |         | $V_{DDIO}$        |

| L4             | TMR4/PCI_PAR/GPIO20 <sup>3,</sup><br>6/ UTP_REOP |                      |         | TIMER   | R/GPIO       |                   | PCI      | 7                 | TIMER/GPIO |         |                   |

| L5             | GND                                              |                      |         |         |              |                   |          |                   |            |         | GND               |

| L6             | TMR2/PCI_FRAME/<br>GPIO18 <sup>3, 6</sup>        |                      |         | TIMER   | R/GPIO       |                   | PCI      | TIMER/GPIO UTOPIA |            |         | $V_{DDIO}$        |

| L7             | SCL/GPIO26 <sup>3, 4, 6</sup>                    |                      |         |         |              | I <sup>2</sup> C/ | GPIO     | •                 |            | ,       | $V_{DDIO}$        |

| L8             | UTXD/GPIO15/IRQ9 <sup>3, 6</sup>                 |                      |         |         |              | UART/0            | GPIO/IRQ | )                 |            |         | V <sub>DDIO</sub> |

| L9             | GND                                              |                      |         |         |              |                   |          | *                 |            | GND     |                   |