### Advance Information

MPC8240RXXPNS Rev. 0, 11/2003

MPC8240 Part Number Specification for the XPC8240RXXnnnx Series

Part

Numbers Affected:

This document describes part-number-specific changes to recommended operating conditions and revised electrical specifications, as applicable, from those described in the general *MPC8240 Integrated Processor Hardware Specifications* (Order No. MPC8240EC).

*XPC8240RZU250E XPC8240RVV250E*

Specifications provided in this document supersede those in the *MPC8240 Integrated Processor Hardware Specifications*, Revision 1.0 or later, for the part numbers listed in Table A only. Specifications not addressed herein are unchanged. Because this document is frequently updated, refer to http://www.freescale.com or to a local Freescale sales office for the latest version.

Note that headings and table numbers in this document are not consecutively numbered. They correspond to the heading or table affected in the general hardware specification.

The part numbers addressed in this document are listed in Table A. For more detailed ordering information, see Section 1.9, "Ordering Information."

Table A. Part Number Addressed by This Data Sheet

| м                                | Оре              | rating Conditions | S                   | Significant Differences from                       |  |

|----------------------------------|------------------|-------------------|---------------------|----------------------------------------------------|--|

| Part Number                      | CPU<br>Frequency |                   | T <sub>J</sub> (°C) | Hardware Specification                             |  |

| XPC8240RVV250x<br>XPC8240RZU250x | 250 MHz          | 2.625 ±125 mV     | 0 to 105            | Modified voltage specifications to achieve 250 MHz |  |

**Note:** The X prefix in a Freescale part number designates a "Pilot Production Prototype" as defined by Freescale SOP 3-13. These are part of a limited production volume of prototypes manufactured, tested, and Q.A.-inspected on qualified technology to simulate normal production. These parts have only preliminary reliability and characterization data. Before pilot production prototypes may be shipped, written authorization from the customer must be on file in the applicable sales office acknowledging the qualification status and the fact that product changes may still occur while shipping pilot production prototypes.

## 1.2 Features

This section summarizes changes to the features of the MPC8240 described in the MPC8240 Integrated Processor Hardware Specifications.

Power management

— 2.625-V processor core

## 1.3 General Parameters

This section summarizes changes to the general parameters of the MPC8240 described in the MPC8240 Integrated Processor Hardware Specifications.

• Core power supply 2.625 V ±125 mV DC nominal

## 1.4.1. DC Electrical Characteristics

Table 2 provides the recommended operating conditions for the MPC8240 part numbers described herein.

**Table 2. Recommended Operating Conditions**

| Cha                        | racteristic                             | Symbol           | Recommended<br>Value | Unit  | Notes |

|----------------------------|-----------------------------------------|------------------|----------------------|-------|-------|

| Supply voltage             | V <sub>DD</sub>                         | 2.625 ±5%        | V                    | 4, 6  |       |

| Supply voltage for PCI and | d standard bus standards                | OV <sub>DD</sub> | 3.3 ±0.3             | V     | 6     |

| Supply voltages for memo   | GV <sub>DD</sub>                        | 3.3 ±5%          | V                    | 8     |       |

| PLL supply voltage—CPU     | AV <sub>DD</sub>                        | 2.625 ±5%        | V                    | 4, 6  |       |

| PLL supply voltage—perip   | AV <sub>DD</sub> 2                      | 2.6255 ±5%       | V                    | 4, 7  |       |

| DLL supply voltage         | LAV <sub>DD</sub>                       | 2.625 ±5%        | V                    | 4, 7  |       |

| PCI reference              | LV <sub>DD</sub>                        | 5.0 ±5%          | V                    | 9, 10 |       |

|                            |                                         |                  | 3.3 ±0.3             | V     | 9, 10 |

| Input voltage              | LV <sub>DD</sub> input-tolerant signals | V <sub>in</sub>  | 0 to 3.6 or 5.75     | V     | 2, 3  |

|                            | All other inputs                        |                  | 0 to 3.6             | V     | 5     |

**General Parameters**

**Table 2. Recommended Operating Conditions (continued)**

| Characteristic           | Symbol         | Recommended<br>Value | Unit | Notes |

|--------------------------|----------------|----------------------|------|-------|

| Die-junction temperature | T <sub>j</sub> | 0 to 105             | °C   |       |

#### Notes:

- These are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

- 2. These signals are designed to withstand  $LV_{DD}$  + 0.5 V DC when  $LV_{DD}$  is connected to a 3.3- or 5.0-V DC power supply.

- 3. LV<sub>DD</sub> input tolerant signals: PCI interface, EPIC control, and OSC\_IN signals.

- 4. See Section 1.9, "Ordering Information," for details on a modified voltage (V<sub>DD</sub>) version device.

#### Cautions

- 5. Input voltage (V<sub>in</sub>) must not be greater than the supply voltage (V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>2/LAV<sub>DD</sub>) by more than 2.5 V at all times, including during power-on reset.

- 6.  $OV_{DD}$  must not exceed  $V_{DD}/AV_{DD}/AV_{DD}/AV_{DD}$  by more than 1.8 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 7.  $V_{DD}/AV_{DD}/AV_{DD}/AV_{DD}$  must not exceed  $OV_{DD}$  by more than 0.6 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 8. GV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub>/AV<sub>DD</sub>D/AV<sub>DD</sub> by more than 1.8 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 9.  $LV_{DD}$  must not exceed  $V_{DD}/AV_{DD}/AV_{DD}/AV_{DD}$  by more than 5.4 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 10.LV<sub>DD</sub> must not exceed OV<sub>DD</sub> by more than 3.6 V at any time, including during power-on reset. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

### 1.4.1.5 Power Characteristics

Table 5 provides power consumption data for the MPC8240. Power consumption on the PLL supply pins ( $AV_{DD}$  and  $AV_{DD}$ 2) and the DLL supply pin (LAVDD) less than 15 mW. This parameter is guaranteed by design and is not tested.

**Table 5. Preliminary Power Consumption**

| Mode                     | PCI Bus Clock/Memory Bus Clock<br>CPU Clock Frequency (MHz) |           |            |            |            |            | Unit  | Notes   |

|--------------------------|-------------------------------------------------------------|-----------|------------|------------|------------|------------|-------|---------|

|                          | 33/66/233                                                   | 33/83/250 | 33/100/200 | 33/100/250 | 66/100/200 | 66/100/250 |       |         |

| Typical                  | 3.4                                                         | 3.6       | 3.2        | 3.7        | 3.2        | 3.8        | W     | 1, 5    |

| Maximum—FP               | 3.8                                                         | 4.1       | 3.6        | 4.2        | 3.6        | 4.3        | W     | 1, 2    |

| Maximum—INT              | 3.4                                                         | 3.7       | 3.3        | 3.8        | 3.4        | 3.8        | W     | 1, 3    |

| Doze                     | 2.2                                                         | 2.4       | 2.2        | 2.6        | 2.2        | 2.6        | W     | 1, 4, 6 |

| Nap                      | 700                                                         | 800       | 900        | 900        | 900        | 900        | mW    | 1, 4, 6 |

| Sleep                    | 500                                                         | 500       | 500        | 500        | 800        | 800        | mW    | 1, 4, 6 |

| I/O Power Supplies       |                                                             |           |            |            |            |            |       |         |

| Mode Minimum             |                                                             |           |            | Maximum    |            | Unit       | Notes |         |

| Typical—OV <sub>DD</sub> | 200                                                         |           |            |            | 600        |            | mW    | 7, 8    |

Table 5. Preliminary Power Consumption (continued)

| Mode                     | PCI Bus Clock/Memory Bus Clock<br>CPU Clock Frequency (MHz) |           |            |            |            | Unit       | Notes |      |

|--------------------------|-------------------------------------------------------------|-----------|------------|------------|------------|------------|-------|------|

|                          | 33/66/233                                                   | 33/83/250 | 33/100/200 | 33/100/250 | 66/100/200 | 66/100/250 |       |      |

| Typical—GV <sub>DD</sub> | 300                                                         |           |            | 900        |            |            | mW    | 7, 9 |

#### Notes:

- The values include V<sub>DD</sub>, AV<sub>DD</sub>, AV<sub>DD</sub>, and LAV<sub>DD</sub> but do not include I/O supply power; see Section 1.7.2, "Power Supply Sizing," in the MPC8240 Integrated Processor Hardware Specifications for information on OV<sub>DD</sub> and GV<sub>DD</sub> supply power. One DIMM is used for memory loading.

- Maximum—FP power is measured at V<sub>DD</sub> = 2.625 V with dynamic power management enabled while running an entirely cache-resident, looping, floating point multiplication instruction.

- 3. Maximum—INT power is measured at V<sub>DD</sub> = 2.625 V with dynamic power management enabled while running entirely cache-resident, looping, integer instructions.

- 4. Power saving mode maximums are measured at  $V_{DD} = 2.625 \text{ V}$  while the device is in doze, nap, or sleep mode.

- 5. Typical power is measured at V<sub>DD</sub> = AV<sub>DD</sub> = 2.625 V, OV<sub>DD</sub> = 3.3 V where a nominal FP value, a nominal INT value, and a value where there is a continuous flush of cache lines with alternating ones and zeros on 64-bit boundaries to local memory are averaged.

- 6. Power saving mode data measured with only two PCI\_CLKs and two SDRAM\_CLKs enabled.

- 7. The typical minimum I/O power values were results of the MPC8240 performing cache resident integer operations at the slowest frequency combination of 33:66:166 (PCI:Mem:CPU) MHz.

- The typical maximum OV<sub>DD</sub> value resulted from the MPC8240 operating at the fastest frequency combination of 66:100:250 (PCI:Mem:CPU) MHz and performing continuous flushes of cache lines with alternating ones and zeros to PCI memory.

- The typical maximum GV<sub>DD</sub> value resulted from the MPC8240 operating at the fastest frequency combination of 66:100:250 (PCI:Mem:CPU) MHz and performing continuous flushes of cache lines with alternating ones and zeros on 64-bit boundaries to local memory.

# 1.5 PLL Configurations

The MPC8240 internal PLLs are configured by the PLL\_CFG[0:4] signals. For a given PCI\_SYNC\_IN (PCI bus) frequency, the PLL configuration signals set both the peripheral logic/memory bus PLL (VCO) frequency of operation for the PCI-to-memory frequency multiplying and the MPC603e CPU PLL (VCO) frequency of operation for memory-to-CPU frequency multiplying. The PLL configurations for the MPC8240 is shown in Table 18.

Table 18. MPC8240 Microprocessor PLL Configurations

|             |                                   |                               |                                                 | 250-MHz Part <sup>8, 9</sup>                        |                             | Ratio                                 | os <sup>3, 4</sup>                    |

|-------------|-----------------------------------|-------------------------------|-------------------------------------------------|-----------------------------------------------------|-----------------------------|---------------------------------------|---------------------------------------|

| Ref.<br>No. | PLL_<br>CFG<br>[0:4] <sup>2</sup> | CPU <sup>1</sup><br>HID1[0:4] | PCI Clock Input<br>(PCI_SYNC_IN)<br>Range (MHz) | Peripheral<br>Logic/Mem<br>Bus Clock Range<br>(MHz) | CPU Clock<br>Range<br>(MHz) | PCI to Mem<br>(Mem VCO)<br>Multiplier | Mem to CPU<br>(CPU VCO)<br>Multiplier |

| 0           | 00000                             | 00110                         | 25–33                                           | 75–100                                              | 188–250                     | 3 (6)                                 | 2.5 (5)                               |

| 1           | 00001                             | 11000                         | 25–27                                           | 75–83                                               | 225–250                     | 3 (6)                                 | 3 (6)                                 |

| 2           | 00010                             | 00101                         | 101 50–56 <sup>5</sup> 50–56                    |                                                     | 100–112                     | 1 (4)                                 | 2 (8)                                 |

| 3           | 00011                             | 00101                         |                                                 | Bypass                                              |                             | Bypass                                | 2 (8)                                 |

| 4           | 00100                             | 00101                         | 25–28 <sup>5</sup>                              | 50–56                                               | 100–113                     | 2 (8)                                 | 2 (8)                                 |

**Ordering Information**

Table 18. MPC8240 Microprocessor PLL Configurations (continued)

|             |                                   |       | CPU <sup>1</sup> HID1[0:4] PCI Clock Input (PCI_SYNC_IN) Range (MHz) Peripheral Logic/Mem Bus Clock Range (MHz) CPU Clock Range (MHz) |            | Ratio   | os <sup>3, 4</sup>                    |                                       |

|-------------|-----------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------|------------|---------|---------------------------------------|---------------------------------------|

| Ref.<br>No. | PLL_<br>CFG<br>[0:4] <sup>2</sup> |       |                                                                                                                                       |            | Range   | PCI to Mem<br>(Mem VCO)<br>Multiplier | Mem to CPU<br>(CPU VCO)<br>Multiplier |

| 5           | 00101                             | 00110 |                                                                                                                                       | Bypass     |         | Bypass                                | 2.5 (5)                               |

| 7           | 00111                             | 11000 |                                                                                                                                       | Bypass     |         | Bypass                                | 3 (6)                                 |

| 8           | 01000                             | 11000 | 33 <sup>6</sup> –56 <sup>5</sup>                                                                                                      | 33–56      | 100–168 | 1 (4)                                 | 3 (6)                                 |

| Α           | 01010                             | 00111 | 25–27                                                                                                                                 | 50–55      | 225–250 | 2 (4)                                 | 4.5 (9)                               |

| С           | 01100                             | 00110 | 25–50                                                                                                                                 | 50–100     | 125–250 | 2 (4)                                 | 2.5 (5)                               |

| Е           | 01110                             | 11000 | 25–41                                                                                                                                 | 50–83      | 150–250 | 2 (4)                                 | 3 (6)                                 |

| 10          | 10000                             | 00100 | 25–33                                                                                                                                 | 75–100     | 150–200 | 3 (6)                                 | 2 (4)                                 |

| 12          | 10010                             | 00100 | 33–66                                                                                                                                 | 50–100     | 100–200 | 1.5 (3)                               | 2 (4)                                 |

| 14          | 10100                             | 11110 | 25–35                                                                                                                                 | 50–71      | 175–250 | 2 (4)                                 | 3.5 (7)                               |

| 16          | 10110                             | 11010 | 25–31                                                                                                                                 | 50–62      | 200–250 | 2 (4)                                 | 4 (8)                                 |

| 18          | 11000                             | 11000 | 25–33                                                                                                                                 | 62–83      | 186–250 | 2.5 (5)                               | 3 (6)                                 |

| 1A          | 11010                             | 11010 | 50 <sup>7</sup> –62                                                                                                                   | 50–62      | 200–250 | 1 (2)                                 | 4 (8)                                 |

| 1C          | 11100                             | 11000 | 33 <sup>7</sup> –55                                                                                                                   | 50-83      | 150–250 | 1.5 (3)                               | 3 (6)                                 |

| 1D          | 11101                             | 00110 | 33 <sup>7</sup> –66                                                                                                                   | 50–100     | 125–250 | 1.5 (3)                               | 2.5 (5)                               |

| 1E          | 11110                             | 01111 |                                                                                                                                       | Not usable |         | Off                                   | Off                                   |

| 1F          | 11111                             | 11111 |                                                                                                                                       | NOT USADIE | Off     | Off                                   |                                       |

#### Notes:

- 1. The processor HID1 values only represent the multiplier of the processor's PLL (memory-to-processor multiplier); thus, multiple MPC8240 PLL\_CFG[0:4] values may have the same processor HID1 value. This implies that system software cannot read the HID1 register and associate it with a unique PLL\_CFG[0:4] value.

- 2. PLL\_CFG[0:4] settings not listed (00110, 01001, 01011, 01101, 01111, 10001, 10011, 10101, 10111, 11001, and 11011) are reserved.

- 3. In PLL bypass mode, the PCI\_SYNC\_IN input signal clocks the internal processor directly, the peripheral logic PLL is disabled, and the bus mode is set for 1:1 (PCI:Mem) mode operation. This mode is intended for hardware modeling support. The AC timing specifications given in this document do not apply in PLL bypass mode.

- 4. In clock-off mode, no clocking occurs inside the MPC8240 regardless of the PCI\_SYNC\_IN input.

- 5. Limited due to maximum memory VCO = 225 MHz.

- 6. Limited due to minimum CPU VCO = 200 MHz.

- 7. Limited due to minimum memory VCO = 100 MHz.

- 8. For clarity, range values are shown rounded down to the nearest whole number (decimal place accuracy removed).

- 9. Note that the 250-MHz part is available only in the XPC8240RZUnnnx number series.

# 1.9 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 1.9.1, "Part Numbers Fully Addressed by This Document."

**Document Revision History**

#### Part Numbers Fully Addressed by This Document 1.9.1

Table 19 provides the Freescale part numbering nomenclature for the MPC8240. Note that the individual part numbers correspond to the maximum processor core frequency. For available frequencies, contact a local Freescale sales office. Each part number also contains a revision code that refers to the die mask revision number. The revision level can be determined by reading the Revision ID register at address offset 0x08.

**Table 19. Freescale Part Numbering Nomenclature**

| XPC          | nnnn            | X                                | XX                                   | nnn                    | X                             |

|--------------|-----------------|----------------------------------|--------------------------------------|------------------------|-------------------------------|

| Product Code | Part Identifier | Process Descriptor               | Package                              | Processor<br>Frequency | Revision Level                |

| XPC          | 8240            | R=2.625 V ±125 mV<br>0° to 105°C | ZU = TBGA<br>V V = Lead free<br>TBGA | 250                    | E: 1.3;<br>Revision ID = 0x13 |

# 1.9.2 Part Marking

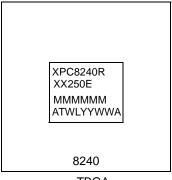

Parts are marked as in the example shown in Figure 28.

Notes:

**TBGA**

MMMMMM is the 6-digit mask number. ATWLYYWWA is the traceability code.

Figure 28. Freescale Part Marking for TBGA Device

# **Document Revision History**

Table B provides a revision history for this part number specification.

**Table B. Document Revision History**

| Revision Number | Substantive Change(s)                                                  |

|-----------------|------------------------------------------------------------------------|

| 0               | Initial release. Note that this document supercedes the MPC8245RZUPNS. |

**Document Revision History**

THIS PAGE INTENTIONALLY LEFT BLANK

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Microprocessors - MPU category:

Click to view products by Freescale manufacturer:

Other Similar products are found below:

MC68302EH20C MC7457RX1000LC MC7457RX1267LC MC7457VG1267LC A2C00010998 A A2C52004004 R5F117BCGNA#20 R5F52106BDLA#U0 R5S72690W266BG#U0 ADJ3400IAA5DOE MPC8245TVV266D MPC8245TZU300D MPC8260ACVVMHBB MPC8323ECVRAFDCA MPC8323VRADDCA MPC8536ECVJAVLA BOXNUC5PGYH0AJ 20-668-0024 P1010NSN5DFB P2010NSN2MHC P2020NXE2HHC P5020NSE7QMB P5020NSE7TNB P5020NSE7VNB LS1020ASN7KQB LS1020AXN7HNB LS1020AXN7KQB A2C00010729 A A2C00039344 T1022NSE7MQB T1022NXN7PQB T1023NSE7MQA T1024NXE7PQA T1042NSE7MQB T1042NSN7MQB T1042NXN7WQB T2080NSE8TTB T2080NSN8PTB T2080NXE8TTB T2081NXN8TTB R5F101AFASP#V0 MC68302CEH20C TS68040MF33A MPC8260ACVVMIBB MPC8280CZUUPEA MPC8313ECVRAFFC MPC8313ECVRAGDC MPC8313EVRADDC MPC8313EVRADDC