Shanghai Fudan Microelectronics Group Company Limited

# FM24C32D 2-Wire Serial EEPROM

With Unique ID and Security Sector

**Data Sheet**

Mar. 2017

INFORMATION IN THIS DOCUMENT IS INTENDED AS A REFERENCE TO ASSIST OUR CUSTOMERS IN THE SELECTION OF SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCT BEST SUITED TO THE CUSTOMER'S APPLICATION; THEY DO NOT CONVEY ANY LICENSE UNDER ANY INTELLECTUAL PROPERTY RIGHTS, OR ANY OTHER RIGHTS, BELONGING TO SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD OR A THIRD PARTY.

WHEN USING THE INFORMATION CONTAINED IN THIS DOCUMENTS, PLEASE BE SURE TO EVALUATE ALL INFORMATION AS A TOTAL SYSTEM BEFORE MAKING A FINAL DECISION ON THE APPLICABILITY OF THE INFORMATION AND PRODUCTS. PURCHASERS ARE SOLELY RESPONSIBLE FOR THE CHOICE, SELECTION AND USE OF THE SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCTS AND SERVICES DESCRIBED HEREIN, AND SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD ASSUMES NO LIABILITY WHATSOEVER RELATING TO THE CHOICE, SELECTION OR USE OF THE SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD ASSUMES NO LIABILITY WHATSOEVER RELATING TO THE CHOICE, SELECTION OR USE OF THE SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCTS AND SERVICES DESCRIBED HEREIN. UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE.

FUTURE ROUTINE REVISIONS WILL OCCUR WHEN APPROPRIATE, WITHOUT NOTICE. CONTACT SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD SALES OFFICE TO OBTAIN THE LATEST SPECIFICATIONS AND BEFORE PLACING YOUR PRODUCT ORDER. PLEASE ALSO PAY ATTENTION TO INFORMATION PUBLISHED BY SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD BY VARIOUS MEANS, INCLUDING SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD HOME PAGE (HTTP://WWW.FMSH.COM/).

PLEASE CONTACT SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD LOCAL SALES OFFICE FOR THE SPECIFICATION REGARDING THE INFORMATION IN THIS DOCUMENT OR SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCTS.

#### Trademarks

Shanghai Fudan Microelectronics Group Co., Ltd name and logo, the "复旦" logo are trademarks or registered trademarks of Shanghai Fudan Microelectronics Group Co., Ltd or its subsidiaries in China.

Shanghai Fudan Microelectronics Group Co., Ltd, Printed in the China, All Rights Reserved.

上海复旦微电子集团股份有限公司

迷 复旦微电子

## Description

The FM24C32D provides 32,768 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 4,096 words of 8 bits each, with 128-bit UID and 32-byte Security Sector. The device's cascadable feature allows up to 8 devices to share a common 2-wire bus. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operations are essential.

### Features

- Low Operation Voltage: V<sub>CC</sub> = 1.7V to 5.5V

- Internally Organized: 4,096 x 8

- 2-wire Serial Interface

- Schmitt Trigger, Filtered Inputs for Noise Suppression

- Bi-directional Data Transfer Protocol

- 1MHz (2.5V~5.5V) and 400 kHz (1.7V) Compatibility

- Write Protect Pin for Hardware Data Protection

- 32-Byte Page Write Modes (Partial Page Writes are Allowed)

- Lockable 32-Byte Security Sector

- 128-Bit Unique ID for each device

- Self-timed Write Cycle (5 ms max)

- High-reliability

- Endurance: 1,000,000 Write Cycles

- Data Retention: 40 Years

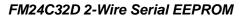

- PDIP8 (RoHS Compliant)

- SOP8, TSSOP8, TDFN8, TSOT23-5L, and Thin 4-ball WLCSP Packages (RoHS Compliant and Halogen-free)

## **Absolute Maximum Ratings**

| Operating Temperature<br>(Plastic Package) | -55 ℃ to +125 ℃ |

|--------------------------------------------|-----------------|

| Operating Temperature<br>(Module Package)  | -20 ℃ to +60 ℃  |

| Storage Temperature<br>(Plastic Package)   | -65 ℃ to +150 ℃ |

| Storage Temperature<br>(Module Package)    | -25 ℃ to +70 ℃  |

| Voltage on Any Pin with Respect to Ground  | -1.0V to +7.0V  |

| Maximum Operating Voltage                  | 6.25V           |

| DC Output Current                          | 5.0 mA          |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

上海复旦微电子集团股份有限公司

## Packaging Type

义 复旦微电子

| Pin Name        | Function                 |

|-----------------|--------------------------|

| A0~A2           | Device Address Inputs    |

| SDA             | Serial Data Input/Output |

| SCL             | Serial Clock Input       |

| WP              | Write Protect            |

| V <sub>CC</sub> | Power Supply             |

| GND             | Ground                   |

| NC              | Not Connect              |

Shanghai Fudan Microelectronics Group Company Limited

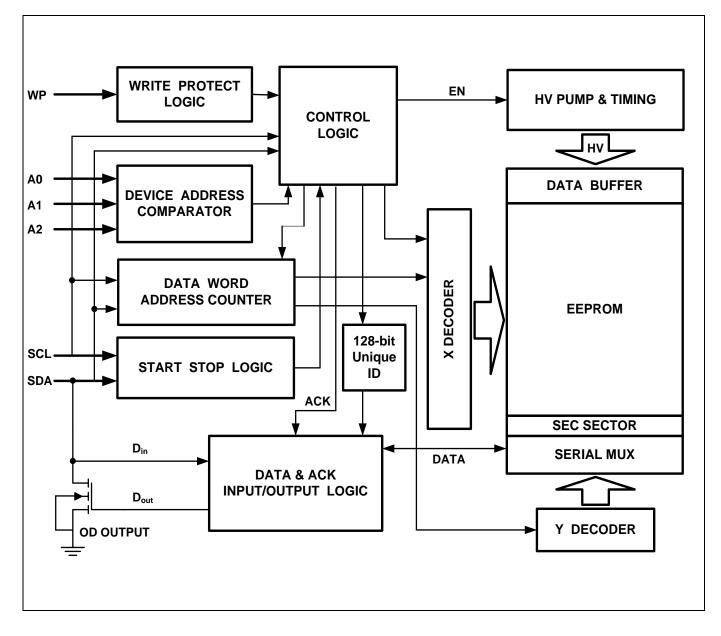

### Figure 1. Block Diagram

**》**复旦微电子

## Pin Description

**SERIAL CLOCK (SCL):** The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.

**SERIAL DATA (SDA):** The SDA pin is bi-directional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.

**DEVICE ADDRESSES (A2, A1, A0):** The A2, A1 and A0 pins are device address inputs that are hardwired or left not connected for hardware compatibility with other FM24CXX devices. When the pins are hardwired, as many as eight 32K devices may be addressed on a single bus system (device addressing is discussed in detail under the Device Addressing section). If the pins are left floating, the A2, A1 and A0 pins will be internally

pulled down to GND if the capacitive coupling to the circuit board  $V_{CC}$  plane is <3pF, if coupling is >3pF, FMSH recommends connecting the address pins to GND.

**WRITE PROTECT (WP):** The FM24C32D has a Write Protect pin that provides hardware data protection. The WP pin allows normal write operations when connected to ground (GND). When the Write Protect pin is connected to VCC, all write operations to the memory are inhibited. If the pin is left floating, the WP pin will be internally pulled down to GND if the capacitive coupling to the circuit board Vcc plane is <3pF. If coupling is >3pF, FMSH recommends connecting the WP to GND. Switching WP to VCC prior to a write operation creates a software write protected function.

### Write Protect Description

| WP Pin Status      | Part of the Memory Protected |

|--------------------|------------------------------|

|                    | FM24C32D                     |

| WP=V <sub>CC</sub> | Full Memory                  |

| WP=GND             | Normal Read/Write Operations |

## **Memory Organization**

**FM24C32D, 32K SERIAL EEPROM:** Internally organized with 128 pages of 32 bytes each, the 32K requires a 12-bit data word address for random word addressing.

**Security Sector :** The FM24C32D offers 32-byte Security Sectors which can be written and (later) permanently locked in Read-only mode. This memory may be used by the system manufacturers to store security and other important information separately from the main memory array.

| Device ADDR           |                        |                     | Byte Number                |   |  |  |  |  |

|-----------------------|------------------------|---------------------|----------------------------|---|--|--|--|--|

| Device ADDR Page ADDR |                        | 31                  |                            | 0 |  |  |  |  |

|                       | 0                      |                     |                            |   |  |  |  |  |

|                       | 1                      |                     |                            |   |  |  |  |  |

| 1010                  | 2                      |                     | Data Memory (128P X 32B)   |   |  |  |  |  |

|                       |                        |                     |                            |   |  |  |  |  |

|                       | 127                    |                     |                            |   |  |  |  |  |

| 1011                  | xxxx x00x              |                     | Security Sector (1P X 32B) |   |  |  |  |  |

|                       | XXXX XXXX <sup>1</sup> |                     |                            |   |  |  |  |  |

| 1011                  | xxxx x01x              |                     | 128 Bits Unique ID (UID)   |   |  |  |  |  |

| 1011                  | xxxx xxxx <sup>2</sup> |                     |                            |   |  |  |  |  |

| 1011                  | xxxx x10x              | 1 Bit Lock Bit (LB) |                            |   |  |  |  |  |

| 1011                  | XXXX XXXX <sup>3</sup> | 1 Bit Lock Bit (LB) |                            |   |  |  |  |  |

Note: 1. Address bits ADDR<10:9> must be 00, ADDR<4:0> define byte address, other bits are don't care. 2. Address bits ADDR<10:9> must be 01, ADDR<3:0> define byte address, other bits are don't care.

3. Address bits ADDR<10:9> must be 10, other bits are don't care.

上海复旦微电子集团股份有限公司

## **Pin Capacitance**

| SYMBOL                        | PARAMETER          | CONDITIONS               | Max | Units |

|-------------------------------|--------------------|--------------------------|-----|-------|

|                               | Input Capacitance  | $V_{IN} = 0V, f = 1MHz$  | 6   | pF    |

| C <sub>OUT</sub> <sup>1</sup> | Output Capacitance | $V_{OUT} = 0V, f = 1MHz$ | 8   | pF    |

Note: 1. This parameter is characterized and is not 100% tested.

## **DC Characteristics**

Applicable over recommended operating range from:  $T_A = -40 \ C$  to  $+85 \ C$ ,  $V_{CC} = +1.7V$  to +5.5V, (unless otherwise noted).

| Symbol                       | Parameter              | Test Condition                              | Min            | Тур  | Max            | Units |

|------------------------------|------------------------|---------------------------------------------|----------------|------|----------------|-------|

| V <sub>CC</sub>              | Supply Voltage         |                                             | 1.7            |      | 5.5            | V     |

| I <sub>CC1</sub>             | Supply Current         | $V_{CC}$ = 5.0V, Read at 400KHz             |                | 0.4  | 1.0            | mA    |

| I <sub>CC2</sub>             | Supply Current         | $V_{CC}$ = 5.0V, Write at 400KHz            |                | 2.0  | 3.0            | mA    |

| I <sub>SB1</sub>             | Standby Current        | $V_{CC}$ = 1.7V, $V_{IN}$ = $V_{CC}/V_{SS}$ |                |      | 1.0            | μA    |

| I <sub>SB2</sub>             | Standby Current        | $V_{CC} = 5.5 V, \ V_{IN} = V_{CC}/V_{SS}$  |                |      | 6.0            | μA    |

| ILI                          | Input Leakage Current  | $V_{IN} = V_{CC}/V_{SS}$                    |                | 0.1  | 3.0            | μA    |

| I <sub>LO</sub>              | Output Leakage Current | $V_{OUT} = V_{CC}/V_{SS}$                   |                | 0.05 | 3.0            | μA    |

| V <sub>IL</sub> <sup>1</sup> | Input Low Level        |                                             | -0.6           |      | $V_{CC} x 0.3$ | V     |

| V <sub>IH</sub> <sup>1</sup> | Input High Level       |                                             | $V_{CC} x 0.7$ |      | $V_{CC} + 0.5$ | V     |

| V <sub>OL2</sub>             | Output Low Level 2     | $V_{CC} = 3.0V, I_{OL} = 2.1 \text{ mA}$    |                |      | 0.4            | V     |

| V <sub>OL1</sub>             | Output Low Level 1     | $V_{CC}$ =1.7V, $I_{OL}$ = 0.15 mA          |                |      | 0.2            | V     |

Note: 1.  $V_{IL}$  min and  $V_{IH}$  max are reference only and are not tested.

## **AC Characteristics**

#### 400 kHz AC characteristics

Recommended operating conditions:  $T_A = -40 \ C$  to  $+85 \ C$ ,  $V_{CC} = +1.7V$  to +5.5V,  $CL = 100 \ pF$  (unless otherwise noted). Test conditions are listed in Note 2.

| Symbol                        | Parameter                                                     | Min       | Max | Units           |

|-------------------------------|---------------------------------------------------------------|-----------|-----|-----------------|

| f <sub>SCL</sub>              | Clock Frequency, SCL                                          |           | 400 | kHz             |

| t <sub>LOW</sub>              | Clock Pulse Width Low                                         | 1.3       |     | μs              |

| t <sub>HIGH</sub>             | Clock Pulse Width High                                        | 0.6       |     | μs              |

| t <sub>l</sub> 1              | Noise Suppression Time                                        |           | 80  | ns              |

| t <sub>AA</sub>               | Clock Low to Data Out Valid                                   | 0.1       | 0.9 | μs              |

| t <sub>BUF</sub> <sup>1</sup> | Time the bus must be free before a new transmission can Start | 1.3       |     | μs              |

| t <sub>HD.STA</sub>           | Start Hold Time                                               | 0.6       |     | μs              |

| t <sub>SU.STA</sub>           | Start Setup Time                                              | 0.6       |     | μs              |

| t <sub>HD.DAT</sub>           | Data In Hold Time                                             | 0         |     | μs              |

| t <sub>SU.DAT</sub>           | Data In Setup Time                                            | 100       |     | ns              |

| t <sub>R</sub>                | Inputs Rise Time <sup>1</sup>                                 |           | 300 | ns              |

| t <sub>F</sub>                | Inputs Fall Time <sup>1</sup>                                 |           | 300 | ns              |

| t <sub>SU.STO</sub>           | Stop Setup Time                                               | 0.6       |     | μs              |

| t <sub>DH</sub>               | Data Out Hold Time                                            | 100       |     | ns              |

| t <sub>WR</sub>               | Write Cycle Time                                              |           | 5   | ms              |

| Endurance <sup>1</sup>        | 3.3V, 25 ℃, Page Mode                                         | 1,000,000 |     | Write<br>Cycles |

#### **1 MHz AC characteristics**

Recommended operating conditions:  $T_A = -40 \ C$  to  $+85 \ C$ ,  $V_{CC} = +2.5V$  to +5.5V,  $CL = 100 \ pF$  (unless otherwise noted). Test conditions are listed in Note 2.

| Symbol                        | Parameter                                                     | Min       | Max | Units           |

|-------------------------------|---------------------------------------------------------------|-----------|-----|-----------------|

| f <sub>SCL</sub>              | Clock Frequency, SCL                                          |           | 1   | MHz             |

| t <sub>LOW</sub>              | Clock Pulse Width Low                                         | 500       |     | ns              |

| t <sub>HIGH</sub>             | Clock Pulse Width High                                        | 320       |     | ns              |

| t <sub>l</sub> 1              | Noise Suppression Time                                        |           | 80  | ns              |

| t <sub>AA</sub>               | Clock Low to Data Out Valid                                   |           | 450 | ns              |

| t <sub>BUF</sub> <sup>1</sup> | Time the bus must be free before a new transmission can Start | 500       |     | ns              |

| t <sub>HD.STA</sub>           | Start Hold Time                                               | 250       |     | ns              |

| t <sub>SU.STA</sub>           | Start Setup Time                                              | 250       |     | ns              |

| t <sub>HD.DAT</sub>           | Data In Hold Time                                             | 0         |     | ns              |

| t <sub>SU.DAT</sub>           | Data In Setup Time                                            | 50        |     | ns              |

| t <sub>R</sub>                | Inputs Rise Time <sup>1</sup>                                 |           | 120 | ns              |

| t <sub>F</sub>                | Inputs Fall Time <sup>1</sup>                                 |           | 120 | ns              |

| t <sub>SU.STO</sub>           | Stop Setup Time                                               | 250       |     | ns              |

| t <sub>DH</sub>               | Data Out Hold Time                                            | 100       |     | ns              |

| t <sub>WR</sub>               | Write Cycle Time                                              |           | 5   | ms              |

| Indurance <sup>1</sup>        | 3.3V, 25 ℃, Page Mode                                         | 1,000,000 |     | Write<br>Cycles |

上海复旦微电子集团股份有限公司 Shanghai Fudan Microelectronics Group Company Limited FM24C32D 2-Wire Serial EEPROM

- Notes: 1. This parameter is characterized and is not 100% tested.

- 2. AC measurement conditions:

- RL (connects to V<sub>CC</sub>): 1.3 kΩInput pulse voltages:  $0.3 V_{CC}$  to  $0.7 V_{CC}$ Input rise and fall times: ≤ 50 ns Input and output timing reference voltages:  $0.5 V_{CC}$

### **Device Operation**

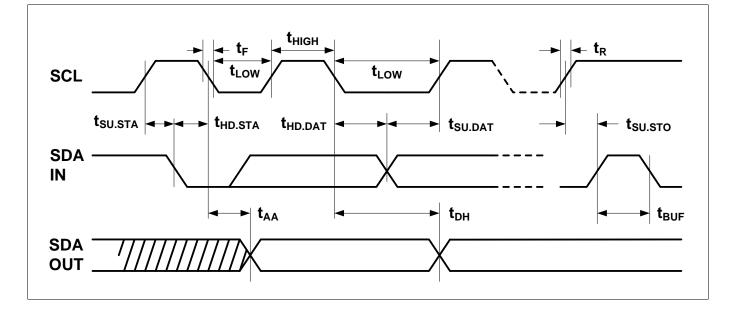

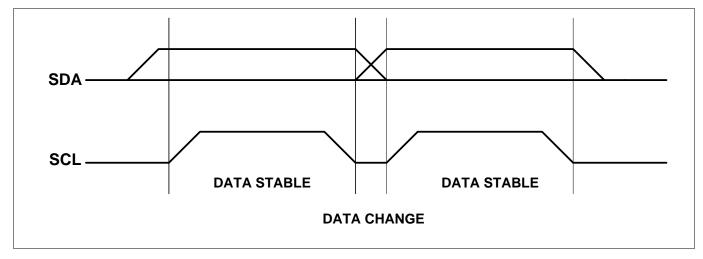

**CLOCK and DATA TRANSITIONS:** The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (refer to Figure 4). Data changes during SCL high periods will indicate a start or stop condition as defined below.

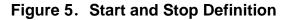

**START CONDITION:** A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (refer to Figure 5).

**STOP CONDITION:** A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (refer to Figure 5).

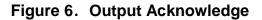

**ACKNOWLEDGE:** All address and data words are serially transmitted to and from the EEPROM in 8-bit

words. The EEPROM sends a zero during the ninth clock cycle to acknowledge that it has received each word.

复旦微电子

**STANDBY MODE:** The FM24C32D features a low-power standby mode which is enabled: (a) upon power-up and (b) after the receipt of the stop bit and the completion of any internal operations.

**Memory RESET:** After an interruption in protocol, power loss or system reset, any 2-wire part can be reset in following these steps:

- 1. Clock up to 9 Cycles,

- 2. Look for SDA high in each cycle while SCL is high and then,

- 3. Create a start condition as SDA is high.

### **Bus Timing**

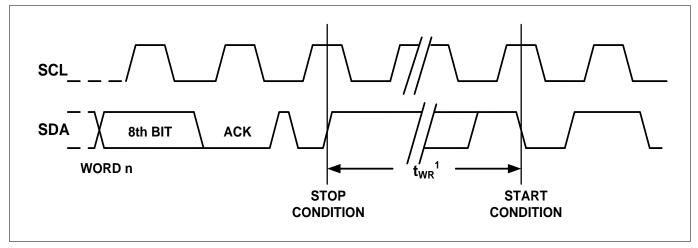

## Write Cycle Timing

Note: 1. The write cycle time t<sub>WR</sub> is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.

#### Figure 4. Data Validity

## **Device Addressing**

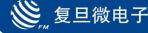

**Data Memory Access:** The 32K EEPROM device requires a 8-bit device address word following a start condition to enable the chip for a read or write operation (refer to Table 1~3).

The device address word consists of a mandatory '1010'(Ah) sequence for the first four most significant bits as shown in Table 1. This is common to all the EEPROM devices.

The 32K EEPROM uses the three device address bits A2, A1, A0 to allow as many as eight devices on the same bus. These bits must compare to their corresponding hard-wired input pins. The A2, A1 and A0 pins use an internal proprietary circuit that biases them to a logic low condition if the pins are allowed to float.

The Module package device address word also consists of a mandatory '1010b'(Ah) sequence for the first four most significant bits. The next 3 bits are all zero.

The eighth bit of the device address is the read/write operation select bit. A read operation is initiated if this bit is high and a write operation is initiated if this bit is low.

Upon a compare of the device address, the EEPROM will output a zero. If a compare is not made, the device will return to a standby state.

**Unique ID Access:** The FM24C32D utilizes a separate memory block containing a factory programmed 128-bit unique ID. Access to this memory location is obtained by beginning the device

address word with a '1011'(Bh) sequence (refer to Table 1). The behavior of the next three bits (A2, A1 and A0) remains the same as during a standard memory addressing sequence.

复旦微电子

The eighth bit of the device address needs be set to a one to read the Serial Number. Writing or altering the 128-bit unique ID is not possible.

For more details on accessing this special feature, See read operations on page 14.

**Security Sector Access:** The FM24C32D offers 32-byte Security Sector which can be written and (later) permanently locked in Read-only mode. Access to this memory location is obtained by beginning the device address word with a '1011b'(Bh) sequence (refer to Table 1). The behavior of the next three bits (A2, A1 and A0) remains the same as during a standard memory addressing sequence.

The eighth bit of the device address is the read/write operation select bit. A read operation is initiated if this bit is high and a write operation is initiated if this bit is low.

For more details on accessing this special feature, See Write Operations and Read Operations on page 13,14.

**NOISE PROTECTION:** Special internal circuitry placed on the SDA and SCL pins prevent small noise spikes from activating the device.

**DATA SECURITY:** The Device has a hardware data protection scheme that allows the user to write protect the entire memory when the WP pin is at  $V_{CC}$ .

上海复旦微电子集团股份有限公司

### Table 1. Device Address

| Access Area              | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|--------------------------|------|------|------|------|------|------|------|------|

| Data Memory              | 1    | 0    | 1    | 0    | A2   | A1   | A0   | R/W  |

| Security Sector          | 1    | 0    | 1    | 1    | A2   | A1   | A0   | R/W  |

| Security Sector Lock Bit | 1    | 0    | 1    | 1    | A2   | A1   | A0   | R/W  |

| Unique ID Number         | 1    | 0    | 1    | 1    | A2   | A1   | A0   | 1    |

|                          | MSB  |      |      |      |      |      |      | LSB  |

### Table 2. First Word Address

| Access Area              | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|--------------------------|------|------|------|------|------|------|------|------|

| Data Memory              | х    | х    | х    | х    | A11  | A10  | A9   | A8   |

| Security Sector          | х    | х    | х    | х    | х    | 0    | 0    | х    |

| Security Sector Lock Bit | х    | х    | х    | х    | х    | 1    | 0    | Х    |

| Unique ID Number         | х    | х    | х    | х    | х    | 0    | 1    | х    |

|                          | MSB  |      |      |      |      |      |      | LSB  |

NOTE: x = Don`t care bit.

### Table 3. Second Word Address

| Access Area              | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|--------------------------|------|------|------|------|------|------|------|------|

| Data Memory              | A7   | A6   | A5   | A4   | A3   | A2   | A1   | A0   |

| Security Sector          | х    | х    | х    | A4   | A3   | A2   | A1   | A0   |

| Security Sector Lock Bit | х    | х    | х    | х    | х    | х    | х    | х    |

| Unique ID Number         | х    | х    | х    | х    | 0    | 0    | 0    | 0    |

|                          | MSB  |      |      |      |      |      |      | LSB  |

NOTE: x = Don`t care bit.

### Write Operations

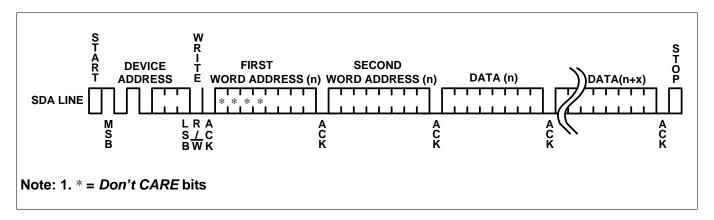

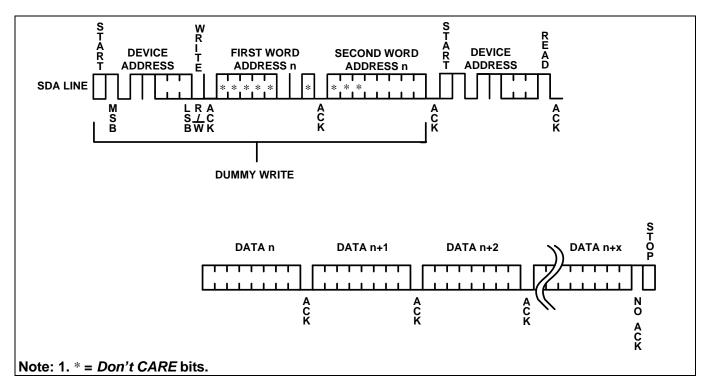

**BYTE WRITE:** A write operation requires two 8-bit data word address following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a zero and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a zero and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condition. At this time the EEPROM enters an internally-timed write cycle,  $t_{WR}$  to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see **Figure 7** on page 15).

**PAGE WRITE:** The 32K EEPROM is capable of 32-byte page writes. A page write is initiated the same way as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to 31 more data words. The EEPROM will respond with a zero after each data word received. The microcontroller must terminate the page write sequence with a stop condition (see **Figure 8** on page 15).

The data word address lower seven bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than 32 data words are transmitted to the EEPROM, the data word address will "roll over" and previous data will be overwritten. **ACKNOWLEDGE POLLING:** Once the internally timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a zero allowing the read or write sequence to continue.

复旦微电子

WRITE SECURITY SECTOR: Write the Security Sector is similar to the page write but requires use of device address, and the special word address seen in Table 1 on page 12. The higher address bits ADDR<11:5> are don't care except for address bits ADDR<10:9>, which must be equal to '00b'. Lower address bits ADDR<4:0> define the byte address inside the Security Sector (see **Figure 12** on page 16).

If the Security Sector is locked, the data bytes transferred during the Write Security Sector operation are not acknowledged (NoAck).

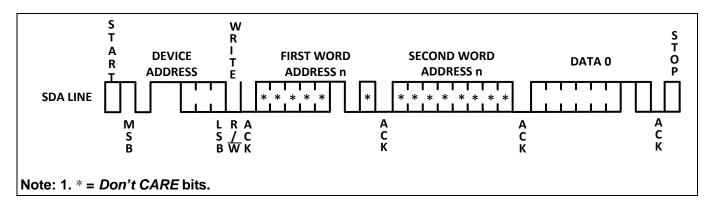

**LOCK SECURITY SECTOR:** Lock the Security Sector is similar to the byte write but requires use of device address, and special word address seen in Table 1 on page 12. The word address bits ADDR<10:9> must be '10b', all other word address bits are don't care. The data byte must be equal to the binary value xxxx xx1x(see **Figure 14** on page 17).

If the Security Sector is locked, the data bytes transferred during the Lock Security Sector operation are not acknowledged (NoAck).

## **Read Operations**

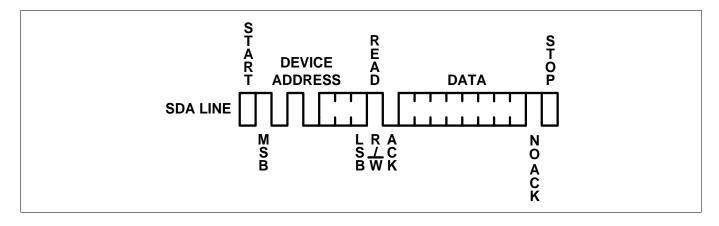

Read operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to one.

**CURRENT ADDRESS READ:** The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address "roll over" during read is from the last byte of the last memory page to the first byte of the first page. The address "roll over" during write is from the last byte of the current page to the first byte of the same page.

Once the device address with the read/write select bit set to one is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input zero but does generate a following stop condition (see **Figure 9** on page 15).

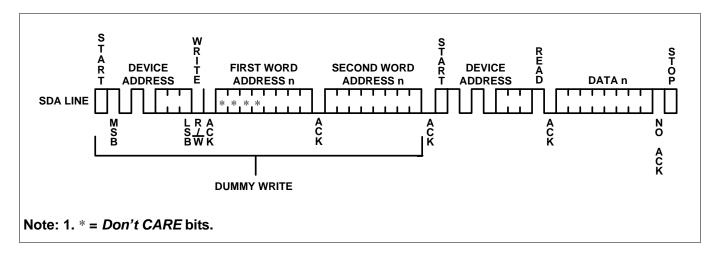

RANDOM READ: A random read requires a "dummy" byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the select bit The read/write high. EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a zero but does generate a following stop condition (see Figure 10 on page 16).

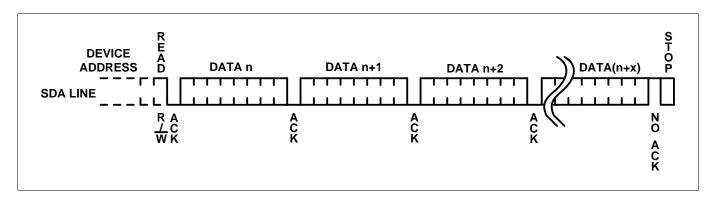

**SEQUENTIAL READ:** Sequential reads are initiated by either a current address read or a random address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will "roll over" and the sequential read will continue. The sequential read operation is terminated when the microcontroller does not respond with a zero but does generate a following stop condition (see **Figure 11** on page 16)

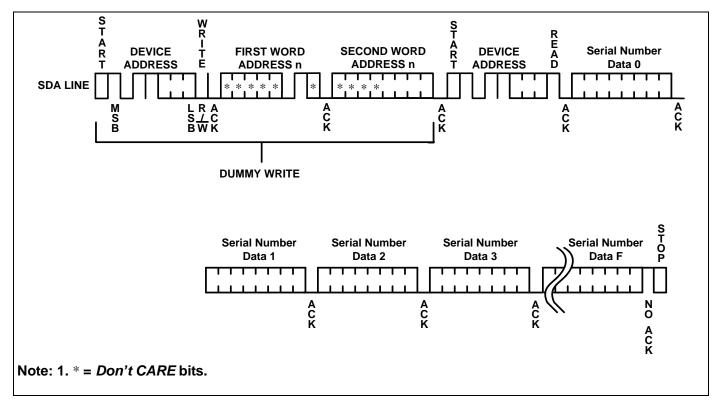

UNIQUE ID READ: Reading the serial number is similar to the sequential read but requires use of the device address, a dummy write, and the use of specific word address seen in Table 1 on page 12. The higher address bits ADDR<11:4> are don't care except for address bits ADDR<10:9>, which must be equal to 'x1b'. Lower address bits ADDR<3:0> define the byte address inside the UID. If the application desires to read the first byte of the UID, the lower address bits L海复旦微电子集团股份有限公司

ADDR<3:0> would need to be '0000b'.

When the end of the 128-bit UID number is reached (16 bytes of data), the data word address will roll-over back to the beginning of the 128-bit UID number. The Unique ID Read operation is terminated when the microcontroller does not respond with a zero (ACK) and instead issues a Stop condition (see **Figure 16** on page 18).

🎉 复旦微电子

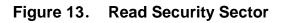

**READ SECURITY SECTOR :** Read the Security Sector is similar to the random read but requires use of device address, a dummy write, and the use of specific word address seen in Table 1 on page 12. The higher address bits ADDR<11:5> are don't care except for address bits ADDR<10:9>, which must be equal to '00b'. The lower address bits ADDR<4:0> define the byte address inside the Security Sector.

The internal byte address is automatically incremented to the next byte address after each byte of data is clocked out. When the last byte (1Fh) is reached, it will roll over to 00h, the first byte of the Security Sector, and continue to increment. (see **Figure 13** on page 17).

**READ LOCK STATUS:** There are two ways to check the lock status of the Security Sector.

1. The first way is initiated by a Security Sector Write, the EEPROM will acknowledge if the Security Sector is unlocked, while it will not acknowledge if the Security Sector is locked.

Once the acknowledge bit is read, it is recommended to generate a Start condition followed by a Stop condition, so that:

- Start: the truncated command is not executed because the Start condition resets the device internal logic

- Stop: the device is then set back into Standby mode by the Stop condition.

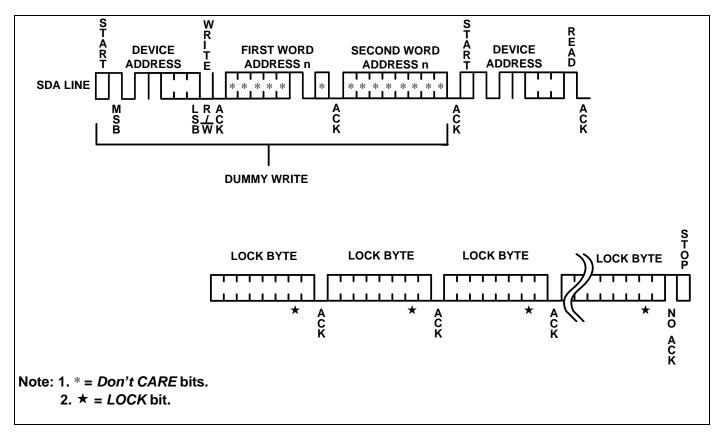

2. The second way is initiated by a Lock Status Read. Lock Status Read is similar to the random read but requires use of device address seen in Table 1 on page 12, a dummy write, and the use of specific word address. The address bits ADDR<10:9> must be '10b', all other address bits are Don't Care. The Lock bit is the BIT1 of the byte read on SDA. It is at "1" when the lock is active and at "0" when the lock is not active. The same data is shifted out repeatedly until the microcontroller does not respond with a zero but does generate a following stop condition (see **Figure 15** on page 18).

### Figure 7. Byte Write

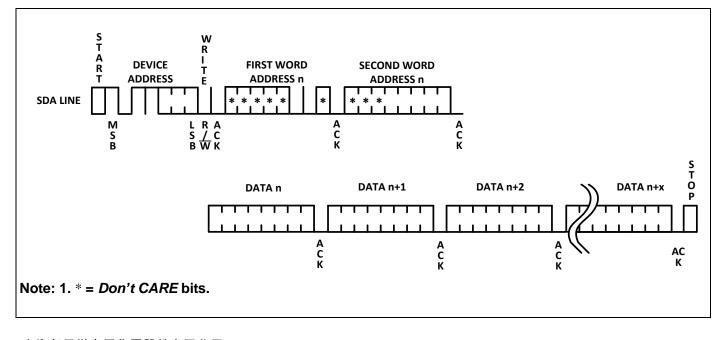

### Figure 8. Page Write

### Figure 9. Current Address Read

Shanghai Fudan Microelectronics Group Company Limited

### Figure 10. Random Read

### Figure 11. Sequential Read

Figure 12. Write Security Sector

### Figure 14. Lock Security Sector

Shanghai Fudan Microelectronics Group Company Limited

### Figure 15. Read Lock Status

### Figure 16. Read Unique ID

### **Ordering Information**

|                                                          |                          | FM        | 24C              | 32 | D -PP | -C | -ŀ |

|----------------------------------------------------------|--------------------------|-----------|------------------|----|-------|----|----|

| Company Prefix                                           |                          |           |                  |    |       |    |    |

| FM = Shanghai Fudan Microel                              | ectronics Group Co., Itd |           |                  |    |       |    |    |

| Product Family                                           |                          |           |                  |    |       |    |    |

| 24C = 2-Wire Serial EEPROM                               |                          |           |                  |    |       |    |    |

| Product Density                                          |                          |           |                  |    |       |    |    |

| 32 = 32K-bit                                             |                          |           |                  |    |       |    |    |

| Device Type                                              |                          |           |                  |    |       |    |    |

| D = with 128-bit Unique ID<br>with 32-byte Security Sect | or                       |           |                  |    |       |    |    |

| Package Type <sup>1</sup>                                |                          |           |                  |    |       |    |    |

| PD = 8-pin PDIP                                          | M2F or M2P = 8-pin Mo    | dule Pack | age <sup>3</sup> |    |       |    |    |

| SO = 8-pin SOP<br>TS = 8-pin TSSOP                       |                          |           |                  |    |       |    |    |

| DN = 8-pin TDFN (2x3mm) <sup>2</sup>                     |                          |           |                  |    |       |    |    |

| $CT = Thin 4-ball WLCSP^{3}$                             |                          |           |                  |    |       |    |    |

| ST = 5-pin TSOT23                                        |                          |           |                  |    |       |    |    |

| Product Carrier                                          |                          |           |                  |    |       |    |    |

| U = Tube                                                 |                          |           |                  |    |       |    |    |

| T = Tape and Reel<br>R = Module Reel                     |                          |           |                  |    |       |    |    |

| HSF ID Code <sup>4</sup>                                 |                          |           |                  |    |       |    |    |

Blank or R = RoHS Compliant G = RoHS Compliant, Halogen-free, Antimony-free

Note:

- 1. For SO, TS, DN package, MSL1 package are available, for detail please contact local sales office.

- 2. For Thinner package please contact local sales office.

- 3. For the details of WLCSP package and Module package please contact local sales office.

- 4. For PD package: R class only. For SO, TS, DN, ST and CT package: G class only.

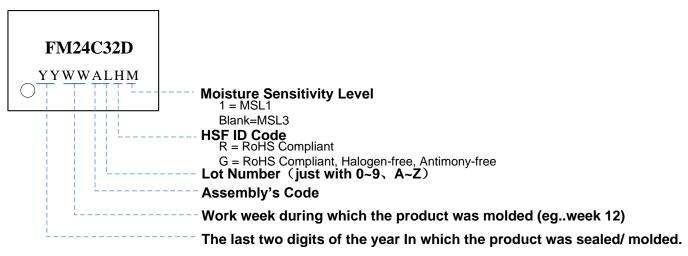

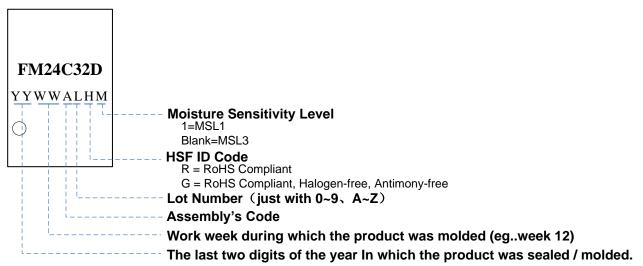

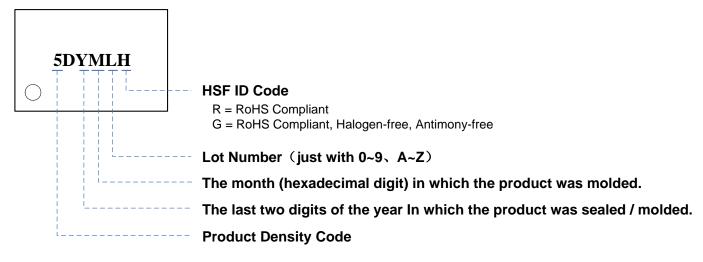

## Part Marking Scheme

#### PDIP8

| h | FM24C32D       |                                                                           |

|---|----------------|---------------------------------------------------------------------------|

| Υ | <u>YYWWALH</u> |                                                                           |

|   |                | HSF ID Code                                                               |

|   |                | R = RoHS Compliant                                                        |

|   |                | Lot Number (just with 0~9、A~Z)                                            |

|   |                | Assembly's Code                                                           |

|   |                | Work week during which the product was molded (egweek 12)                 |

|   | Ĺ              | The last two digits of the year In which the product was sealed / molded. |

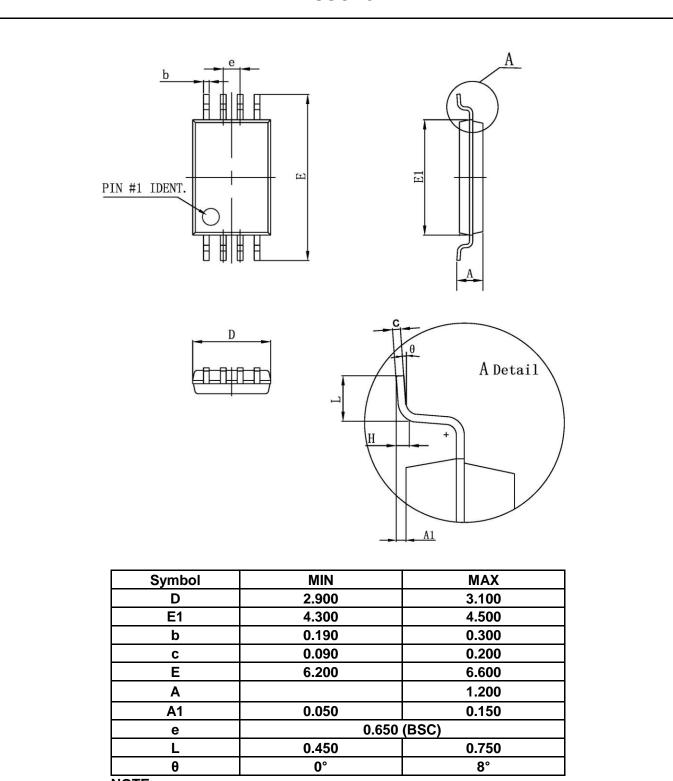

#### TSSOP8

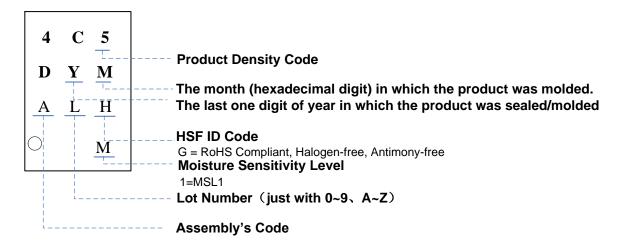

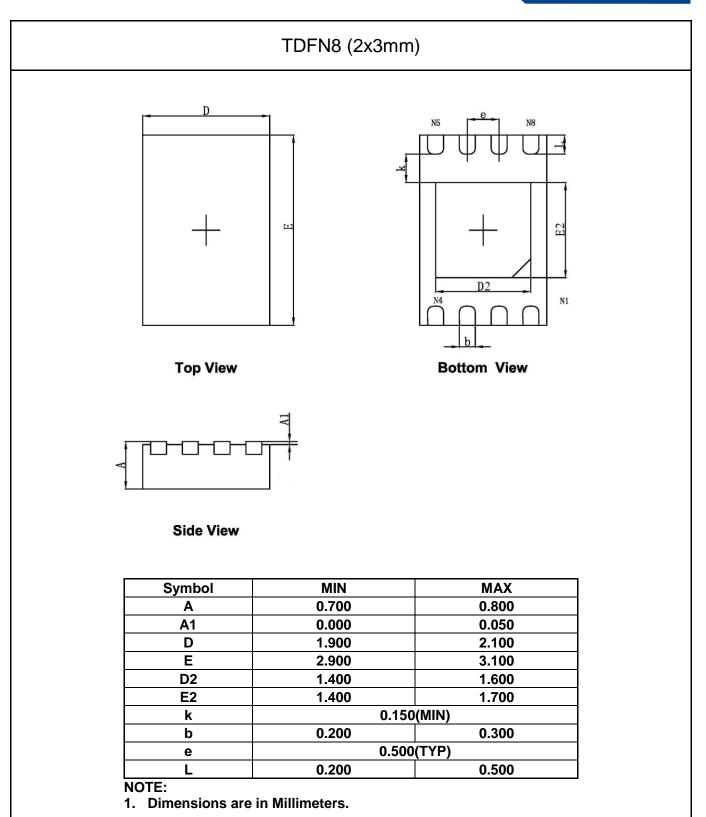

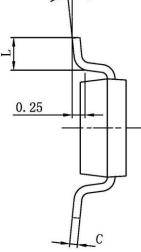

### TDFN8 (2x3mm)

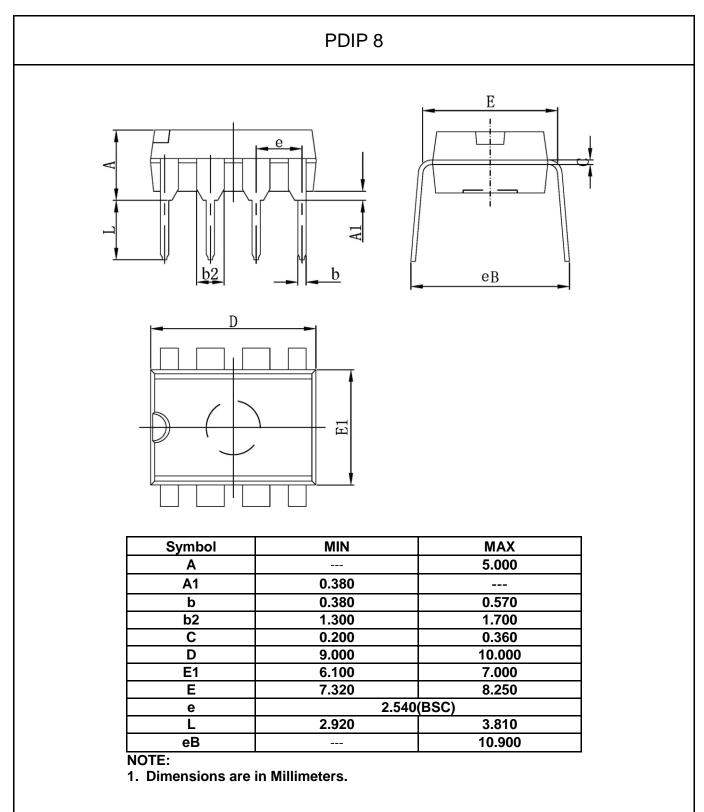

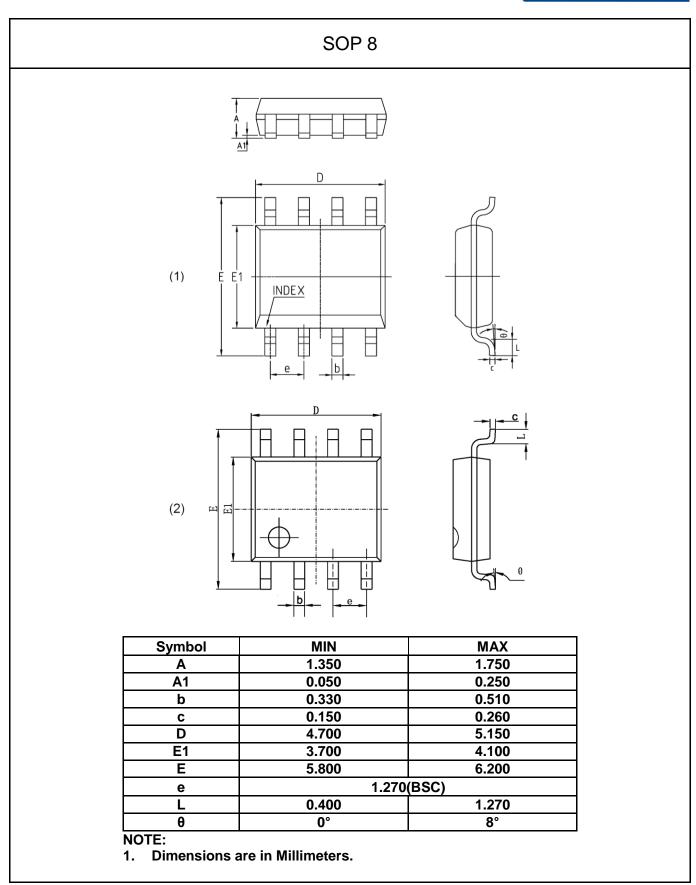

## **Packaging Information**

NOTE:

1. Dimensions are in Millimeters.

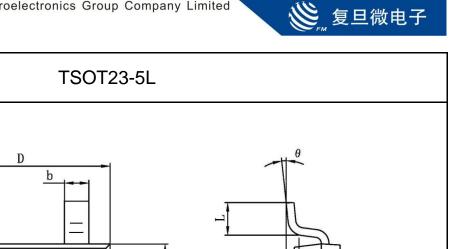

| Symbol | MIN        | MAX        |

|--------|------------|------------|

| Α      | 0.700      | 0.900      |

| A1     | 0.000      | 0.100      |

| A2     | 0.700      | 0.800      |

| b      | 0.350      | 0.500      |

| С      | 0.080      | 0.200      |

| D      | 2.820      | 3.020      |

| E1     | 1.600      | 1.700      |

| E      | 2.650      | 2.950      |

| e      | 0.950(BSC) |            |

| e1     | 1.900(BSC) |            |

| L      | 0.300      | 0.600      |

| θ      | <b>0</b> ° | <b>8</b> ° |

NOTE:

Ы

1. Dimensions are in Millimeters.

## **Revision History**

| Version | Publication date | Pages | Revise Description                         |

|---------|------------------|-------|--------------------------------------------|

| 1.0     | Dec. 2015        | 27    | Initial document Release.                  |

| 1.1     | Mar. 2017        | 28    | Added the 5-pin TSOT23 offering and parts. |

|         |                  |       |                                            |

|         |                  |       |                                            |

## **Sales and Service**

#### Shanghai Fudan Microelectronics Group Co., Ltd.

Address: Bldg No. 4, 127 Guotai Rd, Shanghai City China. Postcode: 200433 Tel: (86-021) 6565 5050 Fax: (86-021) 6565 9115

#### Shanghai Fudan Microelectronics (HK) Co., Ltd.

Address: Unit 506, 5/F., East Ocean Centre, 98 Granville Road, Tsimshatsui East, Kowloon, Hong Kong Tel: (852) 2116 3288 2116 3338 Fax: (852) 2116 0882

#### **Beijing Office**

Address: Room 423, Bldg B, Gehua Building, 1 QingLong Hutong, Dongzhimen Alley north Street, Dongcheng District, Beijing City, China. Postcode: 100007 Tel: (86-010) 8418 6608 Fax: (86-010) 8418 6211

#### **Shenzhen Office**

Address: Room.1301, Century Bldg, No. 4002, Shengtingyuan Hotel, Huaqiang Rd (North), Shenzhen City, China. Postcode: 518028 Tel: (86-0755) 8335 0911 8335 1011 8335 2011 8335 0611 Fax: (86-0755) 8335 9011

# Shanghai Fudan Microelectronics (HK) Ltd Taiwan Representative Office

Address: Unit 1225, 12F., No 252, Sec.1 Neihu Rd., Neihu Dist., Taipei City 114, Taiwan Tel : (886-2) 7721 1889 (886-2) 7721 1890 Fax: (886-2) 7722 3888

# Shanghai Fudan Microelectronics (HK) Ltd Singapore Representative Office

Address : 237, Alexandra Road, #07-01 The Alexcier, Singapore 159929 Tel : (65) 6472 3688 Fax: (65) 6472 3669

# Shanghai Fudan Microelectronics Group Co., Ltd NA Office

Address :2490 W. Ray Road Suite#2 Chandler, AZ 85224 USA Tel : (480) 857-6500 ext 18

#### Web Site: http://www.fmsh.com/

上海复旦微电子集团股份有限公司

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for EEPROM category:

Click to view products by Fudan manufacturer:

Other Similar products are found below :

M29F040-70K6 718278CB 718620G 444358RB 444362FB BR93C46-WMN7TP EEROMH AT24C256BY7-YH-T CAT25320YIGT-KK LE2464DXATBG CAS93C66VP2I-GT3 CAT24S128C4UTR S-25C040A0I-I8T1U S-93S66A0S-J8T2UD N21C21ASNDT3G NV24M01MUW3VTBG S-93A66BD0A-K8T2U3 BR25H128NUX-5ACTR BR24G512FVT-5AE2 CAT24C512C8UTR GT24C04A-2ZLI-TR M24C64-DFCT6TPK M95080-RMC6TG AT24C08D-MAHM-T BR24C21FJ-E2 BR24G02FVJ-3GTE2 BR24L16FJ-WE2 BR24L16FVJ-WE2 BR24S16FJ-WE2 BR24S256F-WE2 BR93L56RFV-WE2 BR93L66F-WE2 BR93L76RFV-WE2 CAT24C16C5ATR CAT24C64C4CTR AT93C46DY6-YH-T 93LC66BT-I/ST BR24T02FVT-WSGE2 24CS08-SSHM-T 24LC08BT-I/ST 24LC512T-ESM BR24L16F-WE2 M93C66-RMC6TG 24AA16T-I/CS16K M35B32-WMN6TP M24M02-DRCS6TPK M24C64-FMC6TG M24C08-WDW6TP M24128-DFCS6TP/K CAT25040LI-G