## Memory FRAM

# 2M (256 K $\times$ 8) Bit SPI

# MB85RS2MTY(AEC-Q100 Compliant)

#### DESCRIPTION

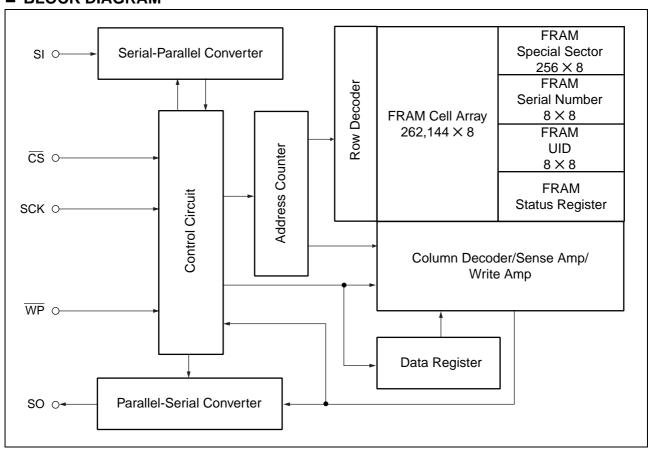

MB85RS2MTY is a FRAM (Ferroelectric Random Access Memory) chip in a configuration of 262,144 words  $\times$  8 bits, using the ferroelectric process and silicon gate CMOS process technologies for forming the nonvolatile memory cells. This product is specifically targeted for high-temperature environment such as automotive applications.

MB85RS2MTY adopts the Serial Peripheral Interface (SPI).

The MB85RS2MTY is able to retain data without using a back-up battery, as is needed for SRAM. The memory cells used in the MB85RS2MTY can be used for 10<sup>13</sup> read/write operations, which is a significant improvement over the number of read and write operations supported by Flash memory and E<sup>2</sup>PROM. As MB85RS2MTY does not need any waiting time in writing process, the write cycle time of MB85RS2MTY is much shorter than that of Flash memories or E<sup>2</sup>PROM.

#### ■ FEATURES

Bit configuration : 262,144 words × 8 bits

Serial Sector Region : 256 words × 8 bits

In this region, data storage after (by) three times reflow based on

JEDEC MSL-3 standard condition is guaranteed.

Unique ID

• Serial Number : 64 bits

In this region, data storage after (by) three times reflow based on

JEDEC MSL-3 standard condition is guaranteed.

• Serial Peripheral Interface : SPI (Serial Peripheral Interfaces)

Correspondent to SPI mode 0 (0, 0) and mode 3 (1, 1)

Operating frequency

High endurance

Data retention

50 MHz (Max)

10<sup>13</sup> times / byte

40 years (+85 °C)

10 years (+105 °C)

3.38 years (+125 °C) or more

Under evaluation for more than 3.38years(+125 °C)

Operating power supply voltage : 1.8 V to 3.6 V

Low power consumption : Operating power supply current 4 mA (Max@50 MHz)

Standby current 220 µA (Max)

Deep Power Down current 30 μA (Max)

Operation ambient temperature range : − 40 °C to +125 °C

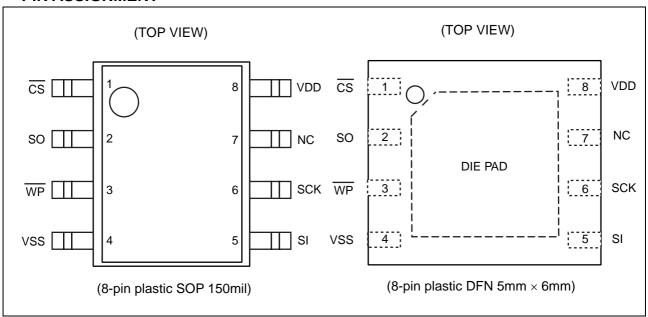

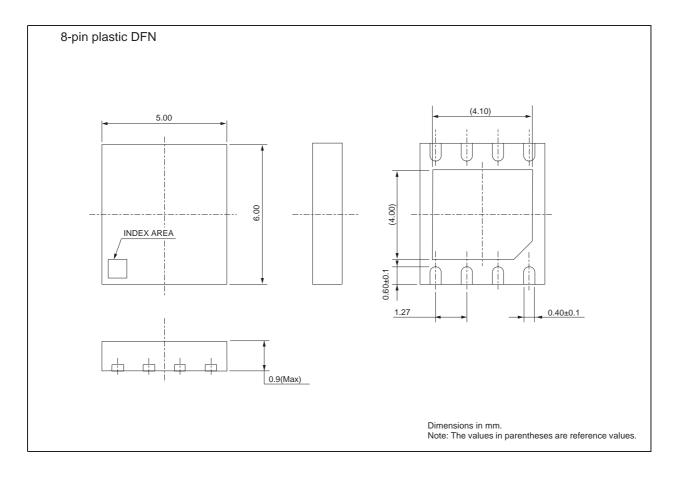

• Package : 8-pin plastic SOP 150mil

8-pin plastic DFN 5mm  $\times$  6mm AEC-Q100 Grade 1 compliant

RoHS compliant

### **■ PIN ASSIGNMENT**

### **■ PIN FUNCTIONAL DESCRIPTIONS**

| Pin No. | Pin Name | Functional description                                                                                                                                                                                                                                                                                                                              |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CS       | Chip Select pin This is an input pin to make chips select. When $\overline{CS}$ is "H" level, device is in deselect (standby) status and SO becomes High-Z. Inputs from other pins are ignored for this time. When $\overline{CS}$ is "L" level, device is in select (active) status. $\overline{CS}$ has to be "L" level before inputting op-code. |

| 3       | WP       | Write Protect pin This is a pin to control writing to a status register. The writing of status register (see "■ STATUS REGISTER") is protected in related with WP and WPEN. See "■WRITING PROTECT" for detail.                                                                                                                                      |

| 7       | NC       | NC pin This pin is not used. With no limitation for its connection.                                                                                                                                                                                                                                                                                 |

| 6       | SCK      | Serial Clock pin This is a clock input pin to input/output serial data. SI is loaded synchronously to a rising edge, SO is output synchronously to a falling edge.                                                                                                                                                                                  |

| 5       | SI       | Serial Data Input pin This is an input pin of serial data. This inputs op-code, address, and writing data.                                                                                                                                                                                                                                          |

| 2       | SO       | Serial Data Output pin This is an output pin of serial data. Reading data of FRAM memory cell array and status register data are output. This is High-Z during standby.                                                                                                                                                                             |

| 8       | VDD      | Supply Voltage pin                                                                                                                                                                                                                                                                                                                                  |

| 4       | VSS      | Ground pin                                                                                                                                                                                                                                                                                                                                          |

| DIE PAD |          | It is allowed for the DIE PAD on the bottom of the DFN8 package to be floating (no connection to anything) or to be connected to VSS.                                                                                                                                                                                                               |

#### **■ BLOCK DIAGRAM**

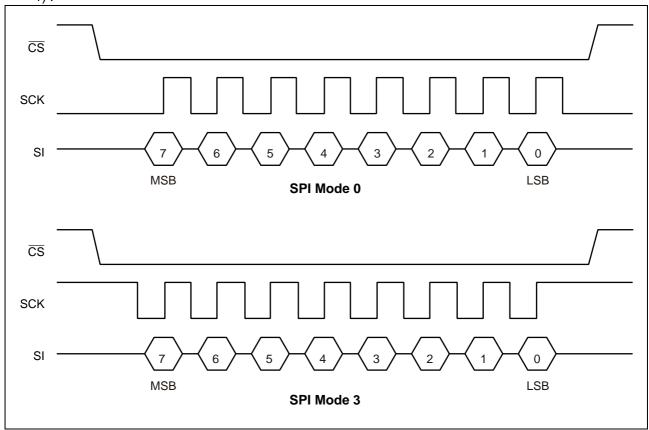

### ■ SPI MODE

MB85RS2MTY corresponds to the SPI mode 0 (CPOL = 0, CPHA = 0), and SPI mode 3 (CPOL = 1, CPHA = 1).

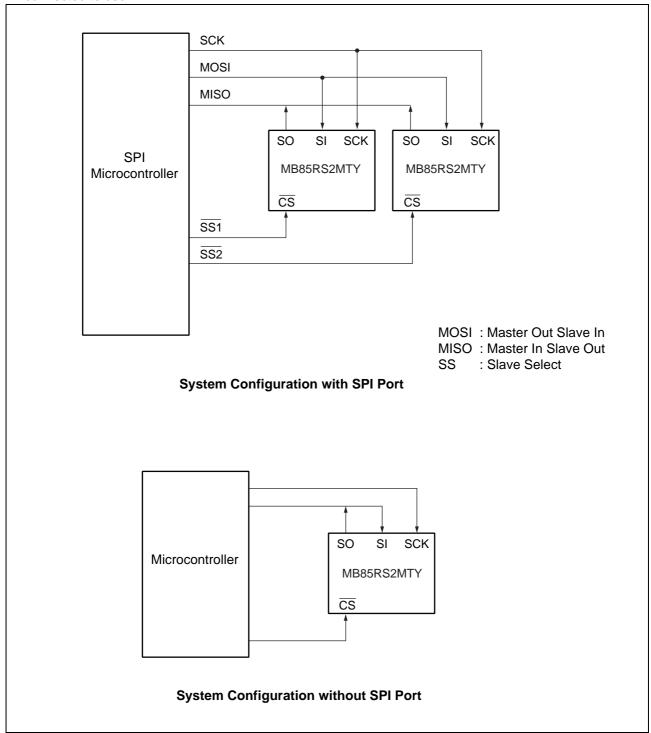

### ■ SERIAL PERIPHERAL INTERFACE (SPI)

MB85RS2MTY works as a slave of SPI. More than 2 devices can be connected by using microcontroller equipped with SPI port. By using a microcontroller not equipped with SPI port, SI and SO can be bus connected to use.

### **■ STATUS REGISTER**

| Bit No. | Bit Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | WPEN     | Status Register Write Protect This is a bit composed of nonvolatile memories (FRAM). WPEN protects writing to a status register (refer to "■ WRITING PROTECT") relating with WP input. Writing with the WRSR command and reading with the RDSR command are possible.                                                                                                                                                                                                                                                                                                                                                             |

| 6 to 4  | _        | Not Used Bits These are bits composed of nonvolatile memories, writing with the WRSR command is possible. These bits are not used but they are read with the RDSR command.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3       | BP1      | Block Protect This is a bit composed of nonvolatile memory. This defines size of write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2       | BP0      | protect block for the WRITE command (refer to "■ BLOCK PROTECT"). Writing with the WRSR command and reading with the RDSR command are possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1       | WEL      | Write Enable Latch This indicates FRAM Array and status register are writable. The WREN command is for setting, and the WRDI command is for resetting. With the RDSR command, reading is possible but writing is not possible with the WRSR command. WEL is reset after the following operations.  After power ON.  After WRDI command recognition.  After return from DPD mode.  Achieving continuous writing mode, WEL is not reset after following operations making it possible to execute writing commands continuously.  After WRSR command recognition.  After WRSN command recognition.  After SSWR command recognition. |

| 0       | 0        | This is a bit fixed to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### ■ OP-CODE

MB85RS2MTY accepts 15 kinds of command specified in op-code. Op-code is <u>a code</u> composed of 8 bits shown in the table below. Do not input invalid codes other than those codes. If  $\overline{\text{CS}}$  is risen while inputting op-code, the command are not performed.

| Name  | Description              | Op-code    |

|-------|--------------------------|------------|

| WREN  | Set Write Enable Latch   | 0000 0110в |

| WRDI  | Reset Write Enable Latch | 0000 0100в |

| RDSR  | Read Status Register     | 0000 0101в |

| WRSR  | Write Status Register    | 0000 0001в |

| READ  | Read Memory Code         | 0000 0011в |

| WRITE | Write Memory Code        | 0000 0010в |

| FSTRD | Fast Read Memory Code    | 0000 1011в |

| DPD   | Deep Power Down Mode     | 1011 1010в |

| RDID  | Read Device ID           | 1001 1111в |

| RUID  | Read Unique ID           | 0100 1100в |

| WRSN  | Write Serial Number      | 1100 0010в |

| RDSN  | Read Serial Number       | 1100 0011в |

| SSWR  | Write Special Sector     | 0100 0010в |

| SSRD  | Read Special Sector      | 0100 1011в |

| FSSRD | Fast Read Special Sector | 0100 1001в |

|       |                          | 1011 1001в |

|       |                          | 1100 0001в |

| RFU   | Reserved                 | 1100 0110в |

|       |                          | 1100 1110в |

|       |                          | 1100 1111в |

#### **■ COMMAND**

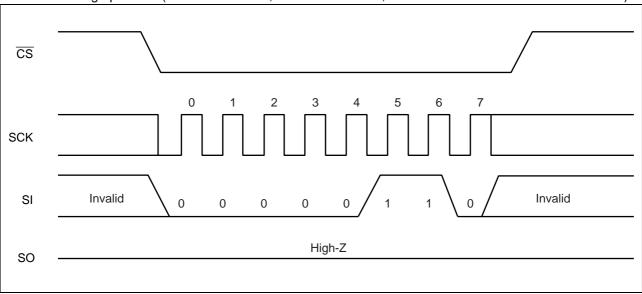

#### • WREN

The WREN command sets WEL (Write Enable Latch) bit to 1. WEL has to be set with the WREN command before writing operation (WRSR command, WRITE command, WRSN command and SSWR command).

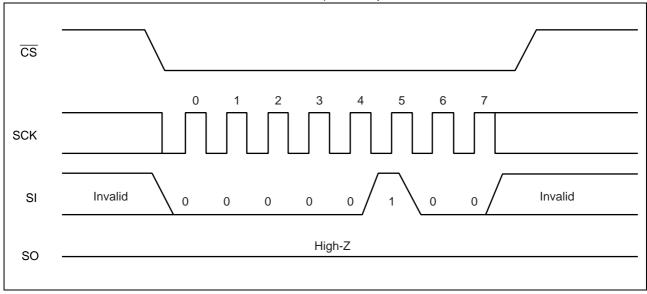

### • WRDI

The WRDI command resets WEL (Write Enable Latch) bit to 0. Writing operation (WRSR command, WRITE command, WRSN command and SSWR command) are not performed when WEL is reset.

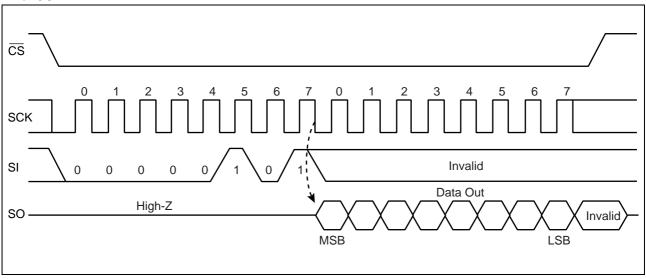

#### • RDSR

The RDSR command reads status register data. After op-code of RDSR is input to SI, 8-cycle clock is input to SCK. The SI value is invalid for this time. SO is output synchronously to a falling edge of SCK. In the RDSR command, repeated reading of status register is enabled by sending SCK continuously before rising of CS.

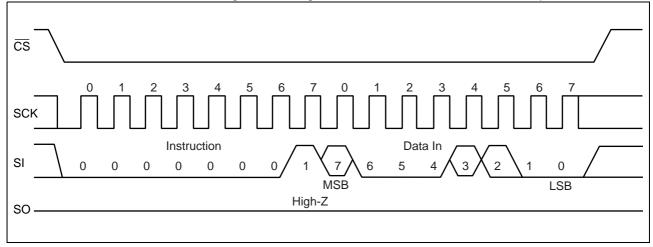

#### • WRSR

The WRSR command writes data to the nonvolatile memory bit of status register. After performing WRSR op-code to a SI pin, 8 bits writing data is input. WEL (Write Enable Latch) is not able to be written with WRSR command. A SI value correspondent to bit 1 is ignored. Bit <u>0 of</u> the status register is fixed to "0" and cannot be written. The SI value corresponding to <u>bit 0</u> is ignored. WP signal level shall be fixed before performing WRSR command, and do not change the <u>WP</u> signal level until the end of command sequence.

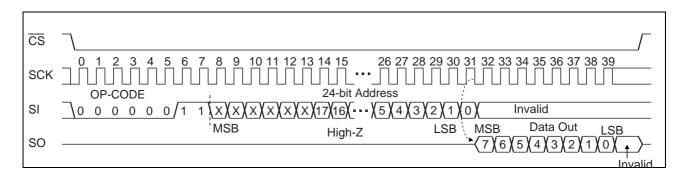

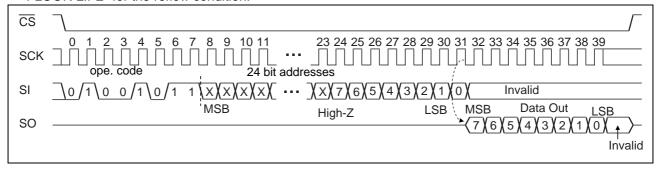

#### • READ

The READ command reads FRAM memory cell array data. Arbitrary 16 bits address and op-code of READ are input to SI. The 6-bit upper address bit is invalid. Then, 8-cycle clock is input to SCK. SO is output synchronously to the falling edge of SCK. While reading, the SI value is invalid. When  $\overline{\text{CS}}$  is risen, the READ command is completed, but keeps on reading with automatic address increment which is enabled by continuously sending clocks to SCK in unit of 8 cycles before  $\overline{\text{CS}}$  rising. When it reaches the most significant address, it rolls over to the starting address, and reading cycle keeps on infinitely.

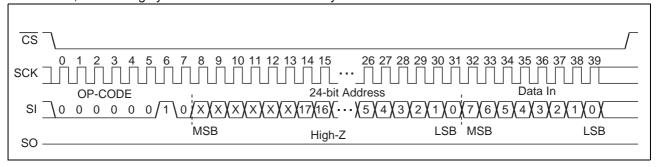

#### • WRITE

The WRITE command writes data to FRAM memory cell array. WRITE op-code, arbitrary 16 bits of address and 8 bits of writing data are input to SI. The 6-bit upper address bit is invalid. When 8 bits of writing data is input, data is written to FRAM memory cell array. Risen  $\overline{CS}$  will terminate the WRITE command, but if you continue sending the writing data for 8 bits each before  $\overline{CS}$  rising, it is possible to continue writing with automatic address increment. When it reaches the most significant address, it rolls over to the starting address, and writing cycle can be continued infinitely.

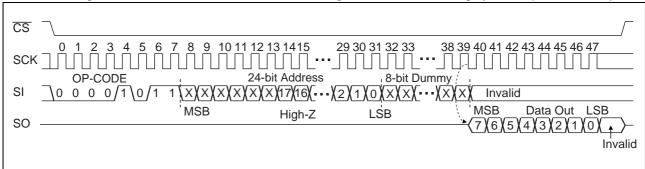

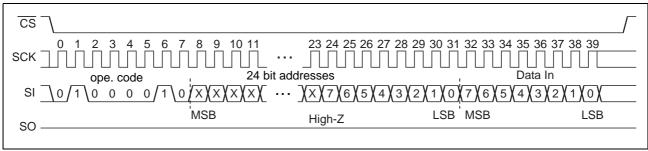

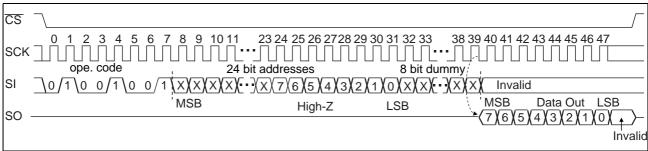

#### • FSTRD

The FSTRD command reads FRAM memory cell array data. Arbitrary 24 bits address and op-code of FSTRD are input to SI followed by 8 bits dummy. The 6-bit upper address bit is invalid. Then, 8-cycle clock is input to SCK. SO is output synchronously to the falling edge of SCK. While reading, the SI value is invalid. When CS is risen, the FSTRD command is completed, but keeps on reading with automatic address increment which is enabled by continuously sending clocks to SCK in unit of 8 cycles before CS rising. When it reaches the most significant address, it rolls over to the starting address, and reading cycle keeps on infinitely.

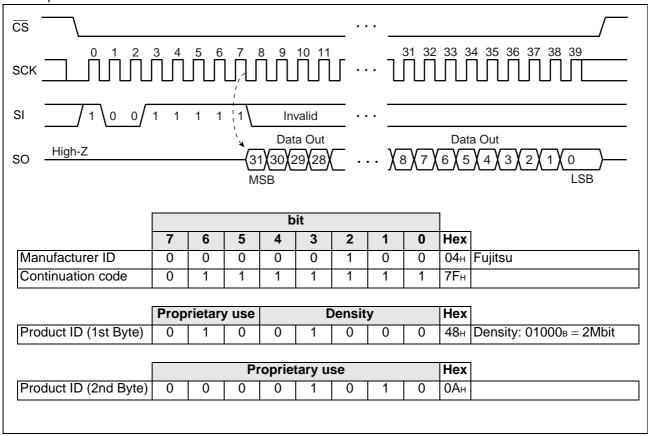

#### • RDID

The RDID command reads fixed Device ID. After performing RDID op-code to SI, 32-cycle clock is input to SCK. The SI value is invalid for this time. SO is output synchronously to a falling edge of SCK. The output is in order of Manufacturer ID (8bit)/Continuation code (8bit)/Product ID (1st Byte)/Product ID (2nd Byte). In the RDID command, 32-bit  $\underline{Device}$  ID is output by continuously sending SCK clock, and SO holds the output state of the last bit until  $\overline{CS}$  is risen.

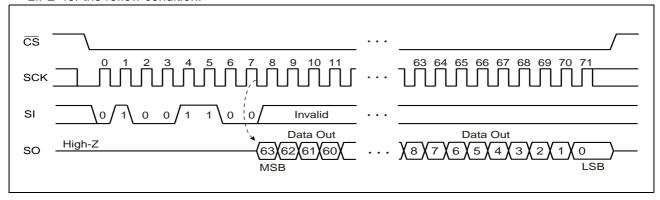

#### • RUID

The RUID command reads an unique ID which is defined in 64bits for each device. After performing RUID op-code to SI, 64-cycle clock is input to SCK. The SI value is invalid for this time. SO is output synchronously to a falling edge of SCK.

The unique ID is stable between before and after reflow. Refer "■ REFLOW CONDITIONS AND FLOOR LIFE" for the reflow condition.

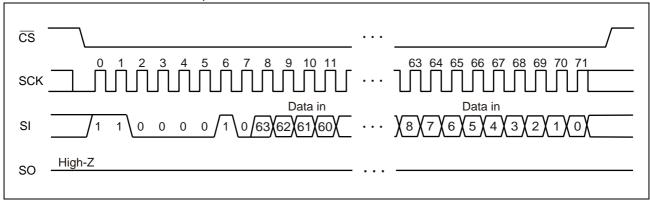

#### •WRSN

The WRSN command writes data to serial number region which is allowed to write only one time. After performing WRSN op-code to SI, 64bits of writing data is input. Once wrote, the serial number region is protected, disabling to overwrite even when issuing WRSN command.

WP signal level shall be fixed before performing WRSN command, and do not change the WP signal level until the end of command sequence.

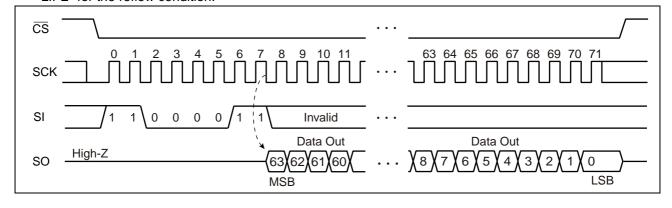

#### •RDSN

The RDSN command reads 64 bits of serial number which is written using WRSN command. After performing RDSN op-code to SI, 64-cycle clock to SCK. The SI value is invalid for this time. SO is output synchronously to a falling edge of SCK. When reading serial number from devices which no WRSN command is executed, "0" for all bits are output.

The serial number is stable between before and after reflow. Refer "■ REFLOW CONDITIONS AND FLOOR LIFE" for the reflow condition.

#### • SSWR

The SSWR command writes data to special sector (a special region of 256 Byte in FRAM). SSWR op-code, arbitrary 24 bits address and 8-bit writing data are input to SI. The 16-bit upper address is invalid. When input of 8-bit writing data is completed, it starts writing data to special sector. Risen  $\overline{\text{CS}}$  will terminate the SSWR command, but if you continue the writing data for each before  $\overline{\text{CS}}$  rising, it is possible to continue writing with automatic address increment. When it reaches the most significant address, roll over is not happen, the data hereafter is ignored.

The data in special sector is stable between before and after reflow. Refer "■ REFLOW CONDITIONS AND FLOOR LIFE" for the reflow condition.

#### • SSRD

The SSRD command reads data from special sector (a special region of 256 Byte in FRAM). SSWR opcode and arbitrary 24 bits address are input to SI. The 16-bit upper address is invalid. Then, 8-cycle clock is input to SCK. SO is output synchronously to the falling edge of SCK. While reading, the SI value is invalid. When  $\overline{\text{CS}}$  is risen, the SSRD command is completed, but keeps on reading with automatic address increment which is enabled by continuously sending clocks to SCK in unit of 8 cycles before  $\overline{\text{CS}}$  rising. When it reaches the most significant address, roll over is not happen.

The data in special sector is stable between before and after reflow. Refer "■ REFLOW CONDITIONS AND FLOOR LIFE" for the reflow condition.

#### • FSSRD

The SSRD command reads data from special sector (a special region of 256 Byte in FRAM). SSWR opcode and arbitrary 24 bits address are input to SI followed by 8 bits dummy. The 16-bit upper address is invalid. Then, 8-cycle clock is input to SCK. SO is output synchronously to the falling edge of SCK. While reading, the SI value is invalid. When  $\overline{\text{CS}}$  is risen, the SSRD command is completed, but keeps on reading with automatic address increment which is enabled by continuously sending clocks to SCK in unit of 8 cycles before  $\overline{\text{CS}}$  rising. When it reaches the most significant address, roll over is not happen.

The data in special sector is stable between before and after reflow. Refer "■ REFLOW CONDITIONS AND FLOOR LIFE" for the reflow condition.

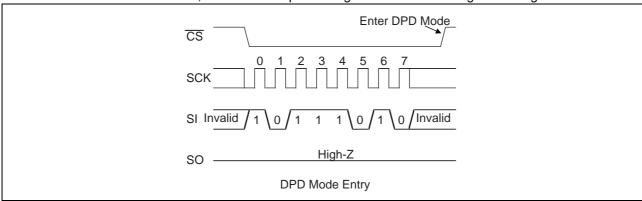

#### • DPD(Deep Power Down)

The DPD command shifts the LSI to a low power mode called "DPD mode". The transition to the DPD mode is carried out at the rising edge of CS after operation code in the DPD command. However, when at least one SCK clock is inputted before the rising edge of CS after operation code in the DPD command, this DPD command is canceled.

After the DPD mode transition, SCK and SI inputs are ignored and SO changes to a High-Z state.

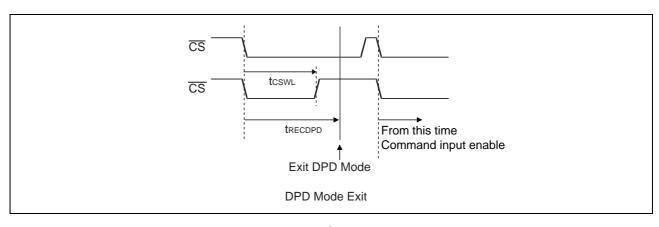

Returning to an normal operation from the DPD mode is carried out after  $t_{RECDPD}$  (Max 10  $\mu$ s) time from the falling edge of  $\overline{CS}$  (see the figure below). It is possible to return  $\overline{CS}$  to H level before  $t_{RECDPD}$  time. However, it is prohibited to bring down  $\overline{CS}$  to L level again during  $t_{RECDPD}$  period.

#### **■ BLOCK PROTECT**

Writing protect block for WRITE command is configured by the value of BP0 and BP1 in the status register.

| BP1 | BP0 | Protected Block              |

|-----|-----|------------------------------|

| 0   | 0   | None                         |

| 0   | 1   | 30000н to 3FFFFн (upper 1/4) |

| 1   | 0   | 20000н to 3FFFFн (upper 1/2) |

| 1   | 1   | 00000н to 3FFFFн (all)       |

#### **■ WRITING PROTECT**

Writing operation of the WRITE command and the WRSR command are protected with the value of WEL, WPEN, WP as shown in the table.

| WEL | WPEN | WP | Protected Blocks | Unprotected Blocks | Status Register |

|-----|------|----|------------------|--------------------|-----------------|

| 0   | Х    | Х  | Protected        | Protected          | Protected       |

| 1   | 0    | Х  | Protected        | Unprotected        | Unprotected     |

| 1   | 1    | 0  | Protected        | Unprotected        | Protected       |

| 1   | 1    | 1  | Protected        | Unprotected        | Unprotected     |

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Symbol          | Ra    | Unit                     |      |

|-------------------------------|-----------------|-------|--------------------------|------|

| Farameter                     | Symbol          | Min   | Max                      | Unit |

| Power supply voltage*         | V <sub>DD</sub> | - 0.5 | + 4.0                    | V    |

| Input voltage*                | Vin             | - 0.5 | $V_{DD} + 0.5 (\le 4.0)$ | V    |

| Output voltage*               | Vouт            | - 0.5 | $V_{DD} + 0.5 (\le 4.0)$ | V    |

| Operation ambient temperature | TA              | - 40  | + 125                    | °C   |

| Storage temperature           | Tstg            | - 55  | + 150                    | °C   |

<sup>\*:</sup> These parameters are based on the condition that Vss is 0 V.

WARNING: Semiconductor devices may be permanently damaged by application of stress (including, without limitation, voltage, current or temperature) in excess of absolute maximum ratings.

Do not exceed any of these ratings.

■ RECOMMENDED OPERATING CONDITIONS

| Parameter                       | Symbol          |      | Unit |       |       |

|---------------------------------|-----------------|------|------|-------|-------|

| Farameter                       | Symbol          | Min  | Тур  | Max   | Ollit |

| Power supply voltage*1          | V <sub>DD</sub> | 1.8  | 3.3  | 3.6   | V     |

| Operation ambient temperature*2 | TA              | - 40 |      | + 125 | °C    |

<sup>\*1:</sup> These parameters are based on the condition that Vss is 0 V.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated under these conditions.

Any use of semiconductor devices will be under their recommended operating condition. Operation under any conditions other than these conditions may adversely affect reliability of device and could result in device failure.

No warranty is made with respect to any use, operating conditions or combinations not represented on this data sheet. If you are considering application under any conditions other than listed herein, please contact sales representatives beforehand.

<sup>\*2:</sup> Ambient temperature when only this device is working. Please consider it to be the almost same as the package surface temperature.

### **■ ELECTRICAL CHARACTERISTICS**

#### 1. DC Characteristics

(within recommended operating conditions)

| Parameter                        | Symbol | Condition                                                                           |        | Value                 |     | Unit                  |       |  |

|----------------------------------|--------|-------------------------------------------------------------------------------------|--------|-----------------------|-----|-----------------------|-------|--|

| Parameter                        | Symbol | Condition                                                                           |        | Min                   | Тур | Max                   | J.III |  |

|                                  |        | $\overline{CS} = V_DD$                                                              | 25 °C  |                       |     | 1                     |       |  |

| Input leakage current*1          | Heat   | <b>C3</b> = <b>V</b> DD                                                             | 125 °C |                       |     | 2                     | ^     |  |

|                                  | lu     | WP, SCK, CS                                                                         | 25 °C  | _                     |     | 1                     | μΑ    |  |

|                                  |        | $SI = 0 V to V_{DD}$                                                                | 125 °C | _                     |     | 2                     |       |  |

| Output lookaga aurrant*2         | lli al | SO 0 1/ to 1/                                                                       | 25 °C  | _                     |     | 1                     | ^     |  |

| Output leakage current*2         | ILO    | $SO = 0 V to V_{DD}$                                                                | 125 °C | _                     |     | 2                     | μΑ    |  |

| Operating power supply current*3 | lod    | SCK = 50MHz                                                                         |        | _                     | 3.2 | 4                     | mA    |  |

| Standby current                  | IsB    | $\begin{array}{c} SCK = SI = \overline{CS} = \\ \overline{WP} = V_{DD} \end{array}$ |        | _                     | 11  | 220                   | μΑ    |  |

| Sleep current                    | Izz    | CS = V <sub>DD</sub> All inputs V <sub>SS</sub> or V <sub>DD</sub>                  |        | _                     | 6   | 30                    | μΑ    |  |

| Input high voltage               | Vıн    | V <sub>DD</sub> = 1.8 V to 3.6 V                                                    |        | $V_{DD} \times 0.7$   | _   | V <sub>DD</sub> + 0.3 | V     |  |

| Input low voltage                | VıL    | V <sub>DD</sub> = 1.8 V to 3.6 V                                                    |        | - 0.3                 |     | $V_{DD} \times 0.3$   | V     |  |

| Output high voltage              | Vон    | Iон = -2 mA                                                                         |        | V <sub>DD</sub> - 0.5 |     | _                     | V     |  |

| Output low voltage               | Vol    | IoL = 2 m/                                                                          | ٩      |                       |     | 0.4                   | V     |  |

<sup>\*1 :</sup> Applicable pin :  $\overline{\text{CS}}$ ,  $\overline{\text{WP}}$ , SCK, SI

<sup>\*2 :</sup> Applicable pin : SO

$<sup>^*3</sup>$ : Input voltage magnitude: VDD – 0.2 V or VSS

#### 2. AC Characteristics

| Darameter                | Cymbal          | Va  | lue | l lmi4 | Condition                                  |  |

|--------------------------|-----------------|-----|-----|--------|--------------------------------------------|--|

| Parameter                | Symbol          | Min | Max | Unit   | $V_{DD}$                                   |  |

| SCK clock frequency      | fcк             | _   | 50  | MHz    | all commands ex-<br>cept for READ/<br>SSRD |  |

|                          |                 | _   | 40  |        | READ command                               |  |

|                          |                 | _   | 10  |        | SSRD command                               |  |

| Clock high time          | tсн             | 9   | _   | ns     |                                            |  |

| Clock low time           | <b>t</b> cL     | 9   | _   | ns     |                                            |  |

| Chip select set up time  | <b>t</b> csu    | 11  | _   | ns     |                                            |  |

| Chip select hold time    | <b>t</b> csH    | 5   | _   | ns     |                                            |  |

| Output disable time      | top             | _   | 10  | ns     |                                            |  |

| Output data valid time   | todv            | _   | 9   | ns     | *1                                         |  |

| Output hold time         | tон             | 0   | _   | ns     |                                            |  |

| Deselect time            | <b>t</b> D      | 40  | _   | ns     |                                            |  |

| Data in rising time      | <b>t</b> R      | _   | 50  | ns     |                                            |  |

| Data falling time        | t⊧              | _   | 50  | ns     |                                            |  |

| Data set up time         | <b>t</b> su     | 5   | _   | ns     |                                            |  |

| Data hold time           | tн              | 5   | _   | ns     |                                            |  |

| DPD recovery pulse width | <b>t</b> cswL   | 100 | _   | ns     |                                            |  |

| DPD recovery time        | <b>t</b> RECDPD | _   | 10  | μS     |                                            |  |

<sup>\*1:</sup> In SSRD command, 60ns(max.)

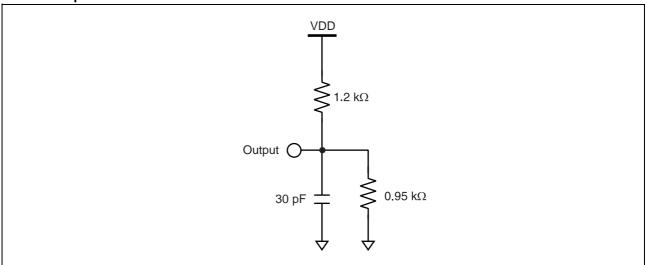

#### **AC Test Condition**

$\begin{array}{lll} \mbox{Power supply voltage} & : 1.8 \ \mbox{V to } 3.6 \ \mbox{V Operation} \\ \mbox{Operation ambient temperature} & : -40 \ \mbox{°C to} \ + 125 \ \mbox{°C} \\ \mbox{Input voltage magnitude} & : V_{DD} \times 0.8 \le V_{IH} \le V_{DD} \\ \mbox{0 } 0 \le V_{IL} \le V_{DD} \times 0.2 \end{array}$

### **AC Load Equivalent Circuit**

### 3. Pin Capacitance

| Parameter          | Symbol   | Condition                                                              | Va  | Unit |       |

|--------------------|----------|------------------------------------------------------------------------|-----|------|-------|

| Farameter          | Syllibol | Condition                                                              | Min | Max  | Oilit |

| Output capacitance | Со       | $V_{DD} = 3.3 \text{ V},$ $V_{IN} = V_{OUT} = 0 \text{ V to } V_{DD},$ | _   | 8    | pF    |

| Input capacitance  | Cı       | $f = 1 \text{ MHz}, T_A = +25 ^{\circ}\text{C}$                        | _   | 6    | pF    |

### **■ TIMING DIAGRAM**

### • Serial Data Timing $\overline{\text{CS}}$ ► tcsH tcsu tcH tCL tcH SCK tsu Valid in SI todv top toн |◀ High-Z High-Z SO : H or L

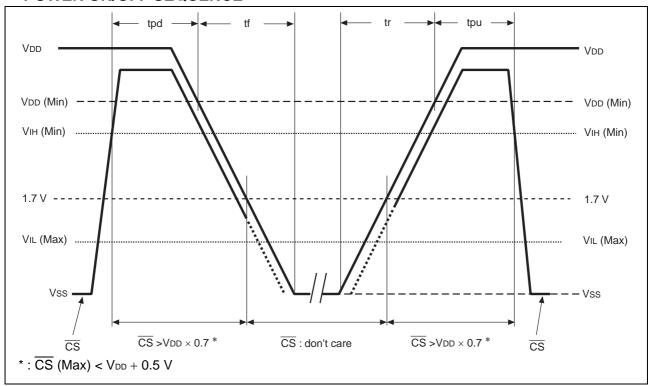

#### **■ POWER ON/OFF SEQUENCE**

In case relative short  $V_{DD}$  pulse whose peak level is beyond 1.7 is applied, please set  $V_{DD}$  falling time, tf, longer than 0.4ms/V. (When  $V_{DD}$  rises beyond 1.7V, and falls just after, if this term is very short the device may loose its function.).

| Doromotor                        | Cumbal | Value |     | l lmi4 | Condition       |

|----------------------------------|--------|-------|-----|--------|-----------------|

| Parameter                        | Symbol | Min   | Max | Unit   | V <sub>DD</sub> |

| CS level hold time at power OFF  | tnd    | 400   | _   | nc     | 1.8V to 2.7V    |

| CS level floid time at power OFF | tpd    | 0     | _   | ns     | 2.7V to 3.6V    |

| CS level hold time at power ON   | tpu    | 450   | _   | μS     | _               |

| Power supply rising time         | tr     | 0.05  | _   | ms/V   | _               |

| Power supply falling time        | tf     | 0.1   |     | ms/V   | _               |

If the device does not operate within the specified conditions of read cycle, write cycle or power on/off sequence, memory data can not be guaranteed.

#### **■ FRAM CHARACTERISTICS**

| Parameter              | Value            |     | Unit       | Remarks                                                 |  |

|------------------------|------------------|-----|------------|---------------------------------------------------------|--|

| Farameter              | Min              | Max | Oill       | Keniarks                                                |  |

| Read/Write Endurance*1 | 10 <sup>13</sup> | _   | Times/byte | Operation Ambient Temperature $T_A = +125$ °C           |  |

|                        | 3.38 or more*3   | _   |            | Operation Ambient Temperature T <sub>A</sub> = + 125 °C |  |

| Data Retention*2       | 10               |     | Years      | Operation Ambient Temperature T <sub>A</sub> = + 105 °C |  |

|                        | 40               |     |            | Operation Ambient Temperature T <sub>A</sub> = +85 °C   |  |

<sup>\*1:</sup> Total number of reading and writing defines the minimum value of endurance, as an FRAM memory operates with destructive readout mechanism.

#### ■ NOTE ON USE

We recommend programming of the device after reflow except for special sector region and serial number region. Data written before reflow cannot be guaranteed.

#### **■ ESD AND LATCH-UP**

(8-pin plastic SOP 150mil)

| Test                                                                | DUT                                              | Value     |

|---------------------------------------------------------------------|--------------------------------------------------|-----------|

| ESD HBM (Human Body Model)<br>JESD22-A114 compliant                 | MB85RS2MTYPNF-GS-AWE2<br>MB85RS2MTYPNF-GS-AWERE2 | ≥  2000 V |

| ESD CDM (Charged Device Model)<br>AEC-Q100-011(FI-CDM) compliant    |                                                  | ≥  1000 V |

| Latch-Up (I-test)<br>JESD78 compliant                               |                                                  | ≥  125mA  |

| Latch-Up (V <sub>supply</sub> overvoltage test)<br>JESD78 compliant |                                                  | ≥ 5.4V    |

<sup>\*2:</sup> Minimum values define retention time of the first reading/writing data right after shipment, and these values are calculated by qualification results.

<sup>\*3:</sup> Under evaluation for more than 3.38years(+125 °C).

#### (8-pin plastic DFN 5mm × 6mm)

| Test                                                                | DUT                    | Value     |

|---------------------------------------------------------------------|------------------------|-----------|

| ESD HBM (Human Body Model)<br>JESD22-A114 compliant                 | MB85RS2MTYPN-GS-AWEWE1 | ≥  2000 V |

| ESD CDM (Charged Device Model)<br>AEC-Q100-011(FI-CDM) compliant    |                        | ≥  500 V  |

| Latch-Up (I-test)<br>JESD78 compliant                               |                        | ≥  125mA  |

| Latch-Up (V <sub>supply</sub> overvoltage test)<br>JESD78 compliant |                        | ≥ 5.4V    |

#### ■ REFLOW CONDITIONS AND FLOOR LIFE

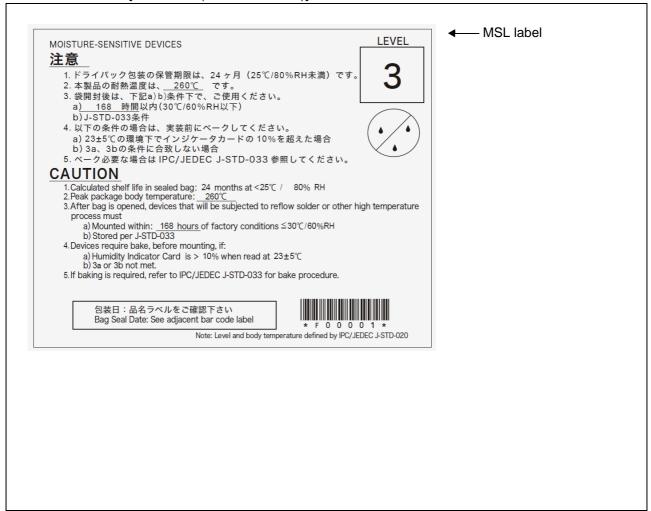

[ JEDEC MSL ] : Moisture Sensitivity Level 3 (ISP/JEDEC J-STD-020D)

#### ■ Current status on Contained Restricted Substances

This product complies with the regulations of REACH Regulations, EU RoHS Directive and China RoHS.

### ■ ORDERING INFORMATION

| Part number             | Package           | Shipping form         | Minimum shipping quantity |

|-------------------------|-------------------|-----------------------|---------------------------|

| MB85RS2MTYPNF-GS-AWE2   | 8-pin plastic SOP | Tube                  | *                         |

| MB85RS2MTYPNF-GS-AWERE2 | 8-pin plastic SOP | Embossed Carrier tape | 1500                      |

| MB85RS2MTYPN-GS-AWEWE1  | 8-pin plastic DFN | Embossed Carrier tape | 1500                      |

<sup>\*:</sup> Please contact our sales office about minimum shipping quantity.

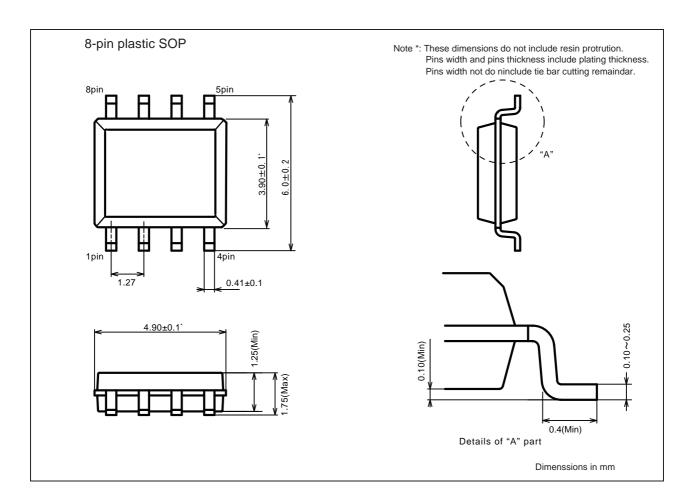

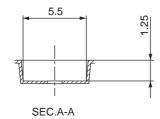

### ■ PACKAGE DIMENSION

| 8-pin plastic SOP | Lead pitch                     | 1.27 mm       |

|-------------------|--------------------------------|---------------|

|                   | Package width × package length | 3.9 mm×4.9 mm |

|                   | Lead shape                     | Gullwing      |

|                   | Sealing method                 | Plastic mold  |

|                   | Mounting heigth                | 1.75 mm MAX   |

|                   |                                |               |

|                   |                                |               |

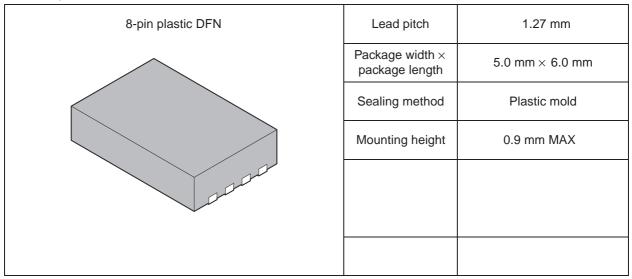

### (Continued)

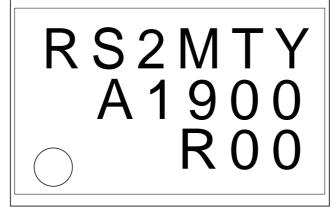

### ■ MARKING (Example)

[MB85RS2MTYPNF-GS-AWE2] [MB85RS2MTYPNF-GS-AWERE2]

[8-pin plastic SOP 150mi]

RS2MTY: Product name

A1900: A(CS code) + 1900(Year and Week code)

R00: Trace code

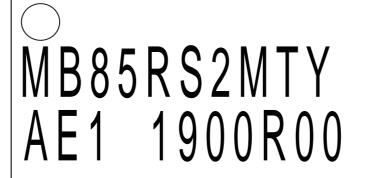

[MB85RS2MTYPN-GS-AWEWE1]

[8-pin plastic DFN 5mm × 6mm]

MB85RS2MTY: Product name

AE1: A(CS code) + E1(Environmental code)

1900R00: 1900(Year and Week code) + R00(Trace code)

#### **■ PACKING INFORMATION**

#### 1. Tube

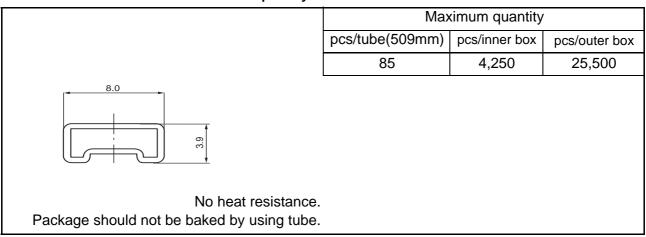

#### 1.1 Tube Dimensions

• Tube/stopper shape (example)

• Tube cross-sections and Maximum quantity

(Dimensions in mm)

• Direction of index in tube

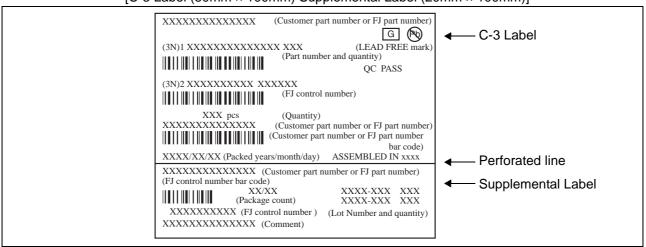

#### 1.2 Product label indicators (example)

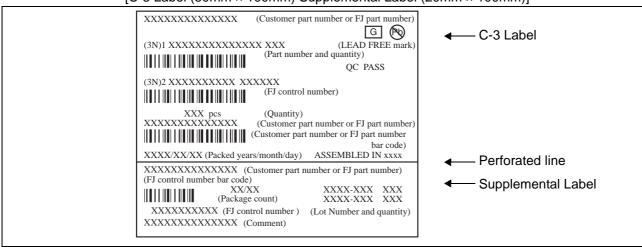

Label I: Label on Inner box/Moisture Barrier Bag/ (It sticks it on the reel for the emboss taping) [C-3 Label (50mm × 100mm) Supplemental Label (20mm × 100mm)]

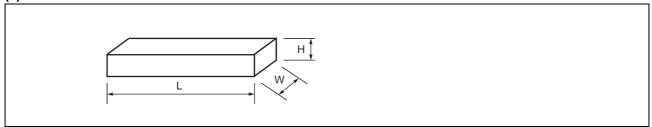

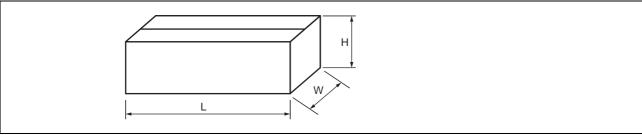

#### 1.3 Dimensions for Containers

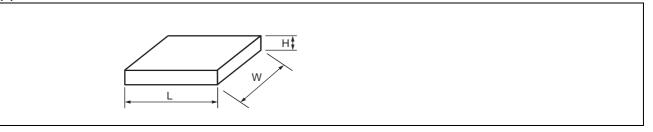

### (1) Dimensions for inner box

| L   | W   | Н  |

|-----|-----|----|

| 549 | 125 | 81 |

(Dimensions in mm)

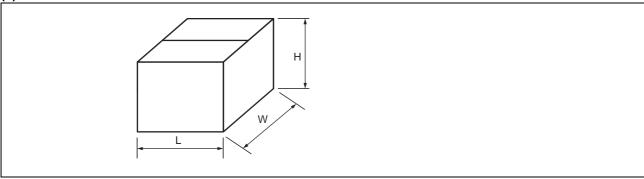

### (2) Dimensions for outer box

| L   | W   | Н   |

|-----|-----|-----|

| 567 | 272 | 269 |

(Dimensions in mm)

### 2. Emboss Tape

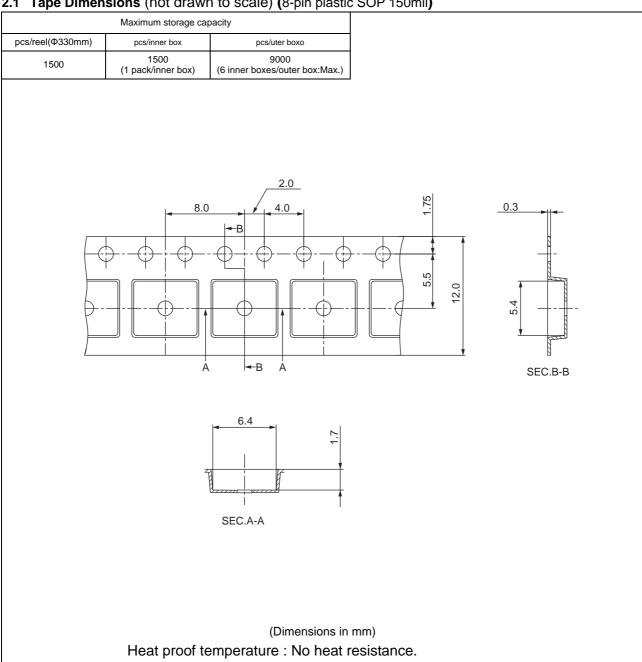

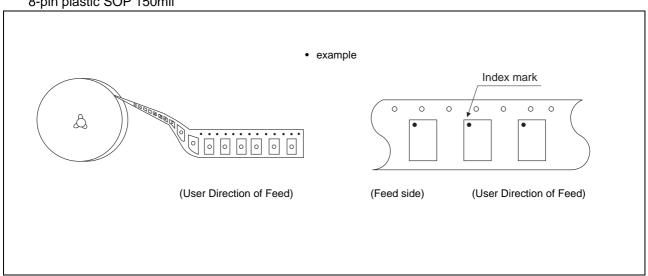

### 2.1 Tape Dimensions (not drawn to scale) (8-pin plastic SOP 150mil)

Package should not be baked by using tape and reel.

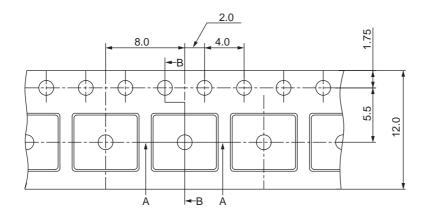

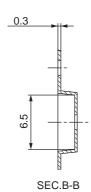

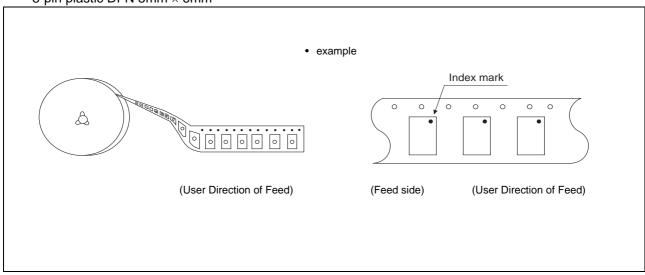

### 2.2 Tape Dimensions (not drawn to scale)(8-pin plastic DFN 5mm × 6mm)

| Maximum storage capacity                     |                            |                                       |

|----------------------------------------------|----------------------------|---------------------------------------|

| pcs/reel(Φ330mm) pcs/inner box pcs/uter boxo |                            | pcs/uter boxo                         |

| 1500                                         | 1500<br>(1 pack/inner box) | 9000<br>(6 inner boxes/outer box:Max) |

(Dimensions in mm)

Heat proof temperature : No heat resistance.

Package should not be baked by using tape and

reel.

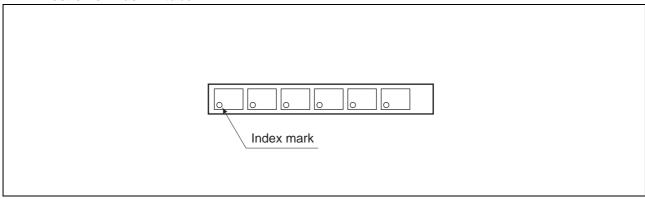

#### 2.3 IC orientation

8-pin plastic SOP 150mil

8-pin plastic DFN 5mm  $\times$  6mm

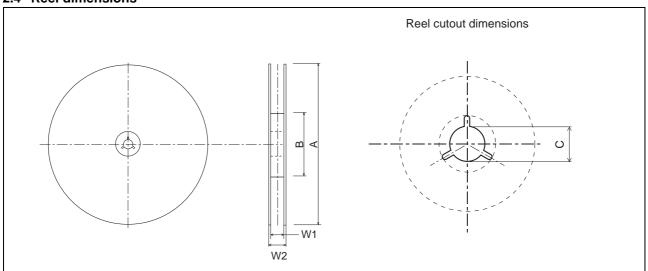

#### 2.4 Reel dimensions

Dimensions in mm

| Α   | В   | С  | W1   | W2   |

|-----|-----|----|------|------|

| 300 | 100 | 13 | 13.5 | 17.5 |

#### 2.5 Product label indicators (example)

Label I: Label on Inner box/Moisture Barrier Bag/ (It sticks it on the reel for the emboss taping) [C-3 Label (50mm × 100mm) Supplemental Label (20mm × 100mm)]

Label II: Moisture Barrier Bag (It sticks it on the Aluminum laminated bag) [MSL Label (100mm × 70mm)]

#### 2.6 Dimensions for Containers

### (1) Dimensions for inner box

| Tape width | L   | W   | Н  |

|------------|-----|-----|----|

| 12         | 350 | 335 | 35 |

(Dimensions in mm)

#### (2) Dimensions for outer box

| L   | W   | Н   |

|-----|-----|-----|

| 384 | 368 | 225 |

(Dimensions in mm)

### ■ MAJOR CHANGES IN THIS EDITION

A change on a page is indicated by a vertical line drawn left side of that page.

| Page           | Section                              | Change Results                             |

|----------------|--------------------------------------|--------------------------------------------|

| 1,             | -FEATURES                            | Specifications are improved as follows.    |

| Data Retention | 10 years (+85 °C)> 40 years (+85 °C) |                                            |

|                |                                      | 2.75 years (+105 °C)> 10 years (+105 °C)   |

|                |                                      | 0.85 years (+125 °C)> 3.38 years (+125 °C) |

| 2              | ■PIN ASSIGNMENT                      | Pin name is revised.                       |

| 2              | ■PIN FUNCTIONAL DESCRIPTIONS         | 7 DNU> 7 NC                                |

#### FUJITSU SEMICONDUCTOR MEMORY SOLUTION LIMITED

Shin-Yokohama TECH Building, 3-9-1 Shin-Yokohama, Kohoku-ku, Yokohama, Kanagawa 222-0033, Japan https://www.fujitsu.com/jp/fsm/en/

#### All Rights Reserved.

FUJITSU SEMICONDUCTOR MEMORY SOLUTION LIMITED, its subsidiaries and affiliates (collectively, "FUJITSU SEMICONDUCTOR MEMORY SOLUTION") reserves the right to make changes to the information contained in this document without notice. Please contact your FUJITSU SEMICONDUCTOR MEMORY SOLUTION sales representatives before order of FUJITSU SEMICONDUCTOR MEMORY SOLUTION device.

Information contained in this document, such as descriptions of function and application circuit examples is presented solely for reference to examples of operations and uses of FUJITSU SEMICONDUCTOR MEMORY SOLUTION device. FUJITSU SEMICONDUCTOR MEMORY SOLUTION disclaims any and all warranties of any kind, whether express or implied, related to such information, including, without limitation, quality, accuracy, performance, proper operation of the device or non-infringement. If you develop equipment or product incorporating the FUJITSU SEMICONDUCTOR MEMORY SOLUTION device based on such information, you must assume any responsibility or liability arising out of or in connection with such information or any use thereof. FUJITSU SEMICONDUCTOR MEMORY SOLUTION assumes no responsibility or liability for any damages whatsoever arising out of or in connection with such information or any use thereof.

Nothing contained in this document shall be construed as granting or conferring any right under any patents, copyrights, or any other intellectual property rights of FUJITSU SEMICONDUCTOR MEMORY SOLUTION or any third party by license or otherwise, express or implied. FUJITSU SEMICONDUCTOR MEMORY SOLUTION assumes no responsibility or liability for any infringement of any intellectual property rights or other rights of third parties resulting from or in connection with the information contained herein or use thereof.

The products described in this document are designed, developed and manufactured as contemplated for general use including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high levels of safety is secured, could lead directly to death, personal injury, severe physical damage or other loss (including, without limitation, use in nuclear facility, aircraft flight control system, air traffic control system, mass transport control system, medical life support system and military application), or (2) for use requiring extremely high level of reliability (including, without limitation, submersible repeater and artificial satellite). FUJITSU SEMICONDUCTOR MEMORY SOLUTION shall not be liable for you and/or any third party for any claims or damages arising out of or in connection with above-mentioned uses of the products.

Any semiconductor devices fail or malfunction with above-mentioned uses of the products.

Any semiconductor devices fail or malfunction with some probability. You are responsible for providing adequate designs and safeguards against injury, damage or loss from such failures or malfunctions, by incorporating safety design measures into your facility, equipments and products such as redundancy, fire protection, and prevention of overcurrent levels and other abnormal operating conditions.

The products and technical information described in this document are subject to the Foreign Exchange and Foreign Trade Control Law of Japan, and may be subject to export or import laws or regulations in U.S. or other countries. You are responsible for ensuring compliance with such laws and regulations relating to export or re-export of the products and technical information described herein. All company names, brand names and trademarks herein are property of their respective owners.

Edited: Marketing Division