# **Bias Power Supply for TFT LCD Panels**

#### **Features**

- 2.5V to 5.5V Input Supply Range

- Active-High Enable Control

- 1.2MHz Current-Mode Boost Regulator

- Fast Transient Response to Pulse Load

- ±1% Accurate Output Voltage

- Built-In 20V/1.8A, 0.7Ω N-Channel MOSFET

- High Efficiency up to 90%

- Over-Current Protection

- Output Under-Voltage Protection

- High-Performance Operational Amplifier

- ±150mA Output Short-Circuit Current

- 12V/µs Slew Rate

- 12MHz, -3dB Bandwidth

- Rail-to-Rail Input and Output

- 600kHz Negative Charge Pump Driver for V<sub>GL</sub>

- 600kHz Positive Charge Pump Driver for V<sub>GH</sub>

- Power-On Sequence Control

- Thermal-Overload Protection

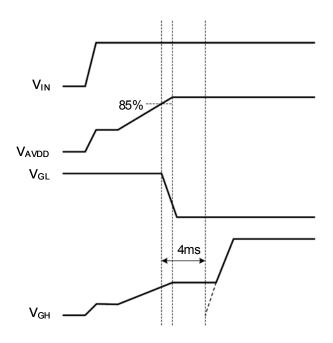

- TQFN3X3-16 Package

#### **Applications**

- **■** Photo Frame

- GPS

- UMPC

### **General Description**

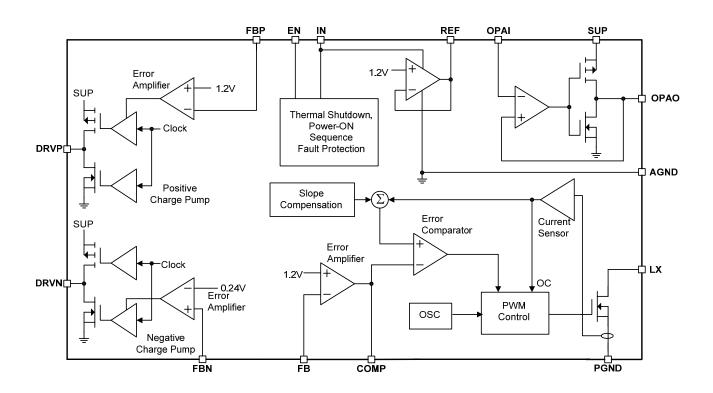

The AT5520A includes a high-performance boost regulator, a  $V_{\text{COM}}$  buffer (unity gain OPA), a  $V_{\text{GH}}$  charge pump driver, and a VGL charge pump driver for active-matrix thin-film transistor (TFT) liquid-crystal displays (LCDs).

The boost converter provides the regulated supply voltage for the panel source driver ICs. The converter is a high switching frequency (1.2MHz) current mode

regulator with an integrated 20V N-Channel  $0.7\Omega$  MOSFET that allows the use of ultra-small inductors and ceramic capacitors. It provides fast transient response to pulsed loading while achieving efficiency over 90%. The device can produce output voltage as high as 18V from an input as low as 2.8V.

The  $V_{\text{COM}}$  buffer can drive the LCD  $V_{\text{COM}}$  voltage that features high short-circuit current (150mA), fast slew rate (12V/µs), wide bandwidth (12MHz) and rail-to-rail input/output.

A positive and a negative charge-pump driver provide adjustable regulated output voltages  $V_{GH}$  and  $V_{GL}$  to bias the TFT. Both the charge-pump driver operate with 600kHz switching frequency.

The AT5520A includes internal power-up sequencing, over/under voltage protections of the boost converter, and over temperature protection to ensure in safe operating.

The AT5520A are available in a 16-pin 3X3 TQFN packages.

### **Ordering Information**

| ORDER       | MARKING | TEMP.          | PACKAGE    |  |

|-------------|---------|----------------|------------|--|

| NUMBER      |         | RANGE          | (Green)    |  |

| AT5520AR41U | 5520A   | -40°C to +85°C | TQFN3X3-16 |  |

Note: R4:TQFN3X3-16 1: Bonding Code U: Tape & Reel

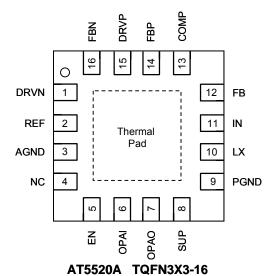

## **Pin Configuration**

Note: Recommend connecting the Thermal Pad to the Ground for excellent power dissipation.

| Absolute Maximum Rating                                                                                                                                                                                                                                                                           |                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| IN to GND0.3V to 7V LX to GND0.3V to 20V PGND to GND0.3V to +0.3V SUP to GND0.3V to 18V OPAO, OPAI, DRVP, DRVN to GND0.3V to (SUP + 0.3V) EN, REF, FB, FBP, FBN, COMP, FREQ to GND0.3V to (V <sub>IN</sub> + 0.3V) Thermal Resistance Junction to Ambient, (θ <sub>JA</sub> )* TQFN3X3-16 103°C/W | $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |

<sup>\*</sup> Please refer to "EV Board PCB Layout Section".

Stress beyond those listed under "Absolute Maximum Rating" may cause permanent damage to the device.

#### **Electrical Characteristics**

$V_{IN}$  =3.3V,  $V_{AVDD}$ =8.5V,  $T_A$  =25°C.

The device is not guaranteed to function outside its operating conditions. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified.

| PARAMETER                                       | METER SYMBOL CONDITION |                                        | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------------------|------------------------|----------------------------------------|-------|------|-------|-------|

| Input Supply Voltage                            | V <sub>IN</sub>        |                                        | 2.5   |      | 5.5   | V     |

| // Under Voltage Leekout Threshold              | $V_{UVLO}$             | V <sub>IN</sub> Rising                 | 1.8   | 2.0  | 2.2   | V     |

| V <sub>IN</sub> Under Voltage Lockout Threshold |                        | Hysteresis                             |       | 0.1  |       | V     |

| V <sub>IN</sub> Quiescent Current               | ,                      | V <sub>FB</sub> =1.3V, LX no switching |       | 0.3  | 0.6   | mA    |

| VIN Quiescent Current                           | IQ                     | V <sub>FB</sub> =1.1V, LX switching    |       | 0.8  | 2     | mA    |

| V <sub>IN</sub> Shut Down Current               | $I_{QSD}$              |                                        |       |      | 1     | μΑ    |

| EN Threshold                                    | V <sub>IH</sub>        |                                        |       |      | 2     | - V   |

| EN THESHOID                                     | V <sub>IL</sub>        |                                        | 0.8   |      |       |       |

| Reference Voltage                               | $V_{REF}$              |                                        | 1.176 | 1.2  | 1.224 | V     |

| Thermal Shutdown Temperature                    | T <sub>SD</sub>        |                                        |       | 150  |       | °C    |

| Thermal Shutdown Hysteresis                     | $\DeltaT_{SD}$         |                                        |       | 25   |       | °C    |

| Main Step-Up Regulator                          |                        |                                        |       |      |       |       |

| Operation Frequency                             | f <sub>OSC</sub>       |                                        |       | 1200 |       | kHz   |

| Maximum Duty Cycle                              |                        |                                        | 85    | 90   |       | %     |

| Feedback Voltage                                | $V_{FB}$               | No load                                | 1.188 | 1.2  | 1.212 | V     |

| FB Input Bias Current                           |                        | V <sub>FB</sub> =1.5V                  | -40   |      | +40   | nA    |

| Transconductance of Error Amplifier             | Gm                     |                                        |       | 70   |       | μA/V  |

| Voltage Gain of Error Amplifier                 | $A_{V}$                |                                        |       | 700  |       | V/V   |

| Feedback Voltage Line Regulation                |                        | V <sub>IN</sub> =2.5 to 5.5V           |       | 0.15 | 0.25  | %/V   |

| LX ON-Resistance                                | R <sub>LX(ON)</sub>    |                                        |       | 0.7  | 1     | Ω     |

| Current Sense Transconductance                  |                        |                                        |       | 4    |       | A/V   |

| Current Limit                                   | I <sub>LIM</sub>       |                                        |       | 1.8  |       | Α     |

| N-MOSFET Leakage Current                        |                        | V <sub>LX</sub> =20V                   |       | 0.1  | 10    | μΑ    |

## **Electrical Characteristics** (continued)

| PARAMETER                  | SYMBOL            | CONDITION                                     |                                               | MIN      | TYP       | MAX   | UNITS |

|----------------------------|-------------------|-----------------------------------------------|-----------------------------------------------|----------|-----------|-------|-------|

| VCOM Buffer                |                   |                                               |                                               |          |           |       |       |

| Supply Voltage Range       | $V_{SUP}$         |                                               |                                               | AVDD     |           | 16    | V     |

| Supply Current             | I <sub>OP</sub>   |                                               |                                               |          | 0.6       | 1.2   | mA    |

| Input Offset Voltage       | Vos               | V <sub>OPAO</sub> = AVDD/2, T                 | <sub>A</sub> = 25°C                           | -15      | 0         | 15    | mV    |

| Input Bias Current         | I <sub>BIAS</sub> |                                               |                                               | -100     |           | 100   | nA    |

| Output Voltage Swing High  | V                 | I <sub>OUT</sub> = 100μA                      |                                               | AVDD-20  | AVDD-5    |       | mV    |

| Output Voltage Swing High  | V <sub>OH</sub>   | $I_{OUT} = 5mA$                               |                                               | AVDD-0.2 | AVDD-0.15 |       | V     |

| Output Valtage Suing Law   | V                 | $I_{OUT} = -100 \mu A$                        |                                               |          | 5         | 20    | mV    |

| Output Voltage Swing Low   | $V_{OL}$          | $I_{OUT} = -5mA$                              |                                               |          | 150       | 200   | mV    |

| Chart Cinavit Commant      |                   | 4- AVDD/0                                     | Source                                        | 100      | 150       |       |       |

| Short-Circuit Current      |                   | to AVDD/2                                     | Sink                                          | 100      | 150       |       | mA    |

| -3dB Bandwidth             | F <sub>3dB</sub>  |                                               |                                               |          | 12        |       | MHz   |

| Gain Bandwidth Product     | GBW               |                                               |                                               |          | 8         |       | MHz   |

| Slew Rate                  | SR                |                                               |                                               | 8        | 12        |       | V/µs  |

| Gate-High Regulator        |                   |                                               |                                               |          |           | _     |       |

| Feedback Reference Voltage | $V_{FBP}$         | No load                                       |                                               | 1.176    | 1.2       | 1.224 | V     |

| DRVP Switch On-Resistance  | R <sub>ON_P</sub> | \/ -10\/  -20                                 | V <sub>SUP</sub> =10V,I <sub>DRVP</sub> =20mA |          | 50        |       | 0     |

| DRVP Switch On-Resistance  | R <sub>on_N</sub> | V <sub>SUP</sub> =1UV,I <sub>DRVP</sub> =20   | JMA                                           |          | 20        |       | Ω     |

| Switching Frequency        | f <sub>SW</sub>   |                                               |                                               |          | 600       |       | kHz   |

| Gate-Low Regulator         |                   |                                               |                                               |          | _         | -     | _     |

| Feedback Reference Voltage | $V_{FBN}$         | No load                                       |                                               | 0.21     | 0.24      | 0.27  | V     |

| DRVN Switch On-Resistance  | R <sub>ON_P</sub> | V <sub>SUP</sub> =10V,I <sub>DRVN</sub> =20mA |                                               |          | 30        |       | Ω     |

| DRVN Switch On-Resistance  | R <sub>on_N</sub> |                                               |                                               |          | 50        |       |       |

| Switching Frequency        | $f_{SW}$          |                                               |                                               |          | 600       |       | kHz   |

| Fault Detector             |                   |                                               |                                               |          | _         | -     | _     |

| FB Fault Trip Level        |                   | V <sub>FB</sub> Falling                       |                                               |          | 0.95      |       | V     |

| FBN Fault Trip Level       |                   | V <sub>FBN</sub> Rising                       |                                               |          | 0.42      |       | V     |

| FBP Fault Trip Level       |                   | V <sub>FBP</sub> Falling                      |                                               |          | 0.95      |       | V     |

| Fault Delay (UVP Delay)    |                   |                                               |                                               |          | 100       |       | ms    |

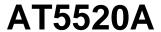

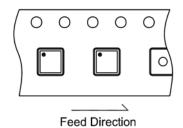

## **Minimum Footprint PCB Layout Section**

#### **TQFN3X3-16**

## **Pin Description**

| PIN         | NAME | FUNCTION                                                                                                                                                                                                                               |

|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | DRVN | Driver output pin of the negative charge pump.                                                                                                                                                                                         |

| 2           | REF  | Reference bypass terminal. Bypass REF to AGND with a minimum of 0.22µF close to this pin.                                                                                                                                              |

| 3           | AGND | Analog Ground                                                                                                                                                                                                                          |

| 4           | NC   | No Connection                                                                                                                                                                                                                          |

| 5           | EN   | Active-High Enable Control Input                                                                                                                                                                                                       |

| 6           | OPAI | VCOM buffer input pin. If OP function is not used, connect this pin to AGND.                                                                                                                                                           |

| 7           | OPAO | VCOM buffer output pin. If OP function is not used, make sure this pin floating.                                                                                                                                                       |

| 8           | SUP  | VCOM buffer, VGH, and VGL charge pump power input. Positive supply rail for the operational amplifiers.                                                                                                                                |

| 9           | PGND | Power Ground.                                                                                                                                                                                                                          |

| 10          | LX   | Switching pin. Drain of the internal power NMOS for the main step-up regulator                                                                                                                                                         |

| 11          | IN   | Supply Input.                                                                                                                                                                                                                          |

| 12          | FB   | Main Boost Regulator Feedback Input. FB regulates to 1.2V nominal. Connect FB to the center of a resistive voltage-divider between the main output and the analog ground (AGND). Place the resistive voltage-divider close to the pin. |

| 13          | COMP | Compensation error amplifier pin.                                                                                                                                                                                                      |

| 14          | FBP  | Feedback pin of positive charge pump. Regulates to 1.2V nominal.                                                                                                                                                                       |

| 15          | DRVP | Driver output pin of the positive charge pump.                                                                                                                                                                                         |

| 16          | FBN  | Feedback pin of negative charge pump. Regulates to 0.24V nominal.                                                                                                                                                                      |

| Thermal Pad |      | Exposed pad should be soldered to PCB board and connected to AGND                                                                                                                                                                      |

### **Block Diagram**

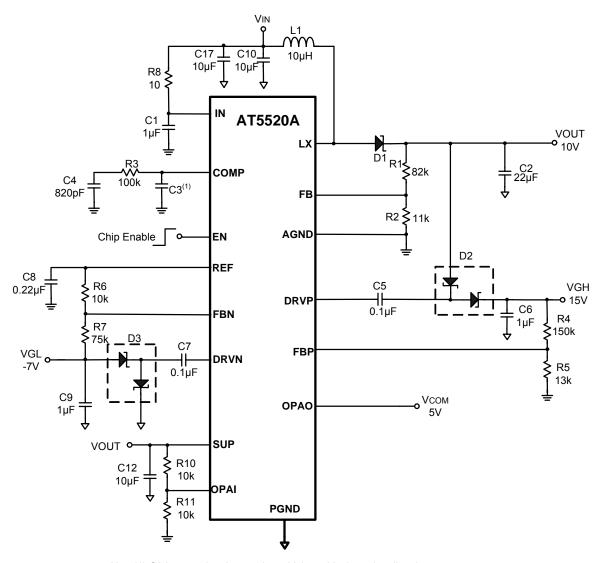

## **Typical Application Circuits**

Note(1):C3 is an optional captacitor which avoids the noise disturbance

### **Application Information**

The AT5520A contains a high performance current mode boost regulator, a gate-on charge pump driver and a gate-off charge pump driver. It also includes of a high- current rail-to rail operation amplifier. The following content contains the detailed description and the information of the component selection.

#### **Boost Regulator**

The boost regulator is a high efficiency current-mode PWM architecture with 1.2MHz operation frequency. It performs fast transient responses to generate source driver supplies for TFT LCD display. The high operation frequency allows smaller components to minimize the thickness of LCD panel. To regulate the output voltage is to set resistive voltage-divider sensing at FB pin. The error amplifier varies the COMP voltage by sensing the FB pin to regulate the output voltage. For better stability, the slope compensation signal that combined with the current-sense signal will be compared with the COMP voltage to determine the current trip point and duty cycle.

#### **Inductor Selection**

A  $4.7\mu H$  or  $10\mu H$  inductor is recommended for small ripple applications. Small form factor and high efficiency are the major concerns for most AT5520A applications. Inductor with low core losses and small DCR (cooper wire resistance) are good choice for AT5520A applications.

#### **Capacitor Selection**

The small size of ceramic capacitors makes them suitable for AT5520A applications. X5R and X7R types are recommended because they retain their capacitance over wider voltage and temperature ranges than other types such as Y5V or Z5U.

#### **Diode Selection**

Schottky diodes, with their low forward voltage drop and fast reverse recovery, are the ideal choices for AT5520A applications. The forward voltage drop of a Schottky diode represents the conduction losses in the diode, while the diode capacitance (CT or CD) represents the switching losses. For diode selection, both forward voltage drop and diode capacitance need to be considered. Schottky diodes with higher current ratings usually have lower forward voltage drop and larger diode capacitance, which can cause significant switching losses of the AT5520A. A Schottky diode rated at 2A is sufficient for most AT5520A applications.

#### **Output Voltage**

The regulated output voltage is calculated by the following formula:

$$V_{\text{OUT}} = 1.2V \times \left(1 + \frac{R1}{R2}\right)$$

The recommended value for R2 should be up to  $100k\Omega$  without some sacrificing. Place the resistor-divider as close as possible to the chip can reduce noise sensitivity.

#### **Loop Compensation**

The voltage feedback loop can be compensated with an external compensation network consisted of R3, C4 as Typical Application Circuit. Choose R3 to set high frequency integrator gain for fast transient response and C4 to set the integrator zero to maintain loop stability. For typical application  $V_{\text{IN}}$ =3.3V,  $V_{\text{OUT}}$ =8.5V,  $C_{\text{OUT}}$ =22µF  $\times$  2, L=10µH, the recommended value for compensation is as below:

R3=100k $\Omega$ , C4=820pF.

#### **Over Current Protection**

The AT5520A main boost converter has the function of peak current protection to limit peak inductor current. It prevents large current damaging the inductor and diode. During the ON-time, once the inductor current exceeds the current limit, the internal LX switch turns off immediately and shortens the duty cycle. Therefore, the output voltage drops if the over-current condition occurs. Actual current limit is always larger than the nominal value because of the internal circuit delay.

#### **Over Temperature Protection**

The AT5520A main boost converter has thermal protection function to prevent the excessive power dissipation from overheating. When the junction temperature exceeds 150°C, it will shut down the device. Once the device cools down by approximately 25°C, it will start to operate normally.

#### FB under voltage Protection

If the AT5520A boost regulator feed-back voltage is under 0.1V, the internal NMOS switch turns off immediately. And the AT5520A restarts up until FB voltage is higher than 0.1V.

#### **Fault protection**

During steady-state operation, if the output of the boost converter or any of the charge pump outputs does not exceed its respective fault-detection threshold, the AT5520A activates an internal fault timer. If any condition or combination of conditions indicates a continuous fault for the fault-timer duration (100ms typ), the AT5520A sets the fault latch to shut down all the outputs except the reference. Once the fault condition is removed, cycle the input voltage (below the UVLO falling threshold) or EN pin toggled to clear the fault latch and reactivate the device.

#### **Voltage Reference**

The voltage at REF pin is nominally 1.2V, which can deliver up to  $100\mu A$  with good regulation. Connect a  $0.22\mu F$  bypass capacitor between REF and AGND.

#### **Positive Charge Pump**

Typical Application Circuit shows an extract of the positive charge-pump driver circuit. During the first half-cycle, the NMOS turns on and charges C5 to the  $V_{\text{OUT}}$  voltage. During the second half-cycle, the NMOS turns off and the PMOS turns on to charge the DRVP pin up to the SUP voltage. The current of PMOS is controlled by error amplifier to regulate the output voltage  $V_{\text{GH}}$ . At this cycle, C5 is connected in parallel with C6 and pumps the maximum output voltage to  $(V_{\text{SUP}}+V_{\text{OUT}})$ .

The VGH voltage is set by

$$V_{GH} = 1.2V \times \left(1 + \frac{R4}{R5}\right)$$

#### **Negative Charge Pump**

During the first half-cycle, the PMOS turns on and charges C7 to the SUP voltage. During the second half-cycle, the PMOS turns off and the NMOS turns on to discharge the DRVN pin to the ground. The current of NMOS is controlled by error amplifier to regulate the output voltage  $V_{\text{GL}}.$  At this cycle, C7 is connected in parallel with C9 and pumps the maximum negative output voltage to -SUP.

The V<sub>GL</sub> is set by

$$V_{\text{GL}} = 0.24V \times \left(1 + \frac{R7}{R6}\right) - 1.2V \times \left(\frac{R7}{R6}\right)$$

#### **Operational Amplifier**

The function of the operational amplifier is to drive the LCD backplane  $V_{\text{COM}}$ . The operational amplifier features  $\pm 150 \text{mA}$  output short circuit current,  $12 \text{V/}\mu\text{s}$  slew rate, and 12 MHz bandwidth.

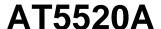

#### **Power-Up Sequence**

The AT5520A employs soft-start circuitry to reduce supply inrush current during start up conditions. When the device exits under-voltage lockout, the soft-start circuitry will slowly ramp up the output voltage.

Once the voltage on IN exceeds approximately 2V, the reference turns on. With a  $0.22\mu F$  REF bypass capacitor, the reference reaches its regulation voltage of 1.2V. When the reference voltage exceeds 0.8V, the ICs enable the boost regulator. Once the FB voltage is above 1V, the gate-off charge pump driver is enabled immediately, and gate-on charge pump driver starts up after 4ms (TYP) delay time.

### **Timing Diagram**

## Package Information

TQFN3X3-16 Package

| Oh.l.  | DIMENSION IN MM |      |      | DI         | Н      |        |  |

|--------|-----------------|------|------|------------|--------|--------|--|

| Symble | MIN.            | NOM. | MAX. | MIN.       | NOM.   | MAX.   |  |

| Α      | 0.70            | 0.75 | 0.80 | 0.0276     | 0.0295 | 0.0315 |  |

| A1     | 0.00            |      | 0.05 | 0.0000     |        | 0.0020 |  |

| A2     | 0.19            | 0.20 | 0.21 | 0.0075     | 0.0079 | 0.0083 |  |

| D      | 2.95            | 3.00 | 3.05 | 0.1161     | 0.1181 | 0.1201 |  |

| E      | 2.95            | 3.00 | 3.05 | 0.1161     | 0.1181 | 0.1201 |  |

| D1     | 1.50            | 1.60 | 1.75 | 0.0591     | 0.0630 | 0.0689 |  |

| E1     | 1.50            | 1.60 | 1.75 | 0.0591     | 0.0630 | 0.0689 |  |

| b      | 0.18            | 0.25 | 0.30 | 0.0071     | 0.0098 | 0.0118 |  |

| е      | 0.50 BSC        |      |      | 0.0197 BSC |        |        |  |

| L      | 0.35            | 0.40 | 0.45 | 0.0138     | 0.0157 | 0.0177 |  |

## **Taping Specification**

| PACKAGE    | Q'Y/REEL |

|------------|----------|

| TQFN3X3-16 | 3,000 ea |

GMT Inc. does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and GMT Inc. reserves the right at any time without notice to change said circuitry and specifications.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LCD Drivers category:

Click to view products by Global Mixed-mode manufacturer:

Other Similar products are found below:

PCF8576CU/2/F2,026 LC75836WH-E CD4056BE LC75829PW-H LC79430KNE-E LC79431KNE-E FAN7317BMX S1D15721D01B000 ICL7106CM44 ICL7106CPL HT1621DM/TR TM1621C(TA1901-A) GN1621DT TM1723(TA2003B) BL55072A GN1623L100 GN1625L100 GN1621S28 GNV1792T48 HT1621M/TR HG1622-LQ44 HT1621BRSZ ML9042-53CVWA-5016 SSP97950AFV SSP55080AKV SSP55080AKV SSP55080AKV SSP97950AKV TPS65132WRVCT BU97501KV-E2 BU9795AFV-E2 BU9799KV-E2 BU9728AKV-E2 TPS65132B2YFFR R1293K241A-E2 BU9795AFV-LBE2 TPS65132A0YFFR PCA85134H/Q900/1,1 BU9795AKV-E2 BU9796AMUV-E2 GN1622B 34801000 BU97510CKV-ME2 BU97520AKV-ME2 BU97550KV-ME2 BU9796AFS-E2 BU97981KV-E2 HG1621BM/TR HT1623 HT1621BRQZ44 AIP1723