165-Bump BGA Commercial Temp Industrial Temp

# 36Mb SigmaDDR-II+<sup>TM</sup> Burst of 2 SRAM

450 MHz–300 MHz 1.8 V V<sub>DD</sub> 1.8 V or 1.5 V I/O

### Features

- 2.0 Clock Latency

- Simultaneous Read and Write SigmaDDR<sup>TM</sup> Interface

- Common I/O bus

- JEDEC-standard pinout and package

- Double Data Rate interface

- Byte Write controls sampled at data-in time

- Burst of 2 Read and Write

- On-Die Termination (ODT) on Data (D), Byte Write ( $\overline{BW}),$  and Clock (K,  $\overline{K})$  inputs

- 1.8 V +100/–100 mV core power supply

- 1.5 V or 1.8 V HSTL Interface

- Pipelined read operation with self-timed Late Write

- Fully coherent read and write pipelines

- ZQ pin for programmable output drive strength

- Data Valid pin (QVLD) Support

- IEEE 1149.1 JTAG-compliant Boundary Scan

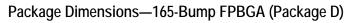

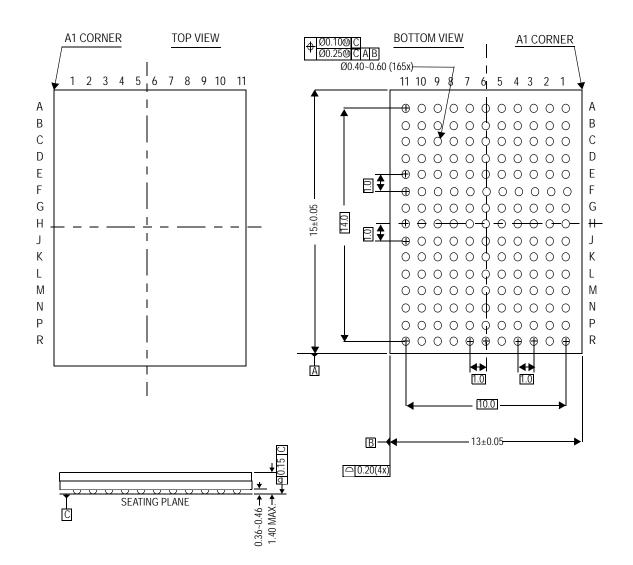

- 165-bump, 13 mm x 15 mm, 1 mm bump pitch BGA package

- RoHS-compliant 165-bump BGA package available

# SigmaDDR<sup>™</sup> Family Overview

The GS8342T07/10/19/37BD are built in compliance with the SigmaDDR-II+ SRAM pinout standard for Common I/O synchronous SRAMs. They are 37,748,736 (36Mb) SRAMs.

The GS8342T07/10/19/37BD SigmaDDR-II+ SRAMs are just one element in a family of low power, low voltage HSTL I/O SRAMs designed to operate at the speeds needed to implement economical high performance networking systems.

# **Clocking and Addressing Schemes**

The GS8342T07/10/19/37BD SigmaDDR-II+ SRAMs are synchronous devices. They employ two input register clock inputs, K and  $\overline{K}$ . K and  $\overline{K}$  are independent single-ended clock inputs, not differential inputs to a single differential clock input buffer.

Each internal read and write operation in a SigmaDDR-II+ B2 RAM is two times wider than the device I/O bus. An input data bus de-multiplexer is used to accumulate incoming data before it is simultaneously written to the memory array. An output data multiplexer is used to capture the data produced from a single memory array read and then route it to the appropriate output drivers as needed. Therefore the address field of a SigmaDDR-II+ B2 RAM is always one address pin less than the advertised index depth (e.g., the 4M x 8 has a 2M addressable index).

### Parameter Synopsis

|       | -450    | -400    | -350    | -333    | -300    |

|-------|---------|---------|---------|---------|---------|

| tKHKH | 2.22 ns | 2.5 ns  | 2.86 ns | 3.0 ns  | 3.3 ns  |

| tKHQV | 0.45 ns |

| 4M x 8 Sigr | naDDR-II+ SRAM- | -Top View |

|-------------|-----------------|-----------|

|-------------|-----------------|-----------|

| _ | 1    | 2                | 3                | 4                | 5                | 6               | 7                | 8                | 9                | 10               | 11  |

|---|------|------------------|------------------|------------------|------------------|-----------------|------------------|------------------|------------------|------------------|-----|

| A | CO   | NC/SA<br>(72Mb)  | SA               | R/W              | NW1              | ĸ               | NC/SA<br>(144Mb) | LD               | SA               | SA               | CQ  |

| В | NC   | NC               | NC               | SA               | NC/SA<br>(288Mb) | К               | NW0              | SA               | NC               | NC               | DQ3 |

| С | NC   | NC               | NC               | V <sub>SS</sub>  | SA               | SA              | SA               | V <sub>SS</sub>  | NC               | NC               | NC  |

| D | NC   | NC               | NC               | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | NC               | NC               | NC  |

| E | NC   | NC               | DQ4              | V <sub>DDQ</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>DDQ</sub> | NC               | NC               | DQ2 |

| F | NC   | NC               | NC               | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | NC               | NC  |

| G | NC   | NC               | DQ5              | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | NC               | NC  |

| Н | Doff | V <sub>REF</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>REF</sub> | ZQ  |

| J | NC   | NC               | NC               | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | DQ1              | NC  |

| К | NC   | NC               | NC               | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | NC               | NC  |

| L | NC   | DQ6              | NC               | V <sub>DDQ</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>DDQ</sub> | NC               | NC               | DQ0 |

| М | NC   | NC               | NC               | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | NC               | NC               | NC  |

| N | NC   | NC               | NC               | V <sub>SS</sub>  | SA               | SA              | SA               | V <sub>SS</sub>  | NC               | NC               | NC  |

| Р | NC   | NC               | DQ7              | SA               | SA               | QVLD            | SA               | SA               | NC               | NC               | NC  |

| R | TDO  | ТСК              | SA               | SA               | SA               | ODT             | SA               | SA               | SA               | TMS              | TDI |

11 x 15 Bump BGA-13 x 15 mm Body-1 mm Bump Pitch

#### Notes:

1. NW0 controls writes to DQ0:DQ3; NW1 controls writes to DQ4:DQ7.

2. Pins A2, A7, and B5 are the expansion addresses.

| 4M x 9 SigmaDDR-II+ SRAM- | Top View |

|---------------------------|----------|

|---------------------------|----------|

| _ | 1    | 2                | 3                | 4                | 5                | 6               | 7                | 8                | 9                | 10               | 11  |

|---|------|------------------|------------------|------------------|------------------|-----------------|------------------|------------------|------------------|------------------|-----|

| A | CO   | NC/SA<br>(72Mb)  | SA               | R/W              | NC               | ĸ               | NC/SA<br>(144Mb) | LD               | SA               | SA               | CQ  |

| В | NC   | NC               | NC               | SA               | NC/SA<br>(288Mb) | К               | BW0              | SA               | NC               | NC               | DQ4 |

| С | NC   | NC               | NC               | V <sub>SS</sub>  | SA               | SA              | SA               | V <sub>SS</sub>  | NC               | NC               | NC  |

| D | NC   | NC               | NC               | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | NC               | NC               | NC  |

| E | NC   | NC               | DQ5              | V <sub>DDQ</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>DDQ</sub> | NC               | NC               | DQ3 |

| F | NC   | NC               | NC               | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | NC               | NC  |

| G | NC   | NC               | DQ6              | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | NC               | NC  |

| Н | Doff | V <sub>REF</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>REF</sub> | ZQ  |

| J | NC   | NC               | NC               | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | DQ2              | NC  |

| К | NC   | NC               | NC               | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | NC               | NC  |

| L | NC   | DQ7              | NC               | V <sub>DDQ</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>DDQ</sub> | NC               | NC               | DQ1 |

| М | NC   | NC               | NC               | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | NC               | NC               | NC  |

| Ν | NC   | NC               | NC               | V <sub>SS</sub>  | SA               | SA              | SA               | V <sub>SS</sub>  | NC               | NC               | NC  |

| Р | NC   | NC               | DQ8              | SA               | SA               | QVLD            | SA               | SA               | NC               | NC               | DQ0 |

| R | TDO  | ТСК              | SA               | SA               | SA               | ODT             | SA               | SA               | SA               | TMS              | TDI |

11 x 15 Bump BGA-13 x 15 mm Body-1 mm Bump Pitch

#### Notes:

3. BW0 controls writes to DQ0 :DQ8.

4. Pins A2, A7, and B5 are the expansion addresses.

2M x 18 SigmaDDR-II+ SRAM—Top View

| _ | 1    | 2                | 3                | 4                | 5                | 6               | 7                | 8                | 9                | 10               | 11  |

|---|------|------------------|------------------|------------------|------------------|-----------------|------------------|------------------|------------------|------------------|-----|

| A | CO   | NC/SA<br>(72Mb)  | SA               | R/W              | BW1              | ĸ               | NC/SA<br>(144Mb) | LD               | SA               | SA               | CQ  |

| В | NC   | DQ9              | NC               | SA               | NC/SA<br>(288Mb) | К               | BW0              | SA               | NC               | NC               | DQ8 |

| С | NC   | NC               | NC               | V <sub>SS</sub>  | SA               | NC              | SA               | V <sub>SS</sub>  | NC               | DQ7              | NC  |

| D | NC   | NC               | DQ10             | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | NC               | NC               | NC  |

| E | NC   | NC               | DQ11             | V <sub>DDQ</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>DDQ</sub> | NC               | NC               | DQ6 |

| F | NC   | DQ12             | NC               | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | NC               | DQ5 |

| G | NC   | NC               | DQ13             | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | NC               | NC  |

| Н | Doff | V <sub>REF</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>REF</sub> | ZQ  |

| J | NC   | NC               | NC               | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | DQ4              | NC  |

| К | NC   | NC               | DQ14             | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | NC               | NC               | DQ3 |

| L | NC   | DQ15             | NC               | V <sub>DDQ</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>DDQ</sub> | NC               | NC               | DQ2 |

| М | NC   | NC               | NC               | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | NC               | DQ1              | NC  |

| N | NC   | NC               | DQ16             | V <sub>SS</sub>  | SA               | SA              | SA               | V <sub>SS</sub>  | NC               | NC               | NC  |

| Р | NC   | NC               | DQ17             | SA               | SA               | QVLD            | SA               | SA               | NC               | NC               | DQ0 |

| R | TDO  | ТСК              | SA               | SA               | SA               | ODT             | SA               | SA               | SA               | TMS              | TDI |

11 x 15 Bump BGA-13 x 15 mm Body-1 mm Bump Pitch

#### Notes:

1. BW0 controls writes to DQ0:DQ8; BW1 controls writes to DQ9:DQ17

2. Pins A2, A7, and B5 are the expansion addresses.

|   | 1    | 2                | 3                | 4                | 5               | 6               | 7               | 8                | 9                | 10               | 11   |

|---|------|------------------|------------------|------------------|-----------------|-----------------|-----------------|------------------|------------------|------------------|------|

| А | Q    | NC/SA<br>(144Mb) | SA               | R/W              | BW2             | ĸ               | BW1             | LD               | SA               | NC/SA<br>(72Mb)  | CQ   |

| В | NC   | DQ27             | DQ18             | SA               | BW3             | к               | BW0             | SA               | NC<br>(288Mb)    | NC               | DQ8  |

| С | NC   | NC               | DQ28             | V <sub>SS</sub>  | SA              | NC              | SA              | V <sub>SS</sub>  | NC               | DQ17             | DQ7  |

| D | NC   | DQ29             | DQ19             | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub>  | NC               | NC               | DQ16 |

| E | NC   | NC               | DQ20             | V <sub>DDQ</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DDQ</sub> | NC               | DQ15             | DQ6  |

| F | NC   | DQ30             | DQ21             | V <sub>DDQ</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DDQ</sub> | NC               | NC               | DQ5  |

| G | NC   | DQ31             | DQ22             | V <sub>DDQ</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DDQ</sub> | NC               | NC               | DQ14 |

| Н | Doff | V <sub>REF</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>REF</sub> | ZQ   |

| J | NC   | NC               | DQ32             | V <sub>DDQ</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DDQ</sub> | NC               | DQ13             | DQ4  |

| К | NC   | NC               | DQ23             | V <sub>DDQ</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>DDQ</sub> | NC               | DQ12             | DQ3  |

| L | NC   | DQ33             | DQ24             | V <sub>DDQ</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>DDQ</sub> | NC               | NC               | DQ2  |

| М | NC   | NC               | DQ34             | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub>  | NC               | DQ11             | DQ1  |

| Ν | NC   | DQ35             | DQ25             | V <sub>SS</sub>  | SA              | SA              | SA              | V <sub>SS</sub>  | NC               | NC               | DQ10 |

| Р | NC   | NC               | DQ26             | SA               | SA              | QVLD            | SA              | SA               | NC               | DQ9              | DQ0  |

| R | TDO  | ТСК              | SA               | SA               | SA              | ODT             | SA              | SA               | SA               | TMS              | TDI  |

11 x 15 Bump BGA—13 x 15 mm<sup>2</sup> Body—1 mm Bump Pitch

#### Notes:

3. BW0 controls writes to DQ0:DQ8; BW1 controls writes to DQ9:DQ17; BW2 controls writes to DQ18:DQ26; BW3 controls writes to DQ27:DQ35

4. Pins A2, A10, and B9 are the expansion addresses.

# **Pin Description Table**

| Symbol           | Description                     | Туре         | Comments                 |

|------------------|---------------------------------|--------------|--------------------------|

| SA               | Synchronous Address Inputs      | Input        | —                        |

| R/W              | Synchronous Read                | Input        | High: Read<br>Low: Write |

| BW0-BW3          | Synchronous Byte Writes         | Input        | Active Low               |

| NW0-NW1          | Synchronous Nybble Writes       | Input        | Active Low<br>(x8 only)  |

| LD               | Synchronous Load Pin            | Input        | Active Low               |

| К                | Input Clock                     | Input        | Active High              |

| K                | Input Clock                     | Input        | Active Low               |

| TMS              | Test Mode Select                | Input        | —                        |

| TDI              | Test Data Input                 | Input        | _                        |

| ТСК              | Test Clock Input                | Input        | —                        |

| TDO              | Test Data Output                | Output       | —                        |

| V <sub>REF</sub> | HSTL Input Reference Voltage    | Input        | —                        |

| ZQ               | Output Impedance Matching Input | Input        | _                        |

| MCL              | Must Connect Low                | —            | —                        |

| DQ               | Data I/O                        | Input/Output | Three State              |

| Doff             | Disable DLL when low            | Input        | Active Low               |

| CQ               | Output Echo Clock               | Output       | —                        |

| CQ               | Output Echo Clock               | Output       | —                        |

| V <sub>DD</sub>  | Power Supply                    | Supply       | 1.8 V Nominal            |

| V <sub>DDQ</sub> | Isolated Output Buffer Supply   | Supply       | 1.8 V or 1.5 V Nominal   |

| V <sub>SS</sub>  | Power Supply: Ground            | Supply       | _                        |

| QVLD             | Q Valid Output                  | Output       | _                        |

| ODT              | On-Die Termination              | Input        | Active High              |

| NC               | No Connect                      | _            | _                        |

#### Notes:

1. NC = Not Connected to die or any other pin

2. When ZQ pin is directly connected to V<sub>DDQ</sub>, output impedance is set to minimum value and it cannot be connected to ground or left unconnected.

3. K,  $\overline{K}$  cannot be set to V<sub>REF</sub> voltage.

### Background

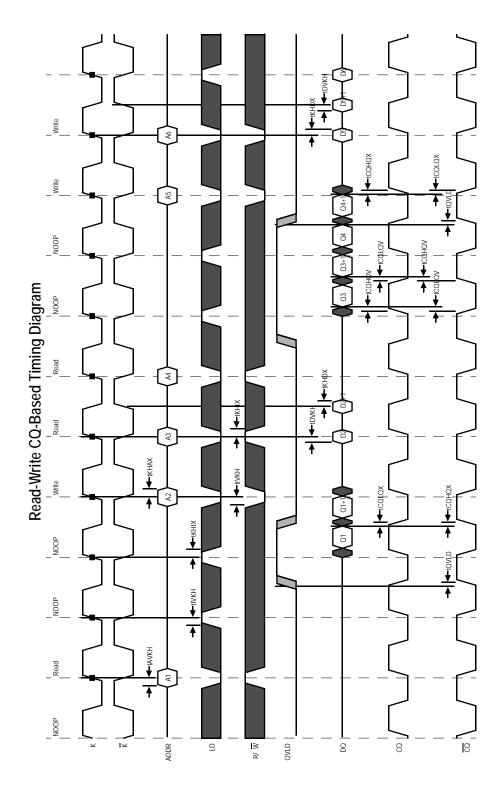

Common I/O SRAMs, from a system architecture point of view, are attractive in read dominated or block transfer applications. Therefore, the SigmaDDR-II+ SRAM interface and truth table are optimized for burst reads and writes. Common I/O SRAMs are unpopular in applications where alternating reads and writes are needed because bus turnaround delays can cut high speed Common I/O SRAM data bandwidth in half.

### **Burst Operations**

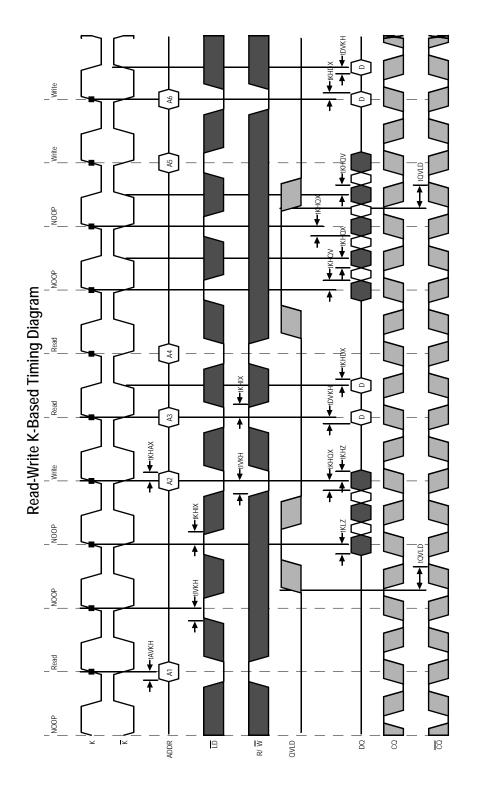

Read and write operations are "Burst" operations. In every case where a read or write command is accepted by the SRAM, it will respond by issuing or accepting two beats of data, executing a data transfer on subsequent rising edges of K and  $\overline{K}$ , as illustrated in the timing diagrams. This means that it is possible to load new addresses every K clock cycle. Addresses can be loaded less often, if intervening deselect cycles are inserted.

### **Deselect Cycles**

Chip Deselect commands are pipelined to the same degree as read commands. This means that if a deselect command is applied to the SRAM on the next cycle after a read command captured by the SRAM, the device will complete the two beat read data transfer and then execute the deselect command, returning the output drivers to High-Z. A high on the LD pin prevents the RAM from loading read or write command inputs and puts the RAM into deselect mode as soon as it completes all outstanding burst transfer operations.

### SigmaDDR-II+ B2 SRAM Read Cycles

The SRAM executes pipelined reads. The status of the Address,  $\overline{\text{LD}}$  and  $R/\overline{W}$  pins are evaluated on the rising edge of K. The read command ( $\overline{\text{LD}}$  low and  $R/\overline{W}$  high) is clocked into the SRAM by a rising edge of K.

### SigmaDDR-II+ B2 SRAM Write Cycles

The status of the Address,  $\overline{\text{LD}}$  and  $\overline{\text{R/W}}$  pins are evaluated on the rising edge of K. The SRAM executes "late write" data transfers. Data in is due at the device inputs on the rising edge of K following the rising edge of K clock used to clock in the write command ( $\overline{\text{LD}}$  and  $\overline{\text{R/W}}$  low) and the write address. To complete the remaining beat of the burst of two write transfer, the SRAM captures data in on the next rising edge of  $\overline{\text{K}}$ , for a total of two transfers per address load.

### **Special Functions**

#### Byte Write and Nybble Write Control

Byte Write Enable pins are sampled at the same time that Data In is sampled. A high on the Byte Write Enable pin associated with a particular byte (e.g.,  $\overline{BW0}$  controls D0–D8 inputs) will inhibit the storage of that particular byte, leaving whatever data may be stored at the current address at that byte location undisturbed. Any or all of the Byte Write Enable pins may be driven High or Low during the data in sample times in a write sequence.

Each write enable command and write address loaded into the RAM provides the base address for a 2-beat data transfer. The x18 version of the RAM, for example, may write 36 bits in association with each address loaded. Any 9-bit byte may be masked in any write sequence.

Nybble Write (4-bit) control is implemented on the 8-bit-wide version of the device. For the x8 version of the device, "Nybble Write Enable" and " $\overline{NWx}$ " may be substituted in all the discussion above.

### **Resulting Write Operation**

| Byte 1<br>D0-D8 |                   |     | Byte 4<br>D9–D17 |

|-----------------|-------------------|-----|------------------|

| Written         | Written Unchanged |     | Written          |

| Bea             | at 1              | Bea | at 2             |

### Example x18 RAM Write Sequence using Byte Write Enables

| Data In Sample Time | BW0 | BW1 | D0-D8      | D9-D17     |

|---------------------|-----|-----|------------|------------|

| Beat 1              | 0   | 1   | Data In    | Don't Care |

| Beat 2              | 1   | 0   | Don't Care | Data In    |

### FLXDrive-II Output Driver Impedance Control

HSTL I/O SigmaDDR-II+ SRAMs are supplied with programmable impedance output drivers. The ZQ pin must be connected to  $V_{SS}$  via an external resistor, RQ, to allow the SRAM to monitor and adjust its output driver impedance. The value of RQ must be 5X the value of the desired RAM output impedance. The allowable range of RQ to guarantee impedance matching continuously is between 175 $\Omega$  and 350 $\Omega$ . Periodic readjustment of the output driver impedance is necessary as the impedance is affected by drifts in supply voltage and temperature. The SRAM's output impedance circuitry compensates for drifts in supply voltage and temperature. A clock cycle counter periodically triggers an impedance evaluation, resets and counts again. Each impedance evaluation may move the output driver impedance level one step at a time towards the optimum level. The output driver is implemented with discrete binary weighted impedance steps.

### Input Termination Impedance Control

These SigmaDDR-II+ SRAMs are supplied with programmable input termination on Data (DQ), Byte Write ( $\overline{BW}$ ), and Clock (K,  $\overline{K}$ ) input receivers. Input termination can be enabled or disabled via the ODT pin (6R). When the ODT pin is tied Low (or left floating–the pin has a small pull-down resistor), input termination is disabled. When the ODT pin is tied High, input termination is enabled. Termination impedance is programmed via the same RQ resistor (connected between the ZQ pin and V<sub>SS</sub>) used to program output driver impedance, and is nominally RQ\*0.6 Thevenin-equivalent when RQ is between 175 $\Omega$  and 250 $\Omega$ . Periodic readjustment of the termination impedance occurs to compensate for drifts in supply voltage and temperature, in the same manner as for driver impedance (see above).

#### Notes:

- 1. When ODT = 1, Byte Write ( $\overline{BW}$ ), and Clock (K,  $\overline{K}$ ) input termination is always enabled. Consequently,  $\overline{BW}$ , K,  $\overline{K}$  inputs should always be driven High or Low; they should never be tri-stated (i.e., in a High-Z state). If the inputs are tri-stated, the input termination will pull the signal to  $V_{DDQ}/2$  (i.e., to the switch point of the diff-amp receiver), which could cause the receiver to enter a meta-stable state and prevent the SRAM from operating within specification.

- 2. When ODT = 1, DQ input termination is enabled during Write and NOP operations, and disabled during Read operations. Specifically, DQ input termination is disabled 0.5 cycles before the SRAM enables its DQ drivers and starts driving valid Read Data, and remains disabled until 0.5 cycles after the SRAM stops driving valid Read Data and disables its DQ drivers; DQ input termination is enabled at all other times. Consequently, the SRAM Controller should disable its DQ input termination, enable its DQ drivers, and drive DQ inputs (High or Low) during Write and NOP operations. And, it should enable its DQ input termination and disable its DQ drivers during Read operations. Care should be taken during Write or NOP -> Read transitions, and during Read -> NOP transitions, to minimize the time during which one device (SRAM or SRAM Controller) has enabled its DQ input termination while the other device has not yet enabled its DQ driver. Otherwise, the input termination will pull the signal to V<sub>DDQ</sub>/2 (i.e., to the switch point of the diff-amp receiver), which could cause the receiver to enter a metastable state and prevent the SRAM from operating within specification.

### Common I/O SigmaDDR-II+ B2 SRAM Truth Table

| V              | K <sub>n</sub> LD |     |                    | Q                  | Operation |  |

|----------------|-------------------|-----|--------------------|--------------------|-----------|--|

| <sup>n</sup> n | LD                | K/W | A + 0              | A + 1              | Operation |  |

| $\uparrow$     | 1                 | Х   | Hi-Z / *           | Hi-Z / *           | Deselect  |  |

| ↑ (            | 0                 | 0   | D@K <sub>n+1</sub> | D@K <sub>n+1</sub> | Write     |  |

| 1              | 0                 | 1   | Q@K <sub>n+2</sub> | Q@K <sub>n+2</sub> | Read      |  |

Notes:

1. "1" = input "high"; "0" = input "low"; "V" = input "valid"; "X" = input "don't care".

2. D1 and D2 indicate the first and second pieces of Write Data transferred during Write operations.

- 3. Q1 and Q2 indicate the first and second pieces of Read Data transferred during Read operations.

- 4. When On-Die Termination is disabled (ODT = 0), DQ drivers are disabled (i.e., DQ pins are tri-stated) for one cycle in response to NOP and Write commands, 2.0 cycles after the command is sampled.

- 5. When On-Die Termination is enabled (ODT = 1), DQ drivers are disabled for one cycle in response to NOP and Write commands, 2.0 cycles after the command is sampled. The state of the DQ pins during that time (denoted by "\*" in the table above) is determined by the state of the DQ input termination. See the Input Termination Impedance Control section for more information.

| BW                          | BW      | Current Operation                                                    | D                          | D                                        |

|-----------------------------|---------|----------------------------------------------------------------------|----------------------------|------------------------------------------|

| K↑<br>(t <sub>n + 1</sub> ) | <u></u> | K↑<br>(t <sub>n</sub> )                                              | K↑<br>(t <sub>n +1</sub> ) | <del>Γ</del> ↑<br>(t <sub>n + 1½</sub> ) |

| Т                           | Т       | Write<br>Dx stored if $\overline{BWn}$ = 0 in both data transfers    | D1                         | D2                                       |

| т                           | F       | Write<br>Dx stored if $\overline{BWn} = 0$ in 1st data transfer only | D1                         | Х                                        |

| F                           | Т       | Write<br>Dx stored if $\overline{BWn} = 0$ in 2nd data transfer only | Х                          | D2                                       |

| F                           | F       | Write Abort<br>No Dx stored in either data transfer                  | Х                          | Х                                        |

### B2 Byte Write Clock Truth Table

Notes:

1. "1" = input "high"; "0" = input "low"; "X" = input "don't care"; "T" = input "true"; "F" = input "false".

2. If one or more  $\overline{BWn} = 0$ , then  $\overline{BW} = "T"$ , else  $\overline{BW} = "F"$ .

# B2 Nybble Write Clock Truth Table

| NW                          | NW                           | Current Operation                                                    | D                           | D                            |

|-----------------------------|------------------------------|----------------------------------------------------------------------|-----------------------------|------------------------------|

| К↑<br>(t <sub>n + 1</sub> ) | ⊼↑<br>(t <sub>n + 1½</sub> ) | K↑<br>(t <sub>n</sub> )                                              | K↑<br>(t <sub>n + 1</sub> ) | ⊼↑<br>(t <sub>n + 1½</sub> ) |

| Т                           | Т                            | Write Dx stored if $\overline{NWn}$ = 0 in both data transfers       | D1                          | D2                           |

| т                           | F                            | Write<br>Dx stored if $\overline{NWn} = 0$ in 1st data transfer only | D1                          | Х                            |

| F                           | Т                            | Write<br>Dx stored if $\overline{NWn} = 0$ in 2nd data transfer only | Х                           | D2                           |

| F                           | F                            | Write Abort<br>No Dx stored in either data transfer                  | Х                           | Х                            |

Notes:

"1" = input "high"; "0" = input "low"; "X" = input "don't care"; "T" = input "true"; "F" = input "false".

If one or more NWn = 0, then NW = "T", else NW = "F".

| BW0 | BW1 | BW2 | BW3 | D0-D8      | D9-D17     | D18-D26    | D27–D35    |

|-----|-----|-----|-----|------------|------------|------------|------------|

| 1   | 1   | 1   | 1   | Don't Care | Don't Care | Don't Care | Don't Care |

| 0   | 1   | 1   | 1   | Data In    | Don't Care | Don't Care | Don't Care |

| 1   | 0   | 1   | 1   | Don't Care | Data In    | Don't Care | Don't Care |

| 0   | 0   | 1   | 1   | Data In    | Data In    | Don't Care | Don't Care |

| 1   | 1   | 0   | 1   | Don't Care | Don't Care | Data In    | Don't Care |

| 0   | 1   | 0   | 1   | Data In    | Don't Care | Data In    | Don't Care |

| 1   | 0   | 0   | 1   | Don't Care | Data In    | Data In    | Don't Care |

| 0   | 0   | 0   | 1   | Data In    | Data In    | Data In    | Don't Care |

| 1   | 1   | 1   | 0   | Don't Care | Don't Care | Don't Care | Data In    |

| 0   | 1   | 1   | 0   | Data In    | Don't Care | Don't Care | Data In    |

| 1   | 0   | 1   | 0   | Don't Care | Data In    | Don't Care | Data In    |

| 0   | 0   | 1   | 0   | Data In    | Data In    | Don't Care | Data In    |

| 1   | 1   | 0   | 0   | Don't Care | Don't Care | Data In    | Data In    |

| 0   | 1   | 0   | 0   | Data In    | Don't Care | Data In    | Data In    |

| 1   | 0   | 0   | 0   | Don't Care | Data In    | Data In    | Data In    |

| 0   | 0   | 0   | 0   | Data In    | Data In    | Data In    | Data In    |

# x36 Byte Write Enable (BWn) Truth Table

# x18 Byte Write Enable (BWn) Truth Table

| BW0 | BW1 | D0–D8      | D9–D17     |

|-----|-----|------------|------------|

| 1   | 1   | Don't Care | Don't Care |

| 0   | 1   | Data In    | Don't Care |

| 1   | 0   | Don't Care | Data In    |

| 0   | 0   | Data In    | Data In    |

# x8 Nybble Write Enable (NWn) Truth Table

| NWO | NW1 | D0-D3      | D4-D7      |

|-----|-----|------------|------------|

| 1   | 1   | Don't Care | Don't Care |

| 0   | 1   | Data In    | Don't Care |

| 1   | 0   | Don't Care | Data In    |

| 0   | 0   | Data In    | Data In    |

### Absolute Maximum Ratings

(All voltages reference to  $V_{\mbox{\scriptsize SS}}$ )

| Symbol           | Description                      | Value                                              | Unit  |

|------------------|----------------------------------|----------------------------------------------------|-------|

| V <sub>DD</sub>  | Voltage on V <sub>DD</sub> Pins  | -0.5 to 2.9                                        | V     |

| V <sub>DDQ</sub> | Voltage in V <sub>DDQ</sub> Pins | –0.5 to V <sub>DD</sub>                            | V     |

| V <sub>REF</sub> | Voltage in V <sub>REF</sub> Pins | –0.5 to V <sub>DDQ</sub>                           | V     |

| V <sub>I/O</sub> | Voltage on I/O Pins              | –0.5 to V <sub>DDQ</sub> +0.5 ( $\leq$ 2.9 V max.) | V     |

| V <sub>IN</sub>  | Voltage on Other Input Pins      | –0.5 to V <sub>DDQ</sub> +0.5 ( $\leq$ 2.9 V max.) | V     |

| V <sub>TIN</sub> | Input Voltage (TCK, TMS, TDI)    | –0.5 to V <sub>DDQ</sub> +0.5 ( $\leq 2.9$ V max.) | V     |

| I <sub>IN</sub>  | Input Current on Any Pin         | +/-100                                             | mA dc |

| I <sub>OUT</sub> | Output Current on Any I/O Pin    | +/-100                                             | mA dc |

| ٦                | Maximum Junction Temperature     | 125                                                | οC    |

| T <sub>STG</sub> | Storage Temperature              | -55 to 125                                         | оС    |

#### Note:

Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Recommended Operating Conditions, for an extended period of time, may affect reliability of this component.

### **Recommended Operating Conditions**

### **Power Supplies**

| Parameter          | Symbol           | Min.                       | Тур. | Max.                       | Unit |

|--------------------|------------------|----------------------------|------|----------------------------|------|

| Supply Voltage     | V <sub>DD</sub>  | 1.7                        | 1.8  | 1.9                        | V    |

| I/O Supply Voltage | V <sub>DDQ</sub> | 1.4                        | -    | V <sub>DD</sub>            | V    |

| Reference Voltage  | V <sub>REF</sub> | V <sub>DDQ</sub> /2 - 0.05 |      | V <sub>DDQ</sub> /2 + 0.05 | V    |

#### Note:.

The power supplies need to be powered up simultaneously or in the following sequence:  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{REF}$ , followed by signal inputs. The power down sequence must be the reverse.  $V_{DDO}$  must not exceed  $V_{DD}$ . For more information, read **AN1021 SigmaQuad and SigmaDDR Power-Up**.

### **Operating Temperature**

| Parameter                                            | Symbol | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|--------|------|------|------|------|

| Junction Temperature<br>(Commercial Range Versions)  | TJ     | 0    | 25   | 85   | °C   |

| Junction Temperature<br>(Industrial Range Versions)* | TJ     | -40  | 25   | 100  | °C   |

Note:

\* The part numbers of Industrial Temperature Range versions end with the character "I". Unless otherwise noted, all performance specifications quoted are evaluated for worst case in the temperature range marked on the device.

### **Thermal Impedance**

| Package | Test PCB<br>Substrate | θ JA (C°/W)<br>Airflow = 0 m/s | θ JA (C°/W)<br>Airflow = 1 m/s | θ JA (C°/W)<br>Airflow = 2 m/s | θ JB (C°/W) | θ JC (C°/W) |

|---------|-----------------------|--------------------------------|--------------------------------|--------------------------------|-------------|-------------|

| 165 BGA | 4-layer               | TBD                            | TBD                            | TBD                            | TBD         | TBD         |

Notes:

1. Thermal Impedance data is based on a number of of samples from mulitple lots and should be viewed as a typical number.

2. Please refer to JEDEC standard JESD51-6.

3. The characteristics of the test fixture PCB influence reported thermal characteristics of the device. Be advised that a good thermal path to the PCB can result in cooling or heating of the RAM depending on PCB temperature.

### HSTL I/O DC Input Characteristics

| Parameter               | Symbol           | Min                        | Мах                        | Units | Notes |

|-------------------------|------------------|----------------------------|----------------------------|-------|-------|

| Input Reference Voltage | V <sub>REF</sub> | V <sub>DDQ</sub> /2 – 0.05 | V <sub>DDQ</sub> /2 + 0.05 | V     | -     |

| Input High Voltage      | V <sub>IH1</sub> | V <sub>REF</sub> + 0.1     | V <sub>DDQ</sub> + 0.3     | V     | 1     |

| Input Low Voltage       | V <sub>IL1</sub> | -0.3                       | V <sub>REF</sub> – 0.1     | V     | 1     |

| Input High Voltage      | V <sub>IH2</sub> | 0.7 * V <sub>DDQ</sub>     | V <sub>DDQ</sub> + 0.3     | V     | 2,3   |

| Input Low Voltage       | V <sub>IL2</sub> | -0.3                       | 0.3 * V <sub>DDQ</sub>     | V     | 2,3   |

Notes:

1. Parameters apply to K, K, SA, DQ, R/W, LD, BW during normal operation and JTAG boundary scan testing.

2. Parameters apply to Doff, ODT during normal operation and JTAG boundary scan testing.

3. Parameters apply to ZQ during JTAG boundary scan testing only.

### HSTL I/O AC Input Characteristics

| Parameter               | Symbol           | Min                        | Мах                        | Units | Notes |

|-------------------------|------------------|----------------------------|----------------------------|-------|-------|

| Input Reference Voltage | V <sub>REF</sub> | V <sub>DDQ</sub> /2 – 0.08 | V <sub>DDQ</sub> /2 + 0.08 | V     | -     |

| Input High Voltage      | V <sub>IH1</sub> | V <sub>REF</sub> + 0.2     | V <sub>DDQ</sub> + 0.5     | V     | 1,2,3 |

| Input Low Voltage       | V <sub>IL1</sub> | -0.5                       | V <sub>REF</sub> – 0.2     | V     | 1,2,3 |

| Input High Voltage      | V <sub>IH2</sub> | V <sub>DDQ</sub> – 0.2     | V <sub>DDQ</sub> + 0.5     | V     | 4,5   |

| Input Low Voltage       | V <sub>IL2</sub> | -0.5                       | 0.2                        | V     | 4,5   |

Notes:

1.  $V_{IH(MAX)}$  and  $V_{IL(MIN)}$  apply for pulse widths less than one-quarter of the cycle time.

2. Input rise and fall times myust be a minimum of 1 V/ns, and within 10% of each other.

3. Parameters apply to K, K, SA, D, R/W, LD, BW during normal operation and JTAG boundary scan testing.

4. Parameters apply to Doff, ODT during normal operation and JTAG boundary scan testing.

5. Parameters apply to ZQ during JTAG boundary scan testing only.

### Capacitance

$(T_A = 25^{o}C, f = 1 \text{ MHz}, V_{DD} = 1.8 \text{ V})$

| Parameter          | Symbol           | Test conditions        | Тур. | Max. | Unit |

|--------------------|------------------|------------------------|------|------|------|

| Input Capacitance  | C <sub>IN</sub>  | V <sub>IN</sub> = 0 V  | 4    | 5    | pF   |

| Output Capacitance | C <sub>OUT</sub> | V <sub>OUT</sub> = 0 V | 6    | 7    | pF   |

| Clock Capacitance  | C <sub>CLK</sub> | —                      | 5    | 6    | pF   |

Note:

This parameter is sample tested.

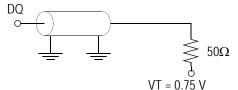

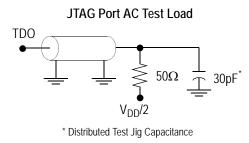

# AC Test Conditions

| Parameter              | Conditions |

|------------------------|------------|

| Input high level       | 1.25       |

| Input low level        | 0.25 V     |

| Max. input slew rate   | 2 V/ns     |

| Input reference level  | .75        |

| Output reference level | 0.75 V     |

Note:

Test conditions as specified with output loading as shown unless otherwise noted.

# AC Test Load Diagram

$$\begin{split} RQ &= 250 \; \Omega \; (\text{HSTL I/O}) \\ V_{\text{REF}} &= 0.75 \; \text{V} \end{split}$$

# Input and Output Leakage Characteristics

| Parameter                                   | Symbol              | Test Conditions                                             | Min.  | Мах    |

|---------------------------------------------|---------------------|-------------------------------------------------------------|-------|--------|

| Input Leakage Current<br>(except mode pins) | I <sub>IL</sub>     | V <sub>IN</sub> = 0 to V <sub>DD</sub>                      | -2 uA | 2 uA   |

| Doff                                        | I <sub>ILDOFF</sub> | $V_{IN} = 0$ to $V_{DD}$                                    | –2 uA | 100 uA |

| ODT                                         | I <sub>ILODT</sub>  | V <sub>IN</sub> = 0 to V <sub>DD</sub>                      | -2 uA | 100 uA |

| Output Leakage Current                      | I <sub>OL</sub>     | Output Disable,<br>V <sub>OUT</sub> = 0 to V <sub>DDQ</sub> | -2 uA | 2 uA   |

# Programmable Impedance HSTL Output Driver DC Electrical Characteristics

| Parameter           | Symbol           | Min.                       | Max.                       | Units | Notes |

|---------------------|------------------|----------------------------|----------------------------|-------|-------|

| Output High Voltage | V <sub>OH1</sub> | V <sub>DDQ</sub> /2 – 0.12 | V <sub>DDQ</sub> /2 + 0.12 | V     | 1, 3  |

| Output Low Voltage  | V <sub>OL1</sub> | V <sub>DDQ</sub> /2 – 0.12 | V <sub>DDQ</sub> /2 + 0.12 | V     | 2, 3  |

| Output High Voltage | V <sub>OH2</sub> | V <sub>DDQ</sub> - 0.2     | V <sub>DDQ</sub>           | V     | 4, 5  |

| Output Low Voltage  | V <sub>OL2</sub> | Vss                        | 0.2                        | V     | 4, 6  |

Notes:

1.  $I_{OH} = (V_{DDQ}/2) / (RQ/5) + -15\% @ V_{OH} = V_{DDQ}/2$  (for:  $175\Omega \le RQ \le 350\Omega$ ).

2.  $I_{OL} = (V_{DDQ}/2) / (RQ/5) + -15\% @ V_{OL} = V_{DDQ}/2$  (for:  $175\Omega \le RQ \le 350\Omega$ ).

3. Parameter tested with RQ = 250  $\Omega$  and V\_{DDQ} = 1.5 V

$4. \quad 0\Omega \leq RQ \leq \infty \Omega$

5. I<sub>OH</sub> = -1.0 mA

6.  $I_{OL} = 1.0 \text{ mA}$

# **Operating Currents**

|                                 |                  |                                                                                                                                                              | -4               | 50                 | -4               | 00                 | -3               | 50                 | -3               | 33                 | -3               | 00                 |       |

|---------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|------------------|--------------------|------------------|--------------------|------------------|--------------------|------------------|--------------------|-------|

| Parameter                       | Symbol           | Test Conditions                                                                                                                                              | 0°<br>to<br>70°C | -40°<br>to<br>85°C | Notes |

| Operating Current<br>(x36): DDR | I <sub>DD</sub>  | $V_{DD}$ = Max, $I_{OUT}$ = 0 mA<br>Cycle Time ≥ $t_{KHKH}$ Min                                                                                              | 860<br>mA        | 870<br>mA          | 770<br>mA        | 780<br>mA          | 725<br>mA        | 735<br>mA          | 660<br>mA        | 670<br>mA          | 570<br>mA        | 580<br>mA          | 2, 3  |

| Operating Current<br>(x18): DDR | I <sub>DD</sub>  | $V_{DD}$ = Max, $I_{OUT}$ = 0 mA<br>Cycle Time ≥ $t_{KHKH}$ Min                                                                                              | 670<br>mA        | 680<br>mA          | 600<br>mA        | 610<br>mA          | 565<br>mA        | 575<br>mA          | 515<br>mA        | 525<br>mA          | 450<br>mA        | 460<br>mA          | 2, 3  |

| Operating Current<br>(x9): DDR  | I <sub>DD</sub>  | $V_{DD}$ = Max, $I_{OUT}$ = 0 mA<br>Cycle Time ≥ $t_{KHKH}$ Min                                                                                              | 670<br>mA        | 680<br>mA          | 600<br>mA        | 610<br>mA          | 565<br>mA        | 575<br>mA          | 515<br>mA        | 525<br>mA          | 450<br>mA        | 460<br>mA          | 2, 3  |

| Operating Current<br>(x8): DDR  | I <sub>DD</sub>  | $V_{DD}$ = Max, $I_{OUT}$ = 0 mA<br>Cycle Time ≥ $t_{KHKH}$ Min                                                                                              | 670<br>mA        | 680<br>mA          | 600<br>mA        | 610<br>mA          | 565<br>mA        | 575<br>mA          | 515<br>mA        | 525<br>mA          | 450<br>mA        | 460<br>mA          | 2, 3  |

| Standby Current<br>(NOP): DDR   | I <sub>SB1</sub> | Device deselected,<br>$I^{OUT} = 0 \text{ mA}, \text{ f} = \text{Max},$<br>All Inputs $\leq 0.2 \text{ V}$<br>or $\geq \text{V}_{\text{DD}} - 0.2 \text{ V}$ | 230<br>mA        | 240<br>mA          | 215<br>mA        | 225<br>mA          | 210<br>mA        | 220<br>mA          | 195<br>mA        | 205<br>mA          | 185<br>mA        | 195<br>mA          | 2, 4  |

Notes:

1. Power measured with output pins floating.

2. Minimum cycle,  $I_{OUT} = 0 \text{ mA}$

3. Operating current is calculated with 50% read cycles and 50% write cycles.

4. Standby Current is only after all pending read and write burst operations are completed.

### **AC Electrical Characteristics**

| Deremeter                                         | Cumhal                                  | -4    | 50   | -4    | 00   | -3    | 50   | -3    | 33   | -3    | 00   | its   | Notes |

|---------------------------------------------------|-----------------------------------------|-------|------|-------|------|-------|------|-------|------|-------|------|-------|-------|

| Parameter                                         | Symbol                                  | Min   | Max  | Min   | Max  | Min   | Мах  | Min   | Мах  | Min   | Мах  | Units | Not   |

| Clock                                             | -                                       |       |      |       |      |       |      |       |      |       |      |       |       |

| K, $\overline{K}$ Clock Cycle Time                | t <sub>кнкн</sub>                       | 2.22  | 8.4  | 2.5   | 8.4  | 2.86  | 8.4  | 3.0   | 8.4  | 3.3   | 8.4  | ns    |       |

| tK Variable                                       | t <sub>KVar</sub>                       | _     | 0.2  | _     | 0.2  | —     | 0.2  | —     | 0.2  | —     | 0.2  | ns    | 4     |

| K, $\overline{K}$ Clock High Pulse Width          | t <sub>KHKL</sub>                       | 0.4   | _    | 0.4   | _    | 0.4   | -    | 0.4   | _    | 0.4   | -    | cycle |       |

| K, $\overline{K}$ Clock Low Pulse Width           | t <sub>KLKH</sub>                       | 0.4   | _    | 0.4   | -    | 0.4   | -    | 0.4   | _    | 0.4   | -    | cycle |       |

| K to K High                                       | t <sub>KHKH</sub>                       | 0.94  | _    | 1.06  | _    | 1.13  | _    | 1.28  | _    | 1.32  | _    | ns    |       |

| K to K High                                       | t <sub>KHKH</sub>                       | 0.94  | —    | 1.06  | _    | 1.13  | _    | 1.28  | —    | 1.32  | -    | ns    |       |

| DLL Lock Time                                     | t <sub>KLock</sub>                      | 2048  | _    | 2048  | _    | 2048  | -    | 2048  | —    | 2048  | -    | cycle | 5     |

| K Static to DLL reset                             | t <sub>KReset</sub>                     | 30    | _    | 30    | _    | 30    | _    | 30    | _    | 30    | _    | ns    |       |

| Output Times                                      |                                         | 1     |      |       | 1    |       |      | 1     | 1    | 1     |      |       |       |

| K, $\overline{K}$ Clock High to Data Output Valid | t <sub>KHQV</sub>                       | —     | 0.45 | _     | 0.45 | _     | 0.45 | -     | 0.45 | -     | 0.45 | ns    |       |

| K, $\overline{K}$ Clock High to Data Output Hold  | t <sub>KHQX</sub>                       | -0.45 | _    | -0.45 | -    | -0.45 | _    | -0.45 | _    | -0.45 | _    | ns    |       |

| K, $\overline{K}$ Clock High to Echo Clock Valid  | t <sub>KHCQV</sub>                      | _     | 0.45 | _     | 0.45 | _     | 0.45 | _     | 0.45 | _     | 0.45 | ns    |       |

| K, $\overline{K}$ Clock High to Echo Clock Hold   | t <sub>KHCQX</sub>                      | -0.45 | _    | -0.45 | _    | -0.45 | _    | -0.45 | _    | -0.45 | _    | ns    |       |

| CQ, CQ High Output Valid                          | t <sub>CQHQV</sub>                      | _     | 0.15 | _     | 0.2  | _     | 0.23 | _     | 0.25 | _     | 0.27 | ns    |       |

| CQ, CQ High Output Hold                           | t <sub>COHOX</sub>                      | -0.15 | —    | -0.2  | _    | -0.23 | _    | -0.25 | _    | -0.27 | -    | ns    |       |

| CQ, CQ High to QVLD                               | t <sub>QVLD</sub>                       | -0.15 | 0.15 | -0.2  | 0.2  | -0.23 | 0.23 | -0.25 | 0.25 | -0.27 | 0.27 | ns    |       |

| CQ Phase Distortion                               | t <sub>сансан</sub><br>t <u>са</u> нсан | 0.85  | _    | 1.0   | _    | 1.08  | _    | 1.25  | _    | 1.29  | _    | ns    |       |

| K Clock High to Data Output High-Z                | t <sub>KHQZ</sub>                       | _     | 0.45 | _     | 0.45 | _     | 0.45 | _     | 0.45 | _     | 0.45 | ns    |       |

| K Clock High to Data Output Low-Z                 | t <sub>KHQX1</sub>                      | -0.45 | _    | -0.45 | _    | -0.45 | _    | -0.45 | _    | -0.45 | -    | ns    |       |

| Setup Times                                       | •                                       | •     | •    | •     | •    | •     |      |       |      |       |      | •     |       |

| Address Input Setup Time                          | t <sub>AVKH</sub>                       | 0.275 | —    | 0.4   | —    | 0.4   | -    | 0.4   | —    | 0.4   | -    | ns    | 1     |

| Control Input Setup Time<br>(R/W)                 | t <sub>IVKH</sub>                       | 0.275 | —    | 0.4   | —    | 0.4   | _    | 0.4   | _    | 0.4   | _    | ns    | 2     |

| Control Input Setup Time<br>(BWX)                 | t <sub>IVKH</sub>                       | 0.22  | _    | 0.28  | _    | 0.28  | _    | 0.28  | _    | 0.28  | _    | ns    | 3     |

| Data Input Setup Time                             | t <sub>DVKH</sub>                       | 0.22  | —    | 0.28  | —    | 0.28  | _    | 0.28  | _    | 0.28  | _    | ns    |       |

| Hold Times                                        | _                                       |       | -    |       |      | -     |      |       |      |       |      | -     |       |

| Address Input Hold Time                           | t <sub>KHAX</sub>                       | 0.275 | _    | 0.4   | _    | 0.4   | -    | 0.4   | _    | 0.4   | -    | ns    | 1     |

| Control Input Hold Time<br>(R/W)                  | t <sub>KHIX</sub>                       | 0.275 | _    | 0.4   | _    | 0.4   | _    | 0.4   | _    | 0.4   | _    | ns    | 2     |

| Control Input Hold Time<br>(BWX)                  | t <sub>KHIX</sub>                       | 0.22  | _    | 0.28  | _    | 0.28  | _    | 0.28  | _    | 0.28  | _    | ns    | 3     |

| Data Input Hold Time                              | t <sub>KHDX</sub>                       | 0.22  | _    | 0.28  | _    | 0.28  | -    | 0.28  | _    | 0.28  | -    | ns    |       |

#### Notes:

1. All Address inputs must meet the specified setup and hold times for all latching clock edges.

2. Control signals are <u>R/W</u>, <u>LD</u>.

Control signals are BW0, BW1 and (BW2, BW3 for x36). 3.

4.

Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge. V<sub>DD</sub> slew rate must be less than 0.1 V DC per 50 ns for DLL lock retention. DLL lock time begins once V<sub>DD</sub> and input clock are stable. 5.

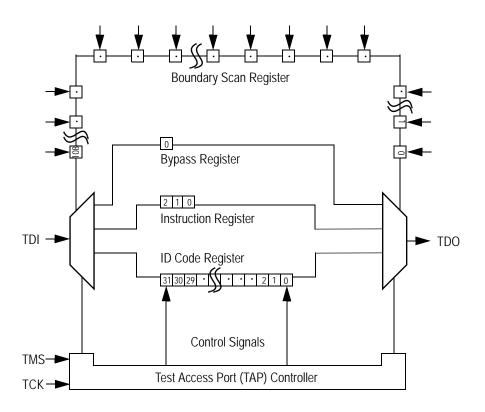

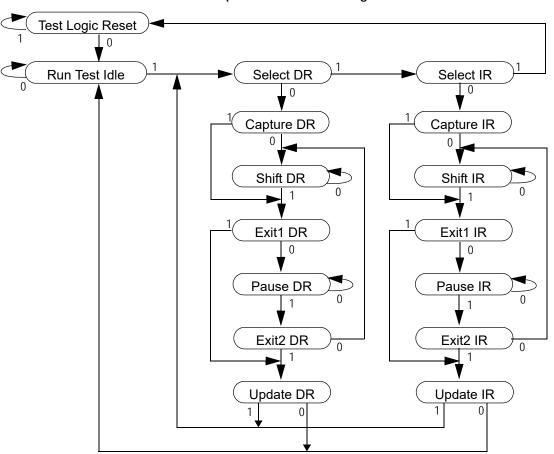

### JTAG Port Operation

#### Overview

The JTAG Port on this RAM operates in a manner that is compliant with IEEE Standard 1149.1-1990, a serial boundary scan interface standard (commonly referred to as JTAG). The JTAG Port input interface levels scale with  $V_{DD}$ . The JTAG output drivers are powered by  $V_{DD}$ .

#### Disabling the JTAG Port

It is possible to use this device without utilizing the JTAG port. The port is reset at power-up and will remain inactive unless clocked. TCK, TDI, and TMS are designed with internal pull-up circuits. To assure normal operation of the RAM with the JTAG Port unused, TCK, TDI, and TMS may be left floating or tied to either  $V_{DD}$  or  $V_{SS}$ . TDO should be left unconnected.

### JTAG Pin Descriptions

| Pin | Pin Name         | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТСК | Test Clock       | In  | Clocks all TAP events. All inputs are captured on the rising edge of TCK and all outputs propagate from the falling edge of TCK.                                                                                                                                                                                                                                                                                                             |

| TMS | Test Mode Select | In  | The TMS input is sampled on the rising edge of TCK. This is the command input for the TAP controller state machine. An undriven TMS input will produce the same result as a logic one input level.                                                                                                                                                                                                                                           |

| TDI | Test Data In     | In  | The TDI input is sampled on the rising edge of TCK. This is the input side of the serial registers placed between TDI and TDO. The register placed between TDI and TDO is determined by the state of the TAP Controller state machine and the instruction that is currently loaded in the TAP Instruction Register (refer to the TAP Controller State Diagram). An undriven TDI pin will produce the same result as a logic one input level. |

| TDO | Test Data Out    | Out | Output that is active depending on the state of the TAP state machine. Output changes in response to the falling edge of TCK. This is the output side of the serial registers placed between TDI and TDO.                                                                                                                                                                                                                                    |

#### Note:

This device does not have a TRST (TAP Reset) pin. TRST is optional in IEEE 1149.1. The Test-Logic-Reset state is entered while TMS is held high for five rising edges of TCK. The TAP Controller is also reset automaticly at power-up.

### **JTAG Port Registers**

#### Overview

The various JTAG registers, refered to as Test Access Port or TAP Registers, are selected (one at a time) via the sequences of 1s and 0s applied to TMS as TCK is strobed. Each of the TAP Registers is a serial shift register that captures serial input data on the rising edge of TCK and pushes serial data out on the next falling edge of TCK. When a register is selected, it is placed between the TDI and TDO pins.

#### Instruction Register

The Instruction Register holds the instructions that are executed by the TAP controller when it is moved into the Run, Test/Idle, or the various data register states. Instructions are 3 bits long. The Instruction Register can be loaded when it is placed between the TDI and TDO pins. The Instruction Register is automatically preloaded with the IDCODE instruction at power-up or whenever the controller is placed in Test-Logic-Reset state.

#### **Bypass Register**

The Bypass Register is a single bit register that can be placed between TDI and TDO. It allows serial test data to be passed through the RAM's JTAG Port to another device in the scan chain with as little delay as possible.

#### **Boundary Scan Register**

The Boundary Scan Register is a collection of flip flops that can be preset by the logic level found on the RAM's input or I/O pins. The flip flops are then daisy chained together so the levels found can be shifted serially out of the JTAG Port's TDO pin. The Boundary Scan Register also includes a number of place holder flip flops (always set to a logic 1). The relationship between the device pins and the bits in the Boundary Scan Register is described in the Scan Order Table following. The Boundary Scan

Register, under the control of the TAP Controller, is loaded with the contents of the RAMs I/O ring when the controller is in Capture-DR state and then is placed between the TDI and TDO pins when the controller is moved to Shift-DR state. SAMPLE-Z, SAMPLE/PRELOAD and EXTEST instructions can be used to activate the Boundary Scan Register.

JTAG TAP Block Diagram

#### Identification (ID) Register

The ID Register is a 32-bit register that is loaded with a device and vendor specific 32-bit code when the controller is put in Capture-DR state with the IDCODE command loaded in the Instruction Register. The code is loaded from a 32-bit on-chip ROM. It describes various attributes of the RAM as indicated below. The register is then placed between the TDI and TDO pins when the controller is moved into Shift-DR state. Bit 0 in the register is the LSB and the first to reach TDO when shifting begins.

### **ID Register Contents**

|       |    |    |                                                      |   |   |   |   |   | See | BSD | )L M | odel |    |    |    |    |   |   |   |   |   |   | G:<br>J | ED | EC | hno<br>Ve<br>Cod | ndo | ЭУ<br>or |   |   |   | Presence Register |

|-------|----|----|------------------------------------------------------|---|---|---|---|---|-----|-----|------|------|----|----|----|----|---|---|---|---|---|---|---------|----|----|------------------|-----|----------|---|---|---|-------------------|

| Bit # | 31 | 30 | 0 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 |   |   |   |   |   |     |     |      |      | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3       | 2  | 1  | 0                |     |          |   |   |   |                   |

|       | Х  | Х  | Х                                                    | Х | Х | Х | Х | Х | Х   | Х   | Х    | Х    | Х  | Х  | Х  | Х  | Х | Х | Х | Х | 0 | 0 | 0       | 1  | 1  | 0                | 1   | 1        | 0 | 0 | 1 | 1                 |

### Tap Controller Instruction Set

#### Overview

There are two classes of instructions defined in the Standard 1149.1-1990; the standard (Public) instructions, and device specific (Private) instructions. Some Public instructions are mandatory for 1149.1 compliance. Optional Public instructions must be implemented in prescribed ways. The TAP on this device may be used to monitor all input and I/O pads, and can be used to load address, data or control signals into the RAM or to preload the I/O buffers.

When the TAP controller is placed in Capture-IR state the two least significant bits of the instruction register are loaded with 01. When the controller is moved to the Shift-IR state the Instruction Register is placed between TDI and TDO. In this state the desired instruction is serially loaded through the TDI input (while the previous contents are shifted out at TDO). For all instructions, the TAP executes newly loaded instructions only when the controller is moved to Update-IR state. The TAP instruction set for this device is listed in the following table.

JTAG Tap Controller State Diagram

#### Instruction Descriptions

#### BYPASS

When the BYPASS instruction is loaded in the Instruction Register the Bypass Register is placed between TDI and TDO. This occurs when the TAP controller is moved to the Shift-DR state. This allows the board level scan path to be shortened to facilitate testing of other devices in the scan path.

#### SAMPLE/PRELOAD

SAMPLE/PRELOAD is a Standard 1149.1 mandatory public instruction. When the SAMPLE / PRELOAD instruction is loaded in the Instruction Register, moving the TAP controller into the Capture-DR state loads the data in the RAMs input and I/O buffers into the Boundary Scan Register. Boundary Scan Register locations are not associated with an input or I/O pin, and are loaded with the default state identified in the Boundary Scan Chain table at the end of this section of the datasheet. Because the RAM clock is independent from the TAP Clock (TCK) it is possible for the TAP to attempt to capture the I/O ring contents while the input buffers are in transition (i.e. in a metastable state). Although allowing the TAP to sample metastable inputs will not harm the device, repeatable results cannot be expected. RAM input signals must be stabilized for long enough to meet the TAPs input data capture set-up plus hold time (tTS plus tTH). The RAMs clock inputs need not be paused for any other TAP operation except capturing the I/O ring contents into the Boundary Scan Register. Moving the controller to Shift-DR state then places the boundary scan register between the TDI and TDO pins.

#### EXTEST

EXTEST is an IEEE 1149.1 mandatory public instruction. It is to be executed whenever the instruction register is loaded with all logic 0s. The EXTEST command does not block or override the RAM's input pins; therefore, the RAM's internal state is still determined by its input pins.

Typically, the Boundary Scan Register is loaded with the desired pattern of data with the SAMPLE/PRELOAD command. Then the EXTEST command is used to output the Boundary Scan Register's contents, in parallel, on the RAM's data output drivers on the falling edge of TCK when the controller is in the Update-IR state.

Alternately, the Boundary Scan Register may be loaded in parallel using the EXTEST command. When the EXTEST instruction is selected, the sate of all the RAM's input and I/O pins, as well as the default values at Scan Register locations not associated with a pin, are transferred in parallel into the Boundary Scan Register on the rising edge of TCK in the Capture-DR state, the RAM's output pins drive out the value of the Boundary Scan Register location with which each output pin is associated.

#### IDCODE

The IDCODE instruction causes the ID ROM to be loaded into the ID register when the controller is in Capture-DR mode and places the ID register between the TDI and TDO pins in Shift-DR mode. The IDCODE instruction is the default instruction loaded in at power up and any time the controller is placed in the Test-Logic-Reset state.

#### SAMPLE-Z

If the SAMPLE-Z instruction is loaded in the instruction register, all RAM outputs are forced to an inactive drive state (high-Z) and the Boundary Scan Register is connected between TDI and TDO when the TAP controller is moved to the Shift-DR state.

# JTAG TAP Instruction Set Summary

| Instruction    | Code | Description                                                                                                                    | Notes |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------|-------|

| EXTEST         | 000  | Places the Boundary Scan Register between TDI and TDO.                                                                         | 1     |

| IDCODE         | 001  | Preloads ID Register and places it between TDI and TDO.                                                                        | 1, 2  |

| SAMPLE-Z       | 010  | Captures I/O ring contents. Places the Boundary Scan Register between TDI and TDO.<br>Forces all RAM output drivers to High-Z. | 1     |

| GSI            | 011  | GSI private instruction.                                                                                                       | 1     |

| SAMPLE/PRELOAD | 100  | Captures I/O ring contents. Places the Boundary Scan Register between TDI and TDO.                                             | 1     |

| GSI            | 101  | GSI private instruction.                                                                                                       | 1     |

| GSI            | 110  | GSI private instruction.                                                                                                       | 1     |

| BYPASS         | 111  | Places Bypass Register between TDI and TDO.                                                                                    | 1     |

#### Notes:

1. Instruction codes expressed in binary, MSB on left, LSB on right.

2. Default instruction automatically loaded at power-up and in test-logic-reset state.

### JTAG Port Recommended Operating Conditions and DC Characteristics

| Parameter                              | Symbol            | Min.                  | Max.                  | Unit | Notes |

|----------------------------------------|-------------------|-----------------------|-----------------------|------|-------|

| Test Port Input Low Voltage            | V <sub>ILJ</sub>  | -0.3                  | 0.3 * V <sub>DD</sub> | V    | 1     |

| Test Port Input High Voltage           | V <sub>IHJ</sub>  | 0.7 * V <sub>DD</sub> | V <sub>DD</sub> +0.3  | V    | 1     |

| TMS, TCK and TDI Input Leakage Current | I <sub>INHJ</sub> | -300                  | 1                     | uA   | 2     |

| TMS, TCK and TDI Input Leakage Current | I <sub>INLJ</sub> | -1                    | 100                   | uA   | 3     |

| TDO Output Leakage Current             | I <sub>OLJ</sub>  | -1                    | 1                     | uA   | 4     |

| Test Port Output High Voltage          | V <sub>OHJ</sub>  | V <sub>DD</sub> – 0.2 | _                     | V    | 5, 6  |

| Test Port Output Low Voltage           | V <sub>OLJ</sub>  | —                     | 0.2                   | V    | 5, 7  |

| Test Port Output CMOS High             | V <sub>OHJC</sub> | V <sub>DD</sub> – 0.1 |                       | V    | 5, 8  |

| Test Port Output CMOS Low              | V <sub>OLJC</sub> | _                     | 0.1                   | V    | 5, 9  |

Notes:

1. Input Under/overshoot voltage must be -1 V < Vi < V<sub>DDn</sub> +1 V not to exceed 2.9 V maximum, with a pulse width not to exceed 20% tTKC.

2.  $V_{ILJ} \le V_{IN} \le V_{DDn}$

3. 0 V

$$\leq$$

V<sub>IN</sub>  $\leq$  V<sub>ILJn</sub>

- 4. Output Disable,  $V_{OUT} = 0$  to  $V_{DDn}$

- 5. The TDO output driver is served by the V<sub>DD</sub> supply.

- 6. I<sub>OHJ</sub> = -2 mA

- 7. I<sub>OLJ</sub> = + 2 mA

- 8.  $I_{OHJC} = -100 \text{ uA}$

- 9.  $I_{OLJC} = +100 \text{ uA}$

# **JTAG Port AC Test Conditions**

| Parameter              | Conditions              |

|------------------------|-------------------------|

| Input high level       | V <sub>DD</sub> – 0.2 V |

| Input low level        | 0.2 V                   |

| Input slew rate        | 1 V/ns                  |

| Input reference level  | V <sub>DD</sub> /2      |

| Output reference level | V <sub>DD</sub> /2      |

Notes:

1.

Include scope and jig capacitance. Test conditions as shown unless otherwise noted. 2.

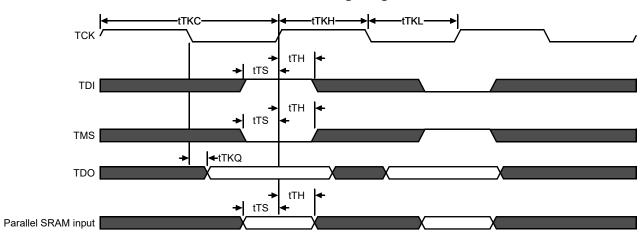

### **JTAG Port Timing Diagram**

### **JTAG Port AC Electrical Characteristics**

| Parameter             | Symbol | Min | Max | Unit |

|-----------------------|--------|-----|-----|------|

| TCK Cycle Time        | tTKC   | 50  | 1   | ns   |

| TCK Low to TDO Valid  | tTKQ   | _   | 20  | ns   |

| TCK High Pulse Width  | tTKH   | 20  | -   | ns   |

| TCK Low Pulse Width   | tTKL   | 20  | -   | ns   |

| TDI & TMS Set Up Time | tTS    | 10  | -   | ns   |

| TDI & TMS Hold Time   | tTH    | 10  | _   | ns   |

# Ordering Information—GSI SigmaDDR-II+ SRAM

| Org    | Part Number <sup>1</sup> | Туре                 | Package                     | Speed<br>(MHz) | T <sub>J</sub> <sup>2</sup> |

|--------|--------------------------|----------------------|-----------------------------|----------------|-----------------------------|

| 4M x 8 | GS8342T07BD-450          | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 450            | С                           |

| 4M x 8 | GS8342T07BD-400          | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 400            | С                           |

| 4M x 8 | GS8342T07BD-350          | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 350            | С                           |

| 4M x 8 | GS8342T07BD-333          | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 333            | С                           |

| 4M x 8 | GS8342T07BD-300          | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 300            | С                           |

| 4M x 8 | GS8342T07BD-450I         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 450            | Ι                           |

| 4M x 8 | GS8342T07BD-400I         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 400            | I                           |

| 4M x 8 | GS8342T07BD-350I         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 350            | I                           |

| 4M x 8 | GS8342T07BD-333I         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 333            | I                           |

| 4M x 8 | GS8342T07BD-300I         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 300            | I                           |

| 4M x 8 | GS8342T07BGD-450         | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 450            | С                           |

| 4M x 8 | GS8342T07BGD-400         | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 400            | С                           |

| 4M x 8 | GS8342T07BGD-350         | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 350            | С                           |

| 4M x 8 | GS8342T07BGD-333         | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 333            | С                           |

| 4M x 8 | GS8342T07BGD-300         | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 300            | С                           |

| 4M x 8 | GS8342T07BGD-450I        | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 450            | I                           |

| 4M x 8 | GS8342T07BGD-400I        | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 400            | I                           |

| 4M x 8 | GS8342T07BGD-350I        | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 350            | I                           |

| 4M x 8 | GS8342T07BGD-333I        | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 333            | I                           |

| 4M x 8 | GS8342T07BGD-300I        | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 300            | I                           |

| 4M x 9 | GS8342T110BD-450         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 450            | С                           |

| 4M x 9 | GS8342T110BD-400         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 400            | С                           |

| 4M x 9 | GS8342T10BD-350          | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 350            | С                           |

| 4M x 9 | GS8342T10BD-333          | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 333            | С                           |

| 4M x 9 | GS8342T10BD-300          | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 300            | С                           |

| 4M x 9 | GS8342T10BD-450I         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 450            | I                           |

| 4M x 9 | GS8342T10BD-400I         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 400            | I                           |

| 4M x 9 | GS8342T10BD-350I         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 350            | I                           |

| 4M x 9 | GS8342T10BD-333I         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 333            | I                           |

| 4M x 9 | GS8342T10BD-300I         | SigmaDDR-II+ B2 SRAM | 165-bump BGA                | 300            | I                           |

| 4M x 9 | GS8342T10BGD-450         | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 450            | С                           |

| 4M x 9 | GS8342T10BGD-400         | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 400            | С                           |

| 4M x 9 | GS8342T10BGD-350         | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 350            | С                           |

Notes:

1. For Tape and Reel add the character "T" to the end of the part number. Example: GS8342TxxBD-333T.

2. C = Commercial Temperature Range. I = Industrial Temperature Range.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

# Ordering Information—GSI SigmaDDR-II+ SRAM (Continued)

| Org     | Part Number <sup>1</sup> | Туре                 | Package                     | Speed<br>(MHz) | T <sub>J</sub> <sup>2</sup> |

|---------|--------------------------|----------------------|-----------------------------|----------------|-----------------------------|

| 4M x 9  | GS8342T10BGD-333         | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 333            | С                           |

| 4M x 9  | GS8342T10BGD-300         | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 300            | С                           |

| 4M x 9  | GS8342T10BGD-450I        | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 450            | I                           |

| 4M x 9  | GS8342T10BGD-400I        | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 400            | I                           |

| 4M x 9  | GS8342T10BGD-350I        | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 350            | I                           |

| 4M x 9  | GS8342T10BGD-333I        | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 333            | I                           |

| 4M x 9  | GS8342T10BGD-300I        | SigmaDDR-II+ B2 SRAM | RoHS-compliant 165-bump BGA | 300            | I                           |