## **Features**

- 300KHz Constant Switching Frequency

- VBAT Rang= 4.5V~13.2V

- Support 0.6V Internal Reference Voltage

- 0-80% Duty Cycle

- 3.6ms Digital Soft-Start Circuit Built-In

- Short Circuit Protection

- Under Voltage Protection and Over Voltage

Protection

- Flexible Over Current Protection Setting

- Thermal Fault Protection

- Integrated Bootstrap Diode

- PSOP-8 package

- Green Product (RoHS, Lead-Free, Halogen-Free Compliant)

## **Applications**

- Mother Board

- Graphic cards

- Cable Modems, Set Top Boxes, and Xdsl Supplies

- Low cost PC

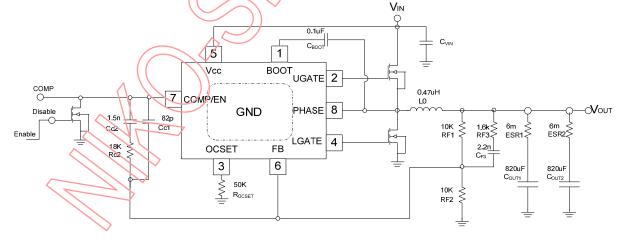

# **Typical Application**

## **General Description**

The GS7253-A is a single buck controller working in a voltage mode with fixed 300 kHz frequency. It allows wide input voltage which is either a single  $5\sim12V$  or two supply voltages for various applications, and the output voltage can be precisely regulated to as low as 0.6V with a maximum tolerance of  $\pm1.0\%$ .

The GS7253-A is equipped with accurate current-limit, under-voltage output and over-voltage output protections. Otherwise, it includes internal 3.6ms digital soft-start and built-in bootstrap diode to simplify the circuit design.

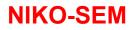

The GS7253-A is available in a simple PSOP-8 Package.

Figure 1 Typical Application of GS7253-A

This document is NIKO-SEM's confidential information. Anyone having confidential obligation to NIKO-SEM shall keep this document confidential. Any unauthorized disclosure or use beyond authorized purpose will be considered as violation of confidentiality and criminal and civil liability will be asserted.

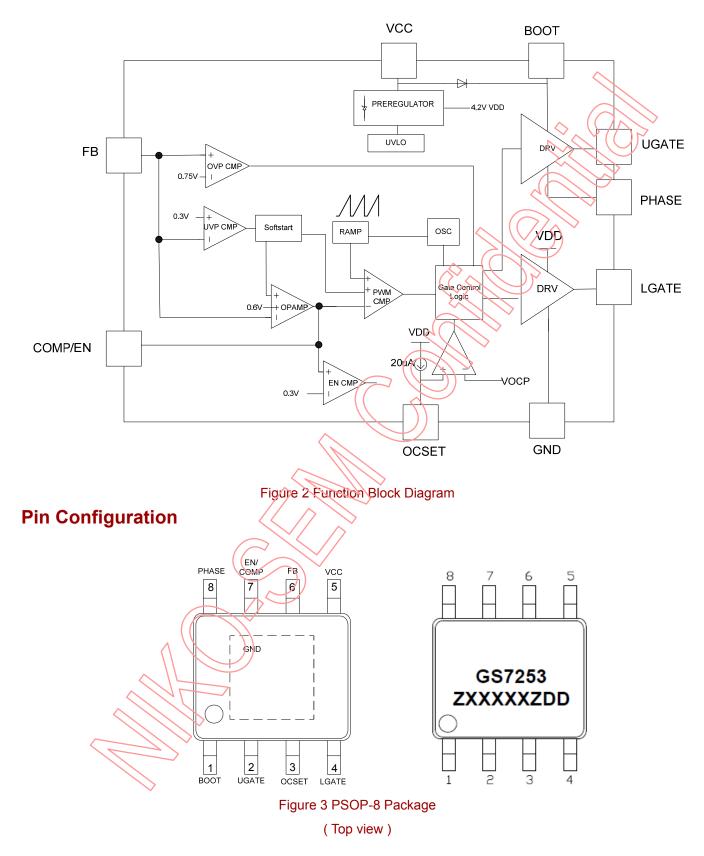

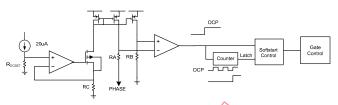

## **Function Block Diagram**

# **Pin Descriptions**

| No.    | Nama                 | I/O  | Pin Function                                                                                                                                                                                                                                                                 |  |

|--------|----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PSOP-8 | Name                 | type |                                                                                                                                                                                                                                                                              |  |

| 1      | BOOT                 | 0    | This pin provides the bootstrap voltage to the high-side gate driver for driving the N-channel MOSFET. An external capacitor from PHASE to BOOT, an internal diode, and the power supply voltage VCC, generates the bootstrap voltage for the high-side gate driver (UGATE). |  |

| 2      | UGATE                | 0    | High-side Gate Driver Output. This pin is the gate driver for high-side MOSFET.                                                                                                                                                                                              |  |

| 3      | OCSET                | I    | Connecting a resistor (ROCSET) between OCSET and GND sets the over-current trip point.                                                                                                                                                                                       |  |

| 4      | LGATE                | 0    | This pin is the gate driver for low-side MOSFET                                                                                                                                                                                                                              |  |

| 5      | VCC                  | I    | Power Supply Input for Control Circuitry. Connect a well-decoupled 5V/12V supply voltage to this pin. Ensure that a decoupling capacitor is placed near the IC                                                                                                               |  |

| 6      | FB                   | I    | Feedback Input of Converter. Connecting FB with a resistor-divider from the output sets the output voltage of the converter.                                                                                                                                                 |  |

| 7      | COMP/EN              | 0    | The Output of the error amplifier. Pulling this pin lower than 0.3V disables the controller. Use this pin in combination with the FB pin to compensate the voltage mode loop of the converter.                                                                               |  |

| 8      | PHASE                | 0    | Connect this pin to the source of the upper MOSFET and the drain of the lower MOSFET. This pin is used as the sink for the UGATE driver, and to monitor the voltage drop across the lower MOSFET for over current protection.                                                |  |

| 9      | GND<br>(Exposed Pad) | I    | Signal and Power ground. Connecting this pin to system ground.                                                                                                                                                                                                               |  |

## **Ordering Information**

1. Product name 2. For AMD

| No | ltem         | Contents       |

|----|--------------|----------------|

| 1  | Product name | GS7253         |

| 2  | For AMD      | -A             |

| 3  | Package      | SO: PSOP-8     |

| 4  | Shipping     | R: Tape & Reel |

Example: GS7253-A PSOP-8 Tape & Reel ordering information is "GS7253-ASO-R"

## Absolute Maximum Rating (Note 1)

| Parameter                                           | Symbol                       | Limits                       | Units |

|-----------------------------------------------------|------------------------------|------------------------------|-------|

| VCC to GND                                          | SUPPLY                       | -0.3 ~ 18                    | V     |

| BOOT Voltage                                        | VBOOT-GND                    | -0.3 ~ 36                    | V     |

| BOOT to PHASE Voltage                               | VBOOT-PHASE                  | -0.3 ~ 18                    | V     |

| UGATE to PHASE Voltage                              | V <sub>GU</sub>              | -0.3 ~V <sub>BOOT</sub> +0.3 | V     |

| LGATE to GND Voltage                                | VGL                          | $-0.3 \sim V_{VCC} + 0.3$    | V     |

|                                                     | VPHASE                       | -0.3 ~ 18 (>200ns)           | V     |

| PHASE to GND                                        |                              | -2~ 28 (<200ns)              | V     |

| FB, COMP, OCSET to GND                              |                              | -0.3 ~6                      | V     |

| Package Power Dissipation at $T_A \leq 25^{\circ}C$ | P <sub>D_PSOP-8</sub>        | 1333                         | mW    |

| Junction Temperature                                | TJ                           | - 45 ~ 150                   | °C    |

| Storage Temperature                                 | T <sub>STG</sub>             | - 55 ~ 150                   | °C    |

| Lead Temperature (Soldering) 10S                    | T <sub>LEAD</sub>            | 260                          | °C    |

| ESD (Human Body Mode) (Note 2)                      | $V_{ESD_{HBM}}$              | 2K                           | V     |

| ESD (Machine Mode) (Note 2)                         | $V_{\text{ESD}_{\text{MM}}}$ | 200                          | V     |

## Thermal Information (Note 3)

| Parameter                              | Symbol                 | Limits | Units |

|----------------------------------------|------------------------|--------|-------|

| Thermal Resistance Junction to Ambient | $\theta_{JA_{PSOP-8}}$ | 75     | °C/W  |

# **Recommend Operating Condition** (Note 4)

| Parameter            | Symbol            | Limits        | Units |

|----------------------|-------------------|---------------|-------|

| VIN to GND           | V <sub>IN</sub>   | 3~13.2        | V     |

| VCC to GND           | V <sub>CC</sub>   | 4.5~13.2      | V     |

| COMP to GND          | V <sub>COMP</sub> | COMP Floating | V     |

| Junction Temperature | TJ                | -40~125       | °C    |

| Ambient Temperature  | T <sub>A</sub>    | -40 - 85      | °C    |

## **Electrical Characteristics**

|                          |                   |                                                     | $\langle \bigcirc \rangle \rangle$ |     |       |           |

|--------------------------|-------------------|-----------------------------------------------------|------------------------------------|-----|-------|-----------|

| Parameter                | Symbol            | Test Conditions                                     | Min                                | Тур | Max   | Units     |

| Supply Input             |                   | C                                                   | ))                                 |     |       | •         |

| Supply Voltage           | V <sub>CC</sub>   |                                                     | 4.5                                |     | 13.2  | V         |

| Supply Current           | I <sub>CC</sub>   | UGATE,LGATE Open:<br>V <sub>cc</sub> =12V,Switching |                                    | 3.8 |       | mA        |

| Quiescent Supply Current | I <sub>CC-Q</sub> | V <sub>FB</sub> =0.7V,NO Switching                  |                                    | 2   |       | mA        |

| Power Input Voltage      | V <sub>IN</sub>   |                                                     | 3.0                                |     | 13.2  | V         |

| Power On Reset           |                   |                                                     |                                    |     |       |           |

| POR Threshold            |                   |                                                     | 4.0                                | 4.2 | 4.4   | V         |

| POR Hysteresis           |                   | $\sum$                                              |                                    | 0.5 |       | V         |

| Oscillator               |                   |                                                     |                                    |     |       |           |

| Free Running Frequency   | f <sub>osc</sub>  | GS7253-A                                            | 270                                | 300 | 330   | KHz       |

| Ramp Amplitude           | AVosc             | Guaranteed by Design                                |                                    | 1.8 |       | $V_{P_P}$ |

| Error Amplifier          |                   |                                                     |                                    |     |       |           |

| Open Loop DC Gàin        | A0                | Guaranteed by Design                                |                                    | 88  |       | dB        |

| Gain-Bandwidth Product   | GBW               | Guaranteed by Design                                |                                    | 10  |       | MHz       |

| Slew Rate                | SR                | Guaranteed by Design                                |                                    | 10  |       | V/us      |

| Reference Voltage        | -                 |                                                     | -                                  |     |       | -         |

| Nominal Feedback Voltage | V <sub>FB</sub>   | Internal Reference Mode                             | 0.594                              | 0.6 | 0.606 | V         |

| PWM Controller Gate Drivers   |                        |                                                                                                   |                                   |      |            |      |

|-------------------------------|------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------|------|------------|------|

| Dood Time                     | T <sub>DL</sub>        | $V_{CC}$ =12; $V_{PHASE}$ <1.2V to<br>$V_{LGATE}$ >1.2V                                           |                                   | 30   | 90         | ns   |

| Dead Time                     | T <sub>DH</sub>        | V <sub>CC</sub> =12;V <sub>LGATE</sub> <1.2V to<br>(V <sub>UGATE</sub> -V <sub>PHASE</sub> )>1.2V |                                   | 30   | 90         | ns   |

| UGATE Driver Pull Up          | R <sub>U_UP</sub>      | BOOT-PHASE=12V,<br>UGATE=High, I <sub>UGATE</sub> =-100mA                                         |                                   | 3.5  | - AB-      | ohms |

| UGATE Driver Pull Down        | R <sub>U_DN</sub>      | BOOT-PHASE=12V,<br>UGATE=Low, I <sub>UGATE</sub> =100mA                                           |                                   | 1.9  |            | ohms |

| LGATE Driver Pull Up          | R <sub>L_UP</sub>      | V <sub>CC</sub> =12V, LGATE= High, I <sub>LGATE</sub><br>=-100mA                                  |                                   | 3.8  | $\diamond$ | ohms |

| LGATE Driver Pull Down        | R <sub>L_SINK</sub>    | V <sub>CC</sub> =12V, LGATE=Low,<br>I <sub>LGATE</sub> =100mA                                     | $\hat{\mathcal{I}}_{\mathcal{A}}$ | 1.8  |            | ohms |

| UVP                           |                        | ,                                                                                                 |                                   |      |            |      |

| Under Voltage Protection      | V <sub>FB-UVP</sub>    | V <sub>REF</sub> =0.6V                                                                            | 0.27                              | 0.3  | 0.33       | V    |

| OVP                           | •                      |                                                                                                   | $\sim$                            |      |            |      |

| Over Voltage Protection       | V <sub>FB-OVP</sub>    | V <sub>REF</sub> =0.6V                                                                            | 0.72                              | 0.75 | 0.78       | V    |

| Over Voltage Protection Delay | V <sub>FB-OVP-DL</sub> | V <sub>REF</sub> =0.6V                                                                            |                                   | 20   |            | us   |

| ОСР                           |                        |                                                                                                   |                                   |      |            |      |

| OCSET Current Source          | I <sub>OC_SET</sub>    | VOCSET=10                                                                                         | 18                                | 20   | 22         | uA   |

| OCP Threshold                 | VPHASE1                | VOCSET=1.0,GS7253-A                                                                               |                                   | -250 |            | mV   |

| Other Protection              |                        |                                                                                                   |                                   |      |            |      |

| Soft-Start Interval           | T <sub>SS</sub>        | Internal Reference Mode                                                                           |                                   | 2    |            | mS   |

| Thermal Shutdown Temperature  | T <sub>TSDN</sub>      | $\bigcirc$                                                                                        |                                   | 151  |            | °C   |

| Thermal Shutdown Hysteresis   | THYS_TSON              |                                                                                                   |                                   | 15   |            | °C   |

| Enable Threshold              | VCOMPVEN               | GS7253-A                                                                                          |                                   | 0.3  | 0.35       | V    |

| Boost Diode                   |                        |                                                                                                   |                                   |      |            |      |

| Internal Boot Diode Forward   | ) \$                   | VCC to BOOT, IF=10mA                                                                              | 0.2                               | 0.4  | 0.6        | V    |

Note 1.Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

**Note 2.**Devices are ESD sensitive. Handling precaution recommended.

**Note 3.** $\theta_{JA}$  is measured in the natural convection at  $T_A=25^{\circ}C$  on a high effective thermal conductivity test

# 5V/12V Single Synchronous Buck Controller

board (4 Layers, 2S2P) of JEDEC 51-7 thermal measurement standard. **Note 4.**The device is not guaranteed to function outside its operating conditions.

Rev.:0P11 (Preliminary Specification)

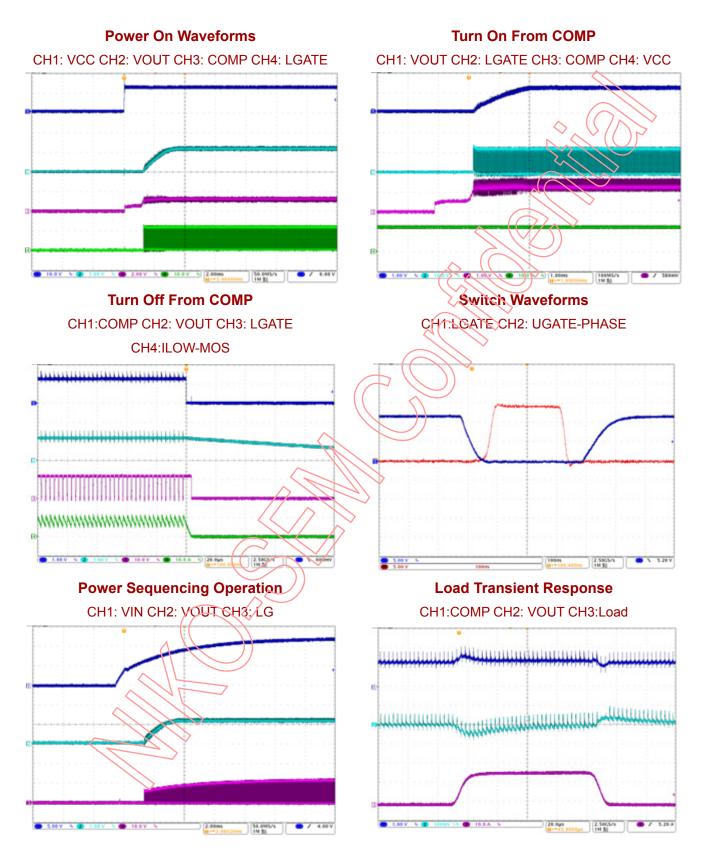

# **Typical Characteristics**

## **Function Description**

The GS7253-A is small size chip with fixed frequency synchronous buck switching controller suitable for applications in notebook computers and other battery operated portable devices. Features include very wide input voltage range and fast dynamic response

## UVLO

An internal under voltage lockout (UVLO) module is used to sense the VCC power supply. The PWM controller is forbidden by the under voltage lockout module when VCC rises above 4.2V, the GS7253-A will initial the control logic circuitries and soft-start ramping generator, and then allows switching .When VCC falls down to 3.7V, the PWM controller is forbidden again. At this time, both sides drive signal UGATE and LGATE are low.

#### **Power Input Detection**

The GS7253-A detects phase voltage to determine whether the Power Input Supply Voltage is powered on. If power input voltage exceeds 2.5V when UGATE turns on for the first time, the PHASE voltage will rise up during the period of UGATE turns on, and the internal detective circuit will detect the PHASE voltage and digital soft-start will continue. If the PHASE voltage does not exceed 2.5V when UGATE turns on, GS7253-A stops soft-start and begins a new soft-start cycle. That means soft-start cycle will restart periodically until GS7253-A detect the PHASE voltage exceeds 2.5V.

## Output Voltage Selection

The output voltage is set by the feedback resistors RFB2 and RFB1 of Pig.1. If the internal 0.6V reference voltage is used, the voltage at the feedback pin is also 0.6V. Therefore the output can be set by the equation below:

VOUT= (1+RFB2/RFB1) ×0.6V

#### Switching Frequency

The switching frequency is a fixed 300kHz for the GS7253-A

#### **Digital Soft-Start**

In order to prevent surge current from power supply input during Power MOSFEF turns on, a built-in digital soft-start is used for this chip. The error amplifier and PWM comparator are both three-input devices. The smaller voltage between reference voltage and an internal soft-start voltage SSE determines the behavior of the non-inverting input of error amplifier, while the smaller voltage between the output of error amplifier and another internal soft-start SSP dominates the behavior of the inverting input of PWM comparator. Both SSP and SSE internally ramps up to internal supply voltage at the end of soft-start, while SSP ramps faster than SSE signal. These two signals are produced digitally and ramps up step by step due to the internal oscillator.

At the beginning of soft-start, the SSE signal actually restrains the FB signal rising too fast, while SSP signal actually restrains the output signal of error amplifier. However, after SSE exceeds the internal reference voltage or SSP exceeds the output of error amplifier, the restraining effect will disappear and both of these two signals keep ramping up until rising to internal supply voltage.

### Power MOSFET Gate Drivers

The GS7253-A has UGATE and LGATE drivers built-in, which can drive two large external N-type MOSFET used as high side and low side. External Boost diode and capacitor are need to power the internal floating drive module, A dead-time circuit is added to monitor the UGATE output and to prevent the high-side MOSFET from turning on until LGATE is fully off. The internal pull-down transistor that drives LGATE low is robust with a 1.60hm typical on-resistance. The

## **GS7253-ASO-R**

# NIKO-SEM

# 5V/12V Single Synchronous Buck Controller

dead-time circuit also monitors the LGATE output and prevents the low-side MOSFET from turning on until UGATE is fully off. The typical dead time from UGATE-falling to LGATE-rising is about 30ns.The typical dead time from LGATE-falling to UGATE-rising is about 30ns

#### **Over Current Protection**

GS7253-A uses the on-state resistance of the low-side power MOSFET  $R_{ON}$  as a current-sense resistor. In this case, the  $R_{OCSET}$  resistor between OCSET PIN and GND sets the over current threshold. Due to the internal 20uA current and the outside 50K resistor, the voltage of OCSET PIN rises to 1.0V after GS7253-A power on. As a result, the resistor  $R_{OCSET}$  supports a fixed voltage. Therefore the Over Current Threshold can be set by the equation below:  $I_{OCP}$ = 20uA\*Rocset /(4\*R<sub>ON</sub>).

When the voltage drop across the low side power MOSFET equals the threshold voltage, positive current limit will activate. Both the high side Power MOSFET and low side Power MOSFET will turn off and a new soft-start will begin. The current sensing circuit actually regulates the inductor peak current. Once the peak of the current-sense signal at PHASE pin is above the current-limit threshold during the period of low side Power MOSFET turns on, the Over Current Protection will work and Digital soft-start restart again. After over current protection occurs for three times, the chip will be latched off until Power Reset or COMP as Enable function is pulled low to reset.

$R_{OCSET}$  is resistor to set the threshold of Over Current Limit and  $R_{ON}$  is the resistance of low side power MOSFET ML. Ensure that noise and DC errors do not corrupt the current-sense signal seen by OCSET and GND.

locp=20uA\*Rocset\*(RA-RB)/ (RC\*Ron)

Figure 4 Over Current Protection Circuit

## Output Over Voltage Protection

When the output voltage rises up to 125% of the internal reference voltage, the internal fault-logic module delays about 20us and turns on the low side Power MOSFET. It stays latched on and the GS7253-A is latched off until Power Reset or COMP as Enable function is pulled low to reset.

## **Output Under Voltage Protection**

When the output voltage falls down to 0.3V, the internal fault-logic module turns off both the high side and low side Power MOSFETs, while a new soft-start begins. The UVP will be blanked during soft-start.

## Thermal Shutdown

GS7253-A monitors the die temperature. If the temperature exceeds the threshold value (typically 152°C), the GS7253-A is shut off. This is non-latch protection, while the chip restarts the digital soft-start process after the temperature fall down.

Jan-12

## Application Information

## Feedback Compensation

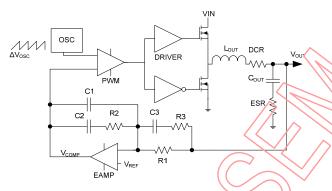

Figure 5 shows the voltage-mode control loop for a synchronous-rectified buck converter. In this loop, the output voltage is regulated to the internal reference voltage. The output of error amplifier is compared with the oscillator triangular wave to provide a pulse width modulated (PWM) wave with an amplitude of VIN at the PHASE node. The PWM wave is smoothed by the output filter (LO and CO).

It is easy to get::

| GAIN -               | R1 + R3        | $(s+\frac{1}{R2C2})(s+\frac{1}{R2C2})$ | $-\frac{1}{(R1+R3)C3})_{*}$            |

|----------------------|----------------|----------------------------------------|----------------------------------------|

|                      | R1 * R3 * C1   | $s(s + \frac{C1 + C2}{R2C1C2})$        | $\frac{1}{2}$ )(s + $\frac{1}{R3C3}$ ) |

| VIN                  | 1 +            | s * ESR * C <sub>OUT</sub>             |                                        |

| $\Delta V_{\rm OSC}$ | 1 + s(ESR + L) | $DCR)C_{OUT} + s^2L$                   | OUT * COUT                             |

Figure 5 VOLTAGE-MODE BUCK CONVERTER

## Modulator Break Frequency Equations

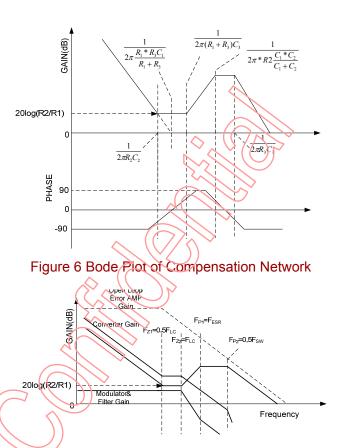

Figure 6 shows a generic Type III compensation, its transfer function and asymptotic Bode plot is given by Figure 7.The Type III compensation network shapes the profile of the gain with respect of frequency in a similar fashion to the Type II compensation network. The Type III network, utilizes two zeroes to give a phase boost of 180°. This boost is necessary to counteract the effects of under damped resonance of the output filter at the double pole.

Figure 7 Asymptotic Bode Plot of Converter Gain According to Figure 6 and Figure 7, use the following guidelines for locating the poles and zeros of the compensation net-work:

- 1. Pick Gain (R2/R1) for desired converter bandwidth.

- 2. Place FZ1 below Filter's Double Pole(50% FLC)

- 3. Place FZ2 at Filter's Double Pole.

- 4. Place FP1 at the ESR Zero.

- 5. Place FP2 at Half the switching Frequency.

- 6. Check the EAMP Gain and estimate Phase Margin.

The following equations can help to calculate the available value:

$$F_{LC} = \frac{1}{2\pi\sqrt{LC}}$$

$$F_{ESR} = \frac{1}{2\pi ESR * C_{OUT}}$$

# 5V/12V Single Synchronous Buck Controller

$$Fz1 = 0.5F_{LC} = \frac{1}{2\pi R_2 C_2}$$

$$Fz_2 = F_{LC} = \frac{1}{2\pi (R_1 + R_3)C_3}$$

$$F\rho_1 = F_{ESR} = \frac{1}{2\pi R_2 C_1 * C_2 / (C_1 + C_2)}$$

$$F\rho_2 = 0.5F_{SW} = \frac{1}{2\pi R_3 C_3}$$

#### **Inductor Selection**

The output inductor is selected to meet the output voltage ripple requirements and minimize the converter's response time to the load transient. It also needs to consider the efficiency, output power and operating frequency. The larger inductance brings lower inductor's current ripple and lower output ripple voltage and results in large size and slower load transient response. It is usually suggested to set ripple current to be approximately 30% of the maximum output current.

The ripple current and ripple voltage can be approximated by:

$$I_{RIPPLE} = \frac{V_{IN} - V_{OUT}}{F_{SW} \times L} \times \frac{V_{OUT}}{V_{IN}}$$

Fsw is the switching frequency of regulator.  $\Delta V_{OUT} = I_{RIPPLE} \times R_{ESR}$

## **Output Capacitor Selection**

The selection of output capacitor  $C_{OUT}$  is determined by the requirement of effective series resistance (ESR) and load step transients. Considering the worst case and assume the capacitance value is  $C_{OUT}$ , the peak-to-peak ripple voltage can be derived in following Equation:

$$\Delta V_{OUT} \leq I_{RIPPLE} \times (R_{ESR} + \frac{1}{8 \times C_{OUT} \times F_{SW}})$$

Considering the demand of the load transient response, the energy that the inductor needs to release is derived in following Equation:

$$E_L = \frac{1}{2} \times L \times (I_{OH}^2 - I_{OL}^2)$$

At the same time, the energy that is delivered to the output capacitor can also be derived as following Equation:

$$E_{C} = \frac{1}{2} \times C_{OUT} \times (V_{f}^{2} - V_{i}^{2})$$

As a result, to meet the load transient response demand, the minimum output capacitance should be

$$C_{OUT} = \frac{L \times (I_{OH}^2 - I_{OL}^2)}{|V_f^2 - V_i^2|}$$

Where

- IOH is the output current under heavy load conditions

- · IOL is the putput current under light load conditions

- Vf is the final peak capacitor voltage

- Vi is the initial capacitor voltage

By the way, Organic semiconductor capacitors or specially polymer capacitors are recommended.

### Input Capacitor Selection

The input filter capacitor should be based on how much ripple the supply can tolerate on the DC input line. The larger capacitor, the less ripple expected but consider should be taken for the higher surge current during the power-up.Use a mix of input bypass capacitors to control the voltage overshoot across the MOSFETs. Use small ceramic capacitors for high frequency decoupling and large bulk capacitors to supply the current when upper MOSFET turns on.

The bulk capacitor is chosen based on the voltage rating and RMS current rating. For reliable operation, select the capacitor voltage rating to be at least 1.3 times higher than the maximum input voltage and a voltage rating of 1.5 times of the maximum input voltage is a conservative guideline. The maximum RMS current rating requirement is approximately lout/2, where lout is the load current. Usually The RMS value of ripple current flowing through the input capacitor is described as :

Irms = IOUT  $(D^{*}(1-D))^{1/2}(A)$

The input capacitor must be cable of handling this ripple current. Sometime, for higher efficiency the low ESR capacitor is necessarily.

#### **MOSFET Selection**

The selection of the N-channel power MOSFETs are determined by the  $R_{DS(ON)}$  and maximum output current requirement. In high-current applications, the MOSFET power dissipation, package selection and heat-sink are also design factors. The power dissipation includes two loss components: conduction loss and switching loss. The following equations give approximately losses for upper MOSFET and lower MOSFET.

$\mathsf{P}_{\mathsf{CONU}} = \mathsf{I}_{\mathsf{OUT}}^2 \mathsf{R}_{\mathsf{DS}} (\mathsf{ON}) \mathsf{D}$

$P_{\text{CONL}} = I_{\text{OUT}}^2 R_{\text{DS}(\text{ON})} (1-D)$

$P_{SWU} = (V_{IN} \bullet I_{OUT}/2) \bullet F_{SW} \bullet T_{SW}$

$P_{SWL} = (V_{IN} \bullet I_{OUT}/2) \bullet F_{SW} \bullet T_{SW}$

Where: D is the duty-cycle,

$T_{SW}$  is the combined switch ON and OFF time, and  $F_{SW}$  is the switching frequency.

According to the GS7253-A current limit principle and its specification, the low side  $R_{DS(ON)}$  times the inductor current value at the over-current point should be equal to 20uA\*Rocset /4. Assuming a 20% guard band,  $R_{DS(ON)}$  should satisfy the following equation during the full temperature range.

$$R_{DS(ON)} \leq \frac{20uA * \text{Rocset}}{(1.2 \times I_{OUT(\text{max})} - 0.5 \times I_{ripple}) * 4}$$

For higher efficiency application, low side power MOSFET with low R<sub>DS (ON)</sub> should be selected. For heavy load application, two low side power MOSFETs are recommended.

### **Bootstrap Capacitor Considerations**

The boot capacitor needs to store about 100 times the gate charge required by the upper MOSFET. A value of  $0.1\mu$ F is typical for many systems driving

#### single MOSFETs.

#### Layout Considerations (To be continued)

- Keep the sensitive small signal nodes far away from switching nodes such as UGATE, LGATE, BOOT and PHASE.

- Keep the switching nodes as short as possible and no other weak signal traces in parallel with the switching nodes' traces.

- The Critical components should be located as close as possible.

- Using Ground plane construction or single point grounding.

- The interconnecting wires indicated by heavy lines should be part of a ground or power plane in a printed circuit board.

- ROCSET close to the OCSET pin because the internal current source is only 20uA.

- Decoupling capacitors, the resistor-divider and boot capacitor should be close to their pins.

- All components for feedback compensation should be located as close to the IC as practical.

**GS7253-ASO-R**

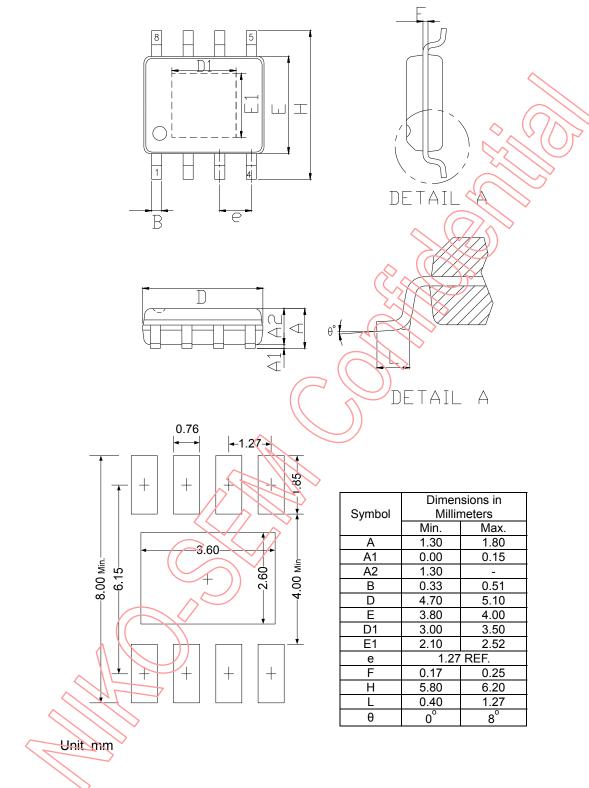

## Package Dimensions, PSOP-8(B)

#### <u>Note</u>

- 1. Min.: Minimum dimension specified.

- 2. Max.: Maximum dimension specified.

- 3. REF.: Reference. Normal/Regular dimension specified for reference.

## DISCLAIMERS

Please read the notice stated in this preamble carefully before Admission e accessing any contents of the document attached. Admission of NIKO-SEM's statement therein is presumed once the document is released to the receiver.

Notice:

Firstly, NIKO SEMICONDUCTOR CO., LTD. (NIKO-SEM), reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its information herein without notice. And the aforesaid information does not form any part or parts of any quotation or contract between NIKO-SEM and the information receiver.

Further, no responsibility is assumed for the usage of the aforesaid information. NIKO-SEM makes no representation that the interconnect of its circuits as described herein will not infringe on exiting or future patent rights and other intellectual property rights, nor do the descriptions contained herein express or imply that any licenses under any NIKO-SEM patent right, copyright, mask work right, or other NIKO-SEM intellectual property right relating to any combination, machine, or process in which NIKO-SEM products or services are used.

Besides, the product in this document is not designed for use in life support appliances, devices, or systems where malfunction of this product can reasonably be expected to result in personal injury. NIKO-SEM customers' using or selling this product for use in such applications shall do so at their own risk and agree to fully indemnify NIKO-SEM for any damage resulting from such improper use or sale.

At last, the information furnished in this document is the property of NIKO-SEM and shall be treated as highly confidentiality; any kind of distribution, disclosure, copying, transformation or use of whole or parts of this document without duly authorization from NIKO-SEM by prior written consent is strictly prohibited. The receiver shall fully compensate NIKO-SEM without any reservation for any losses thereof due to its violation of NIKO-SEM's confidential request. The receiver is deemed to agree on NIKO-SEM's confidential request therein suppose that said receiver receives this document without making any expressly opposition. In the condition that aforesaid opposition is made, the receiver shall return this document to NIKO-SEM immediately without any delay.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Isolated DC/DC Converters category:

Click to view products by GSTEK(Green Solution Technology) manufacturer:

Other Similar products are found below :

ESM6D044440C05AAQ FMD15.24G PSL486-7LR PSR152.5-7IR Q48T30020-NBB0 AVO240-48S12B-6L AVO250-48S28B-6L NAN-0505 HW-L16D JAHW100Y1 217-1617-001 22827 SPB05C-12 SQ24S15033-PS0S 18952 19-130041 CE-1003 CE-1004 GQ2541-7R PSE1000DCDC-12V RDS180245 MAU228 419-2065-201 449-2075-101 J80-0041NL V300C24C150BG 419-2062-200 419-2063-401 419-2067-101 419-2067-501 419-2068-001 DCG40-5G DFC15U48D15 449-2067-000 XGS-0512 XGS-1205 XGS-1212 XGS-2412 XGS-2415 XKS-1215 033456 NCT1000N040R050B SPB05B-15 SPB05C-15 SSQE48T25025-NAA0G L-DA20 HP3040-9RG HP1001-9RTG XKS-2415 XKS-2412