# 3-wire Serial EEPRO Ms 1k/2k/4k

#### **FEATURES**

- Internally organized as 128×8 or 64×16(1k)

256×8 or 128×16(2K), 512×8 or 256×16(4K)

- Wide-voltage range operation 1.8V-5.5V

- 3-wire serial interface bus

- Data retention:100years

- High endurance 1,000,000 Write Cycles

- 2 MHz(5V)clock rate

- Sequential read operation

- Self-timed write cycle(10ms max)

### **ORDERING INFORMATION:**

| DEVICE        | Package Type | MARKING | Packing | Packing Qty  |

|---------------|--------------|---------|---------|--------------|

| AT93C46AN     | DIP8         | 93C46A  | TUBE    | 2000box/reel |

| AT93C56AN     | DIP8         | 93C56A  | TUBE    | 2000box/reel |

| AT93C66AN     | DIP8         | 93C66A  | REEL    | 2000box/reel |

| AT93C46AM/TR  | SOP8         | 93C46A  | REEL    | 2500pcs/reel |

| AT93C56AM/TR  | SOP8         | 93C56A  | REEL    | 2500pcs/reel |

| AT93C66AM/TR  | SOP8         | 93C66A  | REEL    | 2500pcs/reel |

| AT93C46AM/TR  | TSSOP8       | 93C46A  | REEL    | 3000pcs/reel |

| AT93C56AM/TR  | TSSOP8       | 93C56A  | REEL    | 3000pcs/reel |

| AT93C66AM/TR  | TSSOP8       | 93C66A  | REEL    | 3000pcs/reel |

| AT93C46AMM/TR | MSOP8        | 93C46A  | REEL    | 3000pcs/reel |

| AT93C56AMM/TR | MSOP8        | 93C56A  | REEL    | 3000pcs/reel |

| AT93C66AMM/TR | MSOP8        | 93C66A  | REEL    | 3000pcs/reel |

#### **DESCRIPTION**

The AT93Cxx family provides 1k,2k and 4k of serial electrically erasable and programmable read-only memory(EEPROM). The wide Vdd range allows for low-voltage operation down to 1.8V and up to 5.5V The device, fabricated using traditional CMOS EEPROM technology, is optimized for many industrial and commercial applications where low-voltage and low-power operation is essential. The AT93C46A/56A/66A is available in 8-pin DIP,8-pin JEDEC SOP,8-pin TSSOP, and 8-pin MSOP packages and is accessed via a 3-wire serial interface.

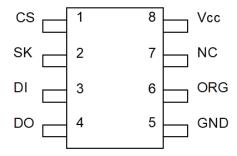

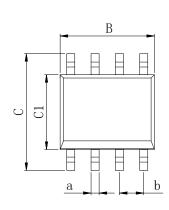

**Figure 1. Pin Configuration**

8-pin DIP/MSOP/SOP/TSSOP

| Pin Name | Function              |

|----------|-----------------------|

| CS       | Chip Select           |

| SK       | Serial Data Clock     |

| DI       | Serial Data Input     |

| DO       | Serial Data Output    |

| GND      | Ground                |

| Vcc      | Power Supply          |

| ORG      | Internal Organization |

| NC       | No Connect            |

#### **ABSOLUTE MAXIMUM RATINGS**

| Condition                 | Min   | Max       |

|---------------------------|-------|-----------|

| Operating Temperature     | -40°C | +85°C     |

| Storage Temperature       | -65°C | +150°C    |

| Voltage on Any Pin with   |       |           |

| Respect to Ground         | -1.0V | VCC+ 7.0V |

| Maximum Operating Voltage | -     | 6.25V     |

| DC Output Current         | -     | 5.0 mA    |

Note: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

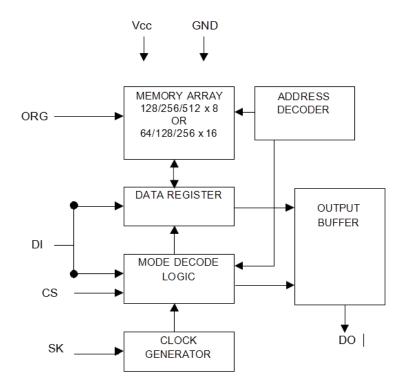

Figure 2. Block Diagram

#### **Notes**

The ORG pin is used to select etween x8 and x16 mode.

When the pin is connected to Vcc, x16 mode is selected.

Otherwise, the ORG pin should be grounded in order to select x8 mode.

The interface for the AT93C46A / 5A6 / 66A is accessed through four different signals: Chip Select (CS), Data Input (DI), Data Output (DO), and Serial Data Clock (SK). The Chip Select (CS) signal must be pulled high before issuing a command through the Data Input (DI) pin. The Serial Data Clock (SK) signal is used in conjunction with the Data Input (DI) pin.

### PIN CAPACITANCE

Applicable over recommended operating range from TA = 25°C, f = 1.0 MHz, Vcc = +5.0V

| Symbol | Test Condition                 | Max | Units | Condition             |

|--------|--------------------------------|-----|-------|-----------------------|

| Соит   | Output Capacitance (DO)        | 5   | pF    | V <sub>OUT</sub> = 0V |

| Cin    | Input Capacitance (CK, SK, DI) | 5   | pF    | V <sub>IN</sub> = 0V  |

## **DC CHARACTERISTICS**

Applicable over recommended operating range from:

TAMB= -40°C to +85°C, Vcc = +1.8V to +5.5V (unless otherwise noted)

| Symbol                                                             | Parameter                             | Test Condition                                                                                   | Min                          | Тур | Max                                        | Units |

|--------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------|-----|--------------------------------------------|-------|

| V <sub>CC1</sub>                                                   | Supply Voltage                        |                                                                                                  | 1.8                          |     | 5.5                                        | V     |

| V <sub>CC2</sub>                                                   | Supply Voltage                        |                                                                                                  | 2.7                          |     | 5.5                                        | V     |

| V <sub>CC3</sub>                                                   | Supply Voltage                        |                                                                                                  | 4.5                          |     | 5.5                                        | V     |

| Icc                                                                | Supply Current V <sub>CC</sub> =5.0V  | READ at 1 MHz                                                                                    |                              | 0.5 | 2.0                                        | mA    |

| Icc                                                                | Supply Current V <sub>CC</sub> =5.0V  | WRITE at 1 MHz                                                                                   |                              | 0.5 | 2.0                                        | mA    |

| I <sub>SB1</sub>                                                   | Standby Current V <sub>CC</sub> =1.8V | CS=0V                                                                                            |                              | 0   | 0.1                                        | μA    |

| I <sub>SB2</sub>                                                   | Standby Current V <sub>CC</sub> =2.7V | CS=0V                                                                                            |                              | 6.0 | 10.0                                       | μA    |

| I <sub>SB3</sub>                                                   | Standby Current V <sub>CC</sub> =5.0V | CS=0V                                                                                            |                              | 17  | 3.0                                        | μA    |

| ILI                                                                | Input Leakage Current                 | VIN=0V to V <sub>CC</sub>                                                                        |                              | 0.1 | 3.0                                        | μA    |

| I <sub>LO</sub>                                                    | Output Leakage Current                | VIN=0V to V <sub>CC</sub>                                                                        |                              | 0.1 | 3.0                                        | μA    |

| V <sub>IL1</sub> <sup>(1)</sup><br>V <sub>IH1</sub> <sup>(1)</sup> | Input Low Level Input High Level      | 2.7V <vcc<5.5v< td=""><td>-0.6<br/>2.0</td><td></td><td>0.8<br/>Vcc+1</td><td>V</td></vcc<5.5v<> | -0.6<br>2.0                  |     | 0.8<br>Vcc+1                               | V     |

| V <sub>IL2</sub> <sup>(1)</sup><br>V <sub>IH2</sub> <sup>(1)</sup> | Input Low Level Input High Level      | 1.8V <v<sub>CC&lt;2.7V</v<sub>                                                                   | -0.6<br>V <sub>CC</sub> ×0.7 |     | V <sub>cc</sub> ×0.3<br>V <sub>cc</sub> +1 | V     |

| V <sub>OL1</sub>                                                   | Output Low Level Output High Level    | 2.7V <v<sub>CC&lt;5.5V;<br/>I<sub>OL</sub>=2.1mA I<sub>OH</sub>=-0.4mA</v<sub>                   | 2.4                          |     | 0.4                                        | V     |

| V <sub>OL2</sub>                                                   | Output Low Level Output High Level    | 1.8V <v<sub>CC&lt;2.7V;<br/>I<sub>OL</sub>=0.15mA I<sub>OH</sub>=-100μA</v<sub>                  | Vcc-0.2                      |     | 0.2                                        | V     |

Note:  $1.V_{IL}$  and  $V_{IH}$  max are reference only and are not tested

## **AC CHARACTERISTICS**

Applicable over recommended operating range from:

$T_{AMB}$ = -40°C to +85°C,  $V_{CC}$  = As specified, CL = 1 TTL Gate &100pF(unless otherwise noted)

| Symbol           | Parameter          | Te                   | est Condition          | Min  | Тур | Max  | Units  |  |

|------------------|--------------------|----------------------|------------------------|------|-----|------|--------|--|

|                  |                    | 4.5                  | V < Vcc < 5.5V         | 0    |     | 2    |        |  |

| <b>f</b> sк      | Clock Frequency,   | 2.7                  | V < Vcc < 5.5V         | 0    |     | 1    | MHz    |  |

| ISK              | SK                 | 1.8V < Vcc < 5.5V    |                        | 0    |     | 0.25 | IVITZ  |  |

|                  |                    | 4.5                  | V < Vcc < 5.5V         | 250  |     |      |        |  |

| t <sub>skH</sub> | SK High Time       |                      | V < Vcc < 5.5V         | 250  |     |      | ns     |  |

| LSKH             | SK High Hille      | 1.8                  | V < Vcc < 5.5V         | 1000 |     |      |        |  |

|                  |                    | _                    | V < Vcc < 5.5V         | 250  |     |      |        |  |

| <b>t</b> skl     | SK Low Time        |                      | V < Vcc < 5.5V         | 250  |     |      | ns     |  |

| LONE             | OIX LOW TIME       | 1.8                  | V < Vcc < 5.5V         | 1000 |     |      | 113    |  |

|                  |                    | 4.5                  | V < Vcc < 5.5V         | 250  |     |      |        |  |

| tcs              | Minimum CS Low     | 2.7                  | V < Vcc < 5.5V         | 250  |     |      | ns     |  |

| tes              | Time               | 1.8                  | V < Vcc < 5.5V         | 1000 |     |      | 115    |  |

|                  |                    | Relative             | $4.5V < V_{CC} < 5.5V$ | 50   |     |      |        |  |

| tcss             | CS Setup Time      | to SK                | $2.7V < V_{cc} < 5.5V$ | 50   |     |      | ns     |  |

| icss             | Co Setup Tillle    | 10 010               | 1.8V < Vcc < 5.5V      | 200  |     |      | 115    |  |

|                  |                    | Relative             | $4.5V < V_{CC} < 5.5V$ | 100  |     |      |        |  |

| tois             | DI Setup Time      | to SK                | $2.7V < V_{CC} < 5.5V$ | 100  |     |      | ns     |  |

| LDIS             | Di Setup Time      | to SK                | 1.8V < Vcc < 5.5V      | 400  |     |      | 115    |  |

|                  |                    | Relative             |                        | 0    |     |      |        |  |

| tсsн             | CS Hold Time       | to SK                |                        |      |     |      | ns     |  |

|                  |                    | Relative             | $4.5V < V_{CC} < 5.5V$ | 100  |     |      |        |  |

| <b>t</b> DIH     | DI Hold Time       | to SK                | $2.7V < V_{cc} < 5.5V$ | 100  |     |      | ns     |  |

| COIII            | Birriola riille    | 10 011               | 1.8V < Vcc < 5.5V      | 400  |     |      | 110    |  |

|                  |                    |                      | $4.5V < V_{cc} < 5.5V$ |      |     | 250  |        |  |

| t <sub>PD1</sub> | Output Delay to    | AC Test              | 2.7V < Vcc < 5.5V      |      |     | 250  | ns     |  |

| 401              | "1"                | 710 1001             | 1.8V < Vcc < 5.5V      |      |     | 1000 | 110    |  |

|                  |                    |                      | $4.5V < V_{cc} < 5.5V$ |      |     | 250  |        |  |

| t <sub>PD0</sub> | Output Delay to    | AC Test              | 2.7V < Vcc < 5.5V      |      |     | 250  | ns     |  |

| L 50             | "0"                | 710 1001             | 1.8V < Vcc < 5.5V      |      |     | 1000 | 110    |  |

|                  |                    |                      | $4.5V < V_{CC} < 5.5V$ |      |     | 250  |        |  |

| tsv              | CS to Status Valid | AC Test              | $2.7V < V_{CC} < 5.5V$ |      |     | 250  | ns     |  |

|                  | Co to Status Valla | 710 1001             | 1.8V < Vcc < 5.5V      |      |     | 1000 | 110    |  |

|                  | CS to DO in High   | AC Test              | $4.5V < V_{CC} < 5.5V$ |      |     | 100  |        |  |

| t <sub>DF</sub>  | Impedance          | CS = V <sub>IL</sub> | $2.7V < V_{CC} < 5.5V$ |      |     | 100  | ns     |  |

| <b>L</b> DF      | '                  |                      | 1.8V < Vcc < 5.5V      |      |     | 400  | 110    |  |

| twp              | Write Cycle        | Time                 | 4.5V < Vcc < 5.5V      |      | 3   | 10   | ms     |  |

| Endurance        | 5.0V, 25°C         |                      |                        | 1M   |     |      | Write  |  |

| Litadianoc       | 0.0 1, 20 0        |                      |                        | 1141 |     |      | Cycles |  |

#### **INSTRUCTION SET FOR THE AT93C46A**

| Instruction | SB | Ор   | Add                                                   | Address                                               |             | ata                              | Comments                                                                   |

|-------------|----|------|-------------------------------------------------------|-------------------------------------------------------|-------------|----------------------------------|----------------------------------------------------------------------------|

|             |    | Code | X8                                                    | X16                                                   | X8          | X16                              |                                                                            |

| READ        | 1  | 10   | $A_6 - A_0$                                           | $A_{\scriptscriptstyle 5} - A_{\scriptscriptstyle 0}$ |             |                                  | Reads data stored at specified memory location.                            |

| EWEN        | 1  | 00   | 11xxxxx                                               | 11xxxx                                                |             |                                  | Write enable command (must be issued before any erase or write operation). |

| ERASE       | 1  | 11   | $A_6 - A_0$                                           | $A_5 - A_0$                                           |             |                                  | Erases memory location A₁ – A₀                                             |

| WRITE       | 1  | 01   | $A_{\scriptscriptstyle 6} - A_{\scriptscriptstyle 0}$ | $A_5 - A_0$                                           | $D_7 - D_0$ | D <sub>15</sub> - D <sub>0</sub> | Writes to memory location A <sub>n</sub> -A <sub>o</sub>                   |

| ERAL        | 1  | 00   | 10xxxxx                                               | 10xxxx                                                |             |                                  | Erases all memory locations. Valid only at Vcc = 4.5V to 5.5V              |

| WRAL 1      |    | 00   | 01xxxxx                                               | 01xxxx                                                | $D_7 - D_0$ | D <sub>15</sub> - D <sub>0</sub> | Writes all memory locations. Valid only at Vcc = 4.5V to 5.5V              |

| EWDS        | 1  | 00   | 00xxxxx                                               | 00xxxx                                                |             |                                  | Disables all erase or write instructions                                   |

Note: The X's in the address field represent don't care values and must be clocked.

## **INSTRUCTION SET FOR THE AT93C46A/56A/66A**

| luna 4 muna 4 in m | C D | Op   | Add                             | ress        | D           | ata                              | Comments                                                                  |

|--------------------|-----|------|---------------------------------|-------------|-------------|----------------------------------|---------------------------------------------------------------------------|

| Instruction        | SB  | Code | X8                              | X16         | X8          | X16                              |                                                                           |

| READ               | 1   | 10   | A <sub>8</sub> - A <sub>0</sub> | $A_7 - A_0$ |             |                                  | Reads data stored at specified memory location.                           |

| EWEN               | 1   | 00   | 11xxxxxxx                       | 11xxxxxx    |             |                                  | Write enable command (must be issued before any erase or writeoperation). |

| ERASE              | 1   | 11   | A <sub>8</sub> - A <sub>0</sub> | $A_7 - A_0$ |             |                                  | Erase memory location A <sub>n</sub> – A <sub>0</sub>                     |

| WRITE              | 1   | 01   | $A_8 - A_0$                     | $A_7 - A_0$ | $D_7 - D_0$ | D <sub>15</sub> — D <sub>0</sub> | Writes memory location A <sub>n</sub> – A <sub>0</sub>                    |

| ERAL               | 1   | 00   | 10xxxxxxx                       | 10xxxxxx    |             |                                  | Erases all memory locations.  Valid only at Vcc = 4.5V to 5.5V            |

| WRAL 1             |     | 00   | 01xxxxxxx                       | 01xxxxxx    | $D_7 - D_0$ | D15 — D0                         | Writes all memory locations.                                              |

| EWDS               | 1   | 00   | 00xxxxxxx                       | 00xxxxx     |             |                                  | Valid only at Vcc = 4.5V to 5.5V. Disables all erase or writeinstructions |

Note: The X's in the address field represent don't care values and must be clocked.

#### **FUNCTIONAL DESCRIPTION**

TheAT93C46A/56A/66A supports 7 different instructions, which must be clocked serially using the CS, SK and DI pins. Before sending each of these instructions, the CS pin must first be pulled high followed by a START bit (logic '1'). The next sequence includes a 2-bit Op Code and usually an 8 or 16-bit address. The next description describes the various functions in the chip.

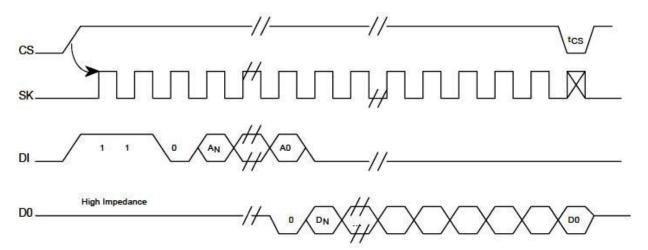

**READ (READ):** The Read (READ) instruction includes the Op Code ("10") followed by the memory address location to be read. After the instruction and address is sent, the data from the memory location can be clocked out using the serial output pin DO. The data changes on the rising edge of the clock, so the falling edge can be used to strobe the output.

Note that during shifting the last address bit, the DO pin is a dummy bit (logic "0").

**ERASE/WRITE (EWEN):** When the chip is first powered-on, no erase or write instructions can be issued. Only when the Erase/Write Enable (EWEN) instruction is sent will the system be allowed to write to the chip. The EWEN command only needs to be issued once after being powered-on. To disable the chip again, the Erase/Write Disable (EWDS) command can be used.

**ERASE (ERASE):** The Erase (ERASE) instruction clears the designated memory location to a logical '1' state. After the Op Code and address location is inputted, the chip will enter into an erase cycle. When the cycle completes, the chip will automatically enter into standby mode.

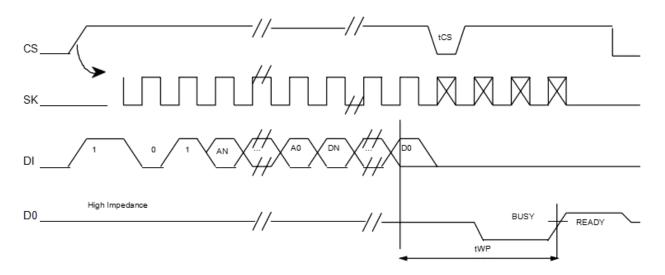

**WRITE (WRITE):** The Write (WRITE) instruction is used to write to a specific memory location. If word mode (x16) is selected, then 16 bits of data will be written into the location. If byte mode (x8) is chosen, then 8 bits of data will be written into the location. The write cycle will begin automatically after the 8 or 16 bits are shifted into the chip.

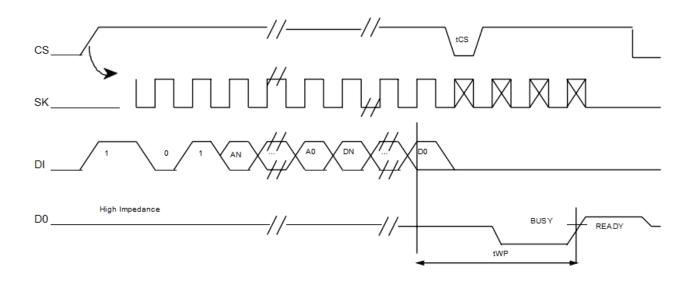

**ERASE ALL (ERAL):** The Erase All (ERAL) instruction is primarily used for testing purposes and only functions when Vcc=4.5 V to 5.5 V. This instruction will clear the entire memory array to '1'.

**WRITE ALL (WRAL):** The Write All (WRAL) instruction will program the entire memory array according to the 8 or 16-bit data pattern provided. The instruction will only be valid when Vcc=4.5 V to 5.5 V.

**ERASE/WRITE DISABLE (EWDS):** The Erase/Write Disable (EWDS) instruction blocks any kind of erase or program operations from modifying the contents of the memory array. This instruction should be executed after erasing or programming to prevent accidental data loss.

Note also that the READ instruction will operate regardless of whether the chip is disabled from program and write operations.

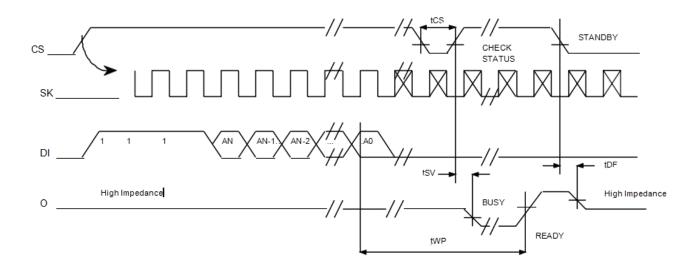

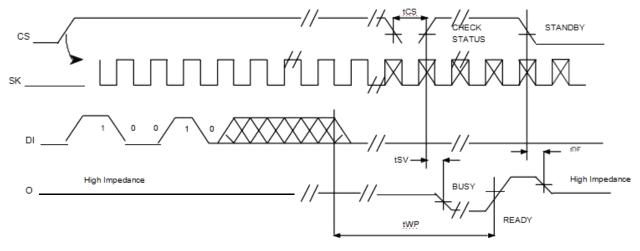

## Ready/Busy

To determine whether the chip has completed an erase or write operation, the CS signal can be pulled LOW for a minimum of 250 ns (tcs) and then pulled back HIGH to enter Ready/Busy mode.

If the chip is currently in the programming cycle, tWP, then the DO pin will go low (logical "0"). When the write cycle completes, the DO pin is pulled high (logical "1") to indicate that the part can receive another instruction. Note that the Ready/Busy polling cannot be done if the chip has already finished and returned back to standby mode.

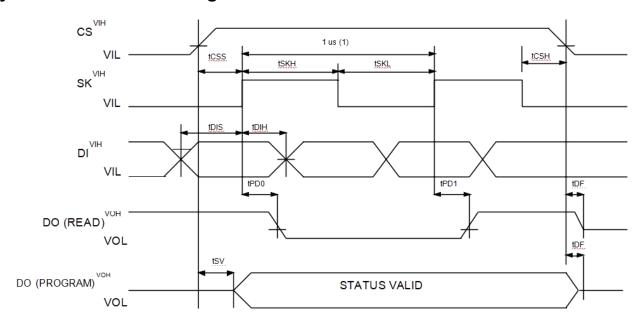

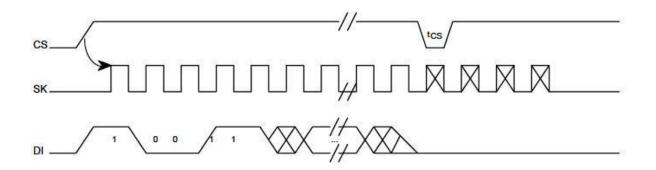

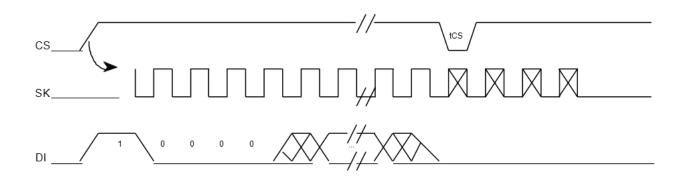

#### TIMING DIAGRAMS

## **Synchronous Data Timing**

Note (1): This is the minimum SK period.

Organization Key for Timing Diagrams

| I/O            | 93             | C46(1K)         | 93                            | C56(2K)                       | 93             | C66(4K)         |

|----------------|----------------|-----------------|-------------------------------|-------------------------------|----------------|-----------------|

|                | X8             | X16             | X8                            | X16                           | X8             | X16             |

| A <sub>N</sub> | A <sub>β</sub> | A <sub>5</sub>  | A <sub>8</sub> <sup>(1)</sup> | A <sub>7</sub> <sup>(2)</sup> | A <sub>8</sub> | A <sub>7</sub>  |

| D <sub>N</sub> | D <sub>7</sub> | D <sub>15</sub> | $D_7$                         | D <sub>15</sub>               | D <sub>7</sub> | D <sub>15</sub> |

#### Notes:

- A<sub>8</sub> is a DON'T CARE value, but the extra clock is required.

- A<sub>7</sub> is a DON'T CARE value, but the extra clock is required.

#### **READ TIMING**

#### **EWEN TIMING**

## **EWDS TIMING**

## **WRITE TIMING**

## **WRITE TIMING**

(1) Valid only at Vcc = 4.5V to 5.5V

## **ERASE TIMING**

## **ERAL TIMING1)**

(1) Valid only at Vcc = 4.5V to 5.5V

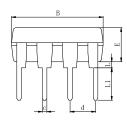

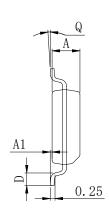

# **Physical Dimensions**

## DIP8

| Dimensions In Millimeters(DIP8) |      |      |      |      |      |      |      |      |      |      |          |

|---------------------------------|------|------|------|------|------|------|------|------|------|------|----------|

| Symbol:                         | Α    | В    | D    | D1   | Е    | L    | L1   | а    | b    | С    | d        |

| Min:                            | 6.10 | 9.00 | 8.40 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.85 | 0.40 | 2 F4 BCC |

| Max:                            | 6.68 | 9.50 | 9.00 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 | 2.54 BSC |

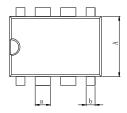

## SOP8

| Dimensions In Millimeters(SOP8) |      |      |      |      |      |      |    |      |          |  |

|---------------------------------|------|------|------|------|------|------|----|------|----------|--|

| Symbol:                         | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |

| Min:                            | 1.35 | 0.05 | 4.90 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 4 07 DCC |  |

| Max:                            | 1.55 | 0.20 | 5.10 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 BSC |  |

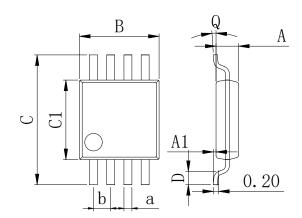

MSOP8

| Dimensions In Millimeters(MSOP8) |      |      |      |      |      |      |    |      |          |  |

|----------------------------------|------|------|------|------|------|------|----|------|----------|--|

| Symbol:                          | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |

| Min:                             | 0.80 | 0.05 | 2.90 | 4.75 | 2.90 | 0.35 | 0° | 0.25 | 0.65 BSC |  |

| Max:                             | 0.90 | 0.20 | 3.10 | 5.05 | 3.10 | 0.75 | 8° | 0.35 | 0.00 BSC |  |

# AT93C46A/56A/66A

#### IMPORTANT STATEMENT:

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by HGSEMI manufacturer:

Other Similar products are found below:

LV5065VB-TLM-H LV5066V-TLM-H LV5725JAZ-AH NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP6153MNTWG NCP81005MNTWG NCP81101BMNTXG NCP81205MNTXG SJ6522AG SJE6600 AZ7500BMTR-E1

IR35215MTRPBF SG3845DM NCP4204MNTXG NCP6132AMNR2G NCP81102MNTXG NCP81206MNTXG UBA2051C NCP1240AD065R2G NCP1240FD065R2G NCP1361BABAYSNT1G NCP1230P100G NX2124CSTR SG2845M NCP1366BABAYDR2G NCP81101MNTXG TEA19362T/1J NCP81174NMNTXG NCP4308DMTTWG NCP4308DMNTWG NCP4308AMTTWG NCP1366AABAYDR2G NCP1251FSN65T1G NCP1246BLD065R2G iW1760B-10 MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G NCP1365AABCYDR2G MCP1633T-E/MG MCP1633-E/MG NCV1397ADR2G NCP81599MNTXG NCP1246ALD065R2G AZ494AP-E1 NCP1247BD065R2G