# Remote 8-bit I/O expander for I<sub>2</sub>C-bus

## **FEATURES**

- Operating supply voltage 2.5 to 6 V

- Low standby current consumption of 10 μA maximum

- I<sup>2</sup>C to parallel port expander

- Open-drain interrupt output

- 8-bit remote I/O port for the I<sup>2</sup>C-bus

- Compatible with most microcontrollers

- Latched outputs with high current drive capability for directly driving LEDs

- Address by 3 hardware address pins for use of up to 8 devices (up to 16 with PCF8574A)

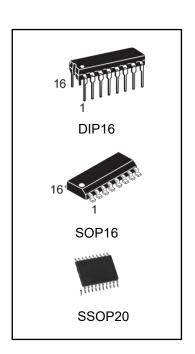

- DIP16, or space-saving SO16 or SSOP20 packages.

# **Ordering Information**

| DEVICE        | Package Type | MARKING  | Packing | Packing Qty  |

|---------------|--------------|----------|---------|--------------|

| PCF8574AN     | DIP16        | PCF8574A | TUBE    | 1000pcs/Box  |

| PCF8574AT/TR  | SOP16W       | PCF8574A | REEL    | 2500pcs/Reel |

| PCF8574AM/TR  | SOP16        | PCF8574A | REEL    | 2000pcs/Reel |

| PCF8574AMS/TR | SSOP20       | PCF8574A | REEL    | 2000pcs/Reel |

| PCF8574N      | DIP16        | PCF8574  | TUBE    | 1000pcs/Box  |

| PCF8574T/TR   | SOP16W       | PCF8574  | REEL    | 2500pcs/Reel |

| PCF8574M/TR   | SOP16        | PCF8574  | REEL    | 2000pcs/Reel |

| PCF8574MS/TR  | SSOP20       | PCF8574  | REEL    | 2000pcs/Reel |

### GENERAL DESCRIPTION

The PCF8574 is a silicon CMOS circuit. It provides general purpose remote I/O expansion for most microcontroller families via the two-line bidirectional bus (I<sup>2</sup>C).

The device consists of an 8-bit quasi-bidirectional port and an I<sup>2</sup>C-bus interface. The PCF8574 has a low current consumption and includes latched outputs with high current drive capability for directly driving LEDs. It also possesses an interrupt line (INT) which can be connected to the interrupt logic of the microcontroller. By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without having to communicate via the I<sup>2</sup>C-bus. This means that the PCF8574 can remain a simple slave device.

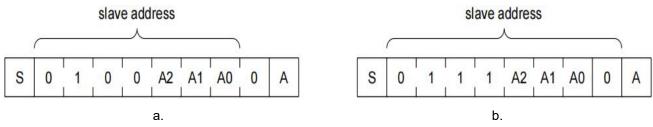

The PCF8574 and PCF8574A versions differ only in their slave address as shown in Fig.9.

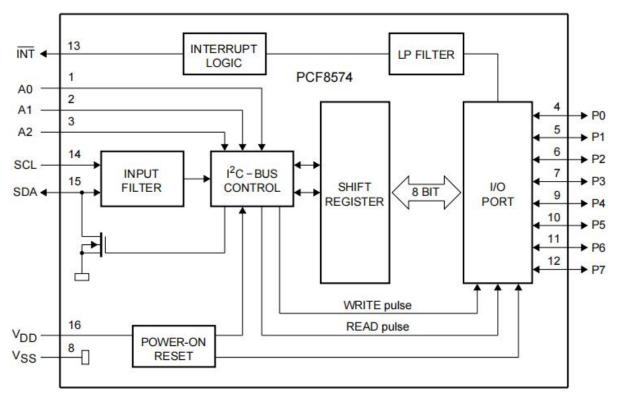

### **BLOCK DIAGRAM**

Fig.1 Block diagram

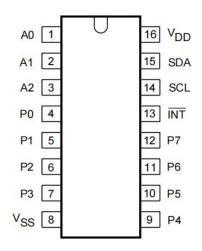

# **Connection Diagrams**

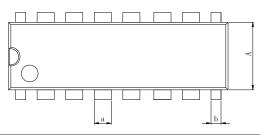

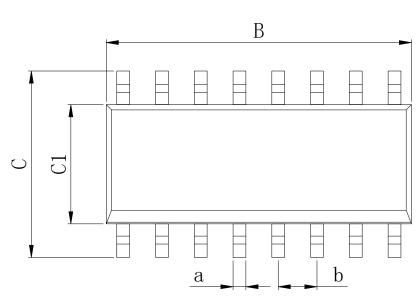

Fig.2 Pin configuration (DIP16; SO16).

Fig.3 Pin configuration (SSOP20).

# **PIN DESCRIPTION**

|        | P               | IN     |                               |

|--------|-----------------|--------|-------------------------------|

| SYMBOL | DIP16;<br>SOP16 | SSOP20 | DESCRIPTION                   |

| A0     | 1               | 6      | address input 0               |

| A1     | 2               | 7      | address input 1               |

| A2     | 3               | 9      | address input 2               |

| P0     | 4               | 10     | quasi-bidirectional I/O 0     |

| P1     | 5               | 11     | quasi-bidirectional I/O 1     |

| P2     | 6               | 12     | quasi-bidirectional I/O 2     |

| P3     | 7               | 14     | quasi-bidirectional I/O 3     |

| VSS    | 8               | 15     | supply ground                 |

| P4     | 9               | 16     | quasi-bidirectional I/O 4     |

| P5     | 10              | 17     | quasi-bidirectional I/O 5     |

| P6     | 11              | 19     | quasi-bidirectional I/O 6     |

| P7     | 12              | 20     | quasi-bidirectional I/O 7     |

| ĪNT    | 13              | 1      | interrupt output (active LOW) |

| SCL    | 14              | 2      | serial clock line             |

| SDA    | 15              | 4      | serial data line              |

| VDD    | 16              | 5      | supply voltage                |

| n.c.   |                 | 3      | not connected                 |

| n.c.   |                 | 8      | not connected                 |

| n.c.   |                 | 13     | not connected                 |

| n.c.   |                 | 18     | not connected                 |

#### CHARACTERISTICS OF THE I2C-BUS

The I<sup>2</sup>C-bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

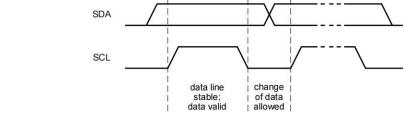

#### Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals (see Fig.4).

#### Start and stop conditions

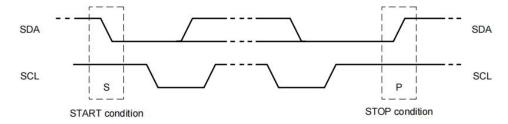

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the start condition (S).

A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the stop condition (P) (see Fig.5).

#### System configuration

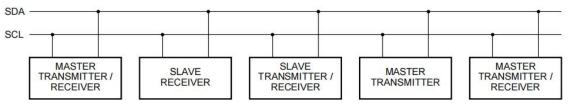

A device generating a message is a 'transmitter', a device receiving is the 'receiver'. The device that controls the message is the 'master' and the devices which are controlled by the master are the 'slaves' (see Fig.6).

Fig.4 Bit transfer.

Fig.5 Definition of start and stop conditions.

Fig.6 System configuration.

#### **Acknowledge**

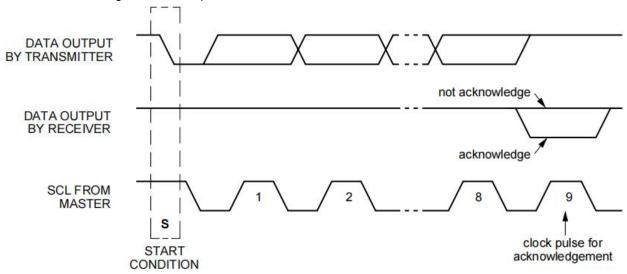

The number of data bytes transferred between the start and the stop conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter whereas the master generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse, set-up and hold times must be taken into account.

A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a stop condition.

Fig.7 Acknowledgment on the I<sup>2</sup>C-bus.

## **FUNCTIONAL DESCRIPTION**

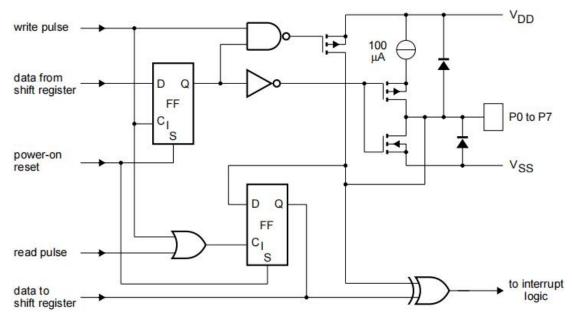

Fig.8 Simplified schematic diagram of each I/O.

# **Addressing**

For addressing see Figs 9, 10 and 11.

- (a) PCF8574.

- (b) PCF8574A.

Fig.9 PCF8574 and PCF8574A slave addresses.

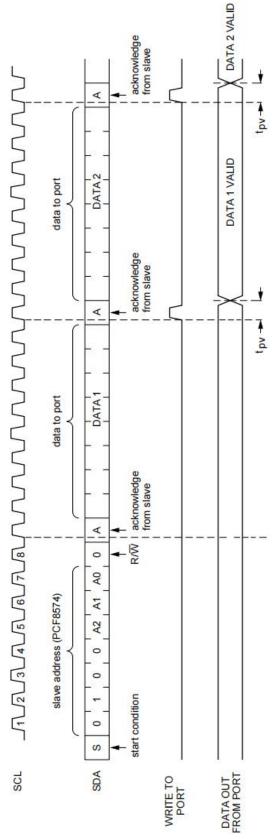

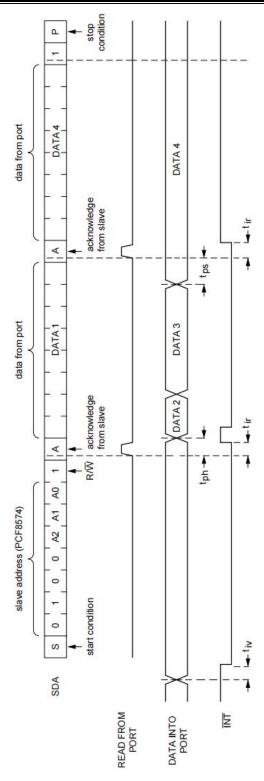

Each of the PCF8574's eight I/Os can be independently used as an input or output. Input data is transferred from the port to the microcontroller by the READ mode (see Fig.11). Output data is transmitted to the port by the WRITE mode (see Fig.10).

Fig.10 WRITE mode (output).

A LOW-to-HIGH transition of SDA, while SCL is HIGH is defined as the stop condition (P). Transfer of data can be stopped at any moment by a stop condition. When this occurs, data present at the last acknowledge phase is valid (output mode). Input data is lost.

Fig.11 READ mode (input).

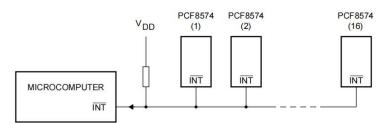

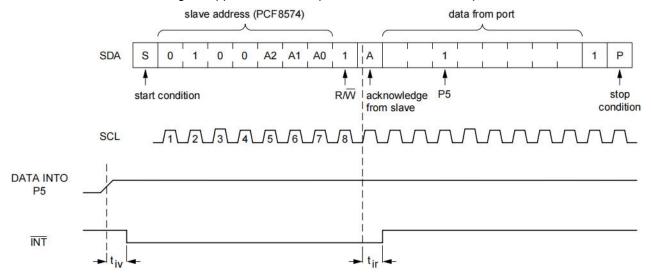

## Interrupt (see Figs 12 and 13)

The PCF8574 provides an open drain output ( $\overline{\text{INT}}$ ) which can be fed to a corresponding input of the microcontroller. This gives these chips a type of master function which can initiate an action elsewhere in the system.

An interrupt is generated by any rising or falling edge of the port inputs in the input mode. After time tiv the signal  $\overline{\text{INT}}$  is valid.

Resetting and reactivating the interrupt circuit is achieved when data on the port is changed to the original setting or data is read from or written to the port which has generated the interrupt.

Resetting occurs as follows:

- In the READ mode at the acknowledge bit after the rising edge of the SCL signal

- In the WRITE mode at the acknowledge bit after the HIGH-to-LOW transition of the SCL signal

- Interrupts which occur during the acknowledge clock pulse may be lost (or very short) due to the resetting

of the interrupt during this pulse.

Each change of the I/Os after resetting will be detected and, after the next rising clock edge, will be transmitted as  $\overline{\text{INT}}$ . Reading from or writing to another device does not affect the interrupt circuit.

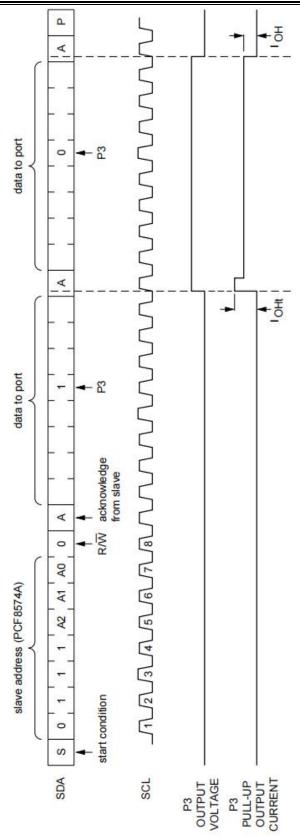

## Quasi-bidirectional I/Os (see Fig.14)

A quasi-bidirectional I/O can be used as an input or output without the use of a control signal for data direction. At power-on the I/Os are HIGH. In this mode only a current source to  $V_{DD}$  is active. An additional strong pull-up to  $V_{DD}$  allows fast rising edges into heavily loaded outputs. These devices turn on when an output is written HIGH, and are switched off by the negative edge of SCL. The I/Os should be HIGH before being used as inputs.

Fig.12 Application of multiple PCF8574s with interrupt.

Fig.13 Interrupt generated by a change of input to I/O P5.

Fig.14 Transient pull-up current I while P3 changes from LOW-to-HIGH and back to LOW.

# **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System

| SYMBOL           | PARAMETER                     | MIN.                  | MAX.           | UNIT                   |

|------------------|-------------------------------|-----------------------|----------------|------------------------|

| $V_{DD}$         | supply voltage                | -0.5                  | +7.0           | V                      |

| $V_{I}$          | input voltage                 | V <sub>SS</sub> - 0.5 | $V_{DD} + 0.5$ | V                      |

| l <sub>l</sub>   | DC input current              | -                     | 20             | mA                     |

| lo               | DC output current             | -                     | 25             | mA                     |

| I <sub>DD</sub>  | supply current                | -                     | 100            | mA                     |

| I <sub>SS</sub>  | supply current                | -                     | 100            | mA                     |

| P <sub>tot</sub> | total power dissipation       | -                     | 400            | mW                     |

| Po               | power dissipation per output  | -                     | 100            | mW                     |

| T <sub>stg</sub> | storage temperature           | -65                   | +150           | $^{\circ}\!\mathbb{C}$ |

| T <sub>amb</sub> | operating ambient temperature | -40                   | +85            | $^{\circ}$             |

### **HANDLING**

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take precautions appropriate to handling MOS devices.

## DC CHARACTERISTICS

$V_{DD}$  = 2.5 to 6 V;  $V_{SS}$  = 0 V; Tamb = -40 to +85 °C; unless otherwise specified.

| SYMBOL           | PARAMETER                | CONDITIONS                                                                                          | TIONS MIN.  |     | MAX.                  | UNIT |

|------------------|--------------------------|-----------------------------------------------------------------------------------------------------|-------------|-----|-----------------------|------|

| Supply           |                          |                                                                                                     |             |     |                       |      |

| $V_{DD}$         | supply voltage           |                                                                                                     | 2.5         |     | 6.0                   | V    |

| I <sub>DD</sub>  | supply current           | operating mode; $V_{DD}$ = 6 V;<br>no load; $V_{I}$ = $V_{DD}$ or $V_{SS}$ ;<br>$f_{SCL}$ = 100 kHz | -           | 40  | 100                   | μΑ   |

| I <sub>stb</sub> | standby current          | standby mode; $V_{DD}$ =6 V; no load; $V_{I}$ = $V_{DD}$ or $V_{SS}$                                | -           | 2.5 | 10                    | μΑ   |

| V <sub>POR</sub> | Power-on reset voltage   | $V_{DD} = 6 \text{ V}$ ; no load;<br>$V_{I} = V_{DD} \text{ or } V_{SS}$ ; note 1                   | -           | 1.3 | 2.4                   | V    |

| Input SCL;       | input/output SDA         |                                                                                                     |             |     |                       |      |

| $V_{IL}$         | LOW level input voltage  | -                                                                                                   | -0.5        | -   | +0.3V <sub>DD</sub>   | V    |

| V <sub>IH</sub>  | HIGH level input voltage | -                                                                                                   | $0.7V_{DD}$ | -   | V <sub>DD</sub> + 0.5 | V    |

| I <sub>OL</sub>  | LOW level output current | V <sub>OL</sub> = 0.4 V                                                                             | 3           | -   | -                     | mA   |

| Iι               | leakage current          | $V_I = V_{DD}$ or $V_{SS}$                                                                          | -1          | -   | +1                    | μΑ   |

| Ci               | input capacitance        | V <sub>I</sub> = V <sub>SS</sub>                                                                    | -           | -   | 7                     | pF   |

| SYMBOL                | PARAMETER                                               | CONDITIONS                                                                                        | MIN.        | TYP. | MAX.                  | UNIT |

|-----------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------|------|-----------------------|------|

|                       |                                                         | I/Os                                                                                              |             |      |                       |      |

| V <sub>IL</sub>       | LOW level input voltage                                 | -                                                                                                 | -0.5        | -    | +0.3V <sub>DD</sub>   | V    |

| V <sub>IH</sub>       | HIGH level input voltage                                | -                                                                                                 | $0.7V_{DD}$ | -    | V <sub>DD</sub> + 0.5 | V    |

| I <sub>IHL(max)</sub> | maximum allowed input current through protection diode  | $V_1 \ge V_{DD}$ or $V_1 \le V_{SS}$                                                              | -           | -    | 400                   | μΑ   |

| I <sub>OL</sub>       | LOW level output current                                | $V_{OL} = 1 \ V; V_{DD} = 5 \ V$                                                                  | 10          | 25   |                       | mA   |

| I <sub>OH</sub>       | HIGH level output current                               | V <sub>OH</sub> = V <sub>SS</sub>                                                                 | 30          | -    | 300                   | μΑ   |

| I <sub>OHt</sub>      | transient pull-up current                               | HIGH during acknowledge (see Fig.14); V <sub>OH</sub> = V <sub>SS</sub> ; V <sub>DD</sub> = 2.5 V | -           | -1   | -                     | mA   |

| Ci                    | input capacitance                                       | -                                                                                                 | -           | -    | 10                    | pF   |

| Co                    | output capacitance                                      | -                                                                                                 | -           | -    | 10                    | pF   |

| Port timing           | ; <b>C</b> <sub>L</sub> ≤ <b>100 pF</b> (see Figs 10 ar | nd 11)                                                                                            |             |      |                       |      |

| t <sub>pv</sub>       | output data valid                                       | -                                                                                                 | -           | -    | 4                     | μs   |

| t <sub>su</sub>       | input data set-up time                                  | -                                                                                                 | 0           | -    | -                     | μs   |

| t <sub>h</sub>        | input data hold time                                    | -                                                                                                 | 4           | -    | -                     | μs   |

| Interrupt II          | NT (see Fig.13)                                         |                                                                                                   |             |      |                       |      |

| I <sub>OL</sub>       | LOW level output current                                | V <sub>OL</sub> = 0.4 V                                                                           | 1.6         | -    | -                     | mA   |

| IL                    | leakage current                                         | $V_I = V_{DD}$ or $V_{SS}$                                                                        | -1          | -    | +1                    | μΑ   |

| TIMING; CL 5          | ≤ 100 pF                                                |                                                                                                   |             | •    |                       |      |

| t <sub>iv</sub>       | input data valid time                                   | -                                                                                                 | -           | -    | 4                     | μs   |

| t <sub>ir</sub>       | reset delay time                                        | -                                                                                                 | -           | -    | 4                     | μs   |

| Select inpu           | its A0 to A2                                            |                                                                                                   |             | •    |                       | -    |

| V <sub>IL</sub>       | LOW level input voltage                                 | -                                                                                                 | -0.5        | -    | +0.3V <sub>DD</sub>   | V    |

| V <sub>IH</sub>       | HIGH level input voltage                                | -                                                                                                 | $0.7V_{DD}$ | -    | V <sub>DD</sub> + 0.5 | V    |

| I <sub>LI</sub>       | input leakage current                                   | pin at V <sub>DD</sub> or V <sub>SS</sub>                                                         | -250        | -    | +250                  | nA   |

### Note

1. The Power-on reset circuit resets the I2C-bus logic with V<sub>DD</sub> < V<sub>POR</sub> and sets all I/Os to logic 1 (with current source to V<sub>DD</sub>).

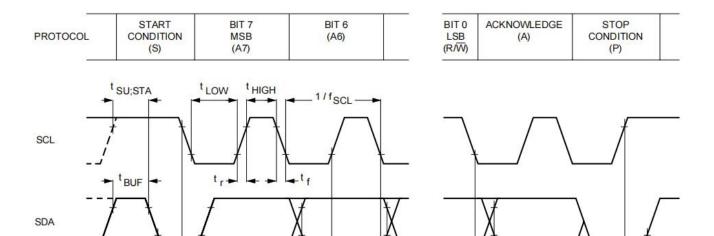

# I<sup>2</sup>C-BUS TIMING CHARACTERISTICS

| SYMBOL                                           | PARAMETER                    | MIN. | TYP. | MAX. | UNIT |  |  |  |

|--------------------------------------------------|------------------------------|------|------|------|------|--|--|--|

| I <sup>2</sup> C-BUS TIMING (see Fig.15; note 1) |                              |      |      |      |      |  |  |  |

| f <sub>SCL</sub>                                 | SCL clock frequency          | -    | -    | 100  | kHz  |  |  |  |

| t <sub>SW</sub>                                  | tolerable spike width on bus | -    | -    | 100  | ns   |  |  |  |

| t <sub>BUF</sub>                                 | bus free time                | 4.7  | -    | -    | μs   |  |  |  |

| t <sub>SU;STA</sub>                              | START condition set-up time  | 4.7  | -    | -    | μs   |  |  |  |

| t <sub>HD;STA</sub>                              | START condition hold time    | 4.0  | -    | -    | μs   |  |  |  |

| t <sub>LOW</sub>                                 | SCL LOW time                 | 4.7  | -    | -    | μs   |  |  |  |

| t <sub>HIGH</sub>                                | SCL HIGH time                | 4.0  | -    | -    | μs   |  |  |  |

| t <sub>r</sub>                                   | SCL and SDA rise time        | -    | -    | 1.0  | μs   |  |  |  |

| <b>t</b> f                                       | SCL and SDA fall time        | -    | -    | 0.3  | μs   |  |  |  |

| t <sub>SU;DAT</sub>                              | data set-up time             | 250  | -    | -    | ns   |  |  |  |

| t <sub>HD;DAT</sub>                              | data hold time               | 0    | -    | -    | ns   |  |  |  |

| t <sub>VD;DAT</sub>                              | SCL LOW to data out valid    | -    | -    | 3.4  | μs   |  |  |  |

| t <sub>SU;STO</sub>                              | STOP condition set-up time   | 4.0  | -    | -    | μs   |  |  |  |

### Note

1. All the timing values are valid within the operating supply voltage and ambient temperature range and refer to  $V_{IL}$  and  $V_{IH}$  with an input voltage swing of  $V_{SS}$  to  $V_{DD}$ .

Fig.15 I<sup>2</sup>C-bus timing diagram.

t HD;DAT

t SU;DAT

t<sub>VD;DAT</sub>

t HD;STA

t SU;STO

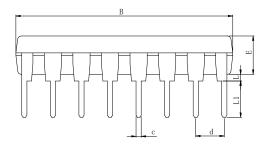

# **Physical Dimensions**

# DIP16

| Dimensions In Millimeters(DIP16) |      |       |      |      |      |      |      |      |      |      |          |

|----------------------------------|------|-------|------|------|------|------|------|------|------|------|----------|

| Symbol:                          | Α    | В     | D    | D1   | E    | L    | L1   | а    | b    | С    | d        |

| Min:                             | 6.10 | 18.94 | 8.40 | 7.42 | 3.10 | 0.50 | 300  | 1.50 | 0.85 | 0.40 | 2 F4 BCC |

| Max:                             | 6.68 | 19.56 | 9.00 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 | 2.54 BSC |

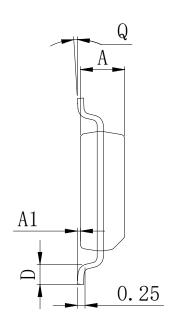

SOP16

| Dimensions In Millimeters(SOP16) |      |      |      |      |      |      |    |      |          |  |

|----------------------------------|------|------|------|------|------|------|----|------|----------|--|

| Symbol:                          | А    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |

| Min:                             | 1.35 | 0.05 | 9.80 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1.27 BSC |  |

| Max:                             | 1.55 | 0.20 | 10.0 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 BSC |  |

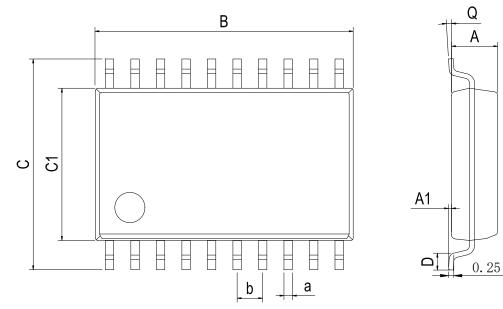

# **Physical Dimensions**

SOP20

| Dimensions In Millimeters(SOP20) |      |      |       |       |      |      |    |      |          |  |

|----------------------------------|------|------|-------|-------|------|------|----|------|----------|--|

| Symbol:                          | Α    | A1   | В     | С     | C1   | D    | Q  | а    | b        |  |

| Min:                             | 2.10 | 0.05 | 12.50 | 10.21 | 7.40 | 0.45 | 0° | 0.35 | 1 27 DSC |  |

| Max:                             | 2.50 | 0.25 | 13.00 | 10.61 | 7.60 | 1.25 | 8° | 0.45 | 1.27 BSC |  |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - I/O Expanders category:

Click to view products by HGSEMI manufacturer:

Other Similar products are found below:

PCA9654EDR2G LA79200V-TLM-E NLVPCA9535EDTR2G TC7SPN334L6X,LF(S PI4IOE5V9555LEX PI4IOE5V6534Q2ZLWEX PI4IOE5V6416Q2LEX 41700-100 PCF8574T/TR MCP23S18T-E/MJ PCA9539AHF,128 PCAL9554BPWJ MCP25050-E/P MCP23017T-E/ML MAX7301ATL+ MAX7301AAX+ MAX7311AUG+T PCF8575DB MAX7301AAX+T PCA9554PW.112 MIC74YQS TCA1116RTWR PI4IOE5V9535LEX PCA9671BS,118 PI4IOE5V9539ZDEX XRA1201PIG24TR-F TCA9535MRGER MCP23018T-E/MJ XRA1203IG24TR-F PI4IOE5V9535ZDEX PI4IOE5V96248ZLEX PI4IOE5V96224ZLEX MCP23S09T-E/SO SC16IS740IPW.112 PCAL6408AHKX PCAL6416AEVJ PCAL9535AHF,128 MCP23018T-E/SS CY8C9520A-24PVXIT CY8C9520A-24PVXI 20-101-1187 20-668-0030 PI4IOE5V6416ZDEX PCF8574P XD8574AP XD8574P XD8555-2 XD82C55-5 XD71055 ECE1088-DZK