## 3.3-V RS-485 TRANSCEIVERS

### **FEATURES**

- Operates With a 3.3-V Supply

- Bus-Pin ESD Protection Exceeds 16 kV HBM

- 1/8 Unit-Load Option Available (Up to 256 Nodes on the Bus)

- Optional Driver Output Transition Times for Signaling Rates (1) of 1 Mbps, 10 Mbps, and 32 Mbps

- Meets or Exceeds the Requirements of ANSI TIA/EIA-485-A

- Bus-Pin Short Circuit Protection From –7 V to 12 V

- Low-Current Standby Mode . . . 1 μA Typical

- Open-Circuit, Idle-Bus, and Shorted-Bus Failsafe Receiver

- Thermal Shutdown Protection

- Glitch-Free Power-Up and Power-Down Protection for Hot-Plugging Applications

### **APPLICATIONS**

- Digital Motor Control

- Utility Meters

- · Chassis-to-Chassis Interconnects

- Electronic Security Stations

- Industrial Process Control

- Building Automation

- Point-of-Sale (POS) Terminals and Networks

- The signaling rate of a line is the number of voltage transitions that are made per second expressed in the units bps (bits per second).

### DESCRIPTION

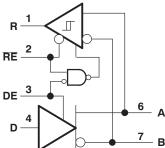

The SN65HVD10, SN65HVD11, and SN65HVD12, combine a 3-state differential line driver and differential input line receiver that operate with a single 3.3-V power supply. They are designed for balanced transmission lines and meet or exceed ANSI standard TIA/EIA-485-A and ISO 8482:1993. These differential bus transceivers are monolithic integrated circuits designed for bidirectional data communication on multipoint bus-transmission lines. The drivers and receivers have active-high and active-low enables respectively, that can be externally connected together to function as direction control. Very low device standby supply current can be achieved by disabling the driver and the receiver.

The driver differential outputs and receiver differential inputs connect internally to form a differential input/output (I/O) bus port that is designed to offer minimum loading to the bus whenever the driver is disabled or  $V_{\rm CC}=0$ . These parts feature wide positive and negative common-mode voltage ranges, making them suitable for party-line applications.

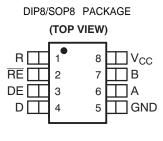

### ORDERING INFORMATION

| DEVICE          | Package Type | MARKING | Packing | Packing Qty  |

|-----------------|--------------|---------|---------|--------------|

| SN65HVD10EIN    | DIP8L        | 65HVD10 | TUBE    | 2000pcs/box  |

| SN65HVD11EIN    | DIP8L        | 65HVD11 | TUBE    | 2000pcs/box  |

| SN65HVD12EIN    | DIP8L        | 65HVD12 | TUBE    | 2000pcs/box  |

| SN65HVD10EIM/TR | SOP8L        | 65HVD10 | REEL    | 2500pcs/reel |

| SN65HVD11EIM/TR | SOP8L        | 65HVD11 | REEL    | 2500pcs/reel |

| SN65HVD12EIM/TR | SOP8L        | 65HVD12 | REEL    | 2500pcs/reel |

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted (1) (2)

|                 |                                       |                                      |                         | UNIT                              |

|-----------------|---------------------------------------|--------------------------------------|-------------------------|-----------------------------------|

| V <sub>CC</sub> | Supply voltage ran                    | nge                                  |                         | −0.3 V to 6 V                     |

|                 | Voltage range at A                    | A or B                               |                         | –9 V to 14 V                      |

|                 | Input voltage range at D, DE, R or RE |                                      |                         | -0.5 V to V <sub>CC</sub> + 0.5 V |

|                 | Voltage input rang                    | e, transient pulse, A and B, through | gh 100 Ω, see Figure 11 | –50 V to 50 V                     |

| lo              | Receiver output current               |                                      |                         | -11 mA to 11 mA                   |

|                 |                                       |                                      | A, B, and GND           | ±16 kV                            |

|                 | Electrostatic discharge               | Human body model <sup>(3)</sup>      | All pins                | ±4 kV                             |

|                 |                                       | Charged-device model (4)             | All pins charge         | ±1 kV                             |

|                 | Continuous total power dissipation    |                                      |                         | See Dissipation Rating Table      |

|                 | Electrical Fast Tra                   | nsient/Burst <sup>(5)</sup>          | A, B, and GND           | ±4 kV                             |

| TJ              | Junction temperate                    | ure                                  |                         | 170°C                             |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(5)</sup> Tested in accordance with IEC 61000-4-4.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

Tested in accordance with JEDEC Standard 22, Test Method A114-A and IEC 60749-26. Tested in accordance with JEDEC Standard 22, Test Method C101.

### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range unless otherwise noted

|                                   |                                       |                    | MIN               | NOM | MAX             | UNIT |

|-----------------------------------|---------------------------------------|--------------------|-------------------|-----|-----------------|------|

| V <sub>CC</sub>                   | Supply voltage                        |                    | 3                 |     | 3.6             |      |

| V <sub>I</sub> or V <sub>IC</sub> | Voltage at any bus terminal (separate | ly or common mode) | -7 <sup>(1)</sup> |     | 12              |      |

| V <sub>IH</sub>                   | High-level input voltage              | D, DE, RE          | 2                 |     | V <sub>CC</sub> | V    |

| V <sub>IL</sub>                   | Low-level input voltage               | D, DE, RE          | 0                 |     | 0.8             |      |

| V <sub>ID</sub>                   | Differential input voltage            | Figure 7           | -12               |     | 12              |      |

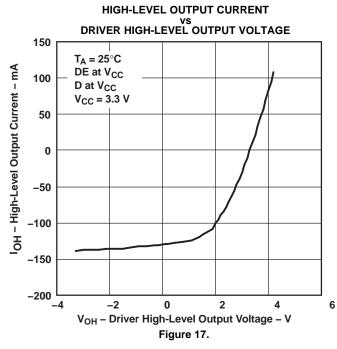

|                                   | High level autout august              | Driver             | -60               |     |                 | A    |

| Іон                               | High-level output current             | Receiver           | -8                |     |                 | mA   |

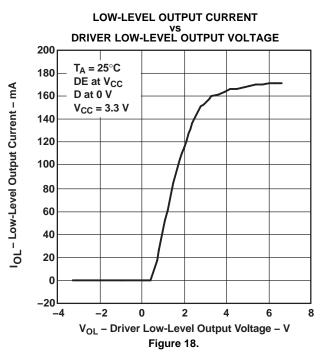

|                                   | Lave lavel autout average             | Driver             |                   |     | 60              | A    |

| I <sub>OL</sub>                   | Low-level output current              | Receiver           |                   |     | 8               | mA   |

| $R_L$                             | Differential load resistance          |                    | 54                | 60  |                 | Ω    |

| C <sub>L</sub>                    | Differential load capacitance         |                    |                   | 50  |                 | pF   |

|                                   |                                       | HVD10              |                   |     | 32              |      |

|                                   | Signaling rate                        | HVD11              |                   |     | 10              | Mbps |

|                                   |                                       | HVD12              |                   |     | 1               |      |

| T <sub>J</sub> <sup>(2)</sup>     | Junction temperature                  |                    |                   |     | 145             | °C   |

The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

### DRIVER ELECTRICAL CHARACTERISTICS

over recommended operating conditions unless otherwise noted

|                     | PARAMETER                                   |            | TES                                                                        | T CONDITIONS                                    | MIN       | TYP <sup>(1)</sup> | MAX      | UNIT |

|---------------------|---------------------------------------------|------------|----------------------------------------------------------------------------|-------------------------------------------------|-----------|--------------------|----------|------|

| V <sub>IK</sub>     | Input clamp voltage                         |            | $I_1 = -18 \text{ mA}$                                                     |                                                 | -1.5      |                    |          | V    |

|                     |                                             |            | I <sub>O</sub> = 0                                                         |                                                 | 2         |                    | $V_{CC}$ |      |

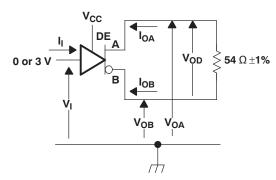

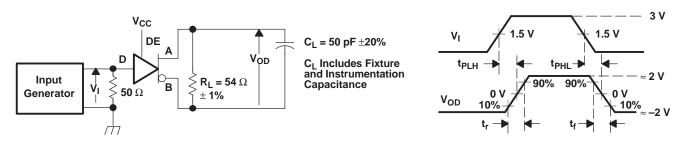

| $ V_{OD} $          | Differential output voltage (2)             |            | $R_L = 54 \Omega$ , See                                                    | Figure 1                                        | 1.5       |                    |          | V    |

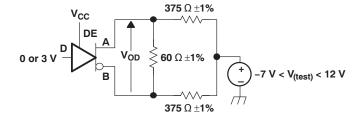

|                     |                                             |            | $V_{\text{test}} = -7 \text{ V to } 1$                                     | 2 V, See Figure 2                               | 1.5       |                    |          |      |

| $\Delta  V_{OD} $   | Change in magnitude of differential voltage | output     | See Figure 1 an                                                            | d Figure 2                                      | -0.2      |                    | 0.2      | V    |

| V <sub>OC(PP)</sub> | Peak-to-peak common-mode output             | voltage    |                                                                            |                                                 |           | 400                |          | mV   |

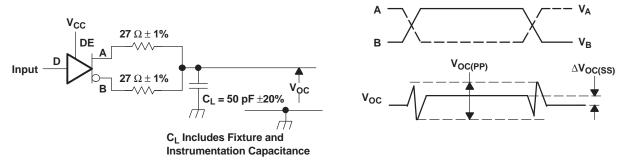

| $V_{OC(SS)}$        | Steady-state common-mode output             | voltage    | See Figure 3                                                               |                                                 | 1.4       |                    | 2.5      | V    |

| $\Delta V_{OC(SS)}$ | Change in steady-state common-movoltage     | ode output | - Occ riguic o                                                             |                                                 | -0.0<br>5 |                    | 0.05     | V    |

| I <sub>OZ</sub>     | High-impedance output current               |            | See receiver input currents                                                |                                                 |           |                    |          |      |

|                     | Input current                               | D          |                                                                            |                                                 | -100      |                    | 0        |      |

| l <sub>l</sub>      | input current                               | DE         |                                                                            |                                                 | 0         |                    | 100      | μA   |

| Ios                 | Short-circuit output current                |            | $-7 \text{ V} \leq \text{V}_{\text{O}} \leq 12 \text{ V}$                  |                                                 | -250      |                    | 250      | mA   |

| C <sub>(OD)</sub>   | Differential output capacitance             |            | $V_{OD} = 0.4 \sin (4)$                                                    | E6πt) + 0.5 V, DE at 0 V                        |           | 16                 |          | pF   |

|                     |                                             |            | RE at V <sub>CC</sub> ,<br>D & DE at V <sub>CC</sub> ,<br>No load          | Receiver disabled and driver enabled            |           | 9                  | 15.5     | mA   |

| I <sub>CC</sub>     | Supply current                              |            | RE at V <sub>CC</sub> ,<br>D at V <sub>CC</sub> ,<br>DE at 0 V,<br>No load | Receiver disabled and driver disabled (standby) |           | 1                  | 5        | μΑ   |

|                     |                                             |            | RE at 0 V,<br>D & DE at V <sub>CC</sub> ,<br>No load                       | Receiver enabled and driver enabled             |           | 9                  | 15.5     | mA   |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3-V supply. (2) For  $T_A > 85$ °C,  $V_{CC}$  is ±5%.

See thermal characteristics table for information regarding this specification.

### **DRIVER SWITCHING CHARACTERISTICS**

over recommended operating conditions unless otherwise noted

|                         | PARAMETER                                           |       | TEST CONDITIONS                                              | MIN                 | TYP <sup>(1)</sup> | MAX       | UNIT |  |

|-------------------------|-----------------------------------------------------|-------|--------------------------------------------------------------|---------------------|--------------------|-----------|------|--|

|                         |                                                     | HVD10 |                                                              | 5                   | 8.5                | 16        |      |  |

| t <sub>PLH</sub>        | Propagation delay time, low-to-high-level output    | HVD11 |                                                              | 18                  | 25                 | 40        | ns   |  |

|                         |                                                     | HVD12 |                                                              | 135                 | 200                | 300       |      |  |

|                         |                                                     | HVD10 |                                                              | 5                   | 8.5                | 16        |      |  |

| t <sub>PHL</sub>        | Propagation delay time, high-to-low-level output    | HVD11 |                                                              | 18                  | 25                 | 40        | ns   |  |

|                         |                                                     | HVD12 |                                                              | 135                 | 200                | 300       |      |  |

|                         |                                                     | HVD10 |                                                              | 3                   | 4.5                | 10        |      |  |

| t <sub>r</sub>          | Differential output signal rise time                | HVD11 | $R_L = 54 \Omega$ , $C_L = 50 pF$ ,<br>See Figure 4          | 10                  | 20                 | 30        | ns   |  |

|                         |                                                     | HVD12 | Jee rigule 4                                                 | 100                 | 170                | 300       |      |  |

|                         |                                                     | HVD10 |                                                              | 3                   | 4.5                | 10        |      |  |

| t <sub>f</sub>          | Differential output signal fall time                | HVD11 |                                                              | 10                  | 20                 | 30        | ns   |  |

|                         | •                                                   | HVD12 |                                                              | 100                 | 170                | 300       |      |  |

|                         |                                                     | HVD10 |                                                              |                     |                    | 1.5       |      |  |

| t <sub>sk(p)</sub>      | Pulse skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  ) | HVD11 |                                                              |                     |                    | 2.5       | ns   |  |

| SK(P)                   | (111)                                               | HVD12 |                                                              |                     |                    | 7         |      |  |

|                         | Part-to-part skew                                   | HVD10 |                                                              |                     |                    | 6         | ns   |  |

| t <sub>sk(pp)</sub> (2) |                                                     | HVD11 |                                                              |                     |                    | 11        |      |  |

| σκ(ρρ)                  |                                                     | HVD12 |                                                              |                     |                    | 100       |      |  |

|                         |                                                     | HVD10 |                                                              |                     |                    | 31        |      |  |

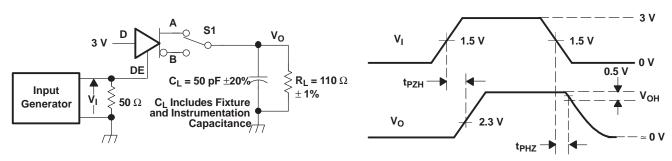

| t <sub>PZH</sub>        | Propagation delay time, high-impedance-to-high-     | HVD11 |                                                              |                     | 55                 |           | ns   |  |

| 1 211                   | level output                                        | HVD12 | $R_L = 110 \Omega$ , $\overline{RE}$ at 0 V,                 |                     |                    |           |      |  |

|                         |                                                     | HVD10 | See Figure 5                                                 | 110 32, TCL at 0 V, |                    | 300<br>25 |      |  |

| t <sub>PHZ</sub>        | Propagation delay time, high-level-to-high-         | HVD11 |                                                              | 55                  |                    |           | ns   |  |

| THE                     | impedance output                                    | HVD12 |                                                              | 300                 |                    |           |      |  |

|                         |                                                     | HVD10 |                                                              |                     |                    | 26        |      |  |

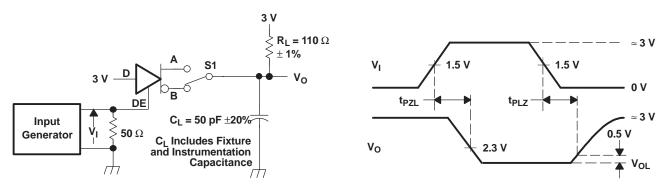

| t <sub>PZL</sub>        | Propagation delay time, high-impedance-to-low-      | HVD11 |                                                              |                     |                    | 55        | ns   |  |

| *FZL                    | level output                                        | HVD12 | $R_L = 110 \Omega, \overline{RE} \text{ at } 0 \text{ V},$   |                     |                    | 300       |      |  |

|                         |                                                     | HVD10 | See Figure 6                                                 |                     |                    | 26        |      |  |

| $t_{PLZ}$               | Propagation delay time, low-level-to-high-          | HVD11 | _                                                            |                     |                    | 75        | ns   |  |

| 4PLZ                    | impedance output                                    | HVD12 |                                                              |                     |                    | 400       | 110  |  |

| t <sub>PZH</sub>        | Propagation delay time, standby-to-high-level outp  |       | $R_L = 110 \Omega$ , $\overline{RE}$ at 3 V,<br>See Figure 5 |                     |                    | 6         | μs   |  |

| t <sub>PZL</sub>        | Propagation delay time, standby-to-low-level output | t     | $R_L = 110 \Omega$ , $\overline{RE}$ at 3 V,<br>See Figure 6 |                     |                    | 6         | μs   |  |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3-V supply.

(2) t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

### RECEIVER ELECTRICAL CHARACTERISTICS

over recommended operating conditions unless otherwise noted

| PARAMETER        |                                                           | TEST CONDITIONS                                                            |                                                 |                              | MIN   | TYP <sup>(1)</sup> | MAX   | UNIT |

|------------------|-----------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------|------------------------------|-------|--------------------|-------|------|

| V <sub>IT+</sub> | Positive-going input threshold voltage                    | $I_O = -8 \text{ mA}$                                                      |                                                 |                              |       | -0.065             | -0.01 |      |

| $V_{IT-}$        | Negative-going input threshold voltage                    | I <sub>O</sub> = 8 mA                                                      |                                                 |                              | -0.2  | -0.1               |       | V    |

| V <sub>hys</sub> | Hysteresis voltage (V <sub>IT+</sub> - V <sub>IT-</sub> ) |                                                                            |                                                 |                              |       | 35                 |       | mV   |

| $V_{IK}$         | Enable-input clamp voltage                                | $I_I = -18 \text{ mA}$                                                     |                                                 |                              | -1.5  |                    |       | V    |

| $V_{OH}$         | High-level output voltage                                 | $V_{ID} = 200 \text{ mV},$                                                 | $I_{OH} = -8 \text{ mA},$                       | See Figure 7                 | 2.4   |                    |       | V    |

| $V_{OL}$         | Low-level output voltage                                  | $V_{ID} = -200 \text{ mV},$                                                | $I_{OL} = 8 \text{ mA},$                        | See Figure 7                 |       |                    | 0.4   | V    |

| loz              | High-impedance-state output current                       | $V_O = 0$ or $V_{CC}$                                                      | $\overline{\text{RE}}$ at $V_{\text{CC}}$       |                              | -1    |                    | 1     | μΑ   |

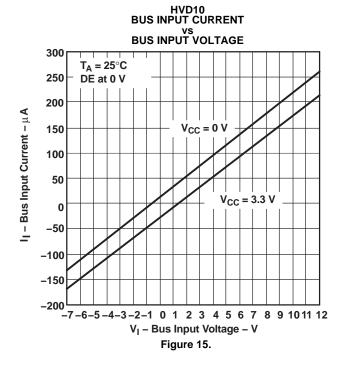

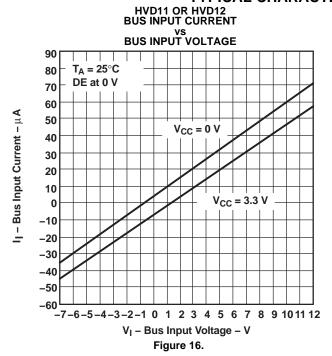

|                  |                                                           | $V_A$ or $V_B = 12 V$                                                      |                                                 |                              |       | 0.05               | 0.11  |      |

|                  |                                                           | $V_A$ or $V_B = 12 V$ ,                                                    | $V_{CC} = 0 V$                                  | HVD11, HVD12,                |       | 0.06               | 0.13  | A    |

| I <sub>I</sub>   | Bus input current                                         | $V_A$ or $V_B = -7 \text{ V}$                                              |                                                 | Other input at 0 V           | -0.1  | -0.05              |       | mA   |

|                  |                                                           | $V_A$ or $V_B = -7 V$ ,                                                    | $V_{CC} = 0 V$                                  |                              | -0.05 | -0.04              |       |      |

|                  |                                                           | $V_A$ or $V_B = 12 V$                                                      |                                                 |                              |       | 0.2                | 0.5   | mA   |

|                  |                                                           | $V_A$ or $V_B = 12 V$ ,                                                    | V <sub>CC</sub> = 0 V                           | HVD10,<br>Other input at 0 V |       | 0.25               | 0.5   |      |

|                  |                                                           | $V_A$ or $V_B = -7 \text{ V}$                                              |                                                 |                              | -0.4  | -0.2               |       |      |

|                  |                                                           | $V_A$ or $V_B = -7 V$ ,                                                    | $V_{CC} = 0 V$                                  |                              | -0.4  | -0.15              |       |      |

| I <sub>IH</sub>  | High-level input current, RE                              | V <sub>IH</sub> = 2 V                                                      |                                                 |                              | -30   |                    | 0     | μΑ   |

| I <sub>IL</sub>  | Low-level input current, RE                               | V <sub>IL</sub> = 0.8 V                                                    |                                                 |                              | -30   |                    | 0     | μΑ   |

| C <sub>ID</sub>  | Differential input capacitance                            | V <sub>ID</sub> = 0.4 sin (4E6                                             | πt) + 0.5 V, DE a                               | at 0 V                       |       | 15                 |       | pF   |

|                  |                                                           | RE at 0 V,<br>D & DE at 0 V,<br>No load                                    | Receiver enabled and driver disabled            |                              |       | 4                  | 8     | mA   |

| I <sub>CC</sub>  | Supply current                                            | RE at V <sub>CC</sub> ,<br>D at V <sub>CC</sub> ,<br>DE at 0 V,<br>No load | Receiver disabled and driver disabled (standby) |                              |       | 1                  | 5     | μA   |

|                  |                                                           | RE at 0 V,<br>D & DE at V <sub>CC</sub> ,<br>No load                       | Receiver enabled and driver enabled             |                              |       | 9                  | 15.5  | mA   |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3-V supply.

### RECEIVER SWITCHING CHARACTERISTICS

over recommended operating conditions unless otherwise noted

|                                 | PARAMETER                                            |                | TEST CONDITIONS                                    | MIN  | TYP <sup>(1)</sup> | MAX | UNIT |

|---------------------------------|------------------------------------------------------|----------------|----------------------------------------------------|------|--------------------|-----|------|

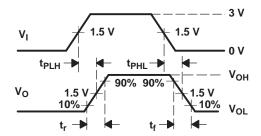

| t <sub>PLH</sub>                | Propagation delay time, low-to-high-level output     | HVD10          |                                                    | 12.5 | 20                 | 25  | 20   |

| t <sub>PHL</sub>                | Propagation delay time, high-to-low-level output     | HVD10          |                                                    | 12.5 | 20                 | 25  | ns   |

| t <sub>PLH</sub>                | Propagation delay time, low-to-high-level output     | HVD11<br>HVD12 | $V_{ID} = -1.5 \text{ V to } 1.5 \text{ V},$       | 30   | 55                 | 70  | ns   |

| t <sub>PHL</sub>                | Propagation delay time, high-to-low-level output     | HVD11<br>HVD12 | C <sub>L</sub> = 15 pF,<br>See Figure 8            | 30   | 55                 | 70  | ns   |

|                                 |                                                      | HVD10          |                                                    |      |                    | 1.5 |      |

| t <sub>sk(p)</sub>              | Pulse skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  )  | HVD11          |                                                    |      |                    | 4   | ns   |

|                                 |                                                      | HVD12          |                                                    |      |                    | 4   |      |

|                                 |                                                      | HVD10          |                                                    |      |                    | 8   |      |

| t <sub>sk(pp)</sub> (2)         | Part-to-part skew                                    | HVD11          |                                                    |      |                    | 15  | ns   |

|                                 |                                                      | HVD12          |                                                    |      |                    | 15  |      |

| t <sub>r</sub>                  | Output signal rise time                              |                | C <sub>L</sub> = 15 pF,                            | 1    | 2                  | 5   | 20   |

| t <sub>f</sub>                  | Output signal fall time                              |                | See Figure 8                                       | 1    | 2                  | 5   | ns   |

| t <sub>PZH</sub> <sup>(1)</sup> | Output enable time to high level                     |                |                                                    |      |                    | 15  |      |

| t <sub>PZL</sub> <sup>(1)</sup> | Coutput enable time to low level                     |                | $C_1 = 15 \text{ pF}, DE \text{ at } 3 \text{ V},$ |      |                    | 15  |      |

| t <sub>PHZ</sub>                |                                                      |                | See Figure 9                                       |      |                    | 20  | ns   |

| t <sub>PLZ</sub>                | Output disable time from low level                   |                |                                                    |      |                    | 15  |      |

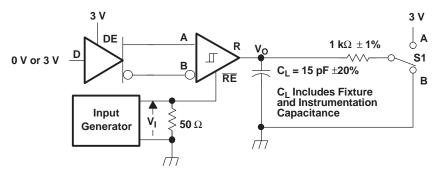

| t <sub>PZH</sub> (2)            | Propagation delay time, standby-to-high-level output |                | $C_1 = 15 \text{ pF}, DE \text{ at } 0,$           |      |                    | 6   |      |

| t <sub>PZL</sub> (2)            | Propagation delay time, standby-to-low-level outp    | ut             | See Figure 10                                      |      |                    | 6   | μs   |

### PARAMETER MEASUREMENT INFORMATION

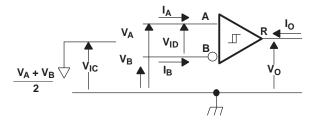

Figure 1. Driver V<sub>OD</sub> Test Circuit and Voltage and Current Definitions

Figure 2. Driver V<sub>OD</sub> With Common-Mode Loading Test Circuit

All typical values are at 25°C and with a 3.3-V supply  $t_{sk(pp)}$  is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

Input: PRR = 500 kHz, 50% Duty Cycle, $t_r$ <6ns,  $t_f$ <6ns,  $Z_O$  = 50  $\Omega$

Figure 3. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

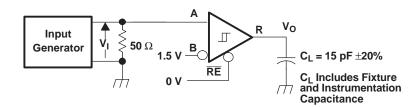

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_{r}$  <6 ns,  $t_{f}$  <6 ns,  $Z_{o}$  = 50  $\Omega$

Figure 4. Driver Switching Test Circuit and Voltage Waveforms

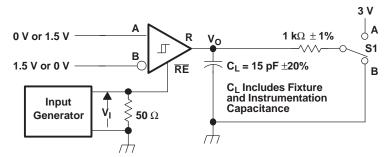

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_{r}$  <6 ns,  $t_{f}$  <6 ns,  $Z_{o}$  = 50  $\Omega$

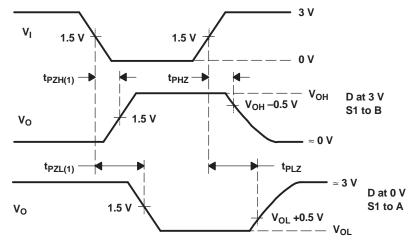

Figure 5. Driver High-Level Enable and Disable Time Test Circuit and Voltage Waveforms

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_r$  <6 ns,  $t_f$  <6 ns,  $Z_o$  = 50  $\Omega$

Figure 6. Driver Low-Level Output Enable and Disable Time Test Circuit and Voltage Waveforms

Figure 7. Receiver Voltage and Current Definitions

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_r$  <6 ns,  $t_f$  <6 ns,  $Z_o$  = 50  $\Omega$

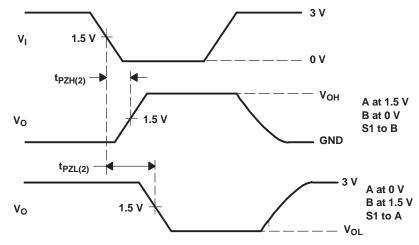

Figure 8. Receiver Switching Test Circuit and Voltage Waveforms

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_r$  <6 ns,  $t_f$  <6 ns,  $Z_o$  = 50  $\Omega$

Figure 9. Receiver Enable and Disable Time Test Circuit and Voltage Waveforms With Drivers Enabled

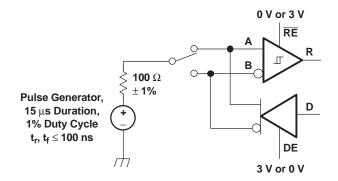

Generator: PRR = 100 kHz, 50% Duty Cycle,  $\rm t_r$  <6 ns,  $\rm t_f$  <6 ns,  $\rm Z_0$  = 50  $\rm \Omega$

Figure 10. Receiver Enable Time From Standby (Driver Disabled)

NOTE: This test is conducted to test survivability only. Data stability at the R output is not specified.

Figure 11. Test Circuit, Transient Over Voltage Test

# PARAMETER MEASUREMENT INFORMATION (continued) FUNCTION TABLES

Table 1. DRIVER<sup>(1)</sup>

|            |              | OUTPUTS |   |  |

|------------|--------------|---------|---|--|

| INPUT<br>D | ENABLE<br>DE | Α       | В |  |

| Н          | Н            | Н       | L |  |

| L          | Н            | L       | Н |  |

| X          | L            | Z       | Z |  |

| Open       | Н            | Н       | L |  |

<sup>(1)</sup> H = high level; L = low level; Z = high impedance; X = irrelevant; ? = indeterminate

Table 2. RECEIVER<sup>(1)</sup>

| DIFFERENTIAL INPUTS $V_{ID} = V_A - V_B$                  | ENABLE<br>RE | OUTPUT<br>R |

|-----------------------------------------------------------|--------------|-------------|

| V <sub>ID</sub> ≤ -0.2 V                                  | L            | L           |

| $-0.2 \text{ V} < \text{V}_{\text{ID}} < -0.01 \text{ V}$ | L            | ?           |

| -0.01 V ≤ V <sub>ID</sub>                                 | L            | Н           |

| X                                                         | Н            | Z           |

| Open Circuit                                              | L            | Н           |

| Short circuit                                             | L            | Н           |

<sup>(1)</sup> H = high level; L = low level; Z = high impedance; X = irrelevant; ? = indeterminate

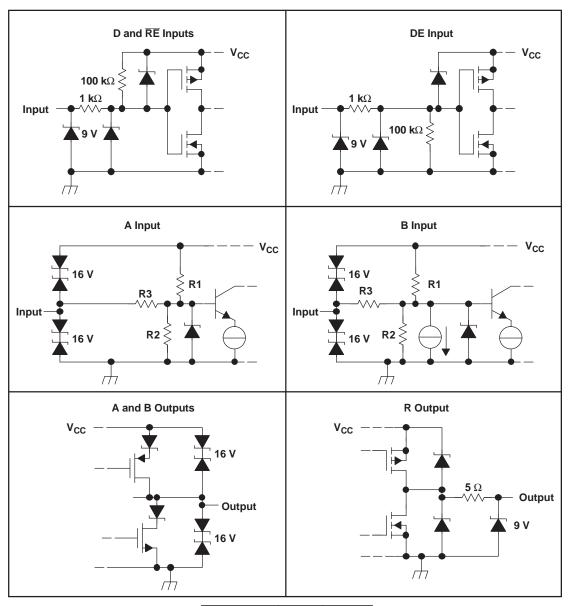

### **EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS**

|           | R1/R2         | R3             |

|-----------|---------------|----------------|

| SN65HVD10 | <b>9 k</b> Ω  | <b>45 k</b> Ω  |

| SN65HVD11 | <b>36 k</b> Ω | <b>180 k</b> Ω |

| SN65HVD12 | <b>36 k</b> Ω | <b>180 k</b> Ω |

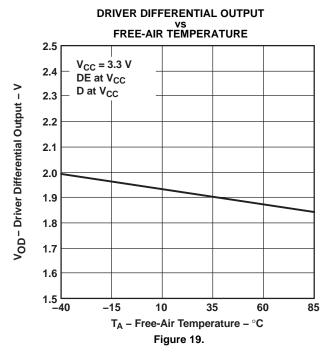

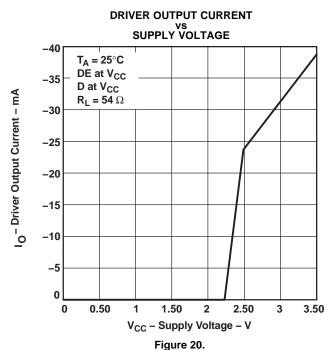

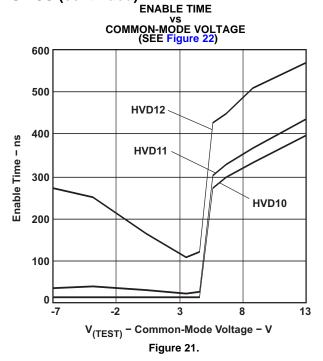

### TYPICAL CHARACTERISTICS

### **TYPICAL CHARACTERISTICS (continued)**

## **TYPICAL CHARACTERISTICS (continued)**

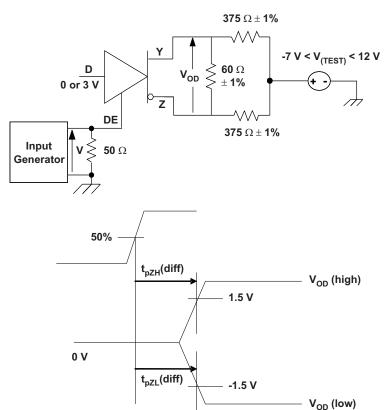

Figure 22. Driver Enable Time From DE to  $V_{\rm OD}$

The time  $t_{PZL}(x)$  is the measure from DE to  $V_{OD}(x)$ .  $V_{OD}$  is valid when it is greater than 1.5 V.

### **APPLICATION INFORMATION**

| Device | Number of Devices on Bus |

|--------|--------------------------|

| HVD10  | 64                       |

| HVD11  | 256                      |

| HVD12  | 256                      |

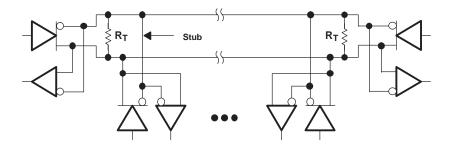

NOTE: The line should be terminated at both ends with its characteristic impedance (R<sub>T</sub> = Z<sub>O</sub>). Stub lengths off the main line should be kept as short as possible.

Figure 23. Typical Application Circuit

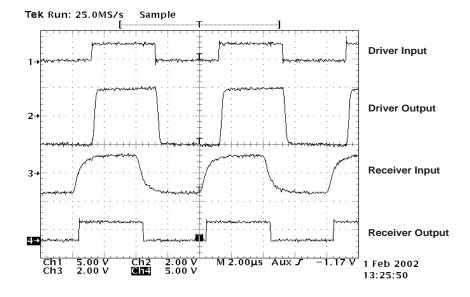

Figure 24. HVD12 Input and Output Through 2000 Feet of Cable

An example application for the HVD12 is illustrated in Figure 23. Two HVD12 transceivers are used to communicate data through a 2000 foot (600 m) length of Commscope 5524 category 5e+ twisted pair cable. The bus is terminated at each end by a  $100-\Omega$  resistor, matching the cable characteristic impedance. Figure 24 illustrates operation at a signaling rate of 250 kbps.

### **LOW-POWER STANDBY MODE**

When both the driver and receiver are disabled (DE low and RE high) the device is in standby mode. If the enable inputs are in this state for less than 60 ns, the device does not enter standby mode. This guards against inadvertently entering standby mode during driver/receiver enabling. Only when the enable inputs are held in this state for 300 ns or more, the device is assured to be in standby mode. In this low-power standby mode, most internal circuitry is powered down, and the supply current is typically less than 1 nA. When either the driver or the receiver is re-enabled, the internal circuitry becomes active.

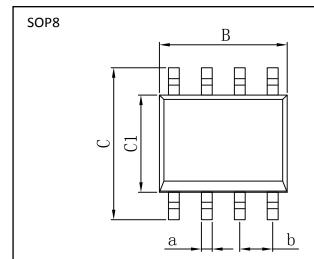

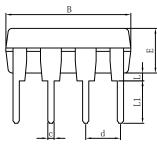

### **PACKAGE**

| Dimensions In Millimeters |       |       |         |           |       |  |  |  |

|---------------------------|-------|-------|---------|-----------|-------|--|--|--|

| Symbol:                   | Min:  | Max:  | Symbol: | Min:      | Max:  |  |  |  |

| Α                         | 1.225 | 1.570 | D       | 0.400     | 0.950 |  |  |  |

| A1                        | 0.100 | 0.250 | Q       | 0°        | 8°    |  |  |  |

| В                         | 4.800 | 5.100 | а       | 0.420 TYP |       |  |  |  |

| С                         | 5.800 | 6.250 | b       | 1.270 TYP |       |  |  |  |

| C1                        | 3.800 | 4.000 |         |           |       |  |  |  |

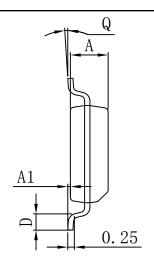

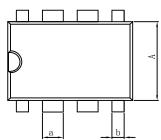

| Dimensions In Millimeters |       |       |          |           |       |

|---------------------------|-------|-------|----------|-----------|-------|

| Symbol:                   | Min:  | Max:  | Symbol : | Min:      | Max:  |

| Α                         | 6.100 | 6.680 | L1       | 3.000     | 3.600 |

| В                         | 9.000 | 9.500 | а        | 1.524 TYP |       |

| D                         | 8.400 | 9.000 | b        | 0.889 TYP |       |

| D1                        | 7.420 | 7.820 | С        | 0.457 TYP |       |

| Е                         | 3.100 | 3.550 | d        | 2.540 TYP |       |

| L                         | 0.500 | 0.700 |          |           |       |

# Important statement:

Huaguan Semiconductor Co,Ltd. reserves the right to change the products and services provided without notice. Customers should obtain the latest relevant information before ordering, and verify the timeliness and accuracy of this information.

Customers are responsible for complying with safety standards and taking safety measures when using our products for system design and machine manufacturing to avoid potential risks that may result in personal injury or property damage.

Our products are not licensed for applications in life support, military, aerospace, etc., so we do not bear the consequences of the application of these products in these fields.

Our documentation is only permitted to be copied without any tampering with the content, so we do not accept any responsibility or liability for the altered documents.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for RS-422/RS-485 Interface IC category:

Click to view products by HGSEMI manufacturer:

Other Similar products are found below:

SP3494CN-L/TR CA-IS3082WX CA-IS3088WX CA-IS3092W XR33038IDTR-F SIT3485ISO XR3077XID-F ADM2687EBRIZ-RL7

SP483EEN-L/TR SN75LBC175ADR SN65ALS1176DR MAX489CPD+ MAX3080CPD+ MXL1535EEWI+ SP483EN-L/TR SP483CNL/TR XR3072XID-F DS16F95J/883 SP1485EEN-L/TR MAX490ESA+T ISL3179EIUZ-T7A ISL3179EIRZ-T7A ISL3179EFRZ-T7A

XR33193ESBTR XR33194ESBTR XR3074XID-F XR3082XID-F SP3490EN-L ADM485JN ADM1485JNZ ADM2687EBRIZ

ADM3491ARZ-REEL7 ADM489ABRZ ADM3073EARZ ADM4850ACPZ-REEL7 ADM4853ACPZ-REEL7 ADM485ANZ

ADM3072EARZ-REEL7 ADM3075EARZ-REEL7 ADM3486EARZ-REEL7 ADM3493ARZ-REEL7 ADM4856ARZ-REEL7

ADM487EARZ-REEL7 ADM1485JRZ-REEL ADM3490ARZ-REEL7 ADM3490EARZ-REEL7 ADM1485ARZ-REEL ADM3071EARZ

ADM3483EARZ-REEL7 ADM3485EARZ-REEL7