# 12-BIT ANALOG-TO-DIGITAL CONVERTERS WITH SERIAL CONTROL AND 11 ANALOG INPUTS

- 12-Bit-Resolution A/D Converter

- 10-μs Conversion Time Over Operating Temperature

- 11 Analog Input Channels

- 3 Built-In Self-Test Modes

- Inherent Sample-and-Hold Function

- Linearity Error . . . ±1 LSB Max

- On-Chip System Clock

- End-of-Conversion Output

- Unipolar or Bipolar Output Operation (Signed Binary With Respect to 1/2 the Applied Voltage Reference)

- Programmable MSB or LSB First

- Programmable Power Down

- Programmable Output Data Length

- CMOS Technology

- Application Report Available<sup>†</sup>

#### SOP20/DIP20 PACKAGE (TOP VIEW) AIN0 [ 20 VCC AIN1 1 2 19**∏** EOC AIN2 [] 3 18 1/O CLOCK AIN3 ∏ 4 17 DATA INPUT AIN4 **∏** 5 16 DATA OUT AIN5 **1** 6 15 CS AIN6 [] 7 14 REF+ 13 REF-AIN7 [] 8 AIN8 [] 9 12 AIN10 GND [] 10 11 **∏** AIN9

#### ORDERING INFORMATION

| DEVICE       | Package Type | MARKING  | Packing | Packing Qty  |

|--------------|--------------|----------|---------|--------------|

| TLC2543CN    | DIP20        | TLC2543C | TUBE    | 18pcs/tube   |

| TLC2543IN    | DIP20        | TLC2543I | TUBE    | 18pcs/tube   |

| TLC2543CM/TR | SOP20        | TLC2543C | REEL    | 2000pcs/REEL |

| TLC2543IM/TR | SOP20        | TLC2543I | REEL    | 2000pcs/REEL |

### description

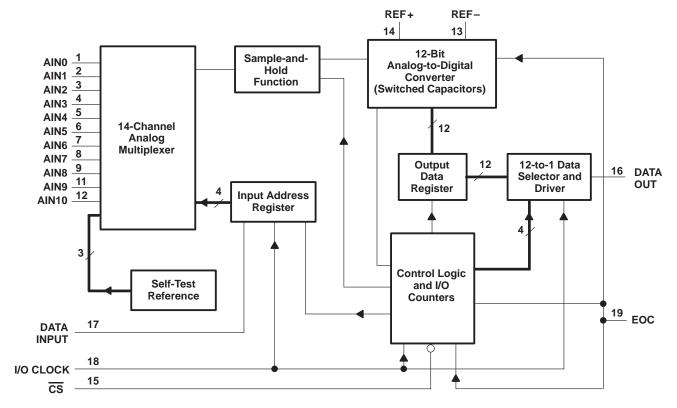

The TLC2543C and TLC2543I are 12-bit, switched-capacitor, successive-approximation, analog-to-digital converters. Each device has three control inputs [chip select ( $\overline{CS}$ ), the input-output clock (I/O CLOCK), and the address input (DATA INPUT)] and is designed for communication with the serial port of a host processor or peripheral through a serial 3-state output. The device allows high-speed data transfers from the host.

In addition to the high-speed converter and versatile control capability, the device has an on-chip 14-channel multiplexer that can select any one of 11 inputs or any one of three internal self-test voltages. The sample-and-hold function is automatic. At the end of conversion, the end-of-conversion (EOC) output goes high to indicate that conversion is complete. The converter incorporated in the device features differential high-impedance reference inputs that facilitate ratiometric conversion, scaling, and isolation of analog circuitry from logic and supply noise. A switched-capacitor design allows low-error conversion over the full operating temperature range.

The TLC2543C is characterized for operation from  $T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ . The TLC2543I is characterized for operation from  $T_A = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ .

## functional block diagram

## **Terminal Functions**

| TERMINAL     |                |     | DECODIFICAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO.            | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AIN0 – AIN10 | 1-9,<br>11, 12 | I   | Analog input. These 11 analog-signal inputs are internally multiplexed. The driving source impedance should be less than or equal to 50 $\Omega$ for 4.1-MHz I/O CLOCK operation and be capable of slewing the analog input voltage into a capacitance of 60 pF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <u>cs</u>    | 15             | I   | Chip select. A high-to-low transition on $\overline{\text{CS}}$ resets the internal counters and controls and enables DATA OUT, DATA INPUT, and I/O CLOCK. A low-to-high transition disables DATA INPUT and I/O CLOCK within a setup time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DATA INPUT   | 17             | I   | Serial-data input. A 4-bit serial address selects the desired analog input or test voltage to be converted next. The serial data is presented with the MSB first and is shifted in on the first four rising edges of I/O CLOCK. After the four address bits are read into the address register, I/O CLOCK clocks the remaining bits in order.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DATA OUT     | 16             | 0   | The 3-state serial output for the A/D conversion result. DATA OUT is in the high-impedance state when $\overline{CS}$ is high and active when $\overline{CS}$ is low. With a valid $\overline{CS}$ , DATA OUT is removed from the high-impedance state and is driven to the logic level corresponding to the MSB/LSB <sup>†</sup> value of the previous conversion result. The next falling edge of I/O CLOCK drives DATA OUT to the logic level corresponding to the next MSB/LSB, and the remaining bits are shifted out in order.                                                                                                                                                                                                                                                                          |

| EOC          | 19             | 0   | End of conversion. EOC goes from a high to a low logic level after the falling edge of the last I/O CLOCK and remains low until the conversion is complete and the data is ready for transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GND          | 10             |     | Ground. GND is the ground return terminal for the internal circuitry. Unless otherwise noted, all voltage measurements are with respect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I/O CLOCK    | 18             | ı   | <ol> <li>Input/output clock. I/O CLOCK receives the serial input and performs the following four functions:</li> <li>It clocks the eight input data bits into the input data register on the first eight rising edges of I/O CLOCK with the multiplexer address available after the fourth rising edge.</li> <li>On the fourth falling edge of I/O CLOCK, the analog input voltage on the selected multiplexer input begins charging the capacitor array and continues to do so until the last falling edge of the I/O CLOCK.</li> <li>It shifts the 11 remaining bits of the previous conversion data out on DATA OUT. Data changes on the falling edge of I/O CLOCK.</li> <li>It transfers control of the conversion to the internal state controller on the falling edge of the last I/O CLOCK.</li> </ol> |

| REF+         | 14             | I   | Positive reference voltage The upper reference voltage value (nominally V <sub>CC</sub> ) is applied to REF+. The maximum input voltage range is determined by the difference between the voltage applied to this terminal and the voltage applied to the REF – terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| REF-         | 13             | ı   | Negative reference voltage. The lower reference voltage value (nominally ground) is applied to REF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Vcc          | 20             |     | Positive supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

<sup>†</sup> MSB/LSB = Most significant bit /least significant bit

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)               | 0.5 V to 6.5 V                             |

|------------------------------------------------------------------|--------------------------------------------|

| Input voltage range, V <sub>I</sub> (any input)                  |                                            |

| Output voltage range, VO                                         | $-0.3 \text{ V to V}_{CC} + 0.3 \text{ V}$ |

| Positive reference voltage, V <sub>ref+</sub>                    | V <sub>CC</sub> + 0.1 V                    |

| Negative reference voltage, V <sub>ref</sub>                     | 0.1 V                                      |

| Peak input current, I <sub>I</sub> (any input)                   | ±20 mA                                     |

| Peak total input current, I <sub>I</sub> (all inputs)            | ±30 mA                                     |

| Operating free-air temperature range, T <sub>A</sub> : TLC2543C  |                                            |

| TLC2543I                                                         | –40°C to 85°C                              |

| Storage temperature range, T <sub>Stq</sub>                      | 65°C to 150°C                              |

| Lead temperature 1,6 mm (1/16 inch) from the case for 10 seconds | 260°C                                      |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to the GND terminal with REF - and GND wired together (unless otherwise noted).

### recommended operating conditions

|                                                                                             |                                |                                  | MIN   | NOM | MAX                  | UNIT |

|---------------------------------------------------------------------------------------------|--------------------------------|----------------------------------|-------|-----|----------------------|------|

| Supply voltage, V <sub>CC</sub>                                                             |                                |                                  |       | 5   | 5.5                  | V    |

| Positive reference voltage, V <sub>ref+</sub> (see No                                       | te 2)                          |                                  |       | Vcc |                      | V    |

| Negative reference voltage, V <sub>ref</sub> (see N                                         | ote 2)                         |                                  |       | 0   |                      | V    |

| Differential reference voltage, $V_{ref+} - V_{ref}$                                        | <sub>ef</sub> _ (see Note 2)   |                                  | 2.5   | Vcc | V <sub>CC</sub> +0.1 | V    |

| Analog input voltage (see Note 2)                                                           |                                |                                  | 0     |     | Vcc                  | V    |

| High-level control input voltage, VIH                                                       | ,                              | V <sub>CC</sub> = 4.5 V to 5.5 V | 2     |     |                      | V    |

| Low-level control input voltage, VIL                                                        | ,                              | V <sub>CC</sub> = 4.5 V to 5.5 V |       |     | 0.8                  | V    |

| Clock frequency at I/O CLOCK                                                                |                                |                                  | 0     |     | 4.1                  | MHz  |

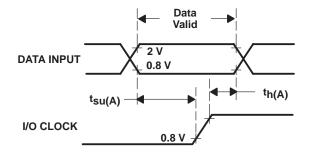

| Setup time, address bits at DATA INPUT before I/O CLOCK↑, t <sub>Su(A)</sub> (see Figure 4) |                                |                                  | 100   |     |                      | ns   |

| Hold time, address bits after I/O CLOCK↑, th(A) (see Figure 4)                              |                                |                                  | 0     |     |                      | ns   |

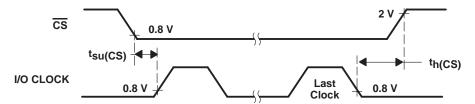

| Hold time, CS low after last I/O CLOCK↓,                                                    | t <sub>h(CS)</sub> (see Figure | e 5)                             | 0     |     |                      | ns   |

| Setup time, CS low before clocking in first                                                 | address bit, t <sub>su(C</sub> | (S) (see Note 3 and Figure 5)    | 1.425 |     |                      | μs   |

| Pulse duration, I/O CLOCK high, twH(I/O)                                                    | )                              |                                  | 120   |     |                      | ns   |

| Pulse duration, I/O CLOCK low, twL(I/O)                                                     |                                |                                  | 120   |     |                      | ns   |

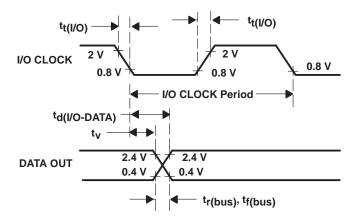

| Transition time, I/O CLOCK high to low, t <sub>t(I/O)</sub> (see Note 4 and Figure 6)       |                                |                                  |       |     | 1                    | μs   |

| Transition time, DATA INPUT and CS, t <sub>t</sub> (CS)                                     |                                |                                  |       |     | 10                   | μs   |

| Or and the first state of the second of T                                                   | TLC2543C                       |                                  | 0     |     | 70                   |      |

| Operating free-air temperature, T <sub>A</sub>                                              | TLC2543I                       |                                  | -40   |     | 85                   | °C   |

NOTES: 2. Analog input voltages greater than that applied to REF+ convert as all ones (111111111111), while input voltages less than that applied to REF- convert as all zeros (000000000000).

http://www.hgsemi.com.cn 4 2018 AUG

<sup>3.</sup> To minimize errors caused by noise at the CS input, the internal circuitry waits for a setup time after CS↓ before responding to control input signals. No attempt should be made to clock in an address until the minimum CS setup time has elapsed.

<sup>4.</sup> This is the time required for the clock input signal to fall from V<sub>IL</sub>max or to rise from V<sub>IL</sub>max to V<sub>IL</sub>ma

# electrical characteristics over recommended operating free-air temperature range, $V_{CC} = V_{ref+} = 4.5 \text{ V}$ to 5.5 V, $f_{(I/O\ CLOCK)} = 4.1 \text{ MHz}$ (unless otherwise noted)

| PARAMETER                                   |                                                   | TEST CONDITIONS                                                    |                                                                             | TLC2543C, TLC2543I        |                      |     | LINUT |     |

|---------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------|----------------------|-----|-------|-----|

| PARAIWE I ER                                |                                                   |                                                                    |                                                                             | MIN                       | TYP†                 | MAX | UNIT  |     |

| VOH High-level output v                     |                                                   | voltago                                                            | $V_{CC} = 4.5 \text{ V},$                                                   | I <sub>OH</sub> = -1.6 mA | 2.4                  |     |       | V   |

|                                             |                                                   | voltage                                                            | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V},$                                 | $I_{OH} = -20 \mu A$      | V <sub>CC</sub> -0.1 |     |       | V   |

| V <sub>OL</sub> Low-level output voltage    |                                                   | $V_{CC} = 4.5 \text{ V},$                                          | $I_{OL} = 1.6 \text{ mA}$                                                   |                           |                      | 0.4 | V     |     |

|                                             |                                                   | voltage                                                            | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V},$                                 | I <sub>OL</sub> = 20 μA   |                      |     | 0.1   | V   |

| IOZ High-impedance off-state output current |                                                   | $V_O = V_{CC}$                                                     | CS at V <sub>CC</sub>                                                       |                           | 1                    | 2.5 |       |     |

|                                             |                                                   |                                                                    | $V_{O} = 0$ ,                                                               | CS at V <sub>CC</sub>     |                      | 1   | -2.5  | μΑ  |

| ΙΗ                                          | High-level input current                          |                                                                    | $V_I = V_{CC}$                                                              |                           |                      | 1   | 2.5   | μΑ  |

| I <sub>I</sub> L                            | I <sub>IL</sub> Low-level input current           |                                                                    | V <sub>I</sub> = 0                                                          |                           |                      | 1   | -2.5  | μΑ  |

| Icc                                         | Operating supply current                          |                                                                    | CS at 0 V                                                                   |                           |                      | 1   | 2.5   | mA  |

| I <sub>CC(PD)</sub>                         | ) Power-down current                              |                                                                    | For all digital inputs,<br>$0 \le V_I \le 0.5 \text{ V or } V_I \ge V_{CC}$ | – 0.5 V                   |                      | 4   | 25    | μΑ  |

|                                             |                                                   |                                                                    | Selected channel at V <sub>CC</sub> ,                                       | Unselected channel at 0 V |                      |     | 1     |     |

| Selected channel leakage current            |                                                   | Selected channel at 0 V,<br>Unselected channel at V <sub>C</sub> ( |                                                                             |                           |                      | -1  | μΑ    |     |

|                                             | Maximum static analog reference current into REF+ |                                                                    | V <sub>ref+</sub> = V <sub>CC</sub> ,                                       | V <sub>ref</sub> _ = GND  |                      | 1   | 2.5   | μΑ  |

| C.                                          | Input                                             | Analog inputs                                                      |                                                                             |                           |                      | 30  | 60    | n.E |

| l Ci                                        | C <sub>i</sub> capacitance (                      |                                                                    |                                                                             |                           |                      | 5   | 15    | pF  |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

## operating characteristics over recommended operating free-air temperature range, $V_{CC} = V_{ref+} = 4.5 \text{ V}$ to 5.5 V, $f_{(I/O\ CLOCK)} = 4.1 \text{ MHz}$

|                     | PARAMETER                                                                                                      | TEST CONDITIONS             | MIN | TYP <sup>†</sup> | MAX                                                 | UNIT                    |

|---------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------|-----|------------------|-----------------------------------------------------|-------------------------|

| EL                  | Linearity error (see Note 5)                                                                                   | See Figure 2                |     |                  | ±1                                                  | LSB                     |

| E <sub>D</sub>      | Differential linearity error                                                                                   | See Figure 2                |     |                  | ±1                                                  | LSB                     |

| EO                  | Offset error (see Note 6)                                                                                      | See Note 2 and Figure 2     |     |                  | ±1.5                                                | LSB                     |

| E <sub>G</sub>      | Gain error (see Note 6)                                                                                        | See Note 2 and Figure 2     |     |                  | ±1                                                  | LSB                     |

| ET                  | Total unadjusted error (see Note 7)                                                                            |                             |     |                  | ±1.75                                               | LSB                     |

|                     |                                                                                                                | DATA INPUT = 1011           |     | 2048             |                                                     |                         |

|                     | Self-test output code (see Table 3 and Note 8)                                                                 | DATA INPUT = 1100           |     | 0                |                                                     | ]                       |

|                     |                                                                                                                | DATA INPUT = 1101           |     | 4095             |                                                     |                         |

| t <sub>conv</sub>   | Conversion time                                                                                                | See Figures 9-14            |     | 8                | 10                                                  | μs                      |

| t <sub>C</sub>      | Total cycle time (access, sample, and conversion)                                                              | See Figures 9–14 and Note 9 |     |                  | 10 + total<br>I/O CLOCK<br>periods +<br>td(I/O-EOC) | μs                      |

| <sup>t</sup> acq    | Channel acquisition time (sample)                                                                              | See Figures 9-14 and Note 9 | 4   |                  | 12                                                  | I/O<br>CLOCK<br>periods |

| t <sub>V</sub>      | Valid time, DATA OUT remains valid after I/O CLOCK↓                                                            | See Figure 6                | 10  |                  |                                                     | ns                      |

| td(I/O-DATA)        | Delay time, I/O CLOCK↓ to DATA OUT valid                                                                       | See Figure 6                |     |                  | 150                                                 | ns                      |

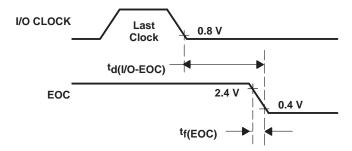

| td(I/O-EOC)         | Delay time, last I/O CLOCK $\downarrow$ to EOC $\downarrow$                                                    | See Figure 7                |     | 1.5              | 2.2                                                 | μs                      |

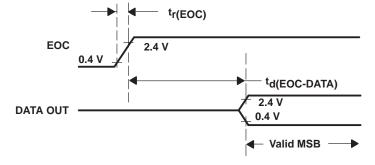

| td(EOC-DATA)        | Delay time, EOC↑ to DATA OUT (MSB/LSB)                                                                         | See Figure 8                |     |                  | 100                                                 | ns                      |

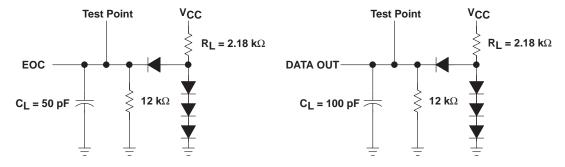

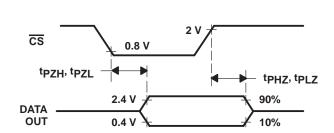

| tpzh, tpzl          | Enable time, CS↓ to DATA OUT (MSB/LSB driven)                                                                  | See Figure 3                |     | 0.7              | 1.3                                                 | μs                      |

| tPHZ, tPLZ          | Disable time, CS↑ to DATA OUT (high impedance)                                                                 | See Figure 3                |     | 70               | 150                                                 | ns                      |

| tr(EOC)             | Rise time, EOC                                                                                                 | See Figure 8                |     | 15               | 50                                                  | ns                      |

| <sup>t</sup> f(EOC) | Fall time, EOC                                                                                                 | See Figure 7                |     | 15               | 50                                                  | ns                      |

| tr(bus)             | Rise time, data bus                                                                                            | See Figure 6                |     | 15               | 50                                                  | ns                      |

| <sup>t</sup> f(bus) | Fall time, data bus                                                                                            | See Figure 6                |     | 15               | 50                                                  | ns                      |

| td(I/O-CS)          | Delay time, last I/O CLOCK $\downarrow$ to $\overline{\text{CS}} \downarrow$ to abort conversion (see Note 10) |                             |     |                  | 5                                                   | μs                      |

<sup>†</sup> All typical values are at  $T_A = 25$ °C.

NOTES: 2. Analog input voltages greater than that applied to REF+ convert as all ones (111111111111), while input voltages less than that applied to REF- convert as all zeros (000000000000).

- 5. Linearity error is the maximum deviation from the best straight line through the A/D transfer characteristics.

- 6. Gain error is the difference between the actual midstep value and the nominal midstep value in the transfer diagram at the specified gain point after the offset error has been adjusted to zero. Offset error is the difference between the actual midstep value and the nominal midstep value at the offset point.

- 7. Total unadjusted error comprises linearity, zero-scale, and full-scale errors.

- 8. Both the input address and the output codes are expressed in positive logic.

- 9. I/O CLOCK period = 1/(I/O CLOCK frequency) (see Figure 7).

- 10. Any transitions of  $\overline{CS}$  are recognized as valid only when the level is maintained for a setup time.  $\overline{CS}$  must be taken low at ≤ 5 μs of the tenth I/O CLOCK falling edge to ensure a conversion is aborted. Between 5 μs and 10 μs, the result is uncertain as to whether the conversion is aborted or the conversion results are valid.

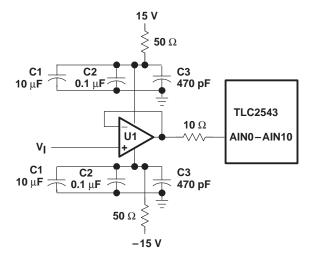

| LOCATION | DESCRIPTION                         | PART NUMBER                           |

|----------|-------------------------------------|---------------------------------------|

| U1       | OP27                                | _                                     |

| C1       | 10-μF 35-V tantalum capacitor       | _                                     |

| C2       | 0.1-μF ceramic NPO SMD capacitor    | AVX 12105C104KA105 or equivalent      |

| C3       | 470-pF porcelain Hi-Q SMD capacitor | Johanson 201S420471JG4L or equivalent |

Figure 1. Analog Input Buffer to Analog Inputs AIN0-AIN10

Figure 2. Load Circuits

Figure 3. DATA OUT to Hi-Z Voltage Waveforms

Figure 4. DATA INPUT and I/O CLOCK Voltage Waveforms

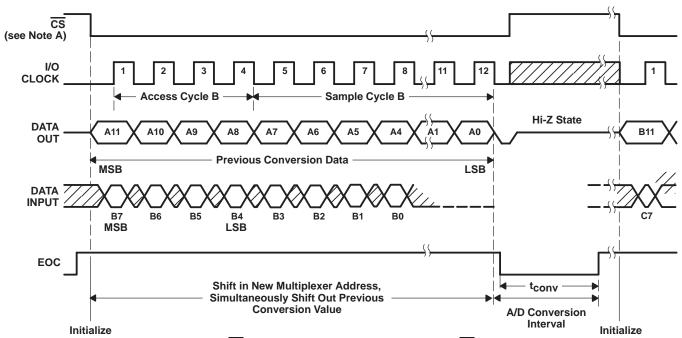

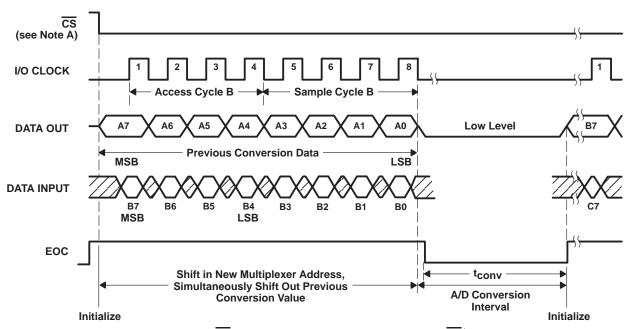

NOTE A: To ensure full conversion accuracy, it is recommended that no input signal change occurs while a conversion is ongoing.

Figure 5. CS and I/O CLOCK Voltage Waveforms

Figure 6. I/O CLOCK and DATA OUT Voltage Waveforms

Figure 7. I/O CLOCK and EOC Voltage Waveforms

Figure 8. EOC and DATA OUT Voltage Waveforms

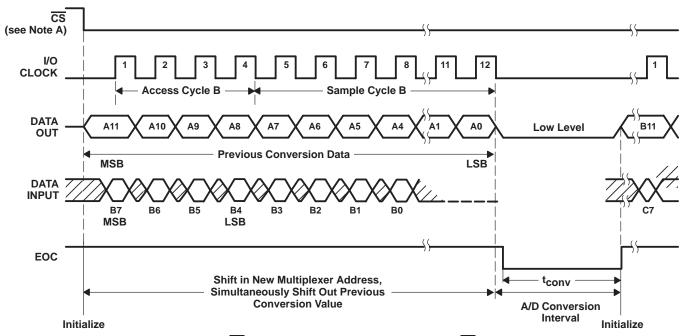

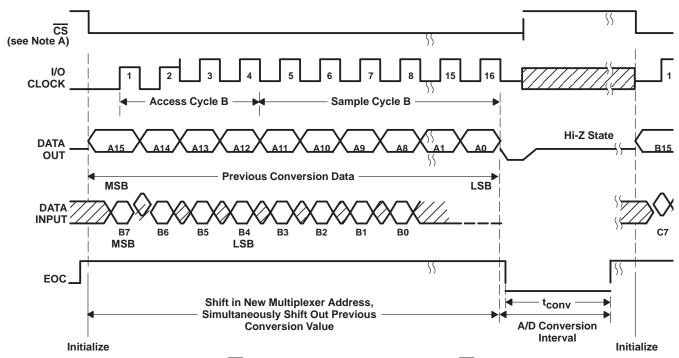

NOTE A: To minimize errors caused by noise at  $\overline{CS}$ , the internal circuitry waits for a setup time after  $\overline{CS}$ ↓ before responding to control input signals. Therefore, no attempt should be made to clock in an address until the minimum  $\overline{CS}$  setup time has elapsed.

Figure 9. Timing for 12-Clock Transfer Using CS With MSB First

NOTE A: To minimize errors caused by noise at  $\overline{CS}$ , the internal circuitry waits for a setup time after  $\overline{CS} \downarrow$  before responding to control input signals. Therefore, no attempt should be made to clock in an address until the minimum  $\overline{CS}$  setup time has elapsed.

Figure 10. Timing for 12-Clock Transfer Not Using CS With MSB First

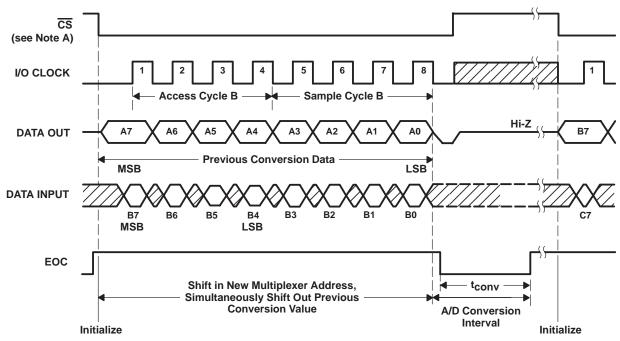

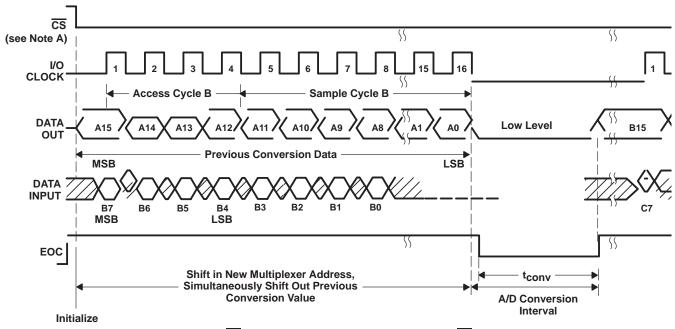

NOTE A: To minimize errors caused by noise at  $\overline{CS}$ , the internal circuitry waits for a setup time after  $\overline{CS}$ ↓ before responding to control input signals. Therefore, no attempt should be made to clock in an address until the minimum  $\overline{CS}$  setup time has elapsed.

Figure 11. Timing for 8-Clock Transfer Using CS With MSB First

NOTE A: To minimize errors caused by noise at  $\overline{CS}$ , the internal circuitry waits for a setup time after  $\overline{CS}$ ↓ before responding to control input signals. Therefore, no attempt should be made to clock in an address until the minimum  $\overline{CS}$  setup time has elapsed.

Figure 12. Timing for 8-Clock Transfer Not Using CS With MSB First

NOTE A: To minimize errors caused by noise at  $\overline{CS}$ , the internal circuitry waits for a setup time after  $\overline{CS}$ ↓ before responding to control input signals. Therefore, no attempt should be made to clock in an address until the minimum  $\overline{CS}$  setup time has elapsed.

Figure 13. Timing for 16-Clock Transfer Using CS With MSB First

NOTE A: To minimize errors caused by noise at  $\overline{CS}$ , the internal circuitry waits for a setup time after  $\overline{CS}$  before responding to control input signals. Therefore, no attempt should be made to clock in an address until the minimum  $\overline{CS}$  setup time has elapsed.

Figure 14. Timing for 16-Clock Transfer Not Using CS With MSB First

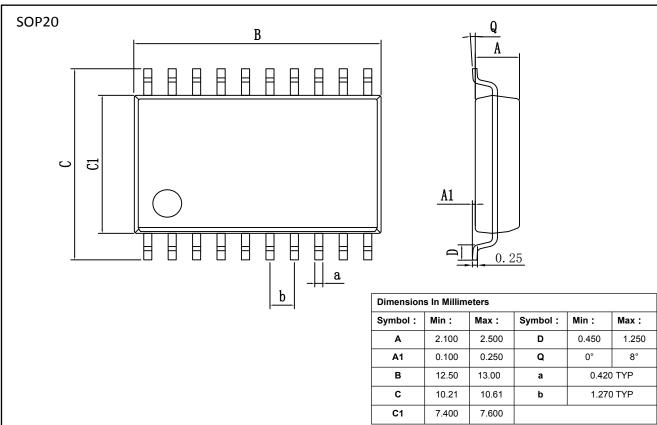

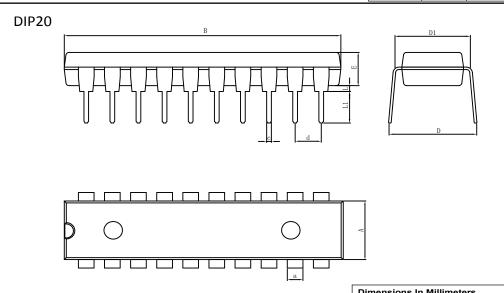

### **PACKAGE**

| Dimensions In Millimeters |        |        |          |           |       |  |  |

|---------------------------|--------|--------|----------|-----------|-------|--|--|

| Symbol:                   | Min:   | Max:   | Symbol : | Min:      | Max:  |  |  |

| Α                         | 6.200  | 6.600  | L        | 0.500     | 0.700 |  |  |

| В                         | 25.950 | 26.550 | L1       | 3.000     | 3.600 |  |  |

| D                         | 8.400  | 9.000  | а        | 1.524 TYP |       |  |  |

| D1                        | 7.320  | 7.920  | С        | 0.457 TYP |       |  |  |

| E                         | 3.200  | 3.600  | d        | 2.540 TYP |       |  |  |

## Important statement:

Huaguan Semiconductor Co,Ltd. reserves the right to change the products and services provided without notice. Customers should obtain the latest relevant information before ordering, and verify the timeliness and accuracy of this information.

Customers are responsible for complying with safety standards and taking safety measures when using our products for system design and machine manufacturing to avoid potential risks that may result in personal injury or property damage.

Our products are not licensed for applications in life support, military, aerospace, etc., so we do not bear the consequences of the application of these products in these fields.

Huaguan Semiconductor Co,Ltd. the performance of the semi conductor products produced by the company can reach the performance indicators that can be applied at the time of sales. the use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan semicondu ctor. Not all parameters of each device need to be tested. The above documents are for reference only, and all are subject to the physical parameters.

Our documentation is only permitted to be copied without any tampering with the content, so we do not accept any responsibility or liability for the altered documents.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Analog to Digital Converters - ADC category:

Click to view products by HGSEMI manufacturer:

Other Similar products are found below:

MCP37211-200I/TE AD9235BCPZRL7-40 HT7316ARQZ ADS1100A3IDBVR HI1175JCB HI3-574AJN-5 HI5714/4CB HI5746KCA

HI5766KCAZ HI5766KCBZ ISOSD61TR ES7201 AD7266BSUZ-REEL AD7708BRZ-REEL7 CLM2543IDW CLM2543CDW

MCP3004T-I/SL ADS7853IPWR GP9301BXI-F10K-D1V10-SH GP9301BXI-F10K-N-SH GP9101-F50-C1H1-SW GP9301BXI-F5K-N-SW

GP9101-F10K-N-SW GP9301BXI-F4K-D1V10-SH GP9301BXI-F1K-L5H2-SH LTC2484IDD#TRPBF AD9245BCPZRL7-20 SSP1120

ADS8332IBRGER ADS8168IRHBR HT7705ARWZ ADS9224RIRHBR ADC101S051CIMF AD7779ACPZ-RL AD7714YRUZ-REEL

LTC2447IUHF#PBF AD9235BRUZRL7-20 AD7888ARUZ-REEL AD7606BBSTZ-RL AD7998BRUZ-1REEL AD7276ARMZ-REEL

AD7712ARZ-REEL AD7997BRUZ-1REEL LTC2348ILX-16#PBF AD2S1210BSTZ-RL7 AD7711ARZ-REEL7 AD7865ASZ-1REEL

AD7923BRUZ-REEL AD7495ARZ-REEL7 AD9629BCPZRL7-40