## Push-Pull Output Sub-Microamp Comparators

#### Description

The Microchip Technology Inc. HT6541/2/3/4 family of comparators is offered in single (HT6541), single with chip select (HT6543), dual (HT6542) and quad (HT6544) configurations. The outputs are push-pull (CMOS/TTL-compatible) and are capable of driving heavy DC or capacitive loads. These comparators are optimized for low power, single-supply operation with greater than rail-to-rail input operation. The push-pull output of the HT6541/2/3/4 family supports rail-to-rail output swing and interfaces with TTL/CMOS logic. The internal input hysteresis eliminates output switching due to internal input noise voltage, reducing current draw. The output limits supply current surges and dynamic power consumption while switching. This product family operates with a single-supply voltage as low as 1.6V and draws less than 1 µA/ comparator of quiescent

current.The related HT6546/7/8/9 family of comparators from Microchip has an open-drain output. Used with a pull-up resistor, these devices can be used as level-shifters for any desired voltage up to 10V and in wired-OR logic.

### Features

- Low Quiescent Current: 600 nA/comparator (typ.)

- + Rail-to-Rail Input: V<sub>SS</sub> 0.3V to V<sub>DD</sub> + 0.3V

- CMOS/TTL-Compatible Output

- Propagation Delay 4 µs (typ.)

- Wide Supply Voltage Range: 1.6V to 5.5V

- · Available in Single, Dual and Quad

- Single available in SOT-23-5, SC-70-5 packages

- Chip Select (CS) with HT6543

- Low Switching Current

- Internal Hysteresis: 3.3 mV (typ.)

- Industrial Temperature: -40°C to +85°C

#### **Typical Applications**

- Laptop Computers

- · Mobile Phones

- Metering Systems

- · Hand-held Electronics

- · RC Timers

- · Alarm and Monitoring Circuits

- · Windowed Comparators

- · Multi-vibrators

#### **Related Devices**

• Open-Drain Output: HT6546/7/8/9

### 1.1 ELECTRICAL CHARACTERISTICS

#### 1.2 Absolute Maximum Ratings †

| V <sub>DD</sub> - V <sub>SS</sub>                       |

|---------------------------------------------------------|

| All inputs and outputs $V_{SS}$ –0.3V to $V_{DD}$ +0.3V |

| Difference Input voltage $ V_{DD} - V_{SS} $            |

| Output Short-Circuit Currentcontinuous                  |

| Current at Input Pins±2 mA                              |

| Current at Output and Supply Pins±30 mA                 |

| Storage temperature65°C to +150°C                       |

| Maximum Junction Temperature (T <sub>J</sub> )+150°C    |

| ESD protection on all pins (HBM;MM)4 kV; 400V           |

|                                                         |

**† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **PIN FUNCTION TABLE**

| NAME                                                            | FUNCTION              |

|-----------------------------------------------------------------|-----------------------|

| $V_{IN}$ +, $V_{INA}$ +, $V_{INB}$ +, $V_{INC}$ +, $V_{INC}$ +, | Non-Inverting Inputs  |

| $V_{IN}$ -, $V_{INA}$ -, $V_{INB}$ -, $V_{INC}$ -, $V_{IND}$ -  | Inverting Inputs      |

| V <sub>DD</sub>                                                 | Positive Power Supply |

| V <sub>SS</sub>                                                 | Negative Power Supply |

| OUT, OUTA, OUTB, OUTC,<br>OUTD                                  | Outputs               |

| CS                                                              | Chip Select           |

| NC                                                              | Not Connected         |

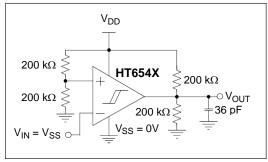

#### **DC CHARACTERISTICS**

**Electrical Specifications:** Unless otherwise indicated,  $V_{DD} = +1.6V$  to +5.5V,  $V_{SS} = GND$ ,  $T_A = +25^{\circ}C$ ,  $V_{IN} = V_{DD}/2$ ,  $V_{IN} = V_{SS}$ , and  $R_L = 100 \text{ k}\Omega$  to  $V_{DD}/2$  (Refer to Figure 1-3).

| Parameters                    | Sym                            | Min                  | Тур                  | Мах                  | Units | Conditions                                                                 |

|-------------------------------|--------------------------------|----------------------|----------------------|----------------------|-------|----------------------------------------------------------------------------|

| Power Supply                  |                                |                      |                      |                      |       |                                                                            |

| Supply Voltage                | V <sub>DD</sub>                | 1.6                  |                      | 5.5                  | V     |                                                                            |

| QuiescentCurrentpercomparator | Ι <sub>Q</sub>                 | 0.3                  | 0.6                  | 1.0                  | μA    | I <sub>OUT</sub> = 0                                                       |

| Input                         |                                |                      |                      |                      |       |                                                                            |

| Input Voltage Range           | V <sub>CMR</sub>               | V <sub>SS</sub> -0.3 | _                    | V <sub>DD</sub> +0.3 | V     |                                                                            |

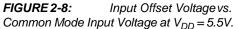

| Common Mode Rejection Ratio   | CMRR                           | 55                   | 70                   | —                    | dB    | $V_{DD} = 5V, V_{CM} = -0.3V \text{ to } 5.3V$                             |

| Common Mode Rejection Ratio   | CMRR                           | 50                   | 65                   | —                    | dB    | V <sub>DD</sub> = 5V, V <sub>CM</sub> = 2.5V to 5.3V                       |

| Common Mode Rejection Ratio   | CMRR                           | 55                   | 70                   | —                    | dB    | $V_{DD} = 5V, V_{CM} = -0.3V \text{ to } 2.5V$                             |

| Power Supply Rejection Ratio  | PSRR                           | 63                   | 80                   | —                    | dB    | $V_{CM} = V_{SS}$                                                          |

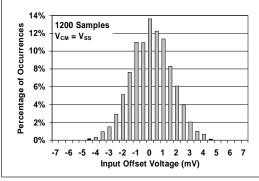

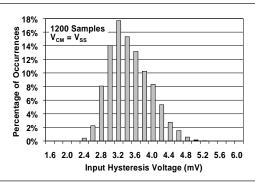

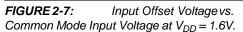

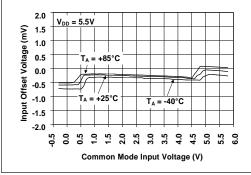

| Input Offset Voltage          | V <sub>OS</sub>                | -7.0                 | ±1.5                 | +7.0                 | mV    | V <sub>CM</sub> = V <sub>SS</sub> (Note 1)                                 |

| Drift with Temperature        | $\Delta V_{OS} / \Delta T_A$   | _                    | ±3                   | —                    | μV/°C | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C, V_{CM} = V_{SS}$           |

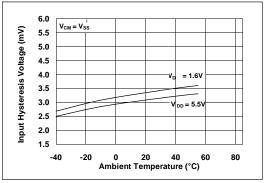

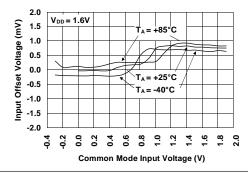

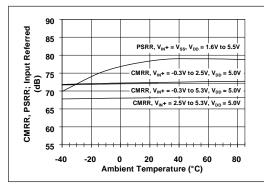

| Input Hysteresis Voltage      | V <sub>HYST</sub>              | 1.5                  | 3.3                  | 6.5                  | mV    | $V_{CM} = V_{SS}$ (Note 1)                                                 |

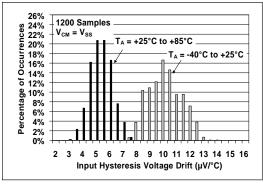

| Drift with Temperature        | $\Delta V_{HYST} / \Delta T_A$ | _                    | 10                   | —                    | μV/°C | $T_A = -40^{\circ}C$ to $+25^{\circ}C$ , $V_{CM} = V_{SS}$                 |

| Drift with Temperature        | $\Delta V_{HYST} / \Delta T_A$ | _                    | 5                    | —                    | µV/°C | $T_A = +25^{\circ}C$ to $+85^{\circ}C$ , $V_{CM} = V_{SS}$                 |

| Input BiasCurrent             | I <sub>B</sub>                 | _                    | 1                    | —                    | pА    | V <sub>CM</sub> =V <sub>SS</sub>                                           |

| Over-Temperature              | Ι <sub>Β</sub>                 | —                    |                      | 100                  | pА    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C, V_{CM} = V_{SS}$<br>(Note 3) |

| Input Offset Current          | I <sub>OS</sub>                | _                    | ±1                   | _                    | pА    | V <sub>CM</sub> =V <sub>SS</sub>                                           |

| Common Mode Input Impedance   | Z <sub>CM</sub>                | _                    | 10 <sup>13</sup>   4 | —                    | Ω  pF |                                                                            |

| Differential Input Impedance  | Z <sub>DIFF</sub>              | _                    | 10 <sup>13</sup>   2 | —                    | Ω  pF |                                                                            |

| Push-Pull Output              |                                |                      |                      |                      |       |                                                                            |

| High-Level Output Voltage     | V <sub>OH</sub>                | V <sub>DD</sub> -0.2 |                      | —                    | V     | I <sub>OUT</sub> = -2 mA, V <sub>DD</sub> = 5V                             |

| Low-Level Output Voltage      | V <sub>OL</sub>                | _                    |                      | V <sub>SS</sub> +0.2 | V     | $I_{OUT} = 2 \text{ mA}, V_{DD} = 5V$                                      |

| Short-Circuit Current         | I <sub>SC</sub>                | _                    | ±50                  | _                    | mA    | (Note 2)                                                                   |

**Note 1:** The input offset voltage is the center (average) of the input-referred trip points. The input hysteresis is the difference between the input-referred trip points.

2: Limit the output current to Absolute Maximum Rating of 30 mA.

3: Input bias current over temperature is not tested for SC-70-5 package.

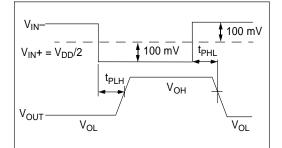

### **AC CHARACTERISTICS**

**Electrical Specifications:** Unless otherwise indicated,  $V_{DD}$  = +1.6V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$  + =  $V_{DD}/2$ , Step = 200 mV, Overdrive = 100 mV, and  $C_L$  = 36 pF (Refer to Figure 1-2 and Figure 1-3).

| Parameters                      | Sym              | Min | Тур  | Max | Units             | Conditions             |

|---------------------------------|------------------|-----|------|-----|-------------------|------------------------|

| Rise Time                       | t <sub>R</sub>   | _   | 0.85 | _   | μs                |                        |

| Fall Time                       | t <sub>F</sub>   | —   | 0.85 | —   | μs                |                        |

| Propagation Delay (High-to-Low) | t <sub>PHL</sub> | —   | 4    | 8   | μs                |                        |

| Propagation Delay (Low-to-High) | t <sub>PLH</sub> | —   | 4    | 8   | μs                |                        |

| Propagation Delay Skew          | t <sub>PDS</sub> | _   | ±0.2 | —   | μs                | (Note 1)               |

| Maximum Toggle Frequency        | f <sub>MAX</sub> | —   | 160  | —   | kHz               | V <sub>DD</sub> = 1.6V |

|                                 | f <sub>MAX</sub> | —   | 120  | —   | kHz               | V <sub>DD</sub> =5.5V  |

| Input Noise Voltage             | EN               | _   | 200  | _   | μV <sub>P-P</sub> | 10 Hz to 100 kHz       |

**Note 1:** Propagation Delay Skew is defined as:  $t_{PDS} = t_{PLH} - t_{PHL}$ .

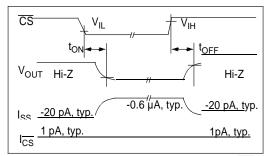

### SPECIFICATIONS FOR HT6543 CHIP-SELECT

Electrical Specifications: Unless otherwise indicated,  $V_{DD}$  = +1.6V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$  =  $V_{DD}/2$ ,  $V_{IN}$  =  $V_{SS}$ , and  $C_L$  = 36 pF (Refer to Figures 1-1 and 1-3).

|                                                            | ,                    |             |     | 1                  | -     |                                                                                   |

|------------------------------------------------------------|----------------------|-------------|-----|--------------------|-------|-----------------------------------------------------------------------------------|

| Parameters                                                 | Sym                  | Min         | Тур | Max                | Units | Conditions                                                                        |

| CS Low Specifications                                      |                      |             |     |                    |       |                                                                                   |

| CS Logic Threshold, Low                                    | V <sub>IL</sub>      | $V_{SS}$    | _   | $0.2V_{\text{DD}}$ | V     |                                                                                   |

| CS Input Current, Low                                      | I <sub>CSL</sub>     | —           | 5.0 | _                  | pА    | $\overline{\text{CS}} = V_{\text{SS}}$                                            |

| CS High Specifications                                     |                      |             |     |                    |       |                                                                                   |

| CS Logic Threshold, High                                   | $V_{\rm IH}$         | $0.8V_{DD}$ | _   | $V_{DD}$           | V     |                                                                                   |

| CS Input Current, High                                     | I <sub>CSH</sub>     | —           | 1   | —                  | pА    | $\overline{CS} = V_{DD}$                                                          |

| $\overline{\text{CS}}$ Input High, V <sub>DD</sub> Current | I <sub>DD</sub>      | —           | 18  | _                  | pА    | $\overline{CS} = V_{DD}$                                                          |

| CS Input High, GND Current                                 | I <sub>SS</sub>      | —           | -20 | _                  | pА    | CS=V <sub>DD</sub>                                                                |

| Comparator Output Leakage                                  | I <sub>O(LEAK)</sub> | —           | 1   | _                  | pА    | V <sub>OUT</sub> =V <sub>DD</sub>                                                 |

| CS Dynamic Specifications                                  | n.                   |             |     | I.                 |       |                                                                                   |

| CSLowtoComparatorOutputLow<br>Turn-onTime                  | t <sub>ON</sub>      | —           | 2   | 50                 | ms    | $\overline{CS} = 0.2 V_{DD} \text{ to } V_{OUT} = V_{DD}/2,$<br>$V_{IN} = V_{DD}$ |

| CS High to Comparator Output<br>High Z Turn-off Time       | t <sub>OFF</sub>     | —           | 10  | _                  | μs    | $\overline{CS} = 0.8 V_{DD} \text{ to } V_{OUT} = V_{DD}/2,$<br>$V_{IN} = V_{DD}$ |

| CS Hysteresis                                              | V <sub>CS_HYST</sub> | _           | 0.6 | _                  | V     | $V_{DD} = 5V$                                                                     |

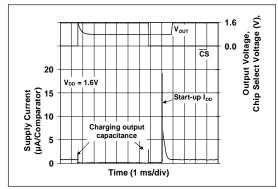

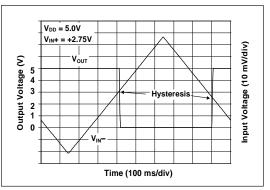

**FIGURE 1-1:** Timing Diagram for the  $\overline{CS}$  Pin on the HT6543.

FIGURE 1-2: Propagation Delay Timing Diagram.

### **TEMPERATURE SPECIFICATIONS**

| Electrical Specifications: Unless otherwise indicated, $V_{DD} = +1.6V$ to +5.5V and $V_{SS} = GND$ . |                |     |     |      |       |            |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|----------------|-----|-----|------|-------|------------|--|--|--|--|

| Parameters                                                                                            | Sym            | Min | Тур | Max  | Units | Conditions |  |  |  |  |

| Temperature Ranges                                                                                    |                |     |     |      |       |            |  |  |  |  |

| Specified Temperature Range                                                                           | T <sub>A</sub> | -40 | —   | +85  | °C    |            |  |  |  |  |

| Operating Temperature Range                                                                           | T <sub>A</sub> | -40 | _   | +125 | °C    | Note       |  |  |  |  |

| Storage Temperature Range                                                                             | TA             | -65 | _   | +150 | °C    |            |  |  |  |  |

| Thermal Package Resistances                                                                           |                |     |     |      |       |            |  |  |  |  |

| Thermal Resistance, 5L-SC-70                                                                          | $\theta_{JA}$  |     | 331 | _    | °C/W  |            |  |  |  |  |

| Thermal Resistance, 5L-SOT-23                                                                         | $\theta_{JA}$  |     | 256 | _    | °C/W  |            |  |  |  |  |

| Thermal Resistance, 8L-PDIP                                                                           | $\theta_{JA}$  |     | 85  |      | °C/W  |            |  |  |  |  |

| Thermal Resistance, 8L-SOIC                                                                           | $\theta_{JA}$  |     | 163 | _    | °C/W  |            |  |  |  |  |

| Thermal Resistance, 8L-MSOP                                                                           | $\theta_{JA}$  |     | 206 | _    | °C/W  |            |  |  |  |  |

| Thermal Resistance, 14L-PDIP                                                                          | $\theta_{JA}$  |     | 70  | _    | °C/W  |            |  |  |  |  |

| Thermal Resistance, 14L-SOIC                                                                          | $\theta_{JA}$  |     | 120 | _    | °C/W  |            |  |  |  |  |

| Thermal Resistance, 14L-TSSOP                                                                         | $\theta_{JA}$  |     | 100 | _    | °C/W  |            |  |  |  |  |

**Note:** The HT6541/2/3/4 operates over this extended temperature range, but with reduced performance. In any case, the Junction Temperature (T<sub>J</sub>) must not exceed the Absolute Maximum specification of +150°C.

### 1.3 Test Circuit Configuration

This test circuit configuration is used to determine the AC and DC specifications.

**FIGURE 1-3:** AC and DC Test Circuit for the Push-Pull Output Comparators.

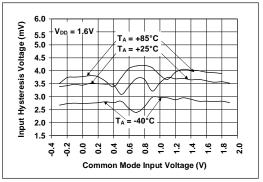

### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**Note:** Unless otherwise indicated,  $V_{DD}$  = +1.6V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$ + =  $V_{DD}/2$ ,  $V_{IN^-}$  = GND,  $R_L$  = 100 k $\Omega$  to  $V_{DD}/2$ , and  $C_L$  = 36 pF.

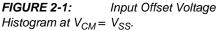

**FIGURE 2-2:** Input Offset Voltage Drift Histogram at  $V_{CM} = V_{SS}$ .

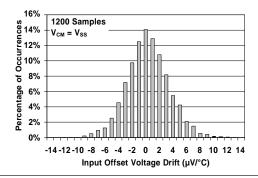

**FIGURE 2-3:** Input Offset Voltage vs. Ambient Temperature at  $V_{CM} = V_{SS}$ .

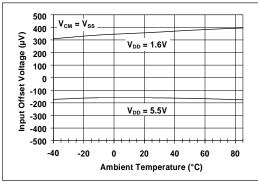

**FIGURE 2-4:** Input Hysteresis Voltage Histogram at  $V_{CM} = V_{SS}$ .

FIGURE 2-5: Input Hysteresis Voltage Drift Histogram.

**FIGURE 2-6:** Input Hysteresis Voltage vs. Ambient Temperature at  $V_{CM} = V_{SS}$ .

**Note:** Unless otherwise indicated,  $V_{DD}$  = +1.6V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$ + =  $V_{DD}/2$ ,  $V_{IN^-}$  =GND,  $R_L$  = 100 k $\Omega$  to  $V_{DD}/2$ , and  $C_L$  = 36 pF.

**FIGURE 2-9:** CMRR, PSRR vs. Ambient Temperature at  $V_{CM} = V_{SS}$ .

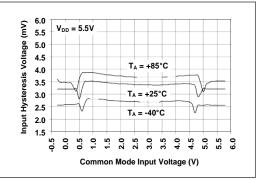

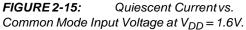

**FIGURE 2-10:** Input Hysteresis Voltage vs. Common Mode Input Voltage at  $V_{DD} = 1.6V$ .

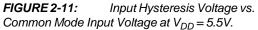

**FIGURE 2-12:** Input Bias Current, Input Offset Current vs. Common Mode Voltage at +85°C.

**Note:** Unless otherwise indicated,  $V_{DD}$  = +1.6V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$  + =  $V_{DD}/2$ ,  $V_{IN^-}$  = GND,  $R_L$  = 100 k $\Omega$  to  $V_{DD}/2$ , and  $C_L$  = 36 pF.

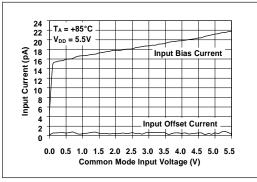

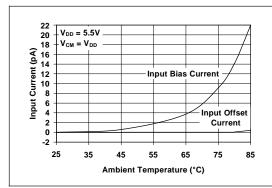

FIGURE 2-13: Input Bias Current, Input Offset Current vs. Ambient Temperature.

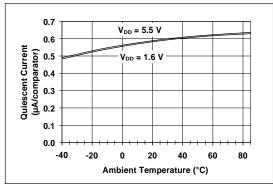

**FIGURE 2-14:** Quiescent Current vs. Ambient Temperature.

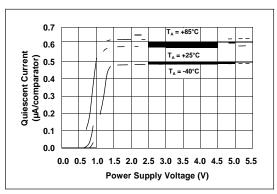

FIGURE 2-16: Quiescent Current vs. Power Supply Voltage.

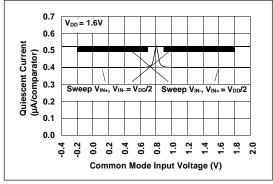

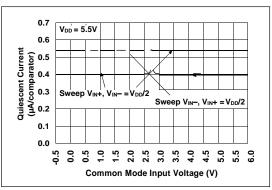

FIGURE 2-17:Quiescent Current vs.Common Mode Input Voltage at  $V_{DD} = 5V$ .

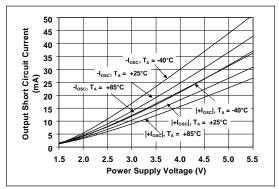

FIGURE 2-18: Output Short-Circuit Current vs. Power Supply Voltage.

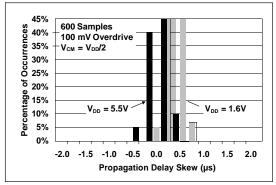

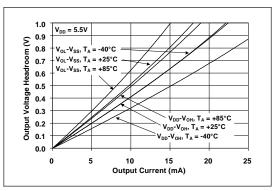

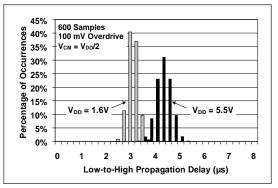

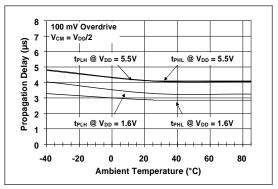

**Note:** Unless otherwise indicated,  $V_{DD}$  = +1.6V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$ + =  $V_{DD}/2$ ,  $V_{IN^-}$  = GND,  $R_L$  = 100 k $\Omega$  to  $V_{DD}/2$ , and  $C_L$  = 36 pF.

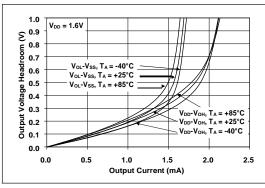

**FIGURE 2-19:** Output Voltage Headroom vs. Output Current at  $V_{DD} = 1.6V$ .

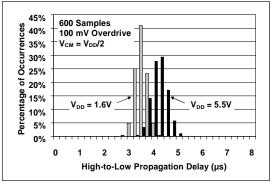

FIGURE 2-20: High-to-Low Propagation Delay Histogram.

FIGURE 2-21: Propagation Delay Skew Histogram.

**FIGURE 2-22:** Output Voltage Headroom vs. Output Current at  $V_{DD} = 5.5V$ .

FIGURE 2-23:Low-to-High PropagationDelay Histogram.

**FIGURE 2-24:** Propagation Delay vs. Ambient Temperature.

Note: Unless otherwise indicated,  $V_{DD}$  = +1.6V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$ + =  $V_{DD}/2$ ,  $V_{IN}$ - = GND,  $R_L$  = 100 k $\Omega$  to V\_DD/2, and  $C_L$  = 36 pF.

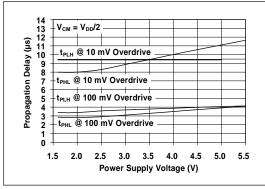

FIGURE 2-25: Propagation Delay vs. Power Supply Voltage.

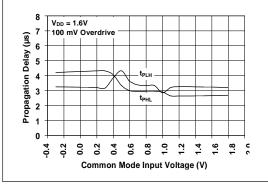

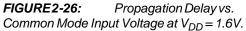

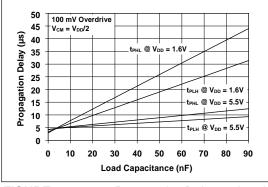

FIGURE2-27: Propagation Delay vs. Load Capacitance.

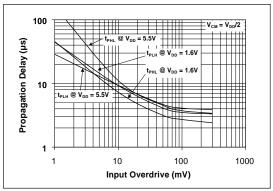

**FIGURE 2-28:** Propagation Delay vs. Input Overdrive.

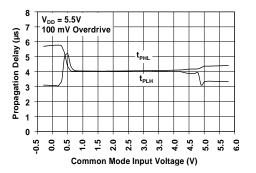

**FIGURE 2-29:** Propagation Delay vs. Common Mode Input Voltage at  $V_{DD} = 5.5V$ .

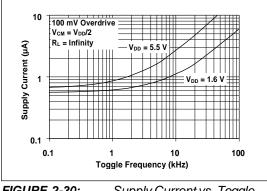

FIGURE 2-30: Frequency.

Supply Current vs. Toggle

**Note:** Unless otherwise indicated,  $V_{DD}$  = +1.6V to +5.5V,  $V_{SS}$  = GND,  $T_A$  = +25°C,  $V_{IN}$ + =  $V_{DD}/2$ ,  $V_{IN^-}$  = GND,  $R_L$  = 100 k $\Omega$  to  $V_{DD}/2$ , and  $C_L$  = 36 pF.

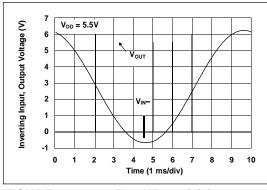

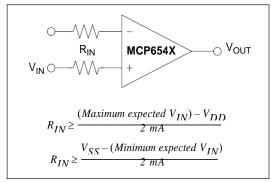

FIGURE 2-31: The HT6541/2/3/4 comparators show no phase reversal.

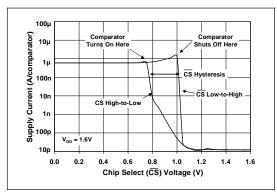

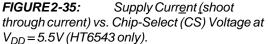

**FIGURE 2-32:** Supply Curr<u>ent</u>(shoot through current) vs. Chip-Select (CS) Voltage at  $V_{DD} = 1.6V$  (HT6543 only).

**FIGURE 2-33:** Sup<u>ply</u> Current (charging current) vs. Chip-Select (CS) pulse at  $V_{DD} = 1.6V$  (HT6543 only).

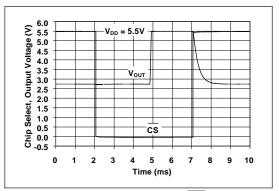

FIGURE2-34: Chip-Select (CS) Step Response (HT6543 only).

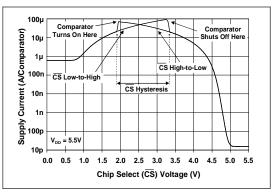

**FIGURE2-36:** Supply Current (charging current) vs. Chip-Select (CS) pulse at  $V_{DD} = 5.5V$  (HT6543 only).

### 3.1 APPLICATIONS INFORMATION

The HT6541/2/3/4 family of push-pull output comparators are fabricated on Microchip's state-of-the-art CMOS process. They are suitable for a wide range of applications requiring very low power consumption.

#### 3.2 Comparator Inputs

The HT6541/2/3/4 comparator family uses CMOS transistors at the input. They are designed to prevent phase inversion when the input pins exceed the supply voltages. Figure 2-31 shows an input voltage exceeding both supplies with no resulting phase inversion.

The input stage of this family of devices uses two differential input stages in parallel: one operates at low input voltages and the other at high input voltages. With this topology, the input voltage is 0.3V above  $V_{DD}$  and 0.3V below  $V_{SS}$ . Therefore, the input offset voltage is measured at both  $V_{SS}$ - 0.3V and  $V_{DD}$ + 0.3V to ensure proper operation.

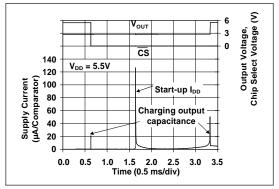

The maximum operating input voltages that can be applied are  $V_{SS}$ - 0.3V and  $V_{DD}$  + 0.3V. Voltages on the inputs that exceed this absolute maximum rating can cause excessive current to flow and permanently damage the device. In applications where the input pin exceeds the specified range, external resistors can be used to limit the current below ±2 mA, as shown in Figure 3-1.

**FIGURE 3-1:** An input resistor  $(R_{IN})$  should be used to limit excessive input current if either of the inputs exceeds the Absolute Maximum specification.

#### 3.3 Push-Pull Output

The push-pull output is designed to be compatible with CMOS and TTL logic, while the output transistors are configured to give rail-to-rail output performance. They are driven with circuitry that minimizes any switching current (shoot-through current from supply-to-supply) when the output is transitioned from high-to-low, or from low-to-high (see Figures 2-15, 2-17, 2-32 through 2-36 for more information).

### 3.4 HT6543 Chip Select (CS)

The HT6543 is a single comparator with chip select (CS). When  $\overline{CS}$  is pulled high, the total current consumption drops to 20 pA (typ); 1 pA (typ) flows through the CS pin, 1 pA (typ) flows through the output pin and 18 pA (typ) flows through the V<sub>DD</sub> pin, as shown in Figure 1-1. When this happens, the comparator output is put into a high-impedance state. By pulling CS low, the comparator is enabled. If the CS pin is left floating, the comparator will not operate properly. Figure 1-1 shows the output voltage and supply current response to a CS pulse.

The internal  $\overline{CS}$  circuitry is designed to minimize glitches when cycling the  $\overline{CS}$  pin. This helps conserve power, which is especially important in battery-powered applications.

#### 3.5 Externally-Set Hysteresis

Greater flexibility in selecting hysteresis (or input trip points) is achieved by using external resistors.

Input offset voltage (V<sub>OS</sub>) is the center (average) of the (input-referred) low-high and high-low trip points. Input hysteresis voltage (V<sub>HYST</sub>) is the difference between the same trip points. Hysteresis reduces output chattering when one input is slowly moving past the other and thus reduces dynamic supply current. It also helps in systems where it is best not to cycle between states too frequently (e.g., air conditioner thermostatic control). The HT6541/2/3/4 family has internally-set hysteresis that is small enough to eliminate output chattering caused by the comparator's own input noise voltage (200  $\mu$ Vp-p).

**FIGURE 3-2:** The HT6541/2/3/4 comparators' internal hysteresis eliminates output chatter caused by input noise voltage.

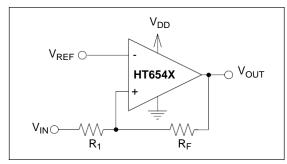

#### 3.5.1 NON-INVERTING CIRCUIT

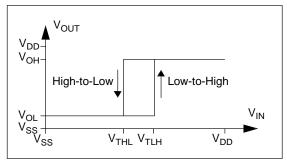

Figure 3-3 shows a non-inverting circuit for singlesupply applications using just two resistors. The resulting hysteresis diagram is shown in Figure 3-4.

**FIGURE 3-3:** Non-inverting circuit with hysteresis for single-supply.

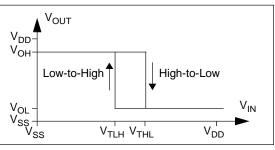

FIGURE 3-4: Hysteresis Diagram for the Non-Inverting Circuit.

The trip points for Figures 3-3 and 3-4 are:

#### EQUATION

$$V_{TLH} = V_{REF} \left( I + \frac{R_I}{R_F} \right) - V_{OL} \left( \frac{R_I}{R_F} \right)$$

$$V_{THL} = V_{REF} \left( I + \frac{R_I}{R_F} \right) - V_{OH} \left( \frac{R_I}{R_F} \right)$$

$$V_{TLH} = \text{trip voltage from low to high}$$

$$V_{THL} = \text{trip voltage from high to low}$$

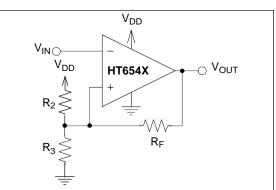

#### 3.5.2 INVERTING CIRCUIT

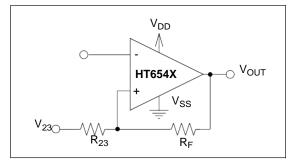

Figure 3-5 shows an inverting circuit for single-supply using three resistors. The resulting hysteresis diagram is shown in Figure 3-6.

FIGURE 3-6: Hysteresis Diagram for the Inverting Circuit.

In order to determine the trip voltages (V<sub>THL</sub> and V<sub>TLH</sub>) for the circuit shown in Figure 3-5, R<sub>2</sub> and R<sub>3</sub> can be simplified to the Thevenin equivalent circuit with respect to V<sub>DD</sub>, as shown in Figure 3-7.

FIGURE 3-7: Thevenin Equivalent Circuit.

Where:

$$R_{23} = \frac{R_2 R_3}{R_2 + R_3}$$

$$V_{23} = \frac{R_3}{R_2 + R_3} \times V_{DD}$$

Using this simplified circuit, the trip voltage can be calculated using the following equation:

#### EQUATION

$$V_{THL} = V_{OH} \left( \frac{R_{23}}{R_{23} + R_F} \right) + V_{23} \left( \frac{R_F}{R_{23} + R_F} \right)$$

$$V_{TLH} = V_{OL} \left( \frac{R_{23}}{R_{23} + R_F} \right) + V_{23} \left( \frac{R_F}{R_{23} + R_F} \right)$$

$V_{TLH}$  = trip voltage from low to high

$V_{THL}$  = trip voltage from high to low

Figure 2-19 and Figure 2-22 can be used to determine typical values for  $V_{OH}$  and  $V_{OL}.$

#### 3.5 Bypass Capacitors

With this family of comparators, the power supply pin (V<sub>DD</sub> for single supply) should have a local bypass capacitor (i.e., 0.01  $\mu$ F to 0.1  $\mu$ F) within 2 mm for good edge rate performance.

#### 3.6 Capacitive Loads

Reasonable capacitive loads (e.g., logic gates) have little impact on propagation delay (see Figure 2-27). The supply current increases with increasing toggle frequency (Figure 2-30), especially with higher capacitive loads.

#### 3.7 Battery Life

In order to maximize battery life in portable applications, use large resistors and small capacitive loads. Also, avoid toggling the <u>o</u>utput more than necessary and do not use chip select (CS) to conserve power for short periods of time. Capacitive loads will draw additional power at start-up.

#### 3.8 PCB Surface Leakage

In applications where low input bias current is critical, PCB (Printed Circuit Board) surface leakage effects need to be considered. Surface leakage is caused by humidity, dust or other contamination on the board. Under low humidity conditions, a typical resistance between nearby traces is  $10^{12}\Omega$ . A 5V difference would cause 5 pA, if current-to-flow. This is greater than the HT6541/2/3/4 family's bias current at 25°C (1 pA, typ).

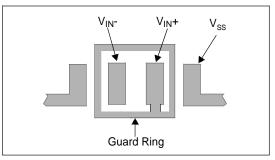

The easiest way to reduce surface leakage is to use a guard ring around sensitive pins (or traces). The guard ring is biased at the same voltage as the sensitive pin. An example of this type of layout is shown in Figure 3-8.

# FIGURE 3-8: Example Guard Ring Layout for Inverting Circuit.

- 1. Inverting Configuration (Figures 3-5 and 3-8):

- a. Connect the guard ring to the non-inverting input pin (V<sub>IN</sub>+). This biases the guard ring to the same reference voltage as the comparator (e.g.,  $V_{DD}/2$  or ground).

- b. Connect the inverting pin ( $V_{IN}$ -) to the input pad without touching the guard ring.

- 2. Non-inverting Configuration (Figure 3-3):

- a. Connect the non-inverting pin ( $V_{IN}$ +) to the input pad without touching the guard ring.

- b. Connect the guard ring to the inverting input pin (V\_{IN}-).

### 3.9 Typical Applications

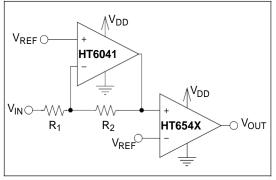

#### 3.9.1 PRECISE COMPARATOR

Some applications require higher DC precision. An easy way to solve this problem is to use an amplifier (such as the HT6041) to gain-up the input signal before it reaches the comparator. Figure 3-9 shows an example of this approach.

FIGURE 3-9: Precise Inverting Comparator.

#### 3.9.2 WINDOWED COMPARATOR

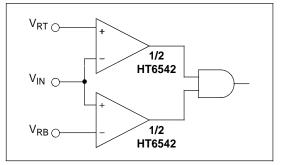

Figure 3-10 shows one approach to designing a windowed comparator. The AND gate produces a logic '1' when the input voltage is between V<sub>RB</sub> and V<sub>RT</sub> (where V<sub>RT</sub> > V<sub>RB</sub>).

FIGURE 3-10: WindowedComparator.

#### 3.9.3 BISTABLE MULTI-VIBRATOR

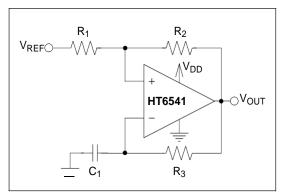

A simple bistable multi-vibrator design is shown in Figure 3-11. V<sub>REF</sub> needs to be between the power supplies (V<sub>SS</sub> = GND and V<sub>DD</sub>) to achieve oscillation. The output duty cycle changes with V<sub>REF</sub>.

FIGURE 3-11: Bistable Multi-vibrator.

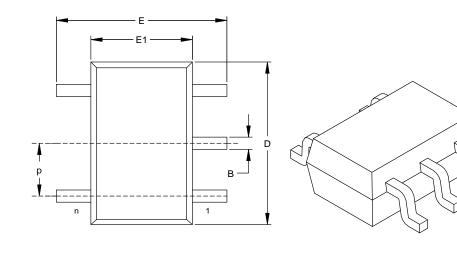

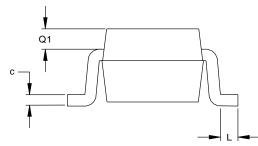

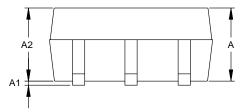

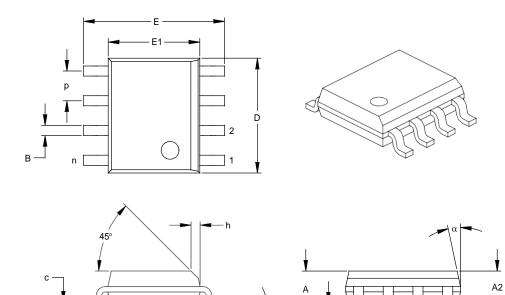

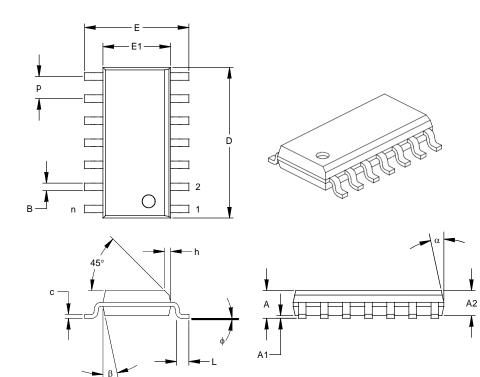

### 5-Lead Plastic Package (LT) (SC-70)

|                                    | Units  |      | INCHES     |      | MILLIMETERS* |            |      |

|------------------------------------|--------|------|------------|------|--------------|------------|------|

| Dimension                          | Limits | MIN  | NOM        | MAX  | MIN          | NOM        | MAX  |

| Number of Pins                     | n      |      | 5          |      |              | 5          |      |

| Pitch                              | р      |      | .026 (BSC) |      |              | 0.65 (BSC) |      |

| Overall Height                     | Α      | .031 |            | .043 | 0.80         |            | 1.10 |

| Molded Package Thickness           | A2     | .031 |            | .039 | 0.80         |            | 1.00 |

| Standoff                           | A1     | .000 |            | .004 | 0.00         |            | 0.10 |

| Overall Width                      | Е      | .071 |            | .094 | 1.80         |            | 2.40 |

| Molded Package Width               | E1     | .045 |            | .053 | 1.15         |            | 1.35 |

| Overall Length                     | D      | .071 |            | .087 | 1.80         |            | 2.20 |

| Foot Length                        | L      | .004 |            | .012 | 0.10         |            | 0.30 |

| Top of Molded Pkg to Lead Shoulder | Q1     | .004 |            | .016 | 0.10         |            | 0.40 |

| Lead Thickness                     | С      | .004 |            | .007 | 0.10         |            | 0.18 |

| Lead Width                         | В      | .006 |            | .012 | 0.15         |            | 0.30 |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .005" (0.127mm) per side.

JEITA (EIAJ) Standard: SC-70 Drawing No. C04-061

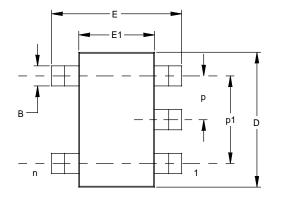

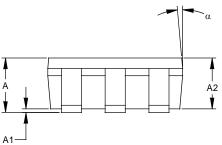

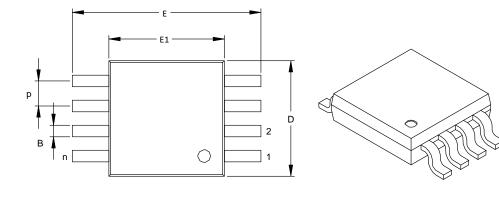

### 5-Lead Plastic Small Outline Transistor (OT) (SOT23)

|                            | Units            |      | INCHES* | N    | MILLIMETERS |      |      |

|----------------------------|------------------|------|---------|------|-------------|------|------|

| Dimensi                    | Dimension Limits |      |         | MAX  | MIN         | NOM  | MAX  |

| Number of Pins             | n                |      | 5       |      |             | 5    |      |

| Pitch                      | р                |      | .038    |      |             | 0.95 |      |

| Outside lead pitch (basic) | p1               |      | .075    |      |             | 1.90 |      |

| Overall Height             | А                | .035 | .046    | .057 | 0.90        | 1.18 | 1.45 |

| Molded Package Thickness   | A2               | .035 | .043    | .051 | 0.90        | 1.10 | 1.30 |

| Standoff §                 | A1               | .000 | .003    | .006 | 0.00        | 0.08 | 0.15 |

| Overall Width              | E                | .102 | .110    | .118 | 2.60        | 2.80 | 3.00 |

| Molded Package Width       | E1               | .059 | .064    | .069 | 1.50        | 1.63 | 1.75 |

| Overall Length             | D                | .110 | .116    | .122 | 2.80        | 2.95 | 3.10 |

| Foot Length                | L                | .014 | .018    | .022 | 0.35        | 0.45 | 0.55 |

| Foot Angle                 | ø                | 0    | 5       | 10   | 0           | 5    | 10   |

| Lead Thickness             | С                | .004 | .006    | .008 | 0.09        | 0.15 | 0.20 |

| Lead Width                 | В                | .014 | .017    | .020 | 0.35        | 0.43 | 0.50 |

| Mold Draft Angle Top       | α                | 0    | 5       | 10   | 0           | 5    | 10   |

| Mold Draft Angle Bottom    | β                | 0    | 5       | 10   | 0           | 5    | 10   |

А

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-178 Drawing No. C04-091

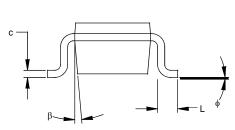

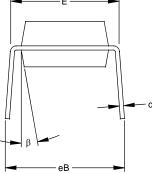

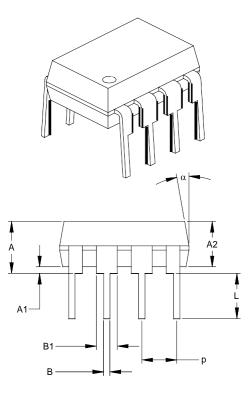

### 8-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

|                            | Units            |      | INCHES* |      | MILLIMETERS |      |       |  |

|----------------------------|------------------|------|---------|------|-------------|------|-------|--|

| Dimensio                   | Dimension Limits |      |         | MAX  | MIN         | NOM  | MAX   |  |

| Number of Pins             | n                |      | 8       |      |             | 8    |       |  |

| Pitch                      | р                |      | .100    |      |             | 2.54 |       |  |

| Top to Seating Plane       | А                | .140 | .155    | .170 | 3.56        | 3.94 | 4.32  |  |

| Molded Package Thickness   | A2               | .115 | .130    | .145 | 2.92        | 3.30 | 3.68  |  |

| Base to Seating Plane      | A1               | .015 |         |      | 0.38        |      |       |  |

| Shoulder to Shoulder Width | E                | .300 | .313    | .325 | 7.62        | 7.94 | 8.26  |  |

| Molded Package Width       | E1               | .240 | .250    | .260 | 6.10        | 6.35 | 6.60  |  |

| Overall Length             | D                | .360 | .373    | .385 | 9.14        | 9.46 | 9.78  |  |

| Tip to Seating Plane       | L                | .125 | .130    | .135 | 3.18        | 3.30 | 3.43  |  |

| Lead Thickness             | С                | .008 | .012    | .015 | 0.20        | 0.29 | 0.38  |  |

| Upper Lead Width           | B1               | .045 | .058    | .070 | 1.14        | 1.46 | 1.78  |  |

| Lower Lead Width           | В                | .014 | .018    | .022 | 0.36        | 0.46 | 0.56  |  |

| Overall Row Spacing §      | eB               | .310 | .370    | .430 | 7.87        | 9.40 | 10.92 |  |

| Mold Draft Angle Top       | α                | 5    | 10      | 15   | 5           | 10   | 15    |  |

| Mold Draft Angle Bottom    | β                | 5    | 10      | 15   | 5           | 10   | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-018

I

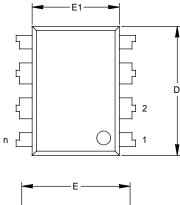

### 8-Lead Plastic Small Outline (SN) - Narrow, 150 mil (SOIC)

| β                        |            |      | ф/<br>_ |      |      |            | ł   |

|--------------------------|------------|------|---------|------|------|------------|-----|

|                          | Units      |      | INCHES* |      | М    | ILLIMETERS |     |

| Dimensi                  | ion Limits | MIN  | NOM     | MAX  | MIN  | NOM        | MAX |

| Number of Pins           | n          |      | 8       |      |      | 8          |     |

| Pitch                    | р          |      | .050    |      |      | 1.27       |     |

| Overall Height           | А          | .053 | .061    | .069 | 1.35 | 1.55       | 1.1 |

| Molded Package Thickness | A2         | .052 | .056    | .061 | 1.32 | 1.42       | 1.5 |

| Standoff §               | A1         | .004 | .007    | .010 | 0.10 | 0.18       | 0.2 |

| Overall Width            | E          | .228 | .237    | .244 | 5.79 | 6.02       | 6.2 |

| Molded Package Width     | E1         | .146 | .154    | .157 | 3.71 | 3.91       | 3.9 |

| Overall Length           | D          | .189 | .193    | .197 | 4.80 | 4.90       | 5.  |

| Chamfer Distance         | h          | .010 | .015    | .020 | 0.25 | 0.38       | 0.  |

| Foot Length              | L          | .019 | .025    | .030 | 0.48 | 0.62       | 0.7 |

| Foot Angle               | ¢          | 0    | 4       | 8    | 0    | 4          | _   |

| Lead Thickness           | С          | .008 | .009    | .010 | 0.20 | 0.23       | 0.2 |

| Lead Width               | В          | .013 | .017    | .020 | 0.33 | 0.42       | 0.  |

| Mold Draft Angle Top     | α          | 0    | 12      | 15   | 0    | 12         |     |

| Mold Draft Angle Bottom  | β          | 0    | 12      | 15   | 0    | 12         |     |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-012 Drawing No. C04-057

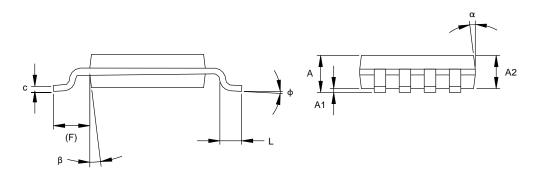

## 8-Lead Plastic Micro Small Outline Package (MS) (MSOP)

|                          | Units |      | INCHES    |      | MILLIMETERS* |          |      |  |

|--------------------------|-------|------|-----------|------|--------------|----------|------|--|

| Dimension L              | imits | MIN  | NOM       | MAX  | MIN          | NOM      | MAX  |  |

| Number of Pins           | n     |      | 8         |      |              | 8        |      |  |

| Pitch                    | р     |      | .026 BSC  |      |              | 0.65 BSC |      |  |

| Overall Height           | А     | -    | -         | .043 | -            | -        | 1.10 |  |

| Molded Package Thickness | A2    | .030 | .033      | .037 | 0.75         | 0.85     | 0.95 |  |

| Standoff                 | A1    | .000 | -         | .006 | 0.00         | -        | 0.15 |  |

| Overall Width            | E     |      | .193 TYP. |      |              | 4.90 BSC |      |  |

| Molded Package Width     | E1    |      | .118 BSC  |      | 3.00 BSC     |          |      |  |

| Overall Length           | D     |      | .118 BSC  |      | 3.00 BSC     |          |      |  |

| Foot Length              | L     | .016 | .024      | .031 | 0.40         | 0.60     | 0.80 |  |

| Footprint (Reference)    | F     |      | .037 REF  |      |              | 0.95 REF |      |  |

| Foot Angle               | ф     | 0°   | -         | 8°   | 0°           | -        | 8°   |  |

| Lead Thickness           | С     | .003 | .006      | .009 | 0.08         | -        | 0.23 |  |

| Lead Width               | В     | .009 | .012      | .016 | 0.22         | -        | 0.40 |  |

| Mold Draft Angle Top     | α     | 5°   | -         | 15°  | 5°           | -        | 15°  |  |

| Mold Draft Angle Bottom  | β     | 5°   | -         | 15°  | 5°           | -        | 15°  |  |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MO-187

Drawing No. C04-111

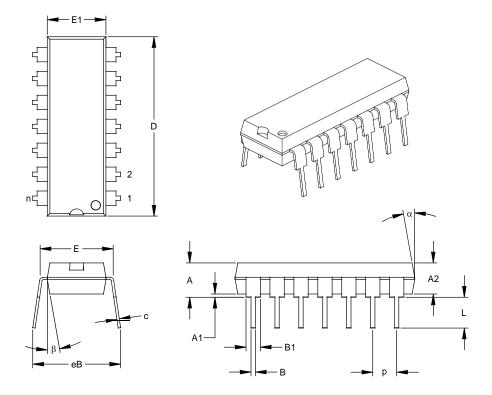

### 14-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

|                            |                  | Units |      | INCHES* |      | N     | MILLIMETERS |       |  |

|----------------------------|------------------|-------|------|---------|------|-------|-------------|-------|--|

| Dimen                      | Dimension Limits |       |      | NOM     | MAX  | MIN   | NOM         | MAX   |  |

| Number of Pins             |                  | n     |      | 14      |      |       | 14          |       |  |

| Pitch                      |                  | р     |      | .100    |      |       | 2.54        |       |  |

| Top to Seating Plane       |                  | Α     | .140 | .155    | .170 | 3.56  | 3.94        | 4.32  |  |

| Molded Package Thickness   |                  | A2    | .115 | .130    | .145 | 2.92  | 3.30        | 3.68  |  |

| Base to Seating Plane      |                  | A1    | .015 |         |      | 0.38  |             |       |  |

| Shoulder to Shoulder Width |                  | Е     | .300 | .313    | .325 | 7.62  | 7.94        | 8.26  |  |

| Molded Package Width       |                  | E1    | .240 | .250    | .260 | 6.10  | 6.35        | 6.60  |  |

| Overall Length             |                  | D     | .740 | .750    | .760 | 18.80 | 19.05       | 19.30 |  |

| Tip to Seating Plane       |                  | L     | .125 | .130    | .135 | 3.18  | 3.30        | 3.43  |  |

| Lead Thickness             |                  | С     | .008 | .012    | .015 | 0.20  | 0.29        | 0.38  |  |

| Upper Lead Width           |                  | B1    | .045 | .058    | .070 | 1.14  | 1.46        | 1.78  |  |

| Lower Lead Width           |                  | В     | .014 | .018    | .022 | 0.36  | 0.46        | 0.56  |  |

| Overall Row Spacing        | §                | eВ    | .310 | .370    | .430 | 7.87  | 9.40        | 10.92 |  |

| Mold Draft Angle Top       |                  | α     | 5    | 10      | 15   | 5     | 10          | 15    |  |

| Mold Draft Angle Bottom    |                  | β     | 5    | 10      | 15   | 5     | 10          | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-005

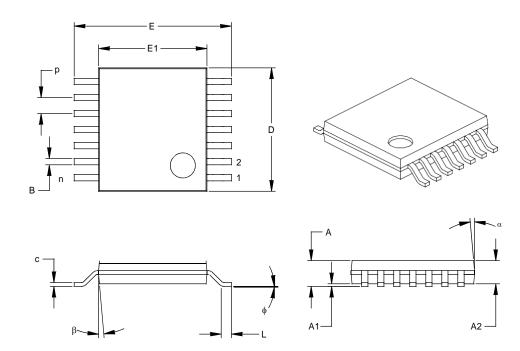

### 14-Lead Plastic Small Outline (SL) – Narrow, 150 mil (SOIC)

|                          | Units      | INCHES* |      |      | MILLIMETERS |      |      |

|--------------------------|------------|---------|------|------|-------------|------|------|

| Dimensi                  | ion Limits | MIN     | NOM  | MAX  | MIN         | NOM  | MAX  |

| Number of Pins           | n          |         | 14   |      |             | 14   |      |

| Pitch                    | р          |         | .050 |      |             | 1.27 |      |

| Overall Height           | Α          | .053    | .061 | .069 | 1.35        | 1.55 | 1.75 |

| Molded Package Thickness | A2         | .052    | .056 | .061 | 1.32        | 1.42 | 1.55 |

| Standoff §               | A1         | .004    | .007 | .010 | 0.10        | 0.18 | 0.25 |

| Overall Width            | E          | .228    | .236 | .244 | 5.79        | 5.99 | 6.20 |

| Molded Package Width     | E1         | .150    | .154 | .157 | 3.81        | 3.90 | 3.99 |

| Overall Length           | D          | .337    | .342 | .347 | 8.56        | 8.69 | 8.81 |

| Chamfer Distance         | h          | .010    | .015 | .020 | 0.25        | 0.38 | 0.51 |

| Foot Length              | L          | .016    | .033 | .050 | 0.41        | 0.84 | 1.27 |

| Foot Angle               | ¢          | 0       | 4    | 8    | 0           | 4    | 8    |

| Lead Thickness           | С          | .008    | .009 | .010 | 0.20        | 0.23 | 0.25 |

| Lead Width               | В          | .014    | .017 | .020 | 0.36        | 0.42 | 0.51 |

| Mold Draft Angle Top     | α          | 0       | 12   | 15   | 0           | 12   | 15   |

| Mold Draft Angle Bottom  | β          | 0       | 12   | 15   | 0           | 12   | 15   |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-012 Drawing No. C04-065

### 14-Lead Plastic Thin Shrink Small Outline (ST) – 4.4 mm (TSSOP)

|                          | Units  | INCHES |      |      | MILLIMETERS* |      |      |

|--------------------------|--------|--------|------|------|--------------|------|------|

| Dimensior                | Limits | MIN    | NOM  | MAX  | MIN          | NOM  | MAX  |

| Number of Pins           | n      |        | 14   |      |              | 14   |      |

| Pitch                    | р      |        | .026 |      |              | 0.65 |      |

| Overall Height           | Α      |        |      | .043 |              |      | 1.10 |

| Molded Package Thickness | A2     | .033   | .035 | .037 | 0.85         | 0.90 | 0.95 |

| Standoff §               | A1     | .002   | .004 | .006 | 0.05         | 0.10 | 0.15 |

| Overall Width            | E      | .246   | .251 | .256 | 6.25         | 6.38 | 6.50 |

| Molded Package Width     | E1     | .169   | .173 | .177 | 4.30         | 4.40 | 4.50 |

| Molded Package Length    | D      | .193   | .197 | .201 | 4.90         | 5.00 | 5.10 |

| Foot Length              | L      | .020   | .024 | .028 | 0.50         | 0.60 | 0.70 |

| Foot Angle               | ¢      | 0      | 4    | 8    | 0            | 4    | 8    |

| Lead Thickness           | С      | .004   | .006 | .008 | 0.09         | 0.15 | 0.20 |

| Lead Width               | B1     | .007   | .010 | .012 | 0.19         | 0.25 | 0.30 |

| Mold Draft Angle Top     | α      | 0      | 5    | 10   | 0            | 5    | 10   |

| Mold Draft Angle Bottom  | β      | 0      | 5    | 10   | 0            | 5    | 10   |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .005" (0.127mm) per side. JEDEC Equivalent: MO-153 Drawing No. C04-087

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Analog Comparators category:

Click to view products by HTCSEMI manufacturer:

Other Similar products are found below :

SC2903VDR2G LM2901SNG LM339SNG UPC271G2-A UPC272G2-A NTE911 LM339EDR2G NTE922 LM2903F-E2 GS331-TR LM397M5/TR LM2903MM/TR LM393MM/TR LM339DR LM2901DR LM139DR LM239DR AIP2903SA.TR LM393XK LM393 LM2901MT/TR TL331IDBVR-TP AIP393SA8.TR LM339MT/TR GSV331R-CR AIP339SA14.TR RS8912XH GS8742-SR GS8011-TR GS8746U-TR NJU7116F-TE1 HT7239ARTZ HT3201ARTZ LM331S5 GS8741-TR HT6541ARTZ GSV332-MR GS8706-TR GSV331-TR GS8740-TR LM239MT/TR LM293MM/TR HT6541BRTZ HT393VRZ HT393VRMZ HT8052ARZ MCP6544-EP MCP6541UT-I/LT MCP6542T-E/MS MCP6549-E/P