## CMOS Real-time clock/calendar

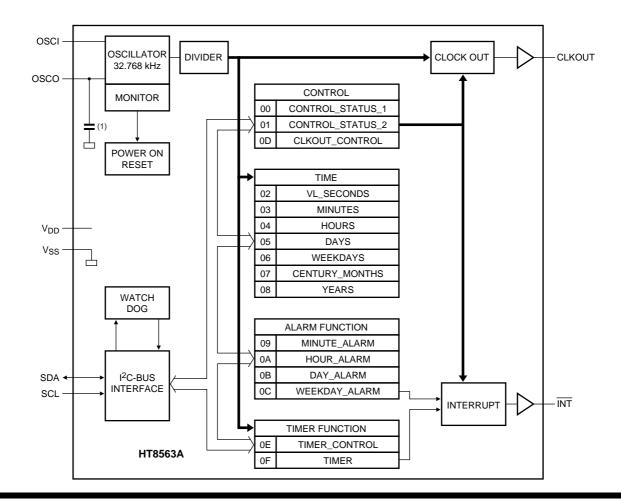

Microcircuit HT8563A is essentially the complete binary-decimal digital watch with calendar, alarm, timer and possesses low power consumption. Addresses and data are transferred in series via the double wire bi-directional bus. The microcircuit is intended for count of real time in hours, minutes and seconds, count of week days, date, month and year. The last day of the month is automatically adjusted for the months with fewer, than 31 days, including correction for the leap year. The watch functions in the 24 hour mode. The microcircuit HT8563A has the built-in power control circuit, which determines the power level < 1V and forms the bit, signaling, that information about the real time may not be correct.

## **Functions and Features**

- count of seconds, minutes, hours, week days, date, months and years with consideration of leap years (until 2100);

- 400 kHz, double wire serial interface;

- programmed orthogonal output signal;

- function programming of alarm, timer and interruption;

- automatic determination of the supply voltage drop;

- consumption current of less, than 450 nA with supply of 2V with the operating oscillator;

- operating temperature range: -40°C +85°C.

## tructural Diagram HT8563A

#### **Operating temperature range HT8563A**

Operating temperature range of the microcircuit HT8563A:  $T_A = -40 \dots + 85$  °C. Limit operating mode HT8563A

Limit and limit permissible operating modes of the microcircuit HT8563A are listed in the table

| Deremeter Description                          | Identifi-        |           | rm        |          |          |

|------------------------------------------------|------------------|-----------|-----------|----------|----------|

| Parameter Description,<br>Measurement Unit     | cation           | Limit Per | rmissible | Limit    |          |

| Measurement Onit                               | Cation           | Not less  | Not over  | Not less | Not over |

| Supply voltage, V                              | V <sub>DD</sub>  | 1.0       | 5.5       | -0.5     | 6.5      |

| Dissipated power, mWt                          | P <sub>tot</sub> | -         | -         | -        | 300      |

| Input voltage SCL, SDA, OSCI, V                | VI               | 0         | 5.5       | -0.5     | 6.5      |

| Output voltage CLKOUT, INT, V                  | Vo               | 0         | 5.5       | -0.5     | 6.5      |

| Direct input or output current via any pin, mA | I <sub>IO</sub>  | -         | -         | -10      | 10       |

All voltages are listed relative to ground. Under influence of the limit mode serviceability of the microcircuits is not guaranteed. After plotting the limit mode serviceability is guaranteed in the limit permissible mode.

## Electric Parameters HT8563A

Electric parameters of the microcircuit HT8563Aat the temperature of  $T_A = -40...+85^{\circ}C$ ,

$V_{CC} = 4.5 - 5.5$  B are indicated in the table

| Parameter Description,       | Identifi         |                                                | N               | orm                |        |

|------------------------------|------------------|------------------------------------------------|-----------------|--------------------|--------|

| Measurement Unit             | -cation          | Measurement Mode                               | Not             | Not over           | Remark |

|                              | oution           |                                                | less            |                    |        |

| 1                            | 2                | 3                                              | 4               | 5                  | 6      |

|                              | $V_{DD}$         | I2C bus –active;                               | 1.8             | 5.5                |        |

| Supply voltage, V            |                  | $F_{SCL} = 400 \text{ kHz}$                    |                 |                    |        |

| Supply voltage, v            |                  | in the non-active                              | 1.0             | 5.5                | 1,2    |

|                              | -                | mode                                           |                 |                    |        |

| Input leakage current, µA    | ILI              | $V_{IN} = V_{DD}; V_{IN} = V_{SS}$             | -               | 1                  |        |

| Output leakage current, µA   | I <sub>LO</sub>  | $V_{OUT} = V_{DD}; V_{OUT} = V_{SS}$           | -               | 1                  |        |

| Consumption current, µA      | I <sub>DD1</sub> | CLKOUT–off,                                    | -               | 800                |        |

|                              |                  | F <sub>SCL</sub> =400 kHz                      |                 |                    |        |

|                              |                  | CLKOUT-off, F <sub>SCL</sub>                   | -               | 200                |        |

|                              |                  | =100 kHz                                       |                 |                    |        |

|                              |                  | CLKOUT–off,                                    | -               | 0.55               | 1,2    |

|                              |                  | F <sub>SCL</sub> =0 kHz, V <sub>DD</sub> =5V   |                 |                    |        |

|                              |                  | CLKOUT–off,                                    | -               | 0.45               | 1,2    |

|                              |                  | F <sub>SCL</sub> =0 kHz, V <sub>DD</sub> =2V   |                 |                    |        |

| Low level input voltage, V   | V <sub>IL</sub>  |                                                | V <sub>SS</sub> | 0.3V <sub>DD</sub> |        |

| High level input voltage, V  | V <sub>IH</sub>  |                                                | $0.7V_{DD}$     | V <sub>DD</sub>    |        |

| Low level output current at  | I <sub>OL1</sub> | $V_{OL} = 0.4 \text{ V}, V_{DD} = 5 \text{ V}$ | 1               | -                  |        |

| pin CLKOUT, mA               | _                |                                                |                 |                    |        |

| High level output current at | I <sub>OH1</sub> | V <sub>OH</sub> = 4.6 V, V <sub>DD</sub> =5 V  | 1               | -                  |        |

| pin CLKOUT, mA               |                  |                                                |                 |                    |        |

| Low level output current at  | I <sub>OL2</sub> | $V_{OL} = 0.4 \text{ V}, V_{DD} = 5 \text{ V}$ | 1               | _                  |        |

| pin INT, mA                  |                  |                                                |                 |                    |        |

|                              |                  |                                                |                 |                    |        |

| 1                                                                                                                                                | 2                | 3                        | 4 | 5 | 6 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------|---|---|---|

| Low level output current at<br>pin SDA, mA                                                                                                       | I <sub>OL3</sub> | VOL = 0.4 V, VDD =5<br>V | 3 | - |   |

| Supply low level, detected by the circuit, V                                                                                                     | V <sub>LOW</sub> |                          |   | 1 | 1 |

| Remarks<br>1 Ta= $(25 \pm 5)^{\circ}$ C<br>2 Parameters of the quartz oscillator: f <sub>OSC</sub> =32.768 kHz, Rs≤40 kOhm, C <sub>L</sub> =8 пF |                  |                          |   |   |   |

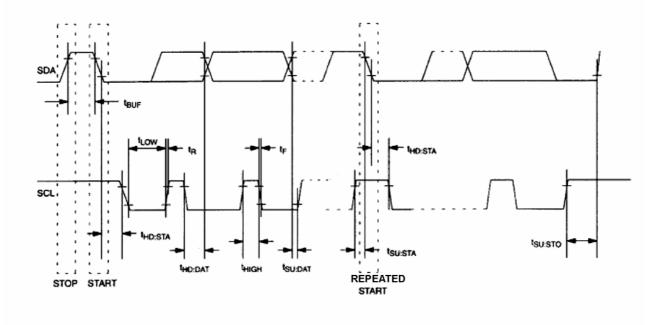

Dynamic parameters of the microcircuit HT8563A at the temperature  $T_A = -40...+85^{\circ}C$ ,  $V_{CC} = 4.5 - 5.5 V$  are listed in the table

| $V_{CC} = 4,5 - 5,5$ V are listed in t<br>Parameter Description, Measurement Unit | Identification                    | Measurement | No       | rm       |

|-----------------------------------------------------------------------------------|-----------------------------------|-------------|----------|----------|

| raiameter Description, Measurement Onit                                           | Identification                    | Mode        | Not less | Not over |

| Cycle frequency SCL, kHz                                                          | f <sub>SCL</sub>                  | _           | 0        | 400      |

| Time of bus vacant condition between the conditions STOP and START, usec          | t <sub>BUF</sub>                  | -           | 4.7      | -        |

| Hold time (repeated) of the condition START, usec                                 | t <sub>HD:STA</sub> ''            | -           | 0.6      | -        |

| Low condition duration of the cycle pulse SCL, usec                               | t <sub>LOW</sub>                  | -           | 1.3      | -        |

| High condition duration of the cycle pulse SCL, usec                              | t <sub>ніGH</sub>                 | -           | 0.6      | -        |

| Presetting time for the repeated condition START, usec                            | t <sub>SU:STA</sub>               | -           | 0.6      | _        |

| Data hold time, usec                                                              | t <sub>HD:DAT</sub> <sup>2)</sup> | -           | 0        | -        |

| Data presetting time, nsec                                                        | t <sub>SU:DAT</sub>               | -           | 100      | -        |

| Rise time for signals SDA and SCL, nsec                                           | t <sub>R</sub>                    | -           | -        | 300      |

| Drop time for signals SDA and SCL, nsec                                           | t <sub>F</sub>                    | -           | -        | 300      |

| Presetting time for the condition STOP, usec                                      | t <sub>su:sto</sub>               | _           | 0.6      | -        |

| Total capacitance load on each bus line, pF                                       | C <sub>B</sub>                    | _           | -        | 400      |

| Capacity input/output, pF                                                         | C <sub>I/O</sub>                  | -           | 10       | 10       |

| Load capacitance of the quartz resonator, pF                                      | C <sub>LX</sub>                   | -           | 12.5     | 12.5     |

1) After this time interval the first cycle signal is formed;

2) The device should internally ensure the hold time, at least, 300 nsec for the signal SDA (relative to  $V_{\text{IHMIN}}$  of the signal SCL) in order to overlap the indeterminancy area of the signal SCL drop front Maximum value  $t_{\text{HD:DAT}}$  should be definite in that case, if the device does not increase duration of the low condition ( $t_{\text{LOW}}$ ) of the signal SCL

## Timing diagramm

#### HT8563A Operation description

HT8563A operates as the «slave» device on the serial bus. For access to it expedient to set the condition START and transfer after the register address the device identification code. The next registers can be address in series till the condition STOP is preset. With  $V_{CC}$  below 1.8 V, access granting to the device by the serial interface is not guaranteed. The current time is counted with the supply voltage 1 ÷ 5.5 V. When the supply level becomes lower, than 1V, the bit VL=1 is formed, signaling, that the information about the current time may be incorrect.

#### **Description of Signals**

$V_{DD}$ - connection of the constant supply.  $V_{DD}$  - input from +1 till +5 V. With supply < 1.8 V access to the interface circuit is not guaranteed.

INT – interruption output. Interruption condition is formed with coincidence of the current time with the alarm settings, or with attainment of the condition "0" of the timer countdown. Interruption, formed from the alarm, forms the continous signal, and from the timer can be both continous and pulse one.

SCL (Input of serial synchrosignal) – SCL is used for synchronization of the dasta transfer by the serial interface.

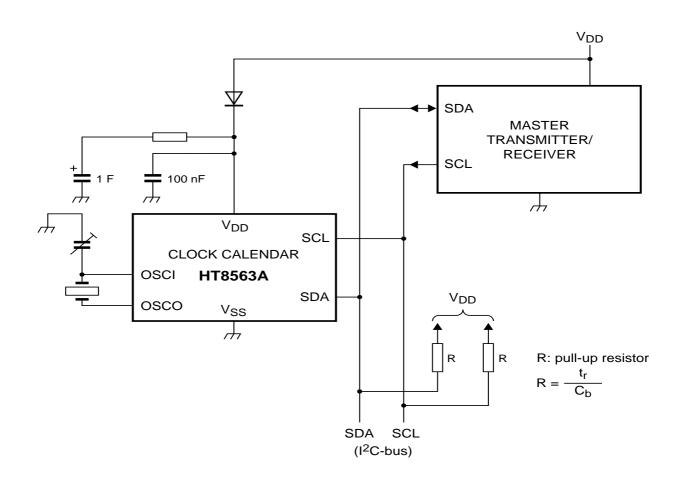

SDA (Input/Output of serial data) – SDA is input/output for the double wire serial interface. Output SDA is the open drain, for which the external load resistor is required to be connected.

CLKOUT (Former output of the orthogonal signal) – For output activation the bit FE is preset to "1". CLKOUT generates the orthogonal signal of four different frequencies (1 Hz, 32 Hz, 1 kHz, 32 kHz). Output CLKOUT is essentially the open drain, for which the external load resistor is required to be connected.

OSCI, OSCO – connection of the standard quartz resonator for the frequency 32.768 kHz. Capacitance load of the internal oscillator for the quartz resonator is equal to

12 pF. HT8563A can operate from the external oscillator with the frequency 32.768 kHz. With this configuration the output OSCI is connected to the signal external oscillator, and OSCO is left unconnected.

#### Watch and Calendar

Acquisition of information on time and date is performed by means of reading the appropriate register bytes. Presetting and time and calendar initialization is performed by means of the appropriate bytes. Information, contained in the time, calendar and alarm registers, is essentially the binary-decimal code. Bit 7 of register 2 is essentially the indication bit of the supply level decrease. < 1V (VL). When this bit = "1", this signifies, that the supply voltage was below the norm, and the information on the current time may be unreliable.

When switching power supply on, all register bits are preset to "0", with the exception of bits FE, VL, TD1, TD0, TESTC and AE, which are preset to "1".

When applying the signal "START" on the double wire bus, the current time transfer occurs from the counters to the auxiliary set of registers. The data on time are read out from these auxiliary registers, while the watch continue to operate. This eliminates the necessity in the repeated reading in case of updating the basic registers in the access process.

| Address | legiste        | Data   |            |         |                |          |                      |                 | Registers / R        | ange    |

|---------|----------------|--------|------------|---------|----------------|----------|----------------------|-----------------|----------------------|---------|

| / (0000 |                |        |            |         |                |          | _                    | rtogiotoro / rt | ungo                 |         |

|         | D7             | D6     | D5         | D4      | D3             | D2       | D1                   | D0              |                      |         |

| 00H     | TEST<br>1      | 0      | STOP       | 0       | TEST<br>C      | 0        | 0                    | 0               | Control 1            |         |

| 01H     | 0              | 0      | 0          | TI/TP   | AF             | TF       | AIE                  | TIE             | Control 2            |         |

| 02H     | VL             | Ten    | s of seco  | onds    |                | Units of | seconds              |                 | Seconds              | 00 – 59 |

| 03H     | х              | Ten    | is of mini | utes    |                | Units of | minutes              |                 | Minutes              | 00 – 59 |

| 04H     | Х              | х      | Tens o     | f hours |                | Units o  | f hours              |                 | Hours                | 00 – 23 |

| 05H     | Х              | х      | Tens of    | of date |                | Units of | of date              |                 | Dates                | 01 – 31 |

| 06H     | х              | х      | х          | х       | х              | D        | ay of we             | ek              | Day of week          | 0-6     |

| 07H     | С              | х      | х          | 10 M.   | Units of month |          | Century / month      | 0-1/01-<br>12   |                      |         |

| 08H     |                | Tens o | f years    |         |                | Units c  | of years             |                 | Year                 | 00 – 99 |

| 09H     | AE             | Ten    | is of mini | utes    |                | Units of | minutes              |                 | Minutes of<br>alarm  | 00 – 59 |

| 0AH     | AE             | Х      | Tens o     | f hours |                | Units o  | of hours             |                 | Hours of alarm       | 00 – 23 |

| 0BH     | AE             | Х      | Tens of    | of date | Units of date  |          |                      | Date of alarm   | 01 – 31              |         |

| 0CH     | AE             | х      | х          | х       | x Day of week  |          | Week day of<br>alarm | 0 – 6           |                      |         |

| 0DH     | FE             | х      | х          | х       | х              | x        | FD1                  | FD0             | Control of<br>CLKOUT |         |

| 0EH     | TE             | Х      | Х          | Х       | Х              | Х        | TD1                  | TD0             | Control of timer     |         |

| 0FH     | Value of timer |        |            |         |                |          |                      |                 | Timer                |         |

**Registers RTC HT8563A**

## **Control Registers**

Control Register 1

TEST1 (activation of test mode) – This bit, preset to logic "1", activates the test mode, with logic "0" normal functioning of the circuit.

STOP – This bit, preset to logic "1" in the test mode perform the zero setting of all dividers, with logic "0" – normal functioning of the circuit.

TESTC (activation of the test mode) – This bit, preset to logic "1", activates the test mode, with logic "0" normal functioning of the circuit.

**Control Register 2**

TI/TP (formation of the pulse interruption signal at output INT) – This bit, preset to logic "0", with appearance of the timer flag TF at output INT forms the constant interruption signal of the low level. The bit, preset to logic "1" at output INT, forms the interruption pulse signal (signal frequencies are listed in the table).

| Timer Input Frequency<br>(Hz) | Period INT (sec). <sup>[1]</sup> |        |  |

|-------------------------------|----------------------------------|--------|--|

|                               | N =1 <sup>[2]</sup>              | N > 1  |  |

| 4096                          | 1/8192                           | 1/4096 |  |

| 64                            | 1/128                            | 1/64   |  |

| 1                             | 1/64                             | 1/64   |  |

| 1/60                          | 1/64                             | 1/64   |  |

[1] TF and INT become active simultaneously.

[2] N – value, loaded to the timer register. Timer is stopped with N = 0.

AF (alarm flag) - bit, in logic "1" informs about interruption by actuation of the alarm, by means of software the bit AF can be reset only.

TF (timer flag) - bit, in logic "1" informs about interruption by actuation of the timer, by the software means the bit TF can be reset only.

AIE (activation of alarm) - bit, preset to logic "1", activates operation of the alarm.

TIE (activation of timer) - bit, preset to logic "1", activates operation of the alarm.

Control Register CLKOUT.

FE (output activation CLKOUT): This bit, preset to logic "1", activates output CLKOUT. Frequency of the output orthogonal signal is determined by the bits FD0 and FD1.

FD – bits determine the frequency of the output orthogonal signal, when output of the orthogonal signal is activated. The frequencies are listed in the table, which can be selected by bits FD.

| FD1 | FD0 | Frequency CLKOUT |

|-----|-----|------------------|

| 0   | 0   | 32.768 kHz       |

| 0   | 1   | 8.192 kHz        |

| 1   | 0   | 4.096 kHz        |

| 1   | 1   | 1 Hz             |

## **Timer Control Register**

TE (timer activation): This bit, preset to logic "1", activates the frequency application to the timer input from the oscillator. The signal frequency is determined by bits TD0 and TD1.

| TD1 | TD0 | Timer Input Frequency |

|-----|-----|-----------------------|

| 0   | 0   | 4096 Hz               |

| 0   | 1   | 64 Hz                 |

| 1   | 0   | 1 Hz                  |

| 1   | 1   | 1 / 60 Hz             |

Double Wire Serial Data Bus

HT8563A supports the bi-directional double wire bus and the data transfer protocol. The bus can be controlled by the "master" device, which generates the cycle signal (SCL), controls access to the bus, generates the conditions START and STOP. Typical bus configuration with the double wire is indicated in the Figure.

Data transfer can be started only when the bus is not busy. In the process of the data transfer, the data line should remain stable, while the cycle signal line is in the HIGH condition. Alterations of the data line conditions at that moment, when the cycle line is in the high condition, will be regarded as the control signals.

In compliance with this the following conditions are determined:

Bus is not busy: both lines of data and cycle signal are in the HIGH condition.

Data transfer start: Alteration of the data line condition during transition from HIGH to LOW, while the cycle line is in the HIGH condition, is determined as the status START.

Depending on the status of the bit R/W, two types of transfer are possible:

1.Data are transferred from the «master» transmiter to the «slave» receiver. The first byte, transferred by the «master» one, is the address of the «slave» one. Then follows sequence of the data bytes. The «slave» one returns the reception confirmation bits after each received byte. Order of the data transfer: the first one is the most senior digit (MSB).

2.Data are transferred from the «slave» transmiter to the «master» receiver. The first byte (address of «slave») is transferred to the «master» one. Then the «master» returns the confirmation bit. This follows after—the «slave» one of the data sequence. The «master» one returns the reception confirmation bit after each received byte, with exception of the last byte. After reception of the last byte the reception confirmation bit does not return.

The «master» device generates all cycle pulse and the conditions START and STOP. Transmission completes with emergence of the condition STOP or the repeated emergence of the condition START. As the repeated condition START is the beginning of the next serial transmission, then the bus is not vacated. Data transfer order: the first one is the most senior digit (MSB).

HT8563A :

1.Mode of the «slave» receiver (writing mode of HT8563A): Serial data and cycles are received via SDA and SCL appropriately. After transfer of each byte the confirming bit is transferred. Conditions START and STOP are understood as the start and end of the serial transmission. Address recognition is performed by the hardware means after reception of the address of the «slave» one and the direction bit. The address byte is the first byte, received after emergence of the condition START, generated by the «master» one. Address byte contains seven address bits HT8563A, equal to 1010001,

#### accompanied

by the direction bit (R/W), which is equal to 0 for writing. After reception and decoding the address HT8563A provides confirmation on the line SDA. After confirmation by HT8563A of the

«slave» address and the write bit, the «master» one transmits the register address of HT8563A. Thus, the register indicator will be set in HT8563A. Then the «master» one will start to transfer each data byte with the subsequent confirmation reception of each byte receipt. Upon completion of writing the «master» one will form the condition STOP, for termination of the data transfer.

Data writing - mode of the receiver

2. Mode of the «slave» transmitter (read-out mode from HT8563A): The first byte is accepted and is processed as in the mode of the «slave» receiver. But in this mode the direction bit will indicate, that the transmission direction is altered. The serial data are transferred by HT8563A by means of SDA, the cycle pulses – by means of SCL. The statuses of START and STOP are recognized as the start and end of transmission in series. The address byte is the first byte, received after emergence of the status START, generated by the «slave» one. The address byte contains the seven address bits HT8563A, equal to 1010001, accompanied with the direction bit (R/W), which is equal to 1 for reading. After reception and decoding the address byte HT8563A accepts confirmation from the line SDA. Then HT8563A starts to transmit the data from the address, to which the register indicator indicates. If the register indicator is not written prior to initialization of the writing mode, then the first read address will be the last address, stored in the register indicator. HT8563A should transmit the bit of «non-confirmation», in order to complete reading.

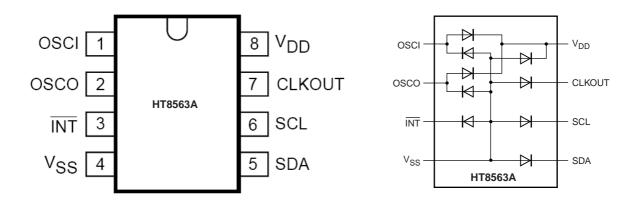

| Pins Description           |                 |                                            |  |  |

|----------------------------|-----------------|--------------------------------------------|--|--|

| Microcircuit Pin<br>Number | Identification  | Purpose of Pin                             |  |  |

| 01                         | OSCI            | Pin for connection of the quartz resonator |  |  |

| 02                         | OSCO            | Pin for connection of the quartz resonator |  |  |

| 03                         | INT             | Interruption output                        |  |  |

| 04                         | V <sub>SS</sub> | Common pin                                 |  |  |

| 05                         | SDA             | Input / Output of data                     |  |  |

| 06                         | SCL             | Synchrosignal input                        |  |  |

| 07                         | CLKOUT          | Frequency divider output                   |  |  |

| 08                         | V <sub>DD</sub> | Supply source pin                          |  |  |

HT8563A

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Real Time Clock category:

Click to view products by HTCSEMI manufacturer:

Other Similar products are found below :

DS1302Z-LF 710029X MCP79400T-I/SN 879047C 405800G RX8900SA UA3 PURE SN RX8900SA UB3 PURE SN RX8130CE B0 RX8130CE BX PCF85263AUKZ RX-4035LC:B3 PURE SN RX-8564LC:B PURE SN RX-4571LC:B PURE SN RX-8803LCUB PURE SN BULK RX8010SJ:B3 PURE SN RX-8035SA:AA PURE SN RX-8025SA:AC0 RX-8571SA:B0 PURE SN RX-8571LCB0 PURE SN RTC-8564JE:BB ROHS MCP79401-I/SN MCP7940N-E/SN BQ32002D RTC-8564JE RX4045SAA MCP7940M-I/P BU9873FVT-GE2 DS3232SN# DS3231SN#T&R DS3231SN# DS3231S# DS1743-100IND+ RX8900CE:UA3 RX-8564LC:B3 PURE SN PT7C4307WEX PT7C4337WEX PCF85063TP/1Z PCF85063ATTAJ DS12CR887-5+ RX-4571SA:B3 PURE SN RX-8025NB:AA3 PURE SN RX-8571LC:B3 PURE SN PCF8563TS/4.118 PCF8583T/5.518 S-35190A-I8T1U 1339-2DVGI8 RX-8564LC:B0 PURE SN 1338-18DVGI8 R2051S01-E2-F S-35390A-T8T1U