# I-jet®

I-jet<sup>®</sup> User Guide

for Advanced RISC Machines Ltd's ARM® Cores

l-jet-l

## **COPYRIGHT NOTICE**

© 2012 IAR Systems AB.

No part of this document may be reproduced without the prior written consent of IAR Systems AB. The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such a license.

#### **DISCLAIMER**

The information in this document is subject to change without notice and does not represent a commitment on any part of IAR Systems. While the information contained herein is assumed to be accurate, IAR Systems assumes no responsibility for any errors or omissions.

In no event shall IAR Systems, its employees, its contractors, or the authors of this document be liable for special, direct, indirect, or consequential damage, losses, costs, charges, claims, demands, claim for lost profits, fees, or expenses of any nature or kind.

#### **TRADEMARKS**

IAR Systems, IAR Embedded Workbench, C-SPY, visualSTATE, The Code to Success, IAR KickStart Kit, I-jet, IAR, and the logotype of IAR Systems are trademarks or registered trademarks owned by IAR Systems AB.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems Incorporated.

All other product names are trademarks or registered trademarks of their respective owners.

#### **EDITION NOTICE**

First edition: September 2012

Part number: I-jet-1

Internal reference: IMAE.

## **Contents**

| Introduction                         | 5  |

|--------------------------------------|----|

| The I-jet In-Circuit Debugging Probe |    |

| Requirements                         | 6  |

| Supported ARM core families          | 7  |

| Supported operating systems          |    |

| Connections                          | 7  |

| Working with I-jet                   | 9  |

| Setup and installation               | 9  |

| Software                             | 9  |

| Probe setup                          | 9  |

| Connecting the target system         | 9  |

| Power-on sequence                    | 9  |

| Power up your evaluation board       | 10 |

| Technical specifications             | 11 |

| Model specifications                 | 11 |

| Version history                      | 12 |

| Target interface                     | 13 |

| JTAG/SWD - MIPI-20                   | 13 |

| JTAG/SWD - MIPI-10                   | 15 |

| Indicators                           | 16 |

| USB                                  | 16 |

| JTAG                                 | 16 |

| TPWR (Target power)                  | 16 |

| Adapters                             | 17 |

| The ARM-20 adapter                   | 17 |

| The ADA-MIPI20-TI14 adapter          | 19 |

| The ADA-MIPI20-cTI20 adapter         | 23 |

I-jet® 4 User Guide

| + <sub>I-jet-1:1</sub>

## Introduction

This chapter gives a short overview of the I-jet in-circuit debugging probe. More specifically, this means:

- The I-jet In-Circuit Debugging Probe

- Requirements

- Supported ARM core families

- Supported operating systems

- Connections.

## The I-jet In-Circuit Debugging Probe

I-jet is an in-circuit debugging probe, which connects to the target board via a JTAG or SWD connection, and to the host PC via the USB port. I-jet is also referred to as a debug probe, debug adapter, or JTAG in-circuit emulator by different tool vendors.

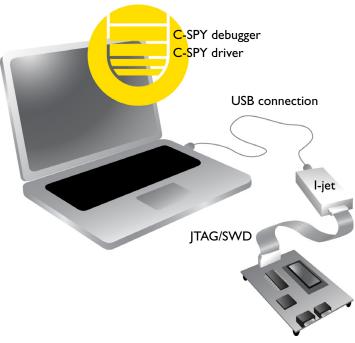

Figure 1: The I-jet in-circuit debugging probe

Besides the typical JTAG debugging, I-jet is capable of providing power to the target board and measuring it with sufficient accuracy to provide a power profile during program execution in real time. This feature is referred to as *power debugging*.

Figure 2: Communication overview

For debugging Cortex-M devices, I-jet supports the SWO (Serial Wire Output) feature, which can be used for tracing the program execution and sending variables at predefined points in your code. I-jet streams the program counter, variables, and power measurement data to the host PC to provide a much better view into program execution in real time.

## Requirements

I-jet needs to be controlled by the IAR C-SPY® Debugger which comes with the IAR Embedded Workbench® IDE.

I-jet®

6 User Guide

UCSARM-4:3

## **Supported ARM core families**

These cores are supported:

- ARM7

- ARM9

- ARM11

- Cortex-M

- Cortex-R

- Cortex-A.

## Supported operating systems

I-jet can be used on these operating systems:

- Windows 7 (64-bit)

- Windows 7 (32-bit)

- Windows Vista

- Windows XP.

## **Connections**

These interfaces are supported:

- JTAG

- SWD/SWO.

I-jet has a MIPI-20 connector on the front panel. I-jet comes with MIPI-20 and MIPI-10 cables, as well as a legacy ARM-20 adapter.

+

Connections

I-jet®

8 User Guide

+ UCSARM-4:3

## Working with I-jet

This chapter describes how to work with I-jet. More specifically, this means:

- Setup and installation

- Connecting the target system.

For information about debugging using I-jet, see the C-SPY® Debugging Guide for ARM.

## Setup and installation

#### **SOFTWARE**

I-jet requires IAR Embedded Workbench for ARM to be installed.

#### **PROBE SETUP**

I-jet does not require any special driver software installation. All drivers for I-jet are part of the installation of IAR Embedded Workbench for ARM.

If you need to install the driver manually, navigate to

For information about using multiple I-jet probes on the same PC, see the *C-SPY*® *Debugging Guide for ARM*.

## Connecting the target system

#### **POWER-ON SEQUENCE**

When the target power is not provided by I-jet, you do not need to follow any special powering sequence. Connect I-jet to a powered and running target board and start debugging.

When *hot-plugging*, the target GND and the USB host GND must be at the same level. To prevent damage due to GND differences, make sure that the PC and the target board power supply are connected to the same wall outlet or a common desktop power strip.

Connecting the target system

## POWER UP YOUR EVALUATION BOARD

If you have an evaluation board that is prepared for it, you can power the board via I-jet through pin 19 on the 20-pin 0.1 in pitch JTAG connector, or pin 11/13 on the small 0.05 in pitch MIPI-20 connector. Target power of up to 400 mA can be supplied from I-jet with overload protection. Most of the IAR Systems KickStart Kits contain an evaluation board that can be powered this way.

**Note:** The target board will get power via I-Jet once you start the compile and download routine, but not before.

I-jet® IO User Guide

UCSARM-4:3

## **Technical specifications**

This chapter provides technical specifications for the I-jet In-Circuit Debugger. More specifically, this means:

- Model specifications

- Version history

- Target interface

- Indicators

- Adapters.

## **Model specifications**

These are the specifications of I-jet:

USB speed 480 Mbps (USB 2.0)

USB connection Micro-B

JTAG connection MIPI-20, MIPI-10

Adapters included ARM-20

I-jet debug interface JTAG and SWD

JTAG/SWD maximum clock 32 MHz

**SWO protocols supported** Manchester and UART

SWO maximum clock speed 60 MHz

**Power supplied to target** 420 mA max at 4.4 V-5 V

**Over-current protection** 520 mA (± 1%)

Target power measurement resolution ~160 µA

**Target power measurement speed** up to 200 ksps (kilo samples per second)

JTAG voltage range (auto-sensing) 1.8 V to 5 V (± 10%)

Version history

JTAG VTref measurement resolution ~2 mV

Current draw from VTref < 50 µA

I-jet comes with a 20-pin MIPI connector (0.05 in  $\times$  0.05 in pitch) on the front panel. It includes two cables:

- A 6-inch cable with 20-pin MIPI connectors on both ends for the Cortex-M targets with 20-pin MIPI headers. Pin 7 on each end is keyed with a white plug.

- A 6-inch cable with 20-pin MIPI connectors on one side (to connect to I-jet), and 10-pin MIPI connector on the other side for connection to Cortex-M targets with 10-pin headers. Pin 7 on each end is keyed with a white plug.

## **Version history**

These are the versions of I-jet:

Version A

The first version.

I-jet®

12 User Guide

UCSARM-4:3

## **Target interface**

This section contains descriptions of pinout, signals, and connectors.

### JTAG/SWD - MIPI-20

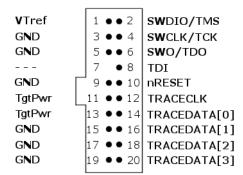

I-jet comes with a 6-inch cable with 20-pin MIPI connectors on both ends for the Cortex-M targets with 20-pin MIPI headers. Pin 7 on each end is keyed with a white plug:

Figure 3: The MIPI-20 connector

These are the MIPI-20 pin definitions:

| Pin | Signal    | Туре        | Description                                                                                                                                                                                                                                              |

|-----|-----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I   | VTref     | Input       | The target reference voltage. Used by I-jet to check whether the target has power, to create the logic-level reference for the input comparators, and to control the output logic levels to the target. It is normally fed from Vdd of the target board. |

| 2   | SWDIO/TMS | I/O, output | JTAG mode set input of taget CPU. This pin should be pulled up on the target. Typically connected to TMS of the target CPU.                                                                                                                              |

| 4   | SWCLK/TCK | Output      | JTAG clock signal to target CPU. It is recommended that this pin is pulled to a defined state of the target board.  Typically connected to TCK of the target CPU.                                                                                        |

Table 1: MIPI-20 pin definitions

| Pin | Signal       | Туре   | Description                                                                                                                                                                                                                                                                                         |

|-----|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | SWO/TDO      | Input  | JTAG data output from target CPU. Typically connected to TDO of the target CPU. When using SWD, this pin is used as Serial Wire Output trace port. (Optional, but not required for SWD communication.)                                                                                              |

|     |              |        | This pin (normally pin 7) does not exist.                                                                                                                                                                                                                                                           |

| 8   | TDI          | Output | JTAG data input of target CPU. It is recommended that this pin is pulled to a defined state on the target board. Typically connected to TDI of the target CPU. For CPUs which do not provide TDI (SWD-only devices), this pin is not used. I-jet will ignore the signal on this pin when using SWD. |

| 10  | nRESET       | I/O    | Target CPU reset signal. Typically connected to the RESET pin of the target CPU, which is typically called nRST, nRESET, or RESET.                                                                                                                                                                  |

| П   | TgtPwr       | Output | This pin can be used for supplying 5 V power to the target hardware from I-jet.                                                                                                                                                                                                                     |

| 12* | TRACECLK     | Input  | Input trace clock.                                                                                                                                                                                                                                                                                  |

| 13  | Tgt Pwr      | Output | This pin can be used for supplying 5 V power to the target hardware from I-jet.                                                                                                                                                                                                                     |

| 14* | TRACEDATA[0] | Input  | Input Trace data pin 0.                                                                                                                                                                                                                                                                             |

| 16* | TRACEDATA[I] | Input  | Input Trace data pin 1.                                                                                                                                                                                                                                                                             |

| 18* | TRACEDATA[2] | Input  | Input Trace data pin 2.                                                                                                                                                                                                                                                                             |

| 20* | TRACEDATA[3] | Input  | Input Trace data pin 3.                                                                                                                                                                                                                                                                             |

Table 1: MIPI-20 pin definitions

### \* Not used.

Pins 3, 5, 9, 15, 17, and 19 are GND pins connected to GND in I-jet. They should also be connected to GND in the target system.

I-jet® I4 User Guide

UCSARM-4:3

## JTAG/SWD - MIPI-10

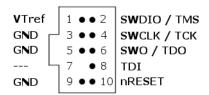

I-jet also comes with a 6-inch cable with a 20-pin MIPI connector on one side (to connect to I-jet) and a 10-pin MIPI connector on the other side for connection to Cortex targets with 10-pin headers. Pin 7 on each end is keyed with a white plug:

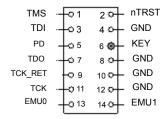

Figure 4: The MIPI-10 connector

These are the MIPI-10 pin definitions:

| Pin | Signal    | Туре        | Description                                                                                                                                                                                                                                              |

|-----|-----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ī   | VTref     | Input       | The target reference voltage. Used by I-jet to check whether the target has power, to create the logic-level reference for the input comparators, and to control the output logic levels to the target. It is normally fed from Vdd of the target board. |

| 2   | SWDIO/TMS | I/O, output | JTAG mode set input of target CPU. This pin should be pulled up on the target. Typically connected to TMS of the target CPU. When using SWD, this pin is used as Serial Wire Output trace port. (Optional, not required for SWD communication)           |

| 3   | GND       | GND         | Connected to logic GND on I-jet.                                                                                                                                                                                                                         |

| 4   | SWCLK/TCK | Output      | JTAG clock signal to target CPU. It is recommended that this pin is pulled to a defined state of the target board.  Typically connected to TCK of the target CPU.                                                                                        |

| 5   | GND       | GND         | Connected to logic GND on I-jet.                                                                                                                                                                                                                         |

| 6   | SWO/TDO   | Input       | JTAG data output from target CPU. Typically connected to TDO of the target CPU.                                                                                                                                                                          |

|     |           |             | This pin (normally pin 7) does not exist.                                                                                                                                                                                                                |

Table 2: MIPI-10 pin definitions

#### Indicators

| Pin | Signal | Туре   | Description                                                                                                                                                                                                                                                                                         |

|-----|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | TDI    | Output | JTAG data input of target CPU. It is recommended that this pin is pulled to a defined state on the target board. Typically connected to TDI of the target CPU. For CPUs which do not provide TDI (SWD-only devices), this pin is not used. I-jet will ignore the signal on this pin when using SWD. |

Table 2: MIPI-10 pin definitions

## **Indicators**

I-jet has three LED indicators on the front. This section describes the indicators and their statuses.

## **USB**

| Indicator status | Description                               |

|------------------|-------------------------------------------|

| Off              | No USB power.                             |

| Green steady     | Initial state or no transfer.             |

| Green blinking   | USB transfers to or from I-jet.           |

| Red blinking     | USB enumeration.                          |

| Red steady       | USB did not enumerate or broken hardware. |

Table 3: USB indicator statuses

## **JTAG**

| Indicator status | Description                                |

|------------------|--------------------------------------------|

| Off              | vTRef on JTAG header is too low.           |

| Green            | vTRef is at or above 1.8 V.                |

| Green blinking   | Indicates JTAG/SWD communication activity. |

Table 4: JTAG indicator statuses

## **TPWR (TARGET POWER)**

| Indicator status | Description                               |

|------------------|-------------------------------------------|

| Off              | Power to target is not provided by I-jet. |

| Green            | Power to target is provided by I-jet.     |

| Yellow           | Warning. Power to target is above 420 mA. |

Table 5: TPWR indicator statuses

| Indicator status | Description                                                        |  |

|------------------|--------------------------------------------------------------------|--|

| Red              | Error. Overcurrent limit (520 mA) detected and power to target was |  |

|                  | switched off for protection.                                       |  |

Table 5: TPWR indicator statuses

## **Adapters**

#### **THE ARM-20 ADAPTER**

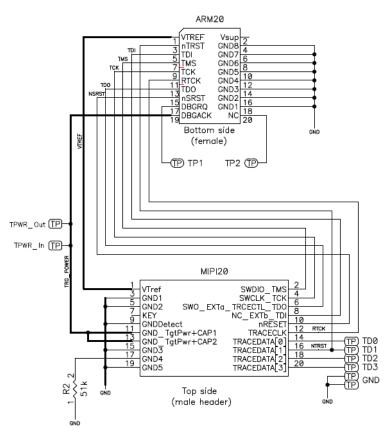

The ARM-20 adapter is included with I-jet. It converts the MIPI-20 I-jet cable to the legacy ARM-20 (0.1 in  $\times$  0.1 in pitch) JTAG headers. This is a diagram of the adapter:

Figure 5: MIPI-20 to ARM-20 JTAG adapter

Adapters

These are the pin definitions of the ARM-20 adapter:

| Pin         | l-jet<br>direction | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nTRST       | Output             | Test Reset       | Active LOW signal that resets the TAP controller's state machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TCK         | Output             | Test Clock       | TCK synchronizes all JTAG transactions. TCK connects to all JTAG devices in the scan chain. TCK flows down the stack of modules and connects to each JTAG device. However, if there is a device in the scan chain that synchronizes TCK to some other clock, then all down-stream devices are connected to the RTCK signal on that processor.                                                                                                                                                                                     |

| TMS         | Output             | Test Mode Select | TMS controls transitions in the tap controller state machine. TMS connects to all JTAG devices in the scan chain as the signal flows down the module stack.                                                                                                                                                                                                                                                                                                                                                                       |

| TDI         | Output             | Test Data Input  | TDI is the test data input signal that is routed to the TDI input of the first device in the scan chain.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TDO         | Input              | Test Data Output | TDO is the return path of the test data input signal TDI. In a multi-device JTAG chain, the TDO of the first device connects to the TDI of the next device, etc. The last device's TDO is connected to the TDO on the JTAG header.                                                                                                                                                                                                                                                                                                |

| RTCK        | Input              | TCK Return       | RTCK is a mechanism for returning the sampled clock to the JTAG equipment, so that the clock is not advanced until the synchronizing device captured the data. In adaptive clocking mode, I-jet is required to detect an edge on RTCK before changing TCK. In a multi-device JTAG chain, the RTCK output from a device connects to the TCK input of the down-stream device.  If there are no synchronizing devices in the scan chain, it is unnecessary to use the RTCK signal and it is connected to ground on the target board. |

| Table 6: AR | RM-20 pin def      | initions         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

I-jet®

User Guide

+ UCSARM-4:3

| Pin                   | I-jet<br>direction | Name                        | Description                                                                                                                                                                                                                                                                                                                                                |

|-----------------------|--------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VTref                 | Input              | Voltage Target<br>Reference | This is the target reference voltage. It indicates that the target has power. VTref is normally fed from Vdd on the target hardware and might have a series resistor (though this is not recommended).  VTref is used by I-jet to detect if target power is active and to set JTAG signal voltage reference for level translators.                         |

| nSRST                 | I/O                | System Reset                | Active LOW open-collector signal that is driven by I-jet to reset the device and/or the target board. I-jet senses this line to determine when you have reset the device.                                                                                                                                                                                  |

| Vsupply               | Output             |                             | This pin is not connected to I-jet.                                                                                                                                                                                                                                                                                                                        |

| DBGRQ                 | Output             |                             | This pin is not connected on I-jet.                                                                                                                                                                                                                                                                                                                        |

| DBGAC<br>K/TRGP<br>WR | Output             | Target Power                | This pin is used under SW control to supply 5 V power to the target board. It should be routed through a jumper shunt to the 5 V DC board input to eliminate the power adapter during debugging. The maximum current supplied by I-jet on this pin is about 420 mA. When the current supplied reaches ~500 mA, the power will be shut down for protection. |

Table 6: ARM-20 pin definitions

The R2 pull-down on pin 17 of the I-jet MIPI20 connector is a signal to the I-jet that a legacy ARM-20 adapter is being used. Other adapters will have different resistors so that I-jet can identify them if needed. A solid GND on this pin means no adapter is being used and the MIPI cable is connected directly between the I-jet and the target board.

#### ARM-20 header information (for target board)

## THE ADA-MIPI20-TI14 ADAPTER

The ADA-MIPI20-TI14 adapter adapts the I-jet standard MIPI-20 cable pinout to the Texas Instruments 14-pin JTAG interface used on many OMAP, DaVinci, and other TMS320, TMS470, and TMS570 target boards.

The adapter has the MIPI-20 male header on top for connecting the I-jet MIPI-20 cable, and a TI-14-style female header (socket) on the bottom. The TI-14 JTAG header is a 14-pin, double-row, 0.1 in  $\times$  0.1 in (2.54 mm  $\times$  2.54 mm) pitch connector with a key (plug) in position 6 to prevent misconnections. In case the key plug is missing, a white arrow on pin 1 of the TI-14 connector helps you ensure proper orientation.

Figure 6: The ADA-MIPI20-TI14 adapter

This is a diagram of the adapter:

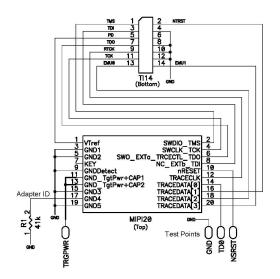

Figure 7: Diagram of the ADA-MIPI20-TI14 adapter

This is the pinout of the target TI-14 JTAG header. Pin 6 should be missing to indicate the proper orientation.

Figure 8: Pinout of the target TI-14 JTAG header

These are the pin defintitions for the TI14 header:

| Pin   | l-jet<br>direction | Name                | Description                                                                                                                                                                                                                            |

|-------|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nTRST | Output             | Test Logic<br>Reset | Active LOW signal that causes all test and debug logic in the device to be reset along with the IEEE 1149.1 TAP.                                                                                                                       |

| TCK   | Output             | Test Clock          | This is the test clock used for driving the IEEE 1149.1 TAP state machine and logic.                                                                                                                                                   |

| TMS   | Output             | Test Mode<br>Select | Directs the next state of the IEEE 1149.1 TAP state machine.                                                                                                                                                                           |

| TDI   | Output             | Test Data<br>Input  | IEEE 1149.1 scan data input to the device.                                                                                                                                                                                             |

| TDO   | Input              | Test Data<br>Output | IEEE 1149.1 scan data output from the device.                                                                                                                                                                                          |

| RTCK  | Input              | TCK Return          | Used only in Adaptive Clocking mode. I-jet monitors RTCK to determine when to send the next TCK.                                                                                                                                       |

| PD    | Input              | Power Detect        | Should be tied to the I/O voltage of the target device. Used by I-jet to detect if target power is active and to set the JTAG signal voltage reference for level translators.                                                          |

| EMU0  | I/O                | Emulation 0         | Depending on the device, EMU pins support boot modes and other features. I-jet does not use this pin but it is routed to the TRACEDATA[2] pin on the MIPI20 connector. For proper booting, this pin should be pulled-up on the target. |

Table 7: TI14 pin definitions

Adapters

| Pin  | l-jet<br>direction | Name        | Description                                                                                                                                                                                                                            |

|------|--------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EMUI | I/O                | Emulation I | Depending on the device, EMU pins support boot modes and other features. I-jet does not use this pin but it is routed to the TRACEDATA[3] pin on the MIPI20 connector. For proper booting, this pin should be pulled-up on the target. |

Table 7: TI14 pin definitions

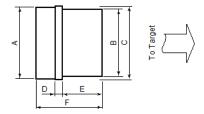

These are the top view dimensions of the ADA-MIPI20-TI14 adapter:

Figure 9: Top view of the ADA-MIPI20-TI14 adapter

| A | 18.9 mm (0.74 in) |

|---|-------------------|

| В | 17.7 mm (0.7 in)  |

| C | 19.4 mm (0.76 in) |

| D | 1.8 mm (0.07 in)  |

| E | 11.0 mm (0.43 in) |

| F | 17.8 mm (0.7 in)  |

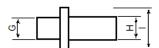

These are the side view dimensions of the ADA-MIPI20-TI14 adapter:

Figure 10: Side view of the ADA-MIPI20-TI14 adapter

| G | 0.5 mm (0.19 in) |

|---|------------------|

| Н | 5.1 mm (0.2 in)  |

| Ī | 9.1 mm (0.36 in) |

## TII4 header information (for target board)

The TI14 header is manufactured by Samtec USA. The model number is TSM-17-DV. For more information, see the manufacturer's web page

http://samtec.com/technical\_specifications/overview.aspx?series=TSM

#### THE ADA-MIPI20-CTI20 ADAPTER

The ADA-MIPI20-cTI20 adapter adapts the I-jet standard MIPI-20 cable pinout to the Texas Instruments compact 20-pin JTAG interface used on some newer OMAP, DaVinci, and other TMS320, TMS470, and TMS570 target boards.

The adapter has the MIPI-20 male header on top for connecting the I-jet MIPI-20 cable, and a cTI-20 style female header (socket) on the bottom. The cTI-20 JTAG header is a 20-pin, double-row, high-density 0.05 in  $\times$  0.1 in  $(1.27 \text{ mm} \times 2.56 \text{ mm})$  pitch connector with a key (plug) in position 6 to prevent misconnections. In case the plug is missing, a white arrow on pin 1 of the cTI-20 connector helps you ensure proper orientation.

Figure 11: The ADA-MIPI20-cTI20 adapter

This is a diagram of the adapter:

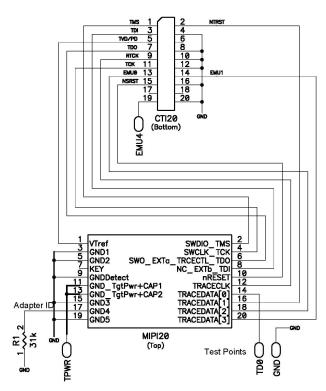

Figure 12: Diagram of the ADA-MIPI20-cTI20 adapter

These are the pin definitions for cTI20:

| Pin   | l-jet<br>direction | Name                | Description                                                                                                      |

|-------|--------------------|---------------------|------------------------------------------------------------------------------------------------------------------|

| nTRST | Output             | Test Logic<br>Reset | Active LOW signal that causes all test and debug logic in the device to be reset along with the IEEE 1149.1 TAP. |

| TCK   | Output             | Test Clock          | This is the test clock used to drive the IEEE 1149.1 TAP state machine and logic.                                |

| TMS   | Output             | Test Mode<br>Select | Directs the next state of the IEEE 1149.1 TAP state machine.                                                     |

Table 8: cTI20 pin definitions

+ UCSARM-4:3

| Pin    | l-jet<br>direction | Name                | Description                                                                                                                                                                                                                            |

|--------|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDI    | Output             | Test Data<br>Input  | IEEE 1149.1 scan data input to the device.                                                                                                                                                                                             |

| TDO    | Input              | Test Data<br>Output | IEEE 1149.1 scan data output from the device.                                                                                                                                                                                          |

| RTCK   | Input              | TCK<br>Return       | Used only in Adaptive Clocking mode. I-jet monitors RTCK to determine when to send the next TCK.                                                                                                                                       |

| PD     | Input              | Power<br>Detect     | Should be tied to the I/O voltage of the target device. Used by I-jet to detect if target power is active and to set the JTAG signal voltage reference for level translators.                                                          |

| EMU0   | I/O                | Emulation 0         | Depending on the device, EMU pins support boot modes and other features. I-jet does not use this pin but it is routed to the TRACEDATA[2] pin on the MIPI20 connector. For proper booting, this pin should be pulled-up on the target. |

| EMUI   | I/O                | Emulation I         | Depending on the device, EMU pins support boot modes and other features. I-jet does not use this pin but it is routed to the TRACEDATA[3] pin on the MIPI20 connector. For proper booting, this pin should be pulled-up on the target. |

| nRESET | I/O                | System<br>Reset     | Active LOW open-collector signal that can be driven by I-jet to reset the device and/or the target board. I-jet senses this line to determine when a board has been reset by the user or by watchdog timer.                            |

Table 8: cTI20 pin definitions

+

Adapters

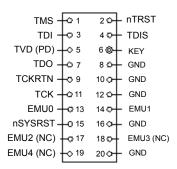

This is the pinout of the target cTI20 JTAG header. Pin 6 should be missing to indicate the proper orientation.

Figure 13: Pinout of the target cTI20 JTAG header

These are the top view dimensions of the ADA-MIPI20-cTI20 adapter:

Figure 14: Top view of the ADA-MIPI20-cTI20 adapter

| A | 18.9 mm (0.74 in) |

|---|-------------------|

| В | 17.7 mm (0.7 in)  |

| C | 19.4 mm (0.76 in) |

| D | 1.8 mm (0.07 in)  |

| J | 6.0 mm (0.24 in)  |

| K | 12.8 mm (0.50 in) |

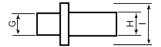

These are the side view dimensions of the ADA-MIPI20-cTI20 adapter:

Figure 15: Side view of the ADA-MIPI20-cTI20 adapter

G 0.5 mm (0.19 in)

H 5.1 mm (0.2 in)

I 9.1 mm (0.36 in)

## cTI20 header information (for target board)

The cTI20 header is manufactured by Samtec USA. The model number is FTR-110-51-S-D-06. For more information, see the manufacturer's web page http://www.samtec.com/technical\_specifications/overview.aspx?series=FTR.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Sockets & Adapters category:

Click to view products by IAR Systems manufacturer:

Other Similar products are found below:

6508-0-00-01-00-00-33-0 AC164341 AC164348 1262 22827 AC164353 TDGL015 ATF15XXDK3-SAA100 SA247 SM64TQ-ACTEL-1

70-0036 DS91230+ SMPA-ISP-ACTEL-3-KIT 16017 KIT 70601-3 SM132CQ-ACTEL IPC0181 IPC0175 IPC0165 AC164397 congaThin MITX/eDP to DP Adapter ML-ADP-EVN ASA.01 ASA.09 ASA.12 ASA.14 TOOLSTICK990MPP MIKROE-425 C305000ACP2

110-83-320-41-605101 110-83-632-41-605101 110-83-640-41-605101 110-83-628-41-605101 116-83-306-41-001101 PA0003 PA0007

PA0009 PA0035 PA0085 PA0096 IPC0079 ATARD-DBGADPT 80-000286 ATSTK600-RC88 ATSTK600-SC06 ATSTK600-RC78

SPC560PADPT64S AC164345 AC164342 14-351000-11-RC