# 24-port 10/100M + 2-port Gigabit Smart Switch Controller

#### **Features**

- Provides 24 SS-SMII, 2 RGMII, 2 1000Base-X SERDES and one MII

- Built-in 2.75Mb RAM

- Support packet length up to 1536 Bytes

- Store & forward, share memory, non-blocking architecture

- Supports flow control

- 802.3x in full duplex

- Collision/carrier\_sense based backpressure in half duplex

- Provides up to 4K MAC address entries

- CRC/ direct hashing algorithm

- Programmable aging timer (55s~15.7hr) error < 4 %</li>

- Configurable MAC address table

- Optional MAC address learning

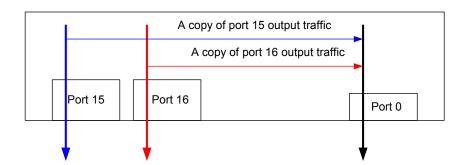

- Supports porting mirroring function (Tx, Rx, Tx&Rx)

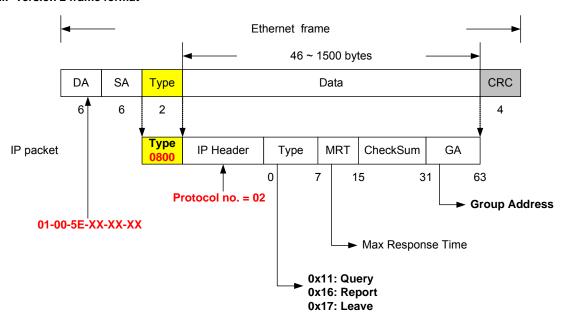

- Supports IGMP snooping function

- Version 1 and Version 2

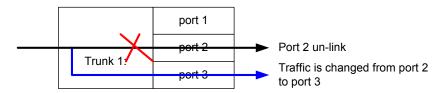

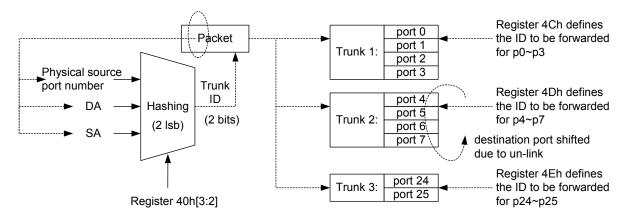

- Supports flexible 3 trunking groups

- (Port 0 ~ port 3, port 4~ port 7, Gigabit port 1 ~ port 2)

- Load balance based on (physiccal port, Destination MAC Address, Source MAC Address, Destination MAC Address/Source MAC Address)

- Link failure recovery

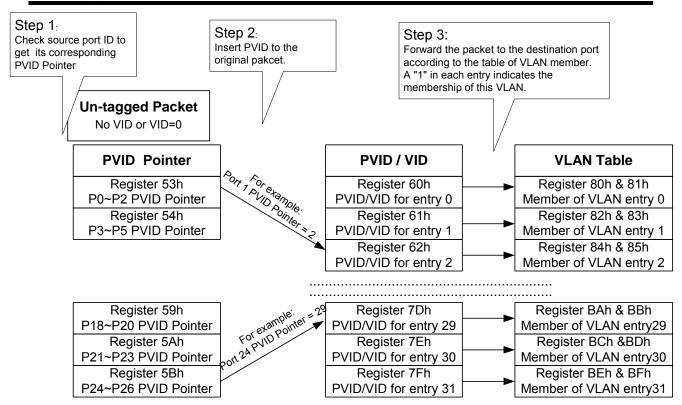

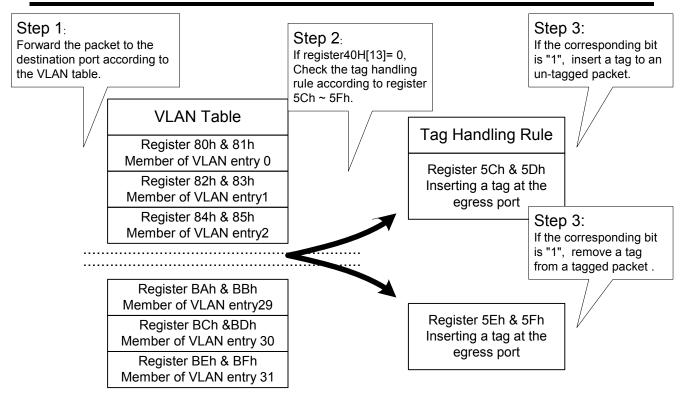

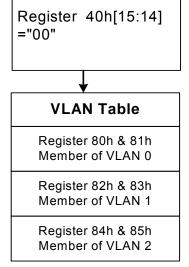

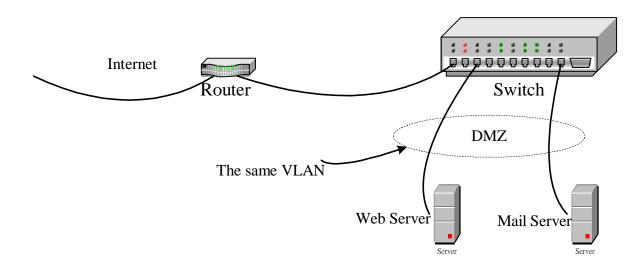

- Supports VLAN

- Port based VLAN

- Tag based VLAN

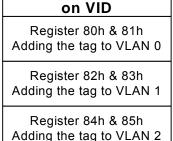

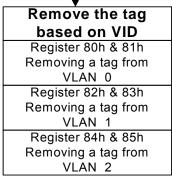

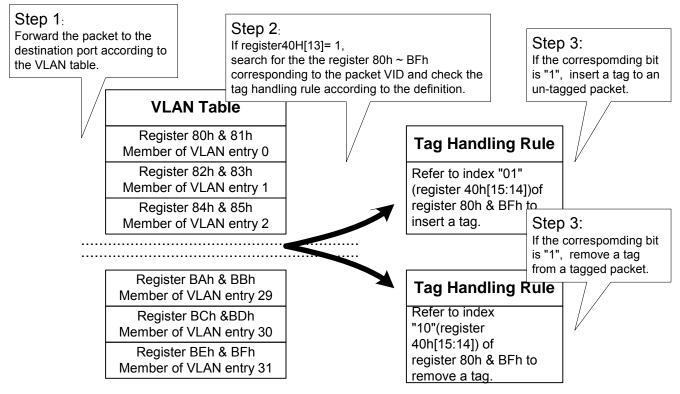

- Add/ remove/ modify tag based on VID or physical port

- Support Class of Service

- Port based CoS

- 802.1Q priority tag based

- IP TOS/DSCP based (IPv4/IPv6)

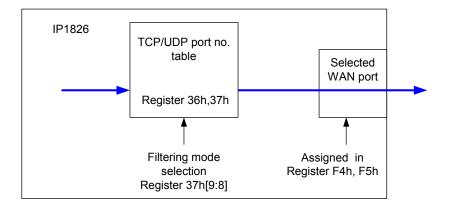

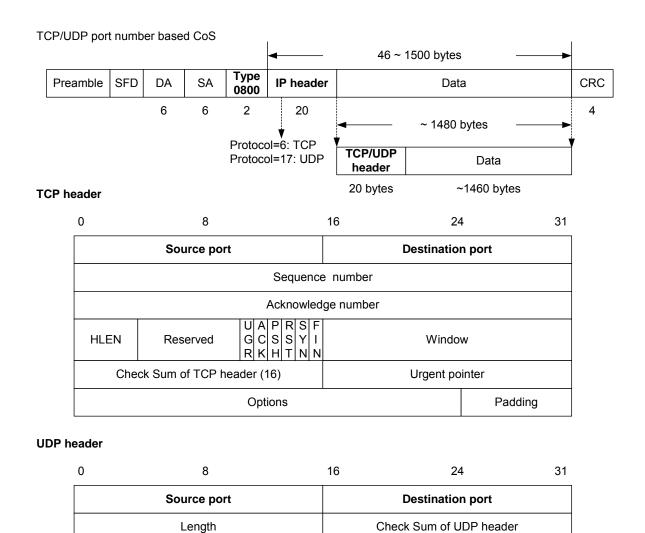

- TCP/UDP port based

- 2 level of priority per port

- WRR/ First-Come-First-serve/ Srict priority

- Broadcast storm control support

- Broadcast rate control per port

- Block broadcast packet that does not belong to ARP or IP packet forwarded to CPU port

- Supports port security

- MAC address based

- IP address based

- TCP/UDP port based

- Supports Bandwidth control with/without flow control

- 480 configurable levels for p0~p23 and MII port (from 32kbps to 63.75 Mbps)

- 508 configurable levels for RGMII port (from 32kbps to 510 Mbps)

- Supports 5 port state for Spanning Tree protocol

- Blocking/ listening/ learning/ forwarding/ disabled

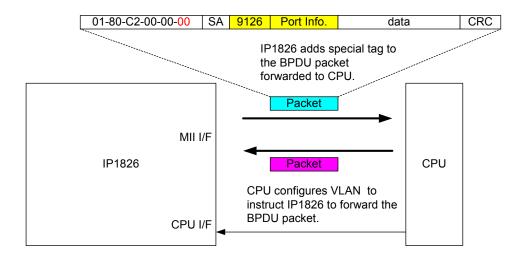

- Forward BPDU to CPU port

- Captures the specific packet and forward it to CPU port

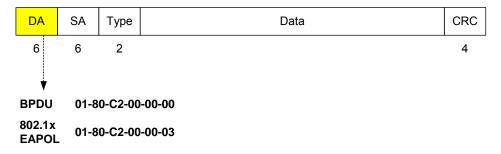

- BPDU, LACP, 802.1x, GMRP, GVRP, ARP

- ICMP, IGMP, TCP, UDP, OSPF

- Packets with specific TCP/UDP port number

- PHY address setting for CPU, Giga 1 and Giga2 port

- Operating mode configuration

- Pin initial setting

- 2 wire serial interface for EEPROM

- 2 wire serial interface for register setting

- Status counters for each port

- RX/TX packet count

- CRC error packet count

- Dropped packet count

- Collision count

- Programmable serial driving LED functions

- Only one 25MHz crystal is needed

- Optional 25Mhz, 50Mhz clock output

- Adjustable IO voltage (3.3/2.5v MII, 3.3/1.8v SS-SMII, 2.7V~1.9V RGMII)

- Built-in 2.5v and 1.9 regulator

- 144 pin EPAD. Lead-free package

## **General Description**

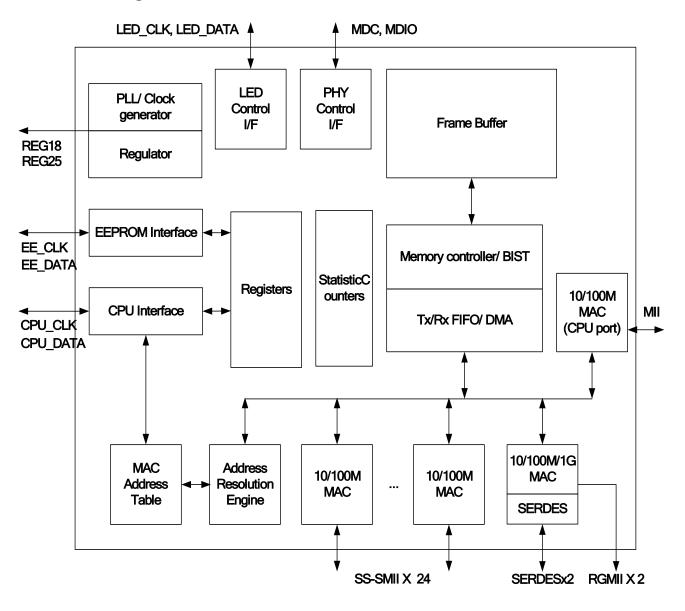

The IP1826D is a non-blocking, store-and-forward architecture switch controller, which supports 24-port SS-SMII, 2-port RGMII/ SERDES, and one-port MII for a 24+2G smart switch application. With two built-in SERDES transceiver, the IP1826D provides a very cost-effective solution for a 24+2 Gigabit fiber without external Gigabit Ethernet transceivers.

**Note:** In the following paragraphs, 24-port SS-SMII is referred to as port  $0 \sim \text{port } 23$ , 2-port RGMII as port 24 (or Giga 1) and port 25 (or Giga 2) and MII port as port 26. These ports are named as  $P0 \sim P26$  in abbreviation. The PHY address for  $P0 \sim P23$  are "8~31" respectively. The PHY addresses "1" and "2" correspond to P24 and P25 respectively.

The IP1826D embeds a 2.75Mb SSRAM for the use of packet buffer and 4K MAC address table. It provides a 2-wire CPU interface, which allows the designer to access to the register. The system configuration can be downloaded from EEPROM upon reset. The serial LED informations is provided through a 2-wire LED interface, simplifing the PCB layout task for LED display. With the external logic devices, the IP1826D can show the status of link, speed, duplex and activity.

In addition to the fundamental function such as the flow control, the broadcast storm control and the programmable MAC address aging time, the IP1826D also supports many advanced features which allow the designer to implement the smart switch features. The IGMP (Internet Group Management Protocol) snooping provides a method to build a multicast link without complicated CPU code. The designer can also use the 2 levels of priority queue to support the real-time streaming application. Supporting both port\_based and tag\_based VLAN, the IP1826D can partition the network traffic by programming the VLAN table. Furthermore the IP1826D supports both non-VID related tag based VLAN and VID related tag based VLAN. The access control based on the MAC layer, the IP layer and TCP/UDP layer provides a method for the designer to implment the Class of Service and the network security.

An 8051 CPU based web controller can easily support the web management. With the web management function, designers can remotely configure and monitor IP1826D smart switches through browsers, such as Microsoft Internet Explorer or Chrome and no program installation is required for the smart switch management.

# **Table of Contents**

| 1 |     |                        |                                                       |    |

|---|-----|------------------------|-------------------------------------------------------|----|

| 2 |     |                        |                                                       |    |

| 3 |     |                        | 2.0                                                   |    |

| 4 |     |                        | ription                                               |    |

|   | 4.1 |                        | Engine and Queue Management                           |    |

|   |     | 4.1.1                  | Packet forwarding                                     |    |

|   |     | 4.1.2                  | Flow Control                                          |    |

|   |     | 4.1.3                  | Bandwidth Control (Egress/Ingress rate control)       |    |

|   |     | 4.1.4                  | Broadcast Storm Control                               |    |

|   |     | 4.1.5                  | Block broadcast packet flooding to CPU port           |    |

|   |     | 4.1.6                  | SS-SMII, RGMII and MII/Reverse MII                    |    |

|   |     | 4.1.7                  | CPU interface                                         |    |

|   |     | 4.1.8                  | Configure the port properties                         |    |

|   |     | 4.1.9<br>4.1.10        | Force link                                            | 20 |

|   |     |                        | Read / write address table (LUT)                      |    |

|   |     | 4.1.11<br>4.1.12       | Read / write PHY registers                            |    |

|   |     | · · · · · <del>-</del> | Read / write EEPROM EEPROM interface                  |    |

|   |     | 4.1.13<br>4.1.14       |                                                       |    |

|   |     | 4.1.14                 | Statistic counters                                    |    |

|   |     | 4.1.15                 | Interrupt                                             |    |

|   |     | 4.1.10                 | LED Display Mode                                      |    |

|   | 4.2 |                        | Group MAC Address Handling Method                     |    |

|   | 4.2 | 4.2.1                  | Port based VI AN                                      |    |

|   |     | 4.2.1                  | Port based VLAN                                       |    |

|   |     |                        | Tag based VLAN                                        |    |

|   |     | 4.2.3<br>4.2.4         | Add/ Remove/ Modify VLAN tag                          |    |

|   |     | 4.2.4                  | VLAN StridingVLAN up-link                             |    |

|   | 4.3 | _                      | f Service                                             |    |

|   | 4.3 | 4.3.1                  |                                                       |    |

|   |     | 4.3.1                  | Output Queue scheduling with priority  Port based CoS |    |

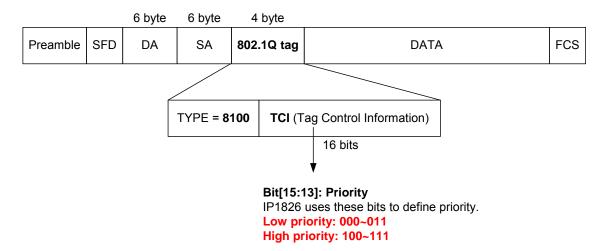

|   |     | 4.3.2                  | 802.1Q priority tag based CoS                         |    |

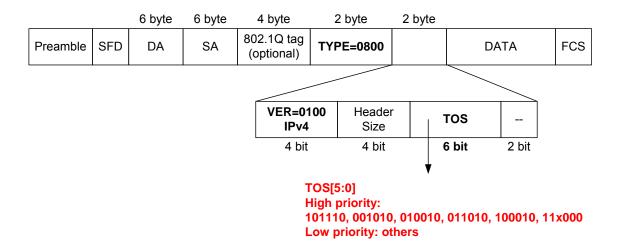

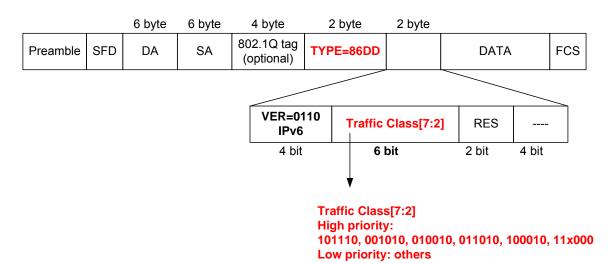

|   |     | 4.3.4                  | IP TOS based CoS                                      |    |

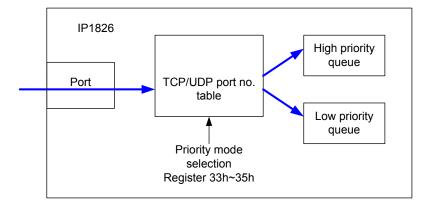

|   |     | 4.3.5                  | TCP/UDP port number based CoS                         |    |

|   | 4.4 |                        | Ethernet protocol frame & IP packet to CPU port       |    |

|   | 4.4 | 4.4.1                  | In-band management frame                              |    |

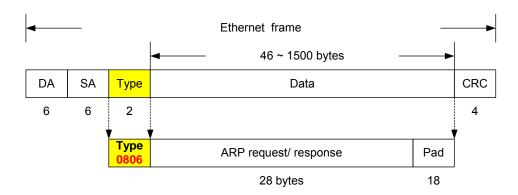

|   |     | 4.4.2                  | ARP, 802.1x                                           |    |

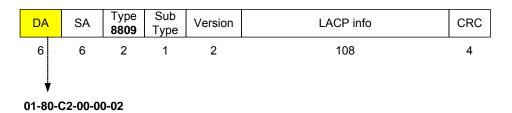

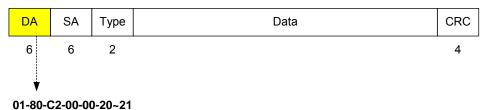

|   |     | 4.4.3                  | BPDU, LACP, GVRP, GMRP                                |    |

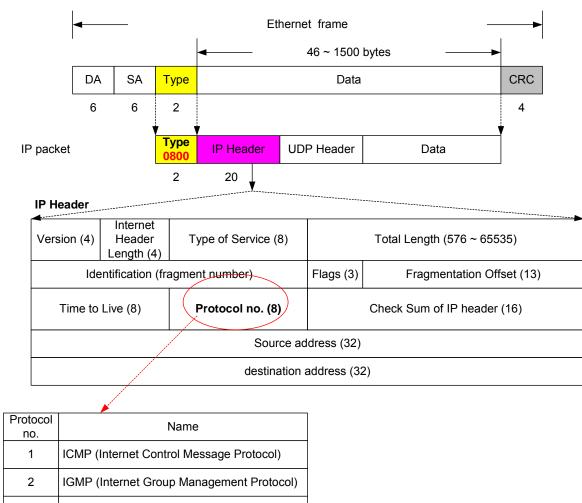

|   |     | 4.4.4                  | ICMP, TCP, UDP, OSPF                                  |    |

|   |     | 4.4.5                  | The other IPv4 protocols                              |    |

|   |     | 4.4.6                  | Block broadcast frame to CPU port                     |    |

|   | 4.5 | -                      | y                                                     |    |

|   | 4.5 | 4.5.1                  | MAC address based Security                            |    |

|   |     | 4.5.1                  | 802.1x port based security                            |    |

|   |     | 4.5.3                  | IP address based Security                             |    |

|   |     | 4.5.4                  | TCP/UDP port based Security                           |    |

|   | 4.6 | -                      | ort filtering                                         |    |

|   | 4.7 |                        | rroring                                               |    |

|   |     | . 511 1911             |                                                       | -  |

|   | 4.8 Trunk       | Channel                                                    | 55  |

|---|-----------------|------------------------------------------------------------|-----|

|   | 4.8.1           | Trunk channel behavior                                     | 55  |

|   | 4.8.2           | Load balance                                               |     |

|   | 4.9 Spanr       | ning tree (receiving/ learning/ forwarding enable/disable) | 56  |

|   | 4.9.1           | BPDU packet forwarding                                     |     |

|   | 4.9.2           | Port states                                                |     |

|   | 4.10 Port F     | Excluding                                                  |     |

|   |                 | Snooping                                                   |     |

|   |                 | e format                                                   |     |

|   | 4.12.1          | Frame format of TCP/UDP header                             |     |

|   | 4.12.2          | Frame format of BPDU and 802.1x                            |     |

|   | 4.12.3          | Frame format of ARP, LACP, GVRP, GMRP                      | 59  |

|   | 4.12.4          | Frame format of ICMP, IGMP, TCP, UDP, OSPF                 |     |

|   | 4.12.5          | Frame format of IGMP                                       |     |

| 5 | Register Map.   |                                                            | 62  |

|   |                 | Control Register (00h~3Ah)                                 |     |

|   |                 | e Control Register (3Bh~3Fh)                               |     |

|   | 5.3 Addre       | ess Resolution Logic Register (40h~E8h)                    | 73  |

|   |                 | r Management Control Register (E9h~EFh)                    |     |

|   |                 | ellaneous Control Register (F0h~FAh)                       |     |

|   | 5.6 SerDe       | es Function Setting (FBh~FFh)                              | 99  |

| 6 | Electrical Char | racteristics                                               | 101 |

|   | 6.1 Absol       | lute Maximum Rating                                        | 101 |

|   | 6.2 AC C        | haracteristics                                             | 102 |

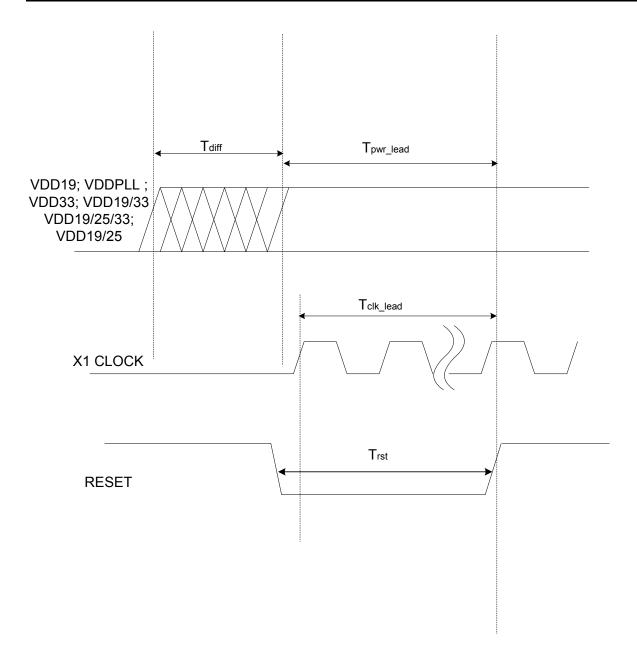

|   | 6.2.1           | Reset, Clock and Power Source                              | 102 |

|   | 6.3 DC C        | haracteristics                                             | 108 |

|   | 6.4 Serial      | Transmitter/Receiver DC characteristic                     | 109 |

| 7 | Order Informat  | tion                                                       | 110 |

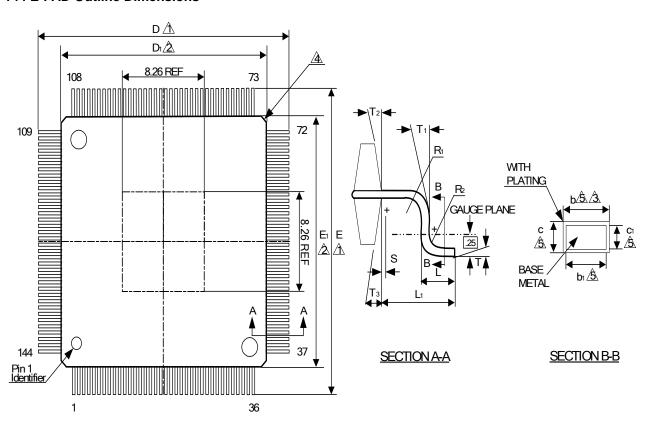

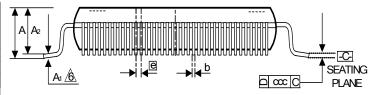

| 8 | Package Detail  | il                                                         | 111 |

# **Revision History**

| Revision #                                                                      | Change Description                                                                                                                                                |  |  |  |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IP1826D-DS-R01                                                                  | Initial release.                                                                                                                                                  |  |  |  |

| IP1826D-DS-R02                                                                  | <ol> <li>Modify SS-SMII \ MII &amp; RGMII V<sub>IL</sub> and V<sub>IH</sub> threshold to DC characteristics</li> <li>Modify register 0x40H description</li> </ol> |  |  |  |

| IP1826D-DS-R03                                                                  | Modify the default value of register : 0xEC and 0xEF                                                                                                              |  |  |  |

| IP1826D-DS-R03.1 Modify MDC signal description: connect a 300ohm bead (page 11) |                                                                                                                                                                   |  |  |  |

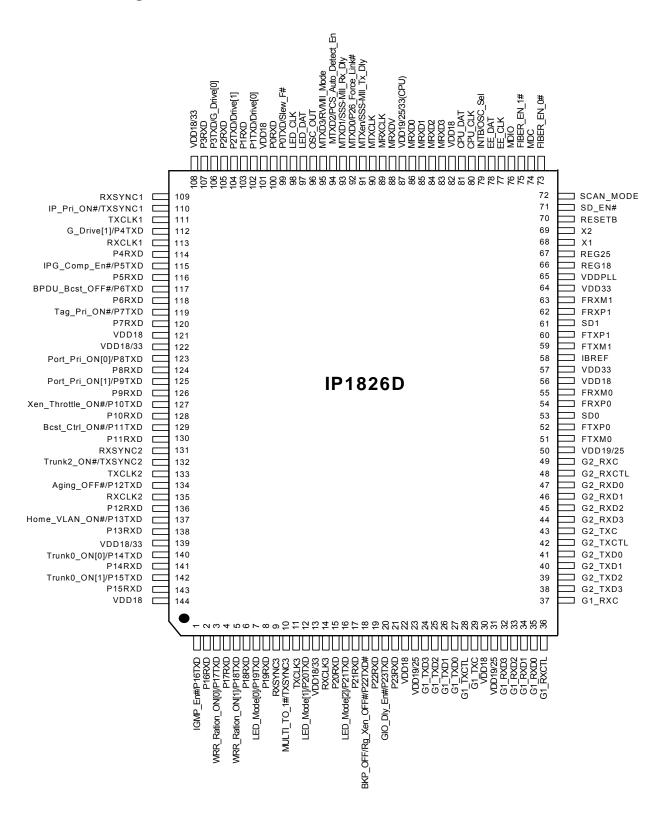

# 1 Pin Diagram

# 2 Block Diagram

# 3 Pin description

| Туре | Description                |

|------|----------------------------|

| Р    | Power or ground            |

| I; O | I: Input pin; O:Output pin |

| IL   | Input latched upon reset   |

| Type | Description                            |  |  |  |

|------|----------------------------------------|--|--|--|

| PD   | PD: Pulled down with internal resistor |  |  |  |

| PU   | PU: Pulled up with internal resistor   |  |  |  |

| I/O  | Bi-direction Input/Output              |  |  |  |

| Pin No.                                                                                                                 | Label                                                                                                                                                                                                                | Туре | Description                                          |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------|

| SS-SMII                                                                                                                 |                                                                                                                                                                                                                      |      |                                                      |

| 99<br>102,104<br>106,112<br>115,117<br>119,123<br>125,127<br>129,134<br>137,140<br>142,1<br>3, 5<br>7,12<br>16,18<br>20 | POTXD, P1TXD, P2TXD, P3TXD, P4TXD, P5TXD, P6TXD, P7TXD, P8TXD, P9TXD, P10TXD, P11TXD, P12TXD, P13TXD, P15TXD, P15TXD, P15TXD, P15TXD, P17TXD, P17TXD, P17TXD, P17TXD, P18TXD, P19TXD, P20TXD, P21TXD, P22TXD, P23TXD | O    | SS-SMII transmits data output for port 0 to port 23. |

| 110<br>132<br>10                                                                                                        | TXSYNC1,<br>TXSYNC2,<br>TXSYNC3                                                                                                                                                                                      | 0    | SS-SMII synchronization output for transmit data     |

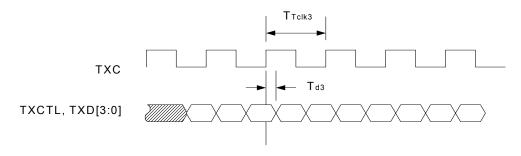

| 111<br>133<br>11                                                                                                        | TXCLK1,<br>TXCLK2,<br>TXCLK3                                                                                                                                                                                         | 0    | SS-SMII transmit clock output                        |

| 100<br>103,105<br>107,114<br>116,118<br>120,124<br>126,128<br>130,136<br>138,141<br>143,2<br>4,6<br>8,15<br>17,19<br>21 | PORXD,<br>P1RXD,<br>P2RXD,<br>P3RXD,<br>P4RXD,<br>P5RXD,<br>P6RXD,<br>P7RXD,<br>P8RXD,<br>P10RXD,<br>P11RXD,<br>P11RXD,<br>P13RXD,<br>P15RXD,<br>P15RXD,<br>P15RXD,<br>P15RXD,<br>P17RXD,<br>P17RXD,<br>P18RXD,<br>P19RXD,<br>P20RXD,<br>P21RXD,<br>P21RXD,<br>P22RXD,<br>P23RXD |   | SS-SMII receive data input            |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------|

| 109<br>131<br>9                                                                                                         | RXSYNC1,<br>RXSYNC2,<br>RXSYNC3                                                                                                                                                                                                                                                  | I | SS-SMII receive synchronization input |

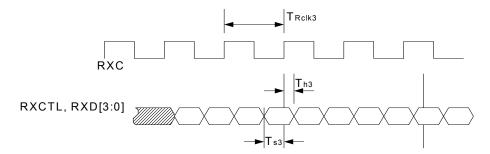

| 113<br>135<br>14                                                                                                        | RXCLK1,<br>RXCLK2,<br>RXCLK3                                                                                                                                                                                                                                                     | I | SS-SMII receive clock input           |

| Pin No.                          | Label                                                                                        | Туре | Description                                                                                                                                                                                                                                                                                                                           |

|----------------------------------|----------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RGMII                            |                                                                                              |      |                                                                                                                                                                                                                                                                                                                                       |

| 24,25<br>26,27<br>38,39<br>40,41 | G1_TXD3,<br>G1_TXD2,<br>G1_TXD1,<br>G1_TXD0,<br>G2_TXD3,<br>G2_TXD2,<br>G2_TXD1,<br>G2_TXD1, | О    | RGMII Transmit Data  When it works in 10BASE-T or 100BASE-TX mode, TXD[3:0] present the transmit data at the rising edge of TXC, and when it works in 1000BASE-T mode, TXD[3:0] present the low nibble of transmit data byte at the rising edge of TXC, and present the high nibble of transmit data byte at the falling edge of TXC. |

| 28<br>42                         | G1_TXCTL,<br>G2_TXCTL                                                                        | 0    | RGMII Transmit Control  A GMII-like signal "TX_EN" is presented on the rising edge of TXC and a GMII-like signal "TX_ER" is derived by logical operation of the value of TXCTL at the falling edge of TXC, with the latched value of TX_EN, per RGMII specification.                                                                  |

| 29<br>43                         | G1_TXC,<br>G2_TXC                                                                            | 0    | RGMII Transmit Clock  It is a 125Mhz clock in 1000BASE-T mode, 25 MHz clock in 100BASE-TX mode, or a 2.5 MHz clock in 10BASE-T mode. IP1001 uses the clock to sample TX_CTL and TXD[3:0].                                                                                                                                             |

| 32,33<br>34,35<br>44,45<br>46,47 | G1_RXD3,<br>G1_RXD2,<br>G1_RXD1,<br>G1_RXD0,<br>G2_RXD3,<br>G2_RXD2,<br>G2_RXD1,<br>G2_RXD0  | I    | RGMII Receive Data  When the PHY works in 10BASE-T or 100BASE-TX mode, RXD[3:0] latch the receive data at the rising edge of RXC, and when it works in 1000BASE-T mode, RXD[3:0] latch the low nibble of receive data byte at the rising edge of RXC, and present the high nibble of transmit data byte at the falling edge of RXC.   |

| 36<br>48                         | G1_RXCTL,<br>G2_RXCTL                                                                        | I    | RGMII Receive Control  A GMII-like signal "RXCTL" is presented on the rising edge of RXC and a GMII-like signal "RX_ER" is derived by logical operation of the value of RXCTL at the falling edge of RXC, with the latched value of RX_DV, per RGMII specification.                                                                   |

| 37<br>49                         | G1_RXC,<br>G2_RXC                                                                            | l    | RGMII Receive Clock.  It is a 125 MHz, 25MHz, or 2.5MHz reference clock from a Gigabit PHY working in 1000BASE-T, 100BASE-TX, or 10BASE-T.                                                                                                                                                                                            |

| •               | on (contine             |             |                                                                                                                                                          |

|-----------------|-------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.         | Label                   | Туре        | Description                                                                                                                                              |

| MII/Reverse     | MII. MII mode           | : this port | acts as a MAC. Reverse MII port: this port acts a PHY.                                                                                                   |

| 91              | MTXEN/MRX<br>DV         | 0           | MII mode(MAC mode): transmit enable Rsverse MII mode(PHY mode): receive data valid.                                                                      |

|                 | MTXD[3:0]/<br>MRXD[3:0] | 0           | MII mode(MAC mode): transmit data Rsverse MII mode(PHY mode): receive data.                                                                              |

| 88              | MRXDV/MTX<br>EN         | I           | MII mode(MAC mode): receive data valid Rsverse MII mode(PHY mode): transmit enable.                                                                      |

| 83,84,85,8<br>6 | MRXD[3:0]/M<br>TXD[3:0] | I           | MII mode(MAC mode): receive data Rsverse MII mode(PHY mode): transmit data                                                                               |

| 90              | MTXCLK                  | I/O         | MII transmit clock. Input for normal (MAC mode) MII. Output for reverse (PHY mode) MII                                                                   |

| 89              | MRXCLK                  | I/O         | MII receive clock. Input for normal (MAC mode) MII. Output for reverse (PHY mode) MII.                                                                   |

| SMI             |                         |             |                                                                                                                                                          |

| 74              | MDC                     | O           | Clock for serial management bus.  It's recommended to connect a 300ohm bead close to the IP1826D and add a 30pf capacitor to ground for noise filtering. |

| 76              | MDIO                    | I/O         | I/O data for serial management bus.  It's recommended to add a 1.5K pull up resistor connecting to VDD and a 30pf capacitor connecting to ground.        |

| EEPROM          |                         |             |                                                                                                                                                          |

| 77              | EE_CLK                  | O, PU       | Serial EEPROM clock output                                                                                                                               |

| 78              | EE_DATA                 | I/O,PU      | Serial EEPROM data                                                                                                                                       |

|                                 | n (continue          |         | <u></u>                                                                                                     |

|---------------------------------|----------------------|---------|-------------------------------------------------------------------------------------------------------------|

| Pin No.                         | Label                | Type    | Description                                                                                                 |

| CPU                             | 1                    | ı       |                                                                                                             |

| 80                              | CPU_CLK              | I, PU   | Serial CPU access clock input.                                                                              |

| 81                              | CPU_DAT              | I/O, PU | Serial CPU data                                                                                             |

| LED                             |                      |         |                                                                                                             |

| 98                              | LED_CLK              | PU      | This pin drives periodical pulse to the serial to parallel latch for the LED display.                       |

| 97                              | LED_DAT              | PU      | This pin drives data pattern to the serial to parallel latch for the LED display.                           |

| Miscellaneous                   | 1                    |         |                                                                                                             |

| 68                              | X1                   | I       | Crystal/ Oscillator 25MHz input. The frequency tolerance is + - 50PPM.                                      |

| 69                              | X2                   | 0       | Crystal output.                                                                                             |

| 70                              | RESETB               | I       | System reset (low active). Should be kept at "low" for at least 10 microseconds.                            |

| 79                              | INTB                 | O, PU   | Interrupt output. Active low. Please refer to register F7h and F8h for more detailed information.           |

| 66                              | REG19                | 0       | 1.9V regulator control.                                                                                     |

|                                 |                      |         | This pin can be connected to the base of the PNP transistor to generate the 1.9V power.                     |

| 67                              | REG25                | 0       | 2.5V regulator control.                                                                                     |

|                                 |                      |         | This pin can be connected to the base of the PNP transistor to generate the 2.5V power.                     |

| 72                              | SCAN_MOD<br>E        | I, PD   | Leave this pin unconnected during normal operation.                                                         |

| 96                              | OSC_OUT              | 0       | A 25Mhz/ 50 Mhz clock output                                                                                |

| Power & Grou                    | nd                   |         |                                                                                                             |

| 22,30,<br>56,82,101,<br>121,144 | VDD19                | Р       | 1.9V power for Core circuit                                                                                 |

| 65                              | VDDPLL               | Р       | 1.9V power for PLL circuit                                                                                  |

| 13,108,122,1<br>39              | VDD19/33             | Р       | 3.3/1.9V power for I/O PAD of SS-SMII port                                                                  |

| 23,31,50                        | VDD19/25             | Р       | 2.5/1.9V power for I/O PAD of RGMII port                                                                    |

| 87                              | VDD19/25/33<br>(CPU) | Р       | 3.3/2.5/1.9V power for I/O PAD of MII port It is recommended to use 2.5 or 1.9V if other VDD power is 1.9V. |

| 57,64                           | VDD33                | Р       | 3.3V power for analog circuit                                                                               |

|                                 | GND                  |         | Exposed PAD (E-PAD (Thermal PAD) is Analog and Digital ground.                                              |

| L.                              | I.                   |         |                                                                                                             |

| Pin No.    | otion (continue             | Type    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|-----------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                             |         | vill be latched upon reset                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 129        | BCST CTRL O                 |         | Enable the broadcast storm control                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 120        | N#                          | 12, 1 0 | 1: Disable (Default); 0: Enable The setting can be updated by writing register 42h~43h.                                                                                                                                                                                                                                                                                                                                                                      |

| 134        | AGING_OFF#                  | IL, PU  | Disable the MAC address table aging function  1: Enable aging (Default); 0: Disable aging The setting can be updated with register 40h[1].                                                                                                                                                                                                                                                                                                                   |

| 142<br>140 | TRUNK0_ON[1] , TRUNK0_ON[0] | IL, PU  | The trunk group 0 setting:  Trunk0_ON[1:0]  00: port 0, 1, 2, 3 trunk-grouped  01: port 0, 1, 2 trunk-grouped  10: port 0, 1, trunk-grouped  11: no trunk (Default)  The setting can be updated with register 4Ch.                                                                                                                                                                                                                                           |

| 132        | TRUNK2_ON#                  | IL, PU  | The trunk group 2 setting: 1: no trunk (Default); 0: port 24 and port 25 trunk-grouped The setting can be updated with register 4Eh.                                                                                                                                                                                                                                                                                                                         |

| 137        | HOME_VLAN_<br>ON#           | IL, PU  | Home VLAN setting enable Port 0 ~ Port23 are all individual VLAN shared with 2 RGMII and MII ports. For example, Port 0, port 24 ~ port 26 form a VLAN group, etc. 1: Disabled (Default); 0: Enabled The setting can be updated with register 80h~B5h.                                                                                                                                                                                                       |

| 1          | IGMP_EN#                    | IL, PU  | IGMP snooping. 1: Disable (Default); 0: Enable The setting can be updated with register C0h[1].                                                                                                                                                                                                                                                                                                                                                              |

| 117        | BPDU_BCST_<br>OFF#          | IL, PU  | Filter the packet with MAC destination address 01-80-c2-00-00-04 ~01-80-c2-00-00-0F  1: Broadcast (Default); 0: Filter  This pin is valid only if pin 20 GIO_DLY_EN# is set to 1.                                                                                                                                                                                                                                                                            |

| 20         | GIO_DLY_EN#                 | IL, PU  | RGMII I/O delay pin setting enable 1: Disable (default); 0: Enable This pin is used to select the modes of pin 3, 127, 18, 119, 117 and 110.                                                                                                                                                                                                                                                                                                                 |

| 10         | MULTI_TO_1#                 | IL, PU  | When set to "0", the switch controller will adjust the queue management to fit the multi-clients to one server application.  1: Disable (default); 0: Enable                                                                                                                                                                                                                                                                                                 |

| 94         | PCS_AUTO_D<br>ETECT_EN      | IL, PD  | Port 25 and 26 TP/ fiber auto switching 1: Enable; 0: Disable (Default)  When the function is turned on, IP1826D enables SERDES or RGMII of port 25(26) depending on the link status of SERDES. If the SERDES link status of port 25(26) is off, IP1826D recognizes port 25(26) as a TP port; otherwise IP1826D recognizes port 25(26) as a fiber port. The details are illustrated in the following table. The setting can be updated with register FFh[7]. |

| 16, 12, 7 | LED_Mode[2]<br>LED_Mode[1]<br>LED_Mode[0] | IL, PU    | Please refer to LED Display Mode.                                                                                                                                                                                                                                                                               |

|-----------|-------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 95        | RVMII_MODE                                | IL,<br>PD | Reverse MII mode<br>1: Reverse MII (IP1826D works as a PHY)<br>0: Normal MII (IP1826D works as a MAC)                                                                                                                                                                                                           |

| 18        | RG_XEN_OFF#<br>/BKP_OFF#                  | IL, PU    | Disable the flow control/back pressure of all ports 1: Turn on (Default); 0: Turn off This pin is valid only if pin 20 GIO_DLY_EN# is set to 1. Can be updated with register D9h[13].                                                                                                                           |

| 3, 127    | TXC_DELAY[1] TXC_DELAY[0]                 | IL, PU    | RGMII TXC output delay added 00: delay 3ns; 01: delay 2ns; 10: delay 1ns; 11: no delay These pins are valid only if pin 20 GIO_DLY_EN# is set to 0. Can be updated with register F9.                                                                                                                            |

| 18        | TXC_REV                                   | IL, PU    | Reverse TXC 0: reverse; 1: normal This pin is valid only if pin 20 GIO_DLY_EN# is set to 0. Can be updated by setting register F9.                                                                                                                                                                              |

| 119, 117  | RXC_DELAY[1]<br>RXC_DELAY[0]              | IL, PU    | RGMII RXC input delay added 00: delay 3ns; 01: delay 2ns; 10: delay 1ns; 11: no delay These pins are valid only if pin 20 GIO_DLY_EN# is set to 0. Can be updated by setting register F9.                                                                                                                       |

| 110       | RXC_REV                                   | IL, PU    | Reverse RXC 0: reverse; 1: normal This pin is valid only if pin 20 GIO_DLY_EN# is set to 0. Can be updated by setting register F9.                                                                                                                                                                              |

| 91        | SS-SMII_Tx_DI<br>y                        | IL, PD    | SS-SMII Tx delay 4ns<br>1:Enable; 0:Disable (Default)                                                                                                                                                                                                                                                           |

| 127       | XEN_THROTTL<br>E_ON#                      | IL, PU    | <ul> <li>Auto turn off the flow control, when the flow control and the priority is enabled.</li> <li>1: Disable auto turn off function (Default)</li> <li>0: Enable auto turn off function</li> <li>This pin is valid only if pin 20 GIO_DLY_EN# is set to 1.</li> </ul>                                        |

| 73        | FIBER_EN_0#                               | IL, PU    | Port 24 RGMII/SERDES selection (force mode) 1: RGMII (Default); 0: SERDES When PCS_AUTO_DETECT_EN is disabled, this pin is used to configure port 24 to be TP or fiber manually. It must be left open to disable force mode, if PCS_AUTO_DETECT_EN is enabled. The setting can be updated with register FFh[5]. |

| 75        | FIBER_EN_1#                               | IL, PU    | Port 25 RGMII/SERDES selection (force mode) 1: RGMII (Default); 0: SERDES When PCS_AUTO_DETECT_EN is disabled, this pin is used to configure port 25 to be TP or fiber manually. It must be left open to disable force mode, if PCS_AUTO_DETECT_EN is enabled. The setting can be updated with register FFh[6]. |

| 71        | SD_EN#                                    | IL, PU    | SD detect mode of port 24 (SD1) and 25 (SD2)  1: Low active (GBIC/ Default); 0: high active The setting can be updated with register FFh[8].                                                                                                                                                                    |

| 92         | P26_FORCE_LI<br>NK#                         | IL, PD | Port 26 (MII) forced link on<br>1: Enable; 0: Disable (Default)<br>The setting can be updated with register D9h[13].                                                                                                                                                               |

|------------|---------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 115        | IPG_COMP_EN<br>#                            | IL, PU | Transmit IPG compensation (+80ppm).  1: Disable (Default); 0: Enable The setting can be updated with register 01h[0].                                                                                                                                                              |

| 125<br>123 | PORT_PRI_ON [1], PORT_PRI_ON [0]            | IL, PU | Enable port base high priority function 11: Disabled (default) 10: Set port 0~3 as high priority port 01: Set port 24, 25 (RGMII port) as high priority port 00: Set port 26 (CPU port) as high priority port The setting can be updated with register 22h~23h.                    |

| 119        | TAG_PRI_ON#                                 | IL, PU | Enable 802.1Q TAG priority function of all ports  1: Disable (Default); 0: Enable This pin is valid only if pin 20 GIO_DLY_EN# is set to 1. The setting can be updated with register 24h~25h.                                                                                      |

| 110        | IP_PRI_ON#                                  | IL, PU | Enable IP TOS/DS priority function of all ports  1: Disable (Default); 0: Enable This pin is valid only if pin 20 GIO_DLY_EN# is set to 1. The setting can be updated with register 26h~27h.                                                                                       |

| 5<br>3     | WRR_RATIO_<br>ON[1],<br>WRR_RATIO_<br>ON[0] | IL, PU | The high priority to low priority ratio of the packet number for the weighted round robin mode.  11: First in first out (Default)  10: 2 to 1; 01: 4 to 1; 00: 8 to 1  These pins are valid only if pin 20 GIO_DLY_EN# is set to 1.  The setting can be updated with register 3Dh. |

| 104<br>102 | DRIVE[1],<br>DRIVE[0]                       | IL, PU | Driving current selection for 3SMII and MII, port 0~23 and port 26 00: 2 mA; 01: 12 mA; 10: 8 mA; 11: 4 mA (Default) The setting can be updated with register FAh[9:8].                                                                                                            |

| 112<br>106 | G_DRIVE[1],<br>G_DRIVE[0]                   | IL, PU | Driving current selection for RGMII, port 24~25<br>00: 4 mA; 01: 2 mA; 10: 12 mA; 11: 8 mA (Default)<br>The setting can be updated with register F9h[13:12].                                                                                                                       |

| 99         | SLEW_F#                                     | IL, PU | Output pad slew rate setting for RGMII, SS-SMII and MII.  1: Normal (Default); 0: Fast The setting can be updated with register FAh[14].                                                                                                                                           |

| 93         | SS-SMII_Rx_DI<br>y                          | IL, PD | SS-SMII Rx delay 4ns<br>1:Enable; 0:Disable (Default)                                                                                                                                                                                                                              |

| 79         | OSC_SEL                                     | IL, PU | OSC Clock selection of pin OSC_OUT.<br>1:25MHz; 0:50MHz                                                                                                                                                                                                                            |

Gigabit Port COMBO Configuration

| Note: X means<br>"don't care" | SDx<br>voltage | PCS_AUTO_<br>DETECT EN | FIBER_EN_x# | SD_EN# | Active I/F                                            | TP/FX Auto<br>Change |

|-------------------------------|----------------|------------------------|-------------|--------|-------------------------------------------------------|----------------------|

| Fiber port                    | voitage        | DETECT_EN              |             |        |                                                       | Change               |

| Link on                       | 0v             | 1                      | NC          | 1      | SERDES<br>(Min GBIC/ GBIC)                            | Yes                  |

| Link off                      | 3.3v           | 1                      | NC          | 1      | RGMII<br>(TP is active if fiber port is<br>link off.) | Yes                  |

| Link on                       | 3.3v           | 1                      | NC          | 0      | SERDES<br>1X9 or 2x5(SFF)                             | Yes                  |

| Link off                      | 0v             | 1                      | NC          | 0      | RGMII<br>(TP is active if fiber port is<br>link off.) | Yes                  |

| Link on                       | 0v             | 0                      | 0           | 1      | SERDES                                                | No                   |

| Link off                      | 3.3v           | 0                      | 0           | 1      | (Min GBIC/ GBIC)                                      | No                   |

| Link on                       | 3.3v           | 0                      | 0           | 0      | SERDES                                                | No                   |

| Link off                      | 0v             | 0                      | 0           | 0      | 1X9 or 2x5(SFF)                                       | No                   |

| Х                             | Χ              | 0                      | 1           | Х      | RGMII                                                 | No                   |

| Pin No.             | Label | Туре | Description                                                                                                                         |  |

|---------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| Gigabit SerDes port |       |      |                                                                                                                                     |  |

| 51                  | FTXM0 | 0    | SERDES TXM. There is an internal 100 ohms resistor between FTXM0 and FTXP0.                                                         |  |

| 52                  | FTXP0 | 0    | SERDES TXP                                                                                                                          |  |

| 53                  | SD0   | I    | Signal detect The input threshold voltage is around 1.6v. It is recommended to use a fiber MAU, which supports TTL level SD signal. |  |

| 54                  | FRXP0 | I    | SERDES RXP. There is an internal 100 ohms resistor between FRXM0 and FRXP0.                                                         |  |

| 55                  | FRXM0 | I    | SERDES RXM                                                                                                                          |  |

| 58                  | IBREF |      | This pin must be connected to analog ground through a 6.19k resister.                                                               |  |

| 59                  | FTXM1 | 0    | SERDES TXM. There is an internal 100 ohms resistor between FTXM1 and FTXP1.                                                         |  |

| 60                  | FTXP1 | 0    | SERDES TXP                                                                                                                          |  |

| 61                  | SD1   | I    | Signal detect The input threshold voltage is around 1.6v. It is recommended to use a fiber MAU, which supports TTL level SD signal. |  |

| 62                  | FRXP1 | I    | SERDES RXP. There is an internal 100 ohms resistor between FRXM1 and FRXP1.                                                         |  |

| 63                  | FRXM1 | I    | SERDES RXM                                                                                                                          |  |

### Note:

- 1. All the trapped pins are latched upon reset and are pulled down or pulled up by a 50K resistor inside the chip.

- 2. The designer can connect a 4.7K ohms resistor to set these pins to "1" or "0" to change the default state.

- 3. The content of an EEPROM will override the pin setting.

# 4 Functional Description

### 4.1 Switch Engine and Queue Management

### 4.1.1 Packet forwarding

IP1826D utilizes the "store & forward" method to handle packet transfer. IP1826D begins to forward a packet to a destination port after the entire packet is received. A received packet will be forwarded to the destination port only if it is error free; otherwise, it will be discarded.

### 4.1.1.1 Address learning and hashing

| Related registers | 40[1:0], 44h~46h |

|-------------------|------------------|

|                   |                  |

IP1826D can handle up to 4096 MAC address entries. And it provides two kinds of hash method to maintain the MAC address table; one is the direct mapping and the other is the CRC algorithm. When the direct mapping method is selected, register 40h[0] set to "1", IP1826D recognizes the least significant 12 bits of the MAC address. When the CRC algorithm is used, register 40h[0] set to "0", IP1826D uses 48-bit MAC address to hash.

The address learning function for each port can be either enabled or disabled by setting the corresponding bit in registers 45h and 46h.

Packets with the following conditions will not be stored in MAC address table.

- Erroneous packet

- 802.3x pause packet

- 802.1D Reserved Group packet

- Multicast source MAC address

### 4.1.1.2 Aging

### Address aging

| Related registers | 40h[1], 44h[9:0] |

|-------------------|------------------|

|-------------------|------------------|

IP1826D supports programmable aging time to meet various system requirement, ranging from 55.3 sec to  $56627 \text{sec} \pm 3.8\%$ . The designer can program aging time by writing register 44h[9:0]. The address aging function can be disabled by programming register 40h[1].

### Packet aging

| Related registers | 3Dh[15], 3Dh[13:8] |

|-------------------|--------------------|

IP1826D supports packet aging (out queue aging). If a packet stays in IP1826D longer than out queue aging time defined in register 3Dh[13:8], IP1826D will drop the packet to improve the efficiency of packet buffer. The packet aging function can be enabled by programming register 3Dh[15].

### 4.1.1.3 802.1D packet forwarding

| Related registers | 01h[1], 02h[1] |

|-------------------|----------------|

|                   |                |

Besides the erroneous packet and the IEEE802.3x pause packet, 802.1D Reserved Group packet with MAC address from 01-80-c2-00-00-04 to 01-80-c2-00-00-0F can be optionally dropped by setting register 01h[1]. A packet with MAC address equal 01-80-c2-00-00-00 can be forwarded to CPU or be dropped according to the setting in register 02h[1]. A packet with MAC address equal 01-80-c2-00-00-03 can be forwarded to CPU or be dropped according to the setting in register 02h[2].

### 4.1.1.4 Inter frame gap compensation

| Related registers | 01h[0] |

|-------------------|--------|

| Ü                 |        |

IP1826D supports an option to transmit a packet with IPG changed from 96 bits to 88 bits after a period of transmission to compensate the data accumulation due to TX clock frequency difference between local machine and link partner. This function can be turned on by writing "1" to register 01h[0].

#### 4.1.2 Flow Control

IP1826D supports two kinds of flow control mechanisms, backpressure for half duplex operation and IEEE 802.3x for full duplex operation.

#### 4.1.2.1 IEEE802.3x

| Related registers   | D2h~D3h, D4h~D5h |

|---------------------|------------------|

| i tolatoa rogiotolo | B2 B0, B B0      |

When operating in full duplex mode, IP1826D supports IEEE802.3x flow control, both symmetric pause and asymmetric pause function. Each port's flow control function can be enabled individually by programming register D2h~D5h. When the packets in buffer reach the threshold, IP1826D generates a "Xoff" pause packet immediately or right after the current packet has been transmitted. When receiving a pause packet, the link partner stops transmission for a period of time defined in the pause packet. This prevents the buffer of IP1826D from overrun. When the packets in buffer lower than threshold, IP1826D generates a "Xon" pause packet to notify the link partner the receive buffer is available.

### 4.1.2.2 Backpressure

| Related registers | D6h~D7h, 01h[2], 01h[3] |

|-------------------|-------------------------|

When operating in half duplex mode, the IP1826D supports backpressure flow control. Each port's backpressure function can be enabled individually by programming register D6h~D7h. When the packets in buffer reach the threshold, IP1826D generates a jam pattern to back off the link partner. IP1826D supports the collision based and carrier-based backpressure. When the collision based backpressure is enabled, register 01h[2] set to "0", IP1826D generates a jam pattern only when the link partner is transmitting data and the receive buffer in IP1826D is not available. When detecting a collision on line, the link partner stops transmission until a back off time expires. When the carrier based backpressure is enabled, register 01h[2] set to "1", IP1826D transmits null packets continuously to prevent link partner's transmission when the buffer is not available.

To prevent the packet loss due to excessive collision caused by backpressure mechanism, designer can clear bit 3 of register 01h to disable the drop function due to 16 consecutive collisions defined in IEEE802.3.

### 4.1.2.3 Flow control off for high priority packet

| Related registers | 01h[6] |

|-------------------|--------|

|                   |        |

To prevent the flow control function from blocking the high priority traffic, each port of IP1826D can turn off flow control function for a period of time automatically when receiving a high priority packet. This function can be enabled by writing register 01h[6].

### 4.1.3 Bandwidth Control (Egress/Ingress rate control)

| Related registers | 03h~1Dh, 01h[5] |

|-------------------|-----------------|

IP1826D implements a sophisticated data rate control mechanism, which is very useful for the bandwidth-limited network. By controlling both the ingress and the egress data rate, IP1826D provides a variety of bandwidth configurations. It limits the maximum byte counts, by which a port can send or receive in a period of time. If the transmit byte counts or receive byte counts of a port reaches a pre-defined threshold, it will stop transmitting or receiving data.

Each port's egress/ingress data rate can be programmed individually. The maximum rate of port0~port 23 are defined in register 03h~1Ah. The maximum rate of port 24, port 25 and port 26 are defined in register 1Bh~1Dh. The high byte of the registers defines the receive rate and low byte defines transmission rate. Register 01h[5] defines the high /low throttle value using in bandwidth control function. It is noted that once the rate is set, it is independent of the status of link speed and flow control. The detailed configuration is shown in the following table.

Maximum output rate (transmit rate)

| vi <u>axiiilulii oul</u> | out rate (transmit rate) |              |                         |

|--------------------------|--------------------------|--------------|-------------------------|

|                          | Port 0~23                | Port 26      | Port 24, 25             |

|                          | Register 03h~1Ah         | Register 1Dh | Register 1Bh~1Ch        |

| Link speed               | 10/100 Mbps              |              | 10/100/1000 Mbps        |

| 01h[5]=0                 | Bit [7:0] * 4K Byte/s    |              | Bit [7:0] * 4K Byte/s.  |

| 01h[5]=1                 | Bit [7:0] * 32K Byte/s   |              | Bit [7:0] * 256K Byte/s |

Maximum input rate (receive rate)

|            | Port 0~23               | Port 26      | Port 24, 25              |

|------------|-------------------------|--------------|--------------------------|

|            | Register 03h~1Ah        | Register 1Dh | Register 1Bh~1Ch         |

| Link speed | 10/100 Mbps             |              | 10/100/1000 Mbps         |

| 01h[5]=0   | Bit [15:8] * 4K Byte/s  |              | Bit [15:8] * 4K Byte/s   |

| 01h[5]=1   | Bit [15:8] * 32K Byte/s |              | Bit [15:8] * 256K Byte/s |

**Note:** The 0x00 rate value denotes the maximum speed.

#### 4.1.4 Broadcast Storm Control

| Related registers | 42h~43h, 44h[15:10] |

|-------------------|---------------------|

To prevent the broadcast storm, the IP1826D implement a broadcast storm control mechanism. When this function is enabled, a port begins to drop the incoming broadcast packets if the received broadcast packet

counts reach the threshold defined in register 44h[15:10]. Each port's broadcast storm protection function can be enabled individually by programming register 42h~43h.

### 4.1.5 Block broadcast packet flooding to CPU port

| Related registers | 40h[4], F2h[0] |

|-------------------|----------------|

IP1826D supports an option to block broadcast packets flooding to CPU port. To enable the function, designer has to assign port 26 as a CPU port by programming register F2h[0], and then turn on the function by programming register 40h[4].

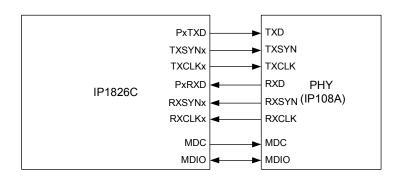

### 4.1.6 SS-SMII, RGMII and MII/Reverse MII

### 4.1.6.1 SS-SMII

| Related registers | FAh |

|-------------------|-----|

|-------------------|-----|

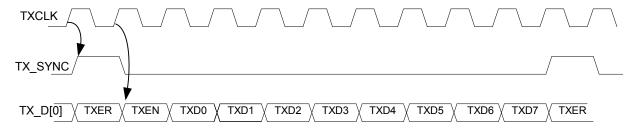

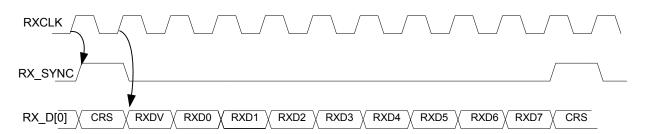

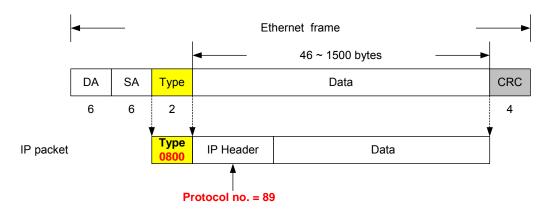

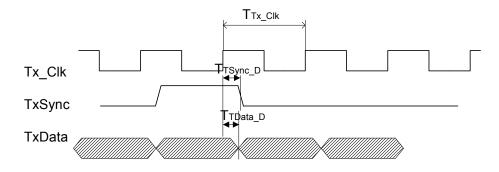

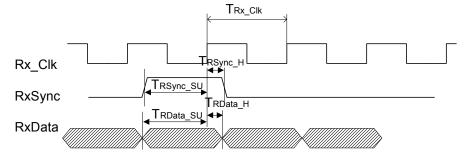

IP1826D sends out data on TX\_D at the rising edge of TXCLK and uses TX\_SYNC to indicate the start of a 10-bit frame. By recognizing the high pulse of the TX\_SYNC, a PHY can capture the correct data stream. A PHY sends out data on RX\_D at the rising edge of RXCLK and uses RX\_SYNC to indicate the start of a 10-bit frame. By recognizing the high pulse of the RX\_SYNC, IP1826D samples the correct data at the rising edge of RXCLK.

Accompanied by the high pulse of TX\_SYNC, the TXEN, TX\_ER and 8-bit TX data are present on the TX\_D pin. For the RX part of SS-SMII, the CRS, RXDV, and 8-bit RX data are present on the RX\_D pin.

To fit the timing requirement, the delay on TXCLK and RXCLK can be adjusted by programming register FAh. The driving current can be adjusted by pin DRIVR[1:0] and register FAh.

Transmit SS-SMII

Receive SS-SMII

SS-SMII

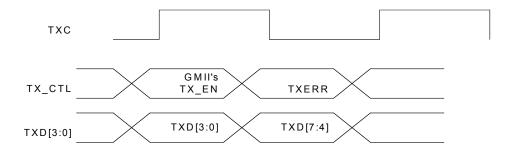

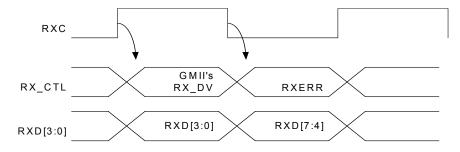

#### 4.1.6.2 RGMII

| Related registers | F9h |

|-------------------|-----|

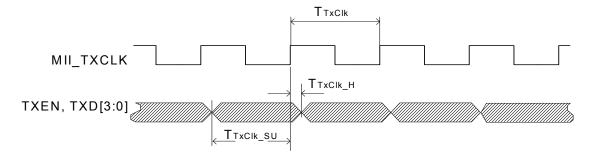

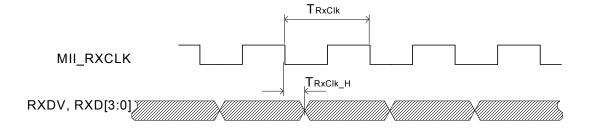

IP1826D sends out data TXD[3:0] and control signal TX\_CTL at the rising and falling edge of TXC. Two GMII like signals TX\_EN and TXERR are embedded in the TX\_CTL. GMII like information TXD[7:0] is embedded in the TXD[3:0]. By recognizing the decoded TX\_EN, TXD[7:0] and TXERR, a PHY can capture the correct data stream.

A PHY sends out data RXD[3:0] and control signal RX\_CTL at the rising and falling edge of RXC. Two GMII like signals RX\_DV and RXERR are embedded in the RX\_CTL. GMII like information RXD[7:0] is embedded in the RXD[3:0]. By recognizing the decoded RX\_DV, RXD[7:0] and RXERR, IP1826D can capture the correct data stream. IP1826D samples the correct data at the rising edge of RXCLK.

To fit the timing requirement, the delay on TXC and RXC can be adjusted by programming register F9h. The driving current can be adjusted by pin G\_DRIVR[1:0] and register F9h.

#### RGMII

TXERR = GMII'S TX\_EN (XOR) GMII'S TX\_ER

RXERR = GMII'S RX\_DV (XOR) GMII'S RX\_ER

**RGMII**

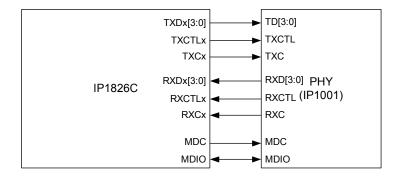

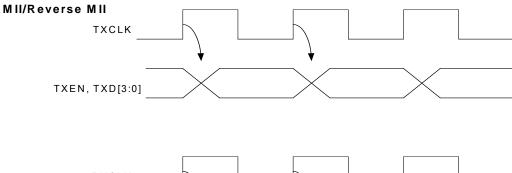

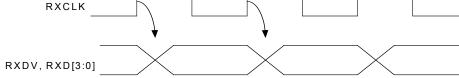

### 4.1.6.3 MII/Reverse MII

| Related registers | FAh[7:6] |

|-------------------|----------|

When set to reverse MII mode(PHY mode), IP1826D sends out data RXDV and RXD[3:0] at the rising and falling edge of RXCLK. By recognizing the RXDV and RXD[3:0], an external CPU can capture the correct data stream.

An external CPU sends out data through TXD[3:0] and control signal TXEN at the rising edge of TXCLK. By recognizing the TXEN, TXD[7:0], IP1826D can capture the correct data stream. IP1826D samples the correct data at the rising edge of TXCLK.

Both TXCLK and RXCLK are sent out by IP1826D. To fit the timing requirement, the delay on TXCLK and RXCLK can be adjusted by programming register FAh[6:7].

**Note:** If the designer set IP1826D to MII mode(MAC mode), the pin function will be swapped between Tx part and Rx part. Please refer to the pin description.

IP1826C acts as PHY

### 4.1.7 CPU interface

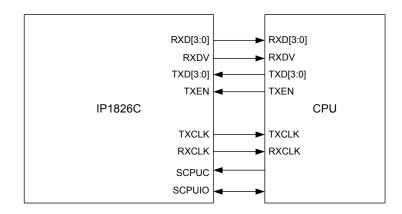

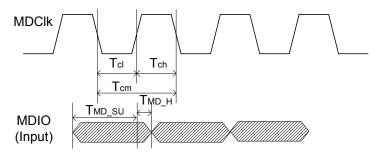

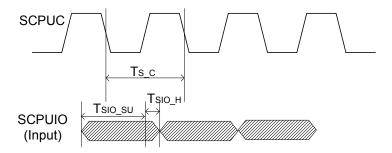

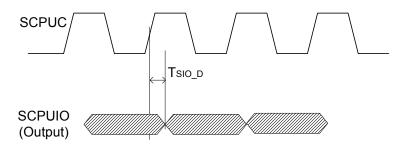

There is no need to program the register of the IP1826D for the generic application. However it's probably necessary to program the internal register to fit some special applications. The interface between the IP1826D and the CPU is a serial bus, which comprises a clock and an I/O signal. Like the access cycle of the serial management interface, the serial interface comprises the switch ID, the read/write command, the address and the data. The access cycle is depicted as below.

The access cycle is much like the access cycle of MDC, MDIO. Care should be taken that the switch ID is 2-bit wide rather than 5-bit wide.

### 4.1.8 Configure the port properties

| Related registers | CBh~D7h, DEh~E7h |

|-------------------|------------------|

|-------------------|------------------|

The designer can configure the property of each port through CPU Interface. The property of each port can be configured individually. The designer can set the auto-negotiation, speed, duplex, pause, and backpressure function by writing register CBh~D7h. Besides updating the property of IP1826D, it also updates the property of the corresponding PHY through SMI.

The designer can get the status of a port by reading register DEh~E7h. The registers provide the status of Asyn pause function, syn pause function, duplex, speed and link of each port.

#### 4.1.9 Force link

IP1826D supports force link function for port 24~ 26. Port 24~ 26 can be configured individually by programming D9h[13:11]. This function is useful when IP1826D is connected to a PHY, which doesn't support SMI. In this case, IP1826D can't get the link status and will not forward/receive a packet through this port. Force link function will keep this port active regardless of the link status.

### 4.1.10 Read / write address table (LUT)

| Related registers | C5h~C8h |

|-------------------|---------|

|-------------------|---------|

Designer can access IP1826D's MAC address table, ranging from 0 to 4095. To write an entry to the MAC address table, designer has to fill the 46-bit data to register C6h~C8h and then specify the address of the entry and issues a write command by programming register C5h. To read an entry from MAC address table, designer has to specify the address of the entry and issues a read command by programming register C5h. The entry can be read from register C6h~C8h. It is note that the bit 14 and 15 of register C8h is invalid, because of entry is 46-bit wide.

Because IP1826D builds and accesses the MAC address table with the address derived with hashing algorithm, designer has to calculate the address of an entry in the same way before accessing the table. That is, if direct hashing is selected, the address of an entry is the 12 LSB of a MAC address. If CRC hashing is selected, the address of an entry is the 12 LSB of CRC calculation result of a MAC address.

### 4.1.11 Read / write PHY registers

| Related registers | DAh~DBh |

|-------------------|---------|

The designer can access the register of a PHY connected to IP1826D through CPU I/F. To read a register of PHY, the designer has to specify the address of the PHY, address of the MII register, read command by programming register DAh. The content of the register can be read from register DBh. To write a register of PHY, designer has to specify the address of the PHY, address of the MII register, write command, and written data by programming register DAh~DBh.

The associated PHY addresses from port 0 to port 23 are 8~31. The PHY addresses of port 24, port 25 and port 26 are programmable and they are defined in register DCh (PHY address: 0~7).

### 4.1.12 Read / write EEPROM

| Related registers | FBh~FCh |

|-------------------|---------|

|-------------------|---------|

The designer can access the EEPROM through CPU I/F. To read one byte from EEPROM, the designer has to specify the byte address, device address, read command by programming register FBh. The data can be read from register FCh. To write one byte to EEPROM through CPU I/F, designer has to specify the byte address, device address, write command and written data by programming register FBh~FCh.

IP1826D-DS-R03.1

### 4.1.13 EEPROM interface

IP1826D supports EEPROM I/F to access 24C04/08/16. After detecting the rising edge of reset input, the IP1826D will start to read the content of EEPROM (acting like an EEPROM master). Being an EEPROM master, the IP1826D downloads the content of EEPROM only if the first two bytes in EEPROM are "1826h".

The mapping relationship between the IP1826D registers and the EEPROM address are depicted as the following table.

| EEPROM address | EEPROM content | IP1826D's Register |

|----------------|----------------|--------------------|

| 00h            | 18h            | XX                 |

| 01h            | 26h            | XX                 |

| 02h            | Expected value | 01h[15:8]          |

| 03h            | Expected value | 01h[7:0]           |

| 04h            | Expected value | 02h[15:8]          |

| 05h            | Expected value | 02h[7:0]           |

| •••••          | •••••          | •••••              |

| •••••          | •••••          | •••••              |

| 1FEh           | Expected value | FFh[15:8]          |

| 1FFh           | Expected value | FFh[7:0]           |

#### Note:

- 1. The EEPROM ID should be set to "3'b000"; i.e. A2=0; A1=0; A0=0

- 2. IP1826D downloads the content of the EEPROM ranging from address 00h to 1F1h; i.e. the register beyond this range is not recognized by IP1826D.

- 3. The ID for IP1826D recognition should be set at address 00h and address 01h as shown in the table.

### 4.1.14 Statistic counters

Related registers 01[10:9], 38h~3Ah, 3Bh~3Ch

IP1826D provides 54 statistic counters, two counters for one port. These counters are enabled if register 01h[10] is set to 1. The designer can select the function of counters to be RX packet count, TX packet count, collision count, or CRC error count by programming register 01h[9] and register 3Bh~3Ch. Each bit of register 3Bh~3Ch is corresponding to one port individually as shown in the following table.

|                              | The function of counters of a port |                         |

|------------------------------|------------------------------------|-------------------------|

| 01h[9], one bit of 3Bh ~ 3Ch | Counter 2                          | Counter 1               |

| 0,0                          | Receive packet count               | Transmit packet count   |

| 0,1                          | Transmit packet count              | Collision count         |

| 1,0                          | Receive packet count               | Drop packet count (MAC) |

| 1,1                          | Receive packet count               | CRC error packet count  |

To read the content of a counter, designer has to specify the address of counter in register 38h[5:0] and issue read command by setting register 38h[8]. Then, designer reads the content of the counter by reading register 39h and 3Ah. The address of counter of each port is shown in the following table.

| Address of counter (38h[5:0]) | Location of counter |

|-------------------------------|---------------------|

| 0                             | Port 0 counter 1    |

| 1                             | Port 0 counter 2    |

| 2                             | Port 1 counter 1    |

| 3                             | Port 1 counter 2    |

|                               |                     |

|                               |                     |

| 46                            | Port 23 counter 1   |

| 47                            | Port 23 counter 2   |

| 48                            | Port 26 counter 1   |

| 49                            | Port 26 counter 2   |

| 50                            | Port 24 counter 1   |

| 51                            | Port 24 counter 2   |

| 52                            | Port 25 counter 1   |

| 53                            | Port 25 counter 2   |

### 4.1.15 Interrupt

| Related registers | F7h~F8h |

|-------------------|---------|

IP1826D provides one interrupt pin to indicate status change. When one of the following conditions happen, IP1826D will asserts the interrupt pins if the function is enabled.

- 1. A CPU R/W SMI command is completed

- 2. A CPU R/W EEPROM command is completed

- 3. Link status changes on PHY of any port

- 4. Auto-negotiation next page received on port 25 and 26 in fiber mode.

- 5. TP/fiber mode change on port 25 and 26.

An interrupt function can be enabled by programming the corresponding bit of register F7h, the interrupt mask register. The designer can read register F8h to identify the interrupt source. The polarity of interrupt pin can be configured by writing register F7h[15].

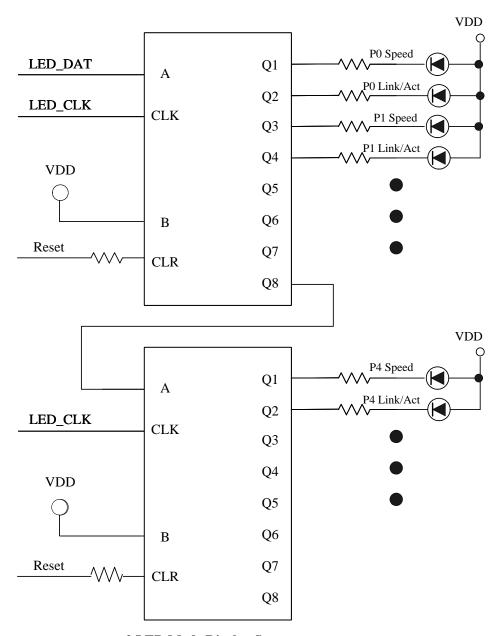

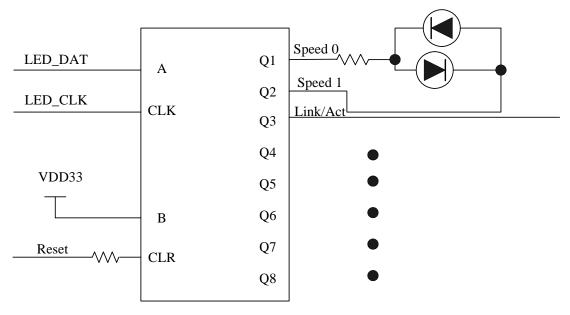

### 4.1.16 LED Display Mode

|                   | <u> </u> |

|-------------------|----------|

| Related registers | DDh      |

The bit stream is output sequentially through LED\_DAT and LED\_CLK and its sequence starts from port 25 to port 0,. In the other word, Port 0 LED status is present on the latest LED bit, as shown in the table. To store the serial LED stream, a serial-to-parallel shift register should be used.

There are 2 dsiplay groups can be configured for LED display.

### ☐ LED Dispaly Mode –Group 1

If register DDh[9] is set to "0", the slow blinking display mode will be present on those port running in half duplex mode or 10Mbps link speed. See the following tabled for the details.

**Display Sequence**

|                   | Register DDh[9]=0   |                                                                                                   |  |

|-------------------|---------------------|---------------------------------------------------------------------------------------------------|--|

| Pin Setting       | Register            | LED Display Sequence.                                                                             |  |

| LED_Mode<br>[2:0] | Setting<br>DDh[2:0] | (1), (2) indicate the bit stream sequence shifted from LED_DAT.                                   |  |

| 111               | 000                 | (1) P25 Link/Act/Dupx; (2) P25 Speed,(Last one) P0 Speed.                                         |  |

| 110               | 001                 | (1) P25 Dupx/Col; (2) P25 Link/Act; (3) P25 Speed;(Last one) P0 Speed                             |  |

| 101               | 010                 | (1) P25 Link/Act; (2) P25 Speed 1; (3) P25 Speed 0;(Last one) P0 Speed 0                          |  |

| 100               | 011                 | Reserved.                                                                                         |  |

| 011               | 100                 | (1) P25 Flow Ctrl; (2) P25 Link/Act/Dupx; (3) P25 Speed 1; (4) P25 Speed 0; (Last one) P0 Speed 0 |  |

| 010               | 101                 | (1) P25 Dupx/Col; (2) P25 Link/Act; (3) P25 Speed1; (4) P25 Speed0;(Last one) P0 Speed0           |  |

| 001 | 110 | (1) P25 Flow Ctrl; (2) P25 Dupx/Col; (3) P25 Link/Act; (4) P25                          |

|-----|-----|-----------------------------------------------------------------------------------------|

|     |     | Speed;(Last one) P0 Speed                                                               |

| 000 | 111 | (1) P25 Tx; (2) P25 Rx; (3) P25 Link/Act; (4) Speed;(Last one)Speed;(Last one) P0 Speed |

### LED Display Behaviour: Register DDh[9]=0

LED mode selection. There are 4 LED display states, as shown below.

●: Light. O: Inactive. ★: Blinking slowly @ 4S cycle. ★:Blinking fast @98 mS cycle.

LED Mode: Pin Setting= 111 or DDh[2:0]=000. (2 LEDs)

| LED Name         | LED Function                                                                                                                                                                                                                   |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|