#### 2EP100R, 2EP101R, 2EP110R, 2EP130R

#### Features

- Open loop full-bridge transformer driver for designing isolated gate driver supplies for a wide variety of switch technologies (IGBTs, SiC MOSFETs, GaN HEMTs, and others)

- Wide input supply range: from 4.5 V to 20 V

- Supports up to 5 W output power supplies

- Wide frequency range: from 50 kHz to 695 kHz with an internal oscillator or external clock

- Highly accurate duty-cycle adjustment: from 10% to 50%

- Adjustable overcurrent threshold

- · Short circuit protection for power outputs

- Overtemperature protection

- Ready output to indicate normal operation

- Small, space-saving package

#### **Potential applications**

- Industrial motor drives compact, standard, premium, servo drives

- Solar inverters

- UPS and energy storage systems

- Welding

- Commercial air-conditioning

- High-voltage DC-DC converters and DC-AC inverters

- · Isolated switch-mode power supplies

- Power meters

#### **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

#### Description

The 2EP1xxR is a full-bridge transformer driver family providing up to 13 W at its outputs for an open-loop isolated supply. It is optimized to supply gate drivers for a variety of switches such as TRENCHSTOP<sup>™</sup> IGBTs, OptiMOS<sup>™</sup> MOSFETs, CoolMOS<sup>™</sup> superjunction MOSFETs, CoolGaN<sup>™</sup> high electron mobility transistors, and CoolSiC<sup>™</sup> MOSFETs together with EiceDRIVER<sup>™</sup> gate driver ICs, and other similar products.

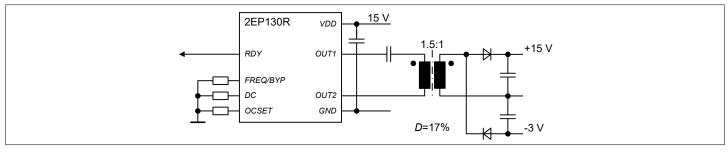

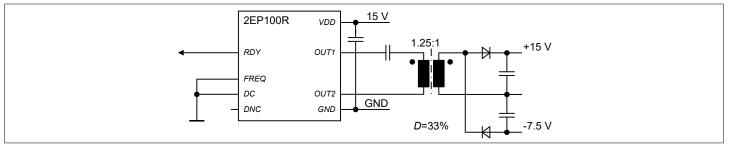

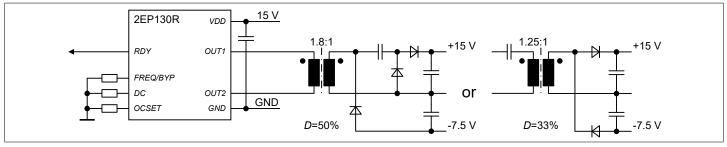

#### Schematic example for 2EP130R

The 2EP1xxR family offers the following product variants:

- 2EP100R and 2EP101R are optimized for low-component count designs for IGBT and SiC MOSFET gate driver supplies

- 2EP110R allows a fine duty-cycle adjustment to adapt the output voltage ratio to the application requirements of SiC and GaN power switches

- 2EP130R is optimized for highly flexible designs to adapt to different application requirements. It provides:

- 5-step overcurrent protection

- 41 selectable switching frequencies or synchronization to external PWM for transformer adaptation

- 41 selectable duty-cycle options to adjust the output supply voltage

- All 2EP1xxR family variants provide several safety functions to secure safe device operation, such as:

- UVLO monitoring

- Overtemperature protection

- Short circuit protection for the outputs

- Average overcurrent protection

- Soft start

- Ready output

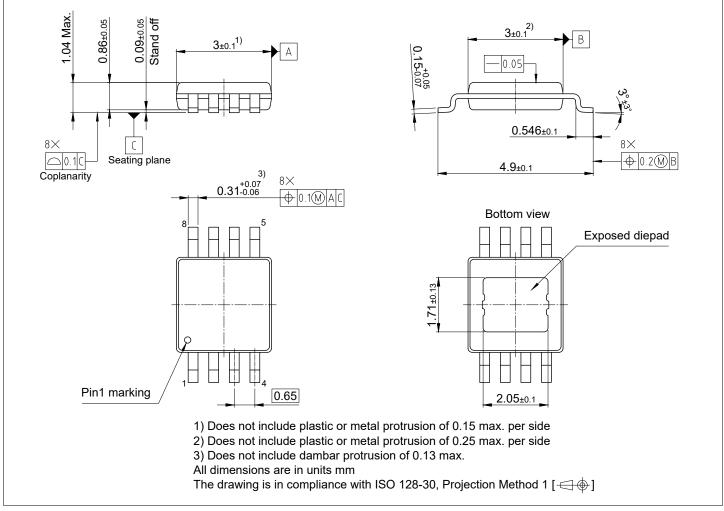

The 2EP1xxR family is available in the thermally enhanced package, PG-TSSOP-8-1, with a fine pitch of 0.65 mm.

| Part number | Function        |            | Adjustment          | Marking                                  |        |

|-------------|-----------------|------------|---------------------|------------------------------------------|--------|

|             | Frequency       | Duty cycle | Overcurrent setting | method                                   |        |

| 2EP100R     | 65 kHz, 103 kHz | 33%, 50%   | OCSET,4             | Pin strapping                            | 2EP100 |

| 2EP101R     | 50 kHz, 65 kHz  | 12%, 17%   | OCSET,4             | Pin strapping                            | 2EP101 |

| 2EP110R     | 50 kHz, 65 kHz  | 10%50%     | OCSET,4             | Pin strapping and resistor ( <i>DC</i> ) | 2EP110 |

| 2EP130R     | 50 kHz 695 kHz  | 10%50%     | OCSET,1 5           | Resistor                                 | 2EP130 |

nfineon

Table of contents

## Table of contents

|         | Table of contents                                                     | 3  |

|---------|-----------------------------------------------------------------------|----|

| 1       | Block diagram                                                         | 6  |

| 2       | Pin configuration and functionality                                   | 6  |

| 2.1     | Pin configuration for 2EP100R, 2EP101R, and 2EP110R                   | 6  |

| 2.2     | Pin configuration for 2EP130R                                         | 7  |

| 3       | Functional description                                                | 7  |

| 3.1     | Output stage                                                          | 8  |

| 3.2     | Monitoring and protection                                             | 8  |

| 3.2.1   | Average overcurrent protection                                        | 8  |

| 3.2.1.1 | Fixed average overcurrent protection in 2EP100R, 2EP101R, and 2EP110R | 9  |

| 3.2.1.2 | Adjustable average overcurrent protection in 2EP130R                  | 0  |

| 3.2.2   | Short circuit protection                                              | 1  |

| 3.2.3   | Overtemperature protection 1                                          | 1  |

| 3.2.4   | Out-of-range detection for external resistors in 2EP110R and 2EP130R  | .1 |

| 3.2.5   | Adjustable resistor's filtering capacitor range1                      | 1  |

| 3.2.6   | Ready output – <i>RDY</i>                                             | 2  |

| 3.3     | Frequency setting                                                     | 2  |

| 3.3.1   | Frequency setting by pin strapping in 2EP100R, 2EP101R, and 2EP110R   | 3  |

| 3.3.2   | Frequency setting by resistor configuration in 2EP130R 1              | 3  |

| 3.4     | Duty-cycle setting                                                    | 3  |

| 3.4.1   | Duty-cycle setting by pin strapping in 2EP100R and 2EP101R            | 4  |

| 3.4.2   | Duty-cycle setting by resistor configuration in 2EP110R and 2EP130R   | 4  |

| 3.5     | Frequency and duty-cycle setting in bypass mode in 2EP130R            | 4  |

| 3.5.1   | Start-up in bypass mode                                               | 4  |

| 3.5.2   | Entering operation in bypass mode1                                    | 6  |

| 3.5.3   | Stopping operation in bypass mode1                                    | 6  |

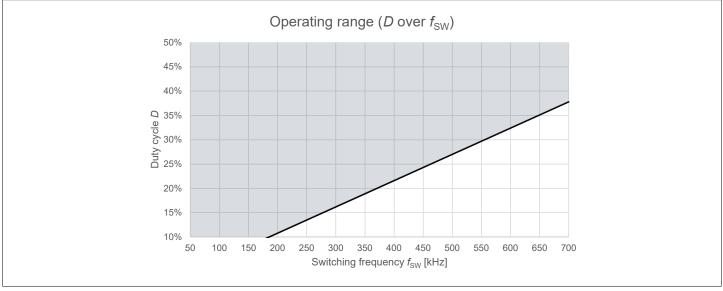

| 3.6     | Useful operating range of duty cycle and switching frequency          | 6  |

| 3.7     | Resistor adjustment table for 2EP110R and 2EP130R 1                   | 7  |

| 3.8     | Description of operating states1                                      | 7  |

| 3.8.1   | Off state                                                             | 8  |

| 3.8.2   | Read configuration state                                              | 8  |

| 3.8.3   | Synchronisation state (bypass mode only)1                             | 8  |

| 3.8.4   | Self-test state                                                       | .8 |

| 3.8.5   | Pre-charge state                                                      | 9  |

| 3.8.6   | Soft start state                                                      | 9  |

| 3.8.7   | Run state                                                             | 9  |

| 3.8.8   | Fault state                                                           | 9  |

| 3.8.9   | Wait state                                                            | 9  |

# infineon

## EiceDRIVER<sup>™</sup> Power 2EP1xxR family datasheet Full-bridge transformer driver for IGBT and SiC MOSFET gate driver supply

#### Table of contents

| 4       | Electrical characteristics and parameters                        |

|---------|------------------------------------------------------------------|

| 4.1     | Absolute maximum ratings                                         |

| 4.2     | Thermal characteristics    21                                    |

| 4.3     | Operating parameters                                             |

| 4.4     | Electrical characteristics                                       |

| 4.4.1   | Power supply                                                     |

| 4.4.2   | Logic input and output                                           |

| 4.4.3   | Adjustment and protection                                        |

| 4.4.4   | Output power stage                                               |

| 5       | Application section                                              |

| 5.1     | Theory of the 2EP1xxR using the voltage doubler topology         |

| 5.2     | Theory of the 2EP1xxR using peak rectification topology    28    |

| 5.3     | Load behavior for open loop converter32                          |

| 5.3.1   | Light-load output voltage increase                               |

| 5.3.2   | Isolated output voltage drop over load versus parasitics         |

| 5.4     | Soft start in application                                        |

| 5.5     | Dimensioning of components for peak rectification topology       |

| 5.5.1   | Capacitors (capacitance and ripple current)                      |

| 5.5.1.1 | 2EP ripple current estimation                                    |

| 5.5.1.2 | Output decoupling                                                |

| 5.5.1.3 | Series capacitor                                                 |

| 5.5.1.4 | Input decoupling                                                 |

| 5.5.2   | Dimensioning of transformer                                      |

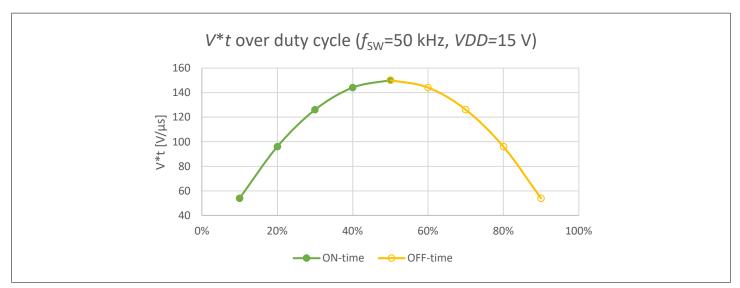

| 5.5.2.1 | Voltage×time product                                             |

| 5.5.2.2 | Main inductance                                                  |

| 5.5.2.3 | Leakage inductance                                               |

| 5.5.2.4 | Winding resistance                                               |

| 5.5.2.5 | Winding ratio or transformer turns ratio                         |

| 5.5.2.6 | Coupling capacitance                                             |

| 5.5.3   | Dimensioning of rectification diodes 38                          |

| 5.5.3.1 | Repetitive peak reverse voltage rating – V <sub>RRM</sub>        |

| 5.5.3.2 | Repetitive peak forward current rating – <i>I</i> <sub>FRM</sub> |

| 5.5.3.3 | Average forward current rating – I <sub>F(av)</sub>              |

| 5.5.3.4 | Forward voltage drop – V <sub>F</sub>                            |

| 5.5.3.5 | Diode reverse current – I <sub>R</sub>                           |

| 5.5.3.6 | Diode capacitance and reverse recovery charge                    |

| 5.5.4   | Configuration resistor selection                                 |

| 5.6     | Use case: IGBT driver supply with 2EP100R and 2EP130R            |

| 5.7     | Use case: Example of SiC MOSFET driver supply41                  |

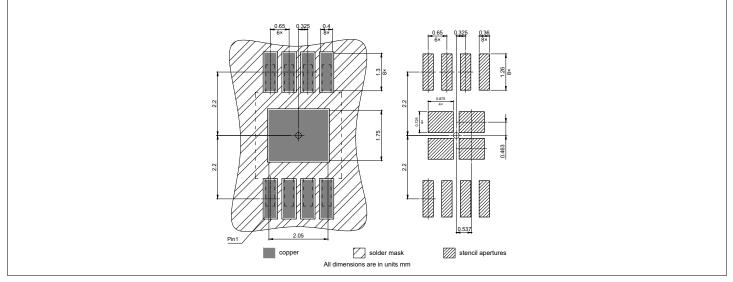

| 6       | Package dimensions                                               |

|         | Revision history                                                 |

Table of contents

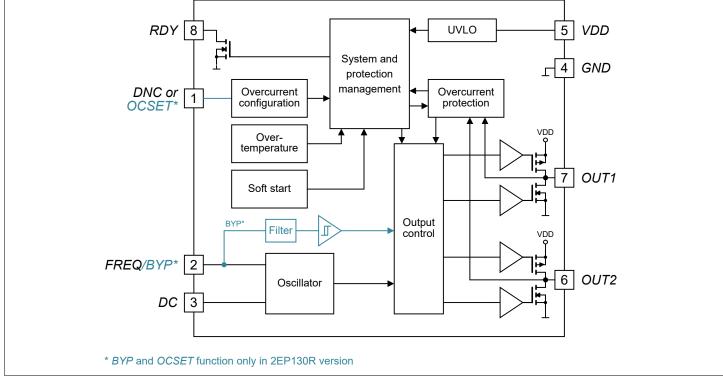

1 Block diagram

#### Figure 2

Block diagram 2EP1xxR family

## 2 Pin configuration and functionality

## 2.1 Pin configuration for 2EP100R, 2EP101R, and 2EP110R

| 0<br>□□□ DNC | RDY 8         |  |

|--------------|---------------|--|

| 2 FREQ       | OUT1 <u>7</u> |  |

| 3 DC         | OUT2 6        |  |

| 4 GND        | VDD 5         |  |

Figure 3 Pin-out for 2EP100R, 2EP101R, and 2EP110R in PG-TSSOP-8-1 (top view)

#### Table 1

#### Pin configuration for 2EP100R, 2EP101R, and 2EP110R

| Pin no. | Pin name | Pin type  | Buffer<br>type     | 2EP110R                                                             | 2EP100R and 2EP101R                                                 |

|---------|----------|-----------|--------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|

| 1       | DNC      | -         | -                  | DNC or connect to GND                                               |                                                                     |

| 2       | FREQ     | DI, logic | digital            | Connect to GND or leave flo                                         | oating/connect to voltage > 3 V                                     |

| 3       | DC       | AI, logic | analog,<br>digital | Duty cycle adjustment<br>input (place a resistor to<br><i>GND</i> ) | Connect to <i>GND</i> or leave floating/connect<br>to voltage > 3 V |

| 4       | GND      | GND       | -                  | Power and signal ground                                             | ·                                                                   |

(table continues...)

| Table 1 | (c       | (continued) Pin configuration for 2EP100R, 2EP101R, and 2EP110R |                |                                                                                |                     |  |  |  |  |  |

|---------|----------|-----------------------------------------------------------------|----------------|--------------------------------------------------------------------------------|---------------------|--|--|--|--|--|

| Pin no. | Pin name | Pin type                                                        | Buffer<br>type | 2EP110R                                                                        | 2EP100R and 2EP101R |  |  |  |  |  |

| 5       | VDD      | PWR                                                             | -              | Positive power supply                                                          |                     |  |  |  |  |  |

| 6       | OUT2     | PWR                                                             | PP             | Second output of the full-b                                                    | ridge               |  |  |  |  |  |

| 7       | OUT1     | PWR                                                             | PP             | First output of the full-bridg                                                 | ge                  |  |  |  |  |  |

| 8       | RDY      | 0                                                               | OD             | Ready output, high active, reports correct device operation, switching outputs |                     |  |  |  |  |  |

| EP      | GND      | GND                                                             | -              | Exposed pad, connect to GND                                                    |                     |  |  |  |  |  |

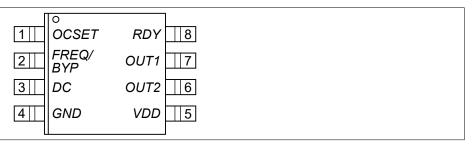

## 2.2 Pin configuration for 2EP130R

#### Figure 4 Pin-out for 2EP130R in PG-TSSOP-8-1 (top view)

#### Table 2Pin configuration for 2EP130R

| Pin no. | Pin name | Pin type  | Buffer<br>type | Function for 2EP130R                                                                                                                                              |

|---------|----------|-----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | OCSET    | AI, logic | analog         | Average overcurrent set input (place a resistor to GND)                                                                                                           |

| 2       | FREQ/BYP | Al, logic | analog,<br>TTL | Frequency adjustment input (place a resistor to <i>GND</i> ) or external clock input in bypass mode (connect a PWM signal with required frequency and duty cycle) |

| 3       | DC       | AI, logic | analog         | Duty cycle adjustment input (place a resistor to <i>GND</i> ) or bypass enable (connect to <i>GND</i> )                                                           |

| 4       | GND      | GND       | -              | Power and signal ground                                                                                                                                           |

| 5       | VDD      | PWR       | -              | Positive power supply                                                                                                                                             |

| 6       | OUT2     | PWR       | PP             | Second output of the full-bridge                                                                                                                                  |

| 7       | OUT1     | PWR       | PP             | First output of the full-bridge                                                                                                                                   |

| 8       | RDY      | 0         | OD             | Ready output, high active, reports correct device operation, switching outputs                                                                                    |

| EP      | GND      | GND       | -              | Exposed pad, connect to GND                                                                                                                                       |

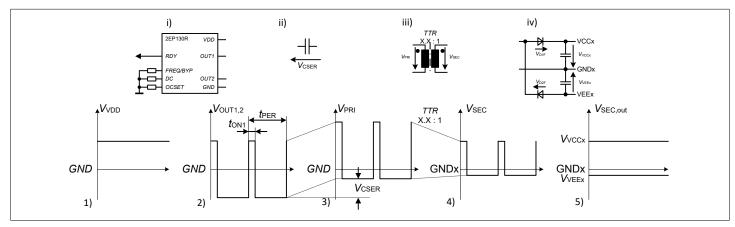

## 3 Functional description

The 2EP1xxR is optimized for asymmetric gate driver supply due its unique duty-cycle adjustment options. It still supports symmetric output supply as well as a wide variety of other single or dual output voltages.

The 2EP1xxR products directly drive a transformer in different topologies, for example:

• Full-bridge with a direct-coupled transformer and a voltage-doubler output rectification for output voltage with a ratio of 2:1

- Full-bridge with a direct-coupled transformer and peak rectification for symmetric output supplies

- Full-bridge with a series capacitor between *OUT1/OUT2* and transformer, and peak rectification for asymmetric output supplies

2EP1xxR reads its configuration from the *FREQ*, *FREQ/BYP*, *OCSET*, and *DC* pins after powering up and stores it internally during operation. A change of configuration at these pins is effective with the next read cycle after a power up.

## 3.1 Output stage

The 2EP1xxR family uses a low-ohmic, integrated, rail-to-rail, full-bridge power stage with fast slew rate. This enables the transformer driver to switch efficiently at a high switching speed.

## 3.2 Monitoring and protection

The 2EP1xxR family is equipped with several monitoring and protection features to ensure device safe operation for both, application and device:

- UVLO protection to ensure that the device operates correctly above the UVLO threshold. It preliminary prevents incorrect operation of the device below the UVLO threshold

- Detecting if the adjustment resistor is out of range

- Ready indication via RDY output

- Adjustable average overcurrent protection

- Short circuit protection (peak overcurrent)

- Overtemperature protection

The overcurrent protection and overtemperature protection are designed as protection elements. Do not operate under overload conditions for a prolonged periods to avoid reducing the lifetime or damaging the device.

## 3.2.1 Average overcurrent protection

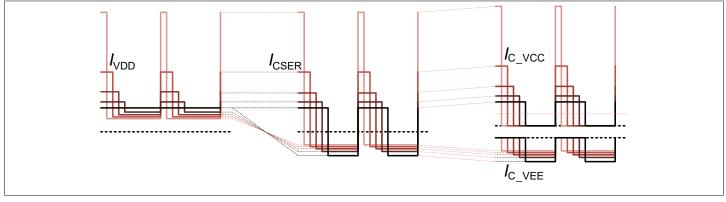

The overcurrent protection is an average overcurrent protection of *OUT1/OUT2*.

The average overcurrent triggers a shutdown if the output current of the device is above the dedicated overcurrent threshold, *I*<sub>OCthr,x</sub>, for more than half the on-time for two consecutive cycles. The same rule applies for the off-time, at that same output with its overcurrent threshold. Due to the open loop nature of the IC, the effectiveness of overcurrent protection at the output of the isolated supply is dependent on the circuit between *OUT1/OUT2* and the isolated power supply outputs.

#### **Overcurrent sensing principal**

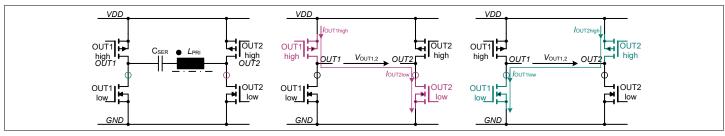

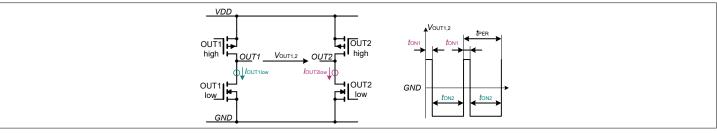

Figure 5

Location of current sensing and current path during operation

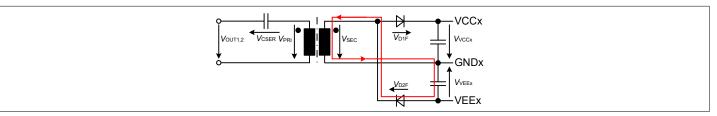

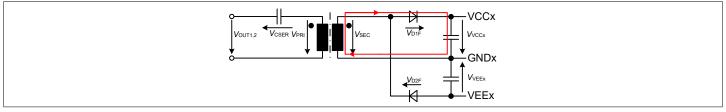

The following figures show the current path and the current sensing location of the transformer driver, 2EP1xxR. The current sensing is implemented at the low side switches as indicated by the circles close to the *OUT1* and *OUT2* drain connections. As the series capacitor,  $C_{SER}$ , and the primary side of the transformer,  $L_{PRI}$ , are connected in series between the pins *OUT1* and *OUT2*, the current path will always include one high side switch and one low side switch.

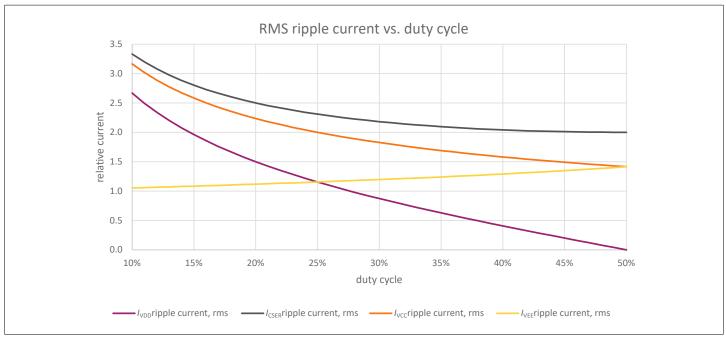

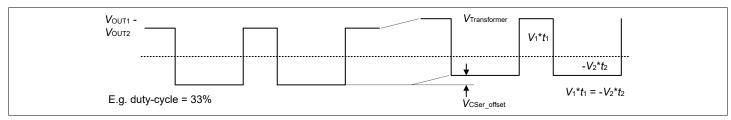

#### Asymmetric load current at duty cycles below 50%

Every duty cycle configuration except 50% introduces a DC offset to the transformer input voltage. This DC offset allows for asymmetric output voltages after peak rectification. However, the application requires a constant output power that is not dependent on the output voltage level. This results in asymmetric input currents for individual sections during the switching period. To compensate for these asymmetric currents, the transformer driver 2EP1xxR adjusts the individual overcurrent limits according to the configured duty cycle.

#### Figure 6

#### Current path mapping to individual segments of the switching period

This diagram shows the mapping of the individual current paths to the timing diagram of the outputs:

- Current during t<sub>ON1</sub> flows through the OUT1 high-side and the OUT2 low-side switch

- Current during t<sub>ON2</sub> flows through the OUT2 high-side and the OUT1 low-side switch

The duration of  $t_{ON1}$  together with the time period,  $t_{PER}$ , defines the duty cycle  $D = \frac{t_{ON1}}{t_{PER}}$

The absolute thresholds of these individual overcurrent limits depend on the product variant. 2EP100R, 2EP101R, and 2EP110R use the overcurrent setting level 4. 2EP130R offers a dedicated pin, *OCSET*, to configure the overcurrent setting level.

# Table 3Individual overcurrent thresholds depending on the configured duty cycle, D, and<br/>overcurrent setting level, OCSET

| OCSET | Ranges of duty cycle D              |                                     |                                     |                                     |                                     |                                     |  |  |  |  |  |

|-------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|--|--|--|--|--|

|       | 10%                                 | - 14%                               | 15%                                 | - 35%                               | 36% - 50%                           |                                     |  |  |  |  |  |

|       | <i>OUT1</i> high<br><i>OUT2</i> low | <i>OUT2</i> high<br><i>OUT1</i> low | <i>OUT1</i> high<br><i>OUT2</i> low | <i>OUT2</i> high<br><i>OUT1</i> low | <i>OUT1</i> high<br><i>OUT2</i> low | <i>OUT2</i> high<br><i>OUT1</i> low |  |  |  |  |  |

| 1     | I <sub>OCthr,3</sub>                | I <sub>OCthr,0</sub>                | I <sub>OCthr,2</sub>                | I <sub>OCthr,0</sub>                | I <sub>OCthr,1</sub>                | I <sub>OCthr,1</sub>                |  |  |  |  |  |

| 2     | I <sub>OCthr,4</sub>                | I <sub>OCthr,0</sub>                | I <sub>OCthr,3</sub>                | I <sub>OCthr,1</sub>                | I <sub>OCthr,2</sub>                | I <sub>OCthr,2</sub>                |  |  |  |  |  |

| 3     | I <sub>OCthr,5</sub>                | I <sub>OCthr,1</sub>                | I <sub>OCthr,4</sub>                | I <sub>OCthr,2</sub>                | I <sub>OCthr,3</sub>                | I <sub>OCthr,3</sub>                |  |  |  |  |  |

| 4     | / <sub>OCthr,6</sub>                | I <sub>OCthr,2</sub>                | I <sub>OCthr,5</sub>                | I <sub>OCthr,3</sub>                | I <sub>OCthr,4</sub>                | I <sub>OCthr,4</sub>                |  |  |  |  |  |

| 5     | I <sub>OCthr,7</sub>                | I <sub>OCthr,3</sub>                | I <sub>OCthr,6</sub>                | I <sub>OCthr,4</sub>                | I <sub>OCthr,5</sub>                | I <sub>OCthr,5</sub>                |  |  |  |  |  |

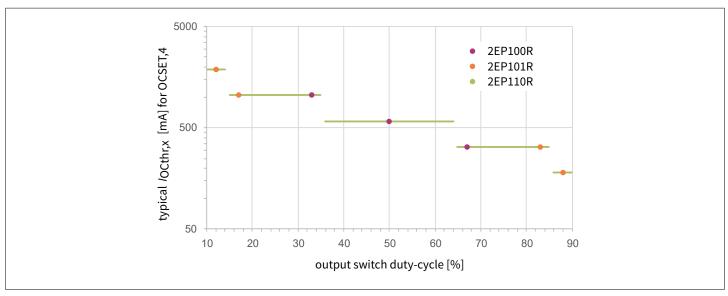

## **3.2.1.1** Fixed average overcurrent protection in 2EP100R, 2EP101R, and 2EP110R

Average overcurrent limit (OUT1, OUT2) for 2EP100R, 2EP101R, and 2EP110R is set to OCSET,4.

The duty-cycle dependent overcurrent settings as shown in Table 3 allow the transformer driver to maximize its output power. Please note that the duty cycle for the *OUT2* high-side and *OUT1* low-side switch become more than 50% for duty cycle selections of D < 50%. Figure 7 shows therefore, the average overcurrent threshold values over the whole duty-cycle range for *OCSET*,4.

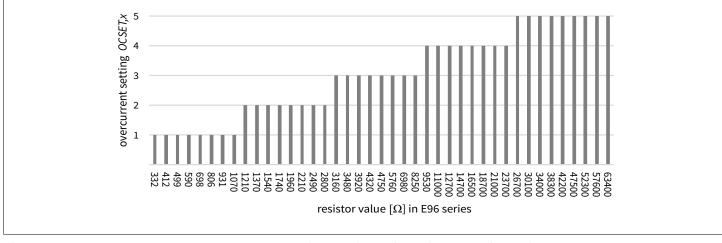

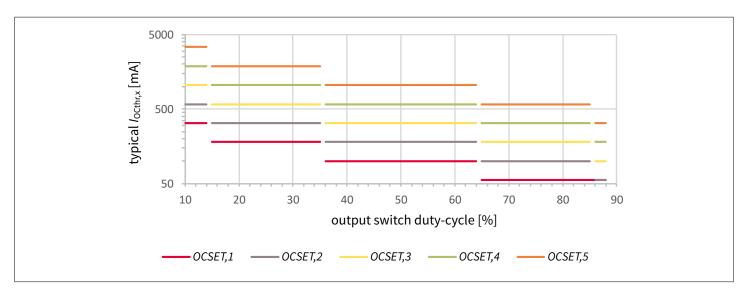

## 3.2.1.2 Adjustable average overcurrent protection in 2EP130R

The adjustable average overcurrent protection feature of 2EP130R allows users to tailor the overcurrent protection for different application power levels.

A resistor from *OCSET* pin to *GND* sets one out of the five average overcurrent settings, *OCSET,x*. Figure 8 shows the recommended E96 resistor values. Within the resistor value range resulting in the same overcurrent setting *OCSET,x* any resistor value is acceptable. For example: *OCSET,4* has a resistor value range of 9530 Ω to 23700 Ω.

Average overcurrent protection settings via resistor configuration for 2EP130R

The duty-cycle dependent overcurrent settings as shown in Table 3 allow the transformer driver to maximize its output power. Please note that the duty cycle for the *OUT2* high-side and *OUT1* low-side switch becomes more than 50% for duty cycle selections of D < 50%. Figure 9 shows therefore, the average overcurrent threshold values over the whole duty cycle range. The five overcurrent settings share a total of eight average overcurrent threshold values.

## 3.2.2 Short circuit protection

All variants of the 2EP1xxR family protect the device through a fixed but filtered short circuit protection (peak current protection).

The short circuit protection (peak overcurrent) of the outputs protect against solder splash or other low-ohmic shorts of the outputs *OUT1/OUT2* to supply *VDD* or *GND* rail.

## 3.2.3 Overtemperature protection

The overtemperature protection triggers a shutdown of the IC in high ambient temperature environments or without sufficient cooling. This protects the IC against thermal stress beyond its maximum rating.

## 3.2.4 Out-of-range detection for external resistors in 2EP110R and 2EP130R

The input pins of the 2EP110R (*DC* pin only) and the 2EP130R (*DC*, *FREQ/BYP*, *OCSET* pins) for the external resistors have an out-of-range detection circuit.

This ensures that the transformer drivers only start if those resistor values are within their specified operating range  $(200 \ \Omega < R_{set} < 82 \ k\Omega)$  or activate an alternative operating mode (2EP130R *DC* pin to *GND*: bypass mode). 2EP1xxR continuously repeats the resistor read-out at start-up until all resistor values are within the range. During the repetitive read-out phase, the *RDY* pin stays low and the output stage stays in tri-state. The following table lists the out-of-range detection values for 2EP110R and 2EP130R.

| Pin name | Product | R <sub>set</sub> < 200 Ω | R <sub>set</sub> > 82 kΩ |

|----------|---------|--------------------------|--------------------------|

| DC       | 2EP130R | Activates bypass mode    | Out of range             |

| DC       | 2EP110R | Out of range             |                          |

| OCSET    | 2EP130R |                          |                          |

| FREQ/BYP | 2EP130R |                          |                          |

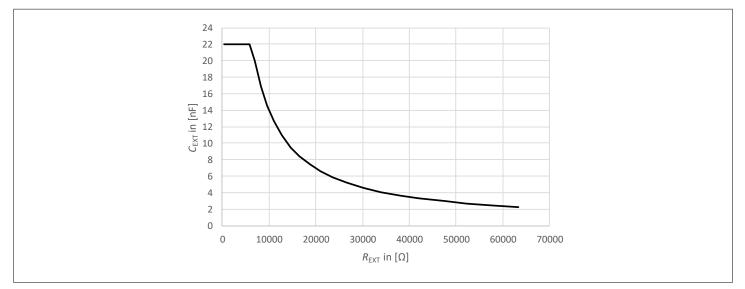

## 3.2.5 Adjustable resistor's filtering capacitor range

The transformer driver 2EP110R and 2EP130R support filter capacitors at the input pins for external resistors, depending on the individual resistor value connected to that pin. This filtering method is suitable for application circuits with high noise expectancy even at power supply start-up.

This selection of optional filter capacitor value applies to the following pins and product variants:

• *DC*: 2EP110R and 2EP130R

- FREQ/BYP: 2EP130R only

- OCSET: 2EP130R only

## 3.2.6 Ready output – RDY

The ready output, *RDY*, is an open-drain output. Use an external pull-up circuit to a voltage supply of up to 5.5 V for a proper logic output signal.

During operation, a high at the *RDY* pin indicates that the:

- Device is properly supplied (>UVLO)

- Device is configured

- Soft start has finished

- Outputs are switching

During operation, a low at the *RDY* pin indicates that the:

- Device has a fault status:

- Average overcurrent protection triggered

- Peak current protection triggered

- Overtemperature triggered

- Loss of synchronization

- Read-out resistor is out of range

- Waiting for the bypass signal

- Device in wait cycle

- Device in soft start

## 3.3 Frequency setting

The 2EP1xxR family offers three operating modes to adjust the switching frequency:

- Pin strapping: 2EP100R, 2EP101R, and 2EP110R

- Resistor adjustment: 2EP130R

- Bypass mode: 2EP130R, see Chapter 3.5

## 3.3.1 Frequency setting by pin strapping in 2EP100R, 2EP101R, and 2EP110R

The products 2EP100R, 2EP101R, and 2EP110R provide the option of selecting a frequency via the following pin strapping methods:

- Connecting the pin FREQ to GND with a resistance lower than 1 k $\Omega$  enables a lower switching frequency

- Leaving the pin FREQ open or connecting a resistance larger than 4.7 k $\Omega$  to GND enables a higher switching frequency

## 3.3.2 Frequency setting by resistor configuration in 2EP130R

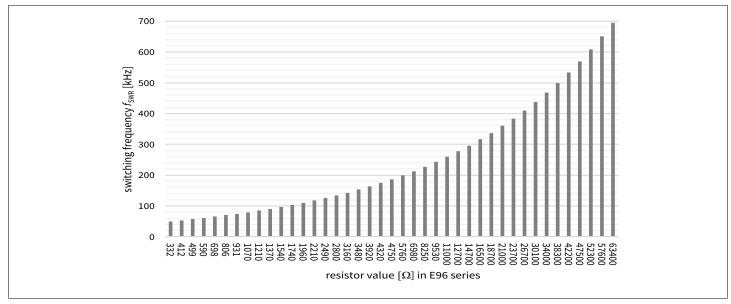

2EP130R provides the option to select frequencies over a wide range, from 50 kHz to 695 kHz. This helps in adapting the device to different application conditions, including transformer parameters.

A resistor from *FREQ/BYP* pin to *GND* sets one out of 41 discrete switching frequencies. Figure 11 shows the resulting switching frequency over the recommended E96 series resistor values. In case any other value within the allowed external resistor value range has been selected, the transformer driver selects the frequency matching to the closest resistor value of these recommended E96 resistor values.

Figure 11 Frequency setting by resistor configuration for 2EP130R

## 3.4 Duty-cycle setting

The 2EP1xxR family offers three operating modes to adjust the highly accurate duty cycle:

- Pin strapping for 2EP100R and 2EP101R

- Resistor setting for 2EP110R and 2EP130R

- Bypass mode for 2EP130R, see Chapter 3.5

A duty-cycle setting other than 50% is mainly used in application circuits with a series capacitor at the primary side and peak rectification at the secondary side of the transformer. Such a configuration allows users to adjust the ratio of the positive to the negative isolated output voltage. The transfer ratio of the transformer defines the relation between the transformer's input and output voltages. Both measures together enable the adjustment of the output voltage for positive and negative rail in a wide voltage range.

## 3.4.1 Duty-cycle setting by pin strapping in 2EP100R and 2EP101R

The products 2EP100R and 2EP101R provide the option of selecting a duty cycle via the following pin strapping methods:

- Connecting the pin *DC* to *GND* with a resistance lower than  $1 k\Omega$  enables a lower duty cycle

- Leaving the pin *DC* open or connecting a resistance larger than 4.7 kΩ to *GND* enables a higher duty cycle

## 3.4.2 Duty-cycle setting by resistor configuration in 2EP110R and 2EP130R

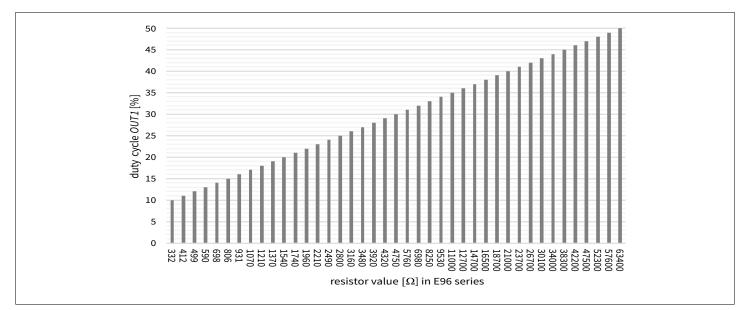

The products 2EP110R and 2EP130R provide the option of selecting duty cycle over a wide range, from 10% to 50%. A resistor from *DC* pin to *GND* sets one out of the 41 duty cycles in single percentage steps.

Figure 12 shows the resulting duty cycle over the recommended E96 series resistor values. In case any other value within the allowed external resistor value range has been selected, the transformer driver selects the duty cycle matching to the closest resistor value of these recommended E96 resistor values.

#### Figure 12 Duty-cycle setting by resistor configuration for 2EP110R and 2EP130R

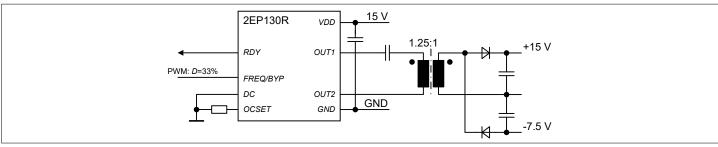

## 3.5 Frequency and duty-cycle setting in bypass mode in 2EP130R

2EP130R offers a bypass mode. When operating in this mode, the external PWM signal bypasses the internal oscillator and modulates directly to the output stage of 2EP130R.

In the bypass mode, 2EP130R supports frequencies in the range of 50 kHz to 695 kHz and a duty cycle in the range of 10% to 50%. For more information regarding useful operating ranges of frequency and duty cycle combinations, see Chapter 3.6.

2EP130R uses the soft start feature in bypass mode, including frequency rise during soft start. Soft start is, therefore, asynchronous to the external PWM signal.

For more information regarding soft start, see Chapter 3.8.6.

## 3.5.1 Start-up in bypass mode

Connecting the *DC* pin to *GND* signals 2EP130R to operate in the bypass mode. After powering up, the externally applied PWM signal at the pin *FREQ/BYP* begins the start-up synchronization and configuration of the device.

#### Start-up synchronization

After the supply passes the UVLO threshold, 2EP130R uses the first three consecutive PWM cycles applied to the *FREQ/BYP* pin to synchronize and sample both frequency and duty cycle.

### Configuration

2EP130R uses the applied and synchronized duty cycle to configure:

- Duty-cycle dependent, average overcurrent setting (see Chapter 3.2.1)

- Duty-cycle setting for soft start

- Pre-charge activation

The following table shows the resulting configuration of duty cycle and pre-charge setting for any allowed input PWM duty cycle.

#### Table 4Bypass mode configuration for 2EP130R

| Input PWM duty | cycle at FREQ/BYP | Output duty cycle at OUT1 | l Pre-charge |  |

|----------------|-------------------|---------------------------|--------------|--|

| Minimum        | Maximum           |                           |              |  |

| 9.0%           | 10.50%            | 10%                       | Yes          |  |

| 10.5%          | 11.40%            | 11%                       |              |  |

| 11.4%          | 12.50%            | 12%                       |              |  |

| 12.5%          | 13.30%            | 13%                       |              |  |

| 13.3%          | 14.30%            | 14%                       |              |  |

| 14.3%          | 15.40%            | 15%                       |              |  |

| 15.4%          | 16.70%            | 16%                       |              |  |

| 16.7%          | 17.40%            | 17%                       |              |  |

| 17.4%          | 18.20%            | 18%                       |              |  |

| 18.2%          | 19%               | 19%                       |              |  |

| 19.0%          | 20%               | 20%                       |              |  |

| 20.0%          | 21.10%            | 21%                       |              |  |

| 21.1%          | 22.20%            | 22%                       |              |  |

| 22.2%          | 23.50%            | 23%                       |              |  |

| 23.5%          | 25%               | 24%                       |              |  |

| 25,0%          | 26.70%            | 26%                       |              |  |

| 26.7%          | 28.60%            | 28%                       |              |  |

| 28.6%          | 30.80%            | 30%                       |              |  |

| 30.8%          | 33.30%            | 32%                       | ]            |  |

| 33.3%          | 36.40%            | 35%                       |              |  |

| 36.4%          | 40%               | 38%                       |              |  |

| 40.0%          | 44.40%            | 43%                       |              |  |

| 44.4%          | 60%               | 50%                       | No           |  |

After start-up synchronization and configuration, the IC performs a soft start. During soft start, 2EP130R ignores the *FREQ/BYP* signal and uses its internal frequency generator. For proper start-up synchronization, the external PWM signal (frequency and duty cycle) must be kept constant during start-up until 2EP130R signals the end of soft start by releasing the *RDY* pin.

## 3.5.2 Entering operation in bypass mode

After the soft start phase, 2EP130R synchronizes to the applied external PWM frequency and duty cycle connected to the *FREQ/BYP* pin. Ensure that the frequency and duty cycle are stable during the soft start to prevent frequency or duty-cycle steps that may create a system overcurrent event.

While operating in the bypass mode, 2EP130R follows the applied frequency and duty cycle. Changes in duty cycle during operation will not cause the transformer driver to change the already identified overcurrent threshold levels, *I*<sub>OCthr,x</sub>. These levels are only set during start-up and the initial duty cycle evaluation.

## 3.5.3 Stopping operation in bypass mode

2EP130R stops synchronous switching operation in the bypass mode in case of an UVLO event or one of the following fault events:

- Loss of synchronization fault

- Doubling of the switching period time compared to the current period time

- Increase beyond the maximum switching period

- Average overcurrent protection fault

- Peak overcurrent protection fault

- Overtemperature fault

For these faults or UVLO events, the IC sets *RDY* to low, and the output stage to tri-state.

After all faults are cleared, or after the supply passes the UVLO threshold, 2EP130R restarts in the bypass mode.

#### Doubling the switching period time compared to the current period time

2EP130R validates cycle-over-cycle, if the on-time or off-time at the *FREQ/BYP* pin has increased more than a factor of 2 compared to the previous on-time or off-time.

#### Increase beyond the maximum switching period

2EP130R validates if the on-time plus the off-time at the *FREQ/BYP* pin is more than the maximum allowed switching period of typically 22.5  $\mu$ s.

## 3.6 Useful operating range of duty cycle and switching frequency

2EP130R offers a wide frequency and duty-cycle operating range. To ensure proper operation of the overcurrent protection, respect the minimal on-time,  $t_{ONmin}$ , of the outputs *OUT1/OUT2*.

## 3.7 Resistor adjustment table for 2EP110R and 2EP130R

Resistor function table for resistor R<sub>FREQ/BYP</sub>, R<sub>DC</sub>, and R<sub>OCSET</sub> when connected to ground with resistor R<sub>set</sub>.

| Table 5                 | Resist<br>settin | tor values: D<br>ng, OCSET, for | uty cycle <i>D</i> f<br>2EP130R or | <sup>•</sup> 2EP110R and 2EP130F<br>y | R; Frequency,    | f <sub>SWR</sub> , and ov | ercurrent |  |

|-------------------------|------------------|---------------------------------|------------------------------------|---------------------------------------|------------------|---------------------------|-----------|--|

| <b>R</b> <sub>set</sub> | f <sub>SWR</sub> | D                               | OCSET                              | <b>R</b> <sub>set</sub>               | f <sub>SWR</sub> | D                         | OCSET     |  |

| Ohm                     | kHz              | %                               |                                    | Ohm                                   | kHz              | %                         |           |  |

| 332                     | 50               | 10                              | 1                                  | 5760                                  | 199              | 31                        | 3         |  |

| 412                     | 53               | 11                              | 1                                  | 6980                                  | 213              | 32                        | 3         |  |

| 499                     | 57               | 12                              | 1                                  | 8250                                  | 227              | 33                        | 3         |  |

| 590                     | 61               | 13                              | 1                                  | 9530                                  | 243              | 34                        | 4         |  |

| 698                     | 65               | 14                              | 1                                  | 11000                                 | 259              | 35                        | 4         |  |

| 806                     | 70               | 15                              | 1                                  | 12700                                 | 277              | 36                        | 4         |  |

| 931                     | 74               | 16                              | 1                                  | 14700                                 | 295              | 37                        | 4         |  |

| 1070                    | 79               | 17                              | 1                                  | 16500                                 | 316              | 38                        | 4         |  |

| 1210                    | 85               | 18                              | 2                                  | 18700                                 | 337              | 39                        | 4         |  |

| 1370                    | 90               | 19                              | 2                                  | 21000                                 | 360              | 40                        | 4         |  |

| 1540                    | 97               | 20                              | 2                                  | 23700                                 | 384              | 41                        | 4         |  |

| 1740                    | 103              | 21                              | 2                                  | 26700                                 | 410              | 42                        | 5         |  |

| 1960                    | 110              | 22                              | 2                                  | 30100                                 | 438              | 43                        | 5         |  |

| 2210                    | 118              | 23                              | 2                                  | 34000                                 | 468              | 44                        | 5         |  |

| 2490                    | 126              | 24                              | 2                                  | 38300                                 | 500              | 45                        | 5         |  |

| 2800                    | 134              | 25                              | 2                                  | 42200                                 | 534              | 46                        | 5         |  |

| 3160                    | 143              | 26                              | 3                                  | 47500                                 | 570              | 47                        | 5         |  |

| 3480                    | 153              | 27                              | 3                                  | 52300                                 | 609              | 48                        | 5         |  |

| 3920                    | 163              | 28                              | 3                                  | 57600                                 | 651              | 49                        | 5         |  |

| 4320                    | 175              | 29                              | 3                                  | 63400                                 | 695              | 50                        | 5         |  |

| 4750                    | 186              | 30                              | 3                                  |                                       |                  |                           |           |  |

## 3.8 Description of operating states

The 2EP1xxR transformer driver ICs implement the following states:

- OFF state

- Read configuration state

- Self-test state

- Pre-charge state

- Soft start state

- Run state

- Fault state

- Wait state

## **EiceDRIVER<sup>™</sup> Power 2EP1xxR family datasheet** Full-bridge transformer driver for IGBT and SiC MOSFET gate driver supply

3 Functional description

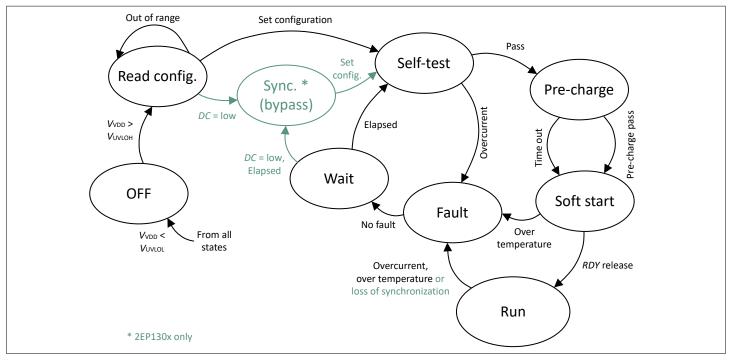

#### Figure 14 Operating state diagram

## 3.8.1 Off state

The device is not powered or supplied with a voltage below the UVLO threshold. Default output stages are in tri-state.

## **3.8.2** Read configuration state

When supplied, and after passing the UVLO threshold, 2EP1xxR enters the read configuration state.

2EP1xxR reads the configuration data from corresponding pins (pin strapping, resistor setting, and bypass mode). After a successful read-out, the transformer driver transitions to the next state by setting the device configuration. The output stage is set to tri-state.

## 3.8.3 Synchronisation state (bypass mode only)

Following the configuration state in the case of bypass mode (*DC* pin is low), the device enters the synchronization state. In the synchronization state, 2EP130R uses the first three consecutive cycles of an applied PWM signal at the *FREQ/BYP* pin to synchronize to the external PWM.

The read-out frequency and duty cycle are used to configure:

- Duty-cycle dependent average overcurrent offset

- Duty cycle for soft start

- Pre-charge activation

The output stage is set to tri-state.

## 3.8.4 Self-test state

The built-in self-test ensures that both outputs, *OUT1* and *OUT2*, have neither a short to supply pin *VDD*, nor a short to ground pin *GND*. A detected short leads to a fault state. The device switches the outputs between active and tri-state.

## 3.8.5 Pre-charge state

The pre-charge function charges the series capacitor with the pre-charge current of typically 18 mA until the series capacitor reaches the pre-charge voltage. 2EP1xxR switches *OUT1* to *GND* and *OUT2* operates as a current source from *VDD*. The pre-charge function depends on the configured duty cycle:

- Duty cycle < 45%: Perform pre-charge

- Duty cycle > 45%: Skip pre-charge

A timeout of typically 20 ms is built in to overcome any stalled conditions caused by pre-charge overtime fault.

## **3.8.6 Soft start state**

2EP1xxR uses the soft start feature to limit the application inrush current. It also results in a smooth ramp-up of the isolated output voltage. The soft start, therefore, operates with a potentially increased frequency and a soft start specific peak current mode.

#### **Frequency increase**

- Increases switching frequency typically to 360 kHz for configured frequencies below 360 kHz

- Uses configured frequency for frequency settings above 360 kHz

#### Soft start specific peak current mode

To secure a stable start-up for capacitive and base loads, 2EP1xxR starts in the peak current mode with the overcurrent threshold value *I*<sub>OCthr,6</sub> for both outputs. During the remaining soft start phase, the overcurrent threshold value gradually adjusts to its individual target value. In case the peak current detection is triggered permanently due to overload, 2EP1xxR stays in the soft start mode indefinitely.

If the transformer driver starts with a higher frequency, the soft start frequency decreases gradually to the configured value. The soft start function ends as soon as the target frequency is reached. 2EP1xxR then releases the *RDY* pin to high.

## 3.8.7 Run state

In this state, the device is in full operation. The outputs are actively switching according to the requested frequency and duty cycle, and the *RDY* signal is released to high. 2EP1xxR exits the run state when any of the following events occur:

- Transition to a fault state:

- Average overcurrent fault

- Peak overcurrent fault

- Overtemperature fault

- Loss of synchronization fault (only applicable in the bypass mode)

- Transition to OFF state: an UVLO event, passing the V<sub>UVLOL</sub> threshold

#### 3.8.8 Fault state

When 2EP1xxR detects a fault, the device stays in the fault state until all faults disappear. 2EP1xxR switches the output state to tri-state and the *RDY* signal to low to signal a failure.

## 3.8.9 Wait state

After a fault has passed, the device enters a wait state to bring the system to a stable initial state and to reduce the stress on the components.

The output stage is kept in tri-state. After the wait cycle time,  $t_{Wait}$ , has elapsed, the system continues in a self-test state to restart.

## 4 Electrical characteristics and parameters

## 4.1 Absolute maximum ratings

#### Table 6Absolute maximum ratings

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only. Operating the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Device reliability may be affected by exposure to absolutemaximum-rated conditions for extended periods of time.

| Parameter                                | Symbol               | Values |      |                          | Unit | Note or condition                       |

|------------------------------------------|----------------------|--------|------|--------------------------|------|-----------------------------------------|

|                                          |                      | Min.   | Тур. | Max.                     |      |                                         |

| Supply voltage                           | V <sub>VDD</sub>     | -0.3   |      | 22                       | V    |                                         |

| Output voltage (OUT1, OUT2)              | V <sub>OUT</sub>     | -0.3   |      | V <sub>VDD</sub><br>+0.3 | V    |                                         |

| Output voltage transient (OUT1,<br>OUT2) | V <sub>OUT</sub>     | -2     |      | V <sub>VDD</sub><br>+2   | V    | <sup>1)</sup> Repetitive pulse < 200 ns |

| Logic input voltages                     | V <sub>LOGIC</sub>   | -0.3   |      | 6.5                      | V    | 2)                                      |

| Logic input voltages                     | V <sub>LOGIC</sub>   | -0.3   |      | V <sub>VDD</sub><br>+0.3 | V    | $V_{\rm VDD}$ < 6.5 V <sup>2)</sup>     |

| RDY sink current                         | I <sub>RDY</sub>     | -      |      | 10                       | mA   |                                         |

| RDY signal voltage                       | V <sub>RDY</sub>     | -0.3   |      | 6.5                      | V    |                                         |

| Junction temperature                     | TJ                   | -40    |      | 150                      | °C   |                                         |

| Storage temperature                      | T <sub>S</sub>       | -55    |      | 150                      | °C   |                                         |

| Power dissipation PG-TSSOP-8             | PD                   |        |      | 930                      | mW   | PG-TSSOP-8, <i>dT</i> = 70 °C           |

| ESD robustness - human body<br>model     | V <sub>ESD,HBM</sub> |        |      | 2                        | kV   | 3)                                      |

| ESD capability - charged device<br>model | ESD,CDM              |        |      | TC<br>500                |      | 4)                                      |

1) Parameter is not subject to production test - verified by design/characterization

2) Valid for externally applied voltages

3) According to ANSI/ESDA/JEDEC-JS-001-2017 (discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor).

4) According to ANSI/ESDA/JEDEC-JS-002-2014 (TC = test condition in volt)

## 4.2 Thermal characteristics

#### Table 7Thermal characteristics

Thermal performance may change significantly with layout and heat dissipation of components in close proximity.

| Parameter                                                                  | Symbol             | Values |      |      | Unit | Note or condition                                                            |

|----------------------------------------------------------------------------|--------------------|--------|------|------|------|------------------------------------------------------------------------------|

|                                                                            |                    | Min.   | Тур. | Max. |      |                                                                              |

| Thermal resistance, junction-to-<br>ambient PG-TSSOP-8                     | R <sub>THJA</sub>  |        |      | 75   | K/W  | $T_{\rm A}$ = 25°C, $P_{\rm D}$ = 930 mW, PG-<br>TSSOP-8                     |

| Characterization parameter,<br>junction-to-package top-side PG-<br>TSSOP-8 | $\Psi_{\sf JPtop}$ |        |      | 14   | K/W  | <i>T</i> <sub>A</sub> = 25°C, <i>P</i> <sub>D</sub> = 930 mW, PG-<br>TSSOP-8 |

## 4.3 **Operating parameters**

#### Table 8Operating parameters

Within the operating range, the IC operates as described in the functional description and electrical characteristics.

| Parameter                       | Symbol             |      | Values | ;                        | Unit | Note or condition                   |

|---------------------------------|--------------------|------|--------|--------------------------|------|-------------------------------------|

|                                 |                    | Min. | Тур.   | Max.                     |      |                                     |

| Supply voltage, operating       | V <sub>VDD</sub>   | 4.5  |        | 20                       | V    |                                     |

| Logic input voltages, operating | V <sub>LOGIC</sub> | -0.3 |        | 5.5                      | V    | $V_{\rm VDD}$ > 5.5 V <sup>1)</sup> |

| Logic input voltages, operating | V <sub>LOGIC</sub> | -0.3 |        | V <sub>VDD</sub><br>+0.3 | V    | $V_{\rm VDD}$ < 5.5 V <sup>1)</sup> |

| Minimum on-time                 | t <sub>ONmin</sub> | 540  |        |                          | ns   |                                     |

| Switching frequency             | f <sub>SW</sub>    | 50   |        | 695                      | kHz  | only 2EP130x                        |

| Ambient temperature, operating  | T <sub>A</sub>     | -40  |        | 125                      | °C   | $T_{\rm J} < T_{\rm OTPOFF}^{2}$    |

1) Valid for externally applied voltages

2) For life time calculations, please contact your local Infineon quality team.

## 4.4 Electrical characteristics

The electrical characteristics include the spread of values within the operating parameters. Electrical characteristics are tested in production at  $T_A$  = 25°C. Typical values represent the median values measured at  $V_{VDD}$  = 15 V, and  $T_A$  = 25°C. Minimum and maximum characteristics are verified by characterization/design. This note is valid for all electrical characteristics unless specified otherwise.

## 4.4.1 Power supply

#### Table 9 Power supply

| Parameter                                 | Symbol               |      | Values |      | Unit | Note or condition                                                                                             |

|-------------------------------------------|----------------------|------|--------|------|------|---------------------------------------------------------------------------------------------------------------|

|                                           |                      | Min. | Тур.   | Max. |      |                                                                                                               |

| Supply voltage UVLO threshold upper limit | V <sub>UVLOH</sub>   | 3.95 | 4.2    | 4.45 | V    |                                                                                                               |

| Supply voltage UVLO threshold lower limit | V <sub>UVLOL</sub>   | 3.65 | 3.9    | 4.15 | V    |                                                                                                               |

| Supply voltage UVLO hysteresis            | V <sub>UVLOHys</sub> | 0.2  | 0.3    | 0.4  | V    |                                                                                                               |

| VDD supply current                        | I <sub>VDD</sub>     |      |        | 6    | mA   | No load, V <sub>VDD</sub> = 15 V, f <sub>SW</sub> =<br>103 kHz or 65 kHz, D = 12%/<br>50%, OCSET,4 for 2EP130 |

## 4.4.2 Logic input and output

#### Table 10 Logic input and output

| Parameter                      | Symbol                  |      | Values | ;    | Unit | Note or condition                                                                            |

|--------------------------------|-------------------------|------|--------|------|------|----------------------------------------------------------------------------------------------|

|                                |                         | Min. | Тур.   | Max. |      |                                                                                              |

| Logic input voltage low        | V <sub>Logic,L</sub>    |      |        | 1.0  | ۷    | 1)                                                                                           |

| Logic input voltage high       | V <sub>Logic,H</sub>    | 2.4  |        |      | V    | 1)                                                                                           |

| Logic input voltage hysteresis | V <sub>Logic,Hys</sub>  | 0.8  |        |      | V    | 1)                                                                                           |

| Logic input filter time        | t <sub>Logic,filt</sub> | 120  | 180    | 280  | ns   | <i>V</i> <sub>Logic</sub> = 3.3 V, <i>V</i> <sub>Logic</sub> rise time < 10 ns, <sup>1</sup> |

| Logic output voltage low RDY   | V <sub>RDY,5</sub>      |      |        | 0.3  | V    | $V_{\rm VDD}$ = 15 V, $I_{\rm sink}$ = 5 mA                                                  |

1) Only for 2EP130x at *FREQ/BYP* pin in bypass mode.

## 4.4.3 Adjustment and protection

#### Table 11 Adjustment and protection

| Parameter                            | Symbol              |      | Values |      | Unit | Note or condition |

|--------------------------------------|---------------------|------|--------|------|------|-------------------|

|                                      |                     | Min. | Тур.   | Max. |      |                   |

| 2EP100, 2EP101, 2EP110               |                     |      |        |      |      |                   |

| Maximum resistance for low detection | R <sub>ISMGND</sub> | 1800 |        |      | Ω    |                   |

| (table continues)                    | 1                   |      | 1      | 1    | 1    | L                 |

### Table 11 (continued) Adjustment and protection

| Parameter                                     | Symbol                |       | Values | ;     | Unit        | Note or condition                                                                             |

|-----------------------------------------------|-----------------------|-------|--------|-------|-------------|-----------------------------------------------------------------------------------------------|

|                                               |                       | Min.  | Тур.   | Max.  |             |                                                                                               |

| Minimum resistance for high detection         | RISMFLOAT             |       |        | 2.43  | kΩ          |                                                                                               |

| Switching frequency 50                        | f <sub>SW50</sub>     | 46    | 50     | 53    | kHz         | 2EP101, 2EP110,<br>FREQ connected to GND                                                      |

| Switching frequency 65                        | f <sub>SW65</sub>     | 62.5  | 65.1   | 67.1  | kHz         | 2EP100: <i>FREQ</i> connected to<br><i>GND</i> ; 2EP101, 2EP110: <i>FREQ</i> left<br>floating |

| Switching frequency 103                       | f <sub>SW103</sub>    | 99    | 103.1  | 106.2 | kHz         | 2EP100: FREQ left floating                                                                    |

| Duty cycle, fixed 1                           | <i>D</i> <sub>1</sub> | 11    | 12     | 13    | %           | 2EP101, DC connected to GND                                                                   |

| Duty cycle, fixed 2                           | D <sub>2</sub>        | 16    | 17     | 18    | %           | 2EP101, <i>DC</i> floating or 3 V < <i>V</i> <sub>DC</sub><br>< 5.5 V                         |

| Duty cycle, fixed 3                           | D <sub>3</sub>        | 32    | 33     | 34    | %           | 2EP100, DC connected to GND                                                                   |

| Duty cycle, fixed 4                           | D <sub>4</sub>        | 49    | 50     | 51    | %           | 2EP100, <i>DC</i> floating or 3 V < V <sub>DC</sub><br>< 5.5 V                                |

| 2EP110x, 2EP130x                              | 1                     | I     |        | -     | -           |                                                                                               |

| External resistor value range                 | R <sub>EXT</sub>      | 0.332 |        | 63.4  | kΩ          |                                                                                               |

| External filter capacitor value range         | C <sub>EXT</sub>      | 0     |        | 22    | nF          | 1) 2)                                                                                         |

| Duty-cycle range resistor adjusted            | D <sub>R</sub>        | 10    |        | 50    | %           | resistor adjusted at DC                                                                       |

| Duty-cycle accuracy, low frequency            | D <sub>ACC,LF</sub>   | -1    |        | 1     | %<br>points | integer duty cycle in 1% steps,<br>$f_{SW} \le 150 \text{ kHz}$                               |

| Duty-cycle accuracy, high frequency           | D <sub>ACC, HF</sub>  | -2    |        | 2     | %<br>points | integer duty-cycle in 1% steps,<br>f <sub>SW</sub> > 150 kHz                                  |

| 2EP130x                                       | 1                     |       |        |       |             |                                                                                               |

| Switching frequency self-<br>oscillating, min | f <sub>SWR,min</sub>  | 46    | 50     | 53    | kHz         | $R_{\rm FREQ/BYP}$ = 332 $\Omega$                                                             |

| Switching frequency self-<br>oscillating, max | f <sub>SWR,max</sub>  | 645   | 695    | 735   | kHz         | $R_{\rm FREQ/BYP}$ = 63.4 k $\Omega$                                                          |

| Bypass mode grounding resistance              | R <sub>BYPGND</sub>   | 0     |        | 200   | Ω           |                                                                                               |

| Frequency synchronization range               | f <sub>SW,SYNC</sub>  | 50    |        | 695   | kHz         | $D_{\rm SYNC} = 50\%, ^{3}$                                                                   |

| Synchronization propagation delay             | t <sub>PD,SYNC</sub>  | 225   | 280    | 340   | ns          | $V_{OUTx}$ at 10% or 90%, $C_{LOAD} = 1$ nF, <sup>3</sup>                                     |

| Duty-cycle synchronization range 1            | D <sub>SYNC1</sub>    | 10    |        | 50    | %           | f <sub>SW,SYNC</sub> < 185 kHz, <sup>3)</sup>                                                 |

| Duty-cycle synchronization range 2            | D <sub>SYNC2</sub>    | 38    |        | 50    | %           | $f_{\rm SW,SYNC}$ = 695 kHz, <sup>3)</sup>                                                    |

| Protection                                    | 1                     | I     |        | 1     |             |                                                                                               |

| Overcurrent threshold 0                       | I <sub>OCthr,0</sub>  | 25    | 60     | 85    | mA          |                                                                                               |

| Overcurrent threshold 1                       | I <sub>OCthr,1</sub>  | 60    | 110    | 140   | mA          |                                                                                               |

| Overcurrent threshold 2                       | I <sub>OCthr,2</sub>  | 108   | 195    | 252   | mA          |                                                                                               |

| Overcurrent threshold 3<br>(table continues)  | I <sub>OCthr,3</sub>  | 200   | 340    | 450   | mA          |                                                                                               |

(table continues...)

#### Table 11(continued) Adjustment and protection

| Parameter                      | Symbol               |      | Values |      | Unit | Note or condition |

|--------------------------------|----------------------|------|--------|------|------|-------------------|

|                                |                      | Min. | Тур.   | Max. |      |                   |

| Overcurrent threshold 4        | I <sub>OCthr,4</sub> | 350  | 585    | 820  | mA   |                   |

| Overcurrent threshold 5        | I <sub>OCthr,5</sub> | 650  | 1175   | 1450 | mA   |                   |

| Overcurrent threshold 6        | I <sub>OCthr,6</sub> | 1300 | 1970   | 2400 | mA   |                   |

| Overcurrent threshold 7        | I <sub>OCthr,7</sub> | 2900 | 3375   | 3800 | mA   |                   |

| Peak-overcurrent threshold     | I <sub>PkOCP</sub>   | 4    | 4.8    | 6    | А    |                   |

| Peak-overcurrent reaction time | t <sub>OCPRDY</sub>  | 100  |        | 540  | ns   |                   |

| Overtemperature threshold      | T <sub>OTPOFF</sub>  | 150  |        |      | °C   | 1)                |

| Overtemperature hysteresis     | T <sub>OTPHys</sub>  | 20   |        |      | °C   | 1)                |

| Wait cycle after fault         | t <sub>Wait</sub>    | 0    |        | 50   | ms   | 1)                |

1) Parameter is not subject to production test - verified by design/characterization

2) For detailed information see graph external filter capacitance  $C_{\text{EXT}}$  vs. external resistance  $R_{\text{EXT}}$ .

3) Device in bypass mode, DC connected to GND, signal applied at FREQ/BYP with  $V_{\text{Logic}} = 3.3 \text{ V}$ , rise time < 10 ns.

## 4.4.4 Output power stage

#### Table 12Output power stage

| Parameter                     | Symbol            |      | Values |      | Unit | Note or condition                                                    |

|-------------------------------|-------------------|------|--------|------|------|----------------------------------------------------------------------|

|                               |                   | Min. | Тур.   | Max. |      |                                                                      |

| Driver output resistance high | R <sub>ON,H</sub> |      | 0.63   | 0.95 | Ω    | $I_{\rm OUT} = 50 \text{ mA}, T_{\rm J} = 125^{\circ} \text{C}^{1}$  |

| Driver output resistance low  | R <sub>ON,L</sub> |      | 0.48   | 0.73 | Ω    | $I_{\rm OUT} = -50 \text{ mA}, T_{\rm J} = 125^{\circ} \text{C}^{1}$ |

| Rise time                     | t <sub>RISE</sub> | 8    | 15     | 25   | ns   | $V_{VDD} = 15 V, C_{LOAD} = 1 nF, V_{OUT}$<br>from 10% to 90%        |

| Fall time                     | t <sub>FALL</sub> | 8    | 15     | 25   | ns   | $V_{VDD} = 15 V, C_{LOAD} = 1 nF, V_{OUT}$<br>from 90% to 10%        |

1) Parameter is not subject to production test - verified by design/characterization

## 5 Application section

Infineon is providing this information as a courtesy only and without acknowledging any legal obligation. Information in the following application chapters is not part of the Infineon component specification, and Infineon does not warrant its accuracy or completeness. Infineon's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

The application circuits with a 2EP transformer driver can use a broad range of voltage rectification topologies. This application section will focus on the voltage doubler and peak rectification topologies. The voltage doubler rectification is a known topology in the industry to generate output voltages with a ratio of 2:1. Peak rectification with 50% duty cycle delivers output voltages with a ratio of 1:1. Combining peak rectification with the adjustable duty cycle of the 2EP enables a wide range of output voltage ratios.

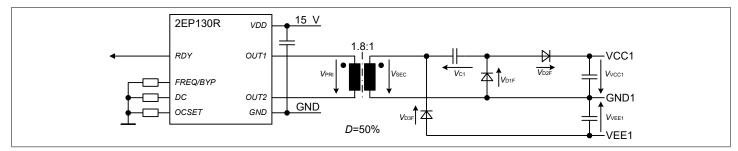

## 5.1 Theory of the 2EP1xxR using the voltage doubler topology

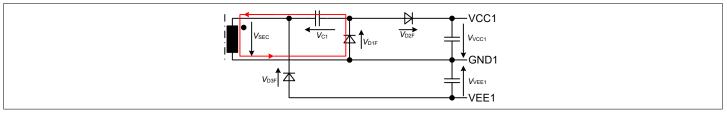

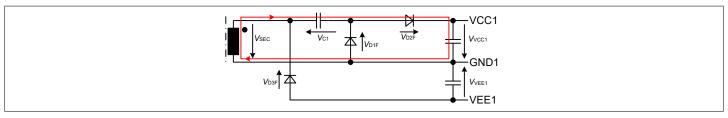

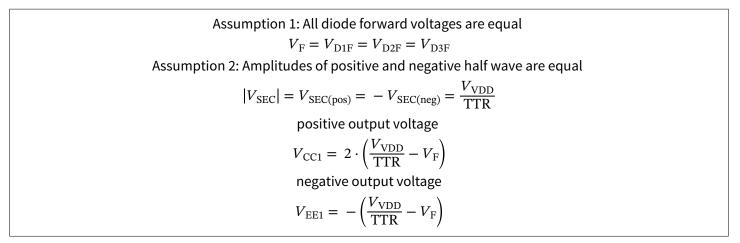

This section describes the theory behind the full-bridge power stage of 2EP1xxR together with the voltage doubler topology to provide two isolated output voltages. Each transformer output winding supports a positive and a negative output voltage. The positive output voltage has double the voltage level compared to the negative output voltage.

The voltage arrows indicate the polarity of the corresponding symbol used in the equations provided later.  $V_{PRI}$  and  $V_{SEC}$  represent the transformer voltages,  $V_{DxF}$  the individual diode forward voltages,  $V_{C1}$  the voltage of the voltage doubler capacitor (flying capacitor), and  $V_{VCC1}/V_{VEE1}$  the output voltage of one of the rails.

The following sections describe how to determine the output voltages of a voltage doubler topology connected to 2EP130R.

#### Full-bridge transformer driver 2EP130R

For output rectification using the voltage doubler topology, the configured duty cycle needs to be at 50%. 2EP130R chops the applied supply voltage,  $V_{VDD}$ , according to the configured switching frequency. The output of *OUT1* is switched between *VDD* and *GND*. The same is valid for *OUT2*. However, its switching pattern is inverted. This results in twice the amplitude of  $V_{VDD}$  across the outputs  $V_{OUT1,2}$ . In the schematic shown above, this voltage is referred to as the primary transformer voltage,  $V_{PRI}$ .

$V_{\rm PRI} = \pm V_{\rm VDD}$

## Transformer, transformer turn ratio (TTR), and transformer saturation

The transformer transforms the primary input voltage,  $V_{PRI}$ , to the secondary side voltage based on the transformer turn ratio (*TTR*). The secondary transformer voltage  $V_{SEC}$  is calculated as:

$$V_{\rm SEC} = \frac{V_{\rm PRI}}{TTR} = \pm \frac{V_{\rm VDD}}{TTR}$$

If the output voltages are loaded asymmetrically or the input duty cycle is not exactly at 50%, the transformer could drift into saturation. The evaluation board EVAL-2EP130R-VD includes, therefore, a series capacitor between *OUT1* and the primary winding. For the sake of simplification, this component is not shown nor considered in the calculations given in this section. This capacitor ensures an equal voltage×time product for primary winding. The equal voltage×time product prevents the transformer from saturating, even when driven with asymmetric loads.

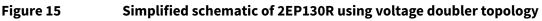

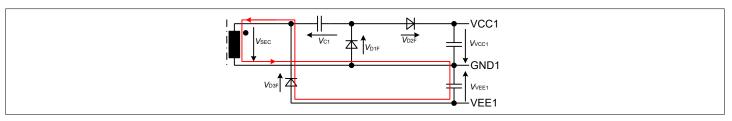

#### Voltage doubler current rectification

Due to the diodes in the voltage doubler circuit, individual current paths must be considered separately. The matching voltage polarity of the secondary transformer voltage must be applied only when calculating the expected output capacitor voltages.

#### Figure 16 Current path of the negative voltage rail

The current path to charge the negative voltage rail requires  $V_{SEC}$  to be in reverse polarity. The current charges the negative output voltage capacitor. The current then closes the circuit via diode D3 in the forward direction resulting in  $V_{D3F}$  voltage drop.

The negative output voltage results in:  $V_{\text{VEE1}} = V_{\text{SEC(neg)}} + V_{\text{D3F}}$

Since the secondary transformer voltage is negative at that half wave, the resulting output voltage is also negative but lowered by the diode's forward voltage.

The positive output voltage requires a two-step approach for the full output voltage. In the first step, the flying capacitor is charged. In the second step, this pre-charged capacitor boosts the voltage for a positive output rail.

#### Figure 17 Current path to charge the bootstrap capacitor of the positive voltage rail

The current path to charge the flying capacitor requires  $V_{SEC}$  to be in reverse polarity. The direction of current is the same as that for the negative output voltage. Therefore, the current during the negative half wave of the secondary winding is doubled compared to the positive half wave. The current flows through the diode, D1, resulting in  $V_{D1F}$  voltage drop. It then charges the flying capacitor before closing the circuit.

The flying capacitor, therefore, has a positive voltage that results in:  $V_{C1} = -V_{SEC(neg)} - V_{D1F}$

As the secondary transformer voltage is negative at that half wave, the resulting flying capacitor voltage, according to the indicated polarity, is positive but reduced by the diode's forward voltage.

#### Figure 18

Current path of the positive voltage rail via the bootstrap capacitor

The current path to finally charge the positive output voltage capacitor requires  $V_{SEC}$  to be in the indicated polarity (positive half wave). It has, therefore, the same polarity as the flying capacitor voltage,  $V_{C1}$ . The resulting current will pass through D2 resulting in a  $V_{D2F}$  voltage drop. It then charges the positive output voltage capacitor before closing the circuit.

The positive output voltage results in:  $V_{\text{VCC1}} = V_{\text{SEC(pos)}} + V_{\text{C1}} - V_{\text{D2F}}$

Both output voltages can then be written as:

Equation 1

#### Voltage doubler application impact

For simplicity the descriptions and formulas were derived for a single transformer output winding. But single rail voltage doubler output has asymmetric current during positive and negative half waves. These asymmetric currents create, at the input side, an asymmetric voltage drop across the resistive elements. The result is a non-equal voltage×time product for the positive and the negative voltage applied to the transformer. This will create a shift in the operating point at the B-H-curve with partial transformer saturation.

There are two ways to compensate for this shift:

**1.** A series capacitor at the primary side of the transformer to equalize the voltage×time product mismatch

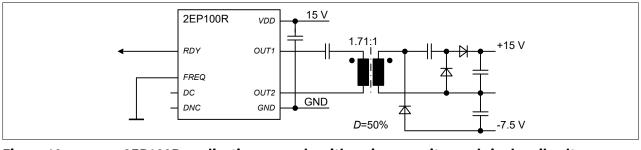

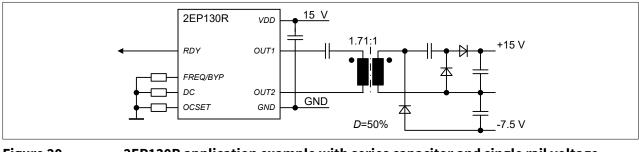

Figure 19

2EP100R application example with series capacitor and single rail voltage doubler

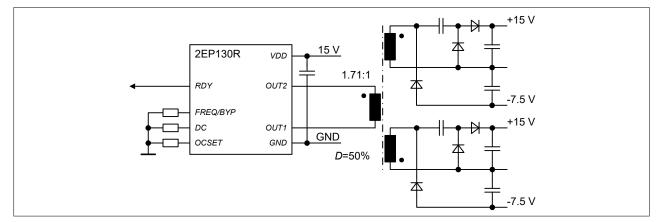

2EP130R application example with series capacitor and single rail voltage doubler

2. Different winding polarities for the two separate output rails in applications with equal loads and dual output transformer

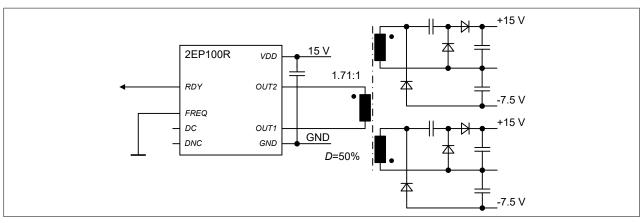

2EP100R application example with voltage doubler on two output rails

Figure 22 2EP130R application example with voltage doubler on two output rails

The voltage doubler topology with dual output transformer allows for the highest output current due to the interleaved current compensation. An additional series capacitor might still be needed for asymmetric load currents on the different rails.

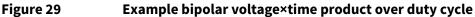

## 5.2 Theory of the 2EP1xxR using peak rectification topology

This section describes the theory behind the full-bridge power stage of 2EP1xxR and the peak rectification topology to provide two isolated output voltages. Each transformer output winding supports a positive and a negative output voltage. The ratio between the positive voltage and negative voltage is defined by the duty cycle.

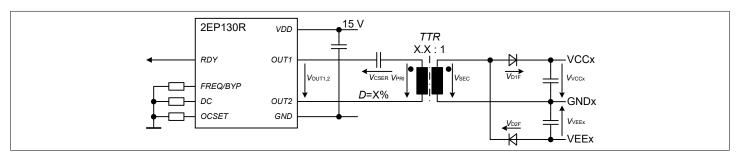

#### Figure 23 Simplified schematic of 2EP130R using peak rectification topology

The voltage arrows indicate the polarity of the corresponding symbol for use in the equations provided later.  $V_{PRI}$  and  $V_{SEC}$  represent the transformer voltages,  $V_{DxF}$  the individual diode forward voltages,  $V_{CSER}$  the voltage across the primary series capacitor, and  $V_{VCCx}/V_{VEEx}$  the output voltage.

The following sections describe how to determine the output voltages of a peak rectification according to:

the applied input voltage to 2EP

- the applied duty cycle by chopping the input voltage

- the level-shift (offset) of the series capacitor

- the transformer turn ratio

- the peak current rectification