32-bit TriCore™ AURIX™ TC3xx microcontroller

# About this document

#### Scope and purpose

This application note describes product safety mechanisms and the actions that must be taken by the product system integrator to ensure the correct operation of the device. This document should be read in conjunction with the AURIX<sup>™</sup> User's Manual and with the AURIX<sup>™</sup> Safety Manual. The associated source code includes methods for fault injection used for testing purposes, alarm triggering, and the implementation of various safety mechanisms listed in the Safety Manual.

# Attention:This document does not provide any code suitable for production. This document does not<br/>give a legally binding example for the implementation of safety-critical functions.

#### **Intended audience**

This application note is written for system engineers, software engineers, and functional safety managers involved in the design or development of a safety-related system who are considering integrating the AURIX<sup>™</sup> TC3xx microcontroller hardware as a Safety Element out of Context (SEooC) into their system.

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Table of contents

# **Table of contents**

| Abou    | t this document                                         | 1    |

|---------|---------------------------------------------------------|------|

| Table   | e of contents                                           | 2    |

| 1       | Introduction                                            |      |

| 1.1     | Key features                                            | 5    |

| 1.2     | Abbreviations and acronyms                              |      |

| 2       | Demonstrator presentation                               | 11   |

| 2.1     | Hardware                                                |      |

| 2.1.1   | Safe components                                         |      |

| 2.1.1.  |                                                         |      |

| 2.1.1.  |                                                         |      |

| 2.1.1.  |                                                         |      |

| 2.1.1.  | •                                                       |      |

| 2.1.2   | Default switch configuration                            |      |

| 2.1.3   | Application Kit - TC397 TFT LEDs                        |      |

| 2.2     | AURIX <sup>™</sup> MCU resource allocation              |      |

| 2.3     | Software overview                                       |      |

| 2.4     | Touch display interface presentation                    |      |

| 2.5     | ASCLIN shell interface                                  | 20   |

| 3       | Boot and startup procedure                              |      |

| 3.1     | Analog power-up                                         |      |

| 3.2     | Boot firmware                                           |      |

| 3.3     | Application SW startup                                  |      |

| 3.3.1   | Safety Kit implementation of the application SW startup |      |

| 3.3.2   | LBIST                                                   |      |

| 3.3.3   | MONBIST                                                 |      |

| 3.3.4   | Firmware check                                          | 27   |

| 3.3.4.  | 1 FW_CHECK implementation                               | 27   |

| 3.3.4.  | 2 Reset triggering                                      |      |

| 3.3.5   | MCU_STARTUP                                             |      |

| 3.3.6   | SMU ALIVE_ALARM_TEST                                    | 32   |

| 3.3.7   | SMU REG_MONITOR_TEST                                    |      |

| 3.3.8   | MBIST                                                   |      |

| 3.3.9   | Enable all SMU alarms                                   |      |

| 4       | Failure management                                      | 35   |

| 4.1     | Error management concept                                |      |

| 4.2     | SMU driver implementation                               |      |

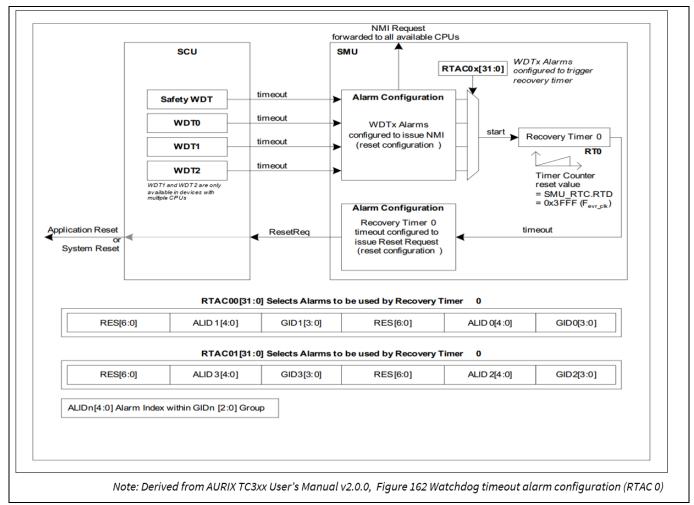

| 4.2.1   | Recovery Timer (RT) and watchdog alarms                 |      |

| 4.2.2   | Fault Signaling Protocol (FSP)                          |      |

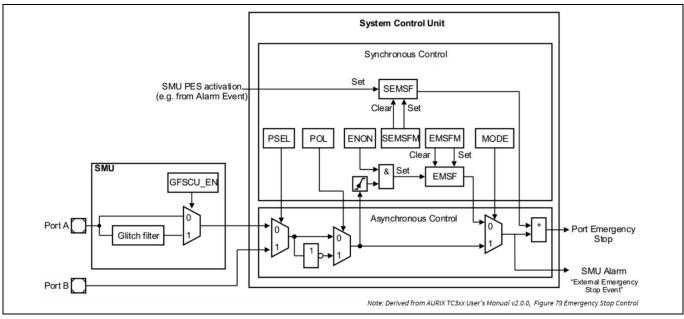

| 4.2.3   | Port Emergency Stop (PES)                               | 41   |

| 5       | System-level hardware requirements                      | 42   |

| 5.1     | External voltage supply                                 |      |

| 5.2     | Error monitoring                                        |      |

| 5.2.1   | FSP activation                                          |      |

| 5.2.2   | Emergency Stop activation                               |      |

| 5.2.3   | Application software notification via NMI or ISR        |      |

| 5.3     | External time-window watchdog                           |      |

| Applica | ation note 2                                            | V1.0 |

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Table of contents

| 6        | Architecture for management of faults          | 47 |

|----------|------------------------------------------------|----|

| 6.1      | Self-tests for latent fault metric support     | 47 |

| 6.1.1    | Power built-in self-test (PBIST)               | 47 |

| 6.1.2    | Logic built-in self-test (LBIST)               | 47 |

| 6.1.3    | Monitor built-in self-test (MONBIST)           | 48 |

| 6.1.4    | Memory built-in self-test (MBIST)              | 48 |

| 6.2      | Functional blocks and safety-related functions | 50 |

| 6.2.1    | MCU function - processing                      | 50 |

| 6.2.1.   | 1 CPU                                          | 50 |

| 6.2.1.   | 2 Processing – FCE                             | 54 |

| 6.2.1.   | 3 Processing - system timer (STM)              | 55 |

| 6.2.1.   | 4 Processing – HSM                             | 56 |

| 6.2.2    | MCU function – Non-volatile memory             | 57 |

| 6.2.2.   | 1 PFlash NVM                                   | 57 |

| 6.2.3    | MCU function – Volatile memory                 |    |

| 6.2.3.   | 1 Extension Memory (EMEM)                      | 62 |

| 6.2.3.   | 2 LMU                                          | 64 |

| 6.2.3.   | 3 SRAM                                         | 64 |

| 6.2.3.   | 4 Default Application Memory (DAM)             | 66 |

| 6.2.3.   |                                                |    |

| 6.2.4    | MCU function – ADAS                            |    |

| 6.2.5    | MCU function - interconnect                    |    |

| 6.2.5.   |                                                |    |

| 6.2.6    | MCU function – Communication                   |    |

| 6.2.7    | Direct Memory Access (DMA)                     |    |

| 6.2.7.   |                                                |    |

| 6.2.8    | MCU function – Infrastructure                  |    |

| 6.2.8.   |                                                |    |

| 6.2.8.   |                                                |    |

| 6.2.8.   |                                                |    |

| 6.2.8.   |                                                |    |

| 6.2.8.   |                                                |    |

| 6.2.8.   |                                                |    |

| 6.2.9    | MCU function – Interfaces                      |    |

| 6.2.9.   |                                                |    |

| 6.2.9.   |                                                |    |

| 6.2.9.   |                                                |    |

| 6.2.10   |                                                |    |

| 6.2.10   | -                                              |    |

| 6.2.10   | • • •                                          |    |

| 6.2.11   |                                                |    |

| 6.2.11   |                                                |    |

| 6.2.11   |                                                |    |

| 6.2.11   | - · · ·                                        |    |

| 6.2.12   |                                                |    |

| 6.2.12   | • • •                                          |    |

| 6.2.13   | =                                              |    |

| 6.2.13   |                                                |    |

| J. Z. I. |                                                |    |

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Table of contents

| References       |  |

|------------------|--|

| Revision history |  |

| Disclaimer       |  |

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Introduction

# 1 Introduction

The development of a safe application can be a challenge when it comes to following strict safety rules. To ease the development of such applications, Infineon provides the TC3xx Safety Manual. The Safety Manual defines the safety mechanisms as an activity or a technical solution to avoid or control systematic failures and to detect random hardware failures or control random hardware failures.

Safety mechanisms are classified in two main types:

- The technical solution, which is internal to the microcontroller by hardware (HW) or software (SW)

- The technical solution, which is either in HW or SW, implemented at the system level by the system integrator

During the design phase of AURIX<sup>™</sup> MCUs, the most common use cases have been taken into account, and safety requirements have been derived from these. For the implementation of these specific safety-related functions, different SMs must be implemented according to the specification in the Safety Manual. The specific SM is required depends on the modules used and the safety level required.

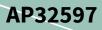

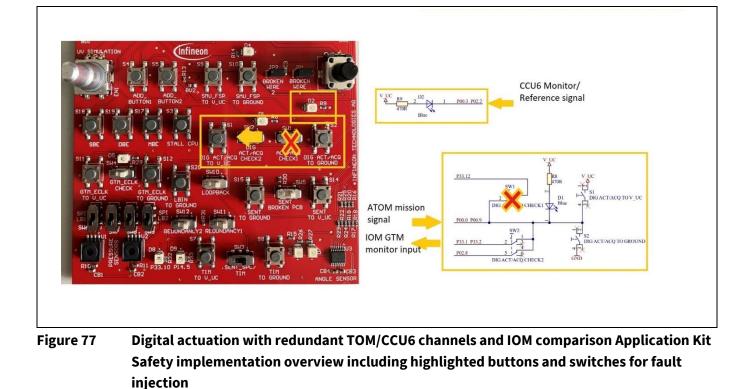

The intention of this application note is to provide implementation hints and code examples for many of these safety mechanisms. Therefore, this document is provided with example software optimized for the Application Kit Safety hardware, which is composed of an Application Kit - AURIX<sup>™</sup> TC397 TFT (KIT\_A2G\_TC397\_5V\_TFT) from Infineon and the new Safety Demo Add-on Shield Board, which is called "Evaluation Board - AURIX<sup>™</sup> TC3xx Safety" (EVABOARD\_A2G\_SAFETY) and the combination of both is called "AURIX<sup>™</sup> Application Kit - TC3xx Safety" (APPKIT\_A2G\_SAFETY). The kit is used for demonstrating the implementation of the safety mechanisms and other diagnostics information.

In addition to the touchscreen and an ASCLIN shell interface, the add-on shield provides several buttons and switches to trigger the injection of faults into the system. An overview of all safety-related functions and SMs covered by the application note can be found in the tables ranging from Table 1 to Table 6.

## 1.1 Key features

The following key features are implemented and supported:

- Boot and startup procedure including all safety mechanisms involved

- Full SMU driver implementation including the following:

- SMU core and SMU standby

- Fault Signaling Protocol (FSP)

- Emergency stop (ES)

- Recovery timer (RT)

- Implementation of safety-related functions and the required safety mechanisms

- Fault injection for testing of various safety mechanisms:

- PFlash ECC error injection

- DMA error injection

- Analog and digital acquisition error injection

- Undervoltage error injection

- Broken wire, etc.

- TFT touchscreen driver

Application note

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Introduction

- TLF35584 PMIC driver

- ASCLIN shell interface

- STM used for basic task scheduling

#### Table 1 Overview of Safety Related Functions covered by this application note

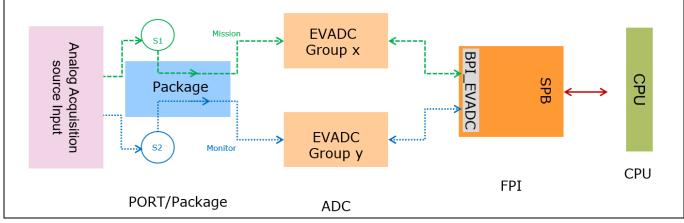

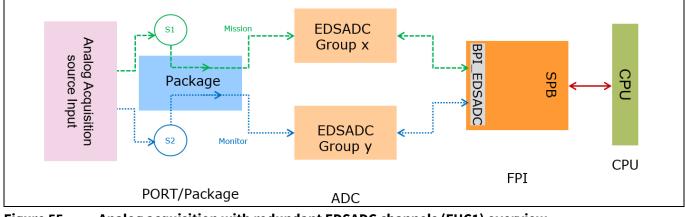

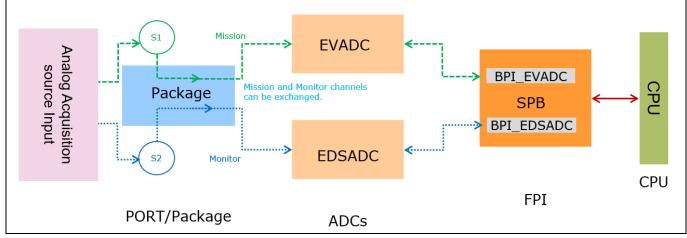

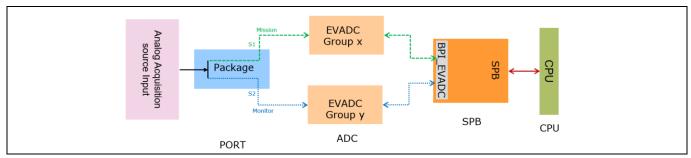

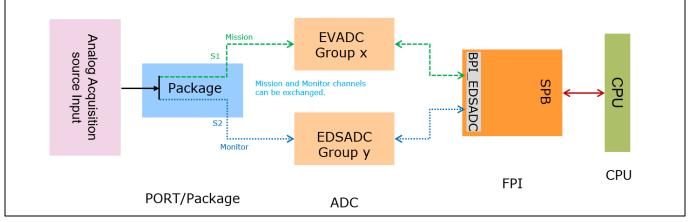

| Safe computation       Yes       • Safety Mechanism AMU*:*         Safety Mechanism CPU.*:*       • Safety Mechanism STM:*         • Safety Mechanism *       • Safety Mechanism MMU*:*         • Safety Mechanism *       • Safety Mechanism DMA.*:*         • Safety Mechanism DMA.*:*       • Safety Mechanism EMEM*:*         • Safety Mechanism EMEM*:*       • Safety Mechanism EMEM*:*         • Safety Mechanism SIM*:*       • Safety Mechanism SIM*:*         Analog acquisition       Yes         Yes       • FUC 0: Analog acquisition with redundant EVADC channels         • FUC 1: Analog acquisition with redundant EDSADC channels       • FUC 2: Analog acquisition with redundant EDSADC channels         • FUC 2: Single analog acquisition with one EVADC channels       • FUC 3: Single analog acquisition with one EDSADC and one EVADC channel         • FUC 4: Single analog acquisition with redundant TIM/TIM channels       • FUC 4: Single analog acquisition with redundant CCU6/TII channels         • FUC 2: Digital acquisition with redundant CCU6/TII channels       • FUC 1: Digital acquisition with redundant CCU6/TII channels         • FUC 2: Digital acquisition with redundant CCU6/TII channels and IOM comparison       • FUC 1: Digital acquisition with redundant CCU6/TII channels and IOM comparison         • FUC 2: Digital acquisition with redundant TOM channels and IOM comparison       • FUC 1: Digital actuation with redundant TOM channels and IOM comparison         • FUC 2 | Safety Related Function | Covered<br>(Yes/Partly/No) | Covered SMs/Functional Use Case (FUC)                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| channelsFUC 1: Analog acquisition with redundant EDSADC<br>channelsFUC 2: Analog acquisition with one EVADC channel<br>and one EDSADC channelFUC 3: Single analog acquisition with EVADC<br>channelsFUC 4: Single analog acquisition with none EDSADC<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Safe computation        |                            | <ul> <li>Safety Mechanism CPU.*:*</li> <li>Safety Mechanism STM:*</li> <li>Safety Mechanism *</li> <li>Safety Mechanism DMA.*:*</li> <li>Safety Mechanism NVM.*:*</li> <li>Safety Mechanism EMEM*:*</li> <li>Safety Mechanism LMU*:*</li> </ul>                                                                                                        |

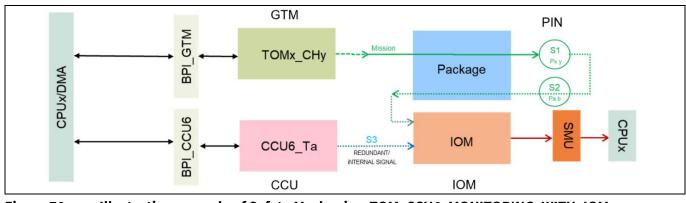

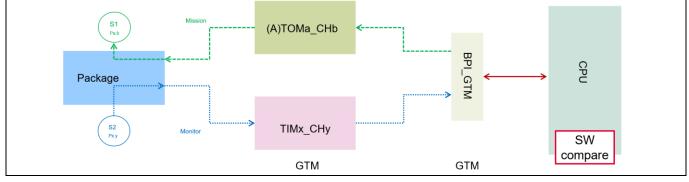

| channels       FUC 1: Digital acquisition with redundant CCU6/TII channels         FUC 2: Digital acquisition with redundant CCU6/GPT12 channels       FUC 2: Digital acquisition with redundant CCU6/GPT12 channels         Digital actuation       Yes       FUC 0: Digital actuation with redundant TOM channels and IOM comparison         FUC 1: Digital actuation with redundant TOM/CCU6 channels and IOM comparison       FUC 1: Digital actuation with redundant TOM/CCU6 channels and IOM comparison         FUC 2: Digital actuation with redundant TOM/TIM channels and application SW comparison       FUC 3: Digital actuation with redundant CCU6/GPT12 channels and application SW comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Analog acquisition      | Yes                        | <ul> <li>FUC 0: Analog acquisition with redundant EVADC channels</li> <li>FUC 1: Analog acquisition with redundant EDSADC channels</li> <li>FUC 2: Analog acquisition with one EVADC channel and one EDSADC channel</li> <li>FUC 3: Single analog acquisition with EVADC channels</li> <li>FUC 4: Single analog acquisition with one EDSADC</li> </ul> |

| <ul> <li>channels and IOM comparison</li> <li>FUC 1: Digital actuation with redundant TOM/CCUE channels and IOM comparison</li> <li>FUC 2: Digital actuation with redundant TOM/TIM channels and application SW comparison</li> <li>FUC 3: Digital actuation with redundant CCU6/GPT12 channels and application SW comparison</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Digital acquisition     | Yes                        | <ul> <li>channels</li> <li>FUC 1: Digital acquisition with redundant CCU6/TIM channels</li> <li>FUC 2: Digital acquisition with redundant</li> </ul>                                                                                                                                                                                                   |

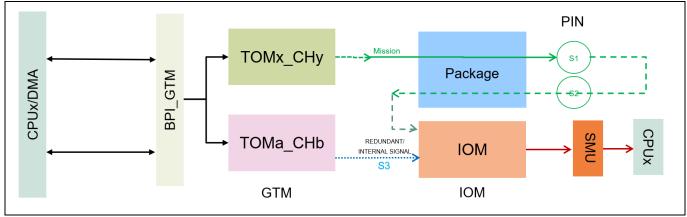

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Digital actuation       | Yes                        | <ul> <li>channels and IOM comparison</li> <li>FUC 1: Digital actuation with redundant TOM/CCU6 channels and IOM comparison</li> <li>FUC 2: Digital actuation with redundant TOM/TIM channels and application SW comparison</li> <li>FUC 3: Digital actuation with redundant CCU6/GPT12 channels and application SW</li> </ul>                          |

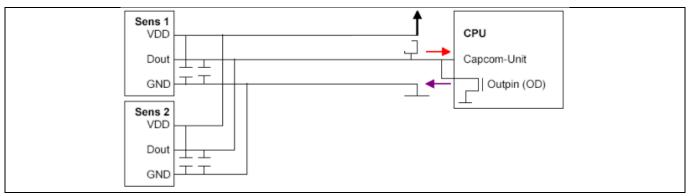

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <br>Sensor acquisition  | Partly                     | Safety mechanism SENT:CHANNEL_REDUNDANCY                                                                                                                                                                                                                                                                                                               |

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Introduction

| Safety Related Function                         | Covered<br>(Yes/Partly/No) | Covered SMs/Functional Use Case (FUC)                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

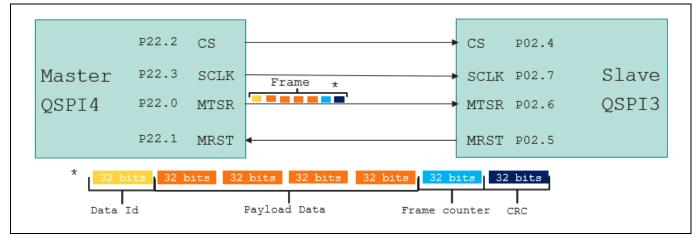

| External communication                          | Partly                     | Safety mechanism QSPI:SAFE_COMMUNICATION                                                                                                                                                                                                                                                                                                                                                                                         |

| Avoidance or detection of common-cause failures | Partly                     | <ul> <li>Safety mechanism<br/>PMS:VEXT_VEVRSB_ABS_RATINGS</li> <li>Safety mechanism<br/>PMS:VEXT_VEVRSB_OVERVOLTAGE</li> <li>Safety mechanism PMS:VX_FILTER</li> <li>Safety mechanism :DTS_RESULT</li> <li>Safety mechanism WATCHDOG_FUNCTION</li> <li>Safety mechanism CLOCK:PLAUSIBILITY</li> <li>Safety mechanism MONBIST_RESULT</li> <li>Safety mechanism PORT:LOOPBACK</li> <li>Safety mechanism PORT:REDUNDANCY</li> </ul> |

| Safe state support                              | Partly                     | <ul> <li>Internal failure reporting</li> <li>External failure reporting (FSP)</li> <li>Alternate failure reporting (As<br/>FSP_ERROR_PIN_MONITOR is implemented)</li> </ul>                                                                                                                                                                                                                                                      |

| Coexistence of HW/SW elements                   | Yes                        | Safety mechanism ISR_MONITOR                                                                                                                                                                                                                                                                                                                                                                                                     |

#### Table 2 Overview of implemented Safety Mechanisms - Safe startup

| Safety Mechanism (SM) | App. Note section | C function name            |

|-----------------------|-------------------|----------------------------|

| LBIST_CFG             | 3.3.2 & 6.1.2     | safetyKitSswLbist          |

| LBIST_MONITOR         | 3.3.2 & 6.1.2     | safetyKitSswLbist          |

| LBIST_RESULT          | 3.3.2 & 6.1.2     | safetyKitSswLbist          |

| MONBIST_CFG           | 3.3.3 & 6.1.3     | Ifx_Ssw_Monbist            |

| MONBIST_RESULT        | 3.3.3 & 6.1.3     | Ifx_Ssw_Monbist            |

| MCU_FW_CHECK          | 3.3.4             | safetyKitSswMcuFwCheck     |

| MCU_STARTUP           | 3.3.5             | safetyKitSswMcuStartup     |

| ALIVE_ALARM_TEST      | 3.3.6             | safetyKitSswAliveAlarmTest |

| REG_MONITOR_TEST      | 3.3.7             | safetyKitSswRegMonitorTest |

| MBIST                 | 3.3.8 & 6.1.4     | safetyKitSswMbist          |

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Introduction

| Safety Mechanism (SM)     | App. note section | C function name                                      |

|---------------------------|-------------------|------------------------------------------------------|

| CONVCTRL:CONFIG_CHECK     | 6.2.10            | initCONVCTRL                                         |

| EVADC:CONFIG_CHECK        | 6.2.10            | initEVADCGroups                                      |

| EVADC:DIVERSE_REDUNDANCY  | 6.2.10            | initAAcqFuc0<br>initAAcqFuc2<br>initAAcqFuc4BrokenWR |

| EVADC:PLAUSIBILITY        | 6.2.10            | plausibilityCheck                                    |

| EVADC:VAREF_PLAUSIBILITY  | 6.2.10            | evadcVarefPlausibilityCheck                          |

| EDSADC:DIVERSE_REDUNDANCY | 6.2.10            | initAAcqFuc1<br>initAAcqFuc2<br>initAAcqFuc4BrokenWR |

| EDSADC:PLAUSIBILITY       | 6.2.10            | plausibilityCheck                                    |

| EDSADC:VAREF_PLAUSIBILITY | 6.2.10            | edsadcVarefPlausibilityCheck                         |

#### Table 3 Overview of implemented Safety Mechanisms - Analog acquisition

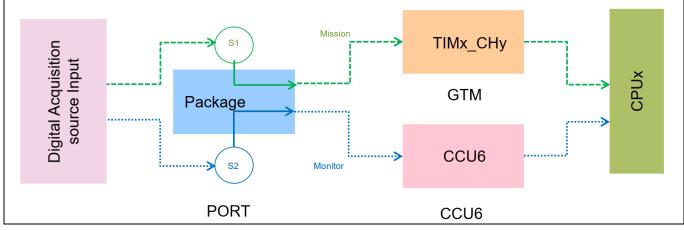

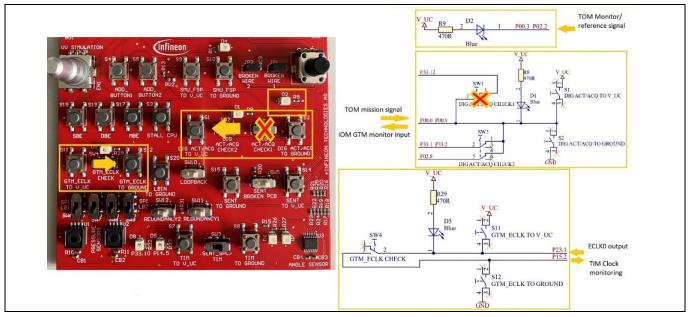

#### Table 4 Overview of implemented Safety Mechanisms - Digital acquisition

| Safety Mechanism          | App. note section | C function name          |

|---------------------------|-------------------|--------------------------|

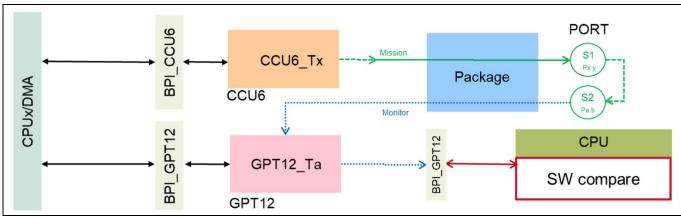

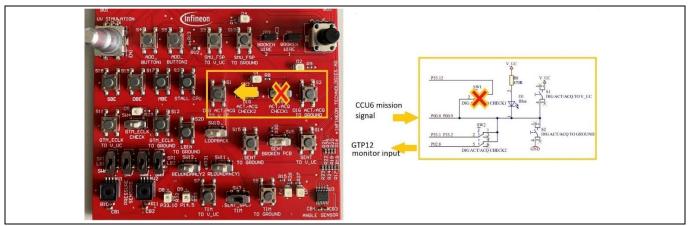

| TIM_REDUNDANCY            | 6.2.11 & 6.2.11.2 | checkRedundancyGTMTIM    |

| GTM_CCU6_REDUNDANCY       | 6.2.11 & 6.2.11.2 | checkRedundancyTIMCCU6   |

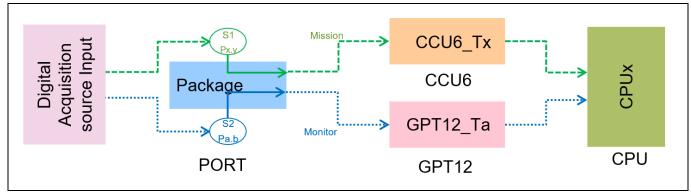

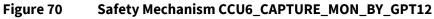

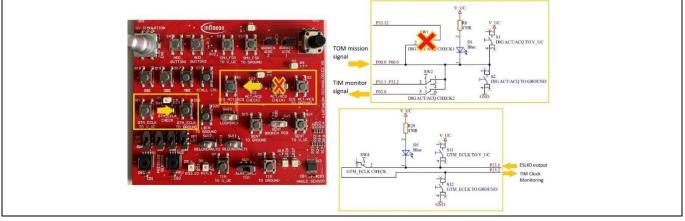

| CCU6_CAPTURE_MON_BY_GPT12 | 6.2.11 & 6.2.11.2 | plausibiltyCheckDAcqFuc2 |

| TIM_CLOCK_MONITORING      | 6.2.11 & 6.2.11.2 | initEclkMonitoring       |

#### Table 5 Overview of implemented Safety Mechanisms - Digital actuation

| Safety Mechanism      | App. note section | C function name             |

|-----------------------|-------------------|-----------------------------|

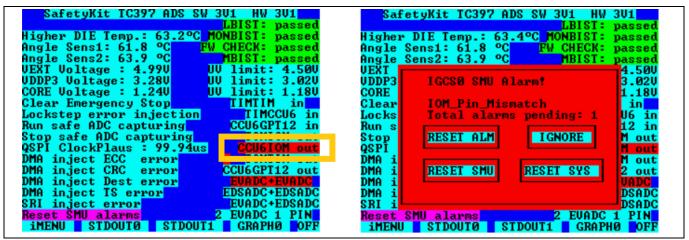

| IOM_ALARM_CHECK       | 6.2.11 & 6.2.11.3 | alarmCheckGTMIOM            |

| CCU6_GPT12_MONITORING | 6.2.11 & 6.2.11.3 | plausibilityCheckDActFuc3   |

| TIM_CLOCK_MONITORING  | 6.2.11 & 6.2.11.3 | initEclkMonitoring          |

| TOM_TIM_MONITORING    | 6.2.11 & 6.2.11.3 | gtmTimPwmMissionIsrDActFuc2 |

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Introduction

| Table 6 Ov | verview of implemented Safety Mechanisms – Other |

|------------|--------------------------------------------------|

|------------|--------------------------------------------------|

| Safety Mechanism                  | App. note section | C function name                                                                 |

|-----------------------------------|-------------------|---------------------------------------------------------------------------------|

| *.*:REG_MONITOR_TEST              | 6.2.3.3           | safetyKitRunRegMonitorTest                                                      |

| DMA: *                            | 6.2.7             | initAndRunDmaTransaction                                                        |

| DTS_CFG                           | 6.2.8.6           | initDieTemperatureSensors                                                       |

| DTS_RESULT                        | 6.2.8.6           | dtsMeasurementISR                                                               |

| CONVCTRL:ALARM_CHECK              | 6.2.10            | initCONVCTRL                                                                    |

| APPLICATION_SW_ALARM              | 6.2.13.1          | softwareCoreAlarmTriggerSMU                                                     |

| STM:MONITOR                       | 6.2.1.3           | runStmMonitoring                                                                |

| CLOCK:OSC_MONITOR                 | 6.2.8.2           | lfxScuCcu_init                                                                  |

| GTM_CONFIG_FOR_GTM                | 6.2.11 & 6.2.11.2 | initDAcqFuc0                                                                    |

| IOM_CONFIG_FOR_GTM                | 6.2.11 & 6.2.11.3 | initDActFuc0                                                                    |

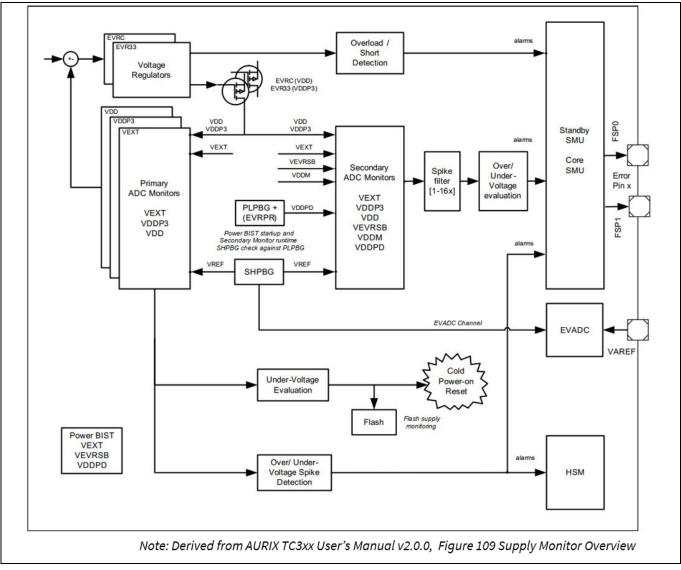

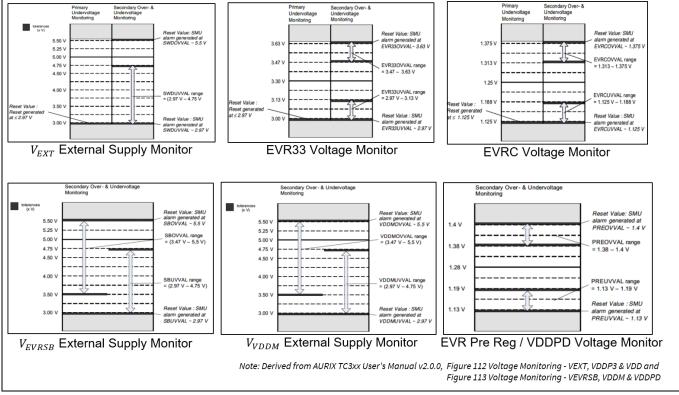

| MON_REDUNDANCY_CFG                | 6.2.8.1           | initVoltageMonitors                                                             |

| VX_MONITOR_CFG                    | 6.2.8.1           | initVoltageMonitors                                                             |

| SMU:CONFIG                        | 4 & 6.2.13.1      | initSMUModule<br>enableFSPcoreSMU<br>enableFSPstdbySMU                          |

| PFLASH: *                         | 6.2.2.1           | runInterityCheckPFLASH,<br>runUpdateCheckPFLASH,<br>runWordlineFailDetectPFLASH |

| EMEM:DATA_INTEGRITY               | 6.2.3.1           | runDataIntegrityEMEM                                                            |

| ISR_MONITOR                       | 6.2.7.1           | isrMonitor                                                                      |

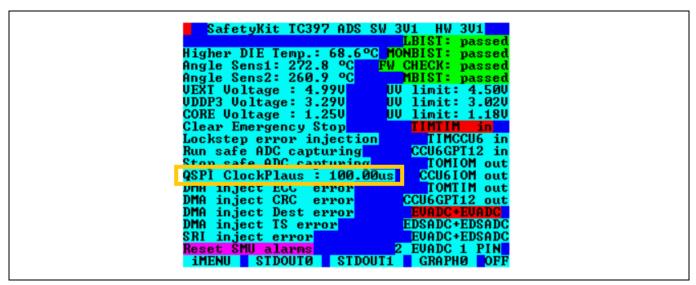

| CLOCK:PLAUSIBILITY                | 6.2.8.2           | initQSPI5ClockPlausibility                                                      |

| QSPI:SAFE_COMMUNICATION           | 6.2.9.1           | initQSPISafeCommunication                                                       |

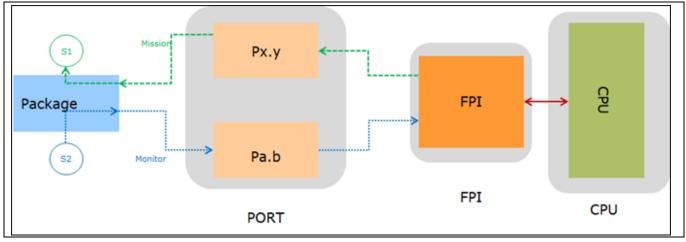

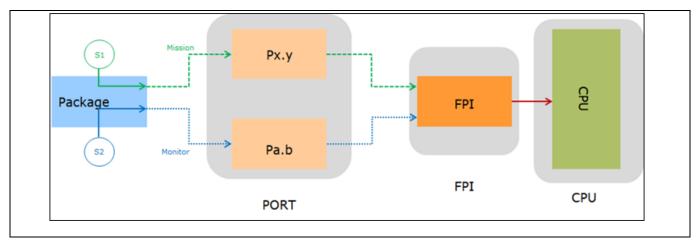

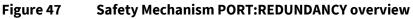

| PORT:LOOPBACK,<br>PORT:REDUNDANCY | 6.2.9.2           | runPortLoopback,<br>runPortRedundancy                                           |

| SENT:CHANNEL_REDUNDANCY           | 6.2.9.3           | initTLE5012Modules<br>checkRedundancySENT                                       |

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Introduction

#### **1.2** Abbreviations and acronyms

- Note: For a list of abbreviations, acronyms, and safety-related definitions, see [1], [2], [3], and [4].

- Note: In this document, the AURIX<sup>™</sup> Application Kit TC3xx Safety is also referred to as "Application Kit Safety" or "Safety Kit". Also, "Evaluation Board AURIX<sup>™</sup> TC3xx Safety" is also called "Safety Evaluation Board" or "Evaluation Board".

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Demonstrator presentation

# 2 Demonstrator presentation

#### 2.1 Hardware

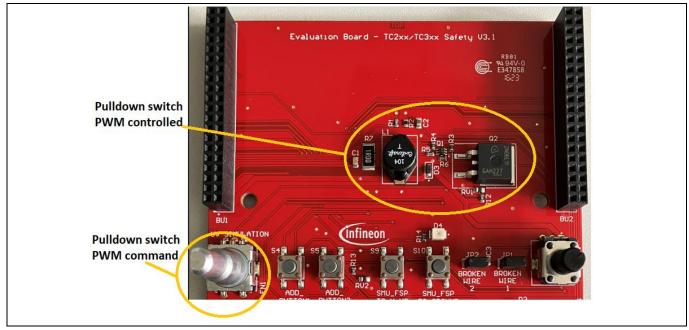

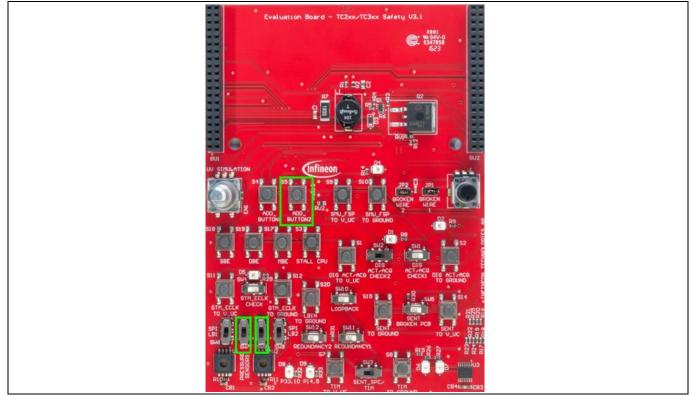

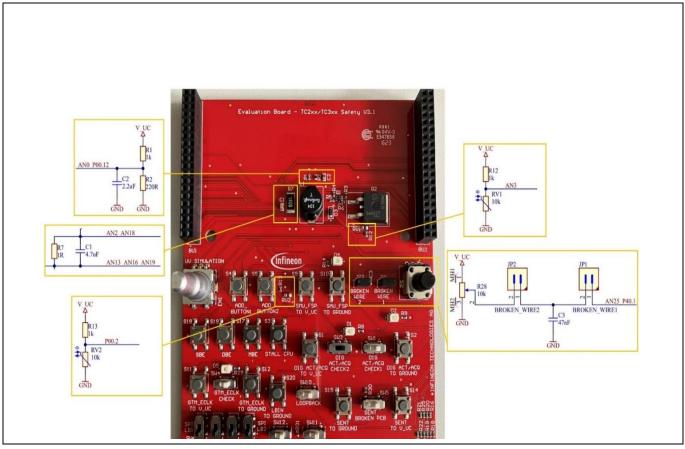

The dedicated full name of the demonstrator is "AURIX<sup>™</sup> Application Kit - TC3xx Safety" and it is composed of two PCBs:

- Application Kit AURIX<sup>™</sup> TC397 TFT (KIT\_A2G\_TC397\_5V\_TFT)

- Evaluation Board AURIX<sup>™</sup> TC3xx Safety (EVABOARD\_A2G\_SAFETY)

The Application Kit - AURIX<sup>™</sup> TC397 TFT itself features a TC397 microcontroller, a TFT touch display, and a TLF35584 safe system power supply. The add-on Evaluation Board - AURIX<sup>™</sup> TC3xx Safety is composed of multiple additional sensors, undervoltage protection circuitry, buttons, and switches allowing to demonstrate the behavior of AURIX<sup>™</sup> MCUs in the presence of a fault. Different faults such as a lockstep error can be directly injected through the touch display of the Application Kit - AURIX<sup>™</sup> TC397 TFT, PFlash error can be injected via a dedicated button on the Evaluation Board.

Note: Do not run the demo without the Evaluation Board - AURIX<sup>™</sup> TC3xx Safety (add-on shield board) as multiple alarms will be reported.

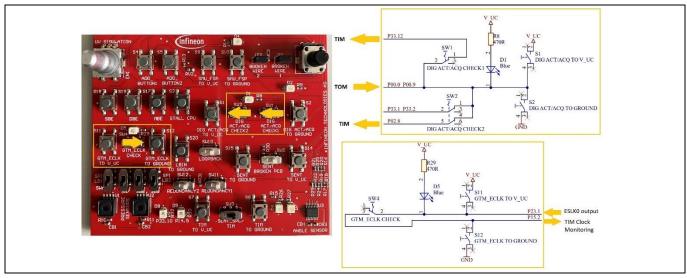

#### Figure 1 shows the board with dedicated naming.

Figure 1 AURIX<sup>™</sup> Application Kit - TC3xx Safety

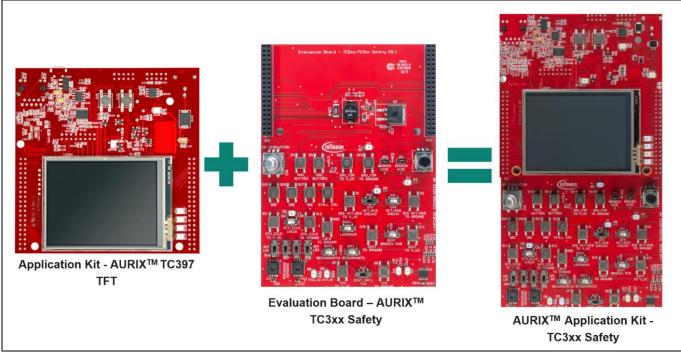

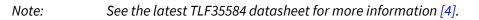

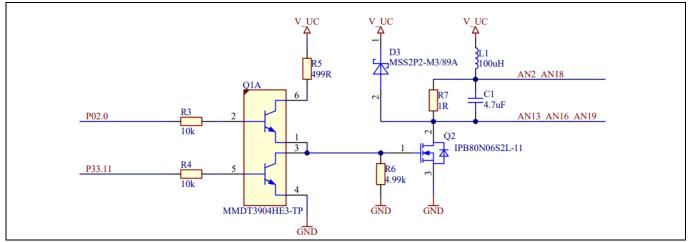

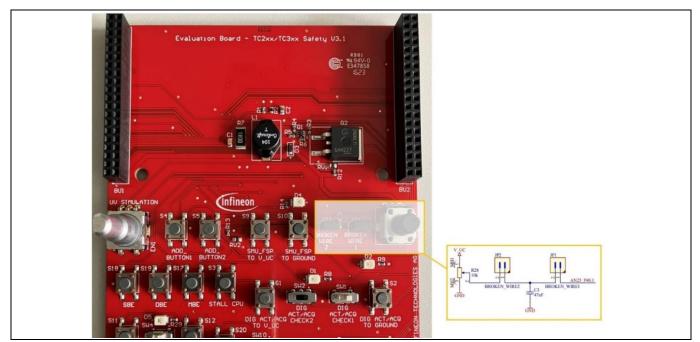

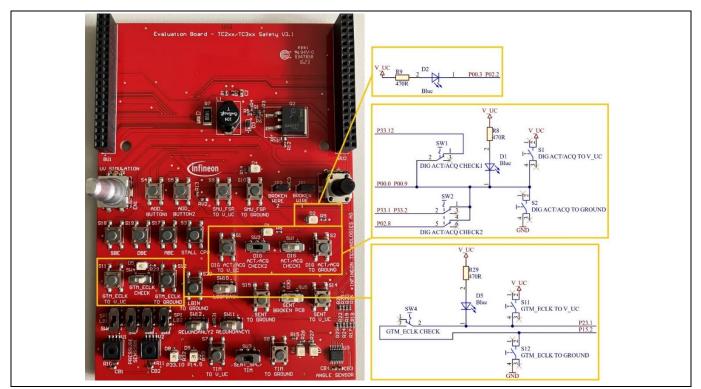

Figure 2 shows the schematic of Evaluation Board - AURIX<sup>™</sup> TC3xx Safety. See the Application Kit Manual TC3x7 for the schematic of Application Kit - AURIX<sup>™</sup> TC397 TFT.

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Demonstrator presentation

Figure 2 Schematic of Evaluation Board - AURIX<sup>™</sup> TC3xx Safety (add-on shield board)

## 2.1.1 Safe components

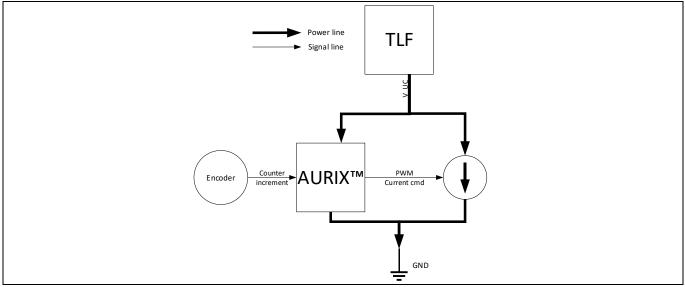

Application Kit - AURIX<sup>™</sup> TC397 TFT including TLF35584 itself has been designed to follow the safety guidelines. To demonstrate the safety application capability, the Safety Evaluation Board also contains other safety components, such as sensors and actuators. The following section provides a detailed overview of all components available on both PCBs.

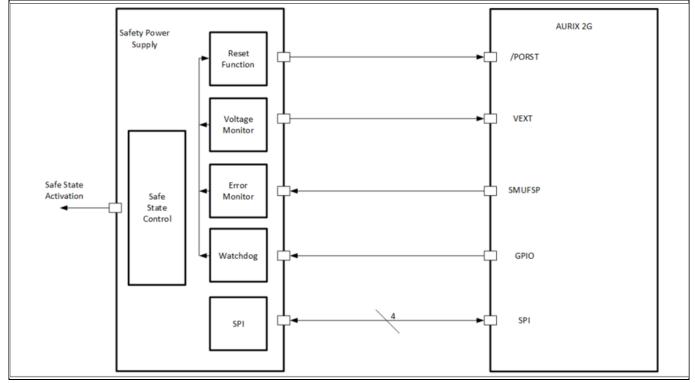

## 2.1.1.1 TLF35584 power supply

TLF35584 is a multi-voltage safety supply for safety-relevant applications supplying 5 V or 3.3 V MCUs, transceivers, and sensors by an efficient and flexible pre-/post-regulator concept over a wide input voltage range. The multiple built-in safety features enable easy realization of microcontroller applications, fulfilling the highest Automotive Safety Integrity Level (ASIL-D):

- Independent voltage monitoring block with reset function

- Configurable functional and window watchdog

- Error monitoring

- 16-bit SPI interface

- Safe state control with two safe state signals with programmable delay

- Input voltage monitoring (overvoltage switch-off)

Application note

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Demonstrator presentation

TLF35584 provides a windowed or question-and-answer watchdog; it must be configured for the required functionality. The application configures the power supply via SPI; by default, TLF35584 will start as a windowed watchdog via SPI. If not triggered, it will reset the system. The chip provides different voltages for ADC reference, communication, controller supply, and other functionalities. SPI communication to and from TLF35584 is protected with an odd parity bit.

See Section 5.1 for more information on the usage of TLF35584. See the latest datasheet for more information about TLF35584 [4].

Note: TLF35584 provides a Microcontroller Programming Support (MPS) mode, which is enabled by default via a hardware pull-up of the TLF35584 MPS pin to 5 V on the evaluation board. While being in MPS mode, the contribution of a watchdog or error monitoring failure to an AURIX™ reset via ROT is blocked.

#### 2.1.1.2 TLE5102BD E9200 magnetic angle sensor

TLE5102BD magnetic angle sensor is a dual-die position sensor based on the giant magnetoresistance (GMR) effect. All connections and sensors are implemented twice. The sensor supports various interfaces to a controller, such as SPC (based on SENT SAE J2716), SPI, Hall, incremental interface, and PWM. SPC and SPI communication is end-to-end protected with a CRC checksum. SPI can be used in parallel with the other interfaces.

By default, the magnetic angle sensor is configured to the SPC interface mode but can be reconfigured to the necessary interface at runtime using SPI. For more information, see the TLE5102 BD datasheet.

## 2.1.1.3 KP256 pressure sensor

The KP256 pressure sensor is connected to the microcontroller via SPI. It also houses a temperature sensor. The communication is protected with an odd parity bit. This sensor demonstrates the QSPI redundancy for future use case.

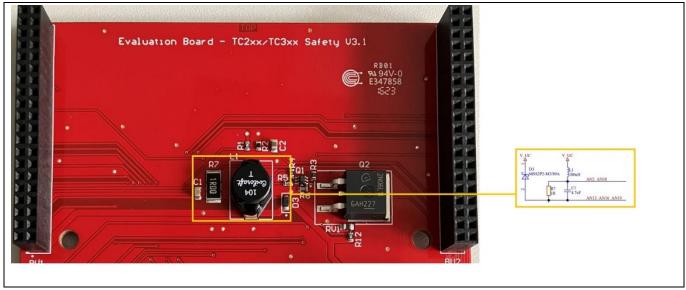

## 2.1.1.4 Other Safety Board components

- Pin-to-pin circuitry with switches to inject hardware faults

- Redundant temperature sensors for safe analog measurement demonstration

- Potentiometer with switch for analog measurement with hardware fault injection

- Encoder

- Single Bit Error (SBE), Double Bit Error (DBE) and Multiple Bit Error (MBE) buttons to inject NVM PFlash error

- Debug LEDs for different purposes

- Action switches (error pin, Emergency Stop, etc.)

- Current pump circuitry to demonstrate undervoltage safety mechanisms

- Four parallel switches to change the functionality between pressure sensor and safe QSPI communication (where two QSPI of the AURIX<sup>™</sup> TC3xx MCU are connected with each other (loopback) to simulate a safe communication safety mechanism)

- Connector for broken-wire case simulation

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Demonstrator presentation

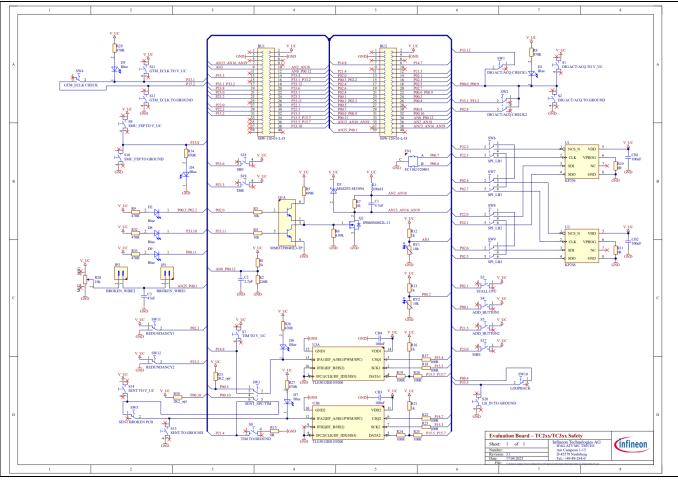

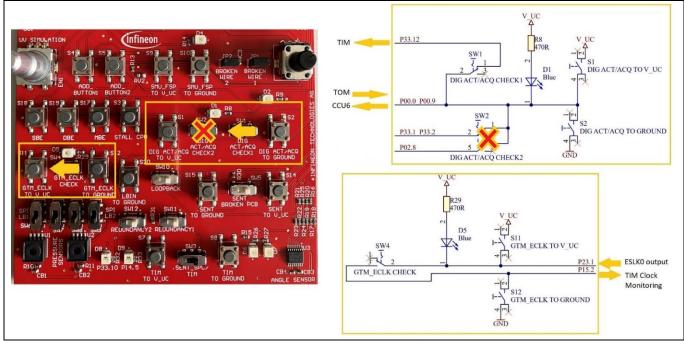

#### 2.1.2 Default switch configuration

This section describes the default hardware configuration where no fault injection is active. In general, the default switch configuration does not interrupt each signal.

#### Attention: This default configuration must be observed to avoid any unintended alarm directly after poweron reset.

| Switch | Default state                      | Comment                          |

|--------|------------------------------------|----------------------------------|

| SW1    | Right                              | Used                             |

| SW2    | Right                              | Used                             |

| SW3    | Right                              | Do not care/not used             |

| SW4    | Left                               | Used                             |

| SW5    | Right                              | SENT/SPC                         |

| SW6    | Down                               | Used                             |

| SW7    | Down                               | Used                             |

| SW8    | Down                               | Used                             |

| SW9    | Down                               | Used                             |

| SW10   | Right                              | Used                             |

| SW11   | Right                              | Used                             |

| SW12   | Right                              | Used                             |

| D1     | On/~50% brightness                 | PWM out                          |

| D2     | Depends on the selected IO example | On when running the TOM_IOM demo |

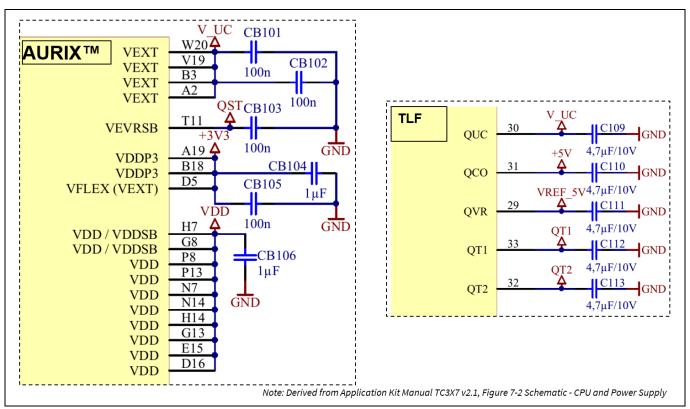

| D4     | On brightness                      | SMU_FSP                          |

| D5     | On/50% brightness                  | GTM_EXCLK                        |

| D6     | On                                 | SENT Protocol                    |

| D7     | On                                 | SENT Protocol                    |

| D8     | Off                                | Spare                            |

| D9     | Toggling                           | QSPI Protocol                    |

| JP1    | Connected                          | BWD                              |

| JP2    | Connected                          | BWD                              |

#### Table 7 Default state of switches and LEDs

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Demonstrator presentation

Figure 3 Default state of switches and jumper on the Evaluation Board - AURIX™ TC3xx Safety

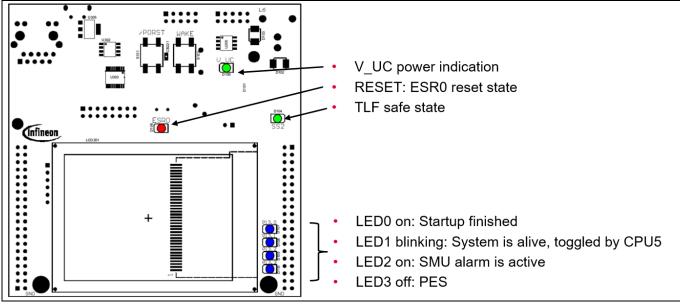

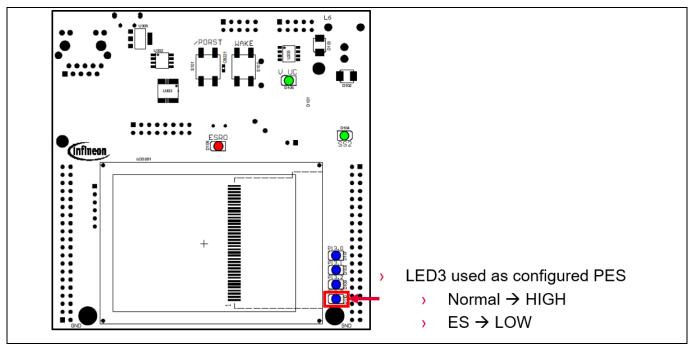

# 2.1.3 Application Kit - TC397 TFT LEDs

Application Kit - TC397 TFT offers four LEDs (D107 to D110) which can be used by the application software. For Application Kit Safety, they are used for the following purposes:

- LED0 (D107): Signals the successful initialization of the application software

- LED1 (D108): Life hold indication, blinking serviced by CPU5.

- **LED2 (D109):** Indicates that a background task is running the infinite while loop to determine if any bit of an SMU alarm status register is set. If yes, which means an SMU alarm is active, this LED is turned on.

- LED3 (D110): Port Emergency Stop. LED "off" when ES is activated.

See the Application Kit TC397 TFT Manual TC3x7 for further information about all nine LEDs on the PCB.

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Demonstrator presentation

Figure 4 Application Kit TC397 TFT LED usage

# 2.2 AURIX<sup>™</sup> MCU resource allocation

For more information about the AURIX<sup>™</sup> MCU resource allocation and project configuration, see the following configuration files:

- \AppSw\AppKit\Cfg\_Illd\Configuration.h

- \AppSw\AppKit\Cfg\_Illd\ConfigurationIsr.h

- \*AppSw\AppKit\AppKit\_Cfg.h*

- \AppSw\SafetyKit\SafetyKit\_Cfg.h

See Table 9 and Table 10 for additional information on resource allocation.

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Demonstrator presentation

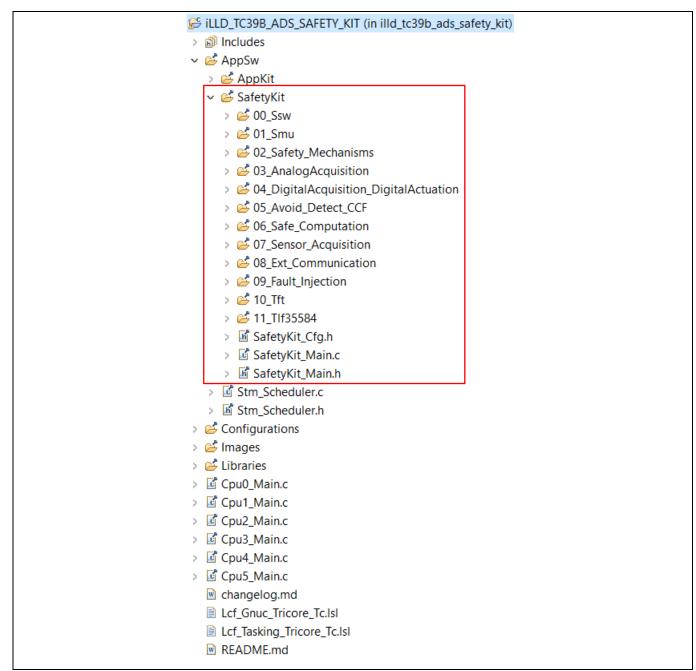

#### 2.3 Software overview

Figure 5 shows the project structure. In addition to the six *CpuX\_Main.c* (*x*=0...5) files, the relevant application software is stored in the *AppSw* folder, which consists of the two folders *AppKit* and *SafetyKit* and the two *Stm\_Scheduler* files used as System Timer (STM) for basic periodic task scheduling.

The *AppKit* (for Application Kit - AURIX<sup>™</sup> TC397 TFT) folder contains software specific for the display, touch application, and ASCLIN shell Interface. The *SafetyKit* folder includes all the code for the safety features implemented and required for this specific application note.

The software project is free-of-cost without any legal binding, and it is developed in the free-of-charge AURIX<sup>™</sup> Development Studio (ADS) integrated development environment (IDE). The project can be easily found in the ADS via import project functionality. It is not tested on other IDE platforms. Some software implementations are based on other AURIX<sup>™</sup> - TC3xx Microcontroller expert trainings, which can be found on the Infineon webpage.

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Demonstrator presentation

Figure 5 Project folder structure

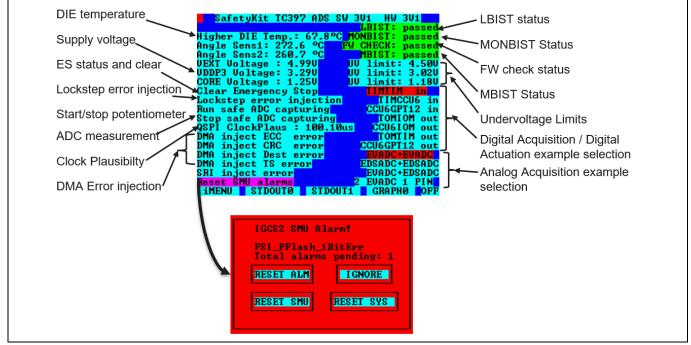

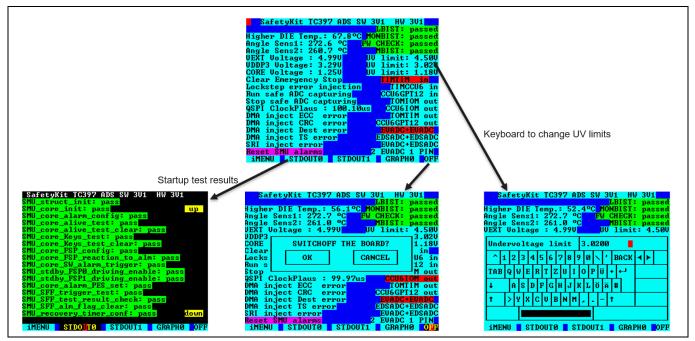

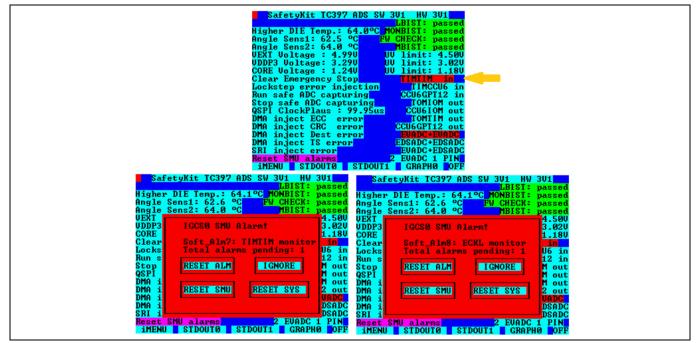

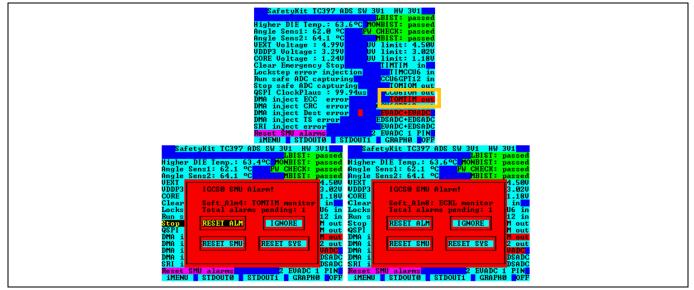

# 2.4 Touch display interface presentation

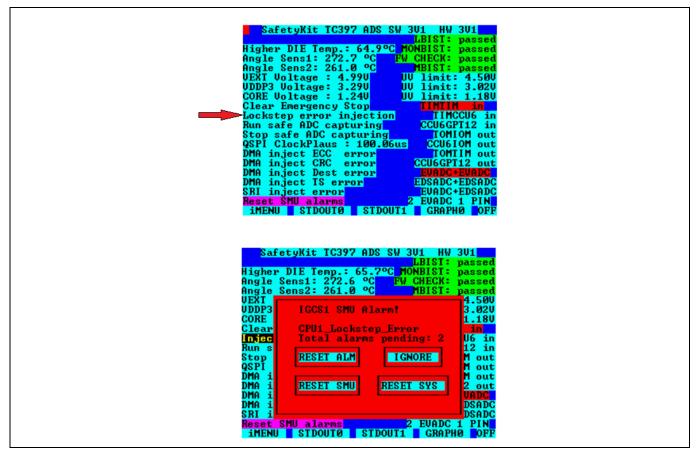

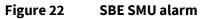

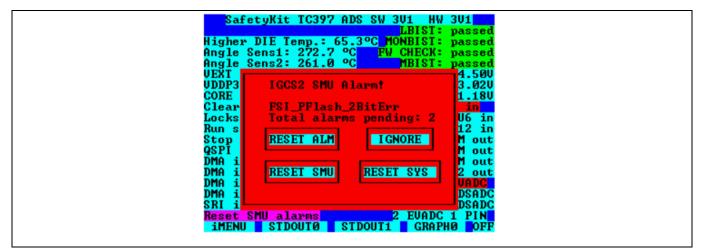

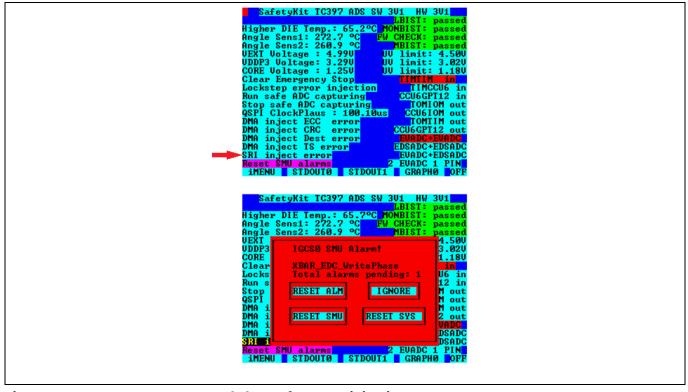

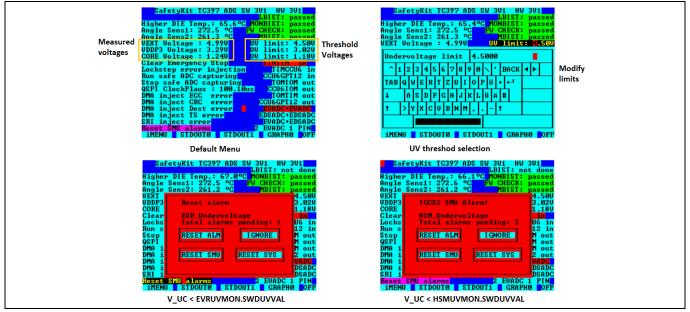

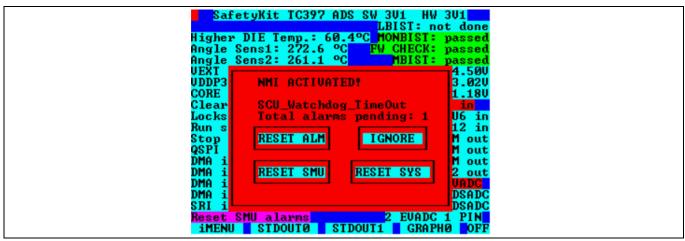

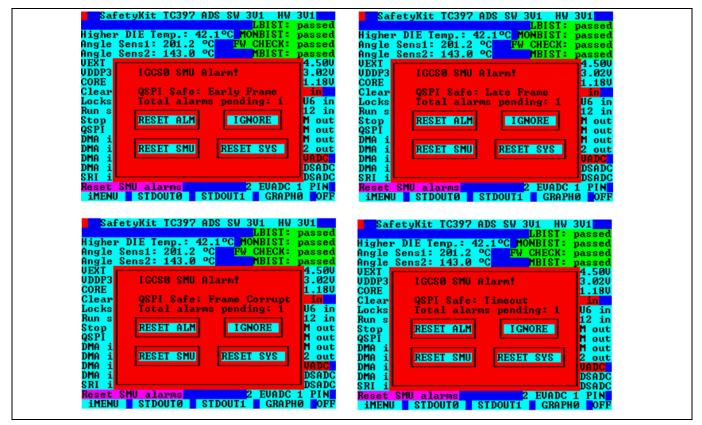

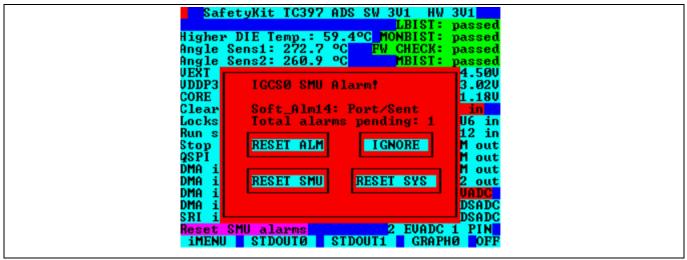

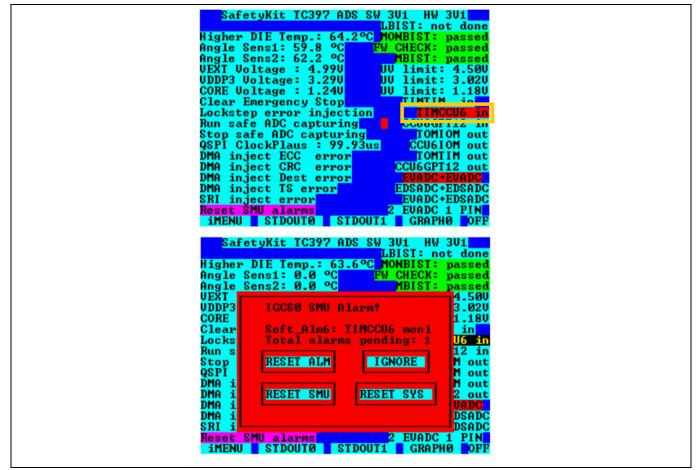

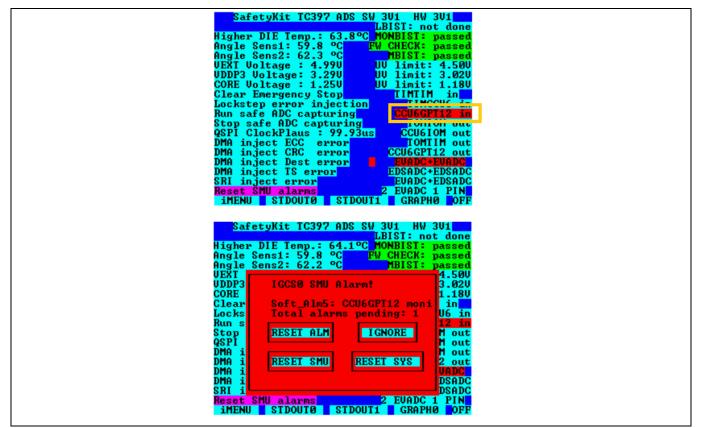

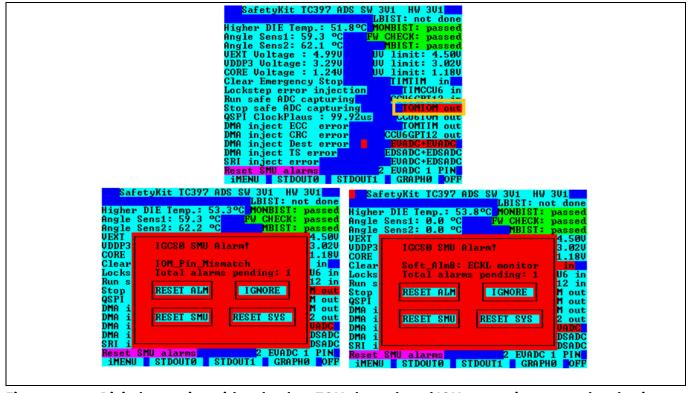

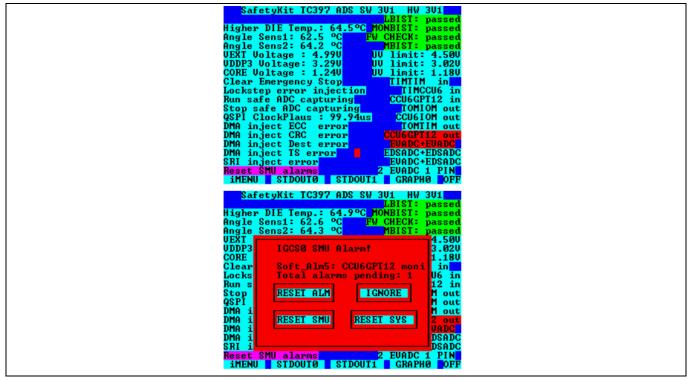

The Application Kit - AURIX<sup>™</sup> TC397 TFT features a touchscreen display, which is used to show the status information, real-time data, or to trigger different actions such as error injection. The default TFT view and an alarm pop-up window are shown in Figure 6. The alarm pop-up has four options to select:

- Reset alarm

- Ignore alarm

- Reset SMU

- Reset system

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Demonstrator presentation

Figure 6 Demonstrator TFT display overview

The TFT display has some more menus available:

- SMU Test Result

- Switch off option

- Keyboard for updating voltage value

STDOUT1 and GRAPH0 are not used currently but keep there just for future or user use.

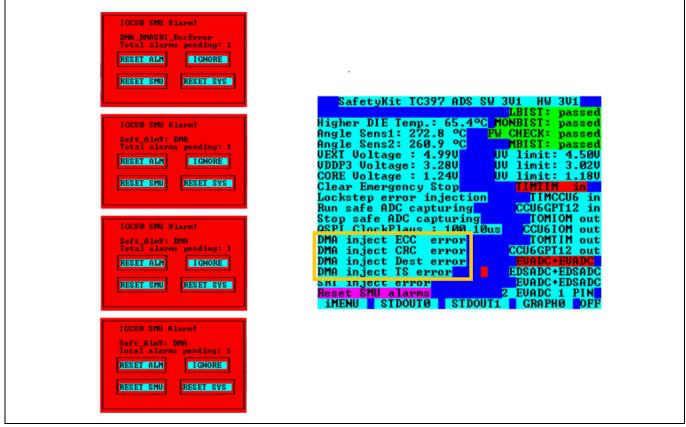

The Figure 7 below is an illustration of the above three options.

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Demonstrator presentation

Figure 7 TFT Display menu options

# 2.5 ASCLIN shell interface

The AURIX<sup>™</sup> Application Kit TC3xx Safety has another option as ASCLIN shell interface (terminal use). Currently, the following three options are available:

- standby: Switch TFL35584 to standby or TLF30682 to disabled state

- Showtlf: Show the status of the TLF35584 register

- trigAlalrm: Trigger a SMU alarm

To use the shell interface, power the Application Kit and connect it to the PC via a USB connector. Open a terminal in ADS (see Figure 8) and adjust the configuration as given below (user serial port can be different).

Figure 8 ASCLIN shell interface configuration

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Demonstrator presentation

After a successful USB connection, the following messages will be displayed in the terminal:

```

Hello World

I am the Safety Application kit TC397 ADS SW 3V1 with HW 3V1...

Enter 'help' to see the available commands

Shell>

```

#### Figure 9 ASCLIN shell interface successful connection

Type "help" and press **Enter** to display the list of functionalities available via this interface. See Figure 10.

```

Shell>help

standby : Switch TLF35584 to standby or TLF30682 to disable state

showtlf : Show status of TLF register

trigAlarm : Trigger an SMU alarm

help : Display command list, and command help.

```

#### Figure 10 ASCLIN shell interface available commands

To get the syntax of a command type the command name and then type "?" (question mark) to list the syntax of the command:

```

Shell>trigAlarm

Syntaxerror : invalid node

Shell>trigAlarm ?

Syntax : trigAlarm AG AN

> Trigger the SMU alarm AN of group AG

Shell>

```

#### Figure 11 ASCLIN shell interface syntax correction

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

# **3** Boot and startup procedure

## 3.1 Analog power-up

When the device comes from an unpowered state and the external power supply reaches 2.4 V, the internal circuitry is activated, and the power management system (PMS) checks the 100 MHz backup clock source (fBACK). If the clock is stable, PBIST (*Safety Mechanism PBIST*) is automatically executed. The device is released from the cold PORST reset only if the PBIST is executed successfully.

#### 3.2 Boot firmware

After PORST release, the system firmware (FW) execution is started by CPU0. The firmware (FW) is a code stored in Boot ROM that is automatically executed by the device after every reset. The FW is configurable via UCB registers and is composed of the following parts (among others):

#### Startup Software (SSW)

The internal SSW firmware contains procedures for device initialization. Depending on the type of reset the device is coming from, the startup software will execute different tasks. Some parts may already be initialized when coming from a reset other than cold PORST. The start-up software takes care of:

- Flash ramp-up

- Device Configuration

- RAM Initialization

- Selection and execution of Startup Modes

- LBIST execution

- Lockstep configuration

- Ending the startup software and starting the User Code

For more information about the firmware execution flow, see the figure "AURIX™ TC3xx Platform Firmware: main flow" in the AURIX™ TC3xx User's Manual [1].

#### **Checker Software (CHSW)**

The checker software verifies that all safety-critical aspects of the startup software have been executed correctly and thus everything is prepared for the execution of the user code.

For more information about the CHSW execution flow, see "AURIX™ TC3xx Platform Checker Software Overview" in the AURIX™ TC3xx User's Manual [1].

#### **Bootstrap Loaders (BSL)**

The BSL routines provide mechanisms to load a user program into the RAM of CPU0. This loaded code is started after exiting the Boot ROM. Therefore, after a successful execution of the firmware, the application software is started.

## 3.3 Application SW startup

During the execution of the application SW startup from a lockstep, the user code is responsible for the execution of several operations for ensuring that latent faults are not present, and for the correct initialization of the MCU before starting the runtime execution.

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

In particular, the application SW must:

- Execute the logic build-in self-test (LBIST) if not already performed during FW

- Evaluate the result of LBIST

- Configure, run, and check the result of MONBIST for ensuring the absence of latent faults in the secondary voltage monitors and standby SMU alarm path

- Execute MCU\_FW\_CHECK

- Verify the correct configuration settings installed by FW as described in MCU\_STARTUP

- Test the functionality of the SMU core alive monitor by the Safety Mechanism ALIVE\_ALARM\_TEST

- Configure, run, and check the result of MBIST for ensuring the absence of faults in RAM

- Ensure to enable all SMU alarms relevant for the application. In particular, the user code must re-enable alarms that were disabled during the configuration procedure

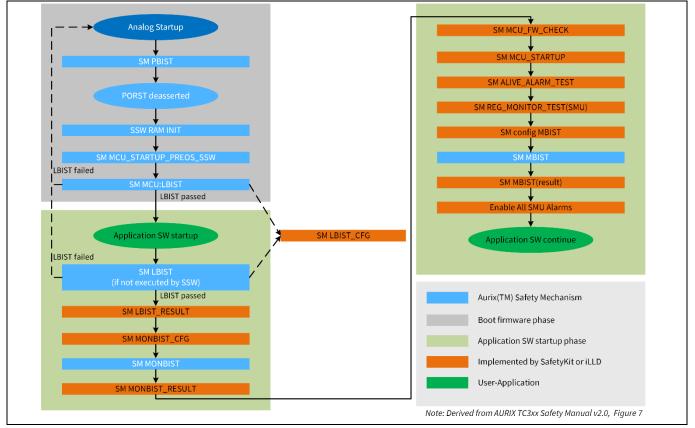

Figure 12 shows the sequence of safety mechanisms involved from an unpowered state to a full operational state of (see the legend on the bottom right for the respective color information):

Figure 12 Safety mechanisms sequence during startup

Note: Depending on the application, additional safety mechanisms at startup are required. For example, if a non-lockstep CPU is used for safety-relevant tasks, all safety mechanisms of the non-lockstep CPU must be considered.

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

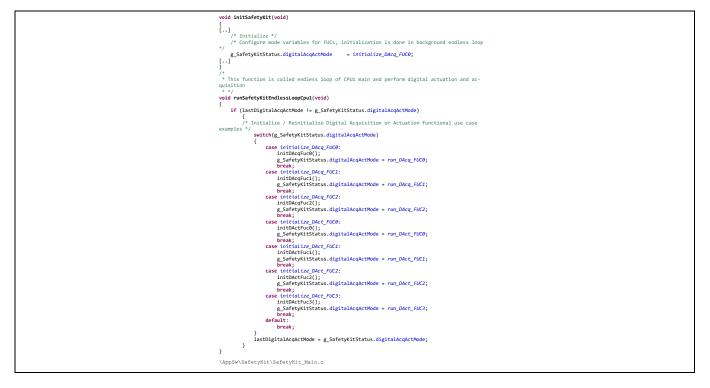

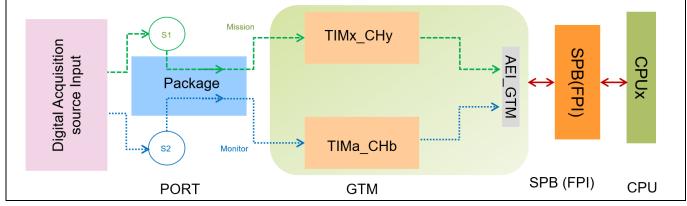

## 3.3.1 Safety Kit implementation of the application SW startup

The full application SW startup sequence can be observed in the following two code snippets. The first one shows the sequential execution of all steps involved; the corresponding macros to enable or disable individual steps can be observed in the second one.

#### Code Listing 1 Safe application software startup code example

```

/* Execute the sequence of SMs when coming from an un-powered state. */

void runSafeAppSwStartup(void)

#if SAFETYKIT_CFG_SSW_ENABLE_LBIST_BOOT || SAFETYKIT_CFG_SSW_ENABLE_LBIST_APPSW

safetyKitSswLbist();

#endif

/* Evaluate reset after LBIST execution */

g_SafetyKitStatus.resetCode = safetyKitEvaluateReset();

/* Evaluate if coming from standby mode */

g_SafetyKitStatus.wakeupFromStandby = safetyKitEvaluateStandby();

#if SAFETYKIT CFG SSW ENABLE MONBIST

g_SafetyKitStatus.sswStatus.monbistStatus = failed;

/* MONBIST Tests and evaluation

* SM:PMS:MONBIST_CFG and SM:MONBIST_RESULT */

Ifx_Ssw_Monbist();

g SafetyKitStatus.sswStatus.monbistStatus = passed;

#endif /* SAFETYKIT_CFG_SSW_ENABLE_MONBIST */

#if SAFETYKIT_CFG_SSW_ENABLE_MCU_FW_CHECK

/* SM:MCU FW CHECK */

safetyKitSswMcuFwCheck();

#endif /* SAFETYKIT_CFG_SSW_ENABLE_MCU_FW_CHECK */

#if SAFETYKIT_CFG_SSW_ENABLE_MCU_STARTUP

/* SM:MCU_STARTUP *

safetyKitSswMcuStartup();

#endif /* SAFETYKIT CFG SSW ENABLE MCU STARTUP */

#if SAFETYKIT_CFG_SSW_ENABLE_ALIVE_ALARM_TEST

safetyKitSswAliveAlarmTest();

#endif /* SAFETYKIT_CFG_SSW_ENABLE_ALIVE_ALARM_TEST */

#if SAFETYKIT_CFG_SSW_ENABLE_REG_MONITOR_TEST

/* SM:SMU:REG_MONITOR_TEST *

safetyKitSswSmuRegMonitorTest();

#endif /* SAFETYKIT_CFG_SSW_ENABLE_REG_MONITOR_TEST */

#if SAFETYKIT_CFG_SSW_ENABLE_MBIST

/* SM:MBIST */

safetyKitSswMbist();

#endif /* SAFETYKIT_CFG_SSW_ENABLE_MBIST */

/* Configure the alarm action for all SMU alarms with default configuration.

* Some configuration might get overwritten with specific configuration later

in the function initSMUModule() *

safetyKitEnableAllSMUAlarms();

}

\AppSw\SafetyKit\00_Ssw\SafetyKit_SSW.c

```

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

#### Code Listing 2 Macros to enable or disable steps of application SW startup

| / **               | Macros                                    |                                   |

|--------------------|-------------------------------------------|-----------------------------------|

| /*****             | <**************************************   | ********************************* |

| #define            | SAFETYKIT_CFG_SSW_ENABLE_LBIST_BOOT       | 1                                 |

| #define            | SAFETYKIT_CFG_SSW_ENABLE_LBIST_APPSW      | 1                                 |

| #define            | SAFETYKIT_CFG_SSW_ENABLE_MONBIST          | 1                                 |

| #define            | SAFETYKIT_CFG_SSW_ENABLE_MCU_FW_CHECK     | 1                                 |

| #define            | SAFETYKIT_CFG_SSW_ENABLE_MCU_STARTUP      | 1                                 |

| #define            | SAFETYKIT_CFG_SSW_ENABLE_ALIVE_ALARM_TEST | 1                                 |

| #define            | SAFETYKIT CFG SSW ENABLE REG MONITOR TEST | 1                                 |

|                    |                                           | 1                                 |

| #define<br>#define |                                           | 1<br>1<br>1<br>1                  |

#### 3.3.2 LBIST

As already mentioned in the sections 3.2 Boot firmware and 3.3 Application SW startup, the LBIST can be either executed by hardware during the boot firmware or by the application software during the application SW startup. Both ways are supported by Application Kit Safety.

To execute the LBIST during the firmware, LBIST must be enabled via the LBIST enable bit (LBISTENA) in the boot mode index (BMI), see Code Listing 3.

As stated in Safety Mechanism LBIST\_CFG, LBIST can be executed with different configurations. The only recommended configuration, which should be used is 'Configuration A', which is given in the device specific User's Manual Appendix [2]. This configuration obtains the best coverage with an execution time less than 6 ms and reasonable power consumption. In fact, with the wrong configuration, LBIST execution can drain too much current that power monitoring will reset the device. To avoid any kind of misconfiguration of the LBIST, use the proper configuration in the User Configuration Block (UCB) UCB04.

The correct execution of the LBIST and the resulting signature is always verified by the application SW (*Safety Mechanism LBIST\_RESULT*).

See Section 6.1.2 Logic built-in self-test (LBIST) for more information.

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

#### Code Listing 3 Eor disabling LBIST execution during boot firmware

```

const Ifx_Ssw_Bmhd bmhd_0_orig =

{

#if SAFETYKIT CFG SSW ENABLE LBIST BOOT

/* 0x000: .<u>bmi</u>: Boot Mode Index (BMI)

*/

0x01FE,

/* 0x002: .bmhdid: Boot Mode Header ID (CODE) = B359H

*/

0xB359,

/* 0x004: .stad: User Code start address

*/

0xA0000000,

0xFA2586D5,

/* 0x008: .crc: Check Result for the BMI Header (offset 00

*/

/* 0x00C: .crcInv: Inverted Check Result for the BMI Header */

0x05DA792A,

#else

/* 0x000: .bmi: Boot Mode Index (BMI)

*/

0x00FE,

*/

0xB359,

/* 0x002: .bmhdid: Boot Mode Header ID (CODE) = B359H

/* 0x004: .stad: User Code start address

*/

0xA0000000,

/* 0x008: .crc: Check Result for the BMI Header (offset 00

*/

0x31795570,

/* 0x00C: .crcInv: Inverted Check Result for the BMI Heade

*/

0xCE86AA8F,

#endif

[..]

const Ifx Ssw Bmhd bmhd 0 copy =

#if SAFETYKIT_CFG_SSW_ENABLE_LBIST_BOOT

0x01FE, /* 0x000: .<u>bmi</u>: Boot Mode Index (BMI)

*/

0xB359,

/* 0x002: .bmhdid: Boot Mode Header ID (CODE) = B359H

*/

0xA0000000,

/* 0x004: .stad: User Code start address

*/

0xFA2586D5,

/* 0x008: .crc: Check Result for the BMI Header (offset 00 */

*/

0xo5DA792A,

/* 0x00C: .crcInv: Inverted Check Result for the BMI Header */

0xB359,

/* 0x002: .bmhdid: Boot Mode Header ID (CODE) = B359H

*/

#else

0x00FE,

/* 0x000: .bmi: Boot Mode Index (BMI)

*/

0xB359,

/* 0x002: .bmhdid: Boot Mode Header ID (CODE) = B359H

*/

*/

/* 0x004: .stad: User Code start

0xA0000000,

0x31795570,

/* 0x008: .crc: Check Result for the BMI Header (offset 00

*/

/* 0x00C: .crcInv: Inverted Check Result for the BMI Heade */

0xCE86AA8F,

#endif

[..]

\Configurations\Ifx Cfg SswBmhd.c

```

Note: Check whether BMHD has been programmed successfully by verifying the value of the "bmi" variable of the "bmhd\_0\_orig" structure (bmi = 0x01FE if LBIST is enabled and bmi = 0xFE if LBIST is disabled).

#### 3.3.3 MONBIST

See Section 6.1.3 Monitor built-in self-test (MONBIST).

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

#### 3.3.4 Firmware check

The *Safety Mechanism MCU\_FW\_CHECK* is required for detecting failures (random hardware and systematic hardware and software), which may have affected the correct execution of the firmware.

In particular:

- Random hardware faults (RHF) can appear as transient or permanent faults and affect one of the hardware parts (CPU, buses, FLASH) that are needed by the firmware

- Systematic faults (hardware/software) can be generated by incorrectly programming a UCB and other registers, which control the firmware execution. Because the number of possible combinations cannot be tested during firmware development, the application needs to verify that firmware execution was correct.

Depending on the AURIX<sup>™</sup> device and the kind of reset performed, the firmware execution varies. Therefore, the application software must verify the correct content of the registers and flags that are relevant for the specific type of reset. For the complete list of registers and SMU alarms expected content, see "Appendix A" of the AURIX<sup>™</sup> TC3xx Safety Manual [3].

If one of the relevant registers or SMU flags do not report the expected value ("fail" condition), it can be concluded that the firmware execution has been corrupted by:

- **Firmware systematic fault:** Can be caused by a specific UCB register combination, leading to an incorrect firmware sequence and MCU initialization

- **Hardware transient fault:** Can be caused by EM interference or other transitory events affecting some hardware part (for example CPU0) during the firmware execution

- **Hardware permanent fault:** Can be caused by faults in the hardware (undetected by LBIST), affecting some hardware part (for example, CPU0) which lead to a firmware execution misbehavior

For firmware systematic faults and hardware permanent faults, the firmware check will fail after every reset, while hardware transient faults have an extremely low probability to affect the device in the same way again during a second attempt. Therefore, if the firmware check fails, it is recommended to perform a second attempt by triggering a device reset (ideally of the same type). If the check fails again, it should be concluded that the device is affected by a permanent hardware fault, and the device should be considered as not reliable.

## 3.3.4.1 FW\_CHECK implementation

The implementation of *Safety Mechanism MCU\_FW\_CHECK* requires various steps. In this example, the main steps are as follows (see Code Listing 4, for the Application Kit Safety implementation of the firmware check):

- Check that the expected SMU alarms have been triggered (registers SMU\_AG[0→11])

- Verification of the content of the SCU\_STMEM[3→6] registers

- Verification of the content of the SCU\_LCLCON[0→1] registers

- Verification of the content of the SSH registers (MCi\_ECCD, MCi\_FAULTSTS, and MCi\_ERRINFO[0], with "i" representing every SRAM used in the application)

# Attention: Register values depend on the AURIX<sup>™</sup> device type and reset type. For the full list of registers and their expected values, see "Appendix A" of the AURIX<sup>™</sup> TC3xx Safety Manual.

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

If all registers and SMU alarms report the expected values, the application SW must:

- Clear the content of the registers mentioned in the tables in "Appendix A" of the Safety Manual [3]

- Clear the SMU alarms SMU\_AG [0 ... 11]

- Clear the corresponding reset status bits in RSTSTAT register

- Proceed further

As already mentioned, if any of the registers do not report the expected values, it shall be assumed that the firmware has not been executed as expected. It is recommended to perform a second attempt by triggering a device reset (ideally of the same type).

#### **STMEM check**

The execution performed by the SSW is checked by the CHSW that indicates the status of several modules in these four registers at the end of each reset:

- SCU\_STMEM3

- SCU\_STMEM4

- SCU\_STMEM5

- SCU\_STMEM6

For more details, see Section 3.1.2.2 "Checks performed by CHSW and exit information" in the AURIX<sup>™</sup> TC3xx User Manual. The expected values of these registers are available in Section 3.1 "Checker Software exit information for ALL CHECKS PASSED" of the device-specific User's Manual Appendix [2].

#### **LCLCON check**

During SSW execution, lockstep cores are enabled according to the UCB\_BMHD registers. After each reset (except an application reset), the application software must verify the status of the LCLCON[ $0 \rightarrow 1$ ] registers according to the enabled lockstep cores:

- SCU\_LCLCON0

- SCU\_LCLCON1

#### **SSH register check**

For each memory controller (MC) used in the application, this routine verifies that the alarm and error status registers are reporting the expected values. The values mainly depend on the reset type. The following registers are verified:

- ECCD

- FAULTSTS

- ERRINFO [0]

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

#### Code Listing 4 Code snippet of firmware check implementation

```

* SM:MCU_FW_CHECK

* */

void safetyKitSswMcuFwCheck(void)

{

if(g_SafetyKitStatus.resetCode.resetType == safetyKitResetTypeColdpoweron)

/* Initialize the g_sswStatusXram data if it was a Cold PORST */

g_sswStatusXram->mcuFwcheckRuns = 0;

}

[..]

/* Increment the firmware check execution counter */

g_sswStatusXram->mcuFwcheckRuns++;

if

(

/* Read SMU alarm register values and compare with expected ones(listed in Appendix A of the

* Safety Manual)

* Note: depending on the device and reset type different register values are expected */

(TRUE == safetyKitFwCheckSmuStmemLclcon(fwCheckSMUTC39B, fwCheckSMUTC39BSize,

g_SafetyKitStatus.resetCode.resetType, fwCheckVerificationSMU)) &&

/* Read SCU_STMEM register values and compare with expected ones(listed in Appendix A of the

* Safety Manual) */

(TRUE == safetyKitFwCheckSmuStmemLclcon(fwCheckSTMEMTC39B, fwCheckSTMEMTC39BSize,

g_SafetyKitStatus.resetCode.resetType, fwCheckVerificationSTMEM)) &&

/* Read SCU_LCLCON register values and compare with expected ones (listed in Appendix A of the

* Safety Manual) */

(TRUE == safetyKitFwCheckSmuStmemLclcon(fwCheckLCLCONTC39B, fwCheckLCLCONTC39BSize,

g_SafetyKitStatus.resetCode.resetType, fwCheckVerificationLCLCON)) &&

/* Read SSH register values of all RAM and compare with expected ones (listed in Appendix A of

* the Safety Manual)*/

(IfxMtu_MbistSel_none == safetyKitFwCheckSsh(g_SafetyKitStatus.resetCode.resetType))

)

{

/* If all four checks have passed set FW check status variable to "passed" */

g_SafetyKitStatus.sswStatus.mcuFwcheckStatus = passed;

/* If all registers and SMU alarm registers have reported the expected values .. */

/* .. clear the content of the registers mentioned in the Appendix table */

safetyKitFwCheckClearSSH(g_SafetyKitStatus.resetCode.resetType);

/* .. clear the SMU alarms SMU_AG0..11 */

safetyKitFwCheckClearSmuAlarms(fwCheckSMUTC39B, fwCheckSMUTC39BSize);

/* .. clear the corresponding reset status bits in RSTSTAT register */

IfxScuRcu_clearColdResetStatus();

}

else

{

g_SafetyKitStatus.sswStatus.mcuFwcheckStatus = failed;

/* If FW check has failed during its first execution trigger the check again */

if(g_sswStatusXram->mcuFwcheckRuns < SAFETKIT_FW_CHECK_MAX_RUNS)</pre>

{

/* Clear COLD PORST reason to preserve the data on the SCR XRAM */

IfxScuRcu_clearColdResetStatus();

safetyKitFwCheckRetriggerCheck(g_SafetyKitStatus.resetCode.resetType);

}

}

[..]

\AppSw\SafetyKit\00_Ssw\SafetyKit_SSW_02_MCU_FW_CHECK.c

```

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

# Attention: Debugger influence Debuggers might have an (undefined) interference to the firmware behavior and alarms set during firmware execution. Therefore, it is mandatory to disconnect the debugger before performing any reset and reconnect it at the end of the firmware execution. Otherwise, the SMU alarms and/or SSH registers may not report expected values.

Attention: "Early" execution The firmware check (Safety Mechanism MCU\_FW\_CHECK) is recommended to perform its execution in the earliest stage possible of the startup. One reason for that is that SMU ALMs and/or SSH registers might be accidentally influenced by actions within the application software. Another reason is that, to meet the startup timing requirements, the application must be able to detect a fault in the firmware check and trigger a second reset (if required) as soon as possible.

# 3.3.4.2 Reset triggering

If one of the checks shown in the previous sections is not met, the application must reset the microcontroller at least once. As described in Section 9.1.2.2 "Reset Types" of the AURIX<sup>™</sup> TC3xx User Manual [1], there are four kinds of resets that can be used in an application:

- Cold power-on reset (cold PORST)

- Warm power-on reset (warm PORST)

- System reset

- Application reset

There are several methods for generating a reset. In general, a PORST (cold or warm) requires the external power supply to either remove the power supply voltage (cold PORST) or assert the PORST pin (warm PORST). System and application resets can be generated by application software through the SWRSTCON and RSTCON registers, respectively. It is possible to store the number of reset events (except for cold PORST) in the Standby Controller Extension RAM, which retains its contents during all resets except cold PORST.

#### Cold reset through LBIST

If the external power supply is unable to generate a cold PORST by removing the supply voltage, it is possible to simulate a cold PORST by triggering a "fake" LBIST. This can be achieved by setting LBISTCTRL0.PATTERNS = 0 and triggering a new LBIST execution by software. The LBIST controller will start and immediately stop the LBIST scan chain. At the end of the LBIST execution, the MCU internally automatically triggers an internal reset, which from a firmware execution point of view is equivalent to a cold PORST.

Ensure the following before launching a new LBIST execution:

- Reset the LBIST controller to its initial state and set the "done" bit to zero again by setting LBISTCTRL0.LBISTRES = 1.

- Clear the cold reset status bits by setting LBISTCTRL2.CLRC = 1.

At the next startup, the application software can detect that an LBIST reset has been executed by checking RSTSTAT.STBYR = 0 and RSTSTAT.LBTERM = 1. The registers and SMU alarms will report the values expected for a cold reset. If one of the checks fails again (it does not necessarily have to be the same condition that failed at the cold PORST), the device must be considered faulty.

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

See Code Listing 5 for the Safety Application Kit implementation and Section 9.3.3 "LBIST Support" in the AURIX™ TC3xx User's Manual [1] for more details.

Code Listing 5 Code snippet of function safetyKitTriggerLbist

```

/*

* SM:LBIST CFG

* */

void safetyKitTriggerLbist(void)

{

/* Increment counter variable which counts the LBIST requests via Application SW

*/

g_sswStatusXram->lbistAppSwReq++;

/* Clear COLD PORST reason to preserve the data on the SCR XRAM */

IfxScuRcu clearColdResetStatus();

/* Trigger LBIST */

if ( IFX SCU CHIPID CHREV TC39X BD == MODULE SCU.CHIPID.B.CHREV)

{

/* Default signature for TC39X-BD device */

IfxScuLbist_triggerInline(&IfxScuLbist_defaultConfig_tc39x_bd);

}

else

{

IfxScuLbist_triggerInline(&IfxScuLbist_defaultConfig);

}

while(1)

{

_nop(); /* After triggering LBIST wait for warm reset */

}

} \AppSw\SafetyKit\00_Ssw\SafetyKit_SSW_00_LBIST.c

```

#### Warm PORST

A warm PORST is generated by an assertion of the PORST pin while keeping the external power supply voltage stable. After a warm PORST, it is possible to configure the firmware to perform a RAM initialization (through the PROCONRAM register) and even to retrigger an LBIST execution (although this is not necessary). The standby domain remains functional during a warm PORST, so the standby RAM (Memory Controller instances 77 and 78) are not accessed during the consequent firmware execution.

#### System and application reset

System and application resets can be easily triggered by the application software during runtime by configuring the following registers. See Code Listing 6 for the Application Kit Safety implementation.

- Configure RSTCON.SW with the required reset (0x1 system, 0x2 application)

- Configure SWRSTCON.SWRSTREQ = 0x1

32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

Code Listing 6 Code snippet of function safetyKitTriggerSwReset

```

/*

* This function triggers either a SW Application Reset or a SW System Reset, based

on the parameter resetType

* */

void safetyKitTriggerSwReset(SafetyKitResetType resetType)

{

/* Get the CPU EndInit password */

uint16 cpuEndinitPw = IfxScuWdt_getCpuWatchdogPassword();

/* Configure the request trigger in the Reset Configuration Register */

IfxScuRcu_configureResetRequestTrigger(IfxScuRcu_Trigger_sw, (IfxScuRcu_Reset-

Type)resetType);

/* Clear CPU EndInit protection to write in the SWRSTCON register of SCU */

IfxScuWdt_clearCpuEndinit(cpuEndinitPw);

/* Trigger a software reset based on the configuration of RSTCON register */

IfxCpu_triggerSwReset();

/* The following instructions are not executed if a SW reset occurs */

/* Set CPU EndInit protection */

IfxScuWdt setCpuEndinit(cpuEndinitPw);

} \AppSw\SafetyKit\00 Ssw\SafetyKit SSW.c

```

## 3.3.5 MCU\_STARTUP

Before entering run mode, the application SW must check for any corruption of data stored in the safety-relevant registers.

To verify whether the contents of these registers is correct, the user code must store a data checksum accumulated over all safety-relevant registers and application-dependent safety registers. When this calculation is completed, the application software must compare the calculated result with an expected checksum stored in the NVM.

See the implemented function <code>void safetyKitSswMcuStartup(void)</code> and to the Safety Mechanism MCU\_STARTUP section in the Safety Manual [3] for more information.

## 3.3.6 SMU ALIVE\_ALARM\_TEST

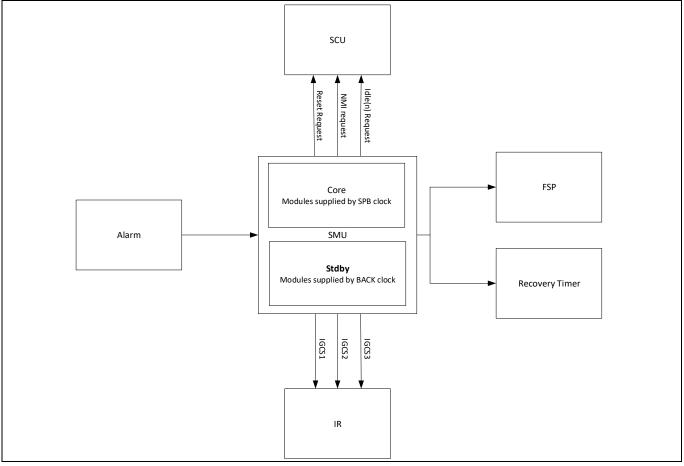

If a malfunction occurs, the primary part of the SMU (SMU\_core) generates an internal *alive* signal to the standby part of the SMU (SMU\_stdby). The SMU Core Alive signal is generated if one of the following conditions is met:

- An alarm event occurs while SMU\_core is in RUN or FAULT state and the SMU\_core alive monitor detects that a reaction has not been generated by SMU\_core.

- A watchdog or recovery timer alarm event occurs while the SMU\_core is in START state and the SMU\_core alive monitor detects that a reaction has not been generated by SMU\_core.

- The application issues an SMU\_ActivateFSP or SMU\_ActivatePES command, but the appropriate reaction is not generated by SMU\_core.

- The alarm configuration is changed while this alarm is being processed.

Application note

#### 32-bit TriCore<sup>™</sup> AURIX<sup>™</sup> TC3xx microcontroller Boot and startup procedure

According to *Safety Mechanism ALIVE\_ALARM\_TEST*, the application software must, at least once per driving cycle, test the SMU core alive monitor and its connection to the SMU standby by triggering the alive alarm.

See the Application Kit Safety implementation (Code Listing 8) and Section 15.3.1.2.5 "Interface to SMU\_stdby" in the User's Manual [1] and *Safety Mechanism ALIVE\_ALARM\_TEST* in the Safety Manual [3] for more information.

#### Code Listing 7 Code snippet of function safety mechanism ALIVE\_ALARM\_TEST

```

/* SM:ALIVE_ALARM_TEST

void safetyKitSswAliveAlarmTest(void)

{

g SafetyKitStatus.smuStatus.smuCoreAliveTestSts

= NA:

g_SafetyKitStatus.smuStatus.smuCoreAliveTestClearSts

= NA:

if((g_SafetyKitStatus.resetCode.resetType == safetyKitResetTypeColdpoweron) ||

(g_SafetyKitStatus.resetCode.resetType == safetyKitResetTypeLbist))

{

/* Start SMU Alive Test */

IfxSmu_startAliveTest();

Poll for command status (success) */

uint8 timeout = 0xFF;

while (SMU_STS.B.RES != 0U && timeout > 0)

{

timeout--:

}

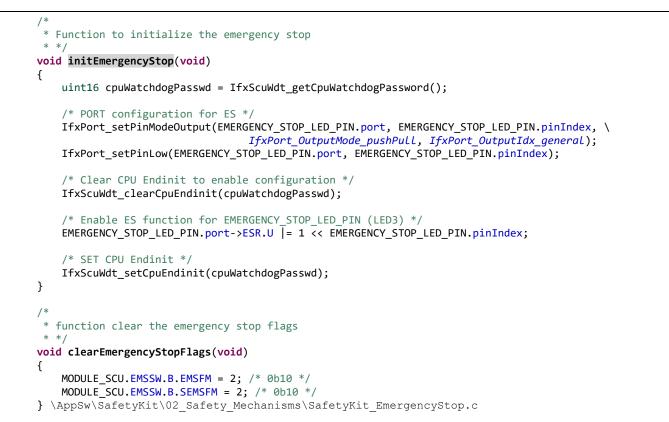

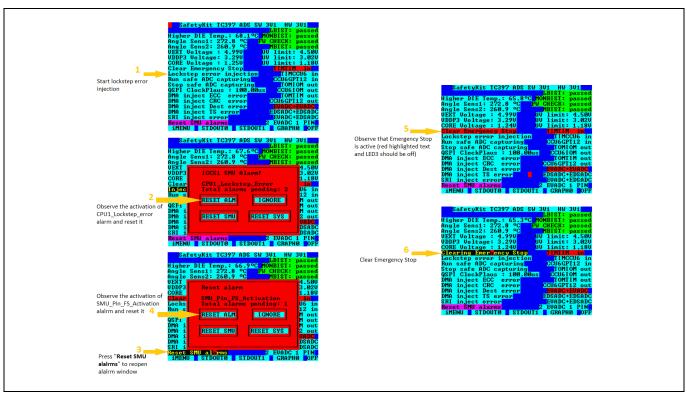

/* Wait for ALM21[16] - SMU Alive Monitor Alarm */