# BTN8960 /62 /80 /82

# **High Current PN Half Bridge**

# **About this document**

# Scope and purpose

This Application Note is intended to provide information and hints for a high current design, using PWM control with the NovalithIC<sup>™</sup> half-bridge family BTN89xy for the automotive environment.

Note:

The following information is only given to help with the implementation of the device and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

## **Abstract**

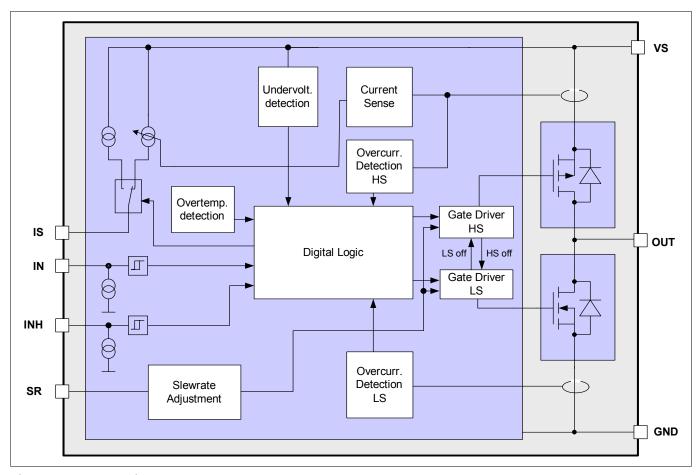

This family contains one P-channel high-side MOSFET and one N-channel low-side MOSFET with an integrated driver IC in one package. The NovalithIC<sup>™</sup> BTN89xy is the interface between the microcontroller and the motor, equipped with diagnostic and protection functions.

Figure 1 **Block Diagram BTN89xy**

As both the high-side and low side switch are placed on one single leadframe this results in many system benefits: Resulting from the low distance between the high-side MOSFET and the low-side MOSFET the stray inductance between them is minimal thus minimizing negative voltage spikes at OUT during switching and improving EMC. As the voltage level of the leadframe is on the output of the half-bridge, only one single cooling area is required (on OUT potential) for the device, thus being used for both a high-side or low-side current switching. For a state of the art N-channel solution, usually two cooling areas are required, each for the highside and low-side MOSFET.

# Table of contents

Due to the p-channel highside switch the need for a charge pump is eliminated thus minimizing EMI. Interfacing to a microcontroller is made easily by the integrated driver IC which features logic level inputs, diagnosis with current sense, slew rate adjustment, dead time generation and protection against overtemperature, undervoltage, overcurrent and short circuit.

# **Table of contents**

|         | About this document                                                           | 1  |

|---------|-------------------------------------------------------------------------------|----|

|         | Table of contents                                                             | 2  |

| 1       | Motor Configurations                                                          | 5  |

| 1.1     | Half-bridge configuration for mono-directional motor control                  | 5  |

| 1.2     | H-Bridge configuration for bidirectional motor control                        | 6  |

| 2       | Parasitic Inductance                                                          | 7  |

| 2.1     | Measuring signals at NovalithIC <sup>TM</sup>                                 | 7  |

| 3       | Design Guideline                                                              | 9  |

| 3.1     | Schematic and layout design rules                                             | 9  |

| 3.2     | DC-link capacitor                                                             | 11 |

| 3.2.1   | Calculation of the DC-link capacitor and Pi-filter                            | 11 |

| 3.2.2   | Undervoltage toggling                                                         | 13 |

| 3.3     | Ground references                                                             | 15 |

| 3.4     | Driving inductive loads over long wires                                       | 16 |

| 3.4.1   | PWM operation                                                                 | 16 |

| 3.4.2   | Current sense                                                                 | 17 |

| 3.5     | Reverse polarity protection                                                   | 17 |

| 3.6     | Cooling                                                                       | 17 |

| 4       | Current Sense Improvement                                                     | 19 |

| 4.1     | Characteristic of the dk <sub>ILIS</sub>                                      | 19 |

| 4.1.1   | Supply voltage dependency of dk <sub>ILIS</sub>                               | 19 |

| 4.1.2   | Life time drift                                                               | 20 |

| 4.1.3   | Temperature drift of the dk <sub>ILIS</sub>                                   | 20 |

| 4.1.4   | Temperature drift of the dk <sub>ILIS</sub> including aging                   | 27 |

| 4.2     | Offset compensation                                                           | 28 |

| 4.3     | Device specific dk <sub>ILIS</sub>                                            | 29 |

| 4.4     | Device fine dk <sub>ILIS</sub> and temperature compensation                   | 30 |

| 4.4.1   | An example of the I <sub>IS</sub> failure with a rough temperature estimation | 31 |

| 4.5     | IS-pin current sensing and fault detection                                    | 31 |

| 4.5.1   | Current sensing concepts in applications                                      | 31 |

| 4.5.1.1 | BTN89xy - advanced current sense and fault diagnosis                          | 32 |

| 4.5.1.2 | BTN79xy current sense limitations                                             |    |

| 4.5.2   | Fault detection                                                               | 34 |

| 4.5.2.1 | Temperature drift of the IS-pin's current in fault condition $I_{ S(lim)}$    | 40 |

# Table of contents

| 4.5.2.2 | Failure detection flow chart                                | 42 |

|---------|-------------------------------------------------------------|----|

| 4.5.2.3 | Lowpass filtered current sense signal                       | 43 |

| 5       | Switching Timing                                            | 46 |

| 5.1     | BTN8982TA Switching Time Dependency on Slew Rate Resistance | 48 |

| 5.1.1   | Timing behavior for rising edge on high-side switch         | 48 |

| 5.1.2   | Timing behavior for falling edge on high-side switch        | 50 |

| 5.1.3   | Timing behavior for rising edge on low-side switch          | 51 |

| 5.1.4   | Timing behavior for falling edge on low-side switch         | 53 |

| 5.2     | BTN8962TA Switching Time Dependency on Slew Rate Resistance | 55 |

| 5.2.1   | Timing behavior for rising edge on high-side switch         | 55 |

| 5.2.2   | Timing behavior for falling edge on high-side switch        | 57 |

| 5.2.3   | Timing behavior for rising edge on low-side switch          | 58 |

| 5.2.4   | Timing behavior for falling edge on low-side switch         | 60 |

| 5.3     | Error of total delay time                                   | 62 |

| 5.4     | Delay time calibration                                      | 64 |

| 5.4.1   | Output voltage based calibration                            | 64 |

| 5.4.2   | Current sense based calibration                             | 65 |

| 5.5     | ADC Timing for current measurement                          | 67 |

| 5.5.1   | Current sense ADC timing                                    | 67 |

| 5.5.2   | Offset current calibration ADC timing                       | 69 |

| 5.6     | Allowed PWM setup for current sense ADC measurements        | 70 |

| 5.6.1   | BTN8962TA                                                   | 71 |

| 5.6.2   | BTN8982TA                                                   | 72 |

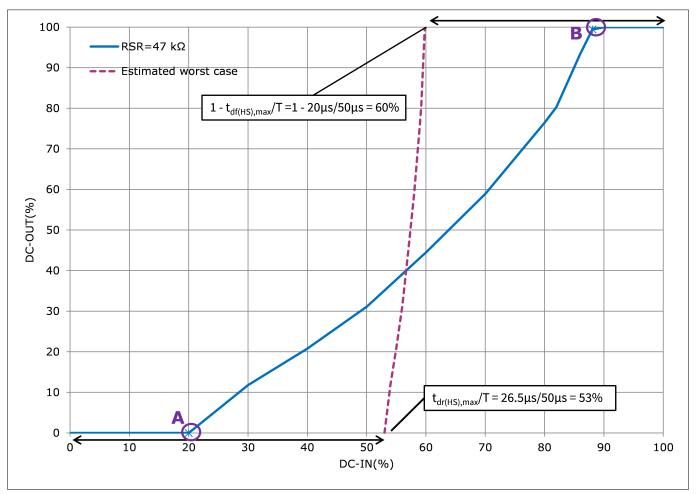

| 5.6.3   | Example calculation                                         | 73 |

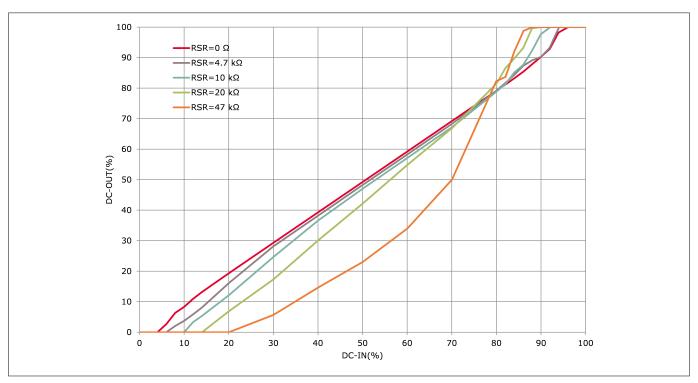

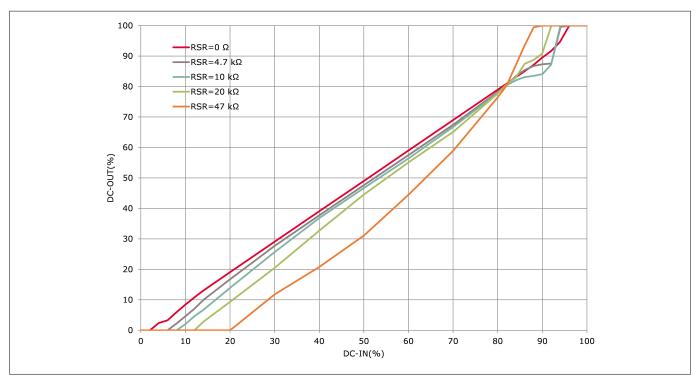

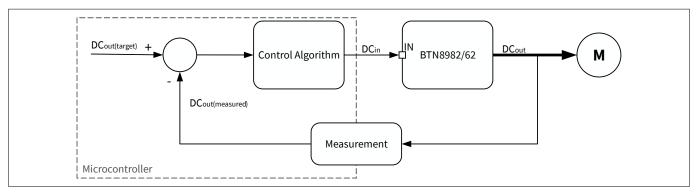

| 5.7     | Output duty cycle relationships                             | 75 |

| 5.7.1   | The device specific spread of the output duty cycle         | 76 |

| 5.7.2   | Output duty cycle improvement methods                       | 77 |

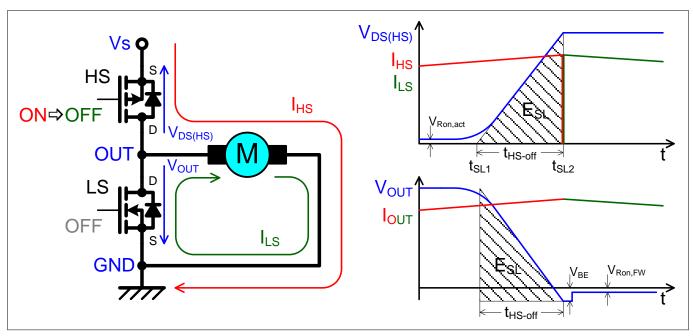

| 6       | Power Dissipation                                           | 79 |

| 6.1     | Power dissipation of the control chip (top chip)            | 79 |

| 6.2     | Conduction power dissipation                                | 79 |

| 6.3     | Power dissipation due to switching                          | 80 |

| 6.4     | Entire power dissipation of the MOSFETs                     | 81 |

| 6.4.1   | PWM control and the duty cycle constraints                  | 82 |

| 6.4.2   | Entire power dissipation in the actuator MOSFET             | 82 |

| 6.4.3   | Entire power dissipation in the freewheeling MOSFET         | 82 |

| 6.5     | Entire power dissipation in the NovalithIC <sup>TM</sup>    | 83 |

| 6.6     | Simplifications                                             | 83 |

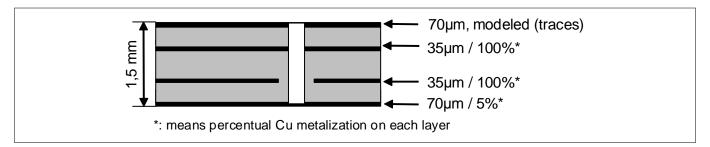

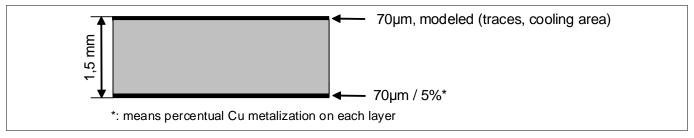

| 7       | Thermal Performance                                         | 85 |

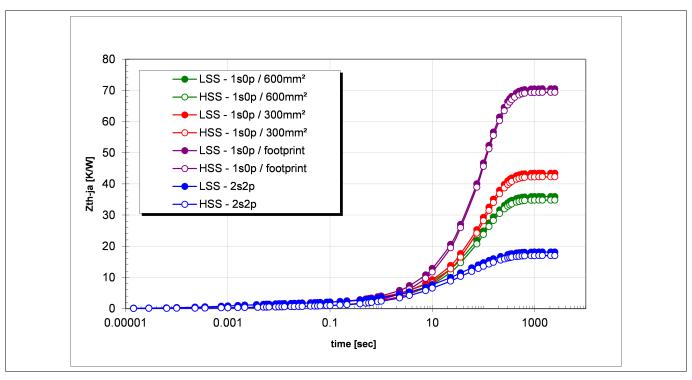

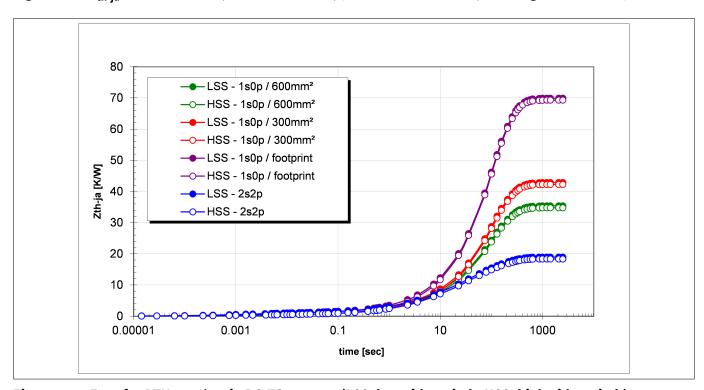

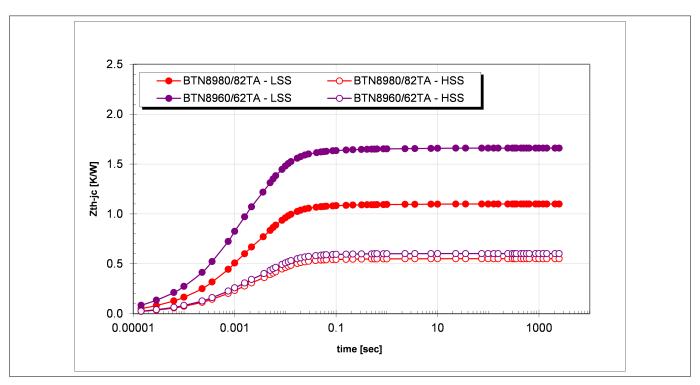

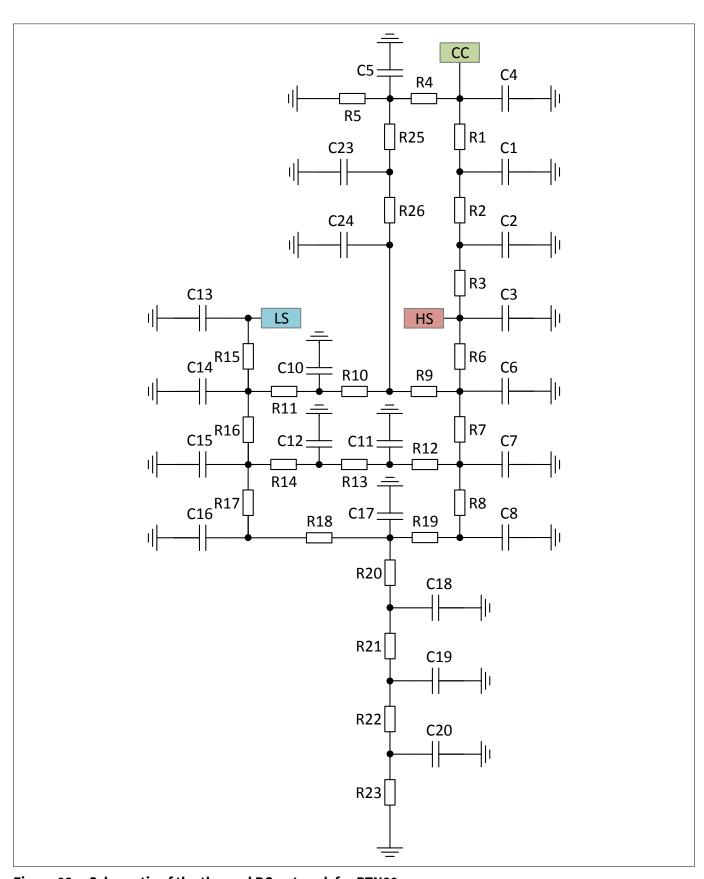

| 7.1     | Zth simulation results                                      | 86 |

| 7.2     | Thermal RC-network                                          | 87 |

| 7.2.1   | Parameters for BTN8960/62                                   | 89 |

# Table of contents

| 7.2.2 | Parameters for BTN8980/82 | <br> | <br> | 90 |

|-------|---------------------------|------|------|----|

|       | Revision History          | <br> | <br> | 93 |

|       | Disclaimer                |      |      | 94 |

4

# Motor Configurations

# **1** Motor Configurations

Electrical motors are built with various architectures. Mechanically commutated motors with brushes, so called DC motors or electrically commutated motors, so called BLDC motors (BrushLess DC motors). Due to the flexibility of the half-bridge concept, the NovalithIC<sup>™</sup> family can support all of them.

Using NovalithIC<sup>™</sup> controlling a DC-motor has the following advantages:

- Extremely low parasitic inductances between high-side and low-side MOSFET.

- Optimized switching performance of the MOSFET's to reduce power losses and EMC emission.

- Driving the motor with PWM for torque and speed control.

- Integrated freewheeling transistor.

- · Integrated current measurement.

- Integrated diagnosis and protection.

- Microcontroller compatible input pins.

- Small and PCB-area saving package.

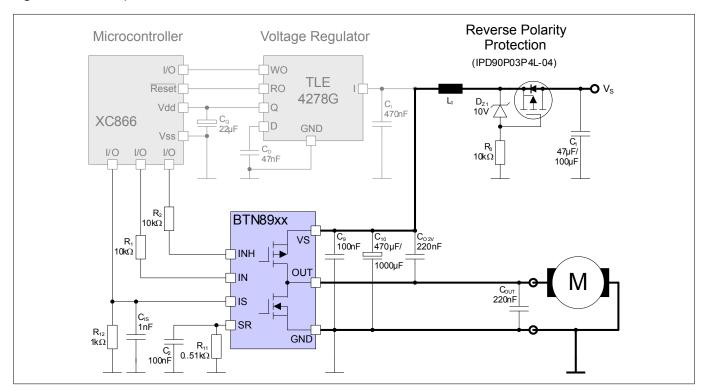

# 1.1 Half-bridge configuration for mono-directional motor control

*Figure 2* shows the design of a mono-directional motor control with NovalithIC<sup>™</sup>. In most cases, the motor is connected between "OUT" and "GND". This is because the chassis of a car is "GND", and therefore a short to "GND" is much more probable than a short to " $V_s$ ". For this reason it is statistically safer with a motor connected to "GND", because if a short occurs in this case, the motor is not running.

Generally, it is also possible to use the NovalithIC<sup>\*\*</sup> to drive the motor between "OUT" and " $V_s$ ". The inverted "IN" signal must be respected.

Figure 2 Application circuit for a monodirectional motor with BTN8962/82

**Motor Configurations**

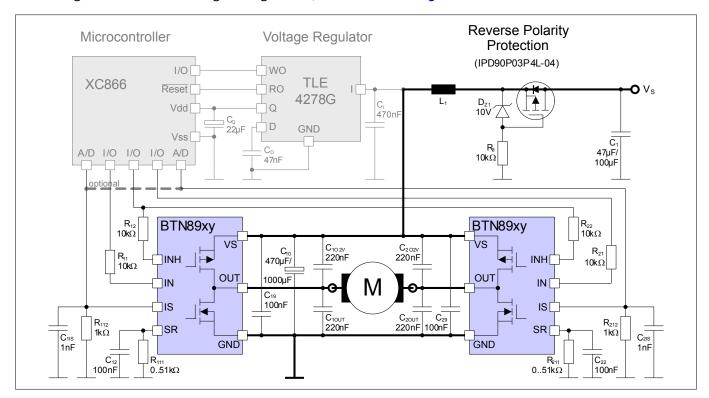

# 1.2 H-Bridge configuration for bidirectional motor control

With the NovalithIC<sup>™</sup> family, it is easy to build an H-bridge for bidirectional DC motor control by simply combining two devices in H-bridge configuration, as it is shown in *Figure 3*.

Figure 3 Application circuit for a bidirectional motor with BTN8962/82 H-bridge

# BTN8960 /62 /80 /82

# **High Current PN Half Bridge**

## **Parasitic Inductance**

#### **Parasitic Inductance** 2

In high-current applications, which the NovalithIC<sup>™</sup> family is designed for, special care must be taken for parasitic inductors. The same is valid in case of very high frequencies, which are interesting with regard to EMC considerations.

Each kind of wire in the application is an inductor, e.g. PCB wires, bond wires, etc. The wire inductance can be estimated with

- 1mm PCB wire length approximately 1.2 nH

- 1 PCB via approximately 1 nH

The voltage drop of a wire can be calculated in the following way:

$$U_L = L \cdot \frac{\mathrm{d}I}{\mathrm{d}t}$$

## **Equation 1**

As can be seen from this equation, care must be taken with the parasitic wire inductors with increasing current and decreasing switching time. The NovalithIC<sup>™</sup> is designed to switch high currents very quickly. This means in applications with Novalith $IC^{\text{T}}$ , the parasitic inductors are relevant and special care must be taken.

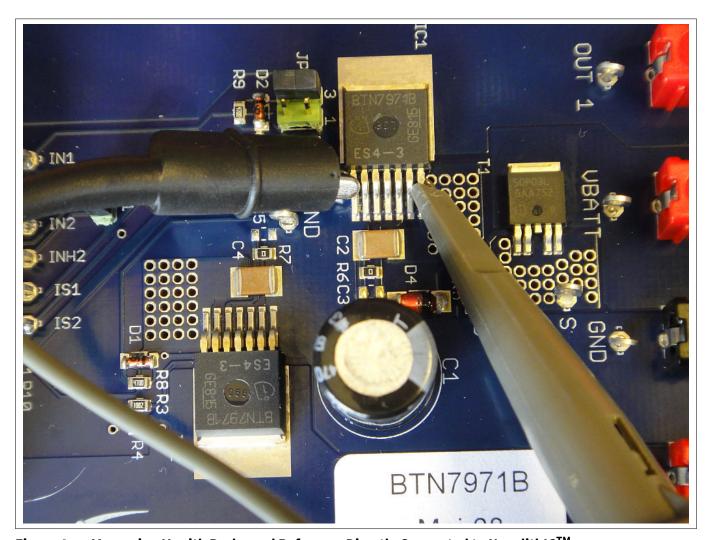

## Measuring signals at NovalithIC™ 2.1

The parasitic inductance also has an influence on the measurement results. To measure the true signals at the NovalithIC<sup>™</sup> it is mandatory to position the measurement probes directly at the device, as it is shown in *Figure 4*. The probe is connected directly to the  $V_s$ -pin of the NovalithIC<sup> $^{\text{T}}$ </sup> and the reference signal directly to the GND-pin of the device.

# infineon

# **Parasitic Inductance**

Figure 4 Measuring  $V_s$  with Probe and Reference Directly Connected to NovalithIC<sup>TM</sup>

Doing so enables to monitoring of the NovalithIC<sup>™</sup> supply voltage when high currents are switched. For example when a short-circuit current is switched, this is the only possibility for measurement if the DC-link capacitor is sufficient to keep the supply voltage above the undervoltage detection threshold (also see *Chapter 3.2*).

## **Design Guideline** 3

For a safe and sufficient motor control design, discrete components are needed. Some of them must be dedicated to the motor application and some to the NovalithIC<sup>™</sup>.

#### 3.1 Schematic and layout design rules

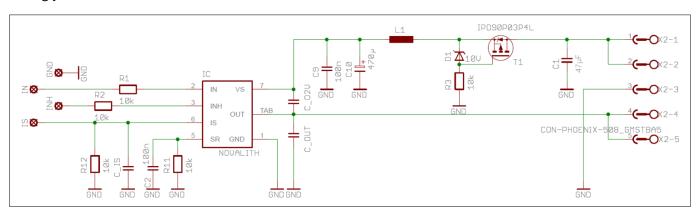

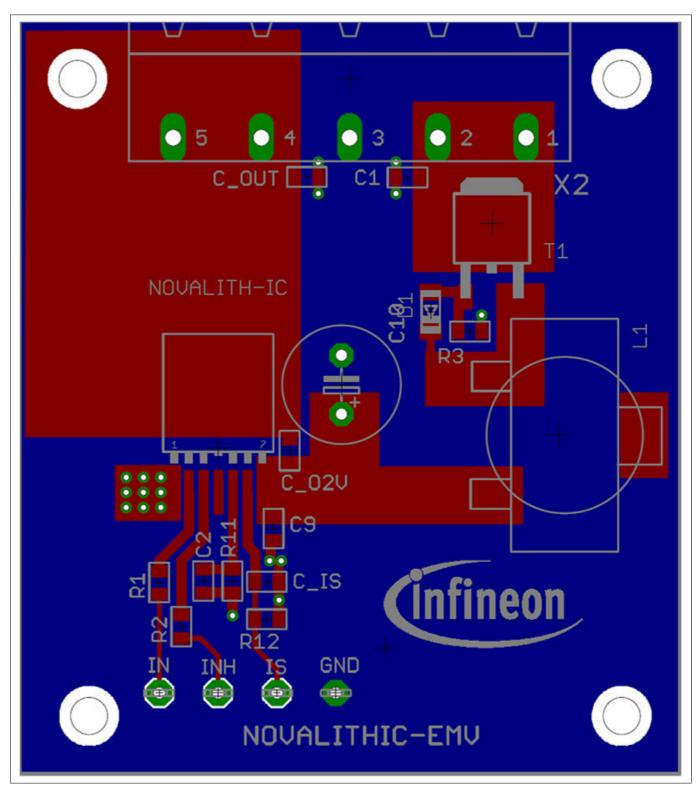

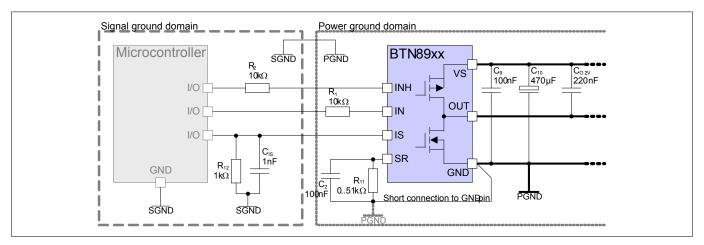

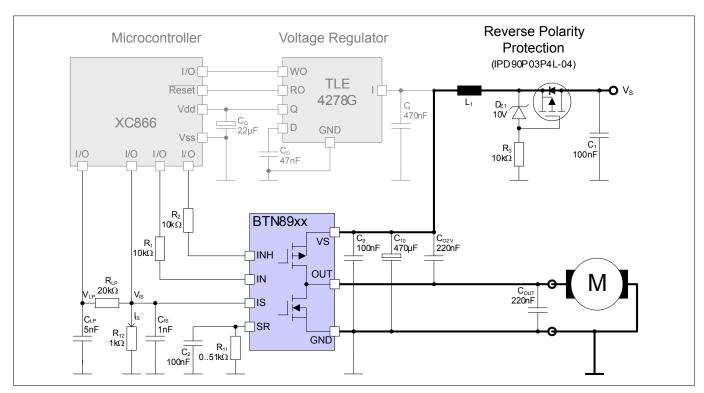

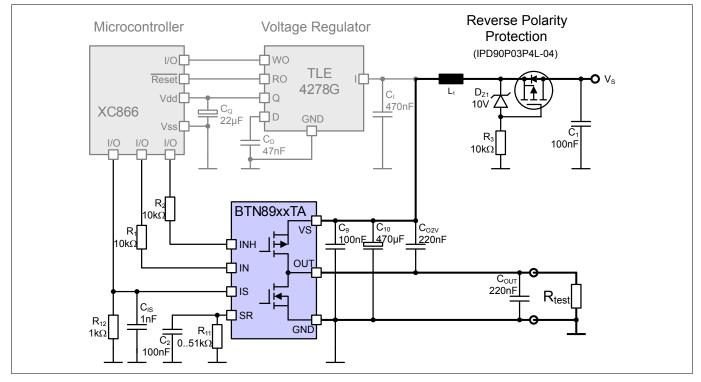

Figure 5 and Figure 6 show an example of a schematic plus a corresponding layout for a half-bridge motor control with NovalithIC<sup>™</sup>.

The best performance in terms of parasitic inductance and EMC can be reached with a GND plane, which we strongly recommend be used.

Figure 5 Example of a half-bridge schematic with NovalithIC<sup>TM</sup>

Important design and layout rules:

The basis for the following items is the parasitic inductance of electrical wires, as described in *Chapter 2*.

- C10, so called DC-link capacitor: This electrolytic capacitor is required to keep the voltage ripple at the V<sub>S</sub>pin of the NovalithIC<sup>™</sup> low during switching operation (the measurement procedure for the supply voltage is described in *Chapter 2.1*). It is strongly recommended that the voltage ripple at the NovalithIC $^{^{\top}}V_s$ -pin to GND-pin be kept below 1 V peak-to-peak. The value of C10 must be aligned accordingly. See **Equation 10**. Most electrolytic capacitors are less effective at cold temperatures. It must be assured that C10 is also effective under the worst case conditions of the application. The layout is very important. As shown in Figure 6, the capacitor C10 must be positioned with very short wiring at the NovalithIC<sup>™</sup>. This must be done to keep the parasitic inductors of the PCB-wires as small as possible.

- C9: This ceramic capacitor supports C10 to keep the supply voltage ripple low and covers the fast transients between the V<sub>s</sub>-pin and the GND-pin. The value of this ceramic capacitor must be chosen so that fast V<sub>s</sub>ripple at the NovalithIC<sup>™</sup> does not exceed 1 V peak-to-peak. The layout wiring for C9 must be shorter than for C10 to the NovalithIC<sup>™</sup> to keep the parasitic PCB-wire inductance as small as possible. In addition the parasitic inductance could be kept low by placing at least two vias for the connection to the GND-layer.

- C\_O2V: This ceramic capacitor is important for EMI in order to avoid entering electromagnetic disturbances into the NovalithIC<sup>™</sup> as much as possible. Good results have been achieved with a value of 220 nF. In terms of layout, it is important to place this capacitor between "OUT" and "V<sub>s</sub>" without significant additional wiring from  $C_02V$  to the  $V_s$ - and OUT-line.

- C\_OUT: This ceramic capacitor helps improve the EMI and the ESD performance of the application. Good results have been achieved with a value of 220 nF. To keep the RF and ESD out of the board, the capacitor is most effective when positioned directly on the board connector. In addition, the parasitic inductance could be kept low by placing at least two vias for the connection to the GND-layer.

- C1: This ceramic capacitor helps to improve the EMI and the ESD performance. In combination with L1 and C10 plus C9 a Pi-filter improves the electromagnetic emission on the  $V_s$ -line. Layout rules are the same as for C\_OUT.

# **i**nfineon

# **Design Guideline**

Example of an half-bridge layout with NovalithIC<sup>TM</sup> (not true to scale) Figure 6

# Other components:

- T1, D1 and R3: Reverse polarity protection. See *Chapter 3.5*.

- R11: Slew rate resistor according to data sheet.

- C2: Stabilization for slew rate resistor (R11).

- R12: Resistor to generate a current sensing voltage from the IS current.

# infineon

# **Design Guideline**

- C\_IS: Ceramic capacitor for EMI improvement. GND connection with at least two GND-vias. A good value is 1 nF. In case the current should be measured during the PWM-phase, this capacitor must be adapted to the ON-time inside the PWM-phase.

- R1 and R2: Device protection in case of μC pins shorted to V<sub>s</sub>.

# 3.2 DC-link capacitor

For the stability of the DC-link voltage a sufficient capacitor is mandatory (in *Figure 2*, *Figure 3* and *Figure 5* it is C10). This is one of the most important component in a motor design with semiconductor switches.

The DC-link capacitor could be insufficient, because:

- The capacitor value is too small.

- The ESR of the capacitor is too high.

- When cold the capacitor value is too small.

- The distance between the DC-link capacitor and the NovalithIC<sup>™</sup> is too large.

- The wiring between the DC-link capacitor and the NovalithIC<sup>™</sup> is too long (see Chapter 2).

The value must be chosen carefully, taking the undervoltage toggling into account, which is described in *Chapter 3.2.2*.

# 3.2.1 Calculation of the DC-link capacitor and Pi-filter

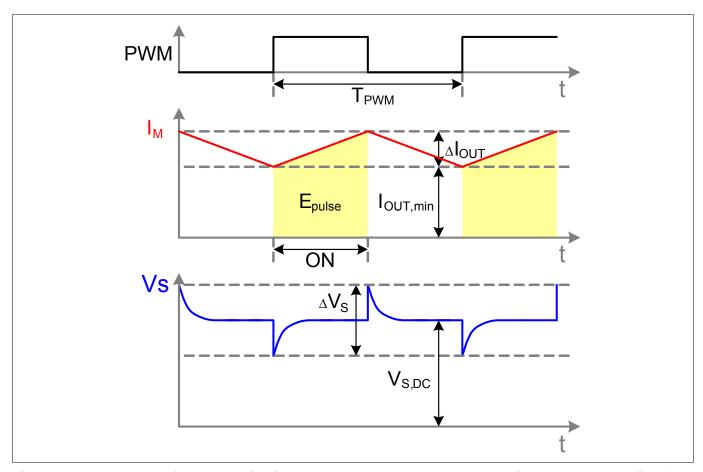

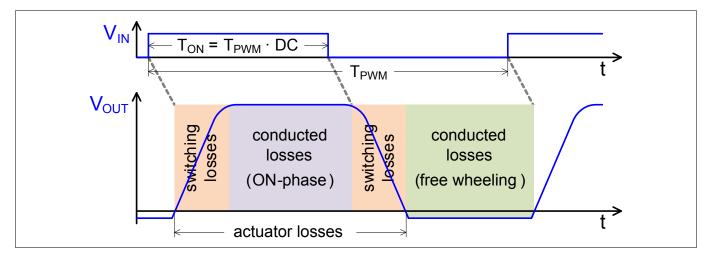

As already mentioned in the design- and layout-rules of *Figure 5* the voltage ripple at the NovalithIC $^{\text{T}}V_s$ -pin must not exceed 1 V peak-to-peak. The necessary DC-link capacitor can be estimated in the following way: Motor control with PWM means for the DC-link voltage to provide energy pulses during the "ON-phase" of the PWM cycle. The DC-link pulses are shown in *Figure 7*.

This energy must be provided by the DC-link capacitor. This can generally be described with

$$E = \frac{1}{2} \cdot C \cdot V^2 = P \cdot T$$

# **Equation 2**

$$C = C_{DC-link}$$

## **Equation 3**

The voltage at the DC-link capacitor consists of the DC-part and the delta voltage from the supply ripple:

$$V = V_{S,\, \mathsf{DC}} + \Delta V_S$$

## **Equation 4**

The total power in this system consists of the DC-power plus the power of the energy pulse ( $E_{\text{pulse}}$ ), which provides the energy to the motor during the ON-phase of the half bridge.

$$P = P_{DC} + \Delta P$$

## **Equation 5**

The maximum pulse length is determined by the PWM frequency, theoretically at a duty cycle of 100%:

# **Design Guideline**

$$T = T_{\text{pulse}} = T_{\text{PWM}} = \frac{1}{f_{\text{PWM}}}$$

# **Equation 6**

Figure 7 PWM control (PWM = IN-pin-signal,  $I_M$  = motor current and  $V_S$  =  $V_S$ -pin-voltage @ NovalithIC)

Insertion of Equation 3 to Equation 6 into Equation 2

$$E = \frac{1}{2} \cdot C_{DC-link} \cdot (V_{S,DC} + \Delta V_S)^2 = (P_{DC} + \Delta P) \cdot T_{PWM}$$

# **Equation 7**

$$\frac{1}{2} \cdot C_{\text{DC-link}} \cdot \left( V_{S, \text{DC}}^2 + 2 \cdot V_{S, \text{DC}} \cdot \Delta V_S + \Delta V_S^2 \right) = P_{\text{DC}} \cdot T_{\text{PWM}} + \Delta P \cdot T_{\text{PWM}}$$

# **Equation 8**

# **Equation 9**

Finally the equation to calculate the DC-link capacitor is:

# **Design Guideline**

$$C_{DC-link} \ge \frac{\triangle P \cdot T_{PWM}}{V_{S, DC} \cdot \triangle V_{S}}$$

## **Equation 10**

Based on **Equation 2** and referring to the energy of on single pulse, as marked with  $E_{\text{pulse}}$  ( $\approx \Delta P \cdot T_{\text{PWM}}$ ) in **Figure 7**:

$$\Delta P = V_S \cdot I_{\text{nom}} \approx V_S \cdot \left(I_{\text{OUT, min}} + \frac{1}{2}\Delta I_{\text{OUT}}\right)$$

## **Equation 11**

The DC-link capacitor is primarily the energy buffer for the switching process of the PWM motor control. Secondly it is part of the Pi-filter. This means first the DC-link capacitor must be calculated according to **Equation 10**. Based on this, it is recommended that the second capacitor of the Pi-filter C1 be estimated with:

$$C_1 = \frac{1}{10} \cdot C_{DC-link} = \frac{1}{10} \cdot C_{10}$$

## **Equation 12**

Generally the border frequency of the L<sub>1</sub>-C<sub>1</sub>-filter is determined with

$$f_g = \frac{1}{2 \cdot \Pi \cdot \sqrt{L_1 \cdot C_1}}$$

## **Equation 13**

We recommend setting the border frequency  $f_g$  to half the value of the PWM -frequency  $f_{PWM}$ .

$$\boldsymbol{f}_g = \frac{1}{2} \cdot \boldsymbol{f}_{\text{PWM}} = \frac{1}{2 \cdot \Pi \cdot \sqrt{L_1 \cdot C_1}}$$

# **Equation 14**

$$\mathbf{L_1} = \frac{1}{\Pi^2 \cdot \mathbf{f_{PWM}}^2 \cdot \mathbf{C_1}}$$

# **Equation 15**

## **Summary**

- 1. Calculate the DC-link capacitor with *Equation 10*.

- 2. Calculate the other capacitor of the Pi-filter with *Equation 12*.

- **3.** Calculate the inductor of the Pi-filter with **Equation 15**.

- **4.** Do not forget the important layout rules and how to measure the supply voltage correctly.

# 3.2.2 Undervoltage toggling

The power supply cable of most modules in a car are several meters long. The longer the supply cable is, the higher its parasitic inductance. In addition, most modules have a Pi-filter at the supply line with a inductor for EMC reasons. The sum of the supply line inductances have a significant influence on the  $V_s$ -voltage. When switching the motor ON during a normal motor start or PWM control, with a insufficient DC-link capacitor the supply voltage drops below the undervoltage threshold and the NovalithIC $^{\text{TM}}$  is switched to tristate. The supply

13

# **Design Guideline**

voltage recovers above the undervoltage threshold and the NovalithIC<sup>™</sup> switches on again, again dropping below the undervoltage threshold ...

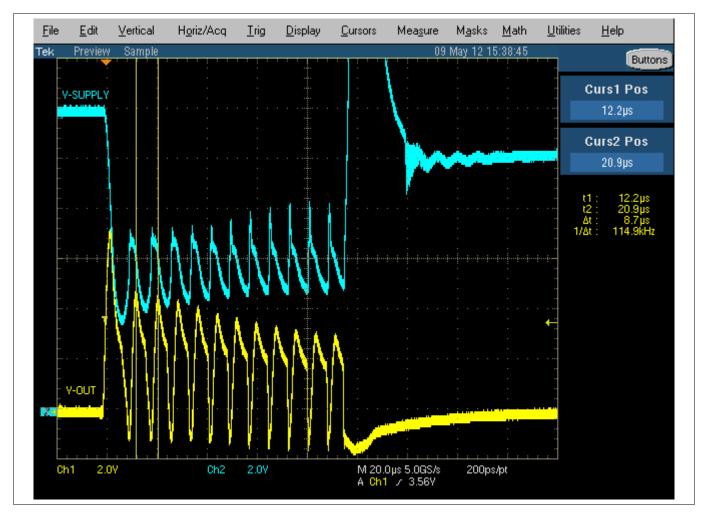

This effect can result in frequencies higher than 100 kHz, as is shown in *Figure 8*. The device will be damaged by the power dissipation of the switching losses, which is faster than the reaction time of the over temperature shut down, because of the high switching frequency.

The undervoltage toggling will be worse if the OUT is shorted to GND.

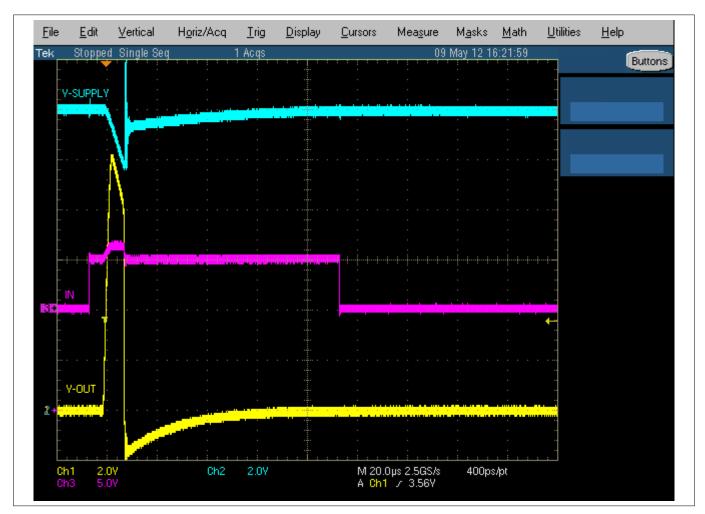

Figure 8 Undervoltage toggling started by short to GND and enabled by an insufficient DC-link capacitor

With a sufficient DC-link capacitor the supply voltage drop is limited so as not to reach the undervoltage threshold, as is shown in Figure 9.

Both measurements in Figure 8 and Figure 9 are conducted with the Infineon "NovalithIC Demo Board V2.1" with BTN7933. The "ON-time" is limed to 100 μs by the IN-signal, as shown in Figure 9. Only the DC-link capacitor is switched between the two measurements.

Figure 9 The sufficient DC-link capacitor avoided undervoltage -toggling in case of a short to GND

#### **Ground references** 3.3

Depending on the different functionalities, different ground references for each pin of the NovalithIC<sup>™</sup> have to be considered, especially in high current applications, in which ground shifts might occur due to parasitic inductances and line resistantaces of the PCB.

Based on the example schematic in *Figure 5*, the different ground reference concepts are illustrated in *Figure* **10**.

Figure 10 Simplified schematic illustrating the ground references for the signal ground (SGND) and power ground (PGND) of the NovalithICTM

Design rules for the ground reference:

- IS-pin: The reference ground for the current sense and failure flag detection is ideally the Analog-to-Digital Converter's / Microcontroller's ground as the IS-pin is a current source. If this is implemented, the absolute maximum ratings shall be respected, also in the case of a ground shift between the Microcontroller's (signal-) ground and the device's ground (GND-pin). Thus it is recommended to connect R12 and C\_IS to the signal ground (SGND) as shown in Figure 10 thus eliminating the influence of a ground shift.

- SR-pin: For the slew rate functionality the reference ground is the device's ground, the GND-pin. Thus R11 and C2 (in Figure 5 and Figure 10) should be placed close to the device and be connected directly to the device's ground with minimal wiring to prevent any influence of disturbance through ground shifts.

- IN/INH-pins: For the digital input pins IN and INH the internal ground reference is the GND-pin of the NovalithIC<sup>™</sup> thus it has to be obtained, that a ground shift between the Microcontroller's (signal-) ground, which is controlling the pins, and the device's ground (GND-pin) isn't influencing the switching behavior and the absolute maximum ratings are respected.

## **Driving inductive loads over long wires** 3.4

Inductive loads have a lowpass filter characteristic, like a motor. Because of this, the wire from the NovalithIC™ OUT to the motor injects electromagnetic disturbances into the OUT-pin. This antenna effect increases as the length of the motor wire increases.

The definition of a long motor wire strongly depends on the application and the environment. To provide a general idea, wire lengths of approximately 20 cm and more are considered as "long wire". The motor wire should therefore be as short as possible.

#### 3.4.1 **PWM operation**

In case of a long motor wire and PWM operation the electromagnetic emission (EME) increases with the wire length and with the switching speed (inversion of  $t_{r(HS)}$ ,  $t_{r(LS)}$ ,  $t_{f(HS)}$  and  $t_{f(LS)}$ ). In this case it is advantageous to reduce the switching speed with the slew rate resistor at the SR-pin (see *Figure 5*, R<sub>11</sub>). Reducing the switching speed has probably a impact on the PWM-frequency, which may needs to be adapted. In any case the power dissipation and the cooling concept needs to be reviewed. The slew rate resistor at the SR-pin should not exceed the max. slew rate resistor value of the data sheet  $R_{SR} \le 51 \text{ k}\Omega$ .

#### 3.4.2 **Current sense**

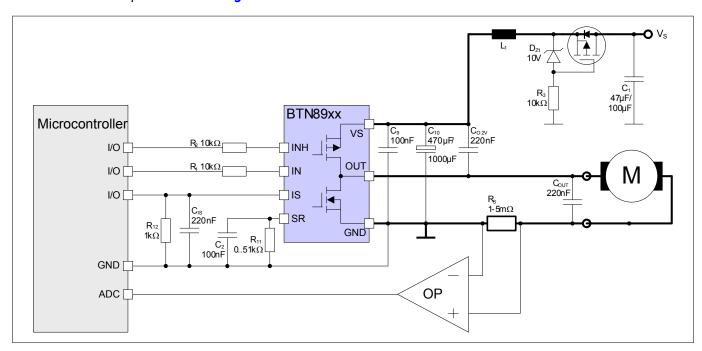

A long motor wire can pick up electromagnetic disturbances which could influence the current sense signal at the IS-pin. If a high accuracy of the current measurement is needed, it is recommended to use the IS-pin as status flag diagnosis and perform the current measurement with an external shunt plus current sense amplifier. An schematic example is shown in Figure 11.

Figure 11 BTN89xx with external current measurement

#### 3.5 Reverse polarity protection

The semiconductor technology of NovalithIC<sup>™</sup> used has a parasitic PN -diode from "GND" to the supply voltage pin " $V_s$ ". If the supply voltage is inverted, a huge current will flow through this parasitic PN -diode and will damage the device. With reverse polarity protection, the reverse current is not possible and the semiconductor components of the design are protected.

In the schematic in *Figure 5*, reverse polarity protection is provided with a P-channel MOSFET (IPD90P03P4L-04), a zener-diode ( $D_1$ ) and a resistor ( $R_3$ ).

Normal operation  $V_s > GND$ :

- P-MOSFET OFF: The application is supplied by the body-diode of the reverse polarity protection transistor (IPD90P03P4L-04), e.g. in case of a power-up. The status "P-MOSFET ON" will quickly be reached.

- P-MOSFET ON: After the power-up in which the body diode was used as a supply path, the zener diode plus the resistor will generate a gate-source voltage in the range of 10 V and the P-MOSFET is in ON-state. Only the R<sub>DS.on</sub> is in the power supply path.

Reverse polarity condition  $V_s$  < GND:

The gate source voltage of the reverse polarity protection transistor is continuously "LOW" and the transistor is switched OFF. No current can flow in this state. The application will not be damaged.

#### Cooling 3.6

The NovalithIC $^{\text{T}}$  half-bridge, driving high current generates power dissipation. These are  $R_{\text{ON}}$  losses and switching losses in case of PWM control, which heat up the device. For details, please see Chapter 6. The package PG-TO263-7-1 provides a low thermal resistance which can be combined with a heat sink on the PCB to avoid exceeding the absolute maximum temperature values of the data sheet.

# **Design Guideline**

In *Figure 6* a cooling area (brown top layer, where the NovalithIC<sup>™</sup>-OUT is connected) has already been drawn. Depending on the power dissipation, other thermal sources on the PCB and the ambient temperature, the cooling needs to be carefully adapted to each application.

In addition the reverse polarity protection transistor T1 (*Figure 5* and *Figure 6*) generates  $R_{DS,on}$  power losses and the cooling concept for this transistor must ensure that the device does not exceed the absolute maximum junction temperature.

# **Current Sense Improvement**

### **Current Sense Improvement** 4

The NovalithIC<sup>TM</sup> half-bridge-family has a current sense function with an IS-pin which provides the output current divided by a factor, so called dk<sub>ILIS</sub>. The precision of the current measurement could be significantly improved by eliminating the IS-offset, dk<sub>ILIS</sub>-production spread and respecting the temperature dependency of the dk<sub>II IS</sub>.

The table below provides an overview of possible combinations of procedures to reduce current measurement errors.

Table 1 **Current sense procedure and benefits**

| Procedures          |                           |                          | Load current tolerance |

|---------------------|---------------------------|--------------------------|------------------------|

| Offset compensation |                           |                          | ±28%                   |

| Offset compensation | Device dkILIS measurement |                          | ±10%                   |

| Offset compensation | Device dkILIS measurement | Temperature estimation   | ±6%                    |

| Offset compensation | Device dkILIS measurement | Temperature compensation | ±3%                    |

#### 4.1 Characteristic of the dk<sub>ILIS</sub>

The  $dk_{ILIS}$  has characteristic dependencies. The most important ones with respect to the supply voltage  $V_s$  and with respect to the temperature, are described in this chapter.

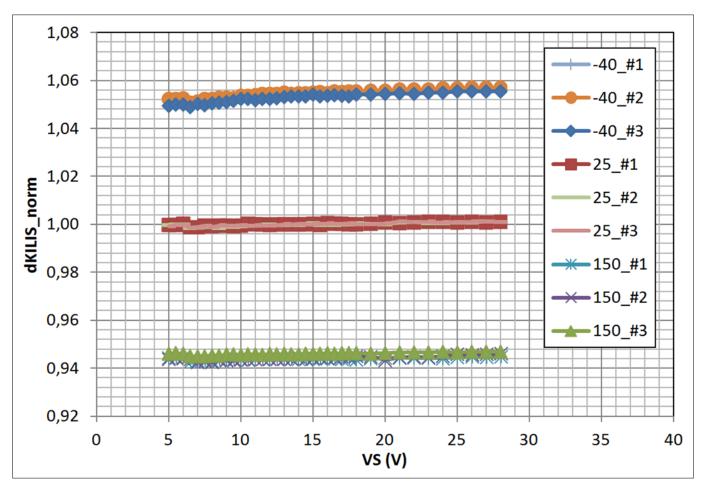

## Supply voltage dependency of dk<sub>ILIS</sub> 4.1.1

The dependency of the  $dk_{ILIS}$  of the supply voltage  $V_s$  is negligible, as **Figure 12** shows. This means the supply voltage can be ignored when calculating the load current.

# infineon

# **Current Sense Improvement**

$dk_{ILIS}$  vs. the supply voltage  $V_s$ Figure 12

#### 4.1.2 Life time drift

Life time tests of 1000 hours at 150°C with a dedicated device stress set up and with many devices from different production lots showed the dk<sub>ILIS</sub> is decreasing over life time up to -3%.

## Temperature drift of the dk<sub>ILIS</sub> 4.1.3

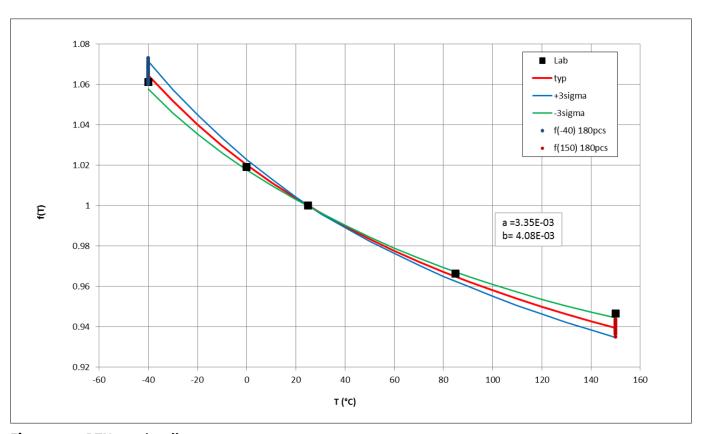

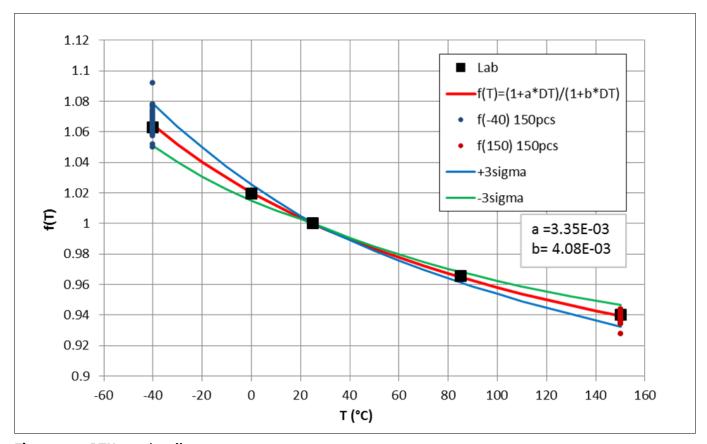

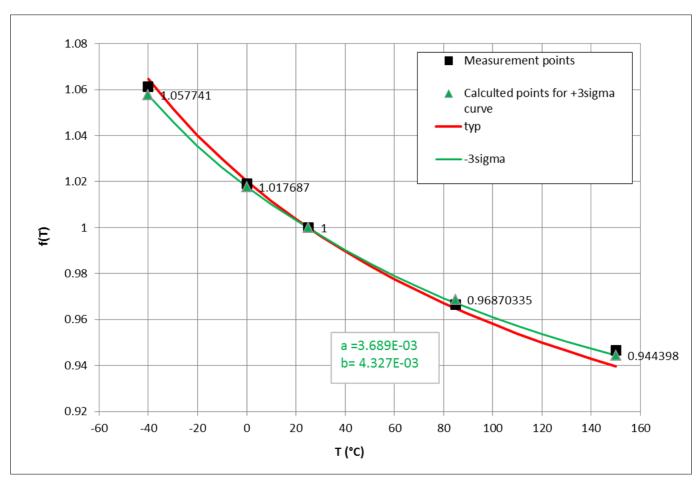

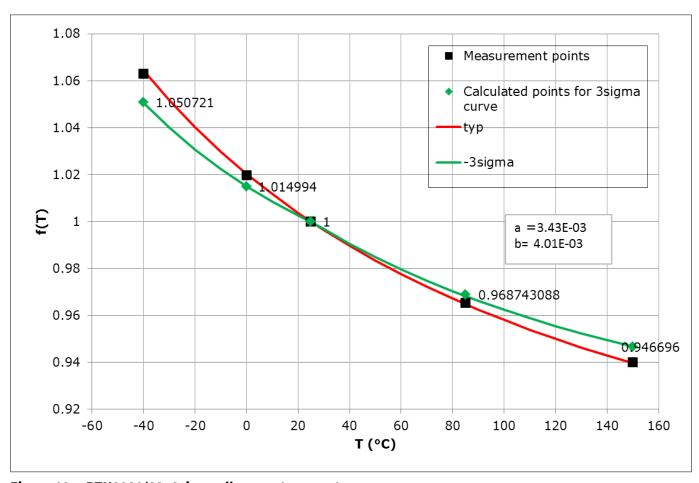

Figure 13 and Figure 14 show the characteristics of the dk<sub>ILIS</sub> vs. temperature and production spread with a scaling at 25°C, including a series of lab measurement points for one device.

Figure 13 BTN8960/62 dk<sub>ILIS</sub> vs. temperature

Figure 14 BTN8980/82 dk<sub>ILIS</sub> vs. temperature

# **Current Sense Improvement**

The function f(T) is dependent on the temperature coefficient of the shunt resistance in the control chip (a), the temperature coefficient of the shunt (b) and DT = T - 25 °C.

Table 2 Parameters in the fitting function

| a        | b        | DT     |

|----------|----------|--------|

| 3.35E-03 | 4.08E-03 | T-25°C |

The red curve in *Figure 13* and in *Figure 14* show the typical temperature dependent dK<sub>ILIS</sub>. It can be calculated by the following equation:

$$dK_{IIIS}(T) = dK_{IIIS}(25^{\circ}C) \cdot f(T)$$

The mean values and standard deviations in *Table 3* and *Table 4* are derived from measurements.

Mean values and standard deviations of BTN8960/62 at -40°C and 150°C Table 3

| T(°C)                 | -40°C    | 150°C    |

|-----------------------|----------|----------|

| Mean                  | 1.065    | 0.939    |

| Standard deviation(σ) | 2.28E-03 | 1.61E-03 |

Mean values and standard deviations of BTN8980/82 at -40°C and 150°C Table 4

| T(°C)                 | -40°C    | 150°C    |

|-----------------------|----------|----------|

| Mean                  | 1.065    | 0.939    |

| Standard deviation(σ) | 4.62E-03 | 2.38E-03 |

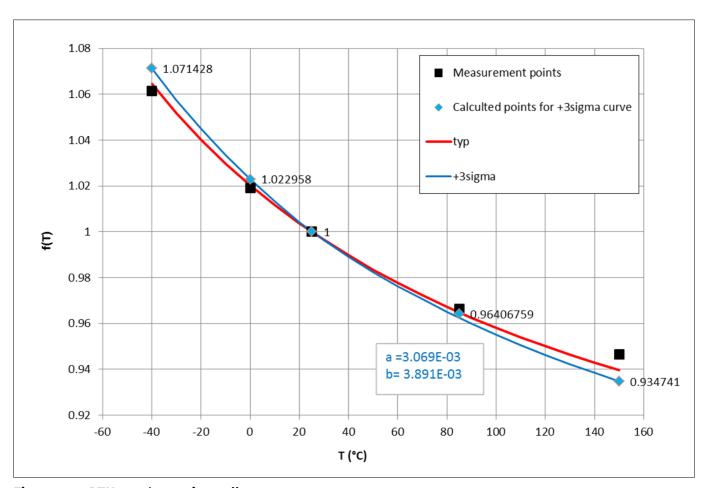

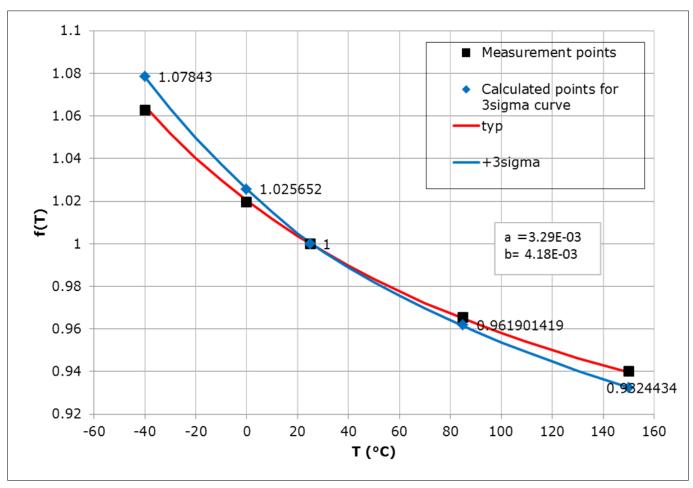

The dKILIS points on ±3sigma curves at different temperatures can be calculated:

- +3 sigma line in Figure 15 and Figure 16

- Case 1 (T < 25°C):  $f(T)_{+3\sigma} = f(T) + 3\sigma(-40^{\circ}C) * (T 25^{\circ}C) / (-40^{\circ}C 25^{\circ}C)$

- Case 2 (T ≥ 25°C) :  $f(T)_{+3\sigma} = f(T) 3\sigma(150$ °C) \* (T 25°C) / (150°C -25°C)

- -3 sigma line in Figure 17 and Figure 18

- Case 1 (T < 25°C) :  $f(T)_{-3\sigma} = f(T) 3\sigma(-40^{\circ}C) * (T 25^{\circ}C) / (-40^{\circ}C 25^{\circ}C)$

- Case 2 (T ≥ 25°C) :  $f(T)_{-3\sigma} = f(T) + 3\sigma(150$ °C) \* (T 25°C) / (150°C -25°C)

Figure 15 BTN8960/62 +3 sigma dk<sub>ILIS</sub> vs. temperature

Figure 16 BTN8980/82 +3 sigma dk<sub>ILIS</sub> vs. temperature

Figure 17 BTN8960 /62 -3 sigma dk<sub>ILIS</sub> vs. temperature

BTN8980/82 -3 sigma dk<sub>ILIS</sub> vs. temperature Figure 18

Based on the equation:  $f(T) = \frac{1+a^*DT}{1+b^*DT}$ , the ±3sigma temperature shift curves are fitted to the calculated points. The equation for the ±3sigma models are shown below:

- Equation for +3 sigma curves in Figure 15 and Figure 16:  $f(T)_{+3\sigma} = \{1 + a(+3\sigma)(T - 25^{\circ}C)\} / \{1 + b(+3\sigma)(T - 25^{\circ}C)\}$

- Equation for -3 sigma curves in Figure 17 and Figure 18:  $f(T)_{-3\sigma} = \{1 + a(-3\sigma)(T - 25^{\circ}C)\} / \{1 + b(-3\sigma)(T - 25^{\circ}C)\}$

Table 5 Parameters in equations for ±3sigma temperature shift curves of BTN8960/62

| Equation          | a         | b         |

|-------------------|-----------|-----------|

| $f(T)_{+3\sigma}$ | 3.069E-03 | 3.891E-03 |

| $f(T)_{-3\sigma}$ | 3.689E-03 | 4.327E-03 |

Parameters in equations for ±3sigma temperature shift curves of BTN8980/82 Table 6

| Equation          | a        | b        |

|-------------------|----------|----------|

| $f(T)_{+3\sigma}$ | 3.29E-03 | 4.18E-03 |

| $f(T)_{-3\sigma}$ | 3.43E-03 | 4.01E-03 |

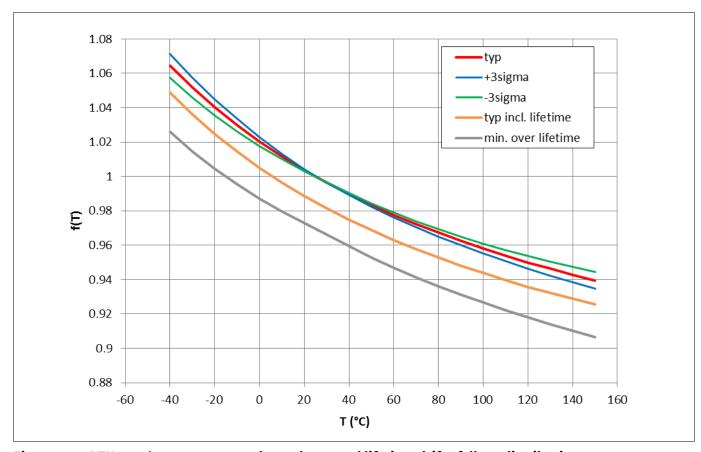

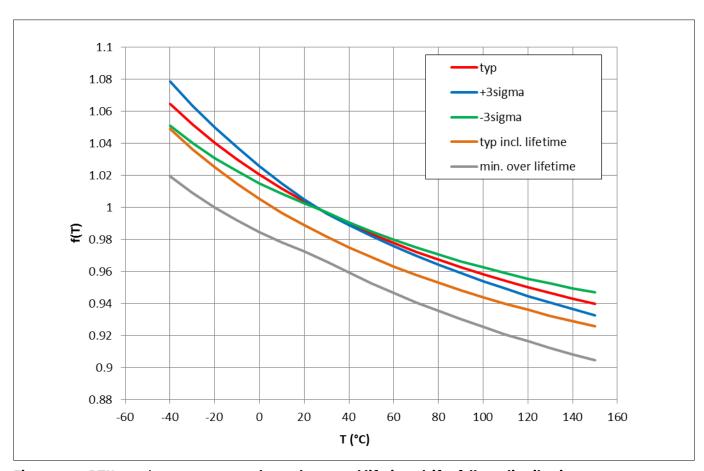

### Temperature drift of the dk<sub>ILIS</sub> including aging 4.1.4

If the aging of the devices are taken into account, the extrem value of dk<sub>ILIS</sub> over lifetime in *Figure 13* and in Figure 14 should be reduced by 3% as shown Figure 19 and in Figure 20. The orange line indicates the typical temperature drift of dk<sub>ILIS</sub> inculding the aging. The equations for the typical dk<sub>ILIS</sub> curve are shown below:

Case 1 (T<25°C):  $f(T) = (f(T)_{+3\sigma} + f(T)_{-3\sigma} * 097) / 2$ Case 2 (T≥ 25°C):  $f(T) = (f(T)_{-3\sigma} + f(T)_{+3\sigma} * 097) / 2$

The grey line indicates the minimum value over lifetime. The equations for the minimum dk<sub>ILIS</sub> curve are shown below:

Case 1 (T< 25°C):  $f(T) = f(T)_{-3\sigma} * 097$ Case 2 (T≥ 25°C):

$f(T) = f(T)_{+3\sigma} * 097$

BTN8960/62 temperature dependency and lifetime drift of dk<sub>ILIS</sub> distribution Figure 19

# infineon

# **Current Sense Improvement**

Figure 20 BTN8980/82 temperature dependency and lifetime drift of dk<sub>ILIS</sub> distribution

# 4.2 Offset compensation

The BTN89xy series is featured with an artificial offset current at the IS-pin. This is shown in Figure 21.

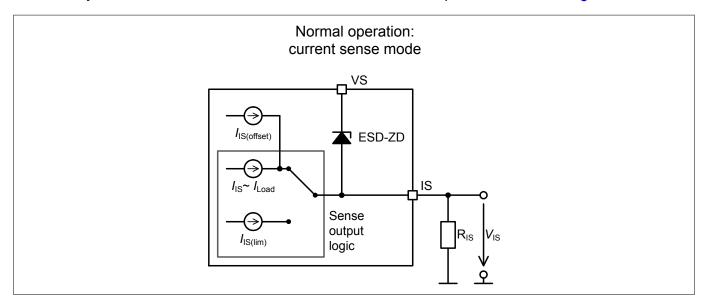

Figure 21 IS-Pin Internal Structure

With this structure, it is possible to always have a measurable offset at IS without a load current. This makes it easy to measure the offset with the microcontroller, store the offset value and process this in the current measurement procedure.

# **Current Sense Improvement**

The offset must be compensated to allow a precise current measurement with the IS-pin.

The offset should be compensated before activating the load. When an application such as a fuel pump runs constantly with PWM, you can perform the offset compensation when INH=high and IN=low. In the PWM-phase, the best measurement results are achieved just before the rising edge of the IN-signal.

With this procedure, the specified dk<sub>ILIS</sub> of ±28% could be reached, even for small load currents. This includes production spread, temperature dependency and aging. Most errors are caused by production spread, which could be compensated by measuring of the dk<sub>ILIS</sub> of each device (device-specific dk<sub>ILIS</sub>). Details of this approach are described in the relevant chapter.

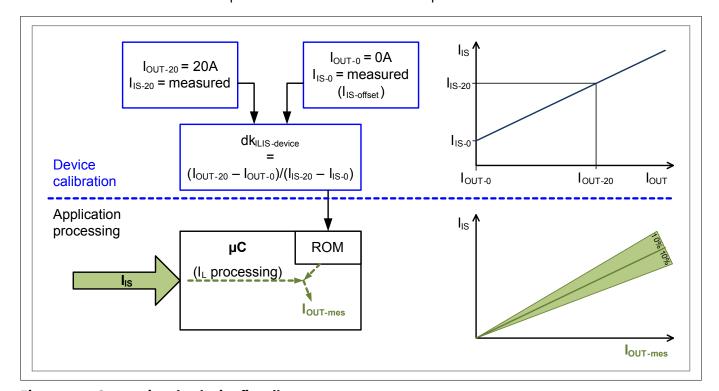

#### 4.3 Device specific dk<sub>II IS</sub>

With a measurement of the offset current and one IS-value at a certain load current at 25 °C (e.g. 20 A), it is possible to determine the individual dk<sub>ILIS-device</sub> and store it permanently to the microcontroller of the application. With this value, the graphs in Figure 13 and in Figure 14 and valid. The extreme values are indicated by the blue line (+3sigma):

- $dk_{II,IS-max-C} = 1.08$  (blue @ -40 °C)

- dk<sub>ILIS-min-H</sub> = 0.93 (blue @ 150 °C)

Taking into account the aging of the device (see Chapter 4.1.4) the minimum value of Figure 13 and Figure 14 (blue line) must be reduced by 3% (multiplying 0.97). This means the extreme values are as follows:

- $dk_{ILIS-max-C} = 1.08$  (blue @ -40 °C)

- $dk_{ILIS-min-H-old} = dk_{ILIS-min-H} * 0.97 = 0.9$

This could be assumed as an error of ±10% including temperature drift and aging.

In this case, the typical value should be assumed as follows:

$dk_{ILIS-tvp} = 0.99$

The device calibration could be implemented in the module test sequence.

Generating the device fine dk<sub>ILIS-device</sub>. Figure 22

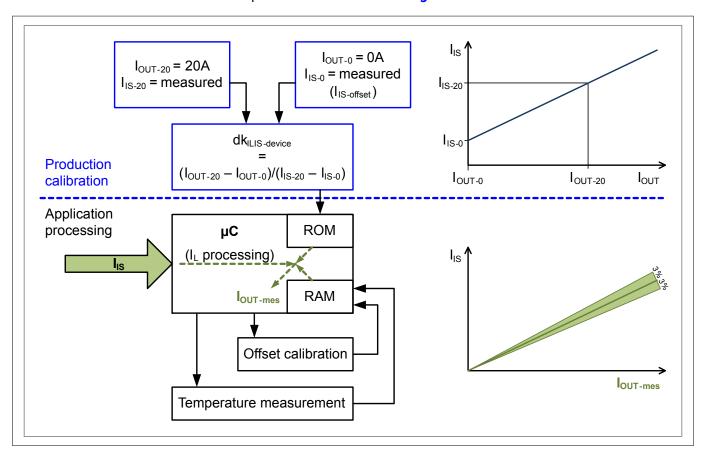

#### 4.4 **Device fine dk**<sub>ILIS</sub> and temperature compensation

On the other hand, the dk<sub>ILIS</sub> is dependent on the temperature, which is shown in *Figure 13* and *Figure 14*. These figures show a characteristic temperature drift with a low content of production spread. This makes it possible to measure the temperature on the PCB and reduce the temperature dependency by means of a calculation in the microcontroller. This procedure is illustrated in Figure 23.

Figure 23 Load current "IOUT" calculation with temperature compensation

Taking the extreme values from Figure 14:

- $dk_{II,IS-max-C} = 1.08$  (blue @ -40 °C)

- dk<sub>ILIS-min-C</sub> = 1.05 (green @ -40 °C)

- dk<sub>ILIS-max-H</sub> = 0.955 (green @ 150 °C)

- dk<sub>ILIS-min-H</sub> = 0.925 (blue @ 150 °C)

Multiplying the min. values with a factor of 0.97 (-3% aging) produces the following values:

- $dk_{ILIS-max-C} = 1.08$  (blue @ -40 °C)

- dk<sub>ILIS-min-C-old</sub> = 1.0185 (green @ -40 °C)

- $dk_{ILIS-max-H} = 0.955$  (green @ 150 °C)

- $dk_{ILIS-min-H-old} = 0.9$  (blue @ 150 °C)

Calculating the typical value for:

- $dk_{ILIS-tvp-C} = 1.05$

- $dk_{ILIS-tvp-H} = 0.928$

These values could be compensated with a temperature measurement and the characteristic from Figure 13 and *Figure 14* to provide the value of  $dk_{IIIS-typ} = 1$ .

With this compensation, the new min. and max. values are:

# **Current Sense Improvement**

- $dk_{ILIS-max-C-T} = 1.03 \text{ (blue @ -40 °C)}$

- $dk_{ILIS-min-C-old-T} = 0.9685 \text{ (green @ -40 °C)}$

- dk<sub>ILIS-max-H-T</sub> = 1.027 (green @ 150 °C)

- dk<sub>ILIS-min-H-old-T</sub> = 0.972 (blue @ 150 °C)

After temperature compensation, the min. and max. values are dk<sub>ILIS-min-H-old-T</sub> and dk<sub>ILIS-max-C-T</sub>.

Ultimately, a current measurement with a precision of ±3% could be achieved!

If higher tolerances are acceptable, the temperature measurement can be less precise.

### 4.4.1 An example of the I<sub>IS</sub> failure with a rough temperature estimation

Assuming the dk<sub>ILIS</sub> was calibrated during production at 25 °C, the I<sub>IS</sub> measurement failure could be reduced to ±6%, only by estimating if the temperature is above or below 25 °C. This estimation could be done e.g. by using the temperature characteristic of the I<sub>IS-offset</sub>, which is included in the data sheet.

Temperature below 25° C:

- $dk_{ILIS-max-C} = 1.08$  (blue @ -40 °C)

- $dk_{ILIS-min-25^{\circ}C} = 1$

Reducing the min. values with the -3% aging (multiplying with 0.97) the following values will be calculated:

- $dk_{ILIS-max-C} = 1.08$  (blue @ -40 °C)

- $dk_{ILIS-min-25^{\circ}C-old} = 0.97$

For temperatures above 25 °C the calculation method is essentially the same.

Ultimately, a current measurement with a precision of ±6% could be achieved without any external temperature measurement!

## IS-pin current sensing and fault detection 4.5

The BTN89xy provides several additional sense and diagnosis functionalities, which will be explained here.

## 4.5.1 **Current sensing concepts in applications**

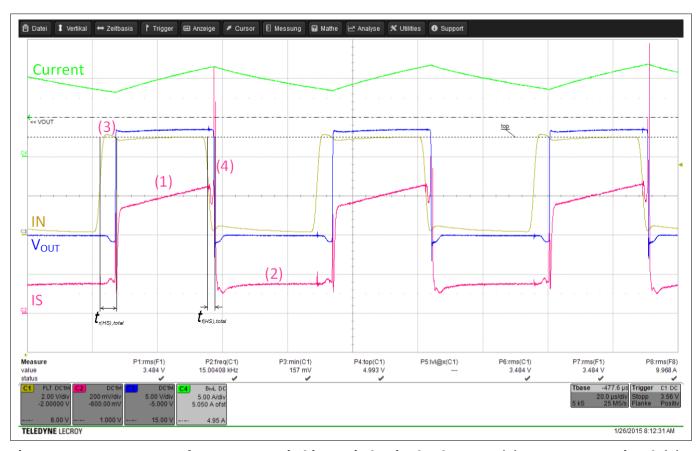

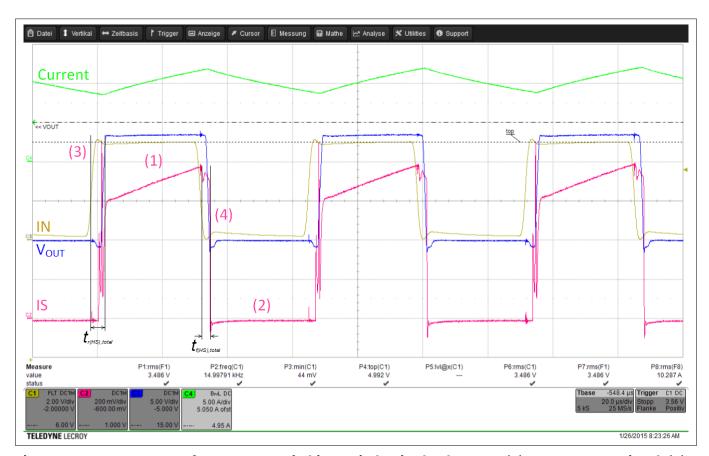

In comparison to its predecessor BTN79xy, the BTN89xy family's current sense output functionality has an advanced feature. For illustration purposes, both the BTN7960 and the BTN8960 were deployed in the same high-side switching scenario, where an inductive load to ground was toggled with a duty cycle of 50%. Both measurements were conducted with the Infineon "NovalithIC" Demo Board V2.2". The resulting measurements are shown in Figure 26 for the BTN7960 and in Figure 25 for the BTN8960. As described in Figure 21, both types have a similar behavior in the case of an error. Instead, their current sense functionality differs in normal operating mode. While the BTN79xy blanks the IS output to 0A when the high-side MOSFET is switched off, the BTN89xy provides the offset current  $I_{IS(offset)}$  instead.

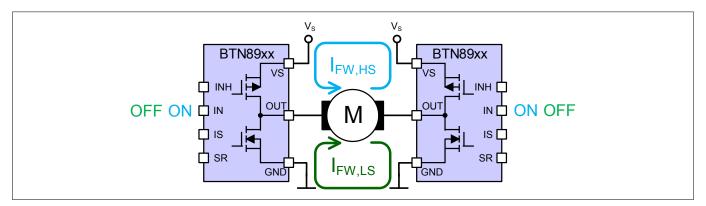

For monitoring purposes, the behavior of both the BTN79xy and the BTN89xy can be used for continuous current monitoring, even in freewheeling mode: In bi-directional motor applications with two BTN89xy, the freewheeling current can be monitored at the high-side MOSFET in forward direction. As shown in Figure 24, the freewheeling current  $I_{\text{FW.HS}}$  can be observed with both high-side MOSFETs being closed. In the scenario shown, the IS output of the left BTN89xy provides the current dependent signal, while the  $I_{\rm FW,HS}$  flows through the right BTN89xy in reverse direction.

Two freewheeling path options for bi-directional motor applications, implemented with two Figure 24 BTN89xy.

#### 4.5.1.1 BTN89xy - advanced current sense and fault diagnosis

In comparison to the BTN79xy, the BTN89xy does not mute the IS current sense output signal, which is always present. This results in the following behavior and additional diagnostic possibilities:

- Offset compensation of  $I_{IS(offset)}$ :

- If no current is flowing through the high-side MOSFET, the current sense offset  $I_{IS(offset)}$  can be monitored at the IS-pin. This can be ensured while the high-side switch is being switched off via the IN-pin and the freewheeling path doesn't go through the high-side MOSFET. If measured, this value can be used for an online offset calibration of  $I_{IS(offset)}$ , according to **Chapter 4.2**. In **Figure 25** this scenario is marked with (2). In the case of a fault condition, the IS-pin will provide a constant current of  $I_{IS(lim)}$ , which can be clearly distinguished from the lower offset current  $I_{IS(offset)}$ .

- Online calibration of  $I_{IS(offset)}$  and continuous current monitoring: If two BTN89xy devices are deployed in H-bridge configuration, the user can choose between either monitoring the freewheeling current or the online calibration of  $I_{\rm IS(offset)}$  by adapting the freewheeling path accordingly. An offset calibration of  $I_{IS(offset)}$  for both the left and right BTN89xy can be carried out by choosing a freewheeling path through both low-side MOSFETs, with the freewheeling current I<sub>FWLS</sub> displayed in Figure 24. As previously described, the current can be monitored continuously with a freewheeling current I<sub>FW.HS</sub> flowing through the two high-side MOSFETs.

Measurement of a BTN8960, switching an inductive load to GND. (1): current sense signal, (2): Figure 25 current sense offset current I<sub>IS(offset)</sub>

#### 4.5.1.2 BTN79xy current sense limitations

The current is sensed to the IS output pin, if the high-side (HS) MOSFET is activated and the INH and IN-pins are high (marked with (1) in *Figure 26*). This results in a current dependent IS output signal. For all other cases, the switching on (3) / off (4) phases of the high-side MOSFET and for low IN inputs (2), the IS output signal is 0 A, as shown in *Figure 26*. In the case of a fault condition, the IS-pin will provide a constant current of  $I_{\rm IS(lim)}$  that can be uniquely identified for a low IN-pin.

Measurement of a BTN7960, switching an inductive load to GND. (1): current sense signal, (2): Figure 26 current sense functionality switched off

#### 4.5.2 **Fault detection**

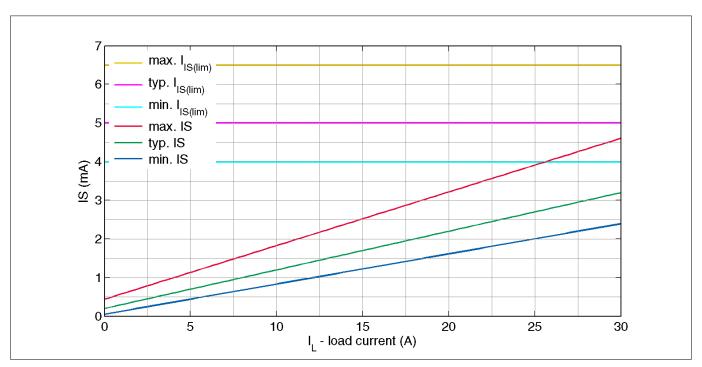

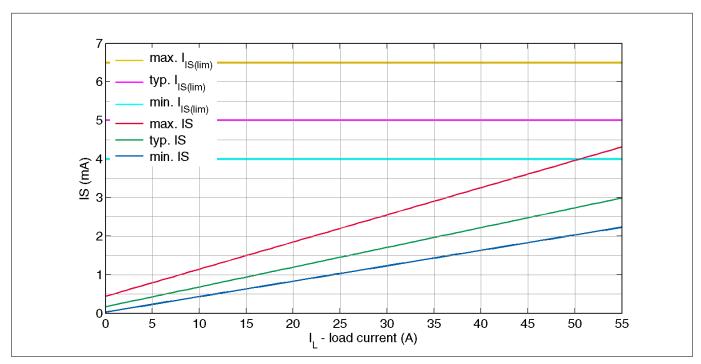

The current sense accuracy depends on the spread of the two parameters  $dk_{\rm ILIS}$  and  $l_{\rm IS(offset)}$ . The resulting maximal, typical and minimal behavior is displayed in Figure 27 for the BTN8960/62 and in Figure 28 for the BTN8980/82. Here, the limits for the sense current in fault condition  $I_{\rm IS(lim)}$  are also shown.

Behavior of the BTN8960/62's IS output pin for current sense and fault condition according to Figure 27 parameter tolerances

Figure 28 Behavior of the BTN8980/82's IS output pin for current sense and fault condition according to parameter tolerances

The possibility to distinguish whether a current sense signal or the constant sense current  $I_{IS(lim)}$ , indicating a fault condition, can be measured at the IS-pin is also an important issue. Therefore the fault distance between the two states is further considered. The combined (possible) output options for both states can be seen in Figure 27 for the BTN8960/62 and in Figure 28 for the BTN8980/82. For a worst case combination of the three parameters  $I_{IS(lim)}$ ,  $dk_{ILIS}$  and  $I_{IS(offset)}$ , provided in the data sheet for the given tolerances, there is a current range, where it is not possible to distinguish the right operation mode, whether there is a fault or not.

# **Current Sense Improvement**

The corresponding break-even points for the BTN8960/62 and BTN8980/82 can be calculated for the load current  $I_1$  accordingly:

$$I_L = dk_{ILIS} \cdot (I_{IS} - I_{IS(offset)}) = dk_{ILIS} \cdot (I_{IS(lim)} - I_{IS(offset)})$$

## **Equation 16**

$$I_L = 7, 2 \cdot 10^3 \cdot (4 \text{ mA} - 440 \,\mu\text{A}) \approx 25, 6 \,A$$

## **Equation 17**

$$I_L = 14 \cdot 10^3 \cdot (4 \text{ mA} - 385 \,\mu\text{A}) \approx 50, 6 \,A$$

## **Equation 18**

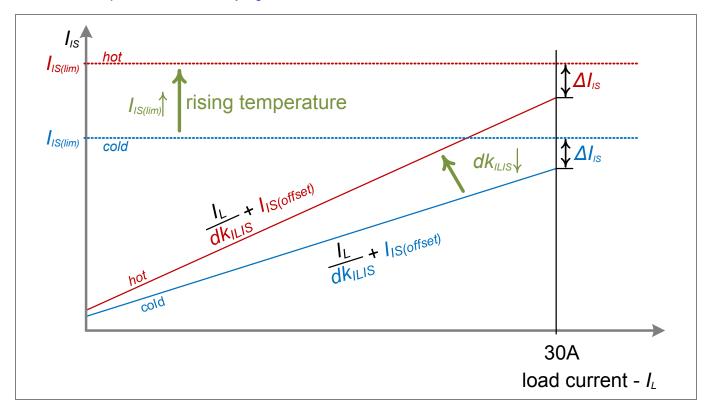

For such a system, it wouldn't be possible to distinguish easily between the fault condition current  $I_{\rm IS(lim)}$  and a current sense signal, for  $I_{\rm L} > 25$  A if the BTN8960/62 is used, and  $I_{\rm L} > 50$  A for the BTN8980/82. For a more precise consideration, also the temperature dependency of  $I_{\rm IS(lim)}$ ,  $dk_{\rm ILIS}$  and  $I_{\rm IS(offset)}$  has to be considered. For the given critical area for load currents  $I_{\rm L} > 25$  A, especially the parameters  $dk_{\rm ILIS}$  and  $I_{\rm IS(lim)}$  have the greatest influence. The temperature dependency of  $dk_{\rm ILIS}$  is described in **Chapter 4.1.3**, and of  $I_{\rm IS(lim)}$  in **Chapter 4.5.2.1**:

- For a rising temperature, the fault condition current  $I_{IS(lim)}$  increases, and vice versa.

- For a rising temperature the dk<sub>ILIS</sub> decreases and vice versa.

This relationship is also illustrated by *Figure 29*.

Figure 29 Illustration of the temperature dependencies of the fault distance and relevant parameters

Additionally the difference between the fault condition current  $I_{IS(lim)}$  and the sensed current  $I_{IS}(I_L)$  can be calculated as follows:

$$\Delta I_{\rm IS} = I_{\rm IS(lim)} - I_{\rm IS(lim)} - \left(\frac{I_L}{dk_{\rm ILIS}} + I_{\rm IS(offset)}\right)$$

#### **Equation 19**

**Equation 19** shows, that for a rising temperature, both  $I_{IS(lim)}$  and  $I_{IS}(I_L)$  (due to  $I_L / dk_{ILIS}$ ) increase.

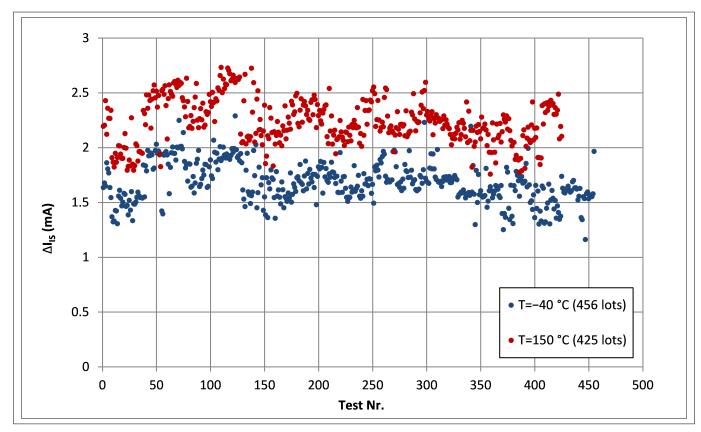

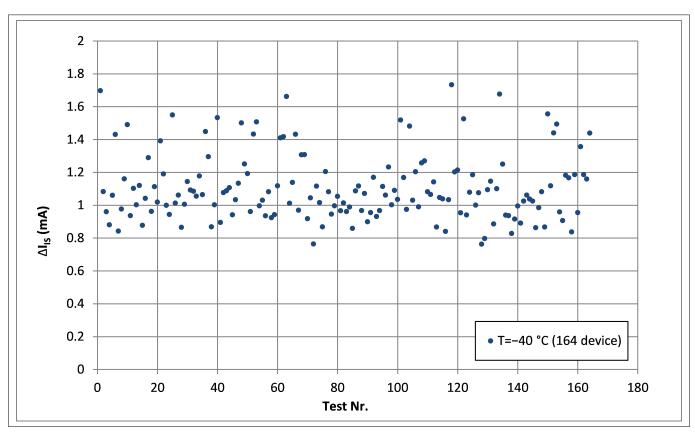

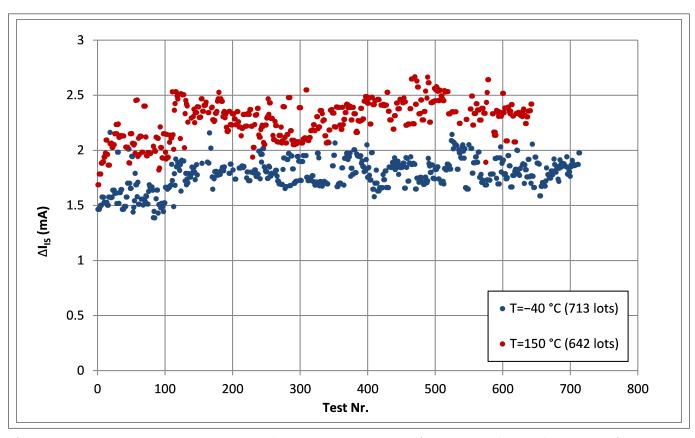

Combining the spread of  $dk_{\rm ILIS}$  and  $l_{\rm IS(lim)}$  over temperature, this behavior results in a  $\Delta l_{\rm IS}$  that, at the min. current limitation detection level  $I_{CLx0,min}$ , is typically above 0,5 mA for the BTN8960/62, as shown in *Figure 30* and Figure 31 and above 0,75 mA for the BTN8980/82, shown in Figure 32 and Figure 33. To summarize, we can say that it is possible to distinguish between a current sense signal  $I_{1S}(I_1)$  and a fault condition current  $I_{1S(lim)}$  for any temperature.

Figure 30 Temperature dependent  $\Delta I_{\rm IS}$  for BTN8960/62, according to Equation 19, for the median value of each lot and temperature at the min. current limitation detection level  $I_L = I_{CLx0.min} = 30$  A.

# **İ**nfineon

### **Current Sense Improvement**

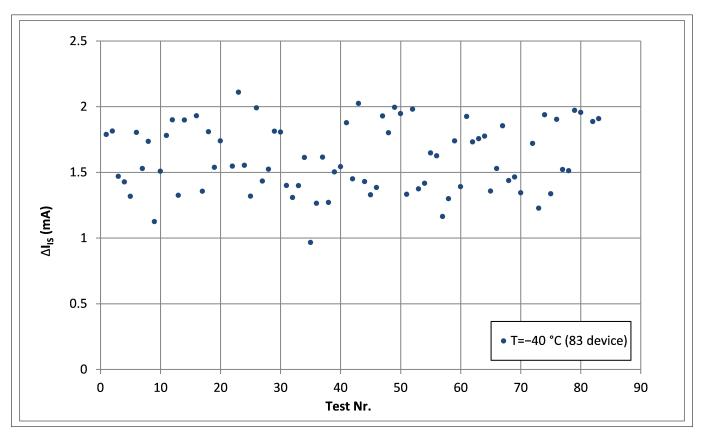

Temperature dependent  $\Delta I_{\rm IS}$  for BTN8960/62, according to Equation 19, calculated individually for each device of lot 447 for -40°C in Figure 30, with  $I_{\rm L} = I_{\rm CLx0,min} = 30$  A. Figure 31

# infineon

### **Current Sense Improvement**

Temperature dependent  $\Delta I_{\rm IS}$  for BTN8980/82, according to Equation 19, for the median value of each lot and temp. at the min. current limitation detection level  $I_{\rm L} = I_{\rm CLx0,min} = 55$  A. Figure 32

Figure 33 Temperature dependent  $\Delta I_{\rm IS}$  for BTN8982, according to *Equation 19* calculated individually for each tested device of lot 85 for -40°C in Figure 32, with  $I_L = I_{CLx0,min} = 55$  A.

#### Temperature drift of the IS-pin's current in fault condition $I_{IS(lim)}$ 4.5.2.1

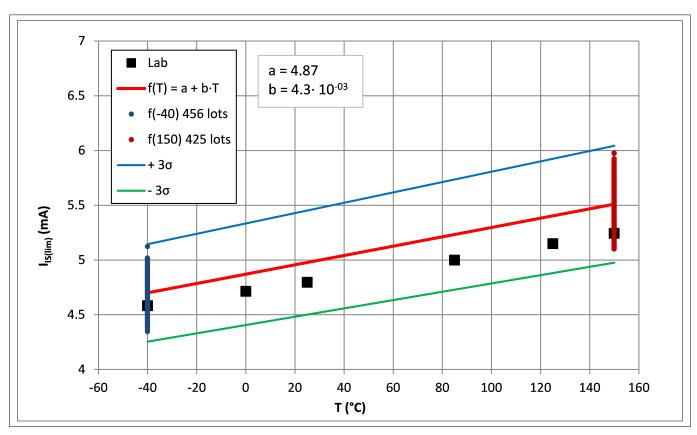

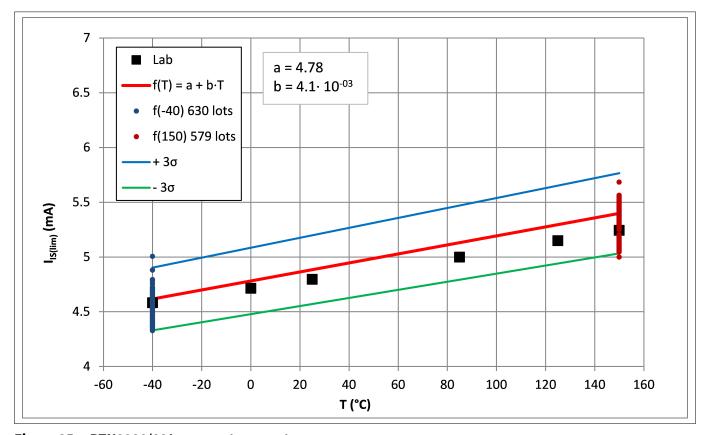

The characteristics of the  $I_{\rm IS(lim)}$  vs. temperature and production spread is shown in *Figure 34* for the BTN8960/62 and in *Figure 35* for the BTN8980/82, including a series of lab measurement points for one device.

Figure 34 BTN8960/62  $I_{IS(lim)}$  vs. temperature

Figure 35 BTN8980/82/<sub>IS(lim)</sub> vs. temperature

#### 4.5.2.2 **Failure detection flow chart**

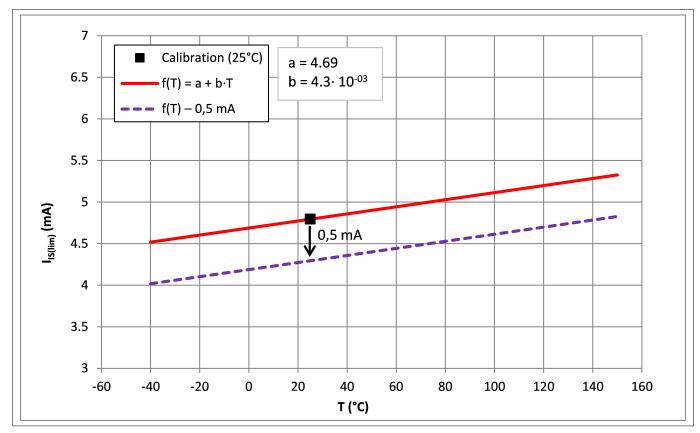

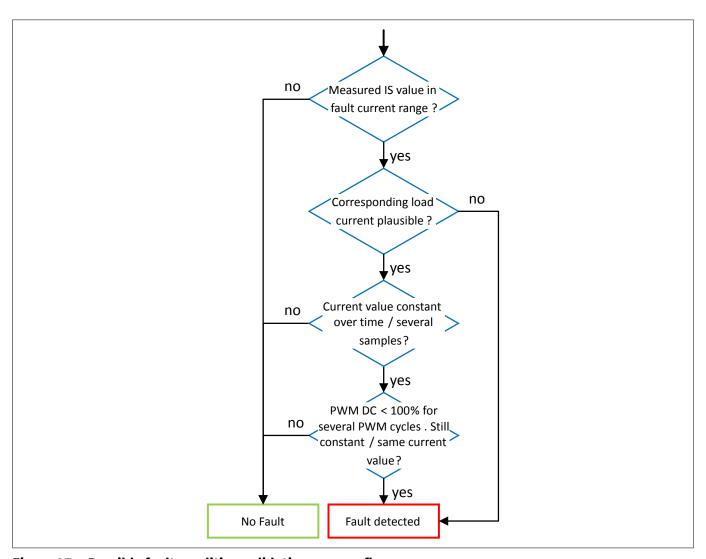

The consideration of  $\Delta I_{\rm IS}$  above provides a procedure for detecting fault conditions ( $I_{\rm IS(lim)}$ ), which is also summarized in Figure 36:

- Calibration of  $I_{\text{IS}(\text{lim})}(T_0)$  for a specific temperature  $T_0$ : Calculation of offset a with the given / typical slope b. Ideally measurement of  $I_{IS(lim)}(T_1)$  for a second temperature  $T_1$ , to perform a two point calibration and calculate both offset a and slope b for each individual device.

- Calculation of temperature dependent  $I_{\text{IS(lim)}}(T) = f(T)$  while the device is operating according to **Chapter** 4.5.2.1.

- If a current limit of  $I_{IS} = I_{IS(lim)}(T)$  0.5 mA is exceeded, a fault condition is detected.

Figure 36 One point calibration of  $I_{IS(lim)}$  and the resulting fault detection level over temperature for the BTN8960/62

Additional measures are available for ascertaining fault conditions. *Figure 37* describes a possible procedure. Carrying out a plausibility check after detecting a potential fault allows you to determine if a specific load current value in the current range of  $I_{IS(lim)}$  is possible at a specific operating point.

If this is the case, check whether that value stays in a certain range by performing a series of measurements. Depending on the application, the scattering of the current sense signal of an electric motor should be much higher than that of the constant fault current. An additional way of validating a fault condition is by measuring the IS output pin for a low IN input pin. As illustrated in *Figure 24*, the fault condition can be monitored by choosing the low-side freewheeling path, ensuring that no current is flowing through the high-side MOSFETs. The fault condition current  $I_{IS(lim)}$  can be clearly distinguished from the lower offset current  $I_{IS(offset)}$ . For applications running with a PWM duty cycle of 100%, the duty cycle must be reduced for certain cycles in order to validate a fault condition. This fault detection procedure is summarized in Figure 37.

Possible fault condition validation process flow Figure 37

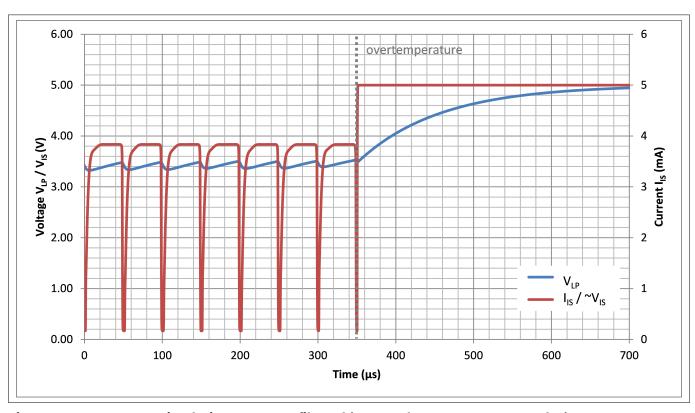

#### Lowpass filtered current sense signal 4.5.2.3

The procedure from *Figure 37* can be implemented with the sense current  $I_{IS}$  being measured by a phase current measurement, as described in *Chapter 5.5.2*, or by a being lowpass filtered. A lowpass filter, as shown in Figure 38, allows to perform an uncoupled ADC measurement from the PWM generation.

Application circuit including a lowpass filtered current sense signal for a monodirectional Figure 38 motor with BTN89xy

The fault distance increases here for a decreasing (effective) duty cycle DC (for a low-side freewheeling path). The average lowpass filtered  $I_{IS}$  signal can be estimated to:

$$V_{\text{LP}} \approx \left( \frac{I_{\text{L}}}{dk_{\text{ILIS}}} \cdot \text{DC} + I_{\text{IS(offset)}} \right) \cdot R_{12}$$

#### **Equation 20**

Based on a measured lowpass filtered voltage  $V_{LP}$  the load current  $I_L$  can now be estimated as follows:

$$I_L \approx \left(\frac{V_{\text{LP}}}{R_{12}} - I_{\text{IS(offset)}}\right) \cdot \frac{dk_{\text{ILIS}}}{DC}$$

### **Equation 21**

While the fault current is constant at  $I_{\rm IS(lim)}$ . A possible scenario is shown in *Figure 39*. Here, a load to ground was simulated. By changing the duty cycle for some periods, the lowpass filtered current sense signal should further decrease thus increasing the fault distance, as the average Motor current decreases and the time during which only the lower offset current is provided by the IS-pin increases.

Another way for fault detection is comparing the lowpass filtered signal  $V_{LP}$  with the  $I_{IS}$  /  $V_{IS}$  signal. As shown in **Figure 39**, the  $I_{IS}$  /  $V_{IS}$  signal, with  $V_{IS} = I_S \cdot R_{12}$ , is above  $V_{LP}$  during the PWM's ON-phases and with  $I_{IS} = I_{IS(offset)}$ below  $V_{LP}$  during the OFF-phase. By comparing the two signals ( $V_{IS}$  and  $V_{LP}$ ), a constant fault signal  $I_{IS(lim)}$  can be detected, as their are only transitions during normal operation.

Figure 39 BTN8982TA simulation: Lowpass-filtered ( $R_{LP}$  = 20 k $\Omega$ ;  $C_{LP}$  = 5 nF;  $R_{12}$  = 1 k $\Omega$ ) current sense signal  $I_{IS}$  for ADC measurement with the fault condition current  $I_{IS(lim)}$  from 350  $\mu$ s. PWM operation (20 kHz; DC = 90%) with load to ground.

# 5 Switching Timing

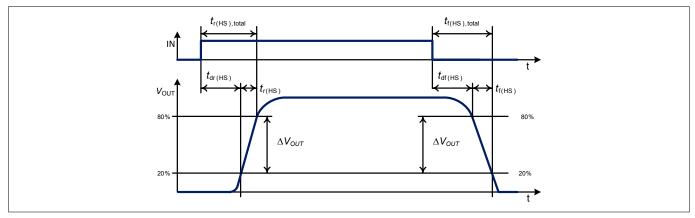

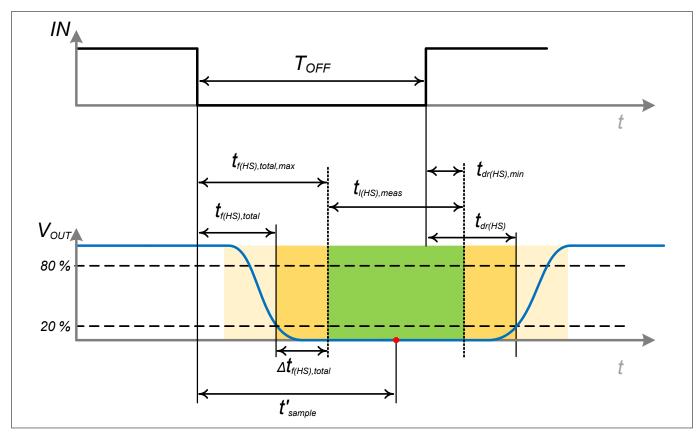

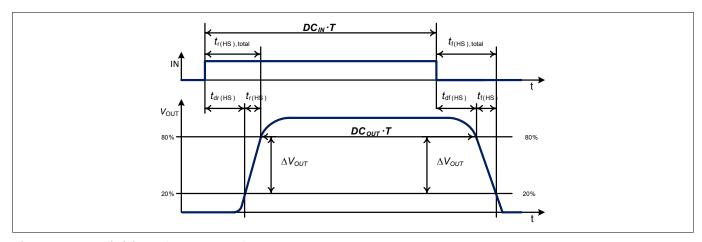

For the ADC measurement of the IS-pin, the timing behavior of the BTN89xy needs to be considered. As the current sense output is proportional to the current through the high-side switch, only the high-side switch behavior is considered here exemplary. The behavior of the low-side switch can be considered in an equal fashion. An overview of the rising and falling switching procedure is shown in *Figure 40*.

Figure 40 Timing behavior overview of a BTN89xy high-side switch

As shown in the data sheet, the time between the IN-pin rising from a 0 to 1 corresponding voltage level and the BTN89xy output voltage rising from (around) 0 V to 80 % of the final output voltage (typically:  $V_{\text{OUT}} \approx V_{\text{S}}$ ) can be summed up to the following delay, as shown in *Figure 40*:

$$t_{r(HS), \text{total}} = t_{dr(HS)} + t_{r(HS)}$$

#### **Equation 22**

For a falling edge on the IN input pin, the delay time between the falling edge of the IN input pin and the lower deviation of 20% of the  $V_{OUT} \approx V_S$  voltage level of the output pin OUT is considered:

$$t_{f(HS), \text{total}} = t_{df(HS)} + t_{f(HS)}$$

#### **Equation 23**

The timings and slew rates of the power switches can be adjusted by connecting a resistor  $R_{SR}$  between the SR-pin and GND-pin of the device. An overview about the, in this document provided, dependencies of the chosen resistor value  $R_{SR}$  on relevant timings is given in *Table 7*.

In the following two subchapter, the BTN8982 is described in Chapter 5.1 and the BTN8962TA in Chapter 5.2.

Table 7 Overview about the dynamic characteristic plots for BTN8982TA and BTN8962TA (R<sub>SR</sub> dependency)

| Pos. (in Data<br>Sheet) <sup>1)2)</sup> | Parameter               | Symbol              | Figure for<br>BTN8982TA | Figure for<br>BTN8962TA |

|-----------------------------------------|-------------------------|---------------------|-------------------------|-------------------------|

| High Side Switc                         | h                       |                     |                         |                         |

| 5.2.7                                   | Rise-Time of HS         | t <sub>r(HS)</sub>  | Figure 41               | Figure 53               |

| 5.2.8                                   | Switch ON Delay Time HS | t <sub>dr(HS)</sub> | Figure 42               | Figure 54               |

<sup>&</sup>lt;sup>1</sup> BTN8982TA/BTN8962TA Data Sheet, Rev. 1.0, 2013-05-17

<sup>&</sup>lt;sup>2</sup> Please note that the provided data is based on a limited number of production parts for a limited period of time.

# BTN8960 /62 /80 /82 High Current PN Half Bridge

Table 7 Overview about the dynamic characteristic plots for BTN8982TA and BTN8962TA (R<sub>SR</sub> dependency) (continued)

| Pos. (in Data<br>Sheet) <sup>1)2)</sup> | Parameter                | Symbol                   | Figure for BTN8982TA | Figure for<br>BTN8962TA |

|-----------------------------------------|--------------------------|--------------------------|----------------------|-------------------------|

|                                         | $t_{r(HS)} + t_{dr(HS)}$ | t <sub>r(HS),total</sub> | Figure 43            | Figure 55               |

| 5.2.9                                   | Fall-Time of HS          | $t_{f(HS)}$              | Figure 44            | Figure 56               |

| 5.2.10                                  | Switch OFF Delay Time HS | t <sub>df(HS)</sub>      | Figure 45            | Figure 57               |

|                                         | $t_{f(HS)} + t_{df(HS)}$ | $t_{f(HS),total}$        | Figure 46            | Figure 58               |

| Low Side Swite                          | ch                       |                          |                      |                         |

| 5.2.11                                  | Rise-Time of LS          | $t_{r(LS)}$              | Figure 47            | Figure 59               |

| 5.2.12                                  | Switch OFF Delay Time LS | t <sub>dr(LS)</sub>      | Figure 48            | Figure 60               |

|                                         | $t_{r(LS)} + t_{dr(LS)}$ | $t_{r(LS),total}$        | Figure 49            | Figure 61               |

| 5.2.13                                  | Fall-Time of HS          | $t_{f(LS)}$              | Figure 50            | Figure 62               |

| 5.2.14                                  | Switch ON Delay Time LS  | t <sub>df(LS)</sub>      | Figure 51            | Figure 63               |

|                                         | $t_{f(LS)} + t_{df(LS)}$ | $t_{f(LS),total}$        | Figure 52            | Figure 64               |

BTN8982TA/BTN8962TA Data Sheet, Rev. 1.0, 2013-05-17

<sup>&</sup>lt;sup>2</sup> Please note that the provided data is based on a limited number of production parts for a limited period of time.

### 5.1 BTN8982TA Switching Time Dependency on Slew Rate Resistance

Unless otherwise specified, the times are specified for  $V_S = 13.5 \text{ V}$ ,  $-40 \,^{\circ}\text{C} \leq T \leq 150 \,^{\circ}\text{C}$ ,  $R_{load} = 2 \,^{\circ}\text{C}$ ,  $30 \,^{\circ}\text{\mu}\text{H} < L_{load} < 40 \,^{\circ}\text{H}$  (in series to  $R_{load}$ ) and single pulse. The typical values are based on the test of all product in the past years. The maximum and minimum values are based on the  $\pm 3\sigma$  and are replaced by test limits in the case of exceeding the datasheet.

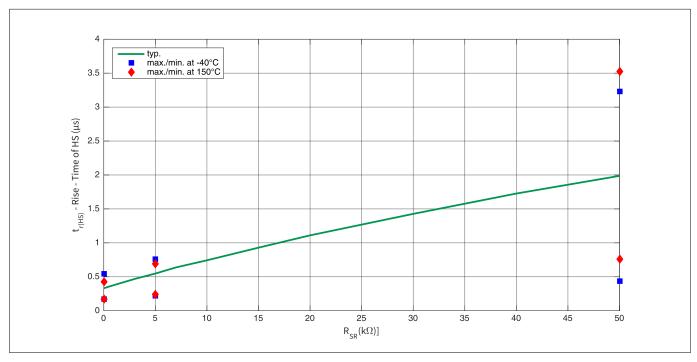

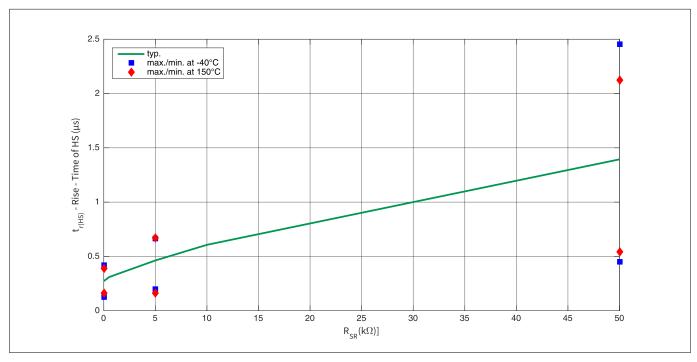

## 5.1.1 Timing behavior for rising edge on high-side switch

Figure 41  $t_{r(HS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the rise-time of the high-side switch of BTN8982TA

# **(infineon**

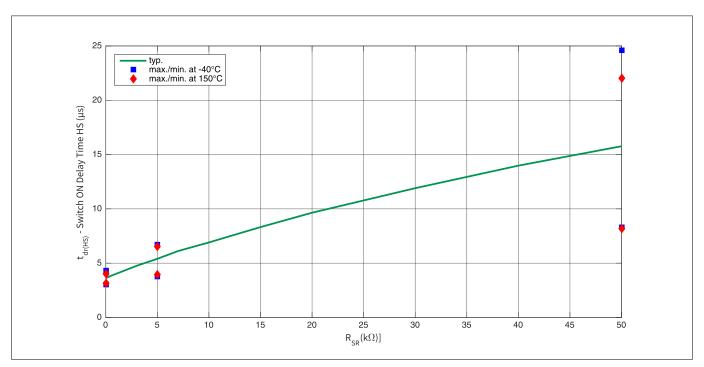

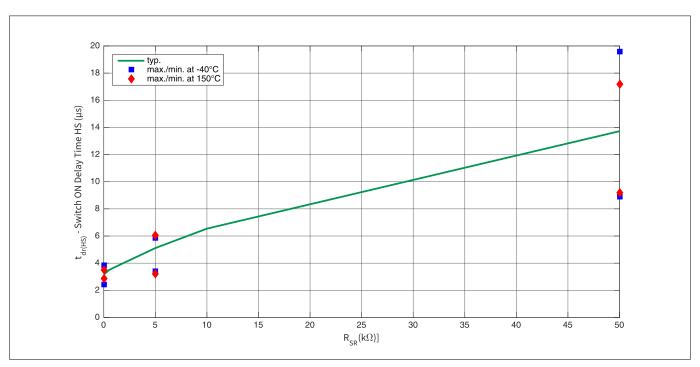

Figure 42  $t_{dr(HS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the switch ON delay time of the high-side switch of BTN8982TA

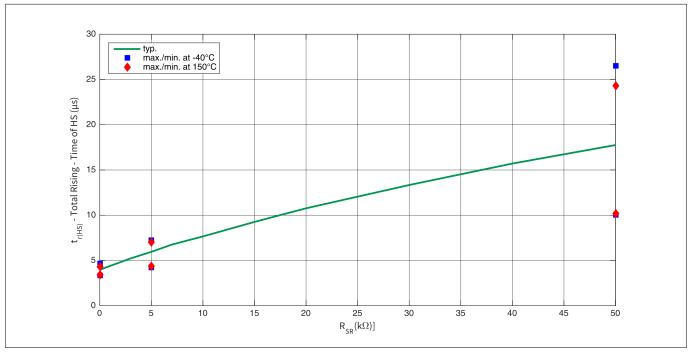

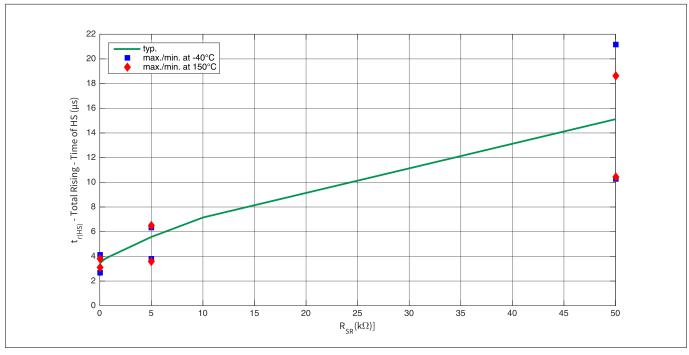

Figure 43 Dependency of the slew rate resistor  $R_{SR}$  on the total rising time of the high-side switch with  $t_{r(HS),total} = t_{r(HS)} + t_{dr(HS)}$ : BTN8982TA

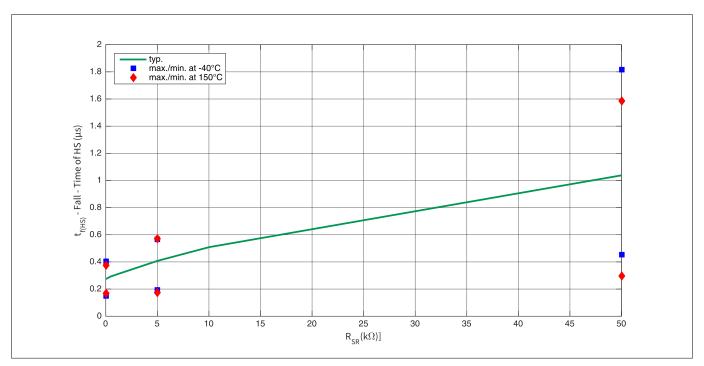

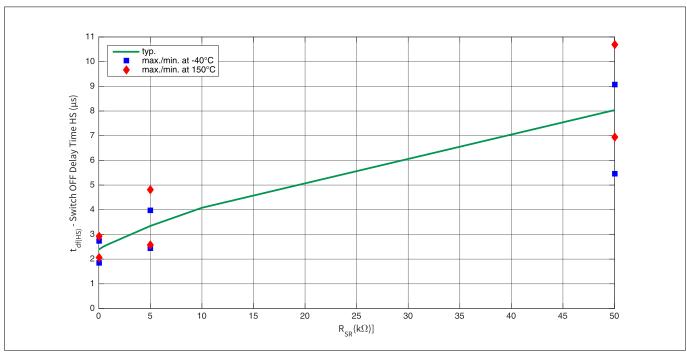

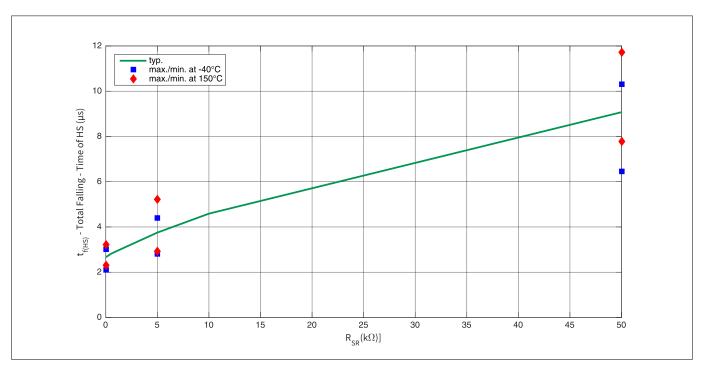

# 5.1.2 Timing behavior for falling edge on high-side switch

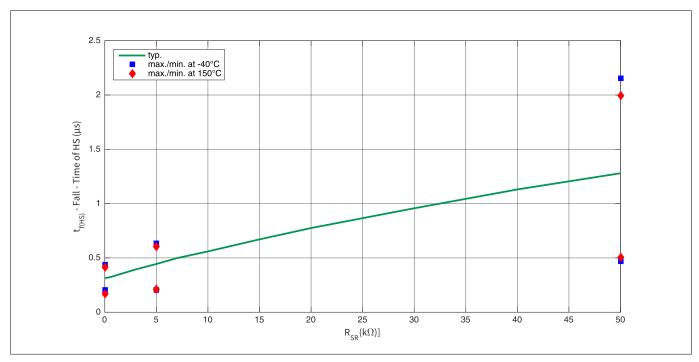

Figure 44  $t_{f(HS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the fall-time of the high-side switch of BTN8982TA

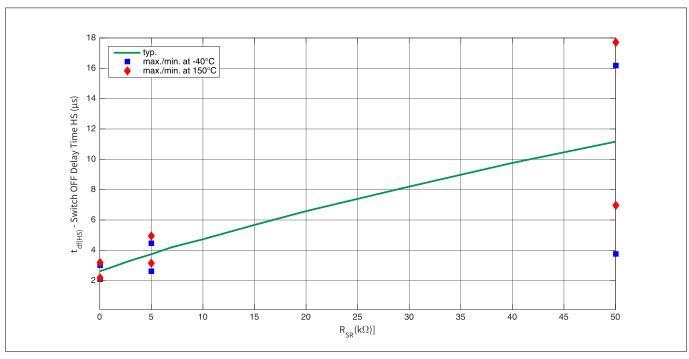

Figure 45  $t_{df(HS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the switch OFF delay time of the high-side switch of BTN8982TA

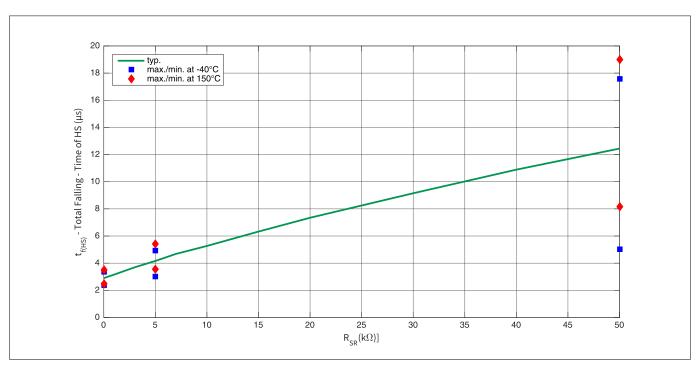

Figure 46 Dependency of the slew rate resistor  $R_{SR}$  on the total falling time of the high-side switch with  $t_{f(HS),total} = t_{f(HS)} + t_{df(HS)}$ : BTN8982TA

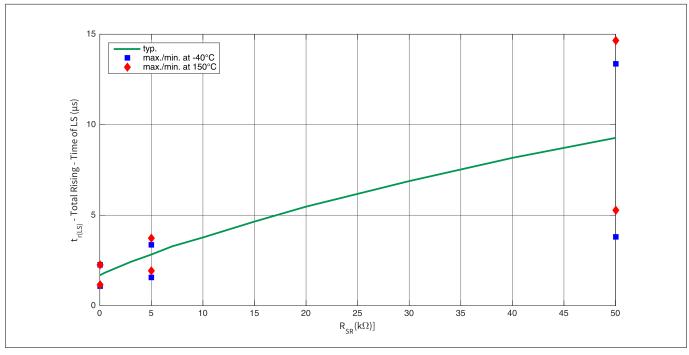

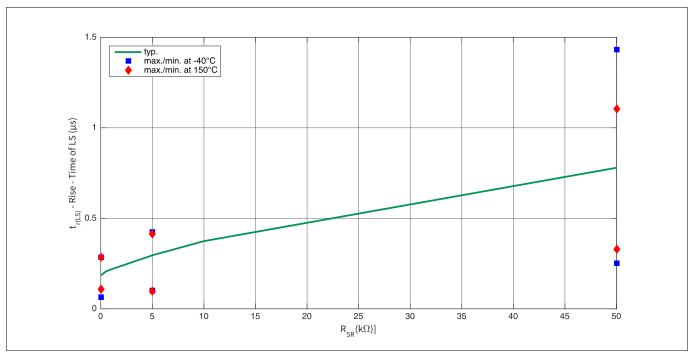

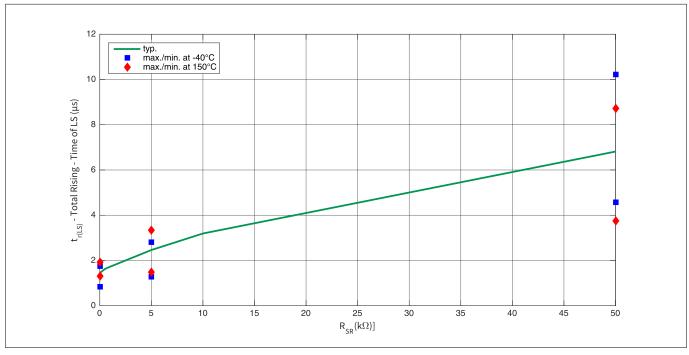

# 5.1.3 Timing behavior for rising edge on low-side switch

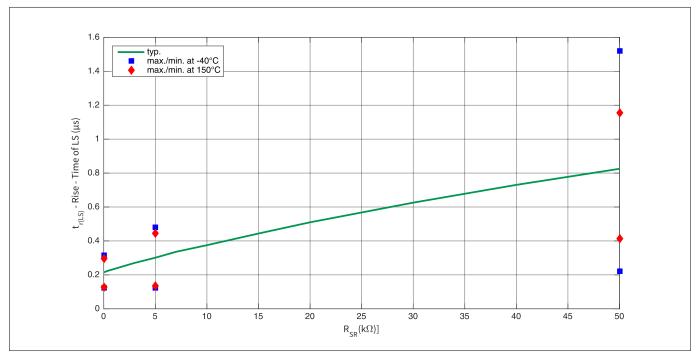

Figure 47  $t_{r(LS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the rise-time of the low-side switch of BTN8982TA

Figure 48  $t_{dr(LS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the switch OFF delay time of the low-side switch of BTN8982TA

Figure 49 Dependency of the slew rate resistor  $R_{SR}$  on the total rising time of the low-side switch with  $t_{r(LS),total} = t_{r(LS)} + t_{dr(LS)}$ : BTN8982TA

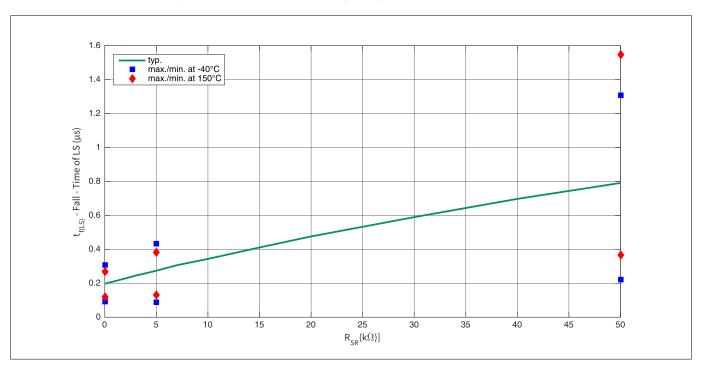

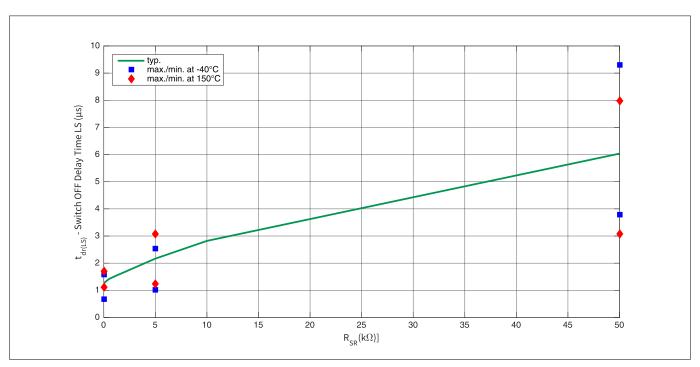

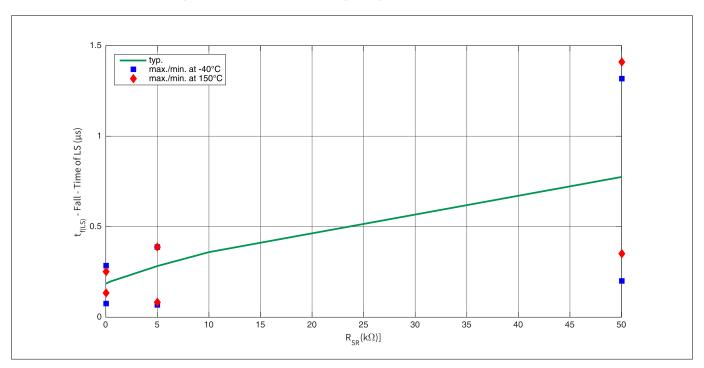

# 5.1.4 Timing behavior for falling edge on low-side switch

Figure 50  $t_{f(LS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the fall-time of the low-side switch of BTN8982TA

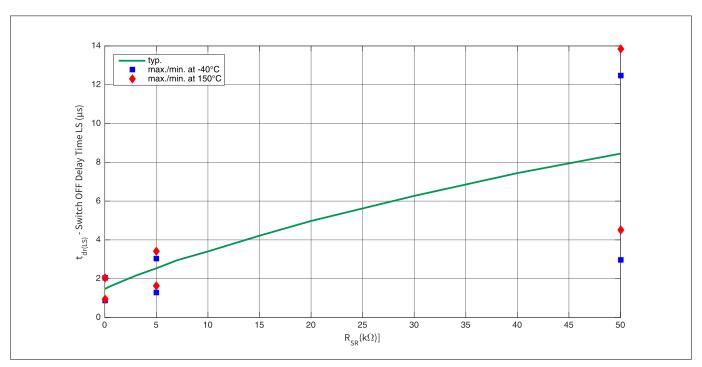

Figure 51  $t_{df(LS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the switch ON delay time of the low-side switch of BTN8982TA

Figure 52 Dependency of the slew rate resistor  $R_{SR}$  on the total falling time of the low-side switch with  $t_{f(LS),total} = t_{f(LS)} + t_{df(LS)}$ : BTN8982TA

#### **5.2** BTN8962TA Switching Time Dependency on Slew Rate Resistance

Unless otherwise specified, the times are specified for  $V_S$  = 13,5 V, -40 °C  $\leq$  T  $\leq$  150 °C,  $R_{load}$  = 2  $\Omega$ , 30  $\mu$ H <  $L_{load}$  <40  $\mu$ H (in series to  $R_{load}$ ) and single pulse. The typical values are based on the test of all product in the past years. The maximum and minimum values are based on the ±3σ and are replaced by test limits in the case of exceeding the datasheet.

#### Timing behavior for rising edge on high-side switch 5.2.1

$t_{\rm r(HS)}$ : Dependency of the slew rate resistor  $R_{\rm SR}$  on the rise-time of the high-side switch of Figure 53 **BTN8962TA**

Figure 54  $t_{

m dr(HS)}$ : Dependency of the slew rate resistor  $R_{

m SR}$  on the switch ON delay time of the high-side switch of BTN8962TA

Figure 55 Dependency of the slew rate resistor  $R_{\rm SR}$  on the total rising time of the high-side switch with  $t_{r(HS),total} = t_{r(HS)} + t_{dr(HS)}$ : BTN8962TA

# 5.2.2 Timing behavior for falling edge on high-side switch

Figure 56  $t_{f(HS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the fall-time of the high-side switch of BTN8962TA

Figure 57  $t_{df(HS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the switch OFF delay time of the high-side switch of BTN8962TA

Figure 58 Dependency of the slew rate resistor  $R_{SR}$  on the total fall-time of the high-side switch with  $t_{f(HS),total} = t_{f(HS)} + t_{df(HS)}$ : BTN8962TA

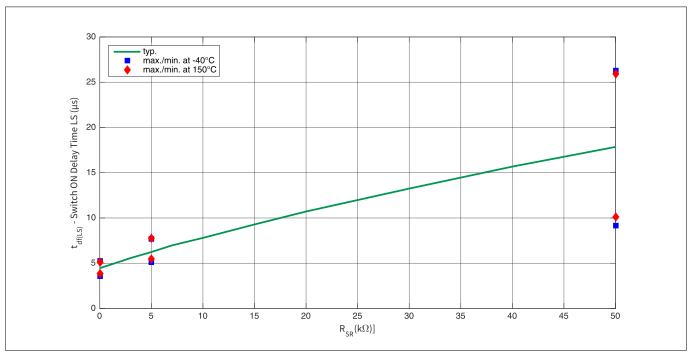

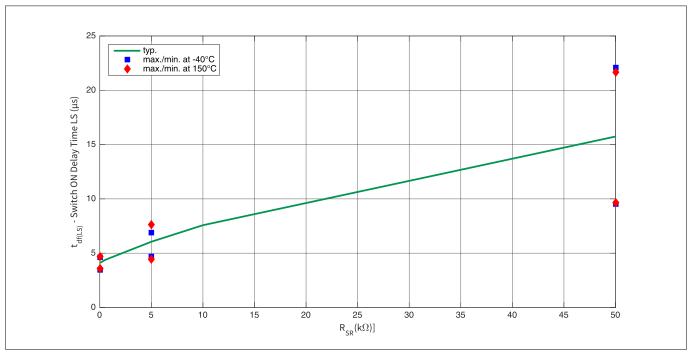

# 5.2.3 Timing behavior for rising edge on low-side switch

Figure 59  $t_{r(LS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the rise-time of the low-side switch of BTN8962TA

Figure 60  $t_{dr(LS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the switch OFF delay time of the low-side switch of BTN8962TA

Figure 61 Dependency of the slew rate resistor  $R_{SR}$  on the total rising time of the low-side switch with  $t_{r(LS),total} = t_{r(LS)} + t_{dr(LS)}$ : BTN8962TA

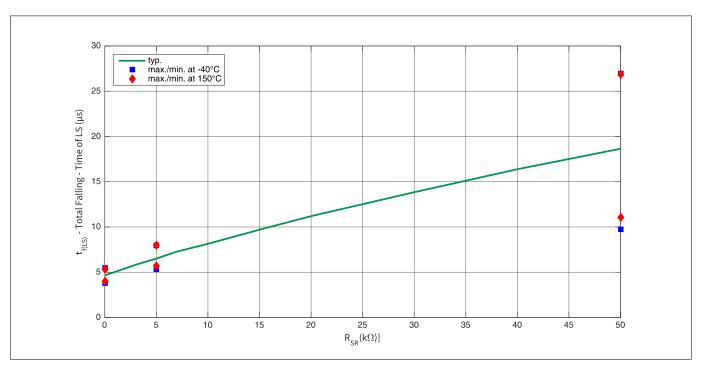

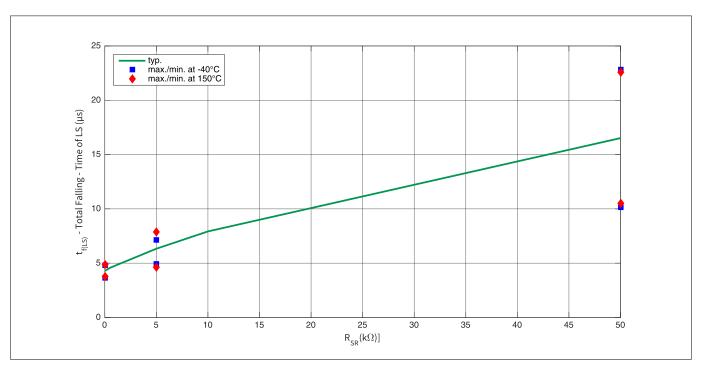

# 5.2.4 Timing behavior for falling edge on low-side switch

Figure 62  $t_{f(LS)}$ : Dependency of the slew rate resistor  $R_{SR}$  on the fall-time of the low-side switch of BTN8962TA

Figure 63  $t_{\rm df(LS)}$ : Dependency of the slew rate resistor  $R_{\rm SR}$  on the switch ON delay time of the low-side switch of BTN8962TA

Figure 64 Dependency of the slew rate resistor  $R_{SR}$  on the total falling time of the low-side switch with  $t_{f(LS),total} = t_{f(LS)} + t_{df(LS)}$ : BTN8962TA

#### 5.3 Error of total delay time

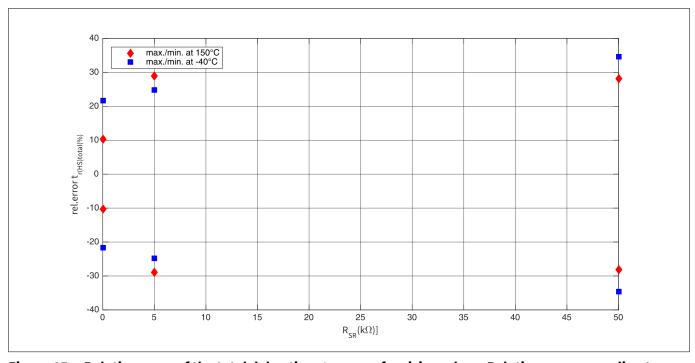

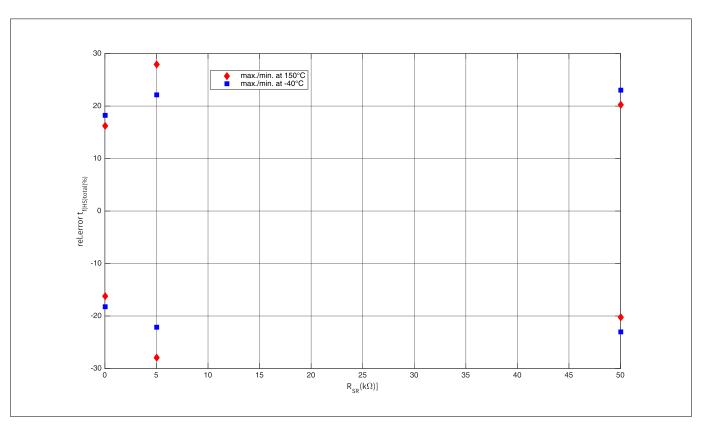

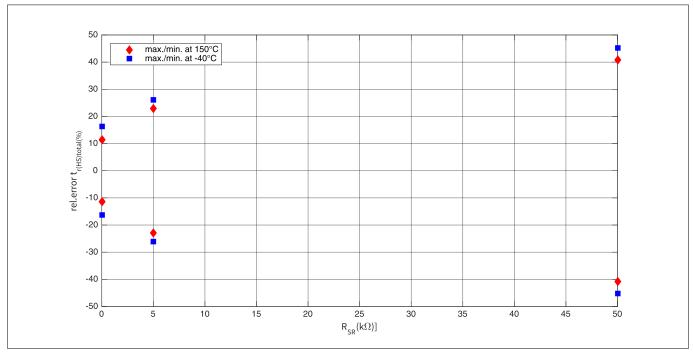

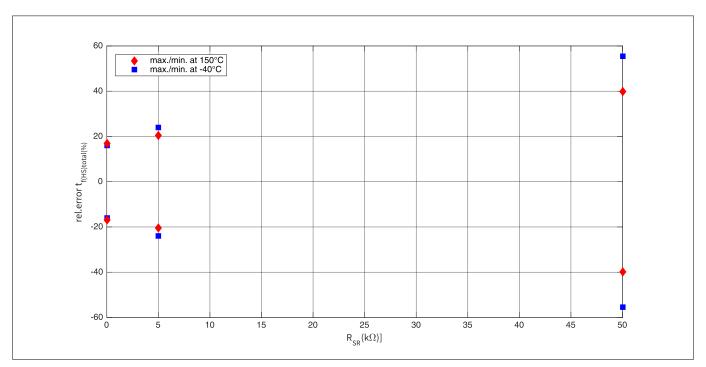

The resulting relative error for the  $\pm 3\sigma$  values, compared to the mean  $t_{x(HS),total}$  value, is summarized in *Figure* 65 / Figure 66 / Figure 67 / Figure 68. The error is calculated as follows:

$$rel, error = \frac{t_{X(HS), min/max} - t_{X(HS), mean}}{t_{X(HS), mean}}$$

#### **Equation 24**

This parameter spread needs to be taken into account especially for short PWM cycle times, respectively high PWM frequencies. If the relative  $t_{r(HS),total}$  /  $t_{f(HS),total}$  error is in the same order of magnitude as the application's PWM cycle time, a separate calibration can be considered to measure the delay times of the individual BTx9yz devices.

Figure 65 Relative error of the total delay time  $t_{r(HS),total}$  for rising edges. Relative error according to Equation 24 for BTN8962TA ( $V_S$  = 13,5 V,  $R_{load}$  = 2  $\Omega$  30  $\mu$ H <  $L_{load}$  < 40  $\mu$ H (in series to  $R_{load}$ ), single pulse)

# infineon

Figure 66 Relative error of the total delay time  $t_{\rm f(HS),total}$  for falling edges. Relative error according to Equation 24 for BTN8962TA ( $V_{\rm S}$  = 13,5 V,  $R_{\rm load}$  = 2  $\Omega$  30  $\mu$ H <  $L_{\rm load}$  < 40  $\mu$ H (in series to  $R_{\rm load}$ ), single pulse)

Figure 67 Relative error of the total delay time  $t_{r(HS),total}$  for rising edges. Relative error according to Equation 24 for BTN8982TA ( $V_S = 13,5$  V,  $R_{load} = 2 \Omega$  30  $\mu$ H <  $L_{load}$  < 40  $\mu$ H (in series to  $R_{load}$ ), single pulse).

Figure 68 Relative error of the total delay time  $t_{f(HS),total}$  for falling edges. Relative error according to Equation 24 for BTN8982TA ( $V_S = 13.5 \text{ V}$ ,  $R_{load} = 2 \Omega 30 \mu H < L_{load} < 40 \mu H$  (in series to  $R_{load}$ ), single pulse).

#### 5.4 **Delay time calibration**

One possibility to determine the total rising time  $t_{r(HS),total}$  and the falling time  $t_{f(HS),total}$  respectively, is by measuring the time once in an end of line test. For such a (single) measurement, the influence of certain parameters like the supply voltage or the load current has to be considered as well and the test setup has to be adjusted accordingly.

It is also possible to use continuous calibration during operation. With such a method, the influence of changing outside parameters is constantly taken into account. In the following two chapters, an output voltage (Chapter **5.4.1**) and current sense based calibration (*Chapter 5.4.2*) is suggested.

#### **Output voltage based calibration** 5.4.1

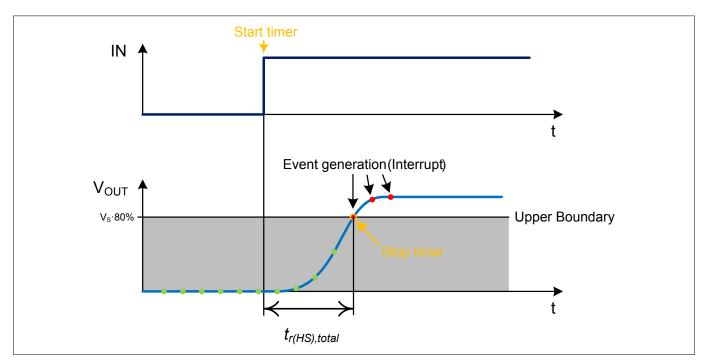

This method can be implemented if both the supply voltage  $V_S$  and the BTN89xy's output voltage  $V_{OUT}$  at the OUT-pin are measured. In that case it would be possible to measure the time between setting the IN input pin from low to high (or from high to low for  $t_{f(HS),total}$ ) and the point of time, the output voltage  $V_{OUT}$  is greater than or equal to 0.8  $V_{\rm S}$ . The measurement procedure is illustrated in *Figure 69*.

The procedure for the total falling delay time  $t_{f(HS),total}$  measurement can be performed in a similar fashion: the delay time between the falling edge of the IN-pin and the lower deviation of 20% of the  $V_{OUT} \approx V_S$  voltage level is considered.

If these two voltage levels are monitored during operation, an online calibration can be performed periodically, too.

# infineon

### **Switching Timing**

Figure 69 Measurement procedure for the total rising time  $t_{r(HS),total}$  based on two voltage measurements

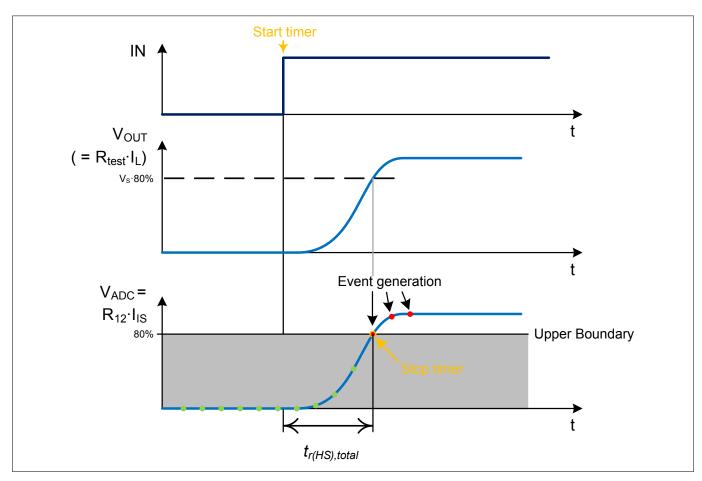

#### 5.4.2 Current sense based calibration

Two different calibration methods are available when only the current sense signal is monitored. One of these can be implemented as an end of line test, while the other is performed during live operation.

Figure 70 End of line test setup for timing calibration with ohmic load R<sub>test</sub>

# BTN8960 /62 /80 /82 **High Current PN Half Bridge**

#### **Switching Timing**

To determine the delay for a rising edge  $t_{r(HS),total}$ , the voltage limit is set to the corresponding current level, which is reached with a voltage drop of 80% of  $V_{OUT} \approx V_{S}$  over the test resistor  $R_{test}$ , as shown in the test setup in Figure 70. As this test is based on the concurrency of the output voltage and current  $I_L$ , only an ohmic load should be used. This setup results in the direct proportional context of  $I_L = V_S/R_{test}$  and with the current sense function from **Chapter 4.5**:

$$I_{IS} = \frac{I_L}{dk_{ILIS}} + I_{IS(offset)} = \frac{V_s}{dk_{ILIS} \cdot R_{test}} + I_{IS(offset)}$$

#### **Equation 25**

The resulting voltage  $V_{ADC}$  on the microcontroller's ADC input pin (according to *Figure 70*):

$$V_{\text{ADC}} = R_{12} \cdot I_{\text{IS}} = \frac{V_{\text{S}} \cdot R_{12}}{\text{d}k_{\text{ILIS}} \cdot R_{\text{test}}} + I_{\text{IS(offset)}} \cdot R_{12}$$

#### **Equation 26**

This means that the comparator threshold should be set to a corresponding voltage level of:

$$V_{\text{ADC, 80 \% }V_{\text{S}}} = 0.8 \cdot \left( \frac{V_{\text{S}} \cdot R_{12}}{\text{d}k_{\text{ILIS}} \cdot R_{\text{test}}} + I_{\text{IS(offset)}} \cdot R_{12} \right)$$

#### **Equation 27**

This procedure allows to measure the input delay  $t_{r(HS),total}$  with a microcontroller's ADC in a predefined end of line test, with a known resistor  $R_{\text{test}}$ . The test is summarized in **Figure 71**. The time measurement is started in parallel to the rising edge of the IN input pin. If the voltage level of  $V_{\rm ADC}$ , as described in **Equation 27**, is reached, the resulting delay time  $t_{r(HS),total}$  can be calculated.

# infineon

#### **Switching Timing**

Figure 71 Measurement procedure for the total rising time  $t_{r(HS),total}$  based on a current sense measurement

This procedure, which is described here for a rising edge, can be implemented in a similar manner to measure the total delay for a falling edge,  $t_{f(HS),total}$ , on the IN-pin, too.

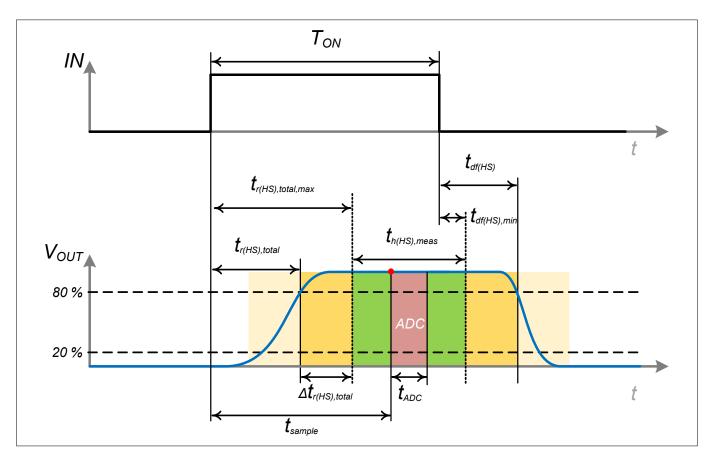

# 5.5 ADC Timing for current measurement

One way to measure the current value for motor control applications is in the center of the PWM duty cycle. The corresponding measuring time frame is summarized in *Figure 72*. Based on the value of resistor  $R_{SR}$ , the time frame is limited by the worst case (min./max.) switching times,  $t_{f(HS),total,min}$  and  $t_{r(HS),total,max}$ . Alternatively, the timing could be based on the delay time calibration/measurement described in the previous *Chapter 5.4*.

# 5.5.1 Current sense ADC timing

Based on *Figure 72*, the time window for an ADC measurement  $t_{h(HS),meas}$  for a high output signal can be calculated as follows:

$$t_{h(HS), \text{ meas}} = T_{ON} + t_{f(HS), \text{ total, min}} - t_{r(HS), \text{ total, max}}$$

#### **Equation 28**

As previously described, the on-time  $T_{ON}$  is based on the following relationship:

# BTN8960 /62 /80 /82 High Current PN Half Bridge

### **Switching Timing**

$$T_{\mathsf{ON}} = T_{\mathsf{PWM}} \cdot \mathsf{DC}$$

### **Equation 29**

$T_{\text{PWM}}$  is the PWM-period-time ( $T_{\text{PWM}} = 1 / f_{\text{PWM}}$ ) and DC corresponds to the duty cycle. This results in:

$$t_{h(HS), \text{ meas}} = T_{PWM} \cdot DC + t_{f(HS), \text{ total, min}} - t_{r(HS), \text{ total, max}}$$

### **Equation 30**

If the measurement should be started in the center of the ADC time window  $t_{h(HS),meas}$ , the sample delay  $t_{sample}$  has to be set to the following:

$$t_{\mathsf{sample}} = t_{r(\mathsf{HS}),\,\mathsf{total},\,\mathsf{max}} + \frac{t_{h(\mathsf{HS}),\,\mathsf{meas}}}{2}$$

### **Equation 31**

If the ADC measurement time window should be placed right in the center of  $t_{h(HS),meas}$  for a given ADC conversion time  $t_{ADC}$ , the sample delay time  $t_{sample}$  can be calculated as follows:

$$t_{\text{sample}} = t_{r(\text{HS}), \text{total}, \text{max}} + \frac{t_{h(\text{HS}), \text{meas}}^{-t_{\text{ADC}}}}{2}$$

### **Equation 32**

This measurement scenario is illustrated in Figure 72.

# infineon

#### **Switching Timing**

Figure 72 Timing for current measurement for high input on IN-pin, with ideal ADC sampling time window

# 5.5.2 Offset current calibration ADC timing

With an additional ADC measurement at low input signals, an online compensation of the IS-pin's offset current  $I_{\text{IS}(\text{offset})}$  can be executed. Based on **Figure 73** and comparable to the current measurement in the previous **Chapter 5.5.1**, the different sampling timings for a low input level can be calculated in a similar fashion. The time window of the ADC measurement  $t_{\text{f(HS)},\text{meas}}$  for a low output signal can be calculated as follows:

$$t_{f(HS), \text{meas}} = T_{PWM} \cdot (1 - DC) + t_{dr(HS), \text{min}} - t_{f(HS), \text{total, max}}$$

#### **Equation 33**

If the ADC measurement should be triggered right in the center of the time window  $t_{h(HS),meas}$ , the required sample delay t 'sample can be calculated according to **Figure 73**:

$$t'_{\text{sample}} = t_{f(\text{HS}), \text{total}, \text{max}} + \frac{t_{f(\text{HS}), \text{meas}}}{2}$$

#### **Equation 34**

The resulting trigger point with the sample delay time t'sample is marked in *Figure 73* (red).

If the ADC sampling window should be placed in the center of  $t_{h(HS),meas}$ , the sample delay time t' sample should be set to:

# BTN8960 /62 /80 /82 High Current PN Half Bridge

#### **Switching Timing**

$$t'_{\text{sample}} = t_{f(\text{HS}), \text{total}, \text{max}} + \frac{t_{f(\text{HS}), \text{meas}} - t_{\text{ADC}}}{2}$$

#### **Equation 35**

In the case of a fault condition, the IS-pin will provide a constant current of  $I_{\rm IS(lim)}$ , instead of the current sense functionality. This current  $I_{\rm IS(lim)}$  can be clearly distinguished from the lower offset current  $I_{\rm IS(offset)}$ . Further details are described in *Chapter 4.5.1.1*.

Figure 73 Timing for current measurement for low input on IN-pin

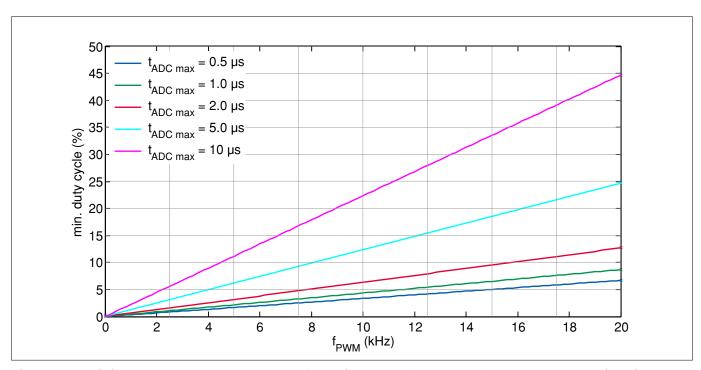

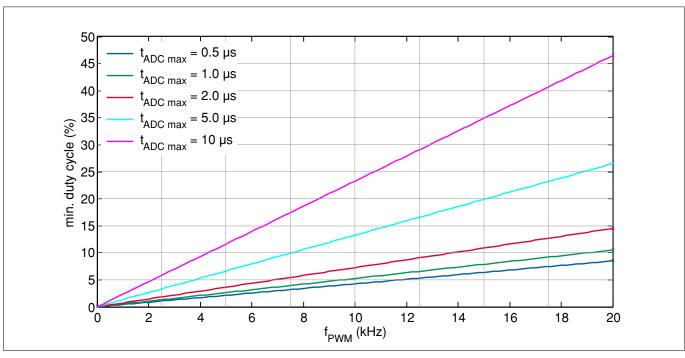

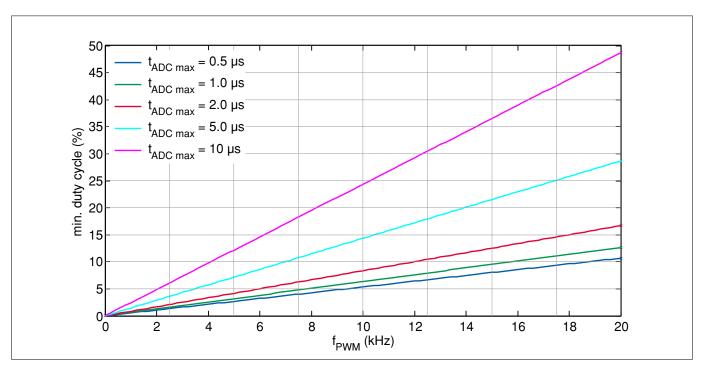

## 5.6 Allowed PWM setup for current sense ADC measurements

Based on the previous *Chapter 5.5*, a relationship between the lowest possible duty cycle  $DC_{\min}$ , corresponding to the minimal time  $T_{\text{ON,min}}$ , and the PWM frequency can be set up. The worst case (max.) ADC conversion time window is  $t_{\text{ADC,max}}$ . For a worst case analysis, the following assumption must be respected in any case, as the time window for the ADC measurement  $t_{\text{h(HS),meas}}$ , according to *Equation 30*, has to be greater than  $t_{\text{ADC,max}}$ :

$$t_{\text{ADC, max}} \leq T_{\text{PWM}} \cdot \text{DC} + t_{\text{d}f(\text{HS}), \, \text{min}} - t_{r(\text{HS}), \, \text{total, max}}$$

#### **Equation 36**

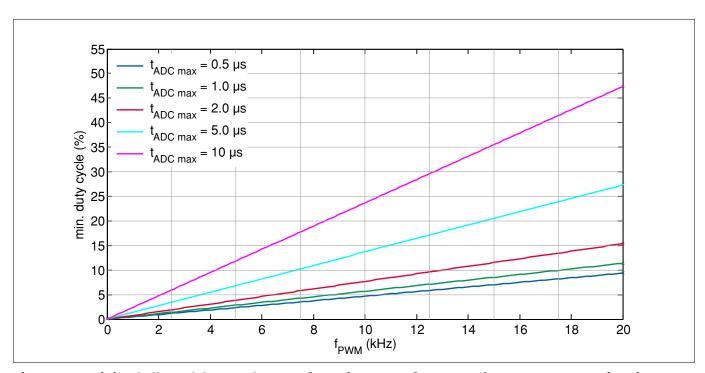

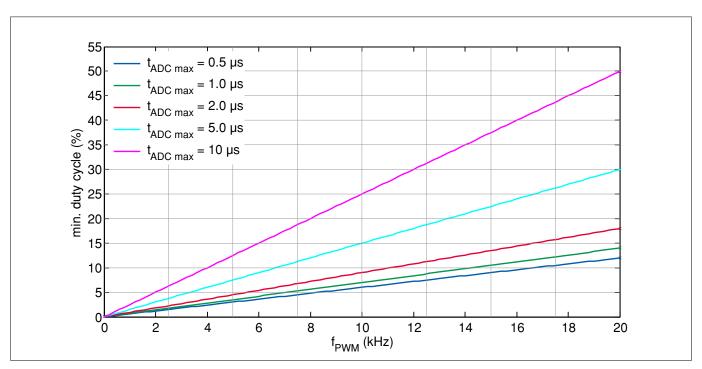

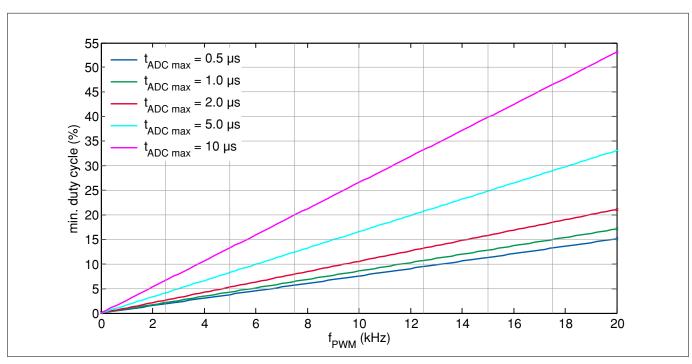

For certain typical values for resistor  $R_{SR}$  (1 k $\Omega$ , 5 k $\Omega$  and 10 k $\Omega$ ) and certain maximal ADC conversion times  $t_{ADC,max}$ , the minimal duty cycles should be respected, as shown in *Figure 74* (BTN8962TA) / *Figure 77* (BTN8982TA) for  $R_{SR}$  = 1 k $\Omega$ , *Figure 75* (BTN8962TA) / *Figure 78* (BTN8982TA) for  $R_{SR}$  = 5 k $\Omega$  and *Figure 76* (BTN8962TA) / *Figure 79* (BTN8982TA) for  $R_{SR}$  = 10 k $\Omega$ .

### 5.6.1 BTN8962TA

Figure 74 Minimal allowed duty cycle  $DC_{min}$  for a given PWM frequency  $f_{PWM}$ , a ADC conversion time  $t_{ADC}$  and  $R_{SR} = 1 \text{ k}\Omega$ , for BTN8962TA

Figure 75 Minimal allowed duty cycle  $DC_{min}$  for a given PWM frequency  $f_{PWM}$ , a ADC conversion time  $t_{ADC}$  and  $R_{SR} = 5 \text{ k}\Omega$ , for BTN8962TA

# infineon

### **Switching Timing**

Figure 76 Minimal allowed duty cycle  $DC_{min}$  for a given PWM frequency  $f_{PWM}$ , a ADC conversion time  $t_{ADC}$  and  $R_{SR} = 10 \text{ k}\Omega$ , for BTN8962TA

### 5.6.2 BTN8982TA

Figure 77 Minimal allowed duty cycle  $DC_{\min}$  for a given PWM frequency  $f_{\text{PWM}}$ , a ADC conversion time  $t_{\text{ADC}}$  and  $R_{\text{SR}} = 1 \text{ k}\Omega$ , for BTN8982TA

#### **Switching Timing**