# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## Continuity of document content

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# Continuity of ordering part numbers

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

# CY7C65216D

# USB-Dual I<sup>2</sup>C Bridge Controller

## Features

- USB 2.0 compliant, Full-Speed (12 Mbps)

- Support for communication driver class (CDC), personal health care device class (PHDC), and vendor device class

- Battery charger detection (BCD) compliant with USB Battery Charging Specification Rev 1.2 (Peripheral Detect only)

Integrated USB termination resistors

- Two-channel configurable I<sup>2</sup>C interfaces

- □ Master/slave up to 400 kHz

- □ Supports multi-master I<sup>2</sup>C

- □ 256 bytes for each transmit and receive buffer per channel

- General-purpose input/output (GPIO) pins: 12

- Configuration utility (Windows) to configure the following: □ Vendor ID (VID), Product ID (PID), and Product and

- Manufacturer descriptors

- □ I<sup>2</sup>C

- Battery Charger Detection compliant to BC-1.2 specification

GPIO

- Driver support for VCOM and DLL

- □ Windows 10: 32- and 64-bit versions

- □ Windows 8.1: 32- and 64-bit versions

- □ Windows 8: 32- and 64-bit versions

- □ Windows 7: 32- and 64-bit versions

- □ Windows Vista: 32- and 64-bit versions

- □ Windows XP: 32- and 64-bit versions

- □ Mac OS-X: 10.6, and later versions

- Linux: Kernel version 2.6.35 onwards

- Clocking: Integrated 48-MHz clock oscillator

- Supports bus-/self-powered configurations

- USB suspend mode for low power

- Operating voltage: 1.71 to 5.5 V

- Operating temperature

Commercial: 0 °C to 70 °C

Industrial: -40 °C to 85 °C

- ESD protection: 2.2 kV HBM

- RoHS compliant package □ 32-pin QFN (5 × 5 × 1 mm. 0.5 mm pitch)

- Ordering part number

CY7C65216D-32LTXI

CY7C65216D-32LTXIT

## Applications

- Medical/healthcare devices

- Point-of-Sale (POS) terminals

- Test and measurement system

- Gaming systems

- Set-top box PC-USB interface

- Industrial

- Networking

- Enabling USB connectivity in legacy peripherals

#### **USB** Compliant

The USB Dual  $l^2$ C Bridge Controller with BCD is fully compliant with USB2.0 Specification and Battery Charging Specification v1.2.

Errata: For information on silicon errata, see "Errata" on page 27. Details include trigger conditions, devices affected, and proposed workaround.

198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised November 25, 2020

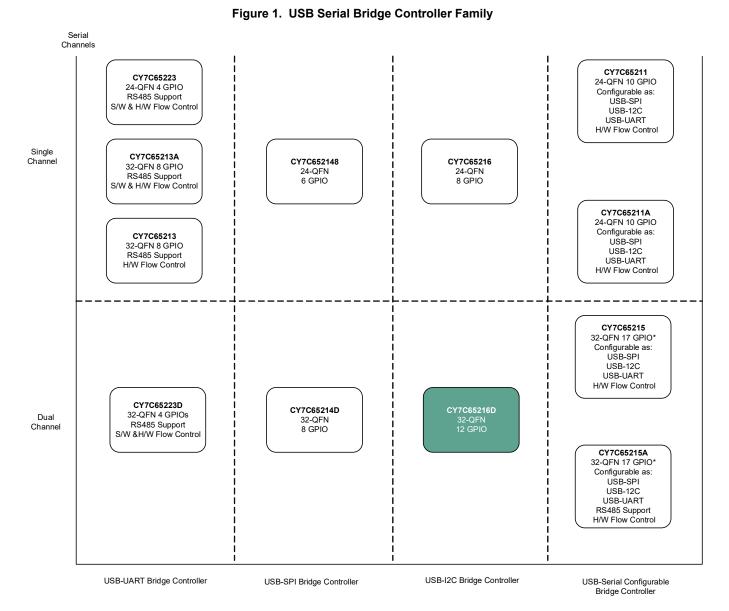

## **USB Serial Bridge Controller Family**

USB Serial bridge Controllers are a family of configurable products for most common applications requiring no firmware changes.

Configuration utility is provided to Configure USB-VID, USB-PID, USB Product and Manufacturer Descriptors. The same configuration utility can be used to configure UART, I<sup>2</sup>C, SPI, Battery Charger Detection, GPIOs, Power mode, and so on.

## Table 1. USB Serial Family Feature Comparison

|            |                  |      |                  | USB-UART                    |                             |                | US                                | B-SPI                | USB-I <sup>2</sup> C              |

|------------|------------------|------|------------------|-----------------------------|-----------------------------|----------------|-----------------------------------|----------------------|-----------------------------------|

| MPN        | # of<br>Channels | GPIO | RS485<br>Support | Software<br>Flow<br>Control | Hardware<br>Flow<br>Control | UART<br>Pins** | SPI Serial<br>Data<br>Width (bit) | SPI Master/<br>Slave | I <sup>2</sup> C Master/<br>Slave |

| CY7C65213  | 1                | 8    | Ν                | Ν                           | Y                           | 8              | -                                 | -                    | _                                 |

| CY7C65213A | 1                | 8    | Y                | N                           | Y                           | 8              | -                                 | -                    | -                                 |

| CY7C65223  | 1                | 4    | Y                | Y                           | Y                           | 2/4/6          | -                                 | -                    | -                                 |

| CY7C65223D | 2                | 4    | Y                | Y                           | Y                           | 2/4/6/8        | -                                 | -                    | -                                 |

| CY7C652148 | 1                | 6    | -                | -                           | -                           | -              | 4-16 bit                          | Master/Slave         | -                                 |

| CY7C65214D | 2                | 8    | -                | -                           | -                           | -              | 4-16 bit                          | Master/Slave         | -                                 |

| CY7C65216  | 1                | 8    | -                | -                           | -                           | -              | -                                 | -                    | Master/Slave                      |

| CY7C65216D | 2                | 12   | -                | -                           | -                           | -              | -                                 | -                    | Master/Slave                      |

| CY7C65211  | 1                | 10*  | Ν                | Ν                           | Y                           | 2/4/6          | 4-16 bit                          | Master/Slave         | Master/Slave                      |

| CY7C65211A | 1                | 10*  | Y                | N                           | Y                           | 2/4/6          | 4-16 bit                          | Master/Slave         | Master/Slave                      |

| CY7C65215  | 2                | 17*  | N                | N                           | Y                           | 2/4/6          | 4-16 bit                          | Master/Slave         | Master/Slave                      |

| CY7C65215A | 2                | 17*  | Y                | Ν                           | Y                           | 2/4/6/8        | 4-16 bit                          | Master/Slave         | Master/Slave                      |

## Legend

\* Represents the total GPIO count offered by the part. This count can dynamically change based on UART / SPI / I<sup>2</sup>C pin configuration. \*\* UART Pins

| **UART Pins | UART Signal                                 |  |  |  |  |

|-------------|---------------------------------------------|--|--|--|--|

| 2           | RxD and TxD                                 |  |  |  |  |

| 4           | RxD, TxD, RTS#, CTS#                        |  |  |  |  |

| 6           | RxD, TxD, RTS#, CTS#, DTR#, DSR#            |  |  |  |  |

| 8           | RxD, TxD, RTS#, CTS#, DTR#, DSR#, DCD#, RI# |  |  |  |  |

## Table 2. Default Serial Channel Configuration

|            | # of     |      | USB       | USB-                | UART      | USB-SPI              | USB-I <sup>2</sup> C              |

|------------|----------|------|-----------|---------------------|-----------|----------------------|-----------------------------------|

| MPN        | Channels | GPIO | Protocol  | ls RS485<br>Enabled | UART Pins | SPI Master/<br>Slave | I <sup>2</sup> C Master/<br>Slave |

| CY7C65213  | 1        | 4    | CDC**     | N                   | 8         | -                    | -                                 |

| CY7C65213A | 1        | 4    | CDC**     | N                   | 8         | -                    | -                                 |

| CY7C65223  | 1        | 4    | CDC**     | Y                   | 4         | -                    | -                                 |

| CY7C65223D | 2        | 4    | CDC**     | Y                   | 4         | -                    | -                                 |

| CY7C652148 | 1        | 6    | Vendor*** | _                   | -         | Master               | -                                 |

| CY7C65214D | 2        | 8    | Vendor*** | -                   | -         | Master               | -                                 |

| CY7C65216  | 1        | 8    | Vendor*** | -                   | -         | -                    | Slave                             |

| CY7C65216D | 2        | 12   | Vendor*** | -                   | -         | -                    | Master                            |

| CY7C65211  | 1        | 3    | CDC**     | N                   | 6         | -                    | -                                 |

| CY7C65211A | 1        | 3    | CDC**     | N                   | 6         | -                    | -                                 |

| CY7C65215  | 2        | 4    | CDC**     | N                   | 6         | -                    | -                                 |

| CY7C65215A | 2        | 4    | CDC**     | N                   | 6         | _                    | _                                 |

\*\* USB CDC Protocol allows the USB host Operating System to detect the device as Virtual COM Port Device. \*\*\* USB Vendor Protocol allows the USB host operating system to detect the device as general USB device. This device is accessible using Cypress Application Library.

## **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the document USB-Serial Bridge Controller Product Overview.

- Overview: USB Portfolio, USB Roadmap

- USB 2.0 Product Selectors: USB-Serial Bridge Controller, USB to UART Controller (Gen I)

- Knowledge Base Articles: Cypress offers a large number of USB knowledge base articles covering a broad range of topics, from basic to advanced level. Recommended knowledge base articles for getting started with USB-Serial Bridge Controller are:

- □ KBA85909 Key Features of the Cypress<sup>®</sup> USB-Serial Bridge Controller

- □ KBA85920 USB-UART and USB-Serial

- □ KBA85921 Replacing FT232R with CY7C65213 USB-UART LP Bridge Controller

- KBA85913 Voltage supply range for USB-Serial

- □ KBA89355 USB-Serial: Cypress Default VID and PID

- □ KBA92641 USB-Serial Bridge Controller Managing I/Os using API

- KBA92442 Non-Standard Baud Rates in USB-Serial Bridge Controllers

- □ KBA91366 Binding a USB-Serial Device to a Microsoft<sup>®</sup> CDC Driver

- □ KBA92551 Testing a USB-Serial Bridge Controller Configured as USB-UART with Linux<sup>®</sup>

- □ KBA91299 Interfacing an External I<sup>2</sup>C Device with the CYUSBS234/236 DVK

- For a complete list of knowledge base articles, click here.

- Code Examples: USB Full-Speed

- Development Kits:

- □ CYUSBS232, Cypress USB-UART LP Reference Design Kit □ CYUSBS234, Cypress USB-Serial (Single Channel)

- Development Kit □ CYUSBS236, Cypress USB-Serial (Dual Channel) Development Kit

- Models: IBIS

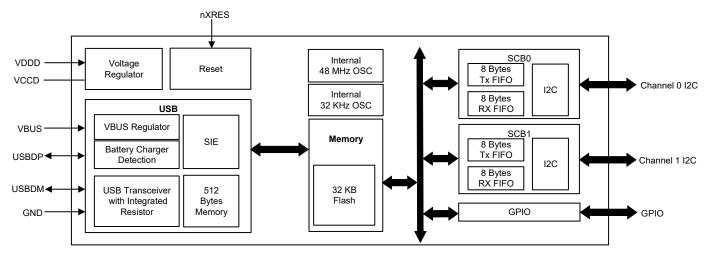

## **Block Diagram**

# CY7C65216D

## Contents

| Functional Overview          | 8 |

|------------------------------|---|

| USB and Charger Detect       | 8 |

| Serial Communication         |   |

| GPIO Interface               | 8 |

| Default Configuration        | 8 |

| Memory                       |   |

| System Resources             |   |

| Suspend and Resume           |   |

| WAKEUP                       |   |

| Software                     |   |

| Internal Flash Configuration |   |

| Electrical Specifications    |   |

| Absolute Maximum Ratings     |   |

| Operating Conditions         |   |

| Device Level Specifications  |   |

| GPIO                         |   |

| nXRES                        |   |

| I2C Specifications           |   |

| Flash Memory Specifications  |   |

| Pin Description              |   |

| =                            |   |

| USB Power Configurations                  | 18 |

|-------------------------------------------|----|

| USB Bus-Powered Configuration             | 18 |

| Self-Powered Configuration                | 19 |

| USB Bus Powered with Variable I/O Voltage | 20 |

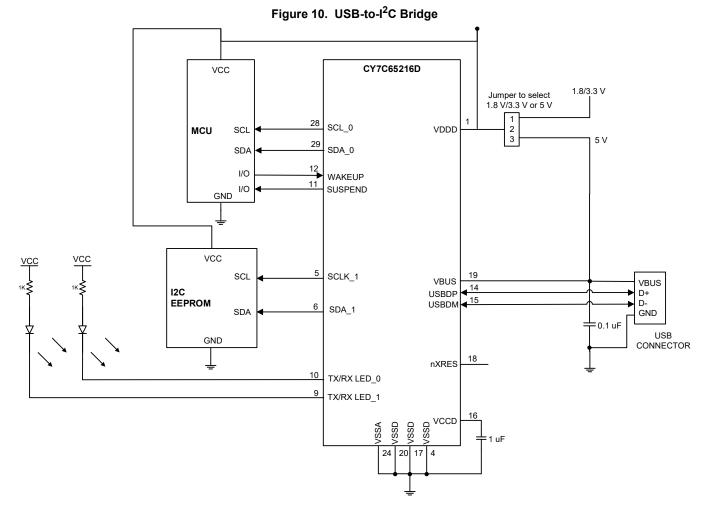

| Application Examples                      | 21 |

| USB to Dual Channel (I2C) Bridge          |    |

| Ordering Information                      |    |

| Ordering Code Definitions                 |    |

| Package Information                       |    |

| Acronyms                                  |    |

| Document Conventions                      |    |

| Units of Measure                          |    |

| Errata                                    | 27 |

| Document History Page                     | 28 |

| Sales, Solutions, and Legal Information   |    |

| Worldwide Sales and Design Support        |    |

| Products                                  |    |

| PSoC® Solutions                           | 29 |

| Cypress Developer Community               |    |

| Technical Support                         |    |

## **Functional Overview**

The CY7C65216D is a Full-Speed USB controller that enables seamless PC connectivity for peripherals with dual-channel  $I^2C$  interfaces. CY7C65216D also integrates BCD, which is compliant with the USB Battery Charging Specification Rev. 1.2. It integrates a voltage regulator, oscillator, and flash memory for storing configuration parameters, offering a cost-effective solution. CY7C65216D supports bus-powered and self-powered modes, and enables efficient system power management with suspend and remote wake-up signals. It is available in a 32-pin QFN package.

## **USB and Charger Detect**

#### USB

CY7C65216D has a built-in USB 2.0 Full-Speed transceiver. The transceiver incorporates the internal USB series termination resistors on the USB data lines and a 1.5-k $\Omega$  pull-up resistor on USBDP.

Table 3. Maximum Speed supported on both SCBs

#### Charger Detection

CY7C65216D supports BCD for Peripheral Detect only and complies with the USB Battery Charging Specification Rev. 1.2. It supports the following charging ports:

- Standard Downstream Port (SDP): allows the system to draw up to 500 mA current from the host

- Charging Downstream Port (CDP): allows the system to draw up to 1.5 A current from the host

- Dedicated Charging Port (DCP): allows the system to draw up to 1.5 A of current from the wall charger

## **Serial Communication**

CY7C65216D has two serial communication blocks (SCBs). Each SCB can implement  $I^2$ C interface. A 256-byte buffer is available in both the TX and RX lines.

Table 3 shows maximum speed supported on both SCBs when they are configured as  $I^2C$ .

| No. | Configuration                                   | SCB0 Maximum Speed       | SCB1 Maximum Speed       |  |  |

|-----|-------------------------------------------------|--------------------------|--------------------------|--|--|

| 1   | SCB0 = I <sup>2</sup> C Master, SCB1 = Disabled | 400 kHz (Both TX and RX) | NA                       |  |  |

| 2   | SCB0 = I <sup>2</sup> C Slave, SCB1 = Disabled  | 400 kHz (Both TX and RX) | NA                       |  |  |

| 3   | SCB0 = $I^2C$ , SCB1 = $I^2C$                   | 400 kHz (Both TX and RX) | 400 kHz (Both TX and RX) |  |  |

## I<sup>2</sup>C Interface

The I<sup>2</sup>C interface implements full multi-master/slave modes and supports up to 400 kHz. The configuration utility tool is used to set the I<sup>2</sup>C address in slave mode. This tool enables only even slave addresses. For further details on protocol, refer to the NXP I<sup>2</sup>C specification rev5.

## Notes

- I<sup>2</sup>C ports are not tolerant of higher voltages and cannot be hot-swapped or powered up independently from the rest of the I<sup>2</sup>C system.

- The minimum fall time of the SCL is met (as per NXP I<sup>2</sup>C specification Rev. 5) when V<sub>DDD</sub> is between 1.71 V and 3.0 V. When V<sub>DDD</sub> is within the range of 3.0 V to 3.6 V, it is recommended to add a 50 pF capacitor on the SCL signal.

#### **GPIO** Interface

CY7C65216D has 12 GPIOs. The configuration utility allows configuration of the GPIO pins. The configurable options are as follows:

- TRISTATE: GPIO can be tristated through Config Utility

- DRIVE 1: Output static 1

- DRIVE 0: Output static 0

- POWER#: Power control for bus power designs

- TXLED#: Drives LED during USB transmit

- RXLED#: Drives LED during USB receive

- TX or RX LED#: Drives LED during USB transmit or receive

GPIO can be configured to drive LED at 8-mA drive strength.

BCD0/BCD1: Two-pin output to indicate the type of USB charger

■ BUSDETECT: Connects VBUS pin for USB host detection

## **Default Configuration**

CY7C65216D is configured as Dual I<sup>2</sup>C Master device.

#### Memory

CY7C65216D has a 512-byte flash. The flash is used to store the USB parameters such as VID/PID, serial number, Product, and Manufacturer Descriptors, which can be programmed by the configuration utility.

#### System Resources

#### Power System

CY7C65216D supports the USB Suspend mode to control power usage. CY7C65216D operates in bus-powered or self-powered modes over a range of 3.15 to 5.5 V.

#### Clock System

CY7C65216D has a fully integrated clock and does not require any external components. The clock system is responsible for providing clocks to all subsystems.

#### Internal 48-MHz Oscillator

The internal 48-MHz oscillator is the primary source of internal clocking in CY7C65216D.

#### Internal 32-kHz Oscillator

The internal 32-kHz oscillator is primarily used to generate clocks for peripheral operation in the USB Suspend mode.

#### Reset

The reset block ensures reliable power-on reset and brings the device back to the default known state. The nXRES (active low) pin can be used by external devices to reset the CY7C65216D.

## Suspend and Resume

The CY7C65216D device asserts the SUSPEND pin when the USB bus enters the suspend state. This helps in meeting the stringent suspend current requirement of the USB 2.0 specification, while using the device in bus-powered mode. The device will resume from the suspend state under any of the following conditions:

- 1. Any activity is detected on the USB bus

- 2. The WAKEUP pin is asserted to generate remote wakeup to the host

## WAKEUP

The WAKEUP pin is used to generate a remote wakeup signal on the USB bus. The remote wakeup signal is sent only if the host enables this feature through the SET\_FEATURE request. The device communicates support for the remote wakeup to the host through the configuration descriptor during the USB enumeration process. The CY7C65216D device allows enabling/disabling and polarity of the remote wakeup feature through the configuration utility.

#### Software

Cypress delivers a complete set of software drivers and the configuration utility to enable product configuration during system development.

#### Drivers for Linux Operating Systems

Cypress provides a User Mode USB driver library (*libcyusbserial.so*) that abstracts vendor commands for the I<sup>2</sup>C interface and provides a simplified API interface to the user applications. This library makes use of the standard open source libUSB library to enable the USB communication. The Cypress serial library supports the USB plug-and-play feature using the Linux 'udev' mechanism.

#### Drivers for Mac OSx

Cypress delivers a dynamically linked shared library (CyUSBSerial.dylib) based on libUSB, which enables communication to the CY7C65216D device.

In addition, CY7C65216D binds to native MAC OSx driver. No special driver is required.

#### Drivers for Windows Operating Systems

For Windows operating systems (XP, Vista, Win7, Win8, Win8.1, and Win10), Cypress delivers a User Mode dynamically linked library–CyUSBSerial DLL–that abstracts vendor-specific interface of CY7C65216D devices and provides convenient APIs to the user. It provides interface APIs for vendor-specific I<sup>2</sup>C and class-specific APIs for PHDC.

USB-I<sup>2</sup>C Bridge Controller works with Cypress provided USB vendor class driver. The Cypress Windows drivers are MS logo certified drivers.

These drivers are bound to device through WU (Windows Update) services.

Cypress drivers also support Windows plug-and-play and power management and USB Remote Wake-up.

## **Device Configuration Utility (Windows Only)**

A Windows-based configuration utility is available to configure various device initialization parameters. This graphical user application provides an interactive interface to define the various boot parameters stored in the device flash.

This utility allows the user to save a user-selected configuration to text or xml formats. It also allows users to load a selected configuration from text or xml formats. The configuration utility allows the following operations:

- View current device configuration

- Select and configure I<sup>2</sup>C, CapSense, battery charging, and GPIOs

- Configure USB VID, PID, and string descriptors

- Save or Load configuration

You can download the free configuration utility and drivers from www.cypress.com.

## **Internal Flash Configuration**

The internal flash memory can be used to store the configuration parameters shown in the following table. A free configuration utility is provided to configure the parameters listed in the table to meet application specific requirements over USB interface. The configuration utility ration utility can be downloaded from www.cypress.com/usbserial.

| Table 4. | Internal Flash | Configuration | for CY7C65216D |

|----------|----------------|---------------|----------------|

|----------|----------------|---------------|----------------|

| Parameter              | Default Value             | Description                                                                                                   |

|------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------|

| USB Configuration      |                           |                                                                                                               |

| USB Vendor ID (VID)    | 0x04B4                    | Default Cypress VID. Can be configured to customer VID.                                                       |

| USB Product ID (PID)   | 0x0005                    | Default Cypress PID. Can be configured to customer PID.                                                       |

| Manufacturer string    | Cypress                   | Can be configured with any string up to 64 characters                                                         |

| Product string         | USB-Serial (Dual Channel) | Can be configured with any string up to 64 characters                                                         |

| Serial string          |                           | Can be configured with any string up to 64 characters                                                         |

| Power mode             | Bus powered               | Can be configured to bus-powered or self-powered mode                                                         |

| Max current draw       | 100 mA                    | Can be configured to any value from 0 to 500 mA. Based on this, the configuration descriptor will be updated. |

| Remote wakeup          | Enabled                   | Can be disabled. Remote wakeup is initiated by asserting WAKEUP pin.                                          |

| USB interface protocol | Vendor                    | Can be configured to function in CDC, PHDC, or Cypress vendor class.                                          |

| BCD                    | Disabled                  | Charger detect is disabled by default. When BCD is enabled, three of the GPIOs must be configured for BCD.    |

## **Electrical Specifications**

## Absolute Maximum Ratings

| Exceeding maximum ratings <sup>[1]</sup> may shorten the useful life of the device. | ■ 2.2-kV HBM per JESD22-A114<br>Latch-up current                               |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Storage temperature                                                                 | Current per GPIO                                                               |

| Ambient temperature with power supplied (Industrial)                                | Operating Conditions                                                           |

| Supply voltage to ground potential<br>V <sub>DDD</sub> 6.0 V                        | T <sub>A</sub> (ambient temperature under bias)<br>Industrial −40 °C to +85 °C |

| V <sub>BUS</sub> 6.0 V                                                              | $V_{BUS} supply  voltage $                                                     |

| V <sub>CCD</sub> 1.95 V                                                             | $V_{\mbox{\scriptsize DDD}}$ supply voltage 1.71 V to 5.50 V                   |

| V <sub>GPIO</sub> V <sub>DDD</sub> + 0.5 V                                          | $V_{CCD}$ supply voltage 1.71 V to 1.89 V                                      |

Static discharge voltage ESD protection levels:

## **Device Level Specifications**

All specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, T<sub>J</sub>  $\leq$  100 °C, and 1.71 V to 5.50 V, except where noted.

## Table 5. DC Specifications

| Parameter        | Description                       | Min  | Тур  | Max  | Units | Details/Conditions                                                                                                                                                                                                                       |

|------------------|-----------------------------------|------|------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                   | 3.15 | 3.30 | 3.45 | V     | Set and configure correct voltage                                                                                                                                                                                                        |

| V <sub>BUS</sub> | V <sub>BUS</sub> supply voltage   | 4.35 | 5.00 | 5.25 | V     | range using the configuration utility for V <sub>BUS</sub> .                                                                                                                                                                             |

|                  |                                   | 1.71 | 1.80 | 1.89 | V     | Used to set I/O and core voltage.                                                                                                                                                                                                        |

| V <sub>DDD</sub> | V <sub>DDD</sub> supply voltage   | 2.0  | 3.3  | 5.5  | V     | Set and configure correct voltage range using the configuration utility for V <sub>DDD</sub> .                                                                                                                                           |

|                  | Output voltage (for core logic)   | _    | 1.80 |      |       | Do not use this supply to drive external device.                                                                                                                                                                                         |

| V <sub>CCD</sub> |                                   |      |      | _    | V     | <ul> <li>1.71 V≤V<sub>DDD</sub>≤1.89 V: Short<br/>the V<sub>CCD</sub> pin with the V<sub>DDD</sub> pin</li> <li>V<sub>DDD</sub> &gt; 2 V – connect a 1-µF<br/>capacitor (Cefc) between the<br/>V<sub>CCD</sub> pin and ground</li> </ul> |

| Cefc             | External regulator voltage bypass | 1.00 | 1.30 | 1.60 | μF    | X5R ceramic or better                                                                                                                                                                                                                    |

| I <sub>DD1</sub> | Operating supply current          | -    | 13   | 18   | mA    | USB 2.0 FS,<br>no GPIO switching at<br>V <sub>BUS</sub> = 5 V, V <sub>DDD</sub> = 5 V                                                                                                                                                    |

| I <sub>DD2</sub> | USB Suspend supply current        | _    | 5    | _    | μA    | Does not include current through<br>a pull-up resistor on USBDP.<br>In USB suspend mode, the D+<br>voltage can go up to a maximum<br>of 3.8 V.                                                                                           |

## Table 6. AC Specifications

| Parameter | Description                  | Min | Тур | Max | Units | Details/Conditions |

|-----------|------------------------------|-----|-----|-----|-------|--------------------|

| Zout      | USB driver output impedance  | 28  | -   | 44  | Ω     | -                  |

| Twakeup   | Wakeup from USB Suspend mode | -   | 25  | -   | μs    | -                  |

Note

<sup>1.</sup> Usage above the absolute maximum conditions may cause permanent damage to the device. Exposure to Absolute Maximum conditions for extended periods of time may affect device reliability. When used below Absolute Maximum conditions but above normal operating conditions the device may not operate to specification.

## GPIO

## Table 7. GPIO DC Specifications

| Parameter           | Description                                      | Min                    | Тур | Max                  | Units | Details/Conditions                                        |

|---------------------|--------------------------------------------------|------------------------|-----|----------------------|-------|-----------------------------------------------------------|

| V <sub>IH</sub> [2] | Input voltage high threshold                     | $0.7 \times V_{DDD}$   | -   | -                    | V     | CMOS Input                                                |

| V <sub>IL</sub>     | Input voltage low threshold                      | _                      | -   | $0.3 \times V_{DDD}$ | V     | CMOS Input                                                |

| V <sub>IH</sub> [2] | LVTTL input, V <sub>DDD</sub> < 2.7 V            | $0.7 \times V_{DDD}$   | -   | -                    | V     | -                                                         |

| V <sub>IL</sub>     | LVTTL input, V <sub>DDD</sub> < 2.7 V            | _                      | -   | $0.3 \times V_{DDD}$ | V     | -                                                         |

| V <sub>IH</sub> [2] | LVTTL input, $V_{DDD} \ge 2.7 V$                 | 2                      | -   | -                    | V     | -                                                         |

| V <sub>IL</sub>     | LVTTL input, $V_{DDD} \ge 2.7 V$                 | -                      | -   | 0.8                  | V     | -                                                         |

| V <sub>OH</sub>     | CMOS output voltage high level                   | V <sub>DDD</sub> - 0.4 | -   | -                    | V     | I <sub>OH</sub> = 4 mA,<br>V <sub>DDD</sub> = 5 V ± 10%   |

| V <sub>OH</sub>     | CMOS output voltage high level                   | V <sub>DDD</sub> – 0.6 | -   | -                    | V     | I <sub>OH</sub> = 4 mA,<br>V <sub>DDD</sub> = 3.3 V ± 10% |

| V <sub>OH</sub>     | CMOS output voltage high level                   | V <sub>DDD</sub> – 0.5 | _   | _                    | V     | I <sub>OH</sub> = 1 mA,<br>V <sub>DDD</sub> = 1.8 V ± 5%  |

| V <sub>OL</sub>     | CMOS output voltage low level                    | -                      | -   | 0.4                  | V     | I <sub>OL</sub> = 8 mA,<br>V <sub>DDD</sub> = 5 V ± 10%   |

| V <sub>OL</sub>     | CMOS output voltage low level                    | -                      | -   | 0.6                  | V     | I <sub>OL</sub> = 8 mA,<br>V <sub>DDD</sub> = 3.3 V ± 10% |

| V <sub>OL</sub>     | CMOS output voltage low level                    | -                      | -   | 0.6                  | V     | I <sub>OL</sub> = 4 mA,<br>V <sub>DDD</sub> = 1.8 V ± 5%  |

| Rpullup             | Pull-up resistor                                 | 3.5                    | 5.6 | 8.5                  | kΩ    | -                                                         |

| Rpulldown           | Pull-down resistor                               | 3.5                    | 5.6 | 8.5                  | kΩ    | -                                                         |

| I <sub>IL</sub>     | Input leakage current (absolute value)           | -                      | -   | 2                    | nA    | 25 °C, V <sub>DDD</sub> = 3.0 V                           |

| C <sub>IN</sub>     | Input capacitance                                | -                      | -   | 7                    | pF    | -                                                         |

| Vhysttl             | Input hysteresis LVTTL; V <sub>DDD</sub> > 2.7 V | 25                     | 40  | -                    | mV    | -                                                         |

| Vhyscmos            | Input hysteresis CMOS                            | $0.05 \times V_{DDD}$  | -   | _                    | mV    | _                                                         |

## Table 8. GPIO AC Specifications

| Parameter              | Description            | Min | Тур | Max | Units | Details/Conditions                                |

|------------------------|------------------------|-----|-----|-----|-------|---------------------------------------------------|

| T <sub>RiseFast1</sub> | Rise Time in Fast mode | 2   | -   | 12  | ns    | V <sub>DDD</sub> = 3.3 V/ 5.5 V,<br>Cload = 25 pF |

| T <sub>FallFast1</sub> | Fall Time in Fast mode | 2   | -   | 12  | ns    | V <sub>DDD</sub> = 3.3 V/ 5.5 V,<br>Cload = 25 pF |

| T <sub>RiseSlow1</sub> | Rise Time in Slow mode | 10  | -   | 60  | ns    | V <sub>DDD</sub> = 3.3 V/ 5.5 V,<br>Cload = 25 pF |

| T <sub>FallSlow1</sub> | Fall Time in Slow mode | 10  | -   | 60  | ns    | V <sub>DDD</sub> = 3.3 V/ 5.5 V,<br>Cload = 25 pF |

| T <sub>RiseFast2</sub> | Rise Time in Fast mode | 2   | —   | 20  | ns    | V <sub>DDD</sub> = 1.8 V, Cload = 25 pF           |

| T <sub>FallFast2</sub> | Fall Time in Fast mode | 20  | —   | 100 | ns    | V <sub>DDD</sub> = 1.8 V, Cload = 25 pF           |

| T <sub>RiseSlow2</sub> | Rise Time in Slow mode | 2   | —   | 20  | ns    | V <sub>DDD</sub> = 1.8 V, Cload = 25 pF           |

| T <sub>FallSlow2</sub> | Fall Time in Slow mode | 20  | _   | 100 | ns    | V <sub>DDD</sub> = 1.8 V, Cload = 25 pF           |

## nXRES

## Table 9. nXRES DC Specifications

| Parameter       | Description                  | Min                    | Тур | Max                  | Units | Details/Conditions |

|-----------------|------------------------------|------------------------|-----|----------------------|-------|--------------------|

| V <sub>IH</sub> | Input voltage high threshold | 0.7 × V <sub>DDD</sub> | -   | -                    | V     | -                  |

| V <sub>IL</sub> | Input voltage low threshold  | _                      | -   | $0.3 \times V_{DDD}$ | V     | -                  |

| Rpullup         | Pull-up resistor             | 3.5                    | 5.6 | 8.5                  | kΩ    | -                  |

| C <sub>IN</sub> | Input capacitance            | -                      | 5   | -                    | pF    | -                  |

| Vhysxres        | Input voltage hysteresis     | -                      | 100 | -                    | mV    | -                  |

## Table 10. nXRES AC Specifications

| Parameter   | Description       | Min | Тур | Мах | Units | Details/Conditions |

|-------------|-------------------|-----|-----|-----|-------|--------------------|

| Tresetwidth | Reset pulse width | 1   | 1   | _   | μs    | -                  |

## I<sup>2</sup>C Specifications

## Table 11. I<sup>2</sup>C AC Specifications

| Parameter        | Description                | Min | Тур | Мах | Units | Details/Conditions |

|------------------|----------------------------|-----|-----|-----|-------|--------------------|

| F <sub>I2C</sub> | I <sup>2</sup> C frequency | 1   | 1   | 400 | kHz   | -                  |

## **Flash Memory Specifications**

## Table 12. Flash Memory Specifications

| Parameter | Description                                                 | Min   | Тур | Мах | Units  | Details/Conditions |

|-----------|-------------------------------------------------------------|-------|-----|-----|--------|--------------------|

| Fend      | Flash endurance                                             | 100 K | -   | _   | cycles | -                  |

|           | Flash retention. $T_A \le 85$ °C, 10 K program/erase cycles | 10    | -   | -   | years  | -                  |

## **Pin Description**

| Pin <sup>[3]</sup> | Туре     | Name     | )        | Default                                                                                               |  |

|--------------------|----------|----------|----------|-------------------------------------------------------------------------------------------------------|--|

| 1                  | Power    | VDDD     | )        | VDDD Core                                                                                             |  |

| 2                  | GPIO     | GPIO_8   | GPIO IN  | GPIO Input Pin (see Table 15)                                                                         |  |

| 3                  | GPIO     | GPIO_9   | GPIO OUT | GPIO Out Pin (see Table 15)                                                                           |  |

| 4                  | Power    | VSSE     | )        | Digital Ground                                                                                        |  |

| 5                  | SCB/GPIO | SCL_     | 1        | SCB1 I <sup>2</sup> C Clock                                                                           |  |

| 6                  | SCB/GPIO | SDA_     | 1        | SCB1 I <sup>2</sup> C Data                                                                            |  |

| 7                  | GPIO     | GPIO_12  | GPIO OUT | GPIO Out Pin (see Table 15)                                                                           |  |

| 8                  | GPIO     | GPIO_13  | GPIO OUT | GPIO Out Pin (see Table 15)                                                                           |  |

| 9                  | GPIO     | TX_RX LE | ED_1     | Notification LED for I <sup>2</sup> C SCB1 Tx/RX                                                      |  |

| 10                 | GPIO     | TX_RX LE | ED_0     | Notification LED for I <sup>2</sup> C SCB0 Tx/RX                                                      |  |

| 11                 | Output   | Susper   | nd       | Asserted when the part enters Low Power mode                                                          |  |

| 12                 | Input    | Wakeu    | ıp       | Wakeup device from suspend mode. Can be configured as active high/low using configuration utility     |  |

| 13                 | GPIO     | GPIO_16  | GPIO OUT | GPIO Out Pin (see Table 15)                                                                           |  |

| 14                 | USBIO    | USBD     | Р        | USB Data Signal Plus, integrates termination resistor and 1.5-k $\Omega$ pull up resistor             |  |

| 15                 | USBIO    | USBD     | М        | USB Data Signal Minus, integrates termination resistor                                                |  |

| 16                 | Power    | VCCE     | )        | Regulated supply, connect to 1-µF cap or 1.8 V (Internal LDO Output)                                  |  |

| 17                 | Power    | VSSE     | )        | Digital Ground                                                                                        |  |

| 18                 | Reset    | nXRE     | S        | Chip Reset active, low. Can be left unconnected or have a pull up resistor connected when not in use. |  |

| 19                 | Power    | VBUS     | 3        | USB VBUS                                                                                              |  |

| 20                 | Power    | VSSD (VE | BUS)     | Digital Ground                                                                                        |  |

| 21                 | GPIO     | GPIO_17  | GPIO OUT | GPIO Out Pin (see Table 15)                                                                           |  |

| 22                 | GPIO     | GPIO_18  | GPIO OUT | GPIO Out Pin (see Table 15)                                                                           |  |

| 23                 | Power    | VDDD_    | 10       | VDDD for IO pins                                                                                      |  |

| 24                 | Power    | VSSA     | ٨        | Analog Ground                                                                                         |  |

| 25                 | GPIO     | GPIO_0   | GPIO IN  | GPIO Input Pin (see Table 15)                                                                         |  |

| 26                 | GPIO     | GPIO_1   | GPIO IN  | GPIO Input Pin (see Table 15)                                                                         |  |

| 27                 | GPIO     | GPIO_2   | GPIO IN  | GPIO Input Pin (see Table 15)                                                                         |  |

| 28                 | SCB/GPIO | SCL_     |          | SCB0 I <sup>2</sup> C Clock                                                                           |  |

| 29                 | SCB/GPIO | SDA_     |          | SCB0 I <sup>2</sup> C Data                                                                            |  |

| 30                 | GPIO     | GPIO_5   | GPIO IN  | GPIO Input Pin (see Table 15)                                                                         |  |

| 31                 | Output   | POWE     | ₹#       | Signal to external logic to indicate<br>USB Unconfigured state and USB Suspend                        |  |

| 32                 | GPIO     | GPIO_7   | GPIO IN  | GPIO Input Pin (see Table 15)                                                                         |  |

Note 3. Any pin acting as an input pin should not be left unconnected.

Figure 2. 32-Pin QFN Pinout

| Pin  | Serial Port 0 | Mode 0 <sup>[4]</sup>   | Mode 1                 |  |

|------|---------------|-------------------------|------------------------|--|

| FIII |               | I <sup>2</sup> C Master | I <sup>2</sup> C Slave |  |

| 2    | SCB0_0        | GPIO_8                  | GPIO_8                 |  |

| 27   | SCB0_1        | GPIO_2                  | GPIO_2                 |  |

| 28   | SCB0_2        | SCL_OUT_0               | SCL_IN_0               |  |

| 29   | SCB0_3        | SDA_0                   | SDA_0                  |  |

| 30   | SCB0_4        | GPIO_5                  | GPIO_5                 |  |

| 3    | SCB0_5        | GPIO_9                  | GPIO_9                 |  |

## Table 13. Serial Communication Block (SCB0) Configuration

## Table 14. Serial Communication Block (SCB1) Configuration

| Pin | Serial Port 1 | <b>Mode 0</b> <sup>[4]</sup> | Mode 1                 |

|-----|---------------|------------------------------|------------------------|

| Pin | Serial Port 1 | I <sup>2</sup> C Master      | I <sup>2</sup> C Slave |

| 5   | SCB1_0        | GPIO_8                       | GPIO_8                 |

| 6   | SCB1_1        | GPIO_2                       | GPIO_2                 |

| 7   | SCB1_2        | SCL_OUT_0                    | SCL_IN_0               |

| 8   | SCB1_3        | SDA_0                        | SDA_0                  |

| 9   | SCB1_4        | GPIO_5                       | GPIO_5                 |

| 10  | SCB1_5        | GPIO_9                       | GPIO_9                 |

## Legend:

| GPIO |

|------|

| SCB0 |

| SCB1 |

Note4. Device configured in Mode 0 as default. Other modes can be configured through Cypress-supplied configuration utility.

## Table 15. GPIO Configuration<sup>[5]</sup>

| <b>GPIO Configuration Option</b> | Description                                                                                                                                                                                                                                                                                                                        |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRISTATE                         | I/O tristated                                                                                                                                                                                                                                                                                                                      |

| DRIVE 1                          | Output static 1                                                                                                                                                                                                                                                                                                                    |

| DRIVE 0                          | Output static 0                                                                                                                                                                                                                                                                                                                    |

| POWER#                           | This output is used to control power to an external logic via switch to cut power off during uncon-<br>figured USB device and USB suspend.<br>0 - USB device in Configured state<br>1 - USB device in Unconfigured state or during USB suspend mode                                                                                |

| TXLED#                           | Drives LED during USB transmit                                                                                                                                                                                                                                                                                                     |

| RXLED#                           | Drives LED during USB receive                                                                                                                                                                                                                                                                                                      |

| TX or RX LED#                    | Drives LED during USB transmit or receive                                                                                                                                                                                                                                                                                          |

| BCD0<br>BCD1                     | Configurable battery charger detect pins to indicate type of USB charger (SDP, CDP, or DCP)<br>Configuration example:<br>00 - Draw up to 100 mA (Unconfigured state)<br>01 - SDP (up to 500 mA)<br>10 - CDP/DCP (up to 1.5 A)<br>11 - Suspend (up to 2.5 mA)<br>This truth table can be configured using the configuration utility |

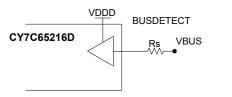

| BUSDETECT                        | VBUS detection. Connect VBUS to this pin via resistor network for VBUS detection when using BCD feature (see Figure 7).                                                                                                                                                                                                            |

Note

5. These signal options can be configured on any of the available GPIO pins using Cypress-supplied configuration utility.

## **USB** Power Configurations

The following section describes possible USB power configurations for the CY7C65216D. Refer to the Pin Description on page 14 for signal details.

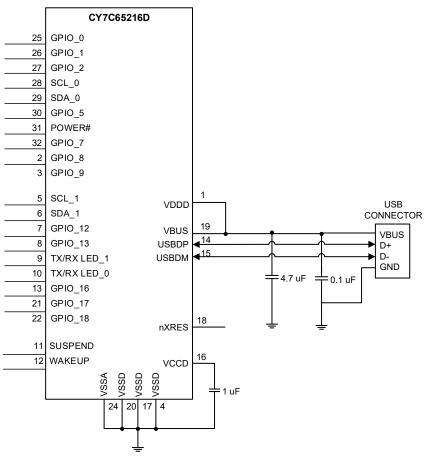

## **USB Bus-Powered Configuration**

Figure 3 shows an example of the CY7C65216D in a bus-powered design. VBUS is connected directly to the CY7C65216D because it has an internal regulator.

The USB bus-powered system must comply with the following requirements:

- 1. The system should not draw more than 100 mA prior to USB enumeration (Unconfigured state).

- 2. The system should not draw more than 2.5 mA during USB Suspend mode.

- 3. A high-power bus-powered system (can draw more than 100 mA when operational) must use POWER# (configured over GPIO) to keep the current consumption below 100 mA prior to USB enumeration, and 2.5 mA during USB Suspend state.

- 4. The system should not draw more than 500 mA from the USB host.

The configuration descriptor in the CY7C65216D flash should be updated to indicate bus power and the maximum current required by the system using the configuration utility.

## Figure 3. Bus-Powered Configuration

## **Self-Powered Configuration**

Figure 4 shows an example of CY7C65216D in a self-powered design.

In this configuration:

- VBUS is powered from USB VBUS. VBUS pin is also used to detect USB connection.

- VDDD is powered from an external power supply.

When VBUS is present, CY7C65216D enables an internal, 1.5-k $\Omega$  pull-up resistor on USBDP. When VBUS is absent (USB host is powered down), CY7C65216D removes the 1.5-k $\Omega$  pull-up resistor on USBDP, and this ensures no current flows from the USBDP to the USB host via a 1.5-k $\Omega$  pull-up resistor, to comply with USB 2.0 specification.

When reset is asserted to CY7C65216D, all the I/O pins are tristated.

Using the configuration utility, the configuration descriptor in the CY7C65216D flash should be updated to indicate that it is self-powered.

Figure 4. Self-Powered Configuration

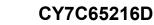

## USB Bus Powered with Variable I/O Voltage

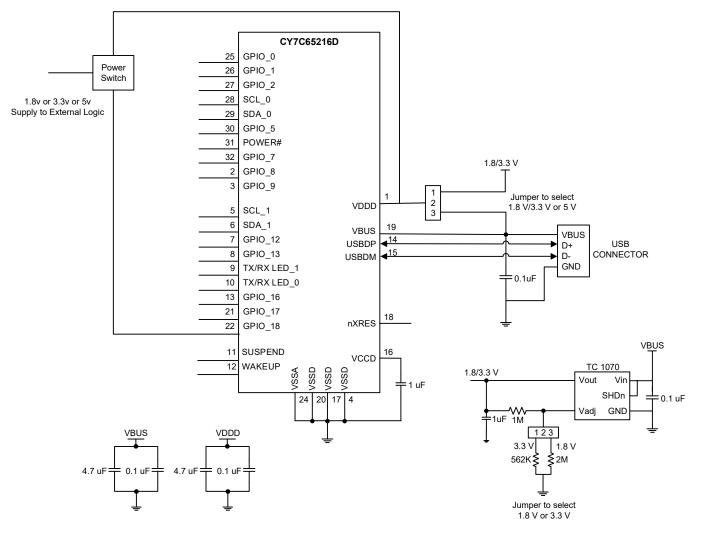

Figure 5 shows CY7C65216D in a bus-powered system with variable I/O voltage. A low dropout (LDO) regulator is used to supply 1.8 V or 3.3 V (using a jumper switch) the input of which is 5 V from VBUS. Another jumper switch is used to select 1.8/3.3 V or 5 V from VBUS for the VDDD pin of CY7C65216D. This allows I/O voltage and supply to external logic to be selected among 1.8 V, 3.3 V, or 5 V.

The USB bus-powered system must comply with the following:

- The system should not draw more than 100 mA prior to USB enumeration (Unconfigured state).

- The system should not draw more than 2.5 mA during USB Suspend mode.

- A high-power bus-powered system (can draw more than 100 mA when operational) must use POWER# (configured over GPIO) to keep the current consumption below 100 mA prior to USB enumeration and 2.5 mA during USB Suspend state.

#### Note 6. 1.71 V ≤ VDDD ≤ 1.89 V - Short VCCD pin with VDDD pin; VDDD > 2 V - connect a 1-μF decoupling capacitor to the VCCD pin.

## **Application Examples**

The following section provides CY7C65216D application examples.

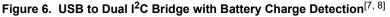

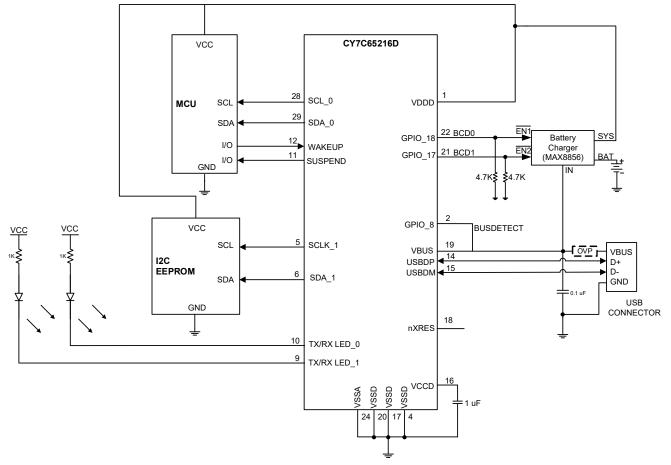

In a battery charger system.a 9-V spike on the VBUS is possible. The CY7C65216D VBUS pin is intolerant to voltage above 6 V. In the absence of over-voltage protection (OVP) on the VBUS line, VBUS should be connected to BUSDETECT (GPIO configured) using the resistive network and the output of battery charger to the VBUS pin of CY7C65216D, as shown in Figure 7.

Figure 7. GPIO VBUS Detect (BUSDETECT)

#### Notes

7. Add a 100-k $\Omega$  pull-down resistor on the V<sub>BUS</sub> pin for quick discharge.

8. Refer Figure 7, Figure 8, Figure 9 and the corresponding descriptions for handling VBUS Over Voltage Protection (OVP).

When VBUS and VDDD are at the same voltage potential, VBUS can be connected to GPIO using a series resistor (Rs). This is shown in Figure 8. If there is a charger failure and VBUS becomes 9 V, then the 10-k $\Omega$  resistor plays two roles. It reduces the amount of current flowing into the forward biased diodes in the GPIO, and it reduces the voltage seen on the pad.

## Figure 8. GPIO VBUS Detection, VBUS = VDDD

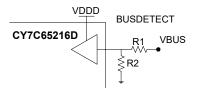

When VBUS > VDDD, a resistor voltage divider is necessary to reduce the voltage from VBUS down to VDDD for the GPIO sensing the VBUS voltage. This is shown in the following figure. The resistors should be sized as follows:

R1 <u>></u> 10 K

R2 / (R1 + R2) = VDDD / VBUS

The first condition limits the voltage and current for the charger failure situation, as described in the previous paragraph, while the second condition allows for normal-operation VBUS detection.

## Figure 9. GPIO VBUS Detection, VBUS > VDDD

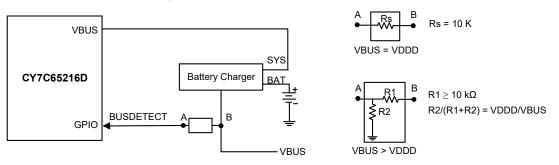

## USB to Dual Channel (I<sup>2</sup>C) Bridge

In Figure 10, CY7C65216D is configured as a USB-to-Dual Channel (I<sup>2</sup>C) Bridge. GPIO1 and GPIO0 are configured as RXLED# and TXLED# to drive two LEDs indicating data USB receive and transmit respectively.

## l<sup>2</sup>C

The CY7C65216D I<sup>2</sup>C can be configured as a Master or Slave using the configuration utility. CY7C65216D supports I<sup>2</sup>C data rates up to 100 kbps in the standard mode (SM) and 400 kbps in the fast mode (FM).

In the master mode, SCL is output from CY7C65216D. In the slave mode, SCL is input to CY7C65216D. The I<sup>2</sup>C slave address for CY7C65216D can be configured using the configuration utility. The SDA data line is bi-directional in the master and slave modes. The drive modes of the SCL and SDA port pins are always open drain.

Refer to the NXP I<sup>2</sup>C specification for further details on protocol.

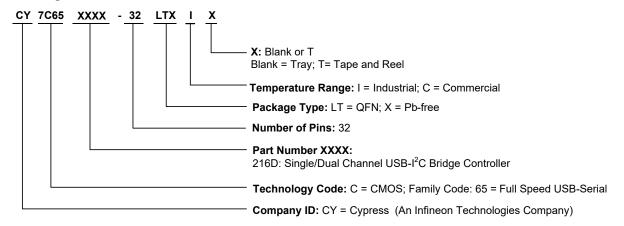

## **Ordering Information**

Table 16 lists the CY7C65216D key package features and ordering codes. For more information, contact your local sales representative.

## Table 16. Key Features and Ordering Information

| Package                                                           | Ordering Code      | Operating Range |

|-------------------------------------------------------------------|--------------------|-----------------|

| 32-pin QFN (5 × 5 × 1 mm, 0.5 mm pitch) (Pb-free)                 | CY7C65216D-32LTXI  | Industrial      |

| 32-pin QFN (5 × 5 × 1 mm, 0.5 mm pitch) (Pb-free) – Tape and Reel | CY7C65216D-32LTXIT | Industrial      |

## **Ordering Code Definitions**

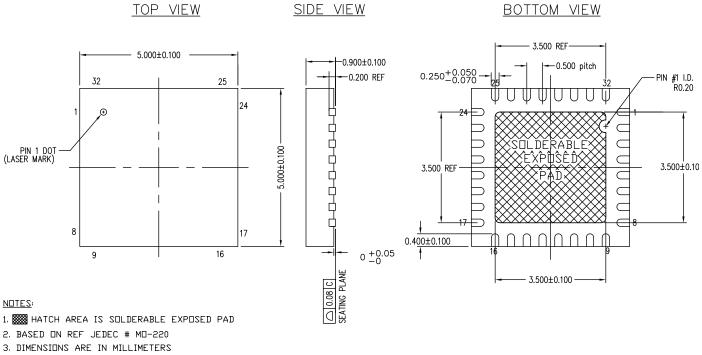

## **Package Information**

The package currently planned to be supported is the 32-pin QFN.

## Figure 11. 32-pin QFN 5 × 5 × 1.0 mm LT32B 3.5 × 3.5 EPAD (Sawn)

4. PACKAGE WEIGHT: SEE CYPRESS PACKAGE MATERIAL DECLARATION DATASHEET (PMDD) POSTED ON THE CYPRESS WEB

#### Table 17. Package Characteristics

| Parameter      | Description                   | Min | Тур | Max | Units |

|----------------|-------------------------------|-----|-----|-----|-------|

| T <sub>A</sub> | Operating ambient temperature | -40 | 25  | 85  | °C    |

| THJ            | Package $\theta_{JA}$         | _   | 19  | _   | °C/W  |

## Table 18. Solder Reflow Peak Temperature

| Package    | Maximum Peak Temperature | Maximum Time at Peak Temperature |

|------------|--------------------------|----------------------------------|

| 32-pin QFN | 260 °C                   | 30 seconds                       |

## Table 19. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package    | MSL   |

|------------|-------|

| 32-pin QFN | MSL 3 |

001-30999 \*D

## Acronyms

## Table 20. Acronyms Used in this Document

| Acronym          | Description                       |

|------------------|-----------------------------------|

| BCD              | battery charger detection         |

| CDC              | communication driver class        |

| CDP              | charging downstream port          |

| DCP              | dedicated charging port           |

| DLL              | dynamic link library              |

| ESD              | electrostatic discharge           |

| GPIO             | general purpose input/output      |

| HBM              | human-body model                  |

| I <sup>2</sup> C | inter-integrated circuit          |

| MCU              | Microcontroller Unit              |

| OSC              | oscillator                        |

| PHDC             | personal health care device class |

| PID              | Product Identification            |

| SCB              | serial communication block        |

| SCL              | I <sup>2</sup> C Serial Clock     |

| SDA              | I <sup>2</sup> C Serial Data      |

| SDP              | Standard Downstream Port          |

| SIE              | serial interface engine           |

| VCOM             | virtual communication port        |

| USB              | Universal Serial Bus              |

| VID              | Vendor Identification             |

## **Document Conventions**

## Units of Measure

## Table 21. Units of Measure

| Symbol | Unit of Measure                           |

|--------|-------------------------------------------|

| °C     | degree Celsius                            |

| DMIPS  | dhrystone million instructions per second |

| kΩ     | kilo-ohm                                  |

| KB     | kilobyte                                  |

| kHz    | kilohertz                                 |

| kV     | kilovolt                                  |

| Mbps   | megabits per second                       |

| MHz    | megahertz                                 |

| mm     | millimeter                                |

| V      | volt                                      |

## Errata

This section describes the errata for the CY7C65216D USB-Serial family. Details include errata trigger conditions, scope of impact, and available workaround.

Contact your local Cypress Sales Representative if you have questions.

## Part Numbers Affected

| Part Number | Device Characteristics |

|-------------|------------------------|

| CY7C65216D  | All Variants           |

## **Qualification Status**

Production

## Errata Summary

The following table defines the errata applicability to available USB-Serial devices.

| Items                                                                  | Affected Part Number | Fix Status          |

|------------------------------------------------------------------------|----------------------|---------------------|

| [1.] I2C Reads are slower when USB-Serial is configured as I2C Master. | CY7C65216D           | Workaround Provided |

| 1. I <sup>2</sup> C Reads are slower when USB-Serial is configured as I <sup>2</sup> C Master.                                                                                                                           |                                                                                                                                                                                                                 |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Problem Definition                                                                                                                                                                                                       | $I^2C$ reads done by USB-Serial configured as $I^2C$ Master are observed to be slower. This is because of significant delay between the $I^2C$ read initiation and the reception of data from the $I^2C$ Slave. |  |

| READ INITIATION     DATA RETURNED FROM THE SLAVE       Device (Slave) Address (7 bits)     Register Address N (8 bits)       S A65 A5 A4 A3 A2 A1 A0 0 A B7 B6 B5 B4 B3 B2 B1 B0 A     DELAY       T R/W = 0 ACK     ACK |                                                                                                                                                                                                                 |  |

| Parameters Affected                                                                                                                                                                                                      | NA                                                                                                                                                                                                              |  |

| Trigger Condition(s)                                                                                                                                                                                                     | No specific trigger condition. The delay is observed between every I <sup>2</sup> C Read initiation from the master and reception of slave data                                                                 |  |

| Scope of Impact                                                                                                                                                                                                          | I <sup>2</sup> C read operations from the master are slower.                                                                                                                                                    |  |

| Workaround                                                                                                                                                                                                               | KBA227320 mentions the steps needed to be taken for reducing this delay.                                                                                                                                        |  |

| Fix Status                                                                                                                                                                                                               | No fix. Workaround is proven.                                                                                                                                                                                   |  |

## **Document History Page**

| Document Title: CY7C65216D, USB-Dual I <sup>2</sup> C Bridge Controller<br>Document Number: 002-31605 |         |                    |                         |

|-------------------------------------------------------------------------------------------------------|---------|--------------------|-------------------------|

| Revision                                                                                              | ECN     | Submission<br>Date | Description of Change   |

| **                                                                                                    | 6993251 | 11/25/2020         | Final datasheet to NSO. |

## Sales, Solutions, and Legal Information

## Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| Arm <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

## **PSoC<sup>®</sup> Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

#### **Cypress Developer Community**

Community | Code Examples | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2020. This document is the property of Cypress Semiconductor Corporation and its subsidiaries ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and the acties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software thereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software is provided by the Software is provided by for use with Cypress hardware production, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress shall have no liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. CYPRESS DOES NOT REPRESENT, WARRANT, OR GUARANTEE THAT CYPRESS PRODUCTS, OR SYSTEMS CREATED USING CYPRESS PRODUCTS, WILL BE FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATALOSS OR THEFT, OR OTHER SECURITY INTRUSION (collectively, "Security Breach"). Cypress disclaims any liability relating to any Security Breach, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any Security Breach. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. "High-Risk Device" means any device or system whose failure could cause personal injury, death, or properly damage. Examples of High-Risk Devices are weapons, nuclear installations, surgical implants, and other medical devices. "Critical Component" means any component of a High-Risk Device whose failure to perform can be reasonably expected to cause, directly or indirectly, the failure of the High-Risk Device, or to affect its safety or effectiveness. Cypress is

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for USB Interface IC category:

Click to view products by Infineon manufacturer:

Other Similar products are found below :

CY7C69356-48LTXC CYUSB2304-68LTXI USB2227-NU-11 USB2251-NU-06 USB3319C-GJ-TR USB3370B-EZK-TR CG7648AM CY7C65215A-32LTXI CYPD2120-24LQXI CYUSB3014-BZXCT CYWB0164BB-BZXI CYWB0224ABS-BZXI CY7C65211A-24LTXI USB3803CI-1-GL-TR LIF-UC120-SWG36ITR50 UPD360-C/6HX UPD360-B/6HX CP2102NP1174GM CY7C65642-28LTXCT CG8454AM DPO2039DABQ-13 USB7216CT-I/KDX USB7216C-I/KDX UPD720211K8-711-BAL-A CYPD4225-40LQXIT CYPM1111-40LQXI USB3317C-GJ-TR CY7C68034-56LTXC CYUSB3302-68LTXI TUSB213IRGYT TUSB213RGYT TUSB214RWBT TUSB215RGYT USB2517I-JZX-TR USB3318-CP USB3343-CP USB3503T-I/ML USB4624I-1080HN CHY100D-TL STUSB1602AQTR TUSB214IRWBT TUSB8043RGCT USB3319C-CP-TR USB3310C-CP-TR USB3310C-CP USB2532I-1080AEN CY7C65213-32LTXIT CY7C68013A-56LTXIT CYUSB2024-BZXI CYUSB3025-BZXI