## Datasheet

## **Product Feature Summary**

#### • 3 phase smart gate driver

- o 5.5 V to 60 V operating supply voltage (recommended operating condition)

- o 1.5 A sink/ 1.5 A source peak gate driver currents

- Programmable driving voltage (7 V, 10 V, 12 V, 15 V)

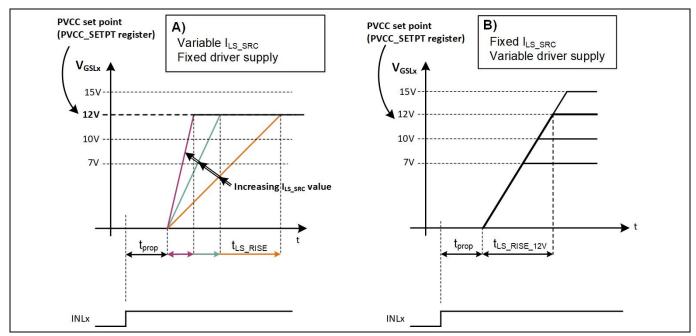

- o Independently programmable high side/low side slew rate control

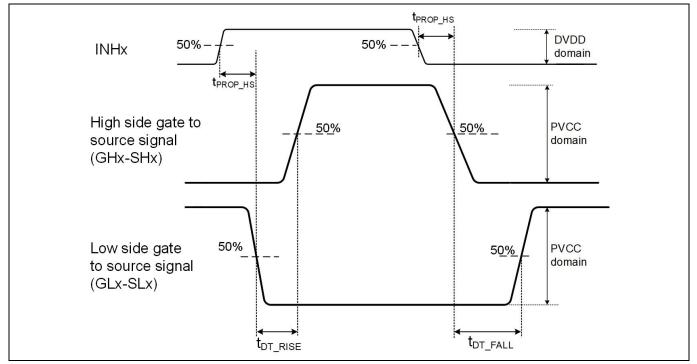

- o Independently programmable dead time for turn on/off switching

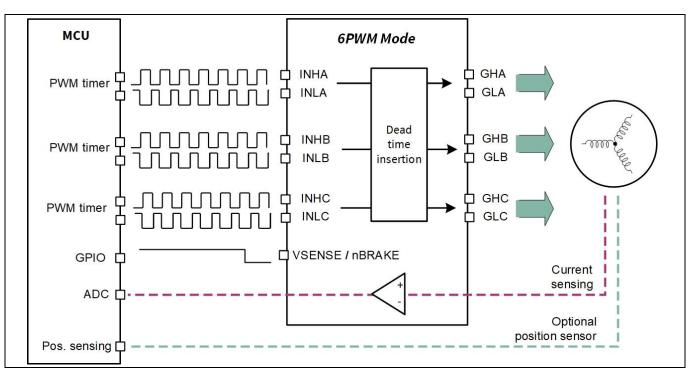

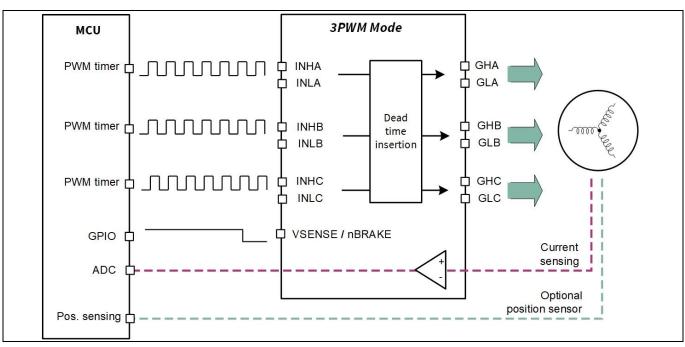

- o Control using 3PWM or 6PWM inputs up to 200 kHz

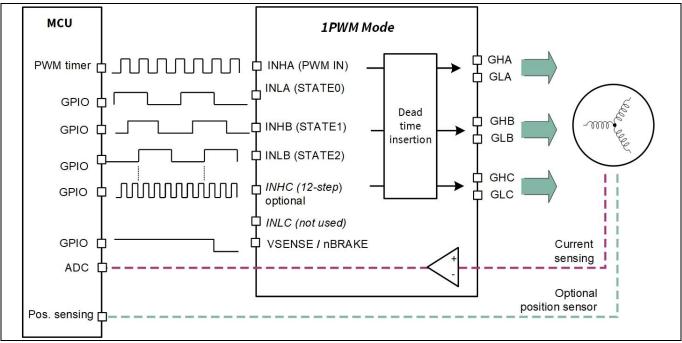

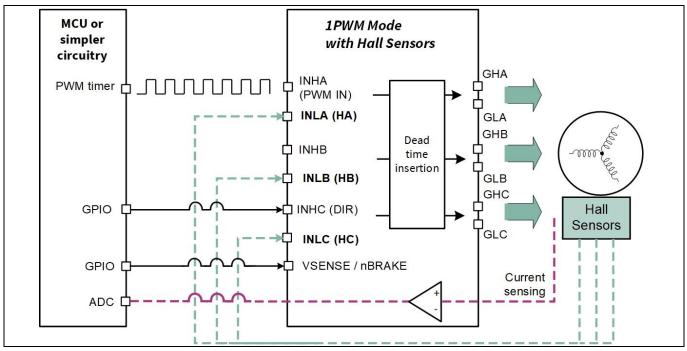

- o Built-in commutation tables for using 1PWM with or without Hall sensors

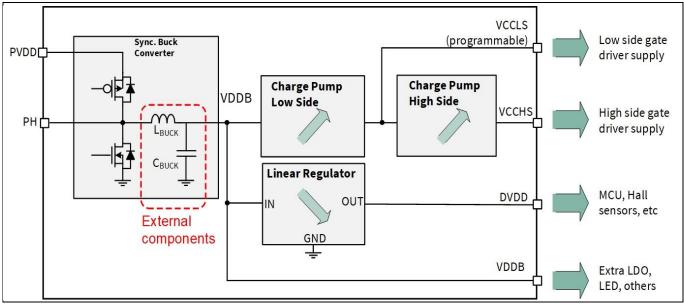

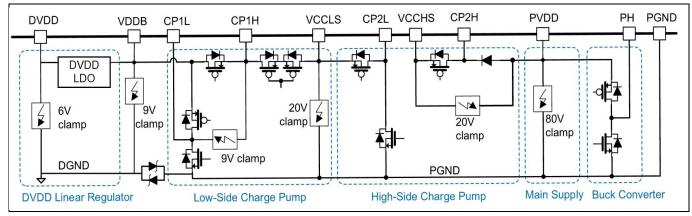

- Integrated power supplies

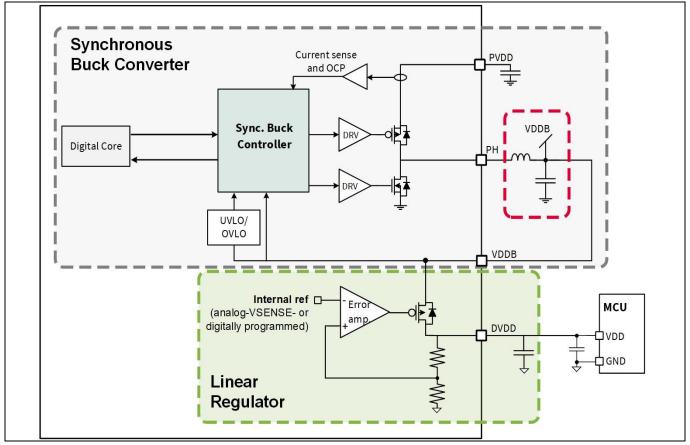

- High efficiency synchronous buck converter with programmable switching frequency. Supplies gate driver charge pumps, DVDD linear regulator and both internal and external components

- Linear regulator with 300 mA current capability for MCU and other components supply (DVDD)

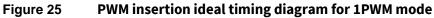

- Dual charge pump for supplying gate driver even at low supply voltage

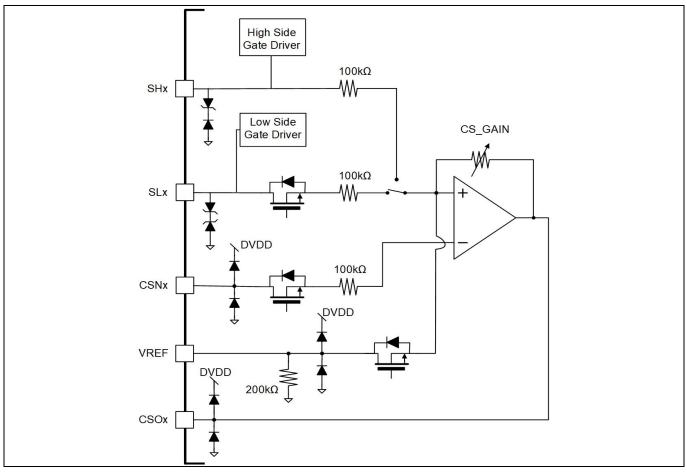

#### • Three integrated current sense amplifiers

- o Adjustable gain and offset

- Configurable low side R<sub>DSON</sub> sensing

- Three integrated Hall sensor comparators

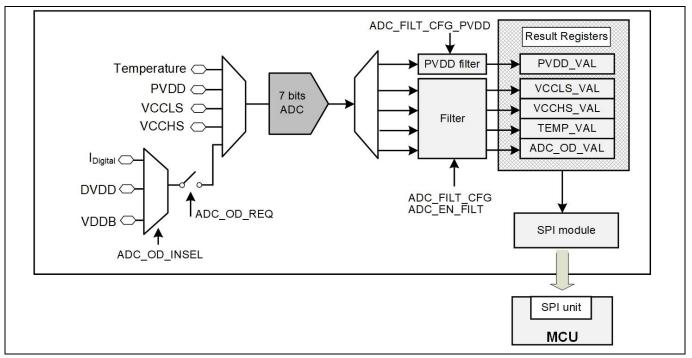

- Integrated ADC for signal monitoring

- Locked rotor detection

- 3.3 V/5 V compatible digital interface

- Programmable SPI digital interface

- Protection features:

- o External brake with programmable braking response

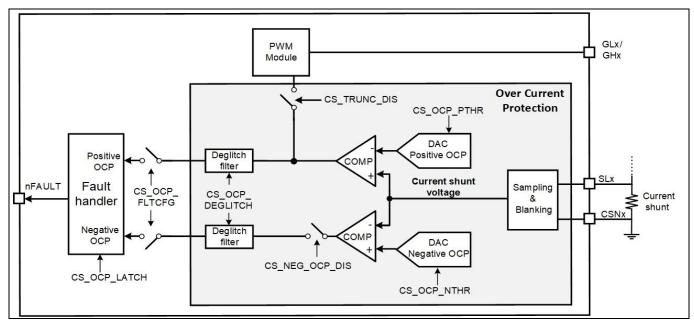

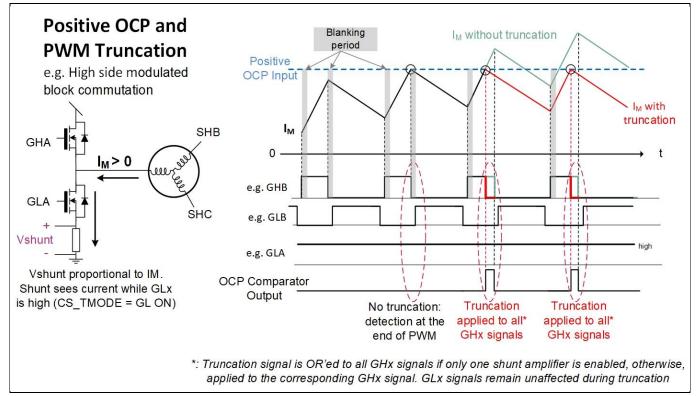

- Over-Current Protection (OCP) on current sense amplifiers (programmable)

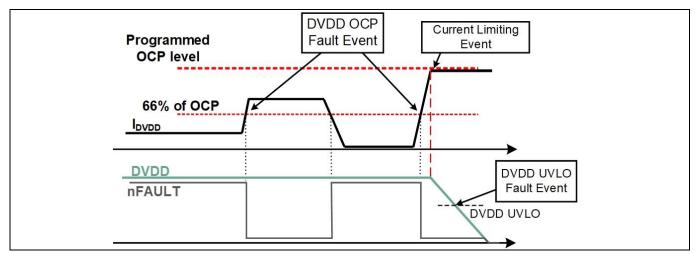

- Over-Current Protection (OCP) for buck converter and DVDD linear regulator (programmable)

- o Under-Voltage Lockouts (UVLO) for internal and external supplies

- o Over-Voltage Fault (OVLO) reporting for buck converter and DVDD linear regulator

- o Over-Temperature warning and shutdown (OTW, OTS)

- Programmable watchdog timer

- o Reporting through nFAULT and SPI registers

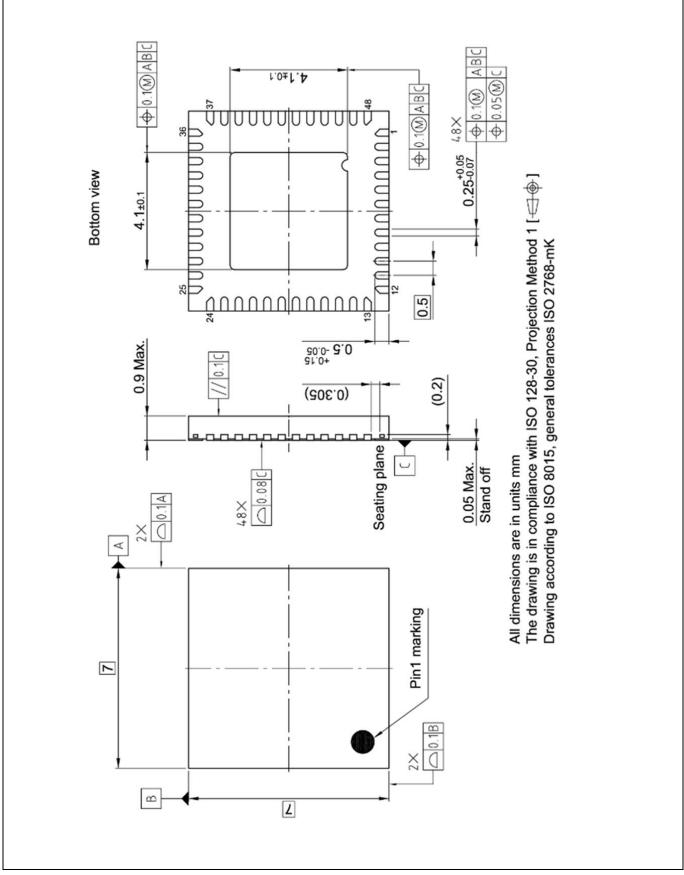

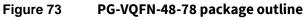

- Thermally enhanced 48pin VQFN package

Datasheet

## **Potential Applications**

- Power tools

- Gardening tools

- 3 Phase BLDC and PMSM motors

- E-bikes

- Robotics, RC toys, consumer drones and multi-copters

- Pumps and fans

## **Product Description**

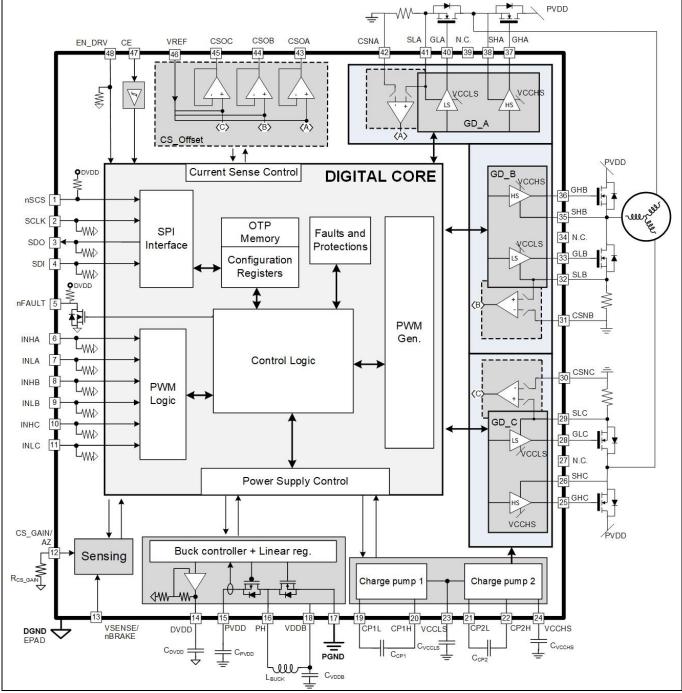

Infineon's MOTIX<sup>™</sup> 6EDL7141 is a gate driver IC for 3 phase BLDC or PMSM motor drive applications. It provides three half-bridge drivers, each capable of driving a high side and low side N-type MOSFET.

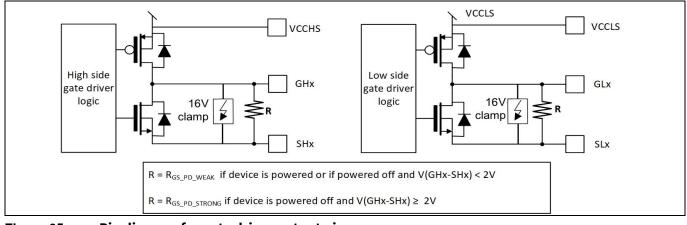

The gate driver is also provided with programmable dead time delays for preventing current shoot-through between HS and LS switches in normal operation.

Separate charge pumps for low and high side gate drivers support 100% duty cycle and low voltage supply operation. Supplies for the gate drivers are programmable to one of the following levels: 7 V, 10 V, 12 V or 15 V. Additionally, the slew rate of the driving signal can be programmed with fine granularity to reduce EMI emissions.

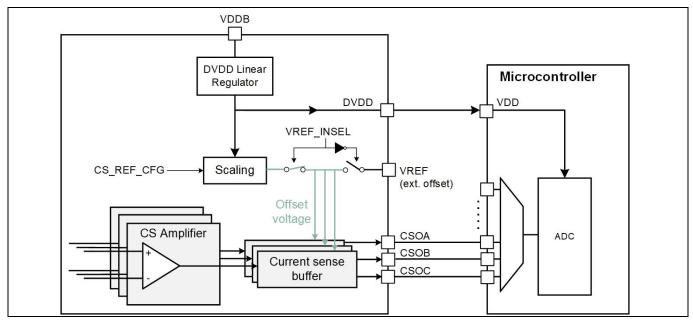

An integrated synchronous buck converter provides an efficient supply of current to the rest of the system. However, power tool systems require high precision current measurements, involving a very precise ADC reference voltage. For that purpose, 6EDL7141 uses a linear voltage regulator (up to 300mA), powered by the buck converter to supply the MCU and other sensitive components in the system. With this advanced power supply architecture, not only the best possible signal quality is achieved, but also the power efficiency is optimized at any input and output condition.

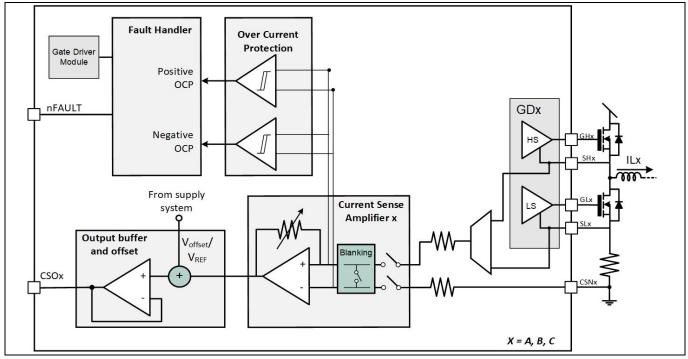

6EDL7141 includes three current sense amplifiers for accurate current measurements that support bidirectional low side current sensing with programmable gain. R<sub>DSON</sub> sensing is supported through internal connection of the phase nodes to the current sense amplifiers inputs. Temperature compensation if needed shall be provided by the user application. Outputs of current sense amplifiers support both 3.3V and 5V allowing most commercial controllers to be compatible. Low noise, low settling times and high accuracy are the main features of the integrated operational amplifiers. An internal buffer can be used to offset the sense amplifier outputs for optimizing the dynamic range.

The device provides numerous protection features for improving application robustness during adverse conditions like monitoring of power supply voltages as well as system parameters. The failure behavior, threshold voltages and filter times of the supervisions of the device are adjustable via SPI. Monitored aspects include inverter currents, gate drive voltages and currents, device temperature, and rotor locked. When a fault occurs, the device stops driving and pulls nFAULT pin low, in order to prevent system damage or other possible malfunction. This signal can be connected to a microcontroller to inform the processor that a fault has happened. The microcontroller can request more information on the fault via SPI commands.

The integrated SPI interface can be used to configure 6EDL7141 for the application. The SPI provides both detailed fault reporting and flexible parameter settings such as gain of the current sense amplifiers, slew rate control of the gate drivers, various protection features or gate driver voltage.

## System Block Diagram

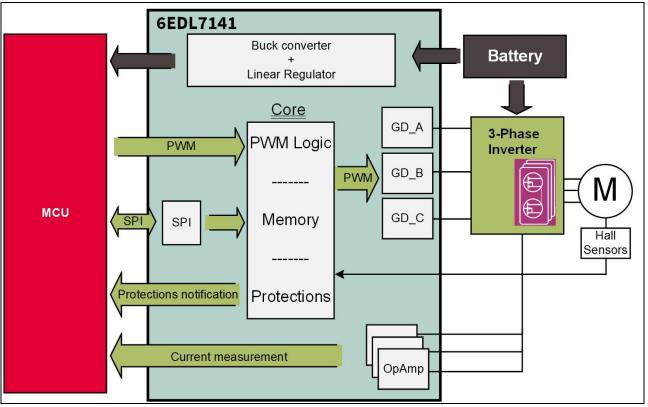

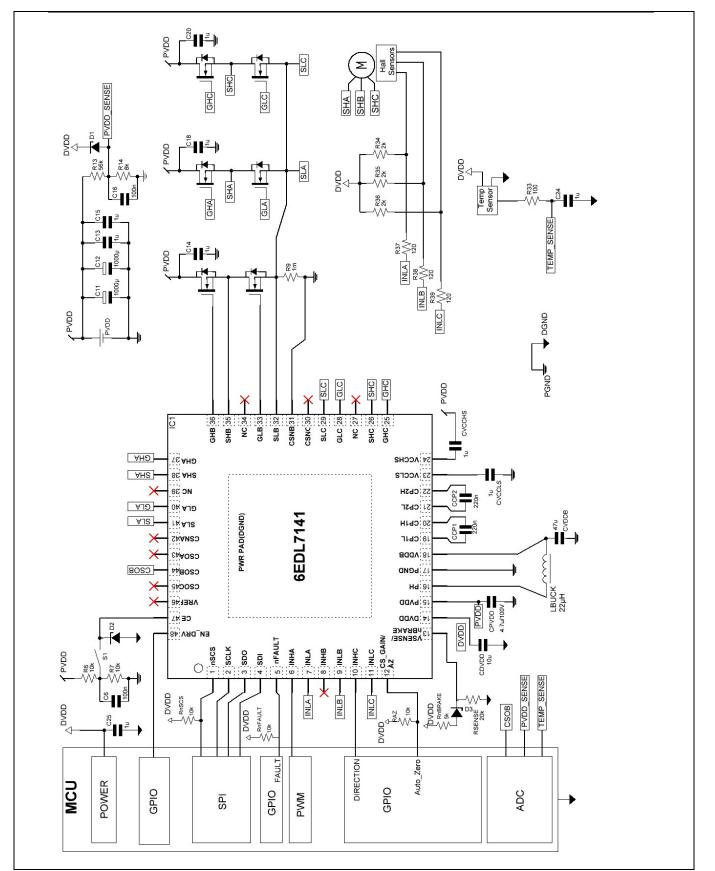

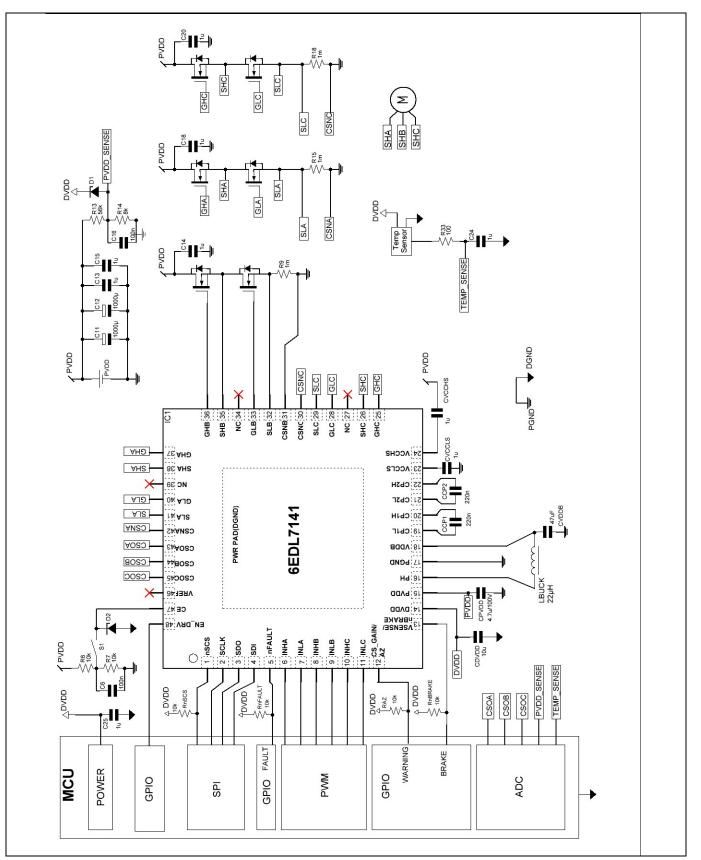

Figure 1 shows a simplified system block diagram where MOTIX<sup>™</sup> 6EDL7141 is used as a 3-phase gatedriver in a µC-based Hall-sensored BLDC motor control system. The integrated buck regulator provides the power supply for both the microcontroller unit (MCU) and the Hall sensors in the BLDC motor.

Figure 1 Simplified System Block Diagram

## **Package Description**

MOTIX<sup>™</sup> 6EDL7141 is integrated in a VQFN48 7mm x 7mm package with an exposed pad. The device and package information is shown in Table 1.

| Table 1 Device and package inform | ation |

|-----------------------------------|-------|

|-----------------------------------|-------|

| Part Number | Package       | Body Size       | Lead Pitch |

|-------------|---------------|-----------------|------------|

| 6EDL7141    | PG-VQFN-48-78 | 7.0 mm × 7.0 mm | 0.5 mm     |

Datasheet

| Table of       | contents                                                                               |    |

|----------------|----------------------------------------------------------------------------------------|----|

| Product        | Feature Summary                                                                        | 1  |

| Potentia       | al Applications                                                                        | 2  |

| Product        | Description                                                                            | 2  |

| Svstem         | Block Diagram                                                                          | 3  |

| -              | e Description                                                                          |    |

| 1              | Pin Configuration                                                                      |    |

| -              | Pin Assignment                                                                         |    |

| 1.2            | Pin Definitions and Functions                                                          |    |

| 2              | General Product Characteristics                                                        |    |

| 2.1            | Absolute Maximum Ratings                                                               |    |

| 2.2            | Recommended Operating Conditions                                                       |    |

| 2.3            | ESD Robustness                                                                         |    |

| 2.4            | Thermal Resistance                                                                     |    |

| 2.5            | Electrical Characteristics                                                             | 14 |

| 2.6            | Electrical Characteristic Graphs                                                       | 26 |

| 3              | Product Features                                                                       | 33 |

| 3.1            | Functional Block Diagram                                                               | 33 |

| 3.2            | PWM Modes                                                                              | 34 |

| 3.2.1          | PWM with 6 Independent Inputs – 6PWM                                                   | 34 |

| 3.2.2          | PWM with 3 Independent Inputs – 3PWM                                                   | 35 |

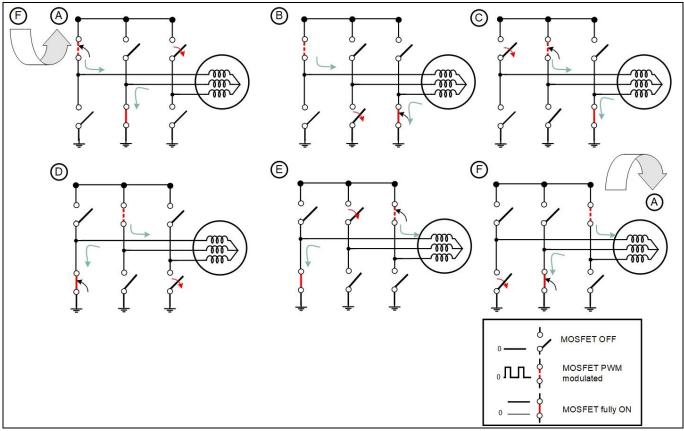

| 3.2.3          | PWM with 1 Input and Commutation Pattern – 1PWM                                        |    |

| 3.2.4          | PWM with 1 Input and Commutation with Hall Sensor Inputs – 1PWM with Hall Sensors      |    |

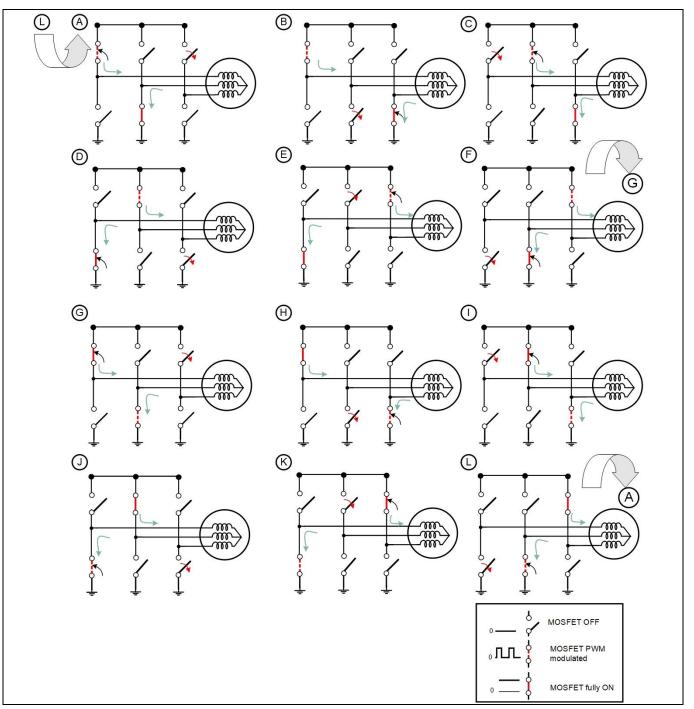

| 3.2.5          | PWM with 1 Input and Commutation with Hall Sensor Inputs and Alternating Recirculation |    |

|                | 1PWM with Hall Sensors and Alternating Recirculation                                   |    |

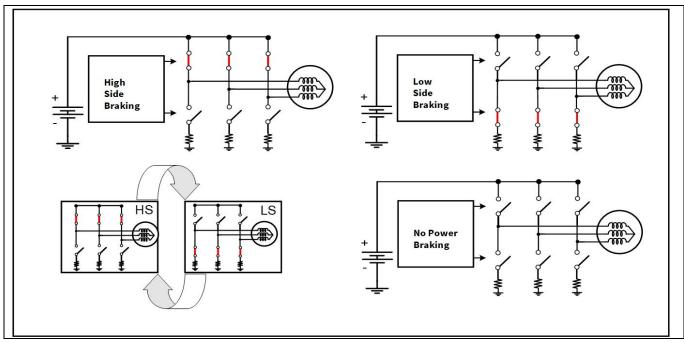

| 3.2.6          | PWM Braking Modes                                                                      |    |

| 3.2.7          | Dead Time Insertion                                                                    |    |

| 3.3            | Integrated Three Phase Gate Driver                                                     |    |

| 3.3.1          | Gate Driver Architecture                                                               |    |

| 3.3.2          | Slew Rate Control                                                                      |    |

| 3.3.3          | Gate Driver Voltage Programmability                                                    |    |

| 3.4            | Charge Pump Configuration                                                              |    |

| 3.4.1<br>3.4.2 | Charge Pump Clock Frequency Selection<br>Charge Pump Clock Spread Spectrum Feature     |    |

| 3.4.2<br>3.4.3 | Charge Pump Clock Spread Spectrum Feature<br>Charge Pump Pre-Charge for VCCLS          |    |

| 3.4.3<br>3.4.4 | Charge Pump Fre-Charge for VCCLS                                                       |    |

| J.T.T          |                                                                                        |    |

Gate Driver and Charge Pumps Protections......53

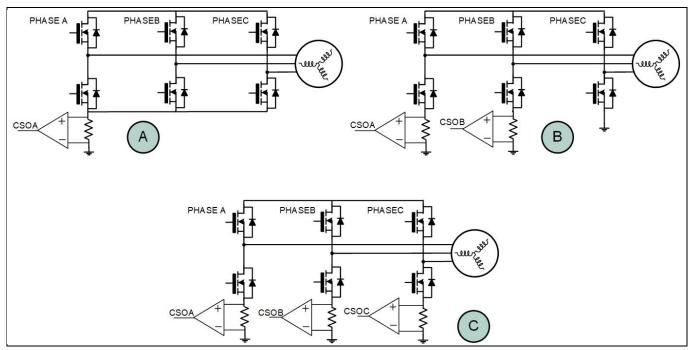

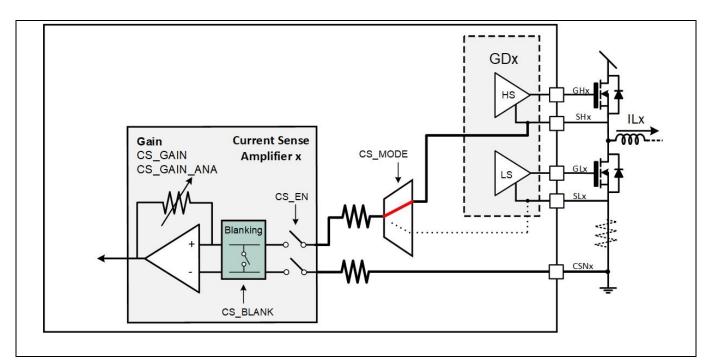

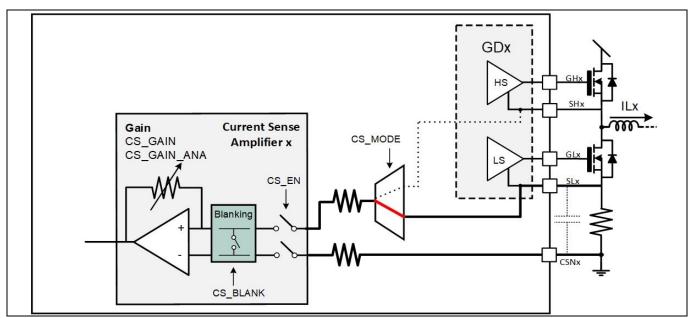

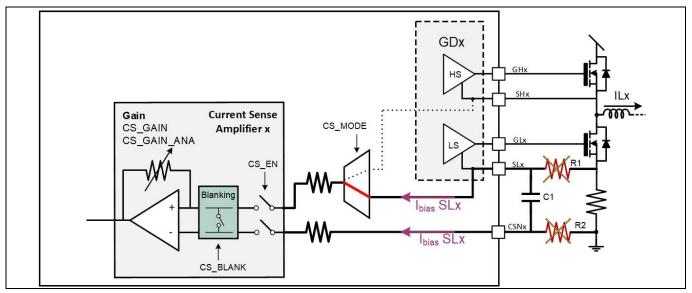

R<sub>DSON</sub> Sensing Mode vs Leg Shunt Mode.....61

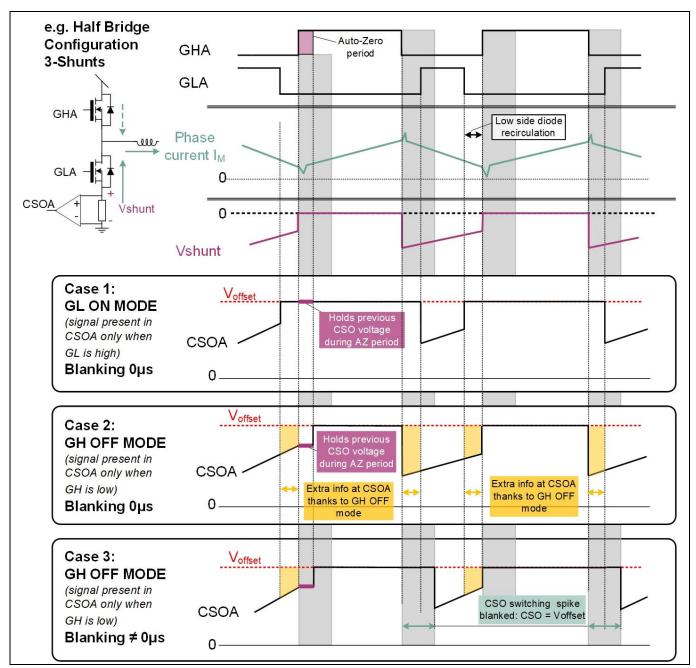

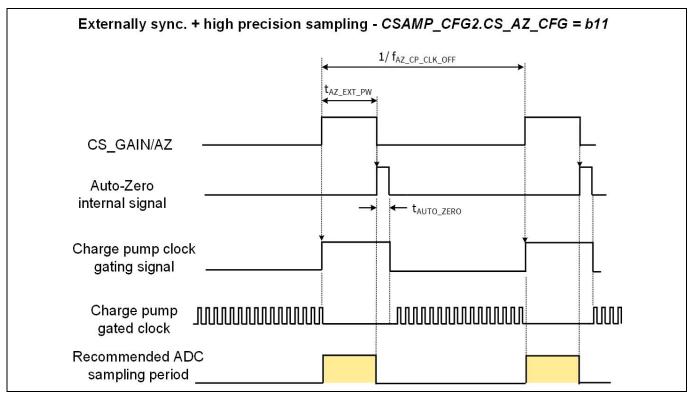

Current Shunt Amplifier Timing Mode......62

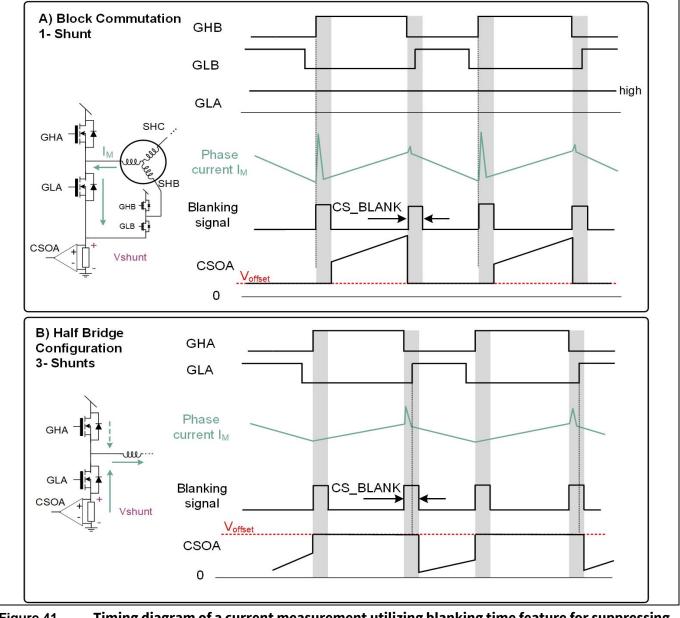

Current Shunt Amplifier Blanking Time ......64

3.4.5

3.5.2

3.6.1

3.6.2

3.6.3

3.6.4

3.6.5

3.6.6

3.6.7

3.6.8

3.6

3.5 3.5.1

| 3.7          | Hall Comparators                                              |    |

|--------------|---------------------------------------------------------------|----|

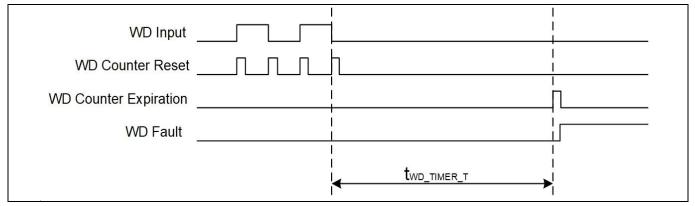

| 3.8          | Watchdog Timers                                               |    |

| 3.8.1        | Buck converter watchdog                                       | 73 |

| 3.8.2        | General Purpose Watchdog                                      | 73 |

| 3.8.3        | Locked-Rotor Protection Watchdog Timer                        | 74 |

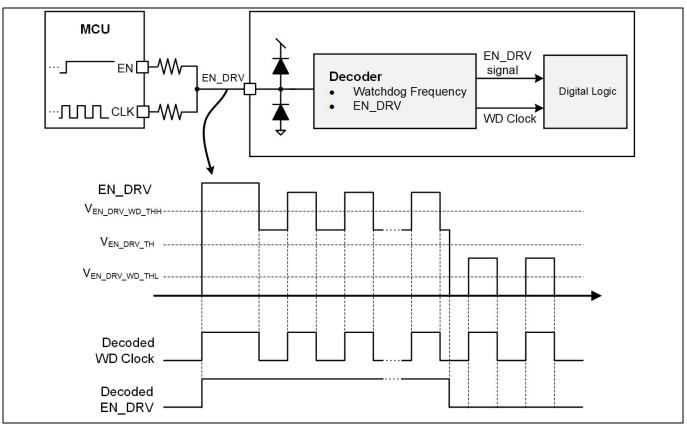

| 3.9          | Multi-Function Pins                                           | 75 |

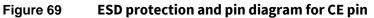

| 3.9.1        | EN_DRV Pin                                                    | 75 |

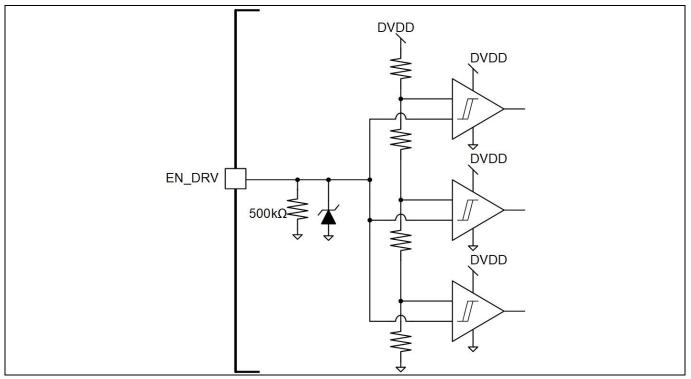

| 3.9.2        | VSENSE/nBRAKE Pin                                             | 76 |

| 3.9.3        | CS_GAIN/AZ Pin                                                | 76 |

| 3.10         | ADC Module-Analog to Digital Converter                        | 77 |

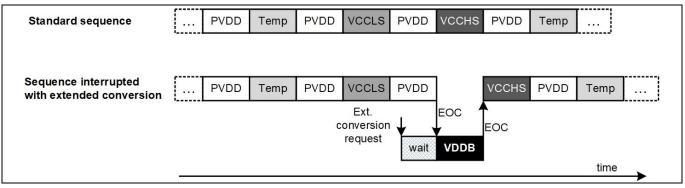

| 3.10.1       | ADC Measurement Sequencing and On Demand Conversion           |    |

| 3.10.2       | Die Temperature Sensor                                        |    |

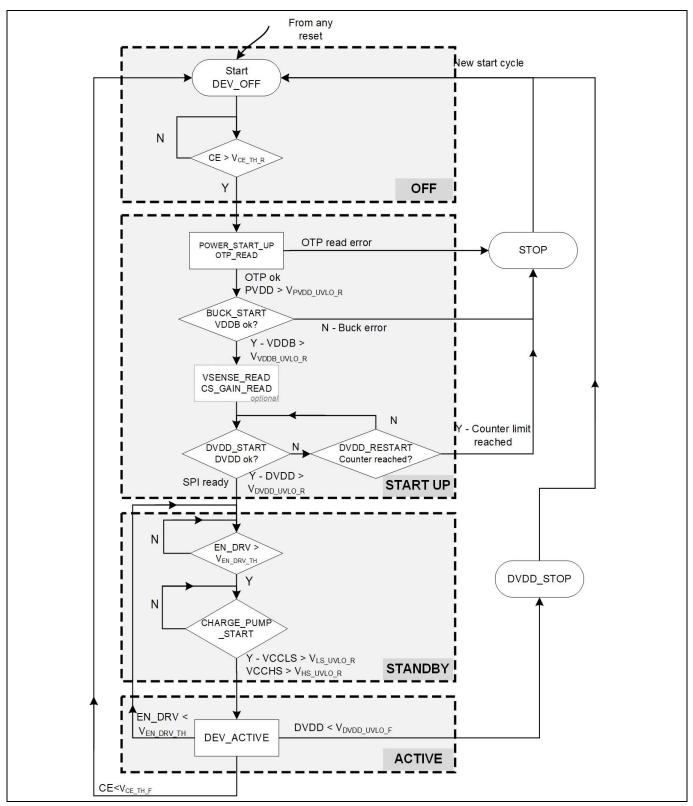

| 4            | Device Start-Up                                               |    |

| 4.1          | Power Supply Start-Up                                         |    |

| 4.2          | Gate Driver and CSAMP Start-up                                |    |

| 5            | Device Functional States                                      |    |

| -            |                                                               |    |

| 6            | Protections and Faults Handling                               |    |

| 7            | Device Programming-OTP and SPI interface                      |    |

| 7.1.1        | OTP User Programming Procedure: Loading Custom Default Values |    |

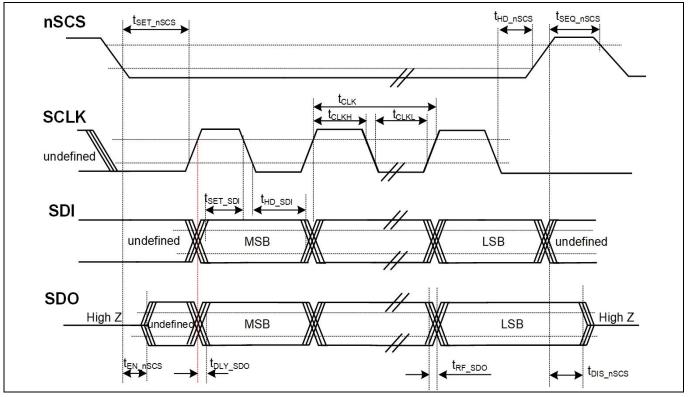

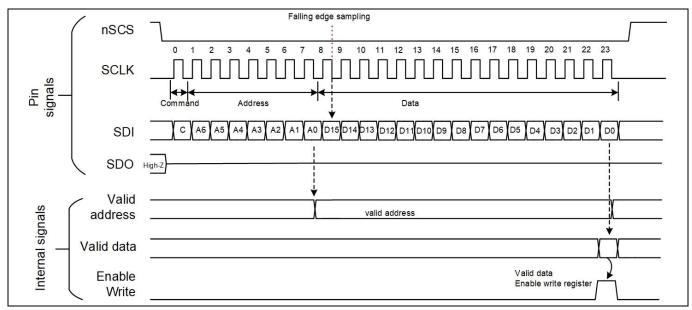

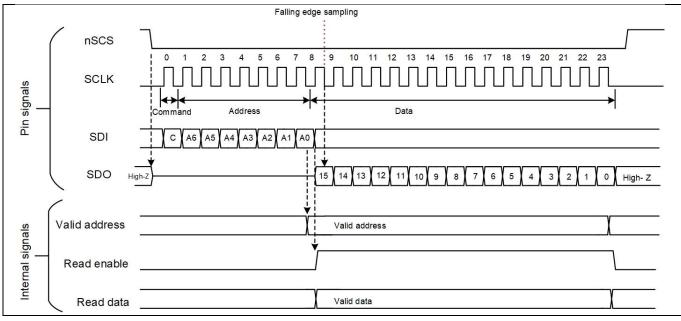

| 7.1.2        | SPI Communication                                             | 91 |

| 8            | Register Map                                                  | 93 |

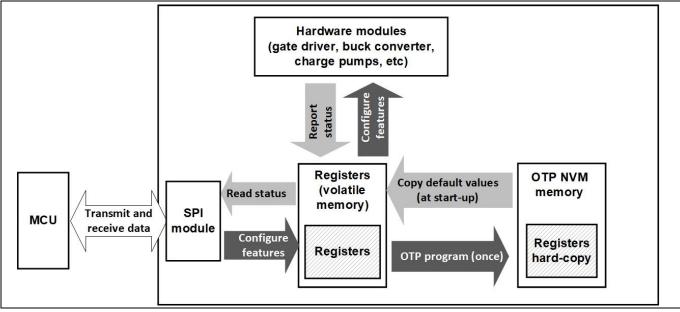

| 8.1          | Device Programmability                                        | 93 |

| 8.2          | Register Map                                                  | 97 |

| Faults Statu | s Register                                                    | 97 |

| Temperatur   | e Status Register                                             |    |

| Power Supp   | ly Status Register                                            |    |

| Functional S | Status Register                                               |    |

| OTP Status I | Register                                                      |    |

| ADC Status I | Register                                                      |    |

| Charge Pum   | ps Status Register                                            |    |

| Device ID Re | gister                                                        |    |

| Faults Clear | Register                                                      |    |

|              | ly Configuration Register                                     |    |

| ADC Configu  | iration Register                                              |    |

| -            | uration Register                                              |    |

|              | iguration Register                                            |    |

|              | onfiguration Register                                         |    |

|              | onfiguration Register 2                                       |    |

| Gate Driver  | Current Control Register                                      |    |

|              | Pre-Charge Current Control Register                           |    |

|              | rce Control Register                                          |    |

|              | Control Register                                              |    |

|              | Register                                                      |    |

|              | p Configuration Register                                      |    |

| Current Sen  | se Amplifier Configuration Register                           |    |

|              | se Amplifier Configuration Register 2                         |    |

|              | n Register                                                    |    |

|              | Application Description                                       |    |

| 9.1          | Recommended External Components                               |    |

|              |                                                               |    |

Datasheet

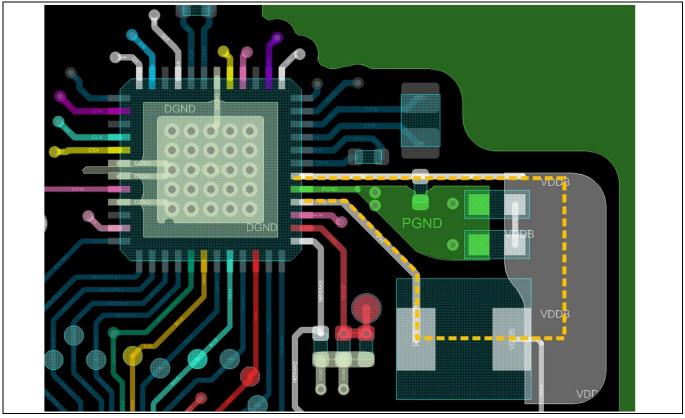

| 9.2                | PCB Layout Recommendations |     |

|--------------------|----------------------------|-----|

| 9.3                | Typical Applications       |     |

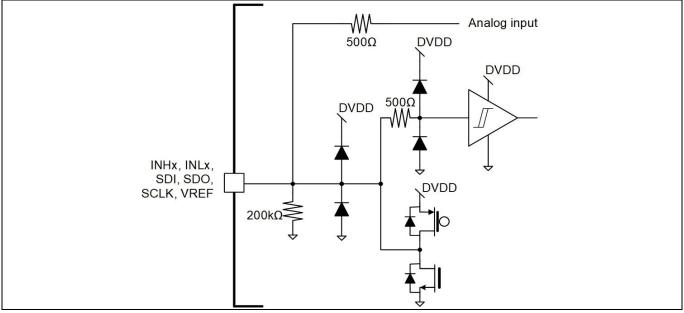

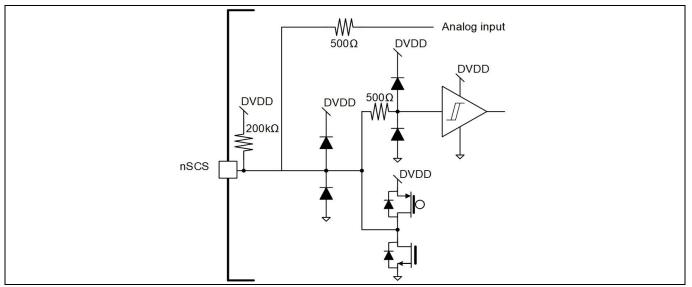

| 10                 | ESD Protection             | 129 |

| 11                 | Package Information        | 133 |

| <b>Revision hi</b> | istory                     | 135 |

## 1 Pin Configuration

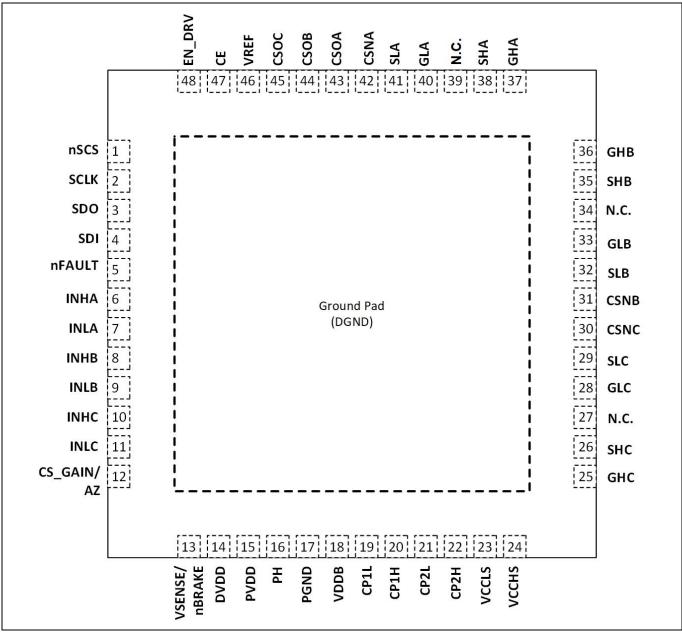

## 1.1 Pin Assignment

In Figure 2, the pinout of MOTIX<sup>™</sup> 6EDL7141 is presented.

## **1.2** Pin Definitions and Functions

Table 2 describes the different characteristics and functionalities assigned to the different pin of 6EDL7141 device.

I: Input, O: output, IO: Input and/or Output, D: Digital, A: Analog, AD: Analog and/or Digital, P: Power, G: Ground.

| able 2 | Pin de            | finition |      |                                                                                                                                                                                                                                                          |  |  |  |  |

|--------|-------------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin #  | Pin Name          | 10       | Туре | Description                                                                                                                                                                                                                                              |  |  |  |  |

| 1      | nSCS              | I        | D    | Chip Select for SPI. Active low                                                                                                                                                                                                                          |  |  |  |  |

| 2      | SCLK              | Ι        | D    | SPI clock signal                                                                                                                                                                                                                                         |  |  |  |  |

| 3      | SDO               | 0        | D    | SPI data output signal                                                                                                                                                                                                                                   |  |  |  |  |

| 4      | SDI               | I        | D    | SPI data input signal                                                                                                                                                                                                                                    |  |  |  |  |

| 5      | nFAULT            | 0        | D    | When low indicates a fault has occurred; connect external pull-up to MCU power supply                                                                                                                                                                    |  |  |  |  |

| 6      | INHA              | I        | D    | PWM input signal for channel A high side. Common PWM signal for PWM mode 1. Connect to DGND if not used                                                                                                                                                  |  |  |  |  |

| 7      | INLA              | I        | D    | PWM input signal for channel A low side.<br>Input of Hall sensor A in 1PWM modes. Connect to DGND if not used                                                                                                                                            |  |  |  |  |

| 8      | INHB              | I        | D    | PWM input signal for channel B high side. Connect to DGND if not used                                                                                                                                                                                    |  |  |  |  |

| 9      | INLB              | I        | D    | PWM input signal for channel B low side.<br>Input of Hall sensor B in 1PWM modes. Connect to DGND if not used                                                                                                                                            |  |  |  |  |

| 10     | INHC              | I        | D    | PWM input signal for channel C high side.<br>DIR signal for 1PWM modes. Connect to DGND if not used                                                                                                                                                      |  |  |  |  |

| 11     | INLC              | I        | D    | PWM input signal for channel C low side.<br>Input of Hall sensor C in 1PWM modes. Connect to DGND if not used                                                                                                                                            |  |  |  |  |

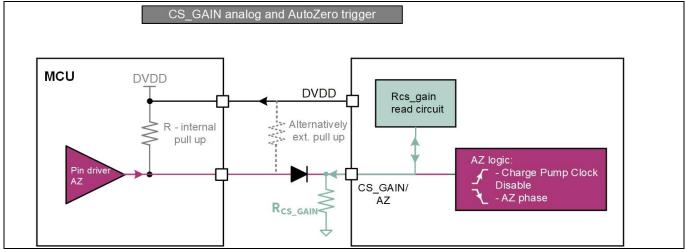

| 12     | CS_GAIN/<br>AZ    | I        | A    | Analog programming for the shunt amplifier gain.<br>Dual function as Auto-Zero: input to control external Auto-Zero<br>function                                                                                                                          |  |  |  |  |

| 13     | VSENSE/<br>nBRAKE | 1        | A/D  | Analog programming of DVDD output voltage during start-up. Connect<br>a pull down resistor to select DVDD voltage:<br>R<=3.3 kΩ→DVDD=3.3 V<br>R>= 10 kΩ→DVDD= 5.0 V<br>After start-up, pin will be in nBRAKE mode: used for motor braking.<br>Active low |  |  |  |  |

| 14     | DVDD              | -        | Ρ    | Supply for external MCU, Hall sensors, etc. Voltage is generated by integrated linear voltage regulator and defined by VSENSE pin or SPI                                                                                                                 |  |  |  |  |

| 15     | PVDD              | -        | Р    | Power supply of the device                                                                                                                                                                                                                               |  |  |  |  |

| 16     | PH                | -        | Р    | Buck phase node voltage. Connect to output inductor                                                                                                                                                                                                      |  |  |  |  |

| 17     | PGND              | -        | G    | Power ground used for buck converter, charge pumps and gate drivers                                                                                                                                                                                      |  |  |  |  |

| 18     | VDDB              | -        | Р    | Buck output voltage. Connect capacitor between VDDB and PGND.                                                                                                                                                                                            |  |  |  |  |

| 19     | CP1L              | -        | Р    | Bottom connection of the charge pump flying capacitor 1                                                                                                                                                                                                  |  |  |  |  |

| 20     | CP1H              | -        | Р    | Top connection of the charge pump flying capacitor 1                                                                                                                                                                                                     |  |  |  |  |

| 21     | CP2L              | -        | Р    | Bottom connection of the charge pump flying capacitor 2                                                                                                                                                                                                  |  |  |  |  |

| 22     | CP2H              | -        | Р    | Top connection of the charge pump flying capacitor 2                                                                                                                                                                                                     |  |  |  |  |

Pin Name

10

Туре

## Datasheet Pin Configuration

Pin #

Description

| FIII # | FIIINAIIIE | 10 | туре | Description                                                                                                                                              |

|--------|------------|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

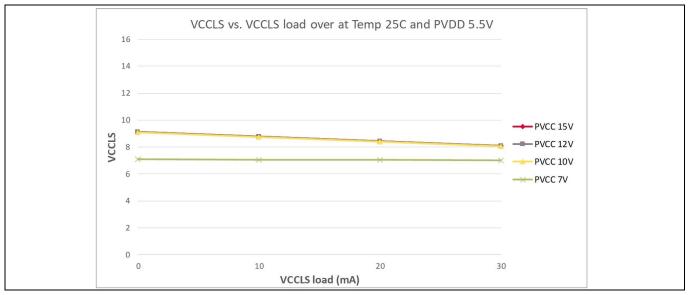

| 23     | VCCLS      | -  | Ρ    | Output of low side charge pump. Connect a capacitor from VCCLS to PGND.                                                                                  |

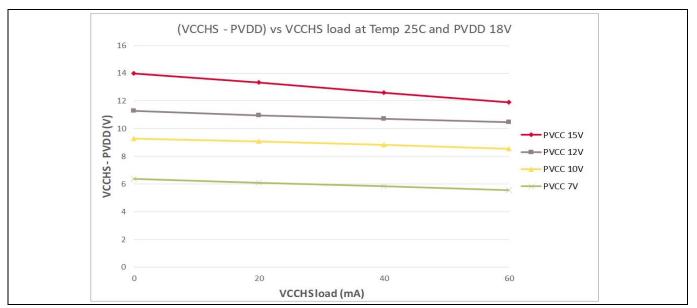

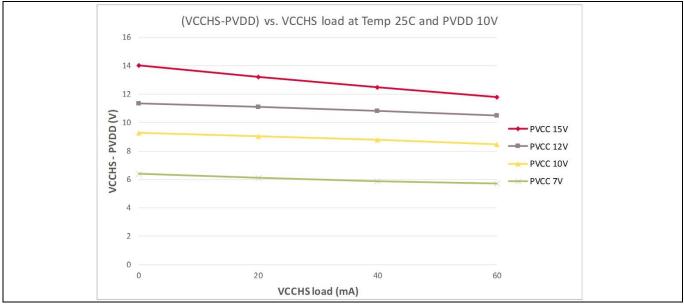

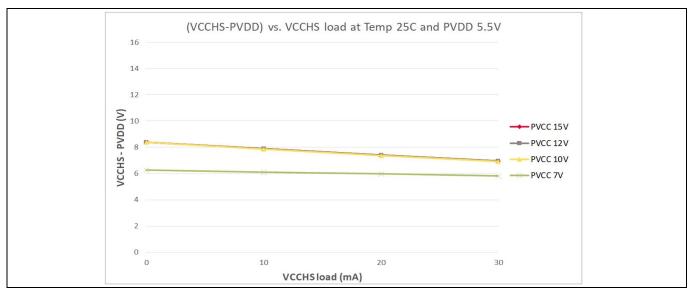

| 24     | VCCHS      | -  | Р    | Output of high side charge pump. Connect a capacitor from VCCHS to PVDD or PGND                                                                          |

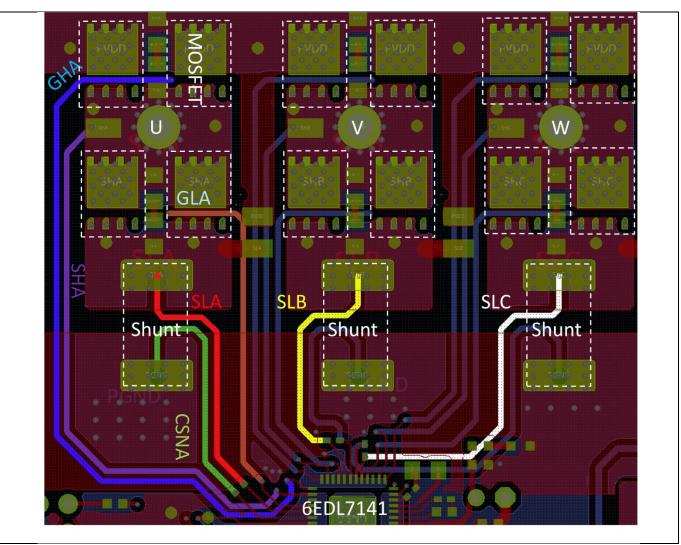

| 25     | GHC        | 0  | А    | High side gate driving signal for phase C. Not connected or connected to PVDD if not used                                                                |

| 26     | SHC        | 10 | А    | High side source connection (phase node) for phase C.<br>Positive input of shunt amplifier C for R <sub>DSON</sub> sensing. Not connected if<br>not used |

| 27     | N.C.       | -  | -    | Not connected                                                                                                                                            |

| 28     | GLC        | 0  | А    | Low side gate driving signal for phase C. Not connected if not used                                                                                      |

| 29     | SLC        | ю  | A    | Low side source connection for phase C.<br>Positive input of shunt amplifier C for shunt sensing. Short to PGND if<br>not used                           |

| 30     | CSNC       | I  | A    | Current sense amplifier negative input for phase C. Short to PGND or DGND if not used                                                                    |

| 31     | CSNB       | I  | А    | Current sense amplifier negative input for phase B. Short to PGND or DGND if not used                                                                    |

| 32     | SLB        | ю  | A    | Low side source connection for phase B.<br>Positive input of shunt amplifier B for shunt sensing. Short to PGND if<br>not used                           |

| 33     | GLB        | 0  | А    | Low side gate driving signal for phase B. Not connected if not used                                                                                      |

| 34     | N.C.       | -  | -    | Not connected                                                                                                                                            |

| 35     | SHB        | ю  | A    | High side source connection (phase node) for phase B.<br>Positive input of shunt amplifier B for R <sub>DSON</sub> sensing. Not connected if<br>not used |

| 36     | GHB        | 0  | А    | High side gate driving signal for phase B. Not connected or connected to PVDD if not used                                                                |

| 37     | GHA        | 0  | А    | High side gate driving signal for phase A. Not connected or connected to PVDD if not used                                                                |

| 38     | SHA        | 10 | A    | High side source connection (phase node) for phase A.<br>Positive input of shunt amplifier A for R <sub>DSON</sub> sensing. Not connected if<br>not used |

| 39     | N.C.       | -  | -    | Not connected                                                                                                                                            |

| 40     | GLA        | 0  | А    | Low side gate driving signal for phase A. Not connected if not used                                                                                      |

| 41     | SLA        | ю  | A    | Low side source connection for phase A.<br>Positive input of shunt amplifier A for shunt sensing. Short to PGND if<br>not used                           |

| 42     | CSNA       | 1  | А    | Current sense amplifier negative input for phase A. Short to PGND or DGND if not used                                                                    |

| 43     | CSOA       | 0  | А    | Current sense amplifier output for phase A. Not connected if not used                                                                                    |

| 44     | CSOB       | 0  | А    | Current sense amplifier output for phase B. Not connected if not used                                                                                    |

| 45     | CSOC       | 0  | А    | Current sense amplifier output for phase C. Not connected if not used                                                                                    |

|        |            |    |      |                                                                                                                                                          |

## Datasheet Pin Configuration

| Pin # | Pin Name   | 10 | Туре | Description                                                                                                                                |

|-------|------------|----|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 46    | VREF       | I  | А    | Optional reference voltage input offsetting the current sense (CS) outputs with respect to DGND. Not connected if not used                 |

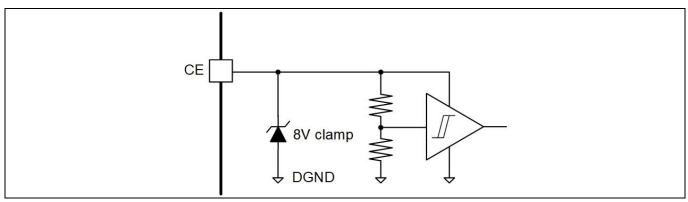

| 47    | CE         | I  | А    | Chip Enable. Starts up the device upon rising edge                                                                                         |

| 48    | EN_DRV     | I  | D    | Enables the gate driver section and internal circuitry based on the configuration. Can be configured as watchdog clock. Internal pull down |

|       | Ground Pad | -  | Р    | Ground connection for digital section. Solder to PCB.                                                                                      |

## 2 General Product Characteristics

## 2.1 Absolute Maximum Ratings

Table 3 shows the absolute maximum ratings for the device. Ratings are intended in the temperature range T<sub>j</sub>=-40°C to T<sub>j</sub>=150°C. All voltages are referred to ground (PGND for buck converter, charge pumps and gate driver related parameters and DGND for the rest), positive currents are flowing into the pin (unless otherwise specified).

| Parameter                                    | Symbol                              |              | Valı | les       | Unit      | Condition                                  |

|----------------------------------------------|-------------------------------------|--------------|------|-----------|-----------|--------------------------------------------|

| Farameter                                    | Symbol                              | Min Typ Max  |      | Unit      | Condition |                                            |

| Supply voltage                               | PVDD                                | -0.3         |      | 70        | V         |                                            |

| Supply voltage slew                          | SR <sub>PVDD</sub>                  |              |      | 2         | V/µs      | During start-up                            |

| rate                                         | SKPVDD                              |              |      | 0.25      | v/µs      | During active mode                         |

| CE pin voltage                               | V <sub>CE</sub>                     | -0.3         |      | 7         | V         |                                            |

| Power ground to<br>digital ground<br>voltage | PGND – DGND                         | -0.3         |      | 0.3       | v         |                                            |

| Low side gate driver<br>supply voltage       | VCCLS                               | -0.3         |      | 20        | V         | This is same as PVCC                       |

| VCCHS voltage                                | VCCHS                               | PVDD-<br>0.3 |      | 90        | V         | VCCHS = PVDD + PVCC                        |

| VCCHS-V <sub>SHx</sub> voltage               | VCCHS-V <sub>SHx</sub>              |              |      | 90        | V         |                                            |

| VCCHS-V <sub>GHx</sub> voltage               | VCCHS-V <sub>GHx</sub>              |              |      | 90        | V         |                                            |

| Source high side                             | V <sub>SHx</sub>                    | -8           |      | 70        | V         | DC voltage                                 |

| voltage                                      |                                     | -10          |      | 70        |           | 500ns pulse max                            |

| Source low side<br>voltage/Shunt             | V <sub>SLx</sub>                    | -8           |      | 8         | V         | DC voltage                                 |

| amplifier positive<br>input voltage          |                                     | -10          |      | 8         |           | 500ns pulse max                            |

| Gate high side                               | V <sub>GHx</sub>                    | -8           |      | VCCHS+0.3 | V         | DC voltage,                                |

| voltage                                      |                                     | -10          |      | VCCHS+0.3 |           | 500ns pulse max                            |

| Gate low side voltage                        | V <sub>GLx</sub>                    | -8           |      | VCCLS+0.3 | V         | DC voltage                                 |

|                                              |                                     | -10          |      | VCCLS+0.3 |           | 500ns pulse max                            |

| Gate to Source high                          | V <sub>GHx</sub> - V <sub>SHx</sub> | -0.3         |      | 16        | V         | DC, T <sub>j</sub> = 25 °C                 |

| side voltage                                 |                                     | -2           |      | 16        |           | 500ns pulse max, T <sub>j</sub> = 2<br>°C  |

| Gate to Source low                           | V <sub>GLx</sub> - V <sub>SLx</sub> | -0.3         |      | 16        | V         | DC, T <sub>j</sub> = 25 °C                 |

| side voltage                                 |                                     | -2           |      | 16        |           | 500ns pulse max, T <sub>j</sub> = 25<br>°C |

#### Table 3Absolute maximum ratings

#### Datasheet

#### **General Product Characteristics**

| Deverseter                                      | Currential                                                                       |      | Valı | ies           | 11     | Constitutions                     |

|-------------------------------------------------|----------------------------------------------------------------------------------|------|------|---------------|--------|-----------------------------------|

| Parameter                                       | Symbol                                                                           | Min  | Тур  | Мах           | — Unit | Condition                         |

| Shunt amplifier<br>negative input<br>voltage    | V <sub>CSN</sub>                                                                 | -0.3 |      | DVDD+0.3      |        |                                   |

| Flying capacitor 1<br>voltage                   | V <sub>CP1H</sub> - V <sub>CP1L</sub> ,                                          | -0.3 |      | 9             | V      |                                   |

| CP1L pin voltage                                | V <sub>CP1L</sub> ,                                                              | -0.3 |      | 9             | V      |                                   |

| CP1H pin voltage                                | V <sub>CP1H</sub> ,                                                              | -0.3 |      | 20            | V      |                                   |

| Flying capacitor 2<br>voltage                   | V <sub>CP2H</sub> - V <sub>CP2L</sub>                                            | -0.3 |      | 70            | V      |                                   |

| CP2L pin voltage                                | V <sub>CP2L</sub>                                                                | -0.3 |      | 20            | V      |                                   |

| CP2H pin voltage                                | V <sub>CP2H</sub>                                                                | -0.3 |      | 90            | V      |                                   |

| Buck converter<br>output voltage                | VDDB                                                                             | -0.3 |      | 9             | V      |                                   |

| Dhace voltage                                   | N                                                                                | -0.3 |      | 70            | V      | DC condition                      |

| Phase voltage                                   | V <sub>PH</sub>                                                                  | -5   |      | - 70          | V      | Less than 20 ns pulse             |

| DVDD regulator<br>output voltage                | DVDD                                                                             | -0.3 |      | 6             | V      |                                   |

| Input/Output pin<br>voltage                     | VINHX, VINLX,<br>VnFAULT, VSCLK,<br>VnSCS, VSDI, VSDO,<br>VCSOX, VREF            | -0.3 |      | DVDD<br>+ 0.3 | V      |                                   |

| Maximum current for digital pins                | I <sub>DIG_IN_MAX</sub>                                                          | -1   |      | 1             | mA     |                                   |

| Analog input pin<br>voltage                     | V <sub>EN_DRV</sub> ,<br>V <sub>VSENSE/nbrake</sub> ,<br>V <sub>CS_GAIN/AZ</sub> | -0.3 |      | 7             | V      | Analog or analog and digital pins |

| Maximum current for analog inputs               | I <sub>an_in_max</sub>                                                           | -1   |      | 10            | mA     |                                   |

| Maximum sink<br>current for open-<br>drain pins | Iod_sink_max                                                                     |      |      | 7             | mA     |                                   |

| VREF pin sink current                           | I <sub>REF_SINK</sub>                                                            | -50  |      | 50            | μA     |                                   |

| Junction<br>temperature                         | TJ                                                                               | -40  |      | 150           | °C     |                                   |

| Storage temperature                             | Ts                                                                               | -55  |      | 150           | °C     |                                   |

| Case temperature                                | T <sub>CASE</sub>                                                                |      |      | 145           | °C     |                                   |

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. These are stress ratings only which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions.

Note: Absolute Maximum Ratings are not subject to production test, specified by design.

Datasheet

**General Product Characteristics**

## 2.2 **Recommended Operating Conditions**

Operating at  $T_A = 25$  °C. All voltages are referred to ground (PGND for buck converter, charge pumps and gate driver related parameters and DGND for the rest), positive currents are flowing into the pin (unless otherwise specified).

| Deverseter                                          | Course la sel                                                                                                                                |            | Values | 5          |       |                                                                  |  |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------------|-------|------------------------------------------------------------------|--|

| Parameter                                           | Symbol                                                                                                                                       | Min        | Тур    | Мах        | Unit  | Condition                                                        |  |

| Supply voltage                                      | PVDD                                                                                                                                         | 5.5        |        | 60         | V     |                                                                  |  |

|                                                     | 6.0                                                                                                                                          |            |        | 2          | Maria | During start-up                                                  |  |

| Supply voltage slew rate                            | SR <sub>PVDD</sub>                                                                                                                           |            |        | 0.25       | V/µs  | During active mode                                               |  |

| CE pin voltage range                                | V <sub>CE</sub>                                                                                                                              | 0          |        | 6          | V     |                                                                  |  |

| External supply voltage<br>regulator output voltage | DVDD                                                                                                                                         | 3.3        |        | 5.5        | v     | Configurable via VSENSE pin<br>or SPI (OTP write)                |  |

| Buck phase voltage                                  |                                                                                                                                              | -0.3       |        | <u> </u>   | N     | DC condition                                                     |  |

| continuous                                          | V <sub>PH</sub>                                                                                                                              | -5         |        | 60         | V     | Less than 20 ns pulse                                            |  |

| Inverter phase voltage                              | V <sub>SHx</sub>                                                                                                                             | -8         |        | 60         |       |                                                                  |  |

| High side gate driver<br>supply voltage             | VCCHS                                                                                                                                        | -0.3       |        | 75         | V     |                                                                  |  |

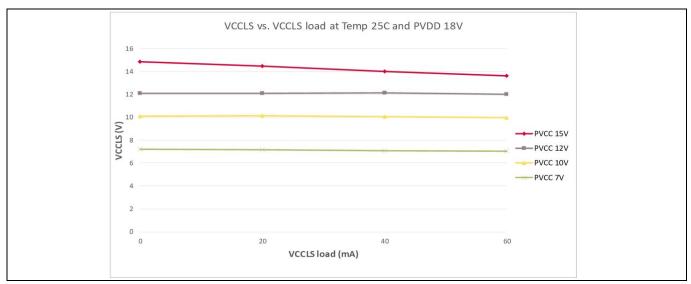

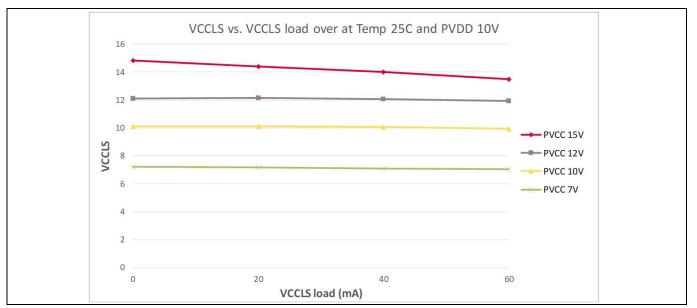

| Gate driver supply<br>voltage (PVCC)                | VCCLS,<br>VCCHS-PVDD                                                                                                                         | 7          |        | 15         | V     | Programmable via SPI. This value is equal to PVCC                |  |

| Gate driver maximum<br>operating frequency          | f <sub>PWM_GD</sub>                                                                                                                          |            |        | 200        | kHz   |                                                                  |  |

| Digital pin I/O voltage<br>range                    | Vinhx, Vinlx, Vnfault,<br>V <sub>CS_GAIN/AZ</sub> Ven_drv,<br>V <sub>SCLK</sub> , V <sub>nSCS</sub> , V <sub>SDI</sub> ,<br>V <sub>SDO</sub> | -0.3       |        | DVDD       | v     | When CS_GAIN/AZ pin works as digital input                       |  |

| Open-drain pins low<br>voltage                      | V <sub>od_lv</sub>                                                                                                                           |            |        | 0.5        | v     | When sinking 5 mA, DVDD = 3.3 V                                  |  |

| Shunt amplifier input<br>voltage range              | V <sub>SLX</sub> , V <sub>CSNx</sub>                                                                                                         | -0.3       |        | 0.3        | v     | Sense amplifier configured for shunt resistor sensing            |  |

| Analog pins voltage<br>range                        | V <sub>CSOx</sub> ,<br>V <sub>VSENSE/nBRAKE</sub> ,<br>V <sub>CS_GAIN/AZ</sub>                                                               | 0          |        | DVDD       | v     | When CS_GAIN/AZ and<br>VSENSE/nBRAKE pins work as<br>analog pins |  |

| VREF input voltage<br>range                         | V <sub>REF</sub>                                                                                                                             | DVDD/<br>4 |        | DVDD<br>/2 |       | VREF is configured as input                                      |  |

| Junction temperature range                          | TJ                                                                                                                                           | -40        |        | 125        | °C    |                                                                  |  |

#### Table 4 Recommended operating conditions

Datasheet

General Product Characteristics

# infineon

## 2.3 ESD Robustness

ESD robustness related data is listed in Table 5.

### Table 5ESD robustness data1)

| Deveneter                       | Symbol                      |     | Values |      | Unit | Condition                              |

|---------------------------------|-----------------------------|-----|--------|------|------|----------------------------------------|

| Parameter                       | Symbol                      | Min | Тур    | Мах  | Unit | Condition                              |

| ESD robustness all<br>pins      | V <sub>esd_hbm</sub>        |     |        | 2000 | V    | HBM <sup>2)</sup>                      |

| ESD robustness all pins         | V <sub>esd_cdm</sub>        |     |        | 500  | V    | CDM <sup>3)</sup>                      |

| ESD robustness<br>(corner pins) | V <sub>esd_cdm_corner</sub> |     |        | 750  | V    | CDM <sup>3)</sup> for corner pins only |

1) Not subject to production test, specified by design

2) ESD robustness, Human Body Model (HBM) according to ANSI/ESDA/JEDEC JS001 (1.5kΩ, 100 pF)

3) ESD robustness, Charge Device Model (CDM) according to ANSI/ESDA/JEDEC JS-002

## 2.4 Thermal Resistance

*Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go* to <u>www.jedec.org</u>.

## Table 6Thermal resistance parameters

| Parameter                                          | Symbol               |                    | Values |     | Unit | Condition                                                          |  |

|----------------------------------------------------|----------------------|--------------------|--------|-----|------|--------------------------------------------------------------------|--|

| Parameter                                          | Symbol               | Symbol Min Typ Max |        | Мах | Unit | Condition                                                          |  |

| Junction-to-ambient thermal resistance             | R <sub>θJA</sub>     |                    | 41.2   |     | °C/W | Ta = 25 °C, FR4 PCB, size:<br>60.0 × 40.0 × 1.5 mm³, stack<br>2S2P |  |

| Junction-to-case (top)<br>thermal resistance       | $R_{\theta JC(top)}$ |                    | 25.55  |     | °C/W | Ta = 25 °C                                                         |  |

| Junction-to-case<br>(bottom) thermal<br>resistance | $R_{\theta JC(bot)}$ |                    | 6.73   |     | °C/W | Ta = 25 °C                                                         |  |

## 2.5 Electrical Characteristics

PVDD = 5.5 to 60 V,  $T_A = 25^{\circ}C$ , unless specified under test condition. All voltages are referred to ground (PGND for buck converter, charge pumps and gate driver related parameters and DGND for the rest), positive currents are flowing into the pin (unless otherwise specified).

Table 7Electrical characteristics

| Parameter                     | Symbol        |     | Values |     |      | Condition                                                                                                                      |  |  |

|-------------------------------|---------------|-----|--------|-----|------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

|                               | Symbol        | Min | Тур    | Мах | Unit | Condition                                                                                                                      |  |  |

| Main Power Supply (PVDD)      |               |     |        |     |      |                                                                                                                                |  |  |

| Supply voltage                | PVDD          | 5.5 |        | 60  | V    |                                                                                                                                |  |  |

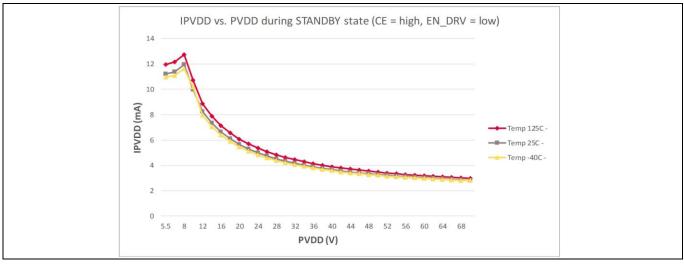

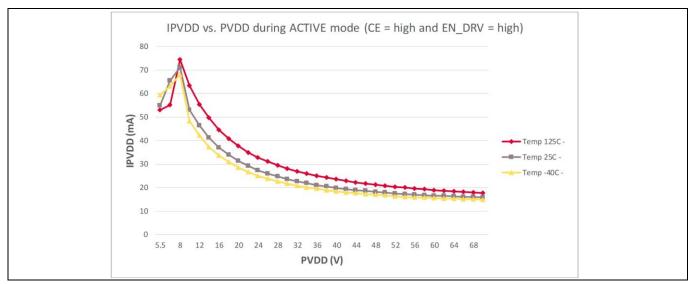

| PVDD current, active mode     | IPVDD_ACTIVE  | 20  |        | 50  | mA   | V <sub>EN_DRV</sub> > V <sub>EN_DRV_TH</sub> , V <sub>CE</sub> > V <sub>CE_TH_R</sub> , PVDD<br>= 40V, typical application run |  |  |

| PVDD current,<br>standby mode | IPVDD_STANDBY | 3   |        | 8   | mA   | $V_{EN_DRV} < V_{EN_DRV_TH}, V_{CE} > V_{CE_TH_R}, PVDD$<br>= 40V                                                              |  |  |

#### Datasheet

|                                                                 |                                 |      | Values |                |      |                                                                                                      |

|-----------------------------------------------------------------|---------------------------------|------|--------|----------------|------|------------------------------------------------------------------------------------------------------|

| Parameter                                                       | Symbol                          | Min  | Тур    | Мах            | Unit | Condition                                                                                            |

| PVDD current, OFF<br>mode                                       | I <sub>PVDD_OFF</sub>           | 25   |        | 40             | μA   | $V_{EN_{DRV}} < V_{EN_{DRV_{TH}}}, V_{CE} < V_{CE_{TH_{R}}}, PVDD = 40V$                             |

|                                                                 |                                 |      | Gate   | Driver         |      |                                                                                                      |

| Low side gate driver<br>supply voltage target                   | VCCLS                           | 7    |        | 15             | v    | Generated from charge pump. Gate<br>driver supply voltage programmable<br>via SPI                    |

| High side gate driver supply voltage target                     | VCCHS                           | 10.8 |        | 74.3           | v    | Generated from charge pump. Gate<br>driver supply voltage programmable<br>via SPI according to VCCLS |

| High side gate driver<br>output                                 | $V_{\text{GHx-}}V_{\text{SHx}}$ |      |        | VCCLS<br>- 0.7 | V    | More details in section 2.6                                                                          |

| Low side gate driver<br>output                                  | $V_{GLx}$ - $V_{SLx}$           |      |        | VCCLS          | v    | More details in section 2.6                                                                          |

| Peak source current<br>(high side and low<br>side drivers)      | I <sub>GD_SRC_PEAK</sub>        |      | 1.5    |                | A    | Current flowing from pin. Gate driver current programmable via SPI                                   |

| Peak sink current<br>(high side and low<br>side drivers)        | I <sub>GD_SNK_</sub> peak       |      | 1.5    |                | A    | Current into the pin. Gate driver<br>current programmable via SPI                                    |

|                                                                 | I <sub>HOLD</sub>               |      | 250    |                |      | Low side gate driver                                                                                 |

| Hold gate current <sup>1)</sup>                                 |                                 |      | 50     |                | mA   | High side gate driver                                                                                |

| Source and sink current accuracy                                | I <sub>GD_ACCURACY</sub>        | -20  |        | 20             | %    |                                                                                                      |

| Charge pump clock<br>frequency                                  | f <sub>cp_clk</sub>             | 190  |        | 1600           | kHz  | Programmable via SPI                                                                                 |

| Charge pump clock<br>accuracy                                   | f <sub>cp_clk_acc</sub>         | -5   |        | 5              | %    |                                                                                                      |

| Charge pump clock<br>frequency spread<br>spectrum <sup>1)</sup> | f <sub>cp_clk_ss</sub>          | 0    |        | 30             | %    |                                                                                                      |

| High side gate driver                                           |                                 |      |        | 60             |      | PVDD ≥ 9.5 V operation                                                                               |

| average current                                                 | I <sub>GD_VCCHS</sub>           |      |        | 30             | mA   | PVDD < 9.5 V operation                                                                               |

|                                                                 |                                 |      |        | 60             |      | PVDD ≥ 9.5 V operation                                                                               |

| Low side gate driver<br>average current                         | I <sub>GD_VCCLS</sub>           |      |        | 30             | mA   | PVDD < 9.5 V operation                                                                               |

#### Datasheet

| Parameter                                                         | Symbol                                         |      | Values |     | Unit | Condition                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------|------------------------------------------------|------|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                         | Symbol                                         | Min  | Тур    | Мах | Unit | Condition                                                                                                                                                                                                                                                        |

| Charge pump ramp                                                  |                                                |      |        | 250 | μs   | $\begin{split} & C_{CPx} = 220 \text{ nF, } C_{VCCLS} = 1 \ \mu\text{F, } I_{LOAD} < \!\!50 \ \mu\text{A,} \\ & PVCC = 12 \ V. \ PVDD \geq 10 \ V. \ Depends \\ & on \ capacitance \ values \ and \ features \\ & like \ charge \ pump \ pre-charge \end{split}$ |

| up time <sup>1)</sup>                                             | t <sub>CP_START</sub>                          |      |        | 1   | ms   | C <sub>CPx</sub> = 220 nF, C <sub>VCCLS</sub> =1 μF, I <sub>LOAD</sub> <50 μA,<br>PVCC = 12 V. PVDD < 10 V. Depends<br>on capacitance values and features<br>like charge pump pre-charge                                                                         |

| Gate driver PWM<br>frequency                                      | f <sub>pwm_gd</sub>                            |      |        | 200 | kHz  |                                                                                                                                                                                                                                                                  |

| Input pin pulse width                                             | t <sub>INx_PW</sub>                            | 80   |        |     | ns   | Applies to INHx and INLx pins. Pre-<br>charge current disabled, current<br>setting to 1.5A                                                                                                                                                                       |

| Dead-time <sup>1)</sup>                                           | t <sub>DT_RISE</sub> ,<br>t <sub>DT_FALL</sub> | 120  |        |     | ns   | This is the minimum dead time value<br>possible. If input signals have dead<br>time lower than this, this value<br>applies otherwise input PWM signal<br>dead time is used. Value is<br>programmable via SPI.                                                    |

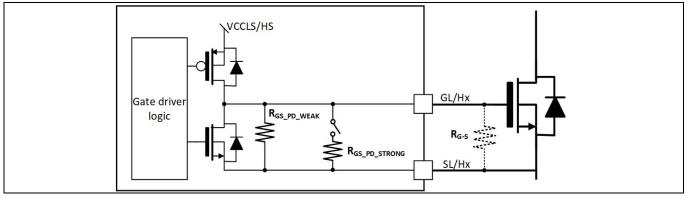

| Gate to Source<br>passive weak pull-<br>down resistor             | R <sub>gs_pd_weak</sub>                        | 70   | 100    | 130 | kΩ   | Always active                                                                                                                                                                                                                                                    |

| Gate to Source active<br>strong pull-down<br>resistor             | R <sub>gs_pd_strong</sub>                      | 0.25 | 1      | 2   | kΩ   | Pull-down resistor enabled when<br>EN_DRV or PVDD are off and V <sub>Gxy</sub> – V <sub>Sxy</sub><br>≥ 2 V. Both high side and low side<br>drivers                                                                                                               |

| Propagation delay<br>INHx to GHx                                  | t <sub>prop_hs</sub>                           | 140  |        | 200 | ns   | Dead time not considered                                                                                                                                                                                                                                         |

| Propagation delay<br>INLx to GLx                                  | t <sub>PROP_LS</sub>                           | 140  |        | 200 | ns   | Dead time not considered                                                                                                                                                                                                                                         |

| Propagation delay<br>matching high-low<br>side <sup>1)</sup>      | tprop_match_hl                                 | 0    | 25     |     | ns   |                                                                                                                                                                                                                                                                  |

| Channel-to-channel<br>propagation delay<br>matching <sup>1)</sup> | t <sub>prop_match_ch</sub>                     | 0    |        | 10  | ns   |                                                                                                                                                                                                                                                                  |

| Channel-to-channel dead time matching <sup>1)</sup>               | t <sub>dt_match_ch</sub>                       | 0    |        | 10  | ns   |                                                                                                                                                                                                                                                                  |

| Gate to source<br>comparator<br>threshold                         | V <sub>gs_cpm_th</sub>                         |      | 250    |     | mV   | Threshold voltage referred to:<br>For pull down GHx - SHx (resp. GLx-<br>SLx for low side driver).<br>For pull up VCCHS - GHx (resp. VCCLS<br>- GLx for low side driver)                                                                                         |

#### Datasheet

| Parameter                                                       | Symbol                 |       | Values    |          | Unit   | Condition                                                                                                                                                                                                           |

|-----------------------------------------------------------------|------------------------|-------|-----------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                       | Symbol                 | Min   | Тур       | Мах      | Unit   | Condition                                                                                                                                                                                                           |

| Gate to source<br>comparator deglitch<br>time <sup>1)</sup>     | tvgs_смр_deglit<br>сн  |       | 500       |          | ns     |                                                                                                                                                                                                                     |

|                                                                 |                        | Synch | ironous l | Buck Con | verter |                                                                                                                                                                                                                     |

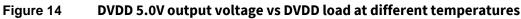

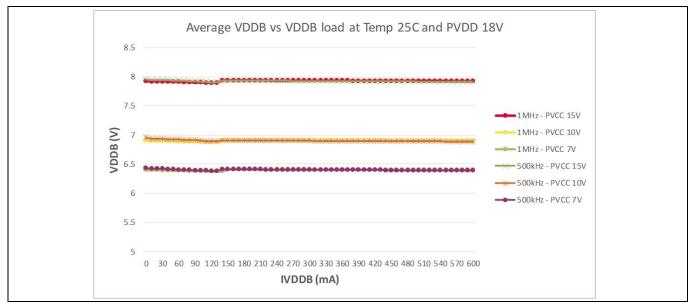

|                                                                 |                        |       | 6.5       |          |        | PVCC_SETPT=b'11, PVDD $\ge 8 \text{ V}, \text{ I}_{\text{VDDB}} = 0 \text{ A}$                                                                                                                                      |

| Buck converter<br>output target voltage                         | VDDB <sub>NOM</sub>    |       | 7.0       |          | v      | PVCC_SETPT=b'10, PVDD ≥ 8.5 V, $I_{VDDB}$ = 0 A                                                                                                                                                                     |

|                                                                 |                        |       | 8.0       |          |        | PVCC_SETPT=b'0x, PVDD ≥ 9.5 V, $I_{VDDB}$<br>= 0 A                                                                                                                                                                  |

|                                                                 |                        | 4.6   |           | 6.5      |        | PVCC_SETPT=b'11,<br>5.5 V $\leq$ PVDD < 8 V<br>Buck with fixed duty cycle. VDDB<br>dependent on I <sub>VDDB</sub> . Min value<br>defined at I <sub>VDDB</sub> = 200mA condition                                     |

| Buck regulator<br>output voltage at low<br>input voltage (PVDD) | VDDB <sub>NOM_LV</sub> | 4.6   |           | 7.0      | V      | PVCC_SETPT=b'10,<br>5.5 V $\leq$ PVDD < 8.5 V<br>Buck with fixed duty cycle. VDDB<br>depends on I <sub>VDDB</sub> . Min value defined at<br>I <sub>VDDB</sub> = 200mA                                               |

|                                                                 |                        | 4.6   |           | 8.0      |        | PVCC_SETPT=b'0x,<br>$5.5 V \le PVDD < 9.5 V$<br>Buck with fixed duty cycle. VDDB<br>depends on I <sub>VDDB</sub> . Min value defined at<br>I <sub>VDDB</sub> = 200mA                                                |

| Buck converter<br>output voltage load                           |                        | -10   |           | 9        | %      | $PVDD > VDDB_{NOM} + 2.5 V, I_{VDDB}$<br>transient from 60 mA to 540 mA (10%<br>to 90% load transient), C_{VDDB} = 47 \mu F,<br>L = 22 \mu H, f_{BUCK_SW} = 500 kHz                                                 |

| regulation <sup>1)</sup>                                        |                        | -9.5  |           | 5        | %      | $\begin{array}{l} PVDD > VDDB_{NOM} + 2.5 \ V, \ I_{VDDB} \\ \text{transient from 60 mA to 540 mA (10\% to 90\% load transient), } C_{VDDB} = 47 \mu F, L \\ = 10 \ \mu H, \ f_{BUCK\_SW} = 1000 \ kHz \end{array}$ |

| Buck converter<br>maximum average<br>current                    |                        |       |           | 600      | mA     | PVDD ≥ 9.5 V. VDDB supplies charge<br>pumps, DVDD linear regulator and<br>VDDB pin                                                                                                                                  |

|                                                                 | I <sub>VDDB_MAX</sub>  |       |           | 200      | mA     | PVDD at low input voltage range<br>(VDDB <sub>NOM_LV</sub> ). VDDB supplies charge<br>pumps, DVDD linear regulator and<br>VDDB pin                                                                                  |

| Buck converter<br>maximum duty cycle                            | DC <sub>BUCK_MAX</sub> |       | 95        |          | %      |                                                                                                                                                                                                                     |

#### Datasheet

|                                                      |                                 |      | Values   |           |      |                                                                                                                                                                                                                                                 |

|------------------------------------------------------|---------------------------------|------|----------|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                            | Symbol                          | Min  | Тур      | Мах       | Unit | Condition                                                                                                                                                                                                                                       |

| Buck converter high<br>side switch R <sub>DSON</sub> | R <sub>dson_buck_hs</sub>       | 0.7  | 1.4      | 2.2       | Ω    |                                                                                                                                                                                                                                                 |

| Buck converter low side switch R <sub>DSON</sub>     | Rdson_buck_ls                   | 0.3  | 0.45     | 1.0       | Ω    |                                                                                                                                                                                                                                                 |

| Buck switching                                       | ſ                               | 450  | 500      | 590       |      | Configurable via OTP write. May vary                                                                                                                                                                                                            |

| frequency                                            | f <sub>buck_sw</sub>            | 850  | 1000     | 1150      | kHz  | during load steps.                                                                                                                                                                                                                              |

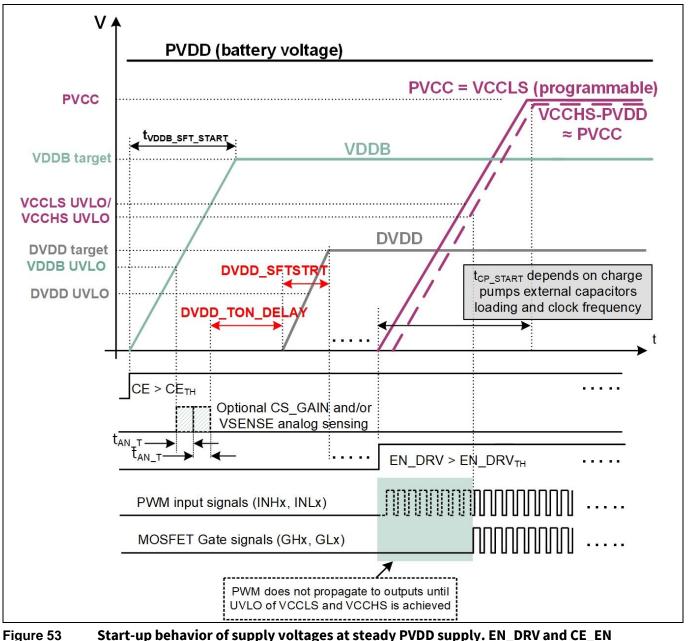

| Buck converter soft<br>start timing                  | t <sub>vddb_sft_start</sub>     |      |          | 1500      | μs   | Actual value depends on buck<br>output filter                                                                                                                                                                                                   |

|                                                      |                                 | Lir  | near Reg | ulator DV | 'DD  |                                                                                                                                                                                                                                                 |

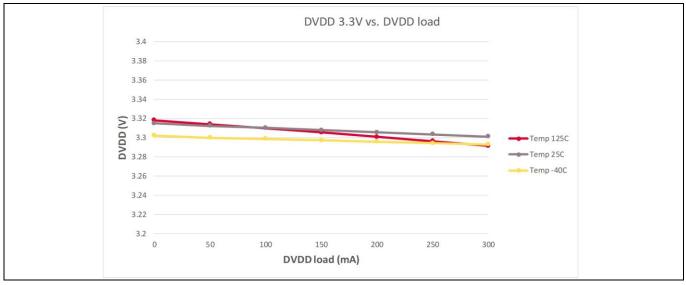

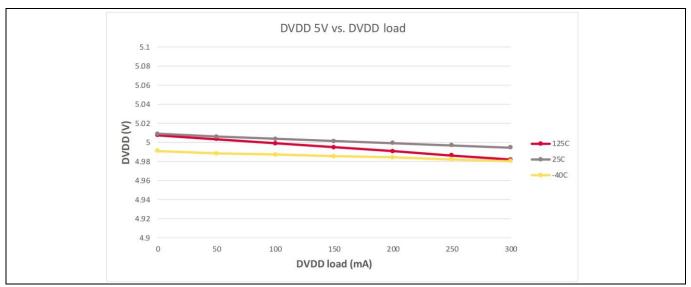

| Regulator target                                     |                                 |      | 3.3      |           |      | Programmable via SPI or external<br>pull down resistor on VSENSE pin:<br>R<=3.3 kΩ→DVDD=3.3 V                                                                                                                                                   |

| output voltage                                       | DVDD                            |      | 5        |           | V    | Programmable via SPI or external<br>pull down resistor on VSENSE pin:<br>R>=10 kΩ→DVDD=5.0 V                                                                                                                                                    |

| Output voltage<br>accuracy                           | DVDD <sub>ACC</sub>             | -2.5 |          | 2.5       | %    |                                                                                                                                                                                                                                                 |

| Load current                                         | I <sub>DVDD</sub>               |      |          | 300       | mA   |                                                                                                                                                                                                                                                 |

| Static line regulation                               |                                 |      |          | 10        | mV   | VDDB=6.5 V8 V, I <sub>DVDD</sub> =300 mA                                                                                                                                                                                                        |

| Static load regulation                               |                                 |      |          | 40        | mV   | VDDB=DVDD+1.5 V, $I_{DVDD} = 1 \text{ mA to}$<br>300 mA step                                                                                                                                                                                    |

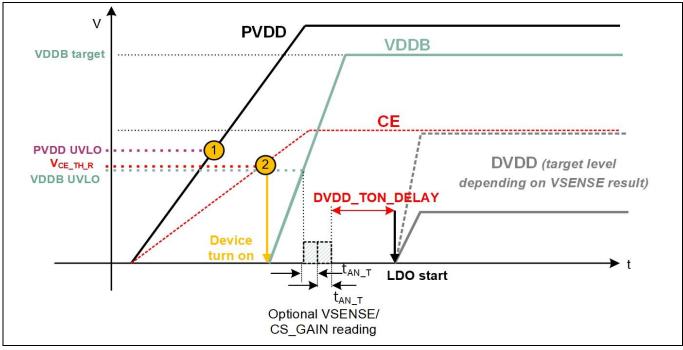

| Analog programming<br>pins period                    | t <sub>AN_T</sub>               |      | 25       |           | μs   | Each VSENSE and/or CS_GAIN                                                                                                                                                                                                                      |

| DVDD turn on delay                                   | tdvdd_ton_dly                   | 200  |          | 800       | μs   | Programmable via SPI. Delay<br>between VDDB UVLO until DVDD<br>ramp up start                                                                                                                                                                    |

| DVDD soft start<br>timing                            | t <sub>dvdd_sft_</sub><br>start | 100  |          | 1600      | μs   | Configurable via SPI- Current<br>limited by $I_{DVDD_1\_LIM}$ . If due to larger<br>$C_{DVDD}$ values, programmed timing<br>is not achievable, start-up time is<br>defined by $t_{DVDD\_SFT\_START} = \frac{C_{DVDD} * DVDD}{I_{DVDD\_1\_LIM}}$ |

#### Datasheet

| infineon |

|----------|

|----------|

| Parameter                                                                | Sumbol                      |              | Values    |              | Unit      | Condition                                                                                                               |

|--------------------------------------------------------------------------|-----------------------------|--------------|-----------|--------------|-----------|-------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                | Symbol                      | Min          | Тур       | Мах          | Unit      | Condition                                                                                                               |

|                                                                          |                             | Cu           | rrent Sei | nse Ampli    | ifier     |                                                                                                                         |

| Closed loop gain                                                         | G <sub>cs</sub>             | 4            |           | 64           | V/V       | Configured either via external resistor or SPI                                                                          |

| Gain error <sup>1)</sup>                                                 | G <sub>CS_ERROR</sub>       | -1           |           | 1            | %         | Measured at SLx-CSNx=0.025 V                                                                                            |

| Offset input referred <sup>1)</sup>                                      | V <sub>cs_os</sub>          |              | 200       | 600          | μV        | Gain=32, inputs shorted                                                                                                 |

| Offset temperature<br>drift <sup>1)</sup>                                | ΔV <sub>cs_os</sub> /<br>ΔT |              | 5         |              | μV/<br>°C |                                                                                                                         |

| Current sense<br>blanking time                                           | t <sub>cs_blank</sub>       | 0            |           | 8            | μs        | Programmable via SPI                                                                                                    |

| Amplifier output                                                         |                             |              | 600       |              |           | Time from input signal step to 1%<br>of final output voltage. Input<br>voltage step of 0.2 V. Gain 4 to 24              |