**IR1152S**

# FIXED 66kHz FREQUENCY, µPFC ONE CYCLE CONTROL PFC IC WITH BROWN-OUT PROTECTION

#### **Features**

- PFC IC with IR proprietary "One Cycle Control"

- Continuous conduction mode boost type PFC

- Fixed 66kHz switching frequency

- Average current mode control

- Input line sensed brownout protection

- Output overvoltage protection

- Open loop protection

- · Cycle by cycle peak current limit

- VCC under voltage lockout

- Programmable soft start

- Micropower startup

- User initiated micropower "Sleep Mode"

- 750mA peak gate drive

- Latch immunity and ESD protection

### Description

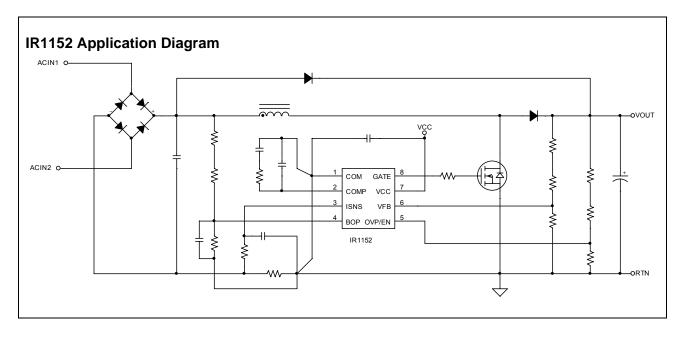

μPFC IR1152 power factor correction IC, based on IR proprietary "One Cycle Control" (OCC) technique, provides for high PF and excellent DC Bus regulation while enabling drastic reduction in component count, PCB area and design time as compared to traditional solutions. The IC is designed to operate in 85-264VAC universal input, continuous conduction mode Boost PFC at fixed 66kHz switching frequency. IR1152 features include input-line sensed brown-out protection, overvoltage protection, cycle by cycle peak current limit, open loop protection,  $V_{CC}$  UVLO, soft-start and micropower startup current of less than 75μA. In addition, for standby power requirements, the IC can be driven into a micropower sleep mode by pulling the OVP/EN pin low where the current consumption is less than 75μA. The IR1152 is available in SO-8 packages.

#### Package

# **Qualification Information**

| Qualification Level        |                        | Industrial                                                                                                                                                          |  |  |  |  |  |  |  |

|----------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                            |                        | Comments: This family of ICs has passed JEDEC's Industrial qualification. IR's Consumer qualification level is granted by extension of the higher Industrial level. |  |  |  |  |  |  |  |

| Moisture Sensitivity Level |                        | MSL2 260°C                                                                                                                                                          |  |  |  |  |  |  |  |

|                            |                        | (per IPC/JEDEC J-STD-020)                                                                                                                                           |  |  |  |  |  |  |  |

|                            | Machine Madel          | Class A                                                                                                                                                             |  |  |  |  |  |  |  |

| ESD                        | Machine Model          | (per JEDEC standard JESD22-A115)                                                                                                                                    |  |  |  |  |  |  |  |

| LSD                        | Llaura au Darde Mardal | Class 1A                                                                                                                                                            |  |  |  |  |  |  |  |

|                            | Human Body Model       | (per EIA/JEDEC standard EIA/JESD22-A114)                                                                                                                            |  |  |  |  |  |  |  |

| 10111                      |                        | Class I, Level A                                                                                                                                                    |  |  |  |  |  |  |  |

| IC Latch-Up Test           |                        | (per JESD78)                                                                                                                                                        |  |  |  |  |  |  |  |

| RoHS Compliant             |                        | Yes                                                                                                                                                                 |  |  |  |  |  |  |  |

# **Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. All voltages are absolute voltages referenced to COM. Thermal resistance and power dissipation are measured under board mounted and still air conditions.

| Parameters                           | Symbol            | Min. | Max. | Units | Remarks                |

|--------------------------------------|-------------------|------|------|-------|------------------------|

| V <sub>CC</sub> Voltage              | $V_{CC}$          | -0.3 | 20   | V     | Not internally clamped |

| ISNS voltage                         | $V_{ISNS}$        | -10  | 0.3  | V     |                        |

| ISNS Current                         | I <sub>ISNS</sub> | -2   | 2    | mA    |                        |

| V <sub>FB</sub> voltage              | $V_{FB}$          | -0.3 | 6.5  | V     |                        |

| V <sub>OVP</sub> voltage             | $V_{OVP}$         | -0.3 | 6.5  | V     |                        |

| V <sub>BOP</sub> voltage             | $V_{BOP}$         | -0.3 | 9    | V     |                        |

| COMP voltage                         | $V_{COMP}$        | -0.3 | 6.5  | V     |                        |

| Gate Voltage                         | $V_{GATE}$        | -0.3 | 18   | V     |                        |

| Junction Temperature Operating Range | T <sub>J</sub>    | -40  | 150  | °C    |                        |

| Storage Temperature                  | Ts                | -55  | 150  | °C    |                        |

| Thermal Resistance                   | $R_{\theta JA}$   |      | 128  | °C/W  |                        |

| Package Power Dissipation            | $P_D$             |      | 976  | mW    | T <sub>AMB</sub> =25°C |

#### **Electrical Characteristics**

The electrical characteristics involve the spread of values guaranteed within the specified supply voltage and junction temperature range  $T_J$  from  $-25^{\circ}$  C to  $125^{\circ}$ C. Typical values represent the median values, which are related to  $25^{\circ}$ C. If not otherwise stated, a supply voltage of  $V_{CC}$  =15V is assumed for test condition

**Supply Section**

| Parameters                                                     | Symbol                | Min. | Тур. | Max. | Units | Remarks                                    |

|----------------------------------------------------------------|-----------------------|------|------|------|-------|--------------------------------------------|

| Supply Voltage Operating Range                                 | V <sub>CC</sub>       |      | 14   | 17   | V     |                                            |

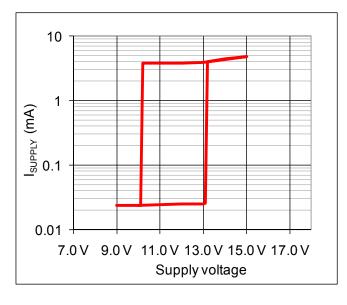

| V <sub>CC</sub> Turn On Threshold                              | V <sub>CC ON</sub>    | 12.2 | 13.1 | 14   | V     |                                            |

| V <sub>CC</sub> Turn Off Threshold<br>(Under Voltage Lock Out) | V <sub>CC UVLO</sub>  | 9.4  | 10.1 | 10.8 | V     |                                            |

| V <sub>CC</sub> Turn On/Off Hysteresis                         | V <sub>CC HYST</sub>  | 2.4  | 3    | 3.6  | V     |                                            |

|                                                                |                       |      |      | 9    | mA    | C <sub>LOAD</sub> =1nF                     |

| Operating Current                                              | I <sub>CC</sub>       |      |      | 14   | mA    | C <sub>LOAD</sub> =4.7nF                   |

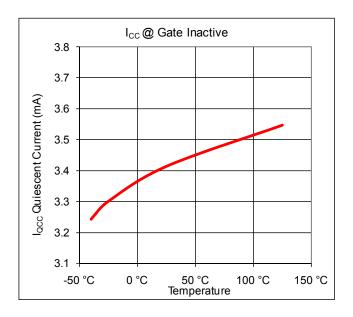

|                                                                |                       |      | 3.5  | 5    | mA    | Stand-by Mode – Inactive gate              |

| Start-up Current                                               | I <sub>CC START</sub> |      | 26   | 75   | μΑ    | V <sub>CC</sub> =V <sub>CC ON</sub> - 0.5V |

| Sleep current                                                  | I <sub>SLEEP</sub>    |      | 26   | 75   | μA    | Pin OVP/EN=0.4V                            |

| Sleep Mode Threshold                                           | $V_{SLEEP}$           | 0.55 |      | 0.8  | V     | Bias on OVP/EN pin                         |

#### **Oscillator Section**

| Parameters                 | Symbol          | Min. | Тур. | Max. | Units | Remarks                          |

|----------------------------|-----------------|------|------|------|-------|----------------------------------|

| Fixed Oscillator Frequency | f               | 58   | 66   | 72.5 |       | T <sub>AMB</sub> =25°C           |

| Tixed Oscillator Frequency | t <sub>SW</sub> | 53.8 |      | 73   | kHz   | -25°C < T <sub>AMB</sub> < 125°C |

| Maximum Duty Cycle         | $D_{MAX}$       | 93   |      | 99   | %     | V <sub>COMP</sub> =5V            |

| Minimum Duty Cycle         | $D_{MIN}$       |      |      | 0    | %     | Pulse Skipping                   |

#### **Protection Section**

| Parameters                                                       | Symbol                 | Min.  | Тур.  | Max.  | Units                 | Remarks                        |

|------------------------------------------------------------------|------------------------|-------|-------|-------|-----------------------|--------------------------------|

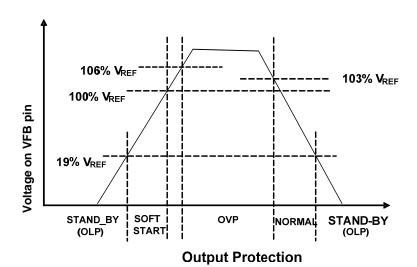

| Open Loop Protection (OLP)Threshold                              | $V_{OLP}$              | 17    | 19    | 21    | $^{ m W}_{ m REF}$    | Bias on VFB pin                |

| Output Overvoltage<br>Protection (OVP)<br>Threshold              | V <sub>OVP</sub>       | 104   | 106   | 108   | %<br>V <sub>REF</sub> | Bias on VFB and/or OVP/EN pins |

| Output Overvoltage<br>Protection Reset Threshold                 | V <sub>OVP(RST)</sub>  | 101   | 103   | 105   | %<br>V <sub>REF</sub> | Bias on VFB and/or OVP/EN pins |

| OVP Input Bias Current                                           | I <sub>OVP(Bias)</sub> |       |       | -0.2  | μA                    |                                |

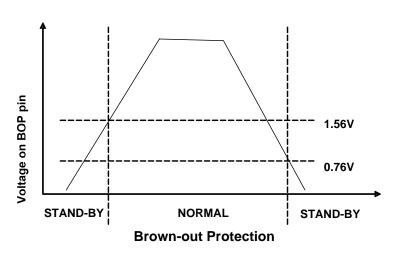

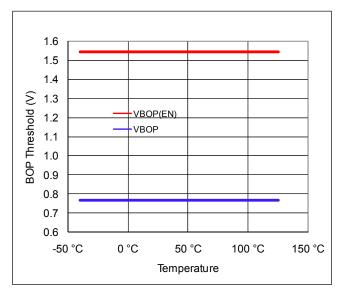

| Brown-out Protection (BOP) Threshold                             | $V_{BOP}$              | 0.68  | 0.78  | 0.88  | V                     | Bias on BOP pin                |

| Brown-out Protection<br>Enable Threshold                         | $V_{BOP(EN)}$          | 1.46  | 1.56  | 1.66  | V                     | Bias on BOP pin                |

| BOP Input Bias Current                                           | I <sub>BOP(Bias)</sub> |       |       | -0.2  | μA                    |                                |

| Peak Current Limit Protection ISNS Voltage Threshold (IPK LIMIT) | V <sub>ISNS(PK)</sub>  | -0.82 | -0.75 | -0.68 | V                     | Bias on ISNS pin               |

**Internal Voltage Reference Section**

| Parameters        | Symbol            | Min. | Тур. | Max. | Units | Remarks                          |

|-------------------|-------------------|------|------|------|-------|----------------------------------|

|                   |                   |      |      |      |       | Regulation Voltage on VFB pin,   |

| Reference Voltage | $V_{REF}$         | 4.9  | 5    | 5.1  | V     | T <sub>AMB</sub> =25°C           |

| Line Regulation   | $R_{REG}$         |      | 10   | 20   | mV    | 14V < V <sub>CC</sub> < 17V      |

| Temp Stability    | T <sub>STAB</sub> |      | 0.4  |      | %     | -25°C < T <sub>AMB</sub> < 125°C |

| Total Variation   | $\Delta V_{TOT}$  | 4.85 |      | 5.1  | V     | Line & Temperature               |

**Voltage Error Amplifier Section**

| Parameters                          | Symbol                     | Min. | Тур. | Max. | Units | Remarks                                                                |

|-------------------------------------|----------------------------|------|------|------|-------|------------------------------------------------------------------------|

| Transconductance                    | g <sub>m</sub>             | 35   | 49   | 59   | μS    |                                                                        |

| Source Current (Normal              | 1                          | 30   | 44   | 58   | μA    | T <sub>AMB</sub> =25°C                                                 |

| Mode)                               | IOVEA(SRC)                 | 17   |      | 80   | μΛ    | -25°C < T <sub>AMB</sub> < 125°C                                       |

|                                     | 1                          | -58  | -44  | -30  |       | T <sub>AMB</sub> =25°C                                                 |

| Sink Current (Normal Mode)          | IOVEA(SNK)                 | -80  |      | -17  | μA    | -25°C < T <sub>AMB</sub> < 125°C                                       |

| Soft Start Delay Time (calculated)  | t <sub>ss</sub>            |      | 60   |      | msec  | $R_{GAIN}$ =1.1k $\Omega$ , $C_{ZERO}$ =0.56 $\mu$ F, $C_{POLE}$ =10nF |

| V <sub>COMP</sub> Voltage (Fault)   | V <sub>COMP FLT</sub>      |      | 1    | 1.4  | V     | @100uA steady state                                                    |

| Effective V <sub>COMP</sub> voltage | $V_{COMP\;EFF}$            | 4.7  | 4.9  | 5.1  | V     |                                                                        |

| VFB Input Bias Current              | I <sub>FB(Bias)</sub>      |      |      | -0.2 | μΑ    | V <sub>FB</sub> =4.9V                                                  |

| Output Low Voltage                  | $V_{OL}$                   |      |      | 0.25 | V     |                                                                        |

| Output High Voltage                 | $V_{OH}$                   | 5    |      | 5.4  | V     |                                                                        |

| V <sub>COMP</sub> Start Voltage     | V <sub>COMP</sub><br>START | 260  | 375  | 485  | mV    |                                                                        |

**Current Amplifier Section**

| Parameters              | Symbol                  | Min. | Тур. | Max. | Units | Remarks                                     |

|-------------------------|-------------------------|------|------|------|-------|---------------------------------------------|

| DC Gain                 | <b>g</b> <sub>DC</sub>  | 2.65 | 3.1  | 3.55 | V/V   |                                             |

| Corner Frequency        | $f_{C}$                 |      | 5    |      | kHz   | Average Current Mode, Note 1                |

| Input Offset Voltage    | $V_{IO}$                |      | 4    | 16   | mV    | Note 1                                      |

| ISNS Input Bias Current | I <sub>ISNS(Bias)</sub> | -57  |      | -13  | μA    | V <sub>FB</sub> =0V, V <sub>ISNS</sub> =-1V |

| Blanking Time           | T <sub>BLANK</sub>      | 170  | 320  | 470  | ns    |                                             |

### **Gate Driver Section**

| Parameters            | Symbol           | Min. | Тур. | Max. | Units | Remarks                                  |

|-----------------------|------------------|------|------|------|-------|------------------------------------------|

| Gate Low Voltage      | $V_{GLO}$        |      |      | 0.8  | V     | I <sub>GATE</sub> = 200mA                |

| Gate High Voltage     | $V_{GTH}$        | 12   | 13   | 14   |       | V <sub>CC</sub> =17V, Internally Clamped |

| Gate High Voltage     | <b>∨</b> GTH     | 10   |      |      | V     | V <sub>CC</sub> =11.5V                   |

| Rise Time             | +                |      | 25   |      | ns    | C <sub>LOAD</sub> = 1nF, VCC=15V         |

| Nise Time             | t <sub>r</sub>   |      | 60   |      | ns    | $C_{LOAD} = 4.7 nF, VCC = 15V$           |

| Fall Time             | +                |      | 35   |      | ns    | C <sub>LOAD</sub> = 1nF, VCC=15V         |

| raii Tiitle           | t <sub>f</sub>   |      | 65   |      | ns    | $C_{LOAD}$ = 4.7nF, VCC=15V              |

| Output Peak Current   | I <sub>OPK</sub> | 750  |      |      | mA    | $C_{LOAD}$ = 4.7nF, VCC=15V, Note 1      |

| Gate Voltage at Fault | $V_{G fault}$    |      |      | 0.08 | V     | I <sub>GATE</sub> = 20mA                 |

Note 1: Guaranteed by design, but not tested in production

# **Lead Assignments & Definitions**

| PIN | SYMBOL | DESCRIPTION                     | IR1152                 |

|-----|--------|---------------------------------|------------------------|

| 1   | COM    | Ground                          |                        |

| 2   | COMP   | Voltage Loop Compensation       | COM 1 8 GATE           |

| 3   | ISNS   | Current sense                   | COMP 7 V <sub>CC</sub> |

| 4   | BOP    | Brown-out Fault Detect          | I <sub>SNS</sub> T3    |

| 5   | OVP/EN | Overvoltage Fault Detect/Enable | I <sub>SNS</sub> 3     |

| 6   | VFB    | Output Voltage Sense            | BOP 4 5 OVP/EN         |

| 7   | VCC    | IC Supply voltage               |                        |

| 8   | GATE   | Gate Drive Output               |                        |

#### **IR1152 General Description**

The  $\mu$ PFC IR1152 IC is intended for power factor correction in continuous conduction mode Boost PFC converters operating at fixed switching frequency with average current mode control. The IC operates based on IR's proprietary "One Cycle Control" (OCC) PFC algorithm based on the concept of resettable integrator.

#### **Theory of Operation**

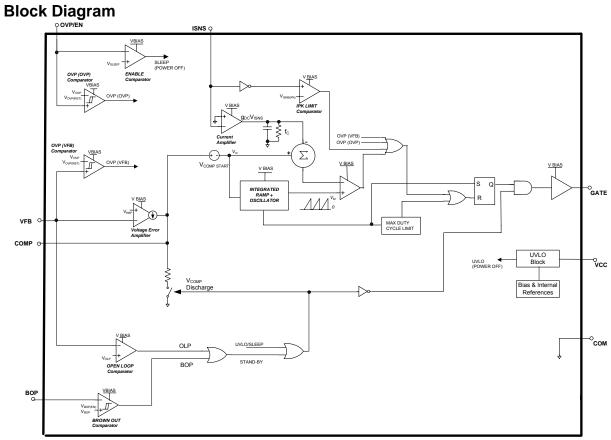

The OCC algorithm based on the resettable integrator concept works using two loops - a slow outer voltage loop and a fast inner current loop. The outer voltage loop monitors the VFB pin and generates an error signal which controls the amplitude of the input current admitted into the PFC converter. In this way, the outer voltage loop maintains output voltage regulation. The voltage loop bandwidth is kept low enough to not track the 2xf<sub>AC</sub> ripple in the output voltage and thus generates an almost DC error signal under steady state conditions. The inner current loop maintains the sinusoidal profile of the input current and thus is responsible for power factor correction. This loop exploits the fact that, in a power factor corrected system, by definition, the information about the sinusoidal variation in input voltage is inherently available in the input line current (or boost inductor current). Thus there is no need to sense the input voltage to generate a current reference. The current loop employs the boost inductor current information to generate PWM signals with a proportional sinusoidal variation. This controls the shape of the input current to be proportional to and in phase with the input voltage. Average current mode operation is envisaged by filtering the switching frequency ripple from the current sense signal using an appropriately sized on-chip RC filter. This filter also contributes to the bandwidth of the current control loop. Thus the filter bandwidth has to be high enough to track the 120Hz rectified, sinusoidal current waveform and also filter out the switching frequency ripple in the inductor current. In IR1152 this averaging function can effectively filter high ripple current ratios (as high as 40% at maximum input current) to accommodate designs with small boost inductances.

The IC determines the boost converter instantaneous duty cycle based on the resettable integrator concept. The required signals are the voltage feedback loop error signal  $V_{\rm m}$  (which is the  $V_{\rm COMP}$  pin voltage minus a DC offset of  $V_{\rm COMP,START})$  and the current sense signal  $V_{\rm ISNS}.$  The resettable integrator generates a cycle-by-cycle, saw-tooth signal called the PWM Ramp which has an amplitude  $V_{\rm m}$  and period  $1/f_{\rm SW}$  hence a slope of  $V_{\rm m}\text{-}f_{\rm SW}.$

The current sense signal is amplified by the current amplifier by a factor  $g_{DC}$  and fed into the summing node where it is subtracted from  $V_m$  to generate the summer voltage (=  $V_m - g_{DC} * V_{ISNS}$ ). The summer voltage is compared with the PWM ramp by the PWM comparator of the IC to determine the gate drive duty cycle. The instantaneous duty is mathematically given by:

$D = (V_m - g_{DC}.V_{ISNS})/V_m$

Assuming steady state conditions where the voltage feedback loop is well regulated ( $V_m$  &  $V_{OUT}$  are DC signals) & hence instantaneous duty cycle follows the boost-converter equation (D = 1 –  $V_{IN}(t)/V_{OUT}$ ), the control equation can be re-written as:

$V_m = g_{DC}.V_{ISNS}/(V_{IN}(t)/V_{OUT})$

Further, recognizing that  $V_{ISNS} = I_L(t).R_{SNS}$  and rearranging yields:

$g_{DC}.I_L(t).R_{SNS} = V_mV_{IN}(t)/V_{OUT}$

Since V<sub>m</sub>, V<sub>OUT</sub> & g<sub>DC</sub> are constant terms:

$I_{I}(t) \propto V_{IN}(t)$

Thus the inductor current follows the input voltage waveform & by definition power factor correction is achieved.

#### Feature set

Fixed Frequency Operation

The IC is programmed to operate at a fixed frequency of 66kHz (Typ). Internalization of the oscillator offers excellent noise immunity even in the noisy PFC environment while integration of the oscillator into the OCC core of the IC eliminates need for digital calibration circuits. Both these factors render the gate drive jitter free thus contributing to elimination of audible noise in PFC magnetics.

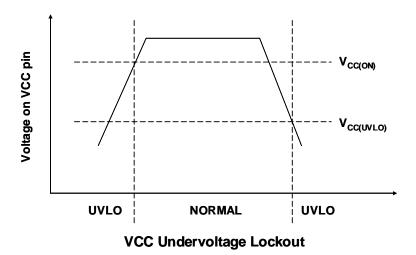

#### IC Supply Circuit & Low start-up current

The IR1152 UVLO circuit maintains the IC in UVLO mode during start-up if VCC pin voltage is less than the VCC turn-on threshold,  $V_{\text{CC,ON}}$  and current consumption is less than 75uA. Should VCC pin voltage should drop below  $V_{\text{CC,UVLO}}$  during normal operation, the IC is pushed back into UVLO mode and VCC pin has to exceed  $V_{\text{CC,ON}}$  again for normal operation. There is no internal voltage clamping of the VCC pin.

#### User initiated Micropower Sleep mode

The IC can be actively pushed into a micropower Sleep Mode where current consumption is less than 75uA by pulling OVP/EN pin below the Sleep threshold,  $V_{SLEEP}$  even while VCC is above  $V_{CC,ON}$ . This allows the user to disable PFC during application stand-by situations in order to meet stand-by regulations. Since  $V_{SLEEP}$  is less than 1V, even logic level signals can be employed.

#### **IR1152 General Description**

#### Programmable Soft Start

The soft start process controls the rate of rise of the voltage feedback loop error signal thus providing a linear increase of the RMS input current that the PFC converter will admit. The soft start time is essentially controlled by voltage error amplifier compensation components selected and is therefore user programmable to some degree based on desired voltage feedback loop crossover frequency.

#### Gate Drive Capability

The gate drive output stage of the IC is a totem pole driver with 750mA peak current drive capability. The gate drive is internally clamped at 13V (Typ). Gate drive buffer circuits can be easily driven with the GATE pin of the IC to suit any system power level.

#### System Protection Features

IR1152 protection features include Brown-out protection (BOP), Open-loop protection (OLP), Overvoltage protection (OVP), Cycle-by-cycle peak current limit (IPK LIMIT), Soft-current limit and VCC under voltage lock-out (UVLO).

- BOP is based on direct input line sensing using a resistor divider/RC filter network. If BOP pin falls below the Brown-out protection threshold  $V_{\rm BOP},$  a Brown-out situation is immediately detected and the following response is executed the gate drive pulse is disabled, VCOMP is actively discharged and IC is pushed into Stand-by Mode. The IC reenters normal operation only after BOP pin exceeds  $V_{\rm BOP(EN)}.$  During start-up the IC is held in Stand-by Mode until this pin exceeds  $V_{\rm BOP(EN)}.$

- OLP is activated whenever the VFB pin voltage falls below  $V_{\text{OLP}}$  threshold. Once open loop is detected the following response is immediately executed the gate drive is immediately disabled, VCOMP is actively discharged and the IC is pushed into Stand-by mode. There is no voltage hysteresis associated with this feature. During start-up the IC is held in Stand-by Mode until VFB exceeds  $V_{\text{OLP}}$ .

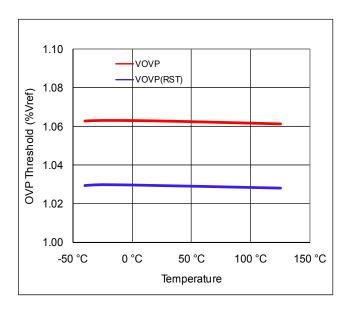

- OVP feature in IR1152 is "dual" and "dedicated". There are 2 overvoltage comparators in IR1152 marked OVP(OVP) and OVP(VFB) in the block diagram. Both these are identical in design, reference the exact same thresholds and thus identical in operation. The non-inverting input of OVP(VFB) comparator is on the VFB pin while that of the OVP(OVP) comparator is on the OVP/EN pin. When either or both of the pin voltages exceeds  $V_{OVP}$ , an overvoltage situation is detected and the gate drive is immediately terminated. The gate drive is re-enabled only after both pin voltages are below V<sub>OVP(RST)</sub>. The redundancy offered by the 2 comparators and use of a dedicated OVP/EN pin ensures the best possible system overvoltage protection against extremes of situations such as component failures, pin-to-pin shorts etc.

- Soft-current limit is an output voltage fold-back type protection feature encountered when the PFC converter input current exceeds to a point where the V<sub>m</sub> voltage saturates. As mentioned earlier, the amplitude of input current is directly proportional to  $V_m$ , the error voltage of the feedback loop.  $V_m$  is clamped to a certain maximum voltage inside the IC (given by  $V_{\text{COMP},\text{EFF}}$  parameter in datasheet). If the input current causes the V<sub>m</sub> voltage to saturate at its maximum value, then any further increase in input current will cause the duty cycle to droop which immediately forces the V<sub>OUT</sub> voltage of the PFC converter to fold-back. Since the highest current is at the peak of the AC sinusoid, the droop in duty cycle commences at the peak of the AC sinusoid when the soft-current limit is encountered. In most converters. the design of the current sense resistor is performed based on soft-current limit (i.e. V<sub>m</sub> saturation) and at the system condition which demands highest input current (minimum V<sub>AC</sub> & maximum P<sub>OUT</sub>).

- Cycle-by-cycle peak current limit protection instantaneously turns-off the gate output whenever the ISNS pin voltage exceeds  $V_{\text{ISNS(PK)}}$  threshold in magnitude. The gate drive is held in the low state as long as the overcurrent condition persists. The gate drive is re-enabled when the magnitude of ISNS pin voltage falls below the  $V_{\text{ISNS(PK)}}$  threshold. This protection feature incorporates a leading edge blanking circuit to improve noise immunity.

#### **IR1152 Pin Description**

**Pin COM:** This is ground potential pin of the IC. All internal devices are referenced to this point.

Pin COMP: External circuitry from this pin to ground compensates the system voltage loop and programs the soft start time. The COMP pin is essentially the output of the voltage error amplifier. The voltage loop error signal V<sub>m</sub> used in the control algorithm is derived from  $V_{COMP}$  ( $V_m = V_{COMP}$ - $V_{\text{COMP,START}}$ ).  $V_{\text{COMP}}$  is actively discharged using an internal resistance to below V<sub>COMP.START</sub> threshold whenever the IC is pushed into Stand-by mode (BOP or OLP condition) or UVLO/Sleep mode. The gate drive output and logic functions of the IC are inactive if VCOMP is less than V<sub>COMP.START</sub>. Also during start-up, the VCOMP voltage has to be less than  $V_{\text{COMP},\text{START}}$  in order to commence operation (i.e. a pre-bias on VCOMP will not allow IC to commence operation).

Pin ISNS: ISNS pin is tied to the input of the current sense amplifier of the IC. The voltage at this pin, which provides the current sense information to the IC, has to be a negative voltage wrt the COM pin. Also since the IC is based on average current mode, the entire inductor current information is necessary. A current sense resistor, located below system ground along the return path to the bridge rectifier, is the preferred current sensing method. ISNS pin is also the inverting input to the cycle-by-cycle peak current limit comparator. Whenever  $V_{\text{ISNS}}$  exceeds  $V_{\text{ISNS}(PK)}$  threshold in magnitude, the gate drive is instantaneously disabled. Any external filtering of the ISNS pin must be performed carefully in order to ensure that the integrity of the current sense signal is maintained for cycle-by-cycle peak current limit protection.

**Pin BOP (Brown-out Protection):** This pin is used to sense the rectified AC input line voltage through a resistor divider/capacitor network which is in effect a voltage division and averaging network, representing a scaled down signal of the average rectified input voltage (average DC voltage +  $2xf_{AC}$  ripple). During start-up the BOP pin voltage has to exceed  $V_{BOP(EN)}$  in order to enable the IC to exit Stand-by mode and enter normal operation. A Brown-out situation is detected whenever the pin voltage falls below  $V_{BOP}$  and the IC is pushed into Stand-by mode. Subsequently the pin has to exceed  $V_{BOP(EN)}$  for the IC to exit Stand-by and resume normal operation.

Pin OVP/EN: The OVP/EN pin is connected to the non-inverting input of the OVP(OVP) overvoltage comparator shown in the block diagram and thus is used to detect output overvoltage situations. The output voltage information is communicated to the OVP pin using a resistive divider. This pin also serves the second purpose of an ENABLE pin. The OVP/EN pin can be used to activate the IC into "micropower sleep" mode by pulling the voltage on this pin below the VSLEEP threshold. The OVP/EN pin can be used to activate the IC into "micropower sleep" mode by pulling the voltage on this pin below the V<sub>SLEEP</sub> threshold.

Pin VFB: The converter output voltage is sensed via a resistive divider and fed into this pin. VFB pin is the inverting input of the output voltage error amplifier. The non-inverting input of this amplifier is connected to an internal 5V reference. The impedance of the divider string must be low enough that it does not introduce substantial error due to the input bias currents of the amplifier, yet high enough to minimize power dissipation. Typical value of external divider impedance will be  $2M\Omega$ . The VFB pin is also connected to the non-inverting input of the OVP(VFB) overvoltage comparator as shown in the block diagram and is used to detect output overvoltage situations. Finally, VFB pin is also the inverting input to the Open Loop comparator. The IC is held in Stand-by Mode whenever VFB pin voltage is below VOLP threshold. IC current consumption is a few mA in this mode.

**Pin VCC:** This is the supply voltage pin of the IC and sense node for the undervoltage lock out circuit. It is possible to turn off the IC by pulling this pin below the minimum turn off threshold voltage, VCC(UVLO) without damage to the IC. This pin is not internally clamped.

**Pin GATE:** This is the gate drive output of the IC. This drive voltage is internally clamped to 13V(Typ) and provides a drive current of ±0.75A peak with matched rise and fall times.

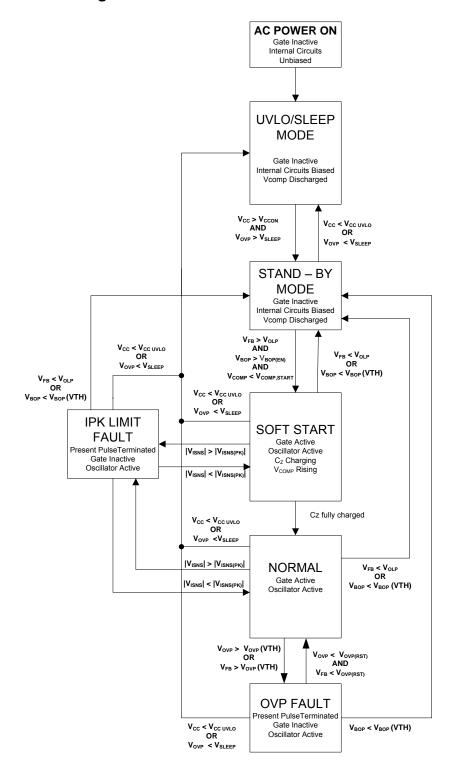

#### **IR1152 Modes of operation**

Referenced to States & Transition Diagram

UVLO/Sleep Mode: The IC is in the UVLO/Sleep mode when VCC pin voltage is below  $V_{\text{CC.ON}}$  at start-up or when VCC pin voltage drops below V<sub>CC.UVLO</sub> during normal operation or when OVP/EN pin voltage is below V<sub>SLEEP</sub>. The UVLO/Sleep mode is accessible from any other state of operation. This mode can be actively invoked by pulling the OVP/EN pin below V<sub>SLEEP</sub> even if VCC pin voltage is above V<sub>CC.ON</sub>. In the UVLO/Sleep state, the gate drive circuit is inactive, most of the internal circuitry is unbiased and the IC draws a quiescent current of I<sub>SLEEP</sub> which is less than 75uA. Also, the internal logic of the IC ensures that whenever the Sleep mode is actively invoked. the COMP pin is actively discharged below V<sub>COMP,START</sub> threshold prior to entering the sleep mode, in order to facilitate soft-start upon resumption of operation.

**Stand-by Mode:** The IC is placed in Stand-by mode whenever an Open-loop and/or a Brown-out situation is detected. A Brown-out situation is sensed when BOP pin voltage is less than  $V_{\text{BOP}(\text{EN})}$  prior to system start-up and when BOP pin voltage drops below  $V_{\text{BOP}}$  after start-up. An Open-loop situation is sensed anytime VFB pin voltage is less than  $V_{\text{OLP}}$ . All internal circuitry is biased in the Stand-by Mode, but the gate is inactive and the IC draws a few mA of current. This state is accessible from any other state of operation of the IC. COMP pin is actively discharged to below  $V_{\text{COMP,START}}$  whenever this state is entered from normal operation in order to facilitate soft-start upon resumption of operation.

Soft Start Mode: During system start-up, the softstart mode is activated once the VCC voltage has exceeded V<sub>CC,ON</sub>, the VFB pin voltage has exceeded V<sub>OLP</sub> and BOP pin voltage has exceeded  $V_{BOP(EN)}$  and VCOMP voltage is less than  $V_{COMP,START}$  i.e. a pre-bias on COMP pin greater than V<sub>COMP,START</sub> threshold will not allow IC to commence operation. The soft start time is the time required for the VCOMP voltage to charge through its entire dynamic range i.e. through  $V_{\text{COMP,EFF}}$ . As a result, the soft-start time is dependent upon the component values selected for compensation of the voltage loop on the COMP pin. To an extent, keeping in mind the voltage feedback loop considerations, the softsystem start time is programmable.

As VCOMP voltage rises gradually, the IC allows a higher and higher RMS current into the PFC converter. This controlled increase of the input current amplitude contributes to reducing system component stress during start-up.

**Normal Mode:** The IC enters the normal operating mode once the soft start transition has been completed (for all practical purposes there is essentially no difference between the soft-start and normal modes). At this point the gate drive is switching and all protection functions of the IC are active. If, from the normal mode, the IC is pushed into either a Stand-by mode or UVLO/Sleep mode then COMP pin is actively discharged below  $V_{\text{COMP,START}}$  and system will go through soft-start upon resumption of operation.

**OVP Mode:** The IC enters OVP mode whenever an overvoltage condition is detected. A system overvoltage condition is recognized when VFB and/or OVP/EN pin voltage exceeds  $V_{\text{OVP}}$  threshold. When this happens the IC immediately disables the gate drive and holds it in that state. The gate drive is re-enabled only when both OVP/EN and VFB pin voltages are less than  $V_{\text{OVP}(RST)}$  threshold. This state is accessible from both the soft start and normal modes of operation.

**IPK LIMIT Mode:** The IC enters IPK LIMIT mode whenever the magnitude of ISNS pin voltage exceeds the  $V_{\text{ISNS}(PK)}$  threshold triggering cycle-bycycle peak over-current protection. When this happens, the IC immediately disables the gate drive and holds it in that state. Gate drive is reenabled when magnitude of ISNS pin voltage drops below  $V_{\text{ISNS}(PK)}$  threshold. This state is accessible from both the soft start and normal modes of operation.

### **State & Transitions Diagram**

# **IR1152 Timing Diagrams**

Figure 1: Supply Current vs. Supply Voltage

Figure 3: Icc Current vs. Temperature

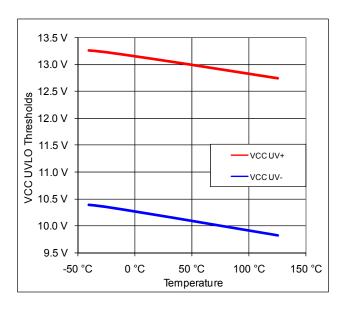

Figure 2: Undervoltage Lockout vs. Temperature

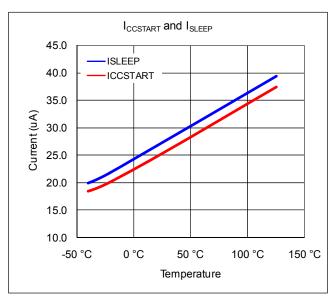

Figure 4: Startup Current and Sleep Current vs. Temperature

5.05

5.03

4.99

4.97

4.95

-50 °C 0 °C 50 °C 100 °C 150 °C

Temperature

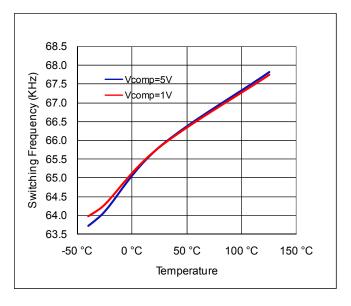

Figure 5: Switching Frequency vs.

Temperature

Figure 6: Reference Voltage vs. Temperature

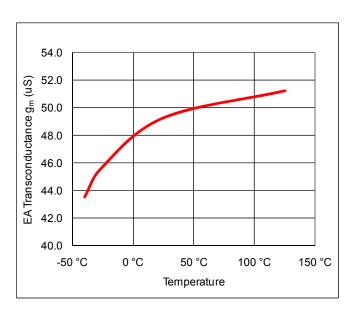

Figure 7: Voltage Error Amplifier Transconductance vs. Temperature

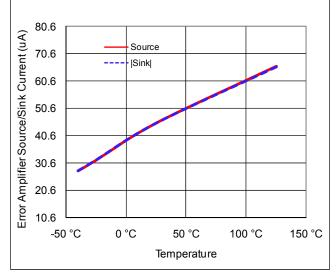

Figure 8: Voltage Error Amplifier Source & Sink Current vs. Temperature

-0.60

(>) plotself -0.70

-0.75

-0.80

-0.85

-0.90

-50 °C 0 °C 50 °C 100 °C 150 °C

Temperature

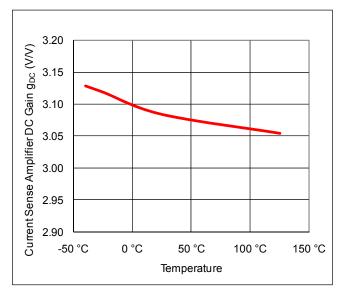

Figure 9: Current Amplifier DC Gain vs. Temperature

Figure 10: Peak Current Limit Threshold  $V_{\text{ISNS(PK)}}$  vs. Temperature

Figure 12: Brown-Out Protection Thresholds vs. Temperature

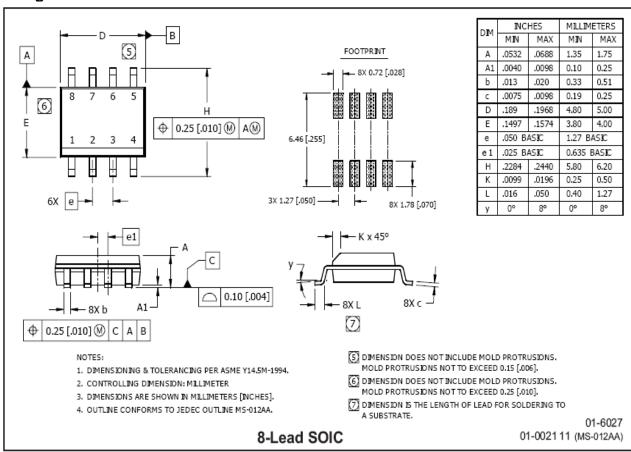

# Package Details: SOIC8N

# Tape and Reel Details: SOIC8N

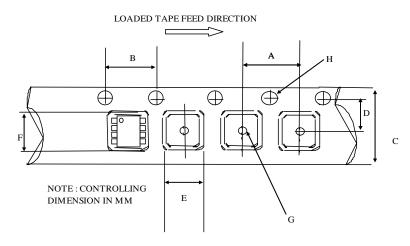

# CARRIER TAPE DIMENSION FOR 8SOICN

|      | Me    | etric | Imp   | erial |

|------|-------|-------|-------|-------|

| Code | Min   | Max   | Min   | Max   |

| Α    | 7.90  | 8.10  | 0.311 | 0.318 |

| В    | 3.90  | 4.10  | 0.153 | 0.161 |

| С    | 11.70 | 12.30 | 0.46  | 0.484 |

| D    | 5.45  | 5.55  | 0.214 | 0.218 |

| E    | 6.30  | 6.50  | 0.248 | 0.255 |

| F    | 5.10  | 5.30  | 0.200 | 0.208 |

| G    | 1.50  | n/a   | 0.059 | n/a   |

| Н    | 1.50  | 1.60  | 0.059 | 0.062 |

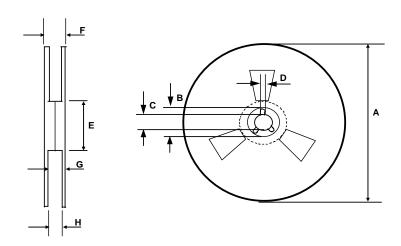

#### **REEL DIMENSIONS FOR 8SOICN**

|      | Me     | tric   | Imperial |        |  |

|------|--------|--------|----------|--------|--|

| Code | Min    | Max    | Min      | Max    |  |

| Α    | 329.60 | 330.25 | 12.976   | 13.001 |  |

| В    | 20.95  | 21.45  | 0.824    | 0.844  |  |

| С    | 12.80  | 13.20  | 0.503    | 0.519  |  |

| D    | 1.95   | 2.45   | 0.767    | 0.096  |  |

| E    | 98.00  | 102.00 | 3.858    | 4.015  |  |

| F    | n/a    | 18.40  | n/a      | 0.724  |  |

| G    | 14.50  | 17.10  | 0.570    | 0.673  |  |

| Н    | 12.40  | 14.40  | 0.488    | 0.566  |  |

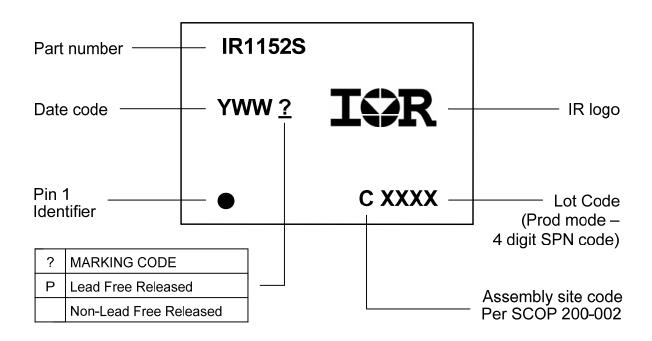

# **Part Marking Information**

### **Ordering Information**

| Base Part Number | Package Type | Standard Pack |          | Commission Down Norwale on |

|------------------|--------------|---------------|----------|----------------------------|

|                  |              | Form          | Quantity | Complete Part Number       |

| IR1152S          | SOIC8N       | Tube/Bulk     | 95       | IR1152SPBF                 |

|                  |              | Tape and Reel | 2500     | IR1152STRPBF               |

The information provided in this document is believed to be accurate and reliable. However, International Rectifier assumes no responsibility for the consequences of the use of this information. International Rectifier assumes no responsibility for any infringement of patents or of other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any patent or patent rights of International Rectifier. The specifications mentioned in this document are subject to change without notice. This document supersedes and replaces all information previously supplied.

For technical support, please contact IR's Technical Assistance Center <a href="http://www.irf.com/technical-info/">http://www.irf.com/technical-info/</a>

#### **WORLD HEADQUARTERS:**

233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Factor Correction - PFC category:

Click to view products by Infineon manufacturer:

Other Similar products are found below:

L6564TD FAN7930MX L4984D NCP1612A1DR2G NCP1618ADR2G TDA4863GXUMA2 ICE2PCS06GXUMA1 PFS7624C-TL

TDA48632GXUMA2 UCC29910APWR UCC2818AQDRQ1 TDA4862GGEGXUMA2 L6561D013TR L6566B ICE3PCS03G

LT1249CN8#PBF NCP1616A1DR2G LT1248IN#PBF LT1509CN#PBF BR6000-R12 ICE3PCS02GXUMA1 DCRL5 B44066R6012E230

ICE2PCS01GXUMA1 ADP1048ARQZ-R7 LT1249IS8#PBF LT1249CS8#PBF FAN4801SMY AL6562AS-13 ICE1PCS01G

NCP1652DR2G ICE2PCS05GXUMA1 ICE2PCS01G ICE2PCS06G ICE3PCS01G TDA4863 TDA4863-2 TDA4863-2G

XDPL8210XUMA1 AP1682EMTR-G1 ISL6731BFBZ L6563A L6563TR NCP1615A1DR2G NCP1605DR2G LT1509CSW#PBF

IRS2505LTRPBF TEA1761T/N2/DG,118 TEA1791T/N1,118 NCP1653DR2G