# Industrial PROFET™

# ITS4075Q-EP-D 75 $m\Omega$ Quad Channel Smart High-Side Power Switch

# 1 Overview

# **Features**

- Quad channel Smart High-Side Power Switch with integrated protection and diagnosis

- Maximum  $R_{DS(ON)}$  75 m $\Omega$  per channel at  $T_i$  = 25°C

- High output current capability: nominal current up to 2.6 A

- Low and accurate current limitation: 4.1 A (± 20 %)

- Extended supply voltage range up to 45 V

- All control inputs 24 V capable and support direct interface to optocouplers

- All control inputs 3.3 V and 5 V logic level compatible

- 4 kV electrostatic discharge protection (ESD)

- · Optimized electromagnetic compatibility

- · Very small, thermally enhanced TSDSO-14 package

- Device robustness validated by extended qualification according to JEDEC standard "JESD47J"

- Green product (RoHS compliant)

# **Potential applications**

- Digital output modules (PLC applications, factory automation)

- Industrial peripheral switches and power distribution

- Switching resistive, inductive and capacitive loads in harsh industrial environments

- Replacement for electromechanical relays, fuses and discrete circuits

- Most suitable for loads that require a precise current limit

# **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC JESD47J.

1

## 75 mΩ Quad Channel Smart High-Side Power Switch

#### Overview

# **Description**

The ITS4075Q-EP-D is a 75 m $\Omega$  Quad Channel Smart High-Side Power Switch providing integrated protection functions and a diagnosis feedback. With four channels capable of currents of more than 2 A each, very low typical  $R_{\rm DS(ON)}$  values of 120 m $\Omega$  at  $T_{\rm J}$  = 125°C and the small PG-TSDSO-14 exposed pad package it combines high current capability with minimum space requirements. The exposed pad of the thermally enhanced PG-TSDSO-14 package allows a very efficient heat transfer from the device to inner layers of the PCB by means of thermal vias. The power transistors are built by N-channel vertical power MOSFETs (DMOS) with charge pump. The ITS4075Q-EP-D is specifically designed to switch resistive, inductive or capacitive loads in harsh industrial environments. The ITS4075Q-EP-D is equipped with essential protection features that make it extremely robust. Diagnostic information can be read out via the STATUS output (ST). The four channel device can be controlled with four separate input pins. Due to their high voltage capability the input pins can be directly interfaced to optocouplers without additional external components.

## **Diagnostic Functions**

- Short circuit to ground (overload) indication

- · Overtemperature switch off indication

- Stable diagnostic signal during short circuit and overtemperature shutdown

- Intelligent channel fault detection system

## **Protection Functions**

- · Stable behavior during undervoltage

- Overtemperature protection with restart after cooling down phase

- · Overload- and short circuit protection

- Reverse polarity / inverse current protection with external components

- Overvoltage protection with external components

- · Loss of ground protection

The qualification of this product is based on JEDEC JESD47J and may reference existing qualification results of similar products. Such referring is justified by the structural similarity of the products. The product is not qualified and manufactured according to the requirements of Infineon Technologies with regard to automotive and/or transportation applications. Infineon Technologies administrates a comprehensive quality management system according to the latest version of the ISO9001 and IATF 16949.

The most updated certificates of the ISO9001 and IATF 16949 are available at www.infineon.com/cms/en/product/technology/quality/

| Туре          | Package     | Marking  |

|---------------|-------------|----------|

| ITS4075Q-EP-D | PG-TSDSO-14 | ITS4075Q |

# $75\,m\Omega$ Quad Channel Smart High-Side Power Switch

# **Table of Contents**

| 1              | Overview                                                                                                          | 1  |

|----------------|-------------------------------------------------------------------------------------------------------------------|----|

|                | Features                                                                                                          | 1  |

|                | Potential applications                                                                                            | 1  |

|                | Product validation                                                                                                | 1  |

|                | Description                                                                                                       | 2  |

|                | Table of Contents                                                                                                 |    |

| 2              | Block Diagram                                                                                                     |    |

| 3              | Pin Configuration                                                                                                 |    |

| 3.1            | Pin Assignment PG-TSDSO-14                                                                                        | 6  |

| 3.2            | Pin Definitions and Functions PG-TSDSO-14                                                                         |    |

| 3.3            | Voltage and Current Definitions                                                                                   |    |

| 4              | General Product Characteristics                                                                                   |    |

| 4.1<br>4.2     | Absolute Maximum Ratings                                                                                          |    |

| 4.2<br>4.3     | Typical Performance Characteristics Operating Current                                                             |    |

| 4.4            | Thermal Resistance                                                                                                |    |

| 5              | Power Stage                                                                                                       | 14 |

| 5.1            | Output ON-state Resistance                                                                                        |    |

| 5.2            | Turn ON/OFF Characteristics with Resistive Load                                                                   |    |

| 5.3            | Inductive Load                                                                                                    |    |

| 5.3.1<br>5.3.2 | Output Clamping  Maximum Load Inductance                                                                          |    |

| 5.4            | Inverse Current Capability                                                                                        |    |

| 5.5            | Electrical Characteristics: Power Stage                                                                           |    |

| 5.6            | Typical Performance Characteristics Power Stage                                                                   | 20 |

| 6              | Protection Functions                                                                                              |    |

| 6.1            | Loss of Ground Protection                                                                                         |    |

| 6.2<br>6.2.1   | Undervoltage Protection                                                                                           |    |

| 6.3            | Reverse Polarity Protection                                                                                       |    |

| 6.4            | Overload Protection                                                                                               |    |

| 6.4.1          | Current Limitation                                                                                                |    |

| 6.4.2          | Temperature Limitation in the Power DMOS                                                                          |    |

| 6.5<br>6.6     | Electrical Characteristics: Protection Functions         Typical Performance Characteristics Protection Functions |    |

| 7              | Diagnostic Functions                                                                                              |    |

| 7.1            | Electrical Characteristics: Diagnostic Functions                                                                  |    |

| 7.2            | Channel Fault Detection                                                                                           |    |

| 7.3            | Typical Performance Characteristics Diagnostic Functions                                                          |    |

| 8              | Input Pins                                                                                                        | 34 |

| 8.1            | Input Circuitry                                                                                                   |    |

| 8.2            | Input Pin Voltage                                                                                                 | 34 |

# $75\,m\Omega$ Quad Channel Smart High-Side Power Switch

| 8.3 | Electrical Characteristics: Input Pins         | 35   |

|-----|------------------------------------------------|------|

| 8.4 | Typical Performance Characteristics Input Pins | 36   |

| 9   | Application Information                        | . 37 |

| 9.1 | Application Diagram                            | 37   |

| 9.2 | Thermal Considerations                         | 38   |

| 10  | Package Outlines                               | . 40 |

| 11  | Revision History                               | . 41 |

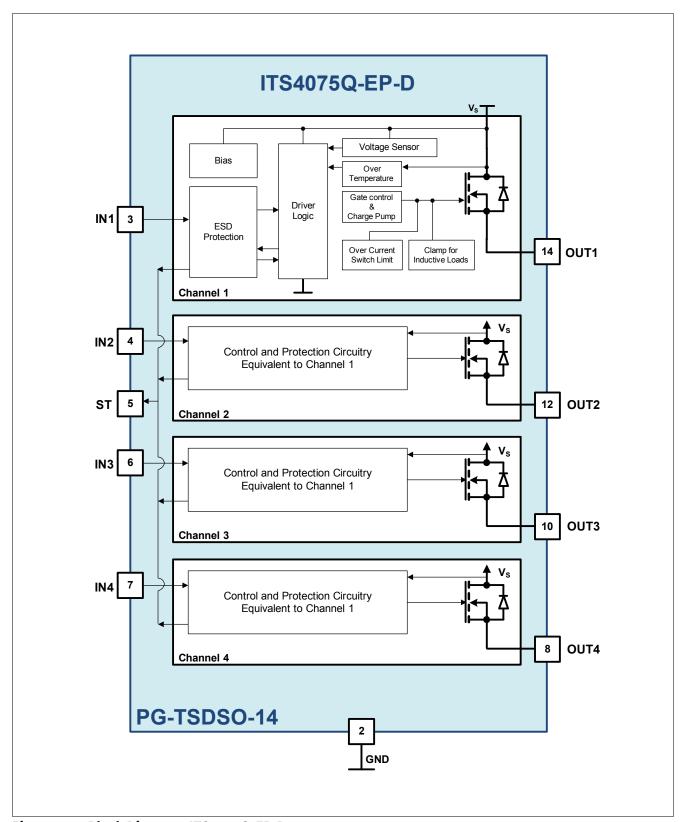

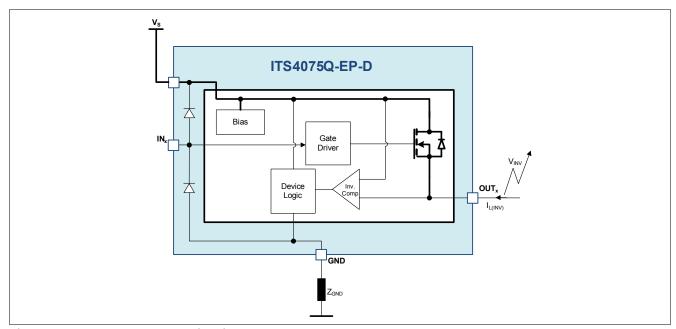

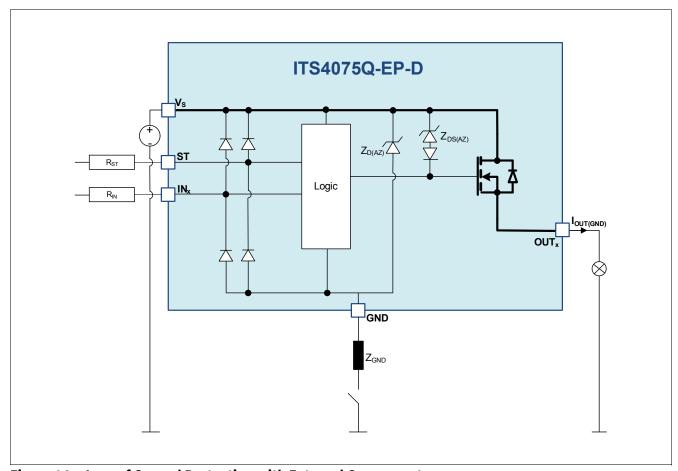

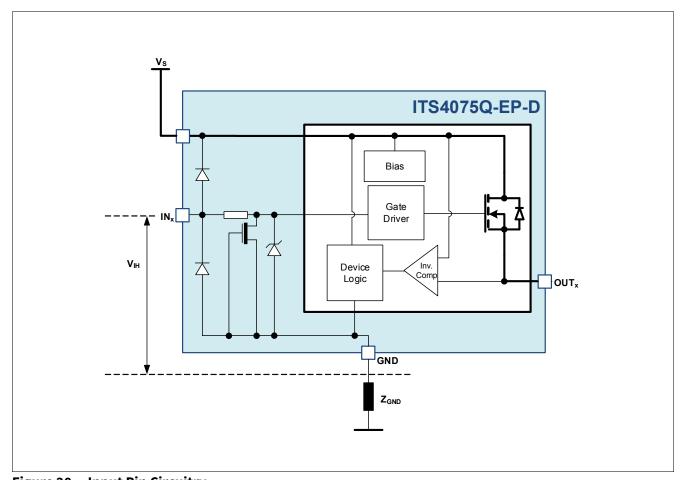

**Block Diagram**

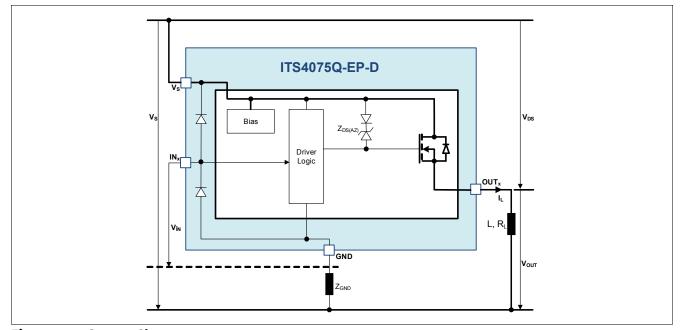

# 2 Block Diagram

Figure 1 Block Diagram: ITS4075Q-EP-D

**Pin Configuration**

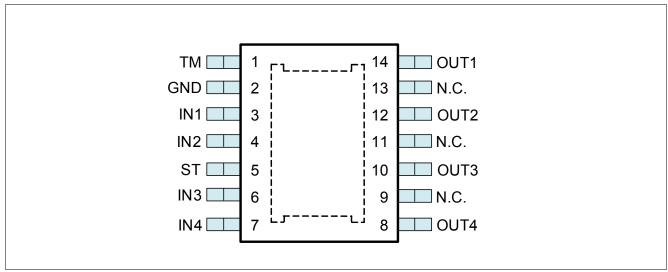

# **3** Pin Configuration

# 3.1 Pin Assignment PG-TSDSO-14

Figure 2 Pin Configuration PG-TSDSO-14

# 3.2 Pin Definitions and Functions PG-TSDSO-14

| Pin         | Symbol | Function                                                                               |

|-------------|--------|----------------------------------------------------------------------------------------|

| 1           | TM     | <b>Test Mode Entry;</b> must be connected to device GND (pin 2) via resistor 1)        |

| 2           | GND    | Ground pin                                                                             |

| 3           | IN1    | INput channel 1; Input signal for channel 1 activation, Active "High"                  |

| 4           | IN2    | INput channel 2; Input signal for channel 2 activation, Active "High"                  |

| 5           | ST     | <b>STatus Feedback;</b> Active "Low", connect with external pull-up resistor to "High" |

| 6           | IN3    | INput channel 3; Input signal for channel 3 activation, Active "High"                  |

| 7           | IN4    | INput channel 4; Input signal for channel 4 activation, Active "High"                  |

| 8           | OUT4   | <b>OUTput 4;</b> Protected high side power output channel 4                            |

| 10          | OUT3   | OUTput 3; Protected high side power output channel 3                                   |

| 12          | OUT2   | OUTput 2; Protected high side power output channel 2                                   |

| 14          | OUT1   | <b>OUTput 1;</b> Protected high side power output channel 1                            |

| 9,11,13     | N.C.   | Not Connected                                                                          |

| Exposed Pad | VS     | Voltage Supply                                                                         |

<sup>1)</sup> To ensure proper functionality of the device the TM pin must be connected to device ground. In order to protect the pin furthermore in case of reverse polarity conditions or ground shifts the TM pin needs to be connected with a serial resistor to device ground. The recommended value for this resistor is  $2.2 \, \mathrm{k}\Omega$ .

**Pin Configuration**

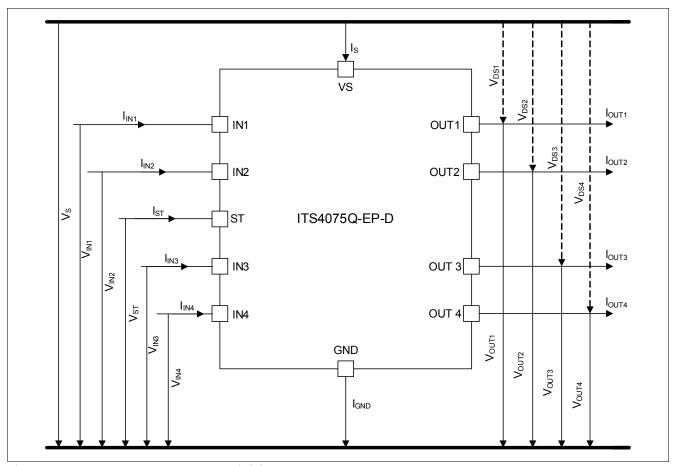

#### **Voltage and Current Definitions** 3.3

Figure 3 shows all terms used in this data sheet, with associated convention for positive values.

**Voltage and Current Definitions** Figure 3

## **General Product Characteristics**

# 4 General Product Characteristics

# 4.1 Absolute Maximum Ratings

Table 1 Absolute Maximum Ratings 1)

$T_i$  = -40°C to 150°C, positive current flowing into pin; (unless otherwise specified)

| Parameter                                               | Symbol                | l Values |      | Unit | Note or Test Condition | Number                                                            |                |  |

|---------------------------------------------------------|-----------------------|----------|------|------|------------------------|-------------------------------------------------------------------|----------------|--|

|                                                         |                       | Min.     | Тур. | Max. |                        |                                                                   |                |  |

| Supply Voltages                                         |                       |          |      |      |                        |                                                                   |                |  |

| Supply voltage                                          | $V_{S}$               | -0.3     | -    | 45   | V                      | -                                                                 | P_4.1.1        |  |

| Reverse polarity voltage                                | - V <sub>S(REV)</sub> | 0        | -    | 28   | V                      | <sup>2)</sup> t<2 min                                             | P_4.1.3        |  |

|                                                         |                       |          |      |      |                        | $T_A = 25^{\circ}C$                                               |                |  |

|                                                         |                       |          |      |      |                        | $R_{\rm L} \ge 25 \Omega$                                         |                |  |

| 0 1 1 1 1                                               | .,                    | •        |      | 0.0  | .,                     | $Z_{\text{GND}} = 150 \Omega$ Power Resistor                      | <b>D</b> 4 4 4 |  |

| Supply voltage for short circuit protection             | $V_{S(SC)}$           | 0        | _    | 36   | V                      | -                                                                 | P_4.1.4        |  |

| Input Pins                                              |                       |          |      |      |                        |                                                                   |                |  |

| Voltage at INPUT pins                                   | $V_{IN}$              | -0.3     | _    | 45   | V                      | $V_{\rm S} > V_{\rm IN}$                                          | P_4.1.5        |  |

| Current through INPUT pins                              |                       | -2       | _    | 2    | mA                     | -                                                                 | P_4.1.6        |  |

| STATUS Pin                                              | IN                    | -2       | _    | Z    | ША                     | _                                                                 | P_4.1.0        |  |

|                                                         | 1/                    | 0.2      |      | 4E   | V                      | 1/ > 1/                                                           | D 4 1 7        |  |

| Voltage at ST pin                                       | V <sub>ST</sub>       | -0.3     | -    | 45   |                        | $V_{\rm S} > V_{\rm ST}$                                          | P_4.1.7        |  |

| Current through ST pin                                  | / <sub>ST</sub>       | -2       | _    | 2    | mA                     | _                                                                 | P_4.1.8        |  |

| Power Stage                                             | _                     |          |      |      | 1                      | 2)                                                                |                |  |

| Power dissipation (DC)                                  | $P_{TOT}$             | _        | _    | 1.9  | W                      | $^{3)}$ $T_A = 85^{\circ}\text{C}$<br>$T_j < 150^{\circ}\text{C}$ | P_4.1.10       |  |

| Maximum energy dissipation                              | $E_{AS}$              | _        | -    | 60   | mJ                     | / <sub>L</sub> = 2 A                                              | P_4.1.11       |  |

| Single pulse (one channel)                              |                       |          |      |      |                        | $T_{\rm j} = 150^{\circ}{\rm C}$<br>$V_{\rm S} = 28 {\rm V}$      |                |  |

| Voltage at power transistor                             | $V_{ m DS}$           | _        | _    | 65   | V                      | _                                                                 | P_4.1.12       |  |

| Currents                                                |                       |          |      |      |                        |                                                                   | ·              |  |

| Current through ground pin                              | / <sub>GND</sub>      | -20      | _    | 20   | mA                     | -                                                                 | P_4.1.13       |  |

| Temporary reverse current through ground pin to $V_{S}$ | / <sub>GND</sub>      | -200     | -    | -    | mA                     | t<2 min                                                           | P_4.1.21       |  |

| Temperatures                                            | 1                     |          |      |      | 1                      |                                                                   |                |  |

| Junction temperature                                    | $T_{i}$               | -40      | _    | 150  | °C                     | -                                                                 | P_4.1.14       |  |

| Storage temperature                                     | $T_{\rm STG}$         | -55      | _    | 150  | °C                     | -                                                                 | P_4.1.15       |  |

| ESD Susceptibility                                      | 1                     | I .      | 1    | 1    | П                      | I                                                                 | 1              |  |

| ESD susceptibility (all pins)                           | V <sub>ESD_HBM</sub>  | -2       | _    | 2    | kV                     | HBM <sup>4)</sup>                                                 | P_4.1.16       |  |

| ESD susceptibility OUT Pin vs. GND and $V_S$ connected  | V <sub>ESD_HBM</sub>  | -4       | -    | 4    | kV                     | HBM <sup>4)</sup>                                                 | P_4.1.17       |  |

## 75 mΩ Quad Channel Smart High-Side Power Switch

#### **General Product Characteristics**

# **Table 1** Absolute Maximum Ratings 1) (cont'd)

$T_i = -40$ °C to 150°C, positive current flowing into pin; (unless otherwise specified)

| Parameter                            | Symbol Values L      |      | Unit | Note or Test Condition | Number |                   |          |

|--------------------------------------|----------------------|------|------|------------------------|--------|-------------------|----------|

|                                      |                      | Min. | Тур. | Max.                   |        |                   |          |

| ESD susceptibility                   | V <sub>ESD_CDM</sub> | -500 | -    | 500                    | V      | CDM <sup>5)</sup> | P_4.1.18 |

| ESD susceptibility pin (corner pins) | V <sub>ESD_CDM</sub> | -750 | _    | 750                    | V      | CDM <sup>5)</sup> | P_4.1.19 |

- 1) Not subject to production test; specified by design.

- 2) Reverse polarity protection can only be achieved in combination with external components: to limit the current through the GND-path a 150  $\Omega$  power resistor needs to be placed between GND-pin and ground. An alternative solution is to use a reverse current diode in the GND-path to realize reverse polarity protection. In this case placing a resistor in the range of  $\geq$  27  $\Omega$  in series to the diode is recommended to improve at the same time the overvoltage capability in case of overvoltage pulses on  $V_{\varsigma}$ .

- 3) This parameter serves as reference for the thermal budget: it illustrates the power dissipation that can be handled by the device in an application under the given boundary conditions before exceeding the maximum rating of  $T_j$  when assuming a  $R_{thJA}$  value for a thermally well dimensioned PCB connection like given in the JEDEC case **P\_4.3.3** in **Chapter 4.4**. As  $R_{thJA}$  depends strongly on the applied PCB and layout of any individual application the actual achievable values of  $P_{TOT}$  can either be lower or higher depending on the given application.

- 4) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS-001(1.5 k $\Omega$ , 100 pF).

- 5) ESD susceptibility, Charged Device Model "CDM" JEDEC JESD22-C101.

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

# $75\,m\Omega$ Quad Channel Smart High-Side Power Switch

### **General Product Characteristics**

# 4.2 Functional Range

# Table 2 Functional Range

$T_i$  = -40°C to 150°C; (unless otherwise specified)

| Parameter                                         | Symbol                 |      | Value       | S   | Unit | Note or                                                                                                                                        | Number  |  |

|---------------------------------------------------|------------------------|------|-------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

|                                                   |                        | Min. | Min. Typ. M |     |      | <b>Test Condition</b>                                                                                                                          |         |  |

| Nominal operating voltage                         | $V_{S(NOM)}$           | 8    | 24          | 36  | V    | $V_{\rm S} > V_{\rm IN}$                                                                                                                       | P_4.2.1 |  |

| Extended operating voltage                        | $V_{S(EOP)}$           | 5    | -           | 45  | V    | $I_{\text{OUT}}^{(1)} V_{\text{S}} > V_{\text{IN}}$ $I_{\text{OUT}}^{(2)} = 2 \text{ A}$ $V_{\text{DS}}^{(2)} < 0.5 \text{ V}$                 | P_4.2.2 |  |

| Minimum functional supply voltage during power-up | $V_{S(OP)_{MIN}}$      | -    | 4.3         | 5   | V    | $V_{\rm S} > V_{\rm IN}$<br>$I_{\rm OUT} = 0$ A to<br>$V_{\rm DS} < 0.5$ V<br>( $V_{\rm S}$ rising;<br>powering up)                            | P_4.2.3 |  |

| Undervoltage shutdown                             | $V_{S(UV)}$            | 3    | 3.5         | 4.1 | V    | $V_{\rm S} > V_{\rm IN}$<br>from $V_{\rm DS} < 0.5 \rm V$<br>to $I_{\rm OUT} = 0 \rm A$<br>( $V_{\rm S}$ dropping<br>from functional<br>range) | P_4.2.4 |  |

| Undervoltage shutdown hysteresis                  | V <sub>S(UV)_HYS</sub> | _    | 850         | _   | m۷   | 1) _                                                                                                                                           | P_4.2.5 |  |

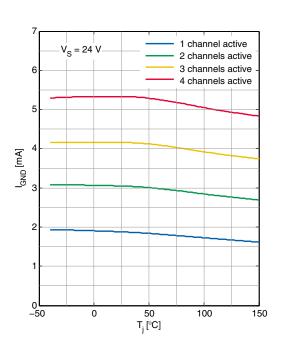

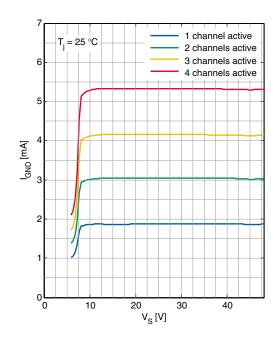

| Operating current One channel active              | / <sub>GND_1</sub>     | -    | 2           | 3   | mA   | $V_S = V_{IN} = 24 \text{ V}$<br>Device in $R_{DS(ON)}$                                                                                        | P_4.2.6 |  |

| Operating current All channels active             | / <sub>GND_4</sub>     | -    | 5.2         | 7   | mA   | $V_{\rm S} = V_{\rm IN} = 24 \text{ V}$<br>Device in $R_{\rm DS(ON)}$                                                                          | P_4.2.9 |  |

| Junction Temperature                              | $T_{\rm j}$            | -40  | _           | 150 | °C   | _                                                                                                                                              | P_4.2.8 |  |

<sup>1)</sup> Not subject to production test; specified by design.

Note:

Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

### **General Product Characteristics**

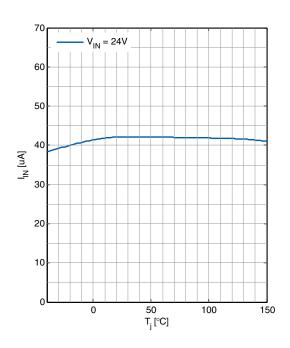

#### **Typical Performance Characteristics Operating Current** 4.3

# **Typical Performance Characteristics**

# Operating Current $I_{\rm GND}$ versus Junction Temperature $T_i$

# Operating Current $I_{\rm GND}$ versus Supply Voltage V<sub>S</sub>

#### **General Product Characteristics**

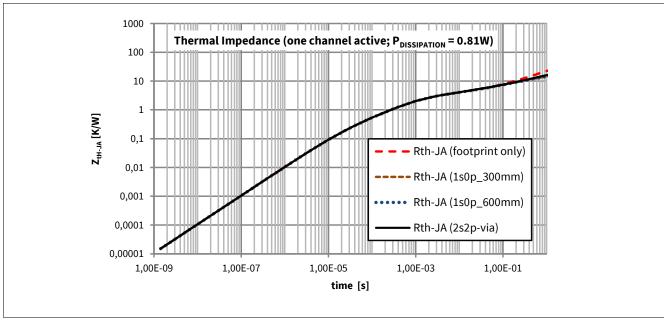

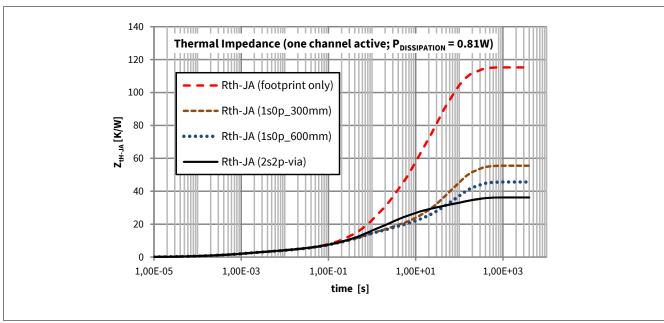

## 4.4 Thermal Resistance

Table 3 Thermal Resistance 1)

| Parameter                               | Symbol                       |      | Value | S    | Unit | Note or               | Number  |

|-----------------------------------------|------------------------------|------|-------|------|------|-----------------------|---------|

|                                         |                              | Min. | Тур.  | Max. |      | <b>Test Condition</b> |         |

| Junction to exposed pad soldering point | R <sub>thJC</sub>            | _    | 1     | _    | K/W  | _                     | P_4.3.1 |

| Junction to ambient All channels active | R <sub>thJA_2s2pvia</sub>    | _    | 33    | _    | K/W  | 2) _                  | P_4.3.3 |

| Junction to ambient All channels active | R <sub>thJA_1s0p</sub>       | -    | 102   | -    | K/W  | 3) _                  | P_4.3.4 |

| Junction to ambient All channels active | R <sub>thJA_1s0p_300mm</sub> | -    | 48    | -    | K/W  | 4) _                  | P_4.3.5 |

| Junction to ambient All channels active | R <sub>thJA_1s0p_600mm</sub> | _    | 40    | -    | K/W  | 5) _                  | P_4.3.6 |

- 1) Not subject to production test; specified by design.

- 2) Specified  $R_{thJA}$  value is according to JEDEC JESD51-2,-5,-7 at natural convection on FR4 2s2p board; the product (chip + package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 2 inner copper layers (2 × 70  $\mu$ m Cu, 2 × 35  $\mu$ m Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

- 3) Specified  $R_{thJA}$  value is according to JEDEC JESD51-3 at natural convection on FR4 1s0p board, footprint; The product (chip + package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 1 × 70  $\mu$ m Cu.

- 4) Specified  $R_{thJA}$  value is according to JEDEC JESD51-3 at natural convection on FR4 1s0p board, 300 mm; The product (chip + package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 1 × 70  $\mu$ m Cu.

- 5) Specified  $R_{thJA}$  value is according to JEDEC JESD51-3 at natural convection on FR4 1s0p board, 600 mm; The product (chip + package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 1 × 70  $\mu$ m Cu.

Figure 4 Thermal Impedance (short time scale; one channel active)

# $75\,m\Omega$ Quad Channel Smart High-Side Power Switch

## **General Product Characteristics**

Figure 5 Thermal Impedance (long time scale; one channel active)

# 5 Power Stage

The power stages are built using an N-channel vertical power MOSFET (DMOS) with charge pump.

# 5.1 Output ON-state Resistance

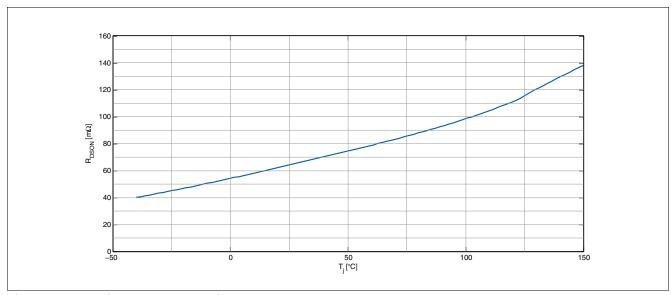

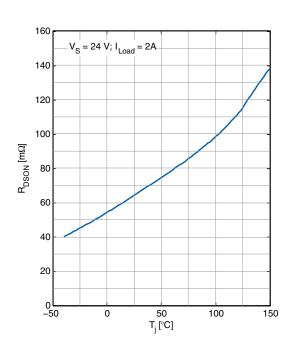

The ON-state resistance  $R_{DS(ON)}$  of the power stage depends on supply voltage as well as on junction temperature  $T_j$ . **Figure 6** shows the influence of temperature on the typical ON-state resistance. The behavior of the power stage in reverse polarity condition is described in **Chapter 6.3**.

Figure 6 Typical ON-state Resistance

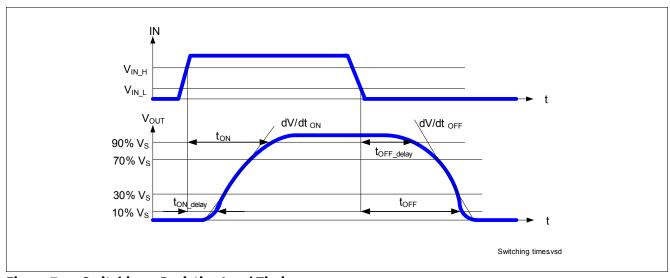

# 5.2 Turn ON/OFF Characteristics with Resistive Load

A "High" signal at the input pin (see **Chapter 8**) causes the power DMOS to switch ON with a dedicated slope, which is optimized in terms of EMC emission.

Figure 7 shows the typical timing when switching a resistive load.

Figure 7 Switching a Resistive Load Timing

## 5.3 Inductive Load

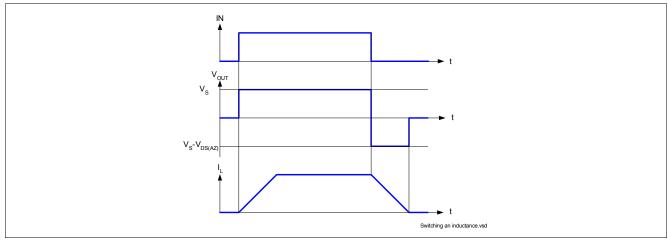

## 5.3.1 Output Clamping

When switching OFF inductive loads with high-side switches, the voltage  $V_{\text{OUT}}$  drops below ground potential, because the inductance intends to continue driving the current. To prevent the destruction of the device by avalanche due to high voltage drop over the power stage a voltage clamp mechanism  $Z_{\text{DS(AZ)}}$  is implemented that limits negative output voltage to a certain level ( $V_{\text{S}} - V_{\text{DS(AZ)}}$ ). The clamping mechanism allows in addition a fast demagnetization of inductive loads because during the phase of active clamping the power is dissipated to a great extent rapidly inside the switch. On the other hand the power dissipated inside the switch while switching off inductive loads can cause considerable stress to the device. Therefore the maximum allowed energy at a given current (and by this also the inductance) is limited. In **Figure 8** and **Figure 9** the basic principle of active clamping as well as simplified waveforms when switching off inductive loads are illustrated.

Figure 8 Output Clamp

Figure 9 Switching an Inductive Load Timing

## 5.3.2 Maximum Load Inductance

During demagnetization of inductive loads, the following energy must be dissipated by the ITS4075Q-EP-D. This energy can be calculated by help of the following equation:

$$E = V_{\mathsf{DS}(\mathsf{AZ})} \times \frac{L}{R_{\mathsf{L}}} \times \left[ \frac{V_{\mathsf{S}} - V_{\mathsf{DS}(\mathsf{AZ})}}{R_{\mathsf{L}}} \times \ln\left(1 - \frac{R_{\mathsf{L}} \times I_{\mathsf{L}}}{V_{\mathsf{S}} - V_{\mathsf{DS}(\mathsf{AZ})}}\right) + I_{\mathsf{L}} \right]$$

(5.1)

Following equation gets simplified under the assumption of  $R_i = 0 \Omega$ :

$$E = \frac{1}{2} \times L \times I^2 \times \left(1 - \frac{V_S}{V_S - V_{DS(AZ)}}\right)$$

(5.2)

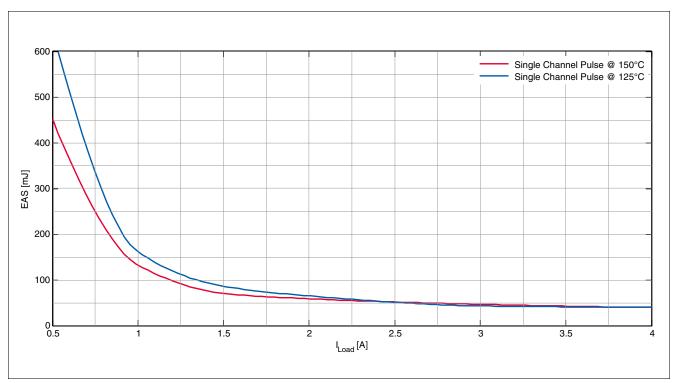

The energy, which may be converted into heat, is limited by the thermal design of the component. See **Figure 10** for the maximum allowed energy dissipation as a function of the load current for a singular pulse event on one channel.

Figure 10 Maximum Energy Dissipation Single Pulse for a Single Channel;  $V_S = 28 \text{ V}$

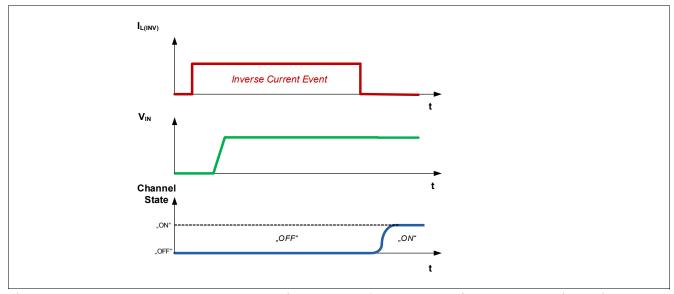

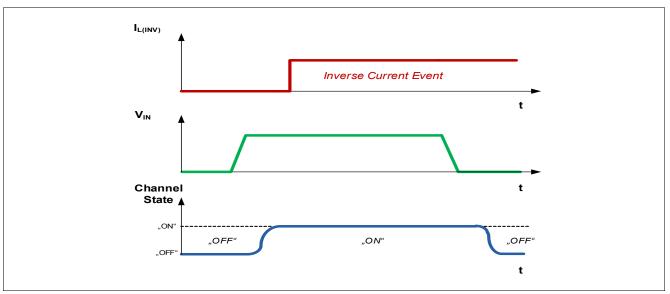

# 5.4 Inverse Current Capability

In case of inverse current, meaning a voltage  $V_{INV}$  at the OUTput higher than the supply voltage  $V_S$ , a current  $I_{INV}$  will flow from output to  $V_S$  pin via the body diode of the power transistor (please refer to **Figure 11**). Channels that are active (ON-state) by the time when the inverse current condition appears will remain active and their output stage will follow the state of the corresponding IN pin, which means that the channel can be switched off during inverse current condition. Channels that are inactive (OFF-state) by the time when the inverse current condition appears will remain inactive regardless of the state of the corresponding IN pin. If during an inverse current condition the IN-pin of a channel is set from "Low" to "High" in order to activate the channel, the output stage of the channel is kept OFF until the inverse current disappears. For all cases the current  $I_{INV}$  should not be higher than  $I_{L(INV)}$ . Please note that during inverse current condition the protection functions of concerned channels are not available.

Figure 11 Inverse Current Circuitry

Figure 12 Inverse Current event: channel in OFF-state (channel remains off for duration of inverse current event)

Figure 13 Inverse Current event: channel in ON-state (output not influenced but can be switched off)

# 5.5 Electrical Characteristics: Power Stage

# Table 4 Electrical Characteristics: Power Stage

$V_{\rm S}$  = 8 V to 36 V,  $T_{\rm j}$  = -40°C to 150°C (unless otherwise specified). Typical values are given at  $V_{\rm S}$  = 24 V,  $T_{\rm i}$  = 25°C

| Parameter                                                           | Symbol                  | Symbol Values |      |      |    | Note or                                                                                            | Number   |  |

|---------------------------------------------------------------------|-------------------------|---------------|------|------|----|----------------------------------------------------------------------------------------------------|----------|--|

|                                                                     |                         | Min.          | Тур. | Max. |    | <b>Test Condition</b>                                                                              |          |  |

| ON-state resistance per channel ( $T_j = 25$ °C)                    | R <sub>DS(ON)</sub>     | -             | -    | 75   | mΩ | $I_{Lx} = 2 \text{ A}$ $I_{IN} = 4.5 \text{ V}$ $T_{j} = 25^{\circ}\text{C}$                       | P_5.5.18 |  |

| ON-state resistance per<br>channel ( <i>T</i> <sub>j</sub> = 125°C) | R <sub>DS(ON)_125</sub> | -             | 120  | -    | mΩ | <sup>2)</sup> $I_{Lx} = 2 \text{ A}$<br>$I_{IN} = 4.5 \text{ V}$<br>$I_{j} = 125^{\circ}\text{C}$  | P_5.5.19 |  |

| ON-state resistance per channel ( $T_j = 150$ °C)                   | R <sub>DS(ON)_150</sub> | -             | -    | 150  | mΩ | $I_{Lx} = 2 \text{ A}$ $I_{IN} = 4.5 \text{ V}$ $T_j = 150^{\circ}\text{C}$                        | P_5.5.1  |  |

| Nominal load current<br>per channel                                 | / <sub>L(NOM)1</sub>    | _             | _    | 2.6  | А  | <sup>1) 2)</sup> $T_j$ < 150°C                                                                     | P_5.5.2  |  |

| Drain to source clamping voltage $V_{DS(AZ)} = [V_S - V_{OUT}]$     | $V_{DS(AZ)}$            | 65            | 70   | 75   | V  | $I_{DS} = 5 \text{ mA}$                                                                            | P_5.5.5  |  |

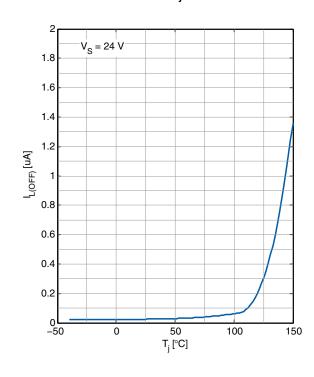

| Output leakage current per<br>channel                               | / <sub>L(OFF)</sub>     | -             | 0.1  | 0.5  | μΑ | $V_{\text{IN}}$ floating $V_{\text{OUT}} = 0 \text{ V}$ $T_{\text{j}} \le 85^{\circ}\text{C}$      | P_5.5.6  |  |

| Output leakage current per<br>channel                               | / <sub>L(OFF)_150</sub> | -             | 1    | 5    | μΑ | $V_{\text{IN}}$ floating<br>$V_{\text{OUT}} = 0 \text{ V}$<br>$T_{\text{j}} = 150^{\circ}\text{C}$ | P_5.5.4  |  |

| Inverse current capability                                          | / <sub>L(INV)</sub>     | _             | 2.2  | -    | А  | $V_{\rm S} < V_{\rm OUTX}$<br>t<2 min                                                              | P_5.5.7  |  |

# 75 mΩ Quad Channel Smart High-Side Power Switch

# **Power Stage**

#### Table 4 **Electrical Characteristics: Power Stage (cont'd)**

$V_{\rm S}$  = 8 V to 36 V,  $T_{\rm i}$  = -40°C to 150°C (unless otherwise specified). Typical values are given at  $V_S = 24 \text{ V}$ ,  $T_i = 25 ^{\circ}\text{C}$

| Parameter                                                 | Symbol                                 |      | Values | S    | Unit | Note or                                   | Number   |  |

|-----------------------------------------------------------|----------------------------------------|------|--------|------|------|-------------------------------------------|----------|--|

|                                                           |                                        | Min. | Тур.   | Max. |      | <b>Test Condition</b>                     |          |  |

| Slew rate (switch on) 30% to 70% of $V_S$                 | $\Delta V / \Delta t_{ON}$             | 0.3  | 0.75   | 1.9  | V/µs | $R_L = 12 \Omega$<br>$V_S = 24 \text{ V}$ | P_5.5.8  |  |

| Slew rate (switch off) 70% to 30% of $V_S$                | -Δ <i>V</i> /Δ <i>t</i> <sub>OFF</sub> | 0.3  | 0.75   | 1.9  | V/µs | $R_L = 12 \Omega$<br>$V_S = 24 \text{ V}$ | P_5.5.9  |  |

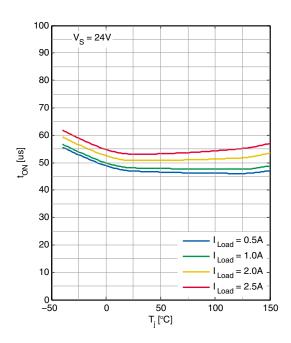

| Turn-ON time to $V_{OUT} = 90\% V_{S}$                    | t <sub>ON</sub>                        | 20   | 55     | 100  | μs   | $R_L = 12 \Omega$<br>$V_S = 24 \text{ V}$ | P_5.5.11 |  |

| Turn-OFF time to $V_{OUT} = 10\%$<br>$V_{S}$              | t <sub>OFF</sub>                       | 20   | 55     | 100  | μs   | $R_L = 12 \Omega$<br>$V_S = 24 \text{ V}$ | P_5.5.12 |  |

| Turn-ON / OFF matching $t_{\text{OFF}}$ - $t_{\text{ON}}$ | $\Delta t_{\rm SW}$                    | -50  | 0      | 50   | μs   | $R_L = 12 \Omega$<br>$V_S = 24 \text{ V}$ | P_5.5.13 |  |

| Turn-ON time to $V_{OUT} = 10\%$<br>$V_{S}$               | t <sub>ON_delay</sub>                  | _    | 25     | 50   | μs   | $R_L = 12 \Omega$<br>$V_S = 24 \text{ V}$ | P_5.5.14 |  |

| Turn-OFF time to $V_{OUT} = 90\%$<br>$V_{S}$              | t <sub>OFF_delay</sub>                 | _    | 25     | 50   | μs   | $R_L = 12 \Omega$<br>$V_S = 24 \text{ V}$ | P_5.5.15 |  |

<sup>1)</sup> This parameter describes the nominal load capability per channel from an electrical point of view respecting a maximum  $T_i \le 150^{\circ}$ C. Please note that depending on the individual thermal design of a real application (and a potentially insufficient thermal budget resulting hereof) additional restrictions for  $I_{L(NOM)}$  may occur for pure thermal reasons in order not to exceed the maximum allowed junction temperature  $T_i = 150$ °C. The latter needs to be considered especially for cases where all four channels are operating simultaneously under high load conditions and at high ambient temperature  $T_{AMB}$ . For further details about potential derating of the nominal load current due to thermal restrictions please refer to "Thermal Considerations" on Page 38.

- 2) Not subject to production test; specified by design.

- 3) Please note that during inverse current condition the protection features are not operational.

# 5.6 Typical Performance Characteristics Power Stage

# **Typical Performance Characteristics**

# ON-State Resistance $R_{\rm DSON}$ versus Junction Temperature $T_{\rm i}$

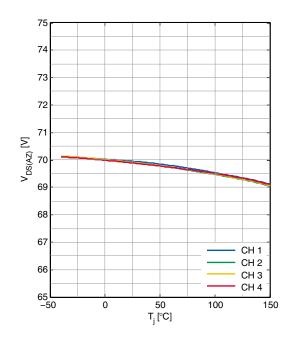

# Output Clamp Voltage $V_{\rm DS(AZ)}$ versus Junction Temperature $T_{\rm i}$

# Leakage Current per channel $I_{L(OFF)}$ versus Junction Temperature $T_i$

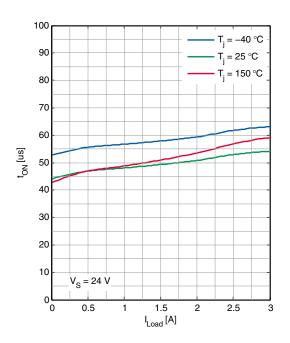

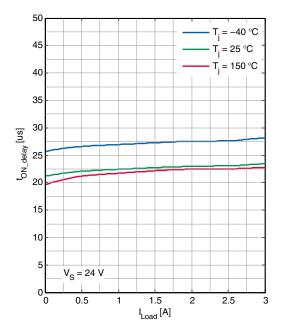

Turn-ON time  $t_{ON}$  to  $V_{OUT}$  = 90% versus Junction Temperature  $T_i$

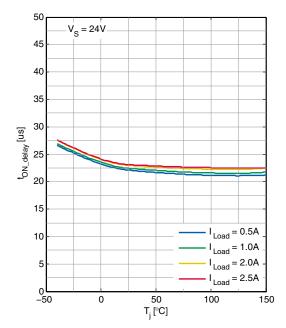

Turn-ON delay time  $t_{\rm ON\_delay}$  to  $V_{\rm OUT}$  = 10% versus Junction Temperature  $T_{\rm i}$

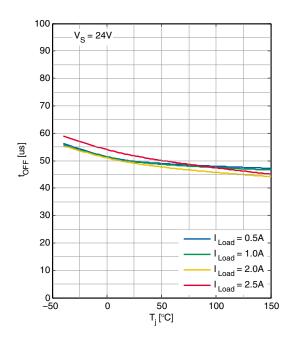

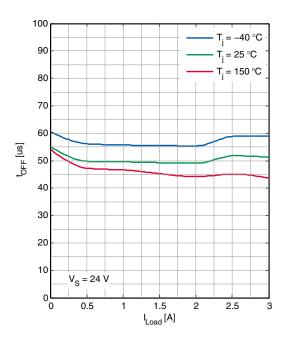

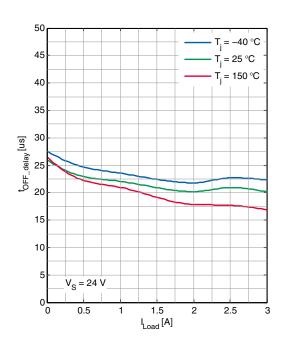

Turn-OFF time  $t_{\text{OFF}}$  to  $V_{\text{OUT}}$  = 90% versus Junction Temperature  $T_{\text{i}}$

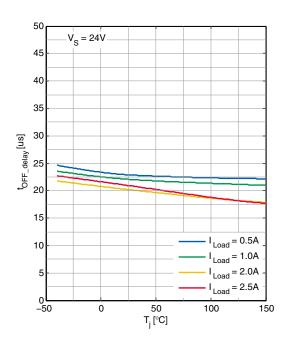

Turn-OFF delay time  $t_{\rm OFF\_delay}$  to  $V_{\rm OUT}$  = 10% versus Junction Temperature  $T_{\rm i}$

Turn-ON time  $t_{\rm ON}$  to  $V_{\rm OUT}$  = 90% versus Load Current  $I_{\rm Load}$

Turn-ON delay time  $t_{\rm ON\_delay}$  to  $V_{\rm OUT}$  = 10% versus Load Current  $I_{\rm Load}$

Turn-OFF time  $t_{\text{OFF}}$  to  $V_{\text{OUT}}$  = 90% versus Load Current  $I_{\text{Load}}$

Turn-OFF delay time  $t_{\rm OFF\_delay}$  to  $V_{\rm OUT}$  = 10% versus Load Current  $I_{\rm Load}$

## 6 Protection Functions

The device provides integrated protection functions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Protection functions are designed to prevent the destruction of the ITS4075Q-EP-D due to fault conditions described in the data sheet. Please note that fault conditions are not considered as normal operation conditions and the protection functions are neither designed for continuous operation nor for repetitive operation.

## 6.1 Loss of Ground Protection

In case of loss of module ground when the load remains connected to ground, the device protects itself by automatically turning OFF (when it was previously ON) or remains OFF, regardless of the voltage applied at the input pins.

In an application where the inputs are directly controlled by logic levels  $< V_S$  (e.g. by a microcontroller without galvanic isolation), it is recommended to use input resistors <sup>1)</sup> between the external control circuit (microcontroller) and the ITS4075Q-EP-D to protect also the external control circuit in case of loss of device ground.

In case of loss of module or device ground, a current  $(I_{OUT(GND)})$  can flow out of the DMOS. **Figure 14** sketches the situation.

$Z_{GND}$  is recommended to be a resistor in series to a diode.

Figure 14 Loss of Ground Protection with External Components

# 6.2 Undervoltage Protection

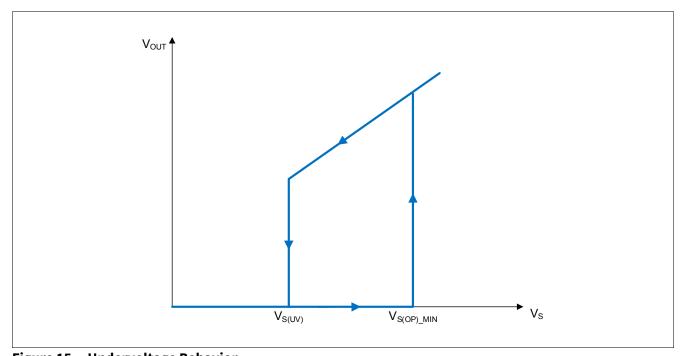

If the supply voltage falls below  $V_{S(UV)}$  the undervoltage protection of the device is triggered.  $V_{S(UV)}$  represents hence the minimum voltage for which the switch still can hold ON. Once the device is off  $V_{S(OP)\_MIN}$  represents the lowest voltage where the device is turning on again (and thus the channels can be switched again). If the supply voltage is below the undervoltage threshold  $V_{S(UV)}$ , the channels of the device are OFF (or turning OFF). As soon as the supply voltage is recovering and exceeding the threshold of the functional supply voltage  $V_{S(OP)\_MIN}$ , the device is re-powering and its channels can be switched again. In addition the protection functions as well as diagnosis become operational once  $V_{SOP\_MIN}$  is reached. Figure 15 sketches the undervoltage mechanism.

Figure 15 Undervoltage Behavior

# 6.2.1 Overvoltage Protection

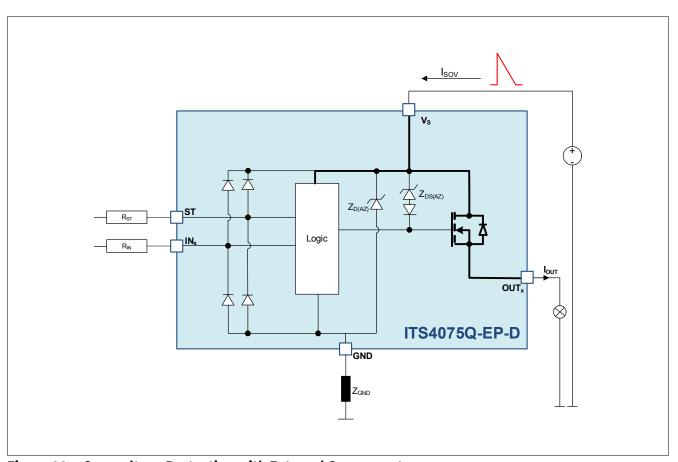

There is an integrated clamping mechanism for overvoltage protection ( $Z_{D(AZ)}$ ). To ensure this mechanism operates properly in the application, the current in the Zener diode  $Z_{D(AZ)}$  must be limited by a ground resistor. **Figure 16** shows a typical application to withstand overvoltage issues. In case of supply voltage higher than  $V_{S(AZ)}$ , the voltage across supply to ground path is clamped. As a result, the internal ground potential rises to  $V_S - V_{S(AZ)}$ . Due to the ESD Zener diodes, the potential at pin INx rises almost to that potential, depending on the impedance of the connected circuitry <sup>1)</sup>. In the case the device was ON, prior to overvoltage, the ITS4075Q-EP-D remains ON. In case the ITS4075Q-EP-D was OFF, prior to overvoltage, the power transistor can be activated. In case the supply voltage is above  $V_{S(SC)}$  and below  $V_{DS(AZ)}$ , the output transistor is still operational and follows the input. If at least one channel is in ON-state, parameters are no longer within specified range and lifetime is reduced compared to the nominal supply voltage range. This especially impacts the short circuit robustness, as well as the maximum energy  $E_{AS}$  capability.  $Z_{GND}$  is recommended to be either a resistor (27  $\Omega$ ) in series to a diode or alternatively a 150  $\Omega$  power resistor.

<sup>1)</sup> Hence, the usage of external input resistors needs to be considered

Figure 16 Overvoltage Protection with External Components

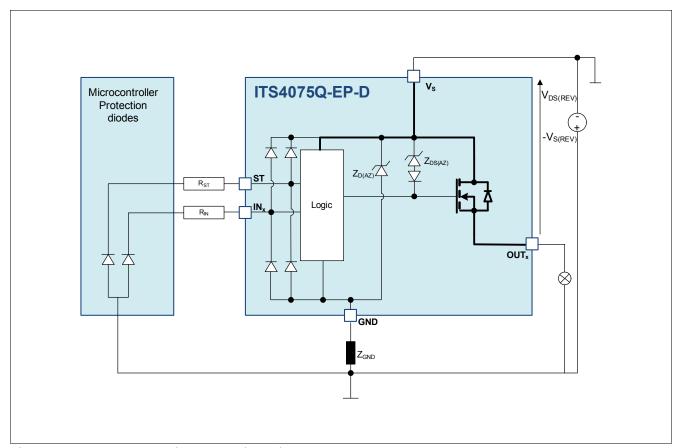

#### 6.3 **Reverse Polarity Protection**

In case of reverse polarity, the intrinsic body diodes of the affected power DMOS channels will dissipate power. The current flowing through the intrinsic body diode is limited externally by the load itself. But in addition the current into the ground path and the logic pins must be limited by an external resistor to the maximum allowed current described in **Chapter 4.1**. **Figure 17** shows a typical application.  $Z_{GND}$  resistor is used to limit the current through the Zener protection of the device.  $Z_{GND}$  is recommended to be either a resistor (~ 27  $\Omega$ ) in series to a diode or alternatively a power resistor ( $\sim$  150  $\Omega$ ).

During reverse polarity no protection functions are available.

Figure 17 **Reverse Polarity Protection with External Components**

## 6.4 Overload Protection

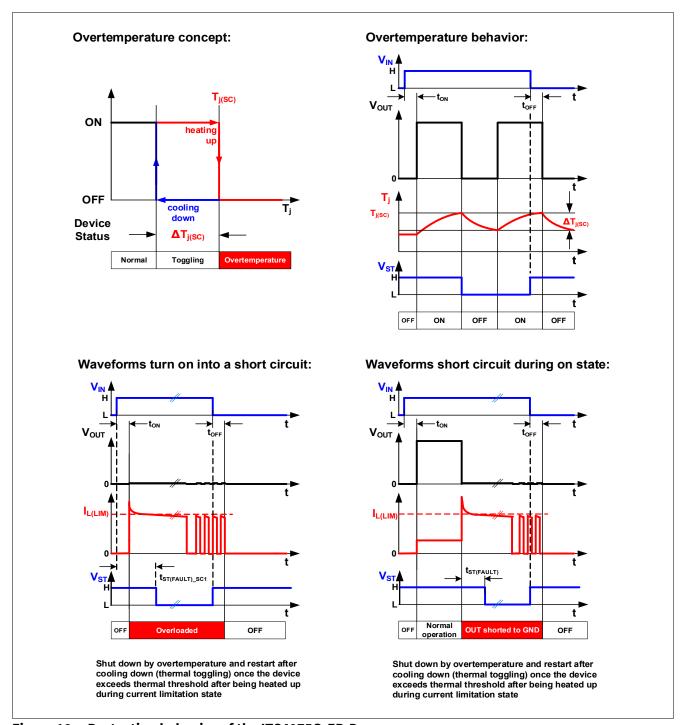

In case of overload, such as high inrush current of a cold lamp filament, or short circuit to ground, the ITS4075Q-EP-D offers a set of protection mechanisms which is illustrated in **Figure 18**.

## 6.4.1 Current Limitation

As a first step, the instantaneous power in the switch is contained within a safe range by limiting the current to the maximum current allowed in the switch  $I_{L(LIM)}$ . During this time, where the current is limited to  $I_{L(LM)}$ , the DMOS temperature is increasing caused by the voltage drop  $V_{DS}$  over the DMOS.

Figure 18 Protection behavior of the ITS4075Q-EP-D

## 75 mΩ Quad Channel Smart High-Side Power Switch

#### **Protection Functions**

## 6.4.2 Temperature Limitation in the Power DMOS

Each channel incorporates one temperature sensor. Activation of this temperature sensor will cause an overheated channel to switch OFF to prevent destruction. Any protective overtemperature shutdown event triggered within a channel is switching OFF the output of the corresponding channel until the temperature reaches an acceptable value again.

A restart functionality is implemented that is switching the channel ON again after the DMOS temperature has sufficiently cooled down.

# **6.5** Electrical Characteristics: Protection Functions

## Table 5 Electrical Characteristics: Protection Functions 1)

$V_{\rm S}$  = 8 V to 36 V,  $T_{\rm i}$  = -40°C to 150°C (unless otherwise specified).

Typical values are given at  $V_S = 24 \text{ V}$ ,  $T_i = 25 ^{\circ}\text{C}$

| Parameter                                          | Symbol                | Values Min. Typ. Max |     | S    | Unit | Note or                                              | Number  |

|----------------------------------------------------|-----------------------|----------------------|-----|------|------|------------------------------------------------------|---------|

|                                                    |                       |                      |     | Max. |      | <b>Test Condition</b>                                |         |

| Loss of Ground                                     |                       | <u>'</u>             |     |      |      |                                                      | '       |

| Output leakage current while GND disconnected      | / <sub>OUT(GND)</sub> | -                    | 0.1 | -    | mA   | <sup>2) 3)</sup> V <sub>S</sub> = 24 V               | P_6.5.1 |

| Reverse Polarity                                   | 1                     | <u>'</u>             |     |      |      |                                                      | '       |

| Drain source diode voltage during reverse polarity | $V_{DS(REV)}$         | -                    | 650 | 700  | mV   | $I_{L} = -2 \text{ A}$ $T_{j} = 150^{\circ}\text{C}$ | P_6.5.2 |

| Overvoltage                                        |                       |                      |     |      |      |                                                      |         |

| Overvoltage protection                             | $V_{S(AZ)}$           | 65                   | 70  | 75   | V    | <sup>4)</sup> / <sub>SOV</sub> = 5 mA                | P_6.5.3 |

| Overload Condition                                 |                       | ·                    |     |      |      |                                                      | ·       |

| Load current limitation                            | / <sub>L(LIM)</sub>   | 3.3                  | 4.1 | 4.9  | Α    | -                                                    | P_6.5.4 |

| Thermal shutdown temperature                       | $\mathcal{T}_{j(SC)}$ | 150                  | 175 | 200  | °C   | 3) _                                                 | P_6.5.6 |

| Thermal shutdown<br>hysteresis                     | $\Delta T_{j(SC)}$    | -                    | 30  | -    | K    | 3) _                                                 | P_6.5.7 |

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Integrated

protection functions are designed to prevent IC from destruction under fault conditions described in the data sheet.

Fault conditions are considered as "outside" normal operating range. Protection functions are designed neither for

continuous nor repetitive operation.

- 2) All pins are disconnected except  $V_S$  and OUT.

- 3) Not subject to production test; specified by design.

- 4) For practical cases it is recommended to place a resistor in the range of ≥ 27 Ω into the GND path to limit the GND current associated with overvoltage events.

# **6.6** Typical Performance Characteristics Protection Functions

# **Typical Performance Characteristics**

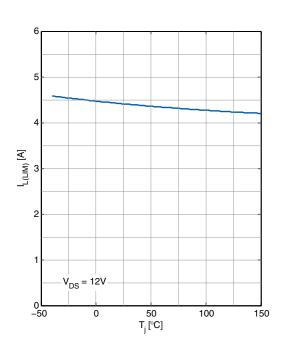

# Current Limit $I_{L(LIM)}$ versus Junction Temperature $T_j$

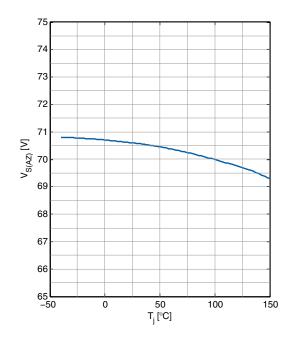

# Clamping Voltage $V_{\rm S(AZ)}$ versus Voltage $T_{\rm i}$

# $75\,m\Omega$ Quad Channel Smart High-Side Power Switch

**Diagnostic Functions**

# 7 Diagnostic Functions

For diagnosis purpose, the ITS4075Q-EP-D provides a digital signal at pin ST. This signal is called STATUS. The STATUS pin is realized as open drain output and must be connected to an external pull-up resistor. During normal operation the STATUS signal is logic "High" (H). During short circuit to ground or overtemperature condition the STATUS signal is logic "Low" (L). **Table 6** shows the corresponding truth table.

Table 6 Diagnostic Truth Table 1) 2)

| <b>Device Operation</b> | IN <sub>x</sub> | all IN <sub>i</sub> except IN <sub>x</sub> | OUT <sub>x</sub> | all OUT <sub>i</sub> except OUT <sub>X</sub> | ST | Comment          |

|-------------------------|-----------------|--------------------------------------------|------------------|----------------------------------------------|----|------------------|

| Normal Operation        | L               | L                                          | OFF              | OFF                                          | Н  | 3) External pull |

|                         | Н               | Н                                          | ON               | ON                                           | Н  | up at ST pin     |

|                         | Н               | don't care                                 | ON               | X                                            | Н  | -                |

|                         | L               | don't care                                 | OFF              | X                                            | Н  |                  |

| Short Circuit to GND    | Н               | don't care                                 | ON               | X                                            | L  | 3) 4)            |

| Overtemperature         | Н               | don't care                                 | OFF 5)           | X                                            | L  | 3)               |

- 1) Please refer to **Table 7** for more details.

- 2) Not subject to production test; specified by design.

- 3) "X" denotes status of OUT<sub>i</sub> according to the status of the corresponding input signals IN<sub>i</sub>.

- 4) Device not in specified  $R_{DS(ON)}$ .

- 5) Channel remains off during cooling-down phase of power stage; then channel tries to re-start.

# 7.1 Electrical Characteristics: Diagnostic Functions

## **Table 7** Electrical Characteristics: Diagnostic Functions

$V_S$  = 8 V to 36 V,  $T_j$  = -40°C to 150°C (unless otherwise specified). Typical values are given at  $V_S$  = 24 V,  $T_j$  = 25°C

| Parameter                                                                      | Symbol                     |      | Value | s               | Unit | Note or<br>Test Condition                                                                                                                                      | Number  |

|--------------------------------------------------------------------------------|----------------------------|------|-------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                                                |                            | Min. | Тур.  | Max.            |      |                                                                                                                                                                |         |

| Diagnostic Timing in Overload C                                                | ondition                   | - 11 | 1     |                 | "    |                                                                                                                                                                | 1       |

| STATUS settling time for overload detection                                    | t <sub>ST(FAULT)</sub>     | -    | 25    | _               | μs   | <sup>1)</sup> $V_S = 24 \text{ V}$ ;<br>load jump of $R_L$ :<br>$12\Omega \rightarrow 3.3 \Omega$ ;<br>Please refer to<br><b>Figure 18</b> for<br>more details | P_7.1.1 |

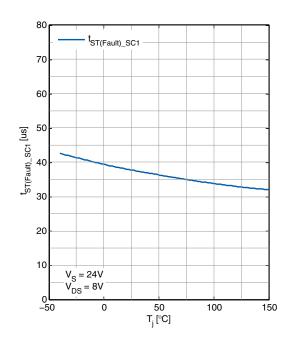

| STATUS settling time for channel start-up into existing overload <sup>2)</sup> | t <sub>ST(FAULT)_SC1</sub> | -    | 45    | 90              | μs   | V <sub>DS</sub> ≥ 8 V;<br>Please refer to<br>Figure 18 for<br>more details                                                                                     | P_7.1.9 |

| "Low" level STATUS voltage                                                     | $V_{\rm ST(L)}$            | -    | -     | 0.5             | V    | $I_{ST} = 1.6 \text{ mA}^{3)}$                                                                                                                                 | P_7.1.3 |

| "High" level STATUS voltage                                                    | $V_{\rm ST(H)}$            | 2    | -     | - <sup>4)</sup> | V    | $V_{\rm S} > V_{\rm ST}$                                                                                                                                       | P_7.1.4 |

| Current through STATUS pin (Operating Range)                                   | / <sub>ST</sub>            | -    | -     | 1.6             | mA   | V <sub>ST</sub> < 0.5 V                                                                                                                                        | P_7.1.5 |

# $75\,m\Omega$ Quad Channel Smart High-Side Power Switch

## **Diagnostic Functions**

# **Table 7 Electrical Characteristics: Diagnostic Functions** (cont'd)

$V_{\rm S}$  = 8 V to 36 V,  $T_{\rm j}$  = -40°C to 150°C (unless otherwise specified).

Typical values are given at  $V_S = 24 \text{ V}$ ,  $T_i = 25 ^{\circ}\text{C}$

| Parameter                                                                                                   | Symbol             |      | Value | s    | Unit | Note or<br>Test Condition          | Number  |

|-------------------------------------------------------------------------------------------------------------|--------------------|------|-------|------|------|------------------------------------|---------|

|                                                                                                             |                    | Min. | Тур.  | Max. |      |                                    |         |

| Channel fault detection interrogation time (Sequential Pulse Width)                                         | T <sub>x</sub>     | 3    | -     | 6    | μs   | $V_{\rm ST}$ < 0.5 V <sup>5)</sup> | P_7.1.2 |

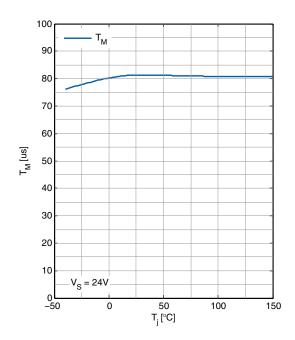

| STATUS signal "High" valid window after $T_x$ on fault affected channel                                     | $\mathcal{T}_{m}$  | 40   | 80    | 150  | μs   | 5) _                               | P_7.1.6 |

| Minimum delay between subsequent $T_x$ interrogation windows.                                               | T <sub>X-2-X</sub> | 200  | -     | -    | μs   | 1) _                               | P_7.1.8 |

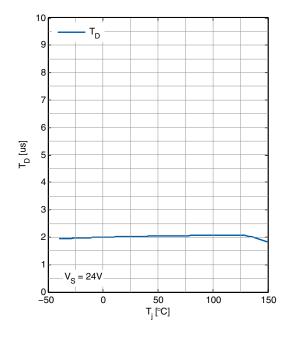

| Maximum delay time between $T_x$ ("High" to "Low") on fault affected channel and STATUS "High" signal $T_m$ | $\mathcal{T}_{D}$  | -    | 8     | -    | μs   | 1) _                               | P_7.1.7 |

- 1) Not subject to production test; specified by design.

- 2) This parameter describes the status settling time when a channel is switched on into an already existing overload condition. This parameter is referenced to the edge of the input pin IN that switches the channel into overload.

- 3) Levels referenced to device ground.

- 4) Depends on pull-up circuit that is used within application; maximum ratings of STATUS pin need to be respected.

- 5) Please refer to "Channel Fault Detection" on Page 31 for more details.

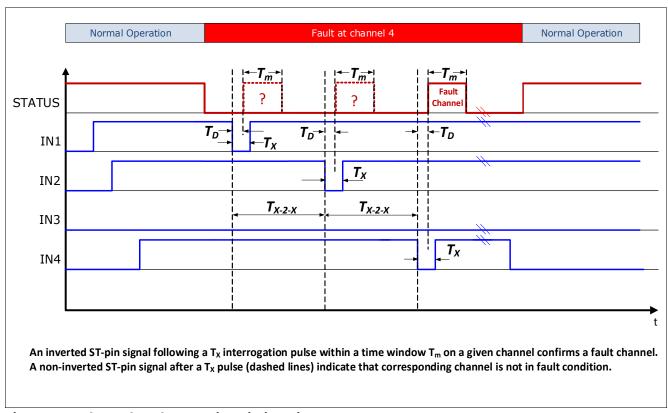

## 7.2 Channel Fault Detection

The ITS4075Q-EP-D is equipped with an intelligent channel fault detection system, which allows with the aid of a microcontroller to identify and communicate the channel on which the fault occurs.

During normal operation the STATUS pin is kept "High" by the external pull-up resistor as shown in Table 6. If - in case of a fault - the application requires the information on which of the channels the fault occurs when a "Low" STATUS is flagged, then the microcontroller can be programmed according to the sequence depicted as an example in Figure 19. The figure shows a case where three channels are active (these are channels 1, 2 and 4). Channel 3 in this example is not switched ON. During normal operation of channels 1, 2 and 4 the STATUS signal is "High". If a fault occurs, e.g. at channel 4, the STATUS signal goes "Low" to flag an error to the microcontroller. The microcontroller, in order to identify on which channel the fault occurs, must send a "Low" pulse sequentially to the input of each active channel, that is channels 1, 2 and 4 in this case. These pulses are shown in Figure 19 and their width is denominated  $T_x$ . The pulse width  $T_x$  should be between 3 µs up to 6 μs in order to make sure that the output does not react to this short inversion input level. The STATUS signal will go to "High" for a short period of time  $T_m$  only after the channel on which the fault occurs gets a "Low" pulse from the microcontroller, which in this case is after channel 4 receives a "Low" pulse for a time  $T_{\rm v}$ . In this way, by reading back whether an inversion of the STATUS flag within  $T_m$  occurs, the microcontroller is able to detect on which channel the fault occurs. Once the microcontroller receives this information it can start to switch OFF the channel on which the fault occurs (channel 4 in this case) via the corresponding input pin. For the delay time  $T_D$  between  $T_X$  going "Low" and  $T_M$  going "High" a value of 8  $\mu$ s needs to be taken into account.

# **Diagnostic Functions**

Figure 19 Channel Fault Detection Timing Diagram

**Diagnostic Functions**

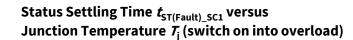

#### **Typical Performance Characteristics Diagnostic Functions** 7.3

**Typical Performance Characteristics**

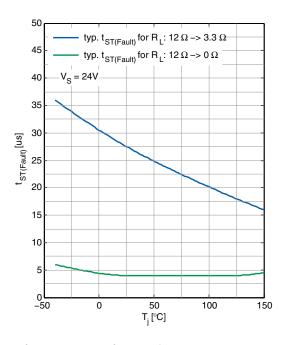

Status Settling Time  $t_{ST(FAULT)}$  versus Junction Temperature  $T_i$  (overload during ON)

Junction Temperature  $T_i$

Maximum Delay Time  $T_D$  ( $T_X$ 'H->L' to ST 'L->H') vs. ST "High" Valid window (after  $T_X$ )  $T_M$  versus Junction Temperature  $T_i$

**Input Pins**

# 8 Input Pins

# 8.1 Input Circuitry

The input circuitry is compatible with 3.3 V and 5 V microcontrollers as well as input levels up to  $V_S^{-1}$ . The concept of the input pin is to react to voltage thresholds which are referenced to device ground. An implemented Schmitt trigger avoids any undefined state if the voltage on the input pin is slowly increasing or decreasing. The output is either OFF or ON but cannot be in a linear or undefined state. **Figure 20** shows the electrical equivalent input circuitry. In case a channel is permanently not needed, the corresponding input pin shall not be left floating but tied with a serial resistor to device ground (not module ground). The recommended value for the serial resistor is  $2.2 \text{ k}\Omega$ .

Figure 20 Input Pin Circuitry

# 8.2 Input Pin Voltage

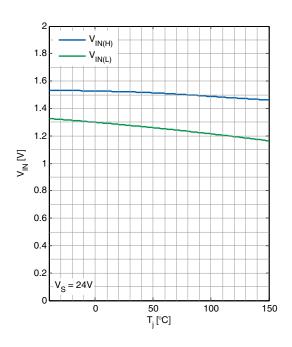

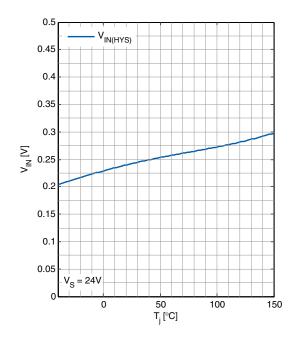

The input pin IN uses a comparator with hysteresis. Switching "ON / OFF" of the channels takes place in a defined region, set by the thresholds  $V_{\text{IN(L)}}$ , max and  $V_{\text{IN(H)}}$ , min. The exact values where the "ON" and "OFF" take place depend on the process, as well as on the temperature. To avoid cross talk and parasitic turn-ON or turn-OFF, a hysteresis is implemented. This ensures an improved immunity to noise.

<sup>1)</sup>  $V_{IN}$  must not exceed  $V_{S}$ . The relation  $V_{IN} \leq V_{S}$  must always be fulfilled.

# $75\,m\Omega$ Quad Channel Smart High-Side Power Switch

**Input Pins**

#### **Electrical Characteristics: Input Pins** 8.3

#### **Electrical Characteristics: Input Pins** Table 8

$V_{\rm S}$  = 8 V to 36 V,  $T_{\rm i}$  = -40°C to 150°C (unless otherwise specified). Typical values are given at  $V_S = 24 \text{ V}$ ,  $T_j = 25 ^{\circ}\text{C}$

| Parameter                        | Symbol             | Values |      |      | Unit | Note or                             | Number       |

|----------------------------------|--------------------|--------|------|------|------|-------------------------------------|--------------|

|                                  |                    | Min.   | Тур. | Max. |      | <b>Test Condition</b>               |              |

| Input Pins Characteristics       | <u>'</u>           | •      | *    |      |      |                                     | <del>-</del> |

| "Low" level input voltage range  | $V_{IN(L)}$        | -0.3   | _    | 0.8  | V    | _ 1)                                | P_8.3.1      |

| "High" level input voltage range | $V_{\rm IN(H)}$    | 2      | -    | 36   | V    | V <sub>S</sub> > V <sub>IN</sub> 1) | P_8.3.2      |

| Input voltage hysteresis         | $V_{\rm IN(HYS)}$  | _      | 250  | _    | mV   | _ 2)                                | P_8.3.3      |

| "Low" level input current        | / <sub>IN(L)</sub> | _      | 35   | 70   | μΑ   | V <sub>IN</sub> = 0.8 V             | P_8.3.4      |

| "High" level input current       | / <sub>IN(H)</sub> | _      | 43   | 70   | μΑ   | V <sub>IN</sub> = 24 V              | P_8.3.5      |

<sup>1)</sup> Levels referenced to device ground.

<sup>2)</sup> Not subject to production test; specified by design.

**Input Pins**

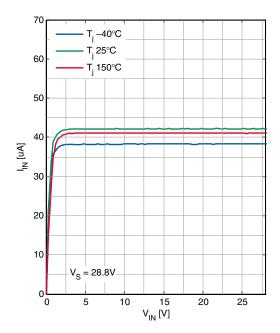

# 8.4 Typical Performance Characteristics Input Pins

# **Typical Performance Characteristics**

# Input Voltage thresholds $V_{\rm IN(L)}$ $V_{\rm IN(H)}$ versus Junction Temperature $T_{\rm i}$

Input Pin Current  $I_{\rm IN(H)}$  versus Supply Voltage  $V_{\rm S}$

# Input Voltage hysteresis $V_{\rm IN(HYS)}$ versus Junction Temperature $T_{\rm i}$

Input Pin Current  $I_{\text{IN(H)}}$  versus Junction Temperature  $T_{\text{i}}$

Note:

**Application Information**

# 9 Application Information

# 9.1 Application Diagram

application.

Linear VOUT External VIN Voltage Regulator components for e.g. IFX1763 Surge Immunity Microcontroller e.g. XMC4xxx I/C OUT1 IN<sub>1</sub> I/C OUT2 IN2 30 kΩ ST ITS4075Q-EP-D OUT3 IN3 I/C OUT4 IN4 тм GND GND External components for reverse polarity protection and overvoltage pulses. Recommended setup for Z<sub>GND</sub> is a diode for reverse polarity in series with a resistor of  $\sim$ 27 $\Omega$  to limit GND current during overvoltage spikes.

This is a very simplified example of an application circuit. The function must be verified in the real

Figure 21 Application Diagram with ITS4075Q-EP-D

In **Figure 21** above a simplified application diagram is shown where the inputs are galvanically isolated from  $V_S$  with optocouplers. Thanks to the fact that the input pins are 24 V capable they can be directly connected to the optocouplers. Reverse polarity protection can be achieved with external components. In this context it should be noted that input pins of channels which are permanently unused have to be tied with 2.2 k $\Omega$  resistance to device ground. In addition the TM-pin must be always be tied with a serial resistor to device ground in order to protect the pin in case of reverse polarity. The recommended value for this serial resistor is also 2.2 k $\Omega$ . For applications where no galvanic isolation is present between the external control circuitry (e.g microcontroller) and the input pins of the ITS4075Q-EP-D serial input resistors need to be placed in order to

# 75 m $\Omega$ Quad Channel Smart High-Side Power Switch

## **Application Information**

protect the external control circuitry and the input structures of the ITS4075Q-EP-D under fault conditions (like e.g. reverse polarity, loss of ground or overvoltage). For further details please also refer to the corresponding sections in **Chapter 6**. The recommended value for such serial input resistors is 10 k $\Omega$  however application specific optimized values may also depend on the individual application conditions as well as the applied external control circuitry / microcontroller.

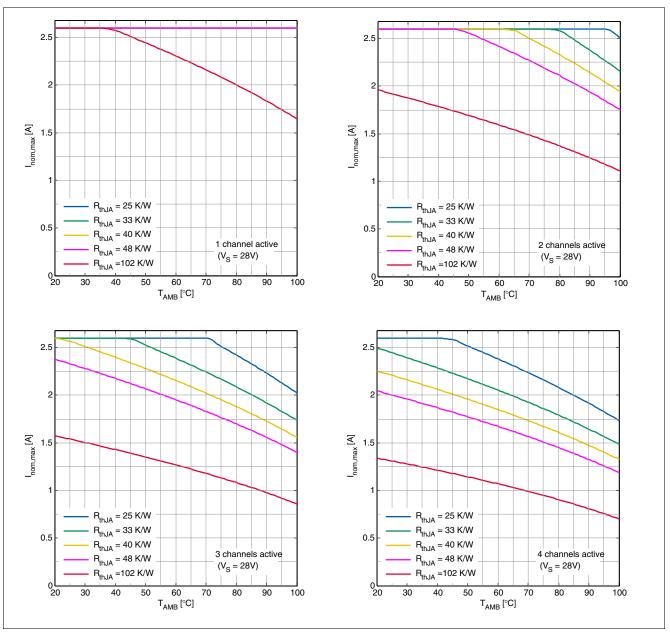

## 9.2 Thermal Considerations

If the cooling possibilities within the application are not sufficient to sink the heat of the dissipated power the junction temperature  $T_j$  of the device may exceed its maximum specified rating of 150°C and eventually trigger a thermal shutdown of the overheated channels to protect the device from destruction. Such thermal shutdown events may occur e.g. if one or more channels are operated in overload conditions that are causing the current limitation functionality to become active. If the current limitation of a channel becomes active the power dissipation will rise rapidly and in many cases lead to thermal shutdown events of the corresponding channels within short periods of time.

But also under nominal load conditions the power dissipation can become too high inside an application if it is applied at high environmental temperature  $T_{AMB}$  and if at the same time the cooling capability of the PCB is not sufficient. In general the cooling capability of an IC on a PCB within an application can be described for static cases by its thermal resistance from junction-to-ambient  $R_{thJA}$ . The thermal resistance  $R_{thJA}$  can be improved by adding cooling area on top- or bottom layer of the PCB or by adding inner layers that are connected to the  $V_S$  layer with thermal vias. Thermal vias show the best efficiency for heat distribution if directly placed underneath the exposed pad of the ITS4075Q-EP-D. The achievable values for  $R_{thJA}$  will differ from application to application. As reference simulation values of  $R_{thJA}$  for a set of standardized JEDEC cases are provided in **Chapter 4.4** "**Thermal Resistance**" on **Page 12**. Actual values in real applications naturally can be lower or higher.

For cases where the achievable thermal resistance  $R_{\rm thJA}$  and the hereof resulting thermal budget within an application is not sufficient for a given ambient temperature  $T_{\rm AMB}$  there is no other choice than to lower the load current to smaller numbers than the allowed maximum nominal current of 2.6 A. **Figure 22** illustrates how the derating of the nominal current due to excessive power dissipation can look like as a function of achievable  $R_{\rm thJA}$  and given  $T_{\rm AMB}$ . The graphs show how the thermal budget with its limiting condition  $T_{\rm j} = 150\,^{\circ}{\rm C}$  can be shared between the influencing parameters  $T_{\rm AMB}$ ,  $T_{\rm thJA}$ ,  $T_{\rm thJA}$ , depending on the number of active channels  $T_{\rm thJA}$ . Next to the standardized JEDEC cases mentioned above also an arbitrarily chosen value of  $T_{\rm thJA} = 25\,{\rm K/W}$  as additional reference for a highly optimized PCB solution is included in the graphs.

The calculation of the thermal budget displayed in the graphs follows simple rules as given in the equations below. It should be noted that the calculation is restricted to static cases where the resulting  $\mathcal{T}_{AMB}$  and  $\mathcal{T}_{j}$  have reached a stable equilibrium.

$$T_{i} = T_{AMB} + R_{thJA} \times P_{DISS}$$

(9.1)

(9.2)

$$P_{DISS} = I_{Load}^2 \times R_{DS(ON)} \times n_{CH} + V_S \times I_{GND}$$

# **Application Information**

Figure 22 Possible thermal derating of nominal current due to insufficient cooling capability of PCB

**Package Outlines**

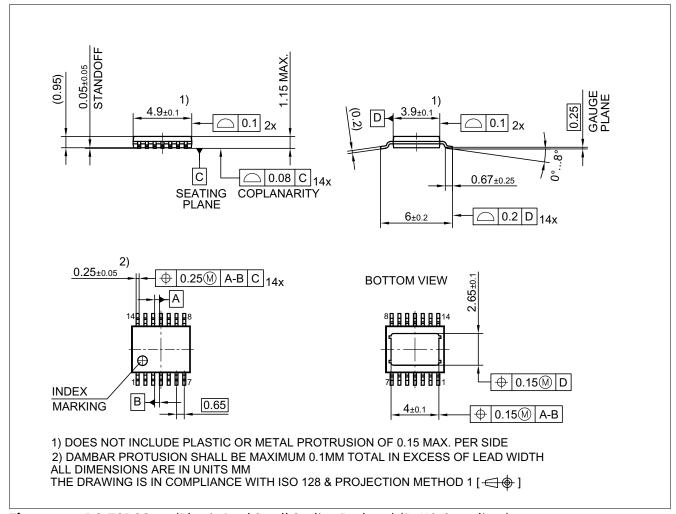

# 10 Package Outlines

Figure 23 PG-TSDSO-14 (Plastic Dual Small Outline Package) (RoHS-Compliant)

### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

# $75\,m\Omega$ Quad Channel Smart High-Side Power Switch

**Revision History**

# 11 Revision History

| Revision | Date       | Changes                                   |

|----------|------------|-------------------------------------------|

| 1.01     | 2018-06-14 | Data Sheet Rev. 1.01<br>Editorial changes |

| 1.0      | 2018-05-22 | Data Sheet (Initial Release)              |

### Trademarks

Edition 2018-06-14 Published by Infineon Technologies AG 81726 Munich, Germany

© 2018 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com

### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

Please note that this product is not qualified according to the AEC Q100 or AEC Q101 documents of the Automotive Electronics Council.

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Switch ICs - Power Distribution category:

Click to view products by Infineon manufacturer:

Other Similar products are found below:

TCK111G,LF(S FPF1018 DS1222 TCK2065G,LF SZNCP3712ASNT3G MIC2033-05BYMT-T5 MIC2033-12AYMT-T5 MIC2033-05BYM6-T5 SLG5NT1437VTR SZNCP3712ASNT1G DML1008LDS-7 KTS1670EDA-TR KTS1640QGDV-TR KTS1641QGDV-TR FPF2260ATMX U6513A MIC2012YM-TR TPS2104DBVR TPS22958NDGKR MIC2098-1YMT-TR MIC94062YMT TR MP6231DN-LF MIC2015-1.2YM6 TR MIC2075-2YM MIC94068YML-TR SIP32461DB-T2-GE1 NCP335FCT2G TCK105G,LF(S AP2411S-13 AP2151DSG-13 AP2172MPG-13 MIC94094YC6-TR MIC94093YC6-TR MIC94064YC6-TR MIC2505-1YM MIC94305YMT-TR MIC94085YFT-TR MIC94081YFT-TR MIC94042YFL-TR MIC94041YFL-TR MIC2005-1.2YM6-TR TPS2032QDRQ1 NCP333FCT2G BTS3050TFATMA1 NCP331SNT1G TPS2092DR TPS2063DR VNV35N07-E MIC2008YML-TR MIC2040-1YMM