## **XDP<sup>™</sup> Digital Power**

Data Sheet Revision 1.0

**Quality Requirement Category: Industrial**

#### **Features**

- Universal AC input (90 305 VAC) or DC input (90 305 VDC)

- Applicable power range of 20 W to 150 W

- Small number of external parts optimizes Bill of Materials (BOM) and form factor

- High efficiency (> 90%)

- Multicontrol mode (Constant Current (CC)/Constant Voltage (CV)/Limited Power (LP)) reduces required product variety

- · Important parameters can be configured after manufacturing

- Low harmonic distortion (Total Harmonic Distortion (THD) < 15%)</li>

- Low output ripple current

- Integrated startup cell ensures fast time to light (< 250 ms)</li>

- Adaptive Temperature Protection

- Ambient operating temperature -40 °C to 85 °C

- Automatic switching between Quasi-Resonant Mode (QRM) and Discontinuous Conduction Mode (DCM)

- Wide output voltage range

- Pulse Width Modulation (PWM) dimming control

- Output dimming by analog reduction of driving current down to 5%

For safe operation, the XDPL8220 contains a comprehensive set of protection features:

- Output overvoltage protection (open load)

- Output undervoltage protection (output short)

- VCC over- and undervoltage lockout

- Input over- and undervoltage protection

- Bus over- and undervoltage protection

- Overcurrent protection for Power Factor Correction (PFC) and Flyback (FB) stage

# **Applications**

Integrated Electronic Control Gear (ECG) for Light Emitting Diode (LED) luminaires

#### **Description**

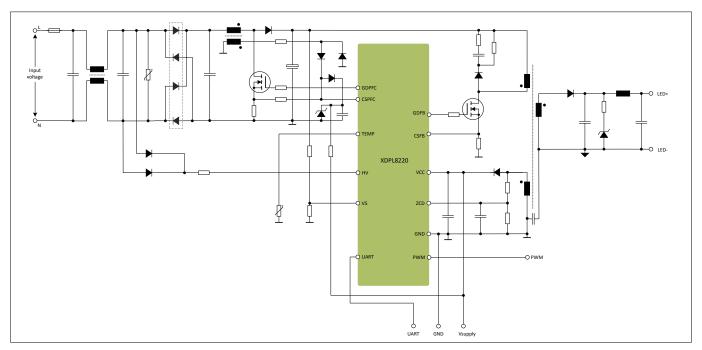

Figure 1 Typical Application for XDPL8220

| Product Type | Package   |

|--------------|-----------|

| XDPL8220     | PG-DSO-16 |

## **Description**

XDPL8220 is a highly integrated next-generation device combining a boundary mode *PFC* plus a quasi-resonant *FB* controller with primary-side regulation. The integration of these functions enables saving of external parts and optimizes performance by harmonized operation of the two stages.

XDPL8220 uses a constant on-time scheme with a **THD** improvement algorithm to provide a high power factor and excellent **THD** performance.

With its unique control scheme of **CV**, **CC** and **LP**, the **LED** driver designer is provided with a large degree of flexibility and can utilize the system hardware to its limits.

The on-chip *One Time Programmable Memory (OTP)* memory has an area for parameters that control the behavior of the circuit, e. g. the output current or the maximum output power. This enables the user of the device to create a platform concept with significantly fewer different hardware versions while still covering the same application range.

The two-stage approach reduces any variation in the output current (flicker) to a non-visible level. By separating the **PFC** from the power conversion part (**FB**), both stages operate in a more stable manner and require fewer margins, which has a positive influence on the cost.

Lighting requires more and more 24/7 operation, making it necessary to have a stand-by mode with short wakeup times and low power consumption. The power consumption of less than 100 mW of the XDPL8220-based systems defines the new standard for stand-by power in lighting **ECG**s.

XDPL8220 enables adaptive temperature protection using either the internal sensor or an external **Negative Temperature Coefficient Thermistor (NTC)**, or both.

Futureproof flexibility with application-oriented programmable operating windows enables management of **LED** generations and portfolio complexity.

## Table of contents

## **Table of contents**

|         | Features                            | 1  |

|---------|-------------------------------------|----|

|         | Applications                        | 1  |

|         | Description                         |    |

|         | Table of contents                   | 3  |

| 1       | Functional Block Diagram            | 5  |

| 2       | Pin Configuration                   | 6  |

| 3       | Functional Description              | 8  |

| 3.1     | PFC Controller Features             |    |

| 3.1.1   | Shared CS/ZCD Function              |    |

| 3.1.2   | Quasi-resonant Mode                 | 9  |

| 3.1.3   | Bus Voltage Sensing                 | 10 |

| 3.1.4   | Input Voltage Sensing               | 11 |

| 3.1.5   | Control Scheme                      |    |

| 3.1.5.1 | Startup                             | 12 |

| 3.1.6   | Multimode Control Scheme            | 13 |

| 3.1.6.1 | Frequency Law                       | 13 |

| 3.1.6.2 | THD Optimization                    | 14 |

| 3.1.7   | Peak Current Limitation             | 14 |

| 3.1.8   | Bus Undervoltage Protection         | 14 |

| 3.1.9   | Bus Overvoltage Protection          | 15 |

| 3.1.10  | Input Undervoltage Protection       |    |

| 3.1.11  | Input Overvoltage Protection        | 15 |

| 3.1.12  | Other PFC Protections               | 16 |

| 3.2     | Flyback Controller Features         | 17 |

| 3.2.1   | Primary Side Regulation             | 17 |

| 3.2.1.1 | Primary Side Current Sensing        | 18 |

| 3.2.1.2 | Primary Side Output Voltage Sensing | 19 |

| 3.2.1.3 | Flyback Bus Voltage Sensing         | 20 |

| 3.2.1.4 | Output Current Calculation          |    |

| 3.2.1.5 | Output Control Scheme               | 21 |

| 3.2.1.6 | Multimode Scheme                    | 22 |

| 3.2.2   | Flyback Startup                     | 23 |

| 3.2.3   | Protection Features                 | 24 |

| 3.2.3.1 | Primary Overcurrent Protection      | 24 |

| 3.2.3.2 | Output Undervoltage Protection      | 24 |

| 3.2.3.3 | Output Overvoltage Protection       | 24 |

| 3.2.3.4 | Output Overcurrent Protection       |    |

| 3.2.3.5 | Output Overpower Protection         | 25 |

# Table of contents

| 3.2.3.6 | Other Flyback Protections                 | 25 |

|---------|-------------------------------------------|----|

| 3.3     | General Controller Features               | 26 |

| 3.3.1   | External Temperature Sensing              | 26 |

| 3.3.2   | Adaptive Temperature Protection           | 26 |

| 3.3.3   | PWM Dimming Interface                     | 27 |

| 3.3.4   | Protection Features                       | 28 |

| 3.3.4.1 | Overtemperature Protection                | 28 |

| 3.3.4.2 | VCC Undervoltage Protection               | 29 |

| 3.3.4.3 | VCC Overvoltage Protection                | 29 |

| 3.3.4.4 | Other General Controller Protections      | 29 |

| 3.3.5   | Protection Reactions                      | 29 |

| 3.3.5.1 | Auto restart                              | 30 |

| 3.3.5.2 | Fast Auto Restart                         | 30 |

| 3.3.5.3 | Latch Mode                                | 31 |

| 3.3.5.4 | Stop Mode                                 |    |

| 4       | Design Support                            | 32 |

| 4.1     | Design Procedure                          | 32 |

| 4.2     | List of Configurable Parameters           | 32 |

| 4.3     | List of Fixed Parameters                  | 39 |

| 5       | Electrical Characteristics and Parameters | 40 |

| 5.1     | Package Characteristics                   | 40 |

| 5.2     | Absolute Maximum Ratings                  | 40 |

| 5.3     | Operating Conditions                      | 41 |

| 5.4     | DC Electrical Characteristics             | 42 |

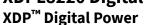

| 6       | Package Dimensions                        | 55 |

| 7       | References                                | 56 |

|         | Abbreviations                             | 56 |

|         | Revision History                          | 59 |

|         | Trademarks                                | 60 |

4

**Functional Block Diagram**

# 1 Functional Block Diagram

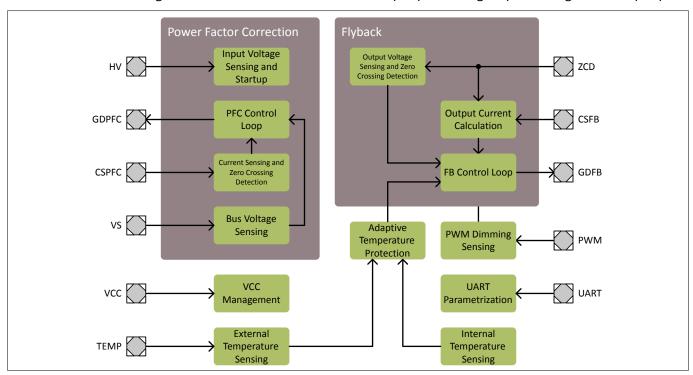

The functional block diagram shows the basic data flow from input pins via signal processing to the output pins.

Figure 2 XDPL8220 Simplified Functional Block Diagram

**Pin Configuration**

#### **Pin Configuration** 2

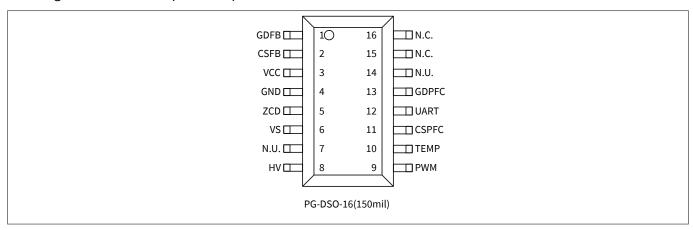

Pin assignments and basic pin description information are shown below.

Figure 3 **Pinning of XDPL8220**

**Pin Definitions and Functions** Table 1

| Name  | Pin | Туре | Function                                                                                                                                                                                                                                                                 |

|-------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GDFB  | 1   | 0    | Gate driver for <b>FB</b> :                                                                                                                                                                                                                                              |

|       |     |      | The GDFB pin is an output for directly driving a power MOSFET of the <i>FB</i> stage.                                                                                                                                                                                    |

| CSFB  | 2   | I    | Current sensing for <b>FB</b> :                                                                                                                                                                                                                                          |

|       |     |      | The CSFB pin is connected to an external shunt resistor and the source of the power MOSFET of the <b>FB</b> stage.                                                                                                                                                       |

| VCC   | 3   | I    | Voltage supply                                                                                                                                                                                                                                                           |

| GND   | 4   | -    | Power and signal ground                                                                                                                                                                                                                                                  |

| ZCD   | 5   | I    | Zero-crossing detection of the <b>FB</b> :                                                                                                                                                                                                                               |

|       |     |      | The ZCD pin is connected to an auxiliary winding of the <i>FB</i> stage for zero-crossing detection as well as primary-side output voltage and backup bus voltage sensing for safety.                                                                                    |

| VS    | 6   | I    | Bus voltage sensing                                                                                                                                                                                                                                                      |

| N.U.  | 7   | -    | Not used. Externally to be connected to GND.                                                                                                                                                                                                                             |

| HV    | 8   | I    | High voltage:  The HV pin is connected to the rectified input voltage via an external resistor.  An internal 600 V HV startup-cell is used to initially charge VCC. In addition, sampled high-voltage sensing is also used for synchronization with the input frequency. |

| PWM   | 9   | I    | <b>PWM</b> dimming: The PWM pin is used as a dimming input.                                                                                                                                                                                                              |

| TEMP  | 10  | 1    |                                                                                                                                                                                                                                                                          |

| TEMP  | 10  |      | External temperature sensor:  Measurement of external temperature using an NTC.                                                                                                                                                                                          |

| CSPFC | 11  | 1    | Current sensing for <b>PFC</b> :                                                                                                                                                                                                                                         |

|       |     |      | The CSPFC pin is connected to an external shunt resistor and the source of the power MOSFET of the <i>PFC</i> stage.                                                                                                                                                     |

**Pin Configuration**

## Table 1 Pin Definitions and Functions (continued)

| Name  | Pin | Туре | Function                                                                                                                                   |

|-------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| UART  | 12  | I/O  | Universal Asynchronous Receiver Transmitter (UART) communication: The UART pin is used for the UART interface to support parameterization. |

| GDPFC | 13  | 0    | Gate driver for <b>PFC</b> : The GDPFC pin is an output for directly driving a power MOSFET of the <b>PFC</b> stage.                       |

| N.U.  | 14  | -    | Not used. Externally to be connected to GND.                                                                                               |

| N.C.  | 15  | -    | Not connected.                                                                                                                             |

| N.C.  | 16  | -    | Not connected.                                                                                                                             |

**Functional Description**

#### **Functional Description** 3

This chapter provides a summary of the integrated functions and features, and describes the relationships between them. The parameters and equations are based on typical values at  $T_A = 25$  °C.

XDPL8220 is a digital dual-stage **PFC** and **FB** controller IC supporting **PWM** dimming functionality. Both stages use configurable multimode operation to select the best mode of operation for every operation condition. Multimode operation automatically switches between Quasi-Resonant Mode, switching in valley n (QRMn) and

XDPL8220 features a comprehensive set of configurable protection modes to detect fault conditions. XDPL8220 provides a high degree of flexibility in design-in of the application. A *Graphic User Interface (GUI)* tool supports users in the configuration of the operational and protection parameters.

**Functional Description**

#### 3.1 **PFC Controller Features**

The **PFC** stage ensures high power quality by maximizing the power factor and minimizing harmonic distortion.

The **PFC** stage operates in **Quasi-Resonant Mode**, **switching in valley 1 (QRM1)** and **QRMn**, to support low load conditions and ensure efficient operation.

The **PFC** stage is implemented as a boost converter. It drains a sinusoidal current from the single-phase line supply and provides stabilized *Direct Current (DC)* voltage at the internal bus voltage rail. The power factor of the single-phase line supply is almost one. Fluctuations in line voltage as well as voltage drops of short duration are compensated.

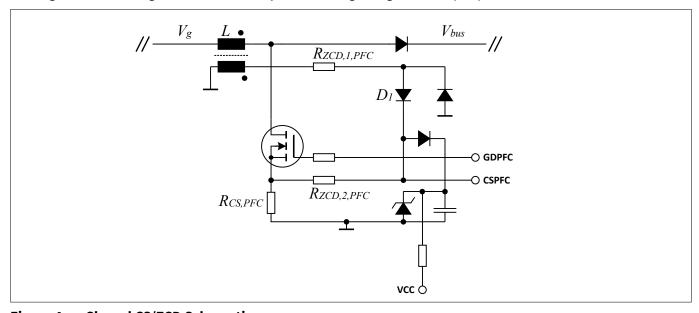

#### 3.1.1 Shared CS/ZCD Function

The **PFC** stage makes use of combined CS/ZCD functionality at the CSPFC pin.

During the gate driver on-time the pin acts as a current sense (CS), while during the gate driver off-time the pin acts as a zero-crossing-detector (ZCD). The CS senses the on-time current and implements overcurrent limitation; the ZCD exploits the quasi-resonant function to minimize conduction losses.

The CSPFC pin is connected via a resistor divider composed of R<sub>ZCD,1,PFC</sub> and R<sub>ZCD,2,PFC</sub> and a set of diodes to an auxiliary winding of the **PFC** choke inductor. It is used for detecting the valleys of the quasi-resonant oscillation to turn on the PFC MOSFET based on the desired valley computed by the multimode PFC control. The diode D<sub>1</sub> allows positive voltage at the CSPFC pin as the valley detection is implemented by the internal hysteretic comparator with a positive reference of nominal THR<sub>HYS</sub> for falling edges. The CSPFC pin senses the drain source current of the switching MOSFET. The CS voltage is measured after a programmable blanking time after turn-on of the switch. An appropriate current sensing resistor R<sub>CS,PFC</sub> is selected on the basis of the maximum current flowing in the switching MOSFET and the dynamic voltage range of the input pin CSPFC.

Figure 4 Shared CS/ZCD Schematic

#### 3.1.2 **Quasi-resonant Mode**

The quasi-resonant mode maintains a high efficiency level.

For **PFC** operating in **QRM1**, the main switch is turned on with a constant on-time for a line and load condition, while the off-time/demagnetization time varies within an Alternating Current (AC) half-cycle depending on the instantaneously rectified AC input voltage Vg. Subsequently, the switching frequency varies within each AC halfcycle with the lowest switching frequency at the peak of the AC input voltage and the highest switching frequency near the zero crossings of the input voltage. A new switching cycle starts immediately when the first QR valley is reached.

## XDP™ Digital Power

#### **Functional Description**

**QRM1** is ideal for full-load operation, where the on-time is large. However, the on-time reduces at light loads, resulting in very high switching frequencies, particularly near the zero crossings of the input voltage. The high switching frequency will increase switching losses, resulting in poor efficiency at light loads. The PFC multimode control can lower the switching frequency by selecting further valleys to achieve QRM2 up to N<sub>vallev,max,PFC</sub> operation. The switching frequency is limited within a defined range and the efficiency at light loads improves.

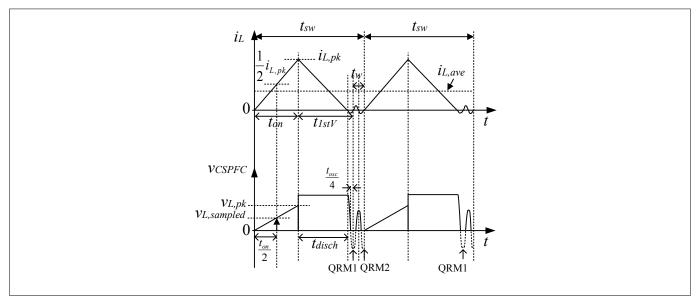

Figure 5 **PFC QRM2 Waveforms**

The equations for the quasi-resonant operation are shown below, where t<sub>w</sub> is an additional delay in each switching cycle when selecting subsequent valleys after the first QR valley and n is the valley number in QRMn.

$$i_{L,pk} = \frac{V_g \cdot t_{on}}{L}$$

$$t_{disch} = \frac{i_{L,pk} \cdot L}{V_{bus} - V_g}$$

$$t_{1stV} = t_{disch} + t_{osc}/2$$

$$t_w = t_{osc} \cdot (n-1)$$

$$t_{sw} = t_{on} + t_{1stV} + t_w$$

$$t_{off} = t_{1stV} + t_w$$

#### **Equation 1**

#### 3.1.3 **Bus Voltage Sensing**

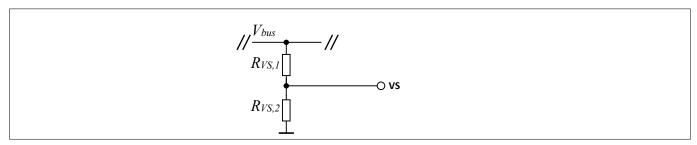

The bus voltage is measured at the VS pin.

The VS pin implements **PFC** bus voltage sensing for bus voltage regulation. The bus voltage is scaled down using a simple resistor divider. A capacitor could in certain cases be added at the pin to ground to filter highfrequency switching noise. The bus voltage sensing is a low leakage input and no additional measures are needed to reduce the current consumption.

### **Functional Description**

Figure 6 **Bus Voltage Sensing Schematic**

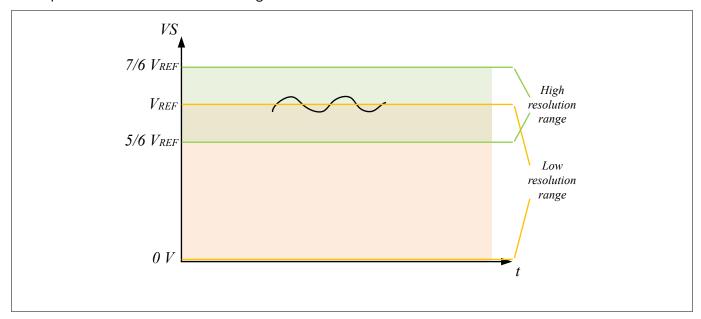

The Analog-to-Digital Converter (ADC) input at the VS pin utilizes two voltage ranges. The wider voltage range from 0 to V<sub>RFF</sub> results in lower resolution. The narrower voltage range from 5/6 V<sub>RFF</sub> to 7/6 V<sub>RFF</sub> gives better voltage resolution. Steady state operation therefore normally takes place in the high-resolution range and soft start operation in the low-resolution range.

Figure 7 **Sensing Ranges**

#### 3.1.4 **Input Voltage Sensing**

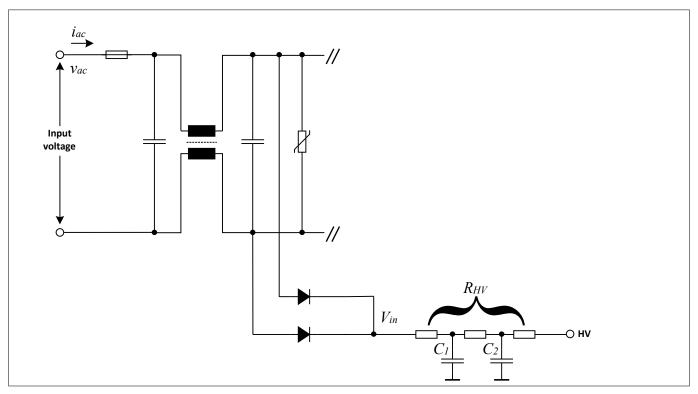

The input voltage is sensed using the HV pin.

The input voltage is used for protection, to generate **AC** zero-crossing signals and to detect the AC/DC source.

#### **Functional Description**

Figure 8 **Input Voltage Sensing Schematic**

The R<sub>HV</sub> probing resistor is usually split into two, or three or more resistors for safety purposes. In fact in case of a resistor being shorted by damage, the high resistive path is maintained by the other resistors avoiding fire, shock to the user and further damage to the application.

A RC filter structure making use of the split resistors filters the unwanted noise for the high voltage input voltage measurement. The filtering effect is kept high due to the usage of the high impedance split resistors and the addition of small capacitance high voltage capacitors.

#### 3.1.5 **Control Scheme**

The **PFC** bus voltage controller embeds a PIT1 controller that calculates a control output representing load and line conditions from the bus voltage error signal.

The bus voltage controller implements regulation during both soft start and steady states.

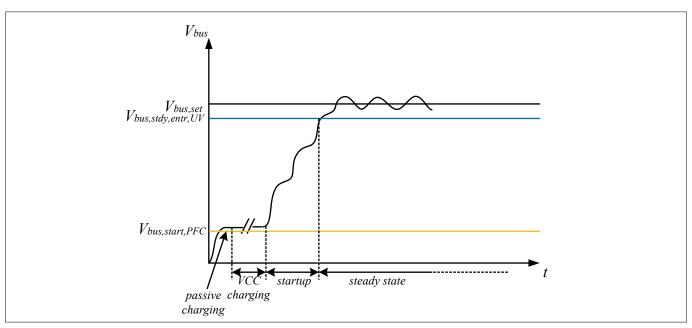

#### 3.1.5.1 Startup

At system startup, the **PFC** initiates a soft start to minimize the switching stress for the power MOSFET, diode and inductor.

The soft start is executed when the bus voltage is higher than the  $V_{bus,start,PFC}$  threshold. This is the brown-in condition. The soft start is aborted if the input under- or overvoltage protection fire. During soft start, the **PFC** stays in **QRM1** operation. Once the V<sub>bus,stdy,entr,UV</sub> threshold is reached, the steady state **PFC** operation starts.

# (in

#### **Functional Description**

Figure 9 V<sub>bus</sub> Soft Start and Regulation

#### 3.1.6 Multimode Control Scheme

The multimode control scheme provides a **PFC** option to dynamically change the operating point by switching between the MOSFET  $V_{ds}$  voltage valleys while following a frequency law and applying **THD** optimization.

The multimode controller uses two different modes of operation:

- **QRM1**: This operation maximizes the efficiency by switching on the 1st valley of the **PFC** ZCD signal. This ensures zero current switching with a minimum of switching losses.

- QRMn: The controller will extend to the next switching valley after the 1st valley to control the bus voltage

following a frequency law.

The multimode optimization consists of the following:

- Frequency law

- THD optimization

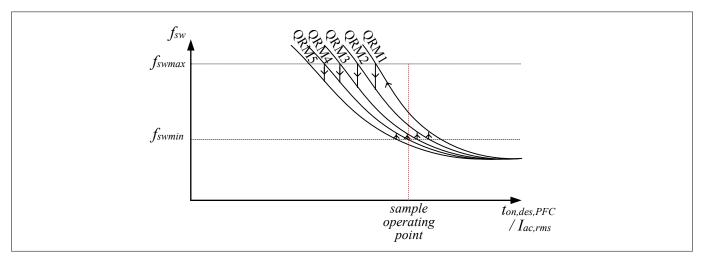

#### 3.1.6.1 Frequency Law

The output of the **PFC** PIT1 bus voltage controller gives the desired on-time, which is constant within each **AC** half cycle. A **PFC** is used to emulate a resistive load  $r_e$  to the **AC** input such that  $i_{ac}$  follows  $v_{ac}$  in both wave shape and phase. The output of the **PFC** bus voltage controller  $t_{on,des,PFC}$  is inversely proportional to the emulated resistive load  $r_e$  such that a smaller  $r_e$  or a higher  $I_{ac,rms}$  will give a larger  $t_{on,des,PFC}$ . Thus,  $t_{on,des,PFC}$  is different for the same load at different line voltages and is proportional to the RMS input current  $I_{ac,rms}$ .

The rule for selecting  $\mbox{\it QRMn}$  is based on the frequency law. A maximum switching frequency  $f_{swmax}$  and a minimum switching frequency  $f_{swmin}$  are defined for the complete  $t_{on,des,PFC}/I_{ac,rms}$  range. The frequency law ensures that the switching frequency is within the desired frequency range. The frequency law is depicted in the figure below.

## XDP™ Digital Power

#### **Functional Description**

Figure 10 **PFC Frequency Law**

As long as the **PFC** controller operating mode fulfills the frequency law, the operating mode does not change. The QR-valley is increased when the highest frequency limit is reached. The QR-valley is decremented when the lowest frequency limit is reached.

To ensure good ZCD detection before the ZCD signal becomes too small in amplitude, only the first up to N<sub>vallev,max,PFC</sub> valleys operations are supported.

#### 3.1.6.2 **THD Optimization**

**THD** optimization reduces the **THD** in the case of light loads and in the case of high **AC** input voltages.

The selection of higher valleys helps to reduce the switching frequency but it also distorts the input current waveform with constant on-time control and thus affects the PFC THD performance. The multimode PFC control also consists of a THD optimization algorithm that optimizes the applied on-time in order to ensure good input current shaping and improved **PFC THD** performance.

#### 3.1.7 **Peak Current Limitation**

The peak current through the switching MOSFET is read via the **PFC** shunt resistor R<sub>CS,PFC</sub> to limit the maximum current through the MOSFET, the choke, and freewheeling diode so as to avoid potential hard failure or lifetime

The OCP causes the current to be limited to cases in which an overcurrent condition occurs. **Overcurrent** Protection Level 1 (OCP1) is implemented by hardware. If the voltage V<sub>CS,PFC</sub> across the shunt resistor exceeds the overcurrent threshold V<sub>CS,OCP1, PFC</sub> for longer than the blanking time t<sub>blank,OCP1,PFC</sub>, the MOSFET is turned off. The MOSFET is turned on when ZCD occurs or the PFC maximum period time-out signal triggers the start of the next switching cycle. Overcurrent Protection Level 2 (OCP2) is a second-level overcurrent protection implemented by hardware. The OCP2 overcurrent threshold is fixed. The OCP2 blanking time is t<sub>blank.OCP2.PFC</sub>.

#### 3.1.8 **Bus Undervoltage Protection**

Undervoltage detection of the bus voltage V<sub>bus</sub> is provided by measurement using the VS pin.

The bus voltage is compared to a configurable undervoltage protection threshold V<sub>bus UV</sub>. If the threshold is exceeded for longer than the blanking time t<sub>blank.Vbus.UV</sub>, the protection will be triggered.

**XDP<sup>™</sup> Digital Power**

**Functional Description**

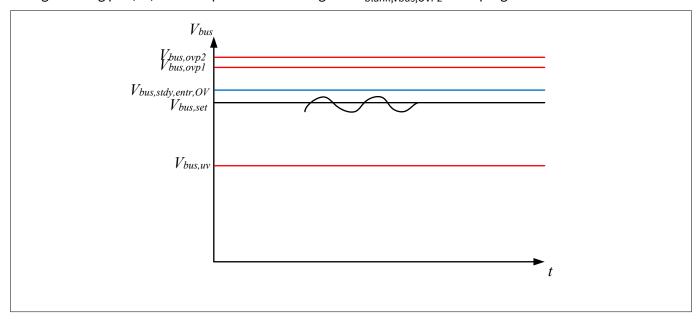

3.1.9

Overvoltage detection of the bus voltage V<sub>bus</sub> is provided by the measurement using the VS pin.

**Bus Overvoltage Protection**

The bus voltage is compared to a configurable overvoltage protection threshold V<sub>bus.OVP1</sub> in *Firmware (FW)*. If a threshold is exceeded for longer than the blanking time t<sub>blank,Vbus,OVP1</sub>, the gate driver stops. The gate driver operation is resumed when V<sub>bus</sub> falls below V<sub>bus,stdv,entr,OV</sub>.

V<sub>bus OVP2</sub> is implemented in *Hardware (HW)* and it is fixed at a voltage which is represented as 2.8 V at the bus voltage sensing pin (VS). The HW permits a blanking time t<sub>blank,Vbus,OVP2</sub> to be programmed.

Figure 11 V<sub>bus</sub> protections

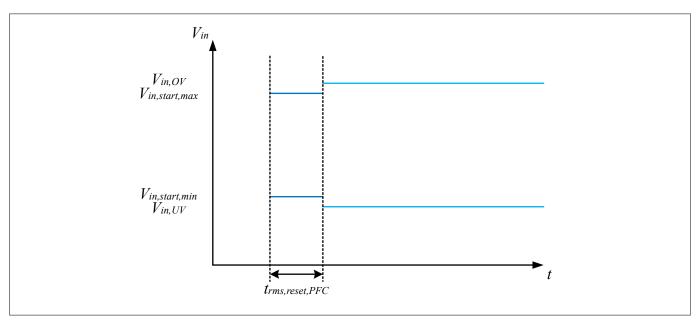

#### 3.1.10 **Input Undervoltage Protection**

Undervoltage detection of the input voltage V<sub>in</sub> is provided by measurement using the HV pin.

Values of V<sub>in,rms</sub> are compared to a configurable input undervoltage protection threshold V<sub>in,UV</sub>. If the threshold is exceeded for longer than the blanking time t<sub>blank,Vin,UV</sub>, the protection will be triggered. XDPL8220 features a configurable startup threshold V<sub>in.start.min</sub> to create hysteresis for flicker-free operation before the second stage starts switching. After startup checks when t<sub>rms,reset,PFC</sub> expires, the comparison is restored to the threshold value V<sub>in.UV</sub>.

#### 3.1.11 **Input Overvoltage Protection**

Overvoltage detection of the input voltage V<sub>in</sub> is provided by measurement using the HV pin.

Values of V<sub>in.rms</sub> are compared to a configurable input overvoltage protection threshold V<sub>in.OV</sub>. If the threshold is exceeded for longer than the blanking time t<sub>blank,Vin,OV</sub>, the protection will be triggered. XDPL8220 features a configurable startup threshold V<sub>in.start.max</sub> to create hysteresis for flicker-free operation before the second stage starts switching. After startup checks when t<sub>rms,reset,PFC</sub> expires, the comparison is restored to the threshold value V<sub>in.OV</sub>.

In the csv file the input OVP shall be disabled by default. Note:

### **XDP<sup>™</sup> Digital Power**

### **Functional Description**

Figure 12 V<sub>in</sub> protections

### 3.1.12 Other PFC Protections

#### **CS Resistor Short Protection**

The input circuit breaker (fuse) shall be chosen appropriately in order to protect in case of current-sense resistor short.

#### **CS Resistor Open Protection**

The external circuitry for shared CS/ZCD pulls the CSPFC pin high in case of CS resistor missing so that the OCP2 protection is triggered.

#### **CSPFC Pin Short to GND Protection**

In case of CSPFC pin short to ground the lack of quasi-resonant oscillations shall trigger the CCM Protection.

#### **CCM Protection**

Continuous conduction mode (CCM) operation may occur during **PFC** startup for a limited time. It is considered as a failure in the system only if CCM operation of the **PFC** converter is observed over a longer period of time. The **PFC** converter may run into CCM operation for a longer period due to a shorted bypass diode, a heavy load step that is out of specification or very low input voltage outside the normal operating range.

When CCM occurs, the magnetizing current in the *PFC* choke does not have the chance to decay to zero before the MOSFET turns on. No quasi-resonant oscillation will be seen at the ZCD signal before the maximum switching period time-out is reached that turns the MOSFET on. This turn-on event without ZCD oscillation is monitored to protect the *PFC* converter from continuous CCM operation. The CCM protection is implemented by firmware.

If any quasi-resonant oscillation is seen at the ZCD signal for longer than the blanking time  $t_{blank,CCM,PFC}$ , the protection is triggered.

#### **Soft Start Failure**

The soft start may take a long time, potentially never reaching steady state operation due to heavy loads or very low input voltages. If t<sub>start,PFC</sub> reaches t<sub>start,max,PFC</sub> before the soft start has ended, the protection is triggered.

**Functional Description**

### 3.2 Flyback Controller Features

The **FB** stage provides primary side control that avoids secondary side control feedback loop circuitry usually needed in isolated power converters. This approach supports a low part count to reduce costs.

The **FB** stage features multi-mode operation and it selects the best mode of operation based on operating conditions.

#### 3.2.1 Primary Side Regulation

The **FB** in XDPL8220 provides primary side control of output current and output voltage. No external feedback components are necessary for the current control as the primary side regulation control loop is fully integrated.

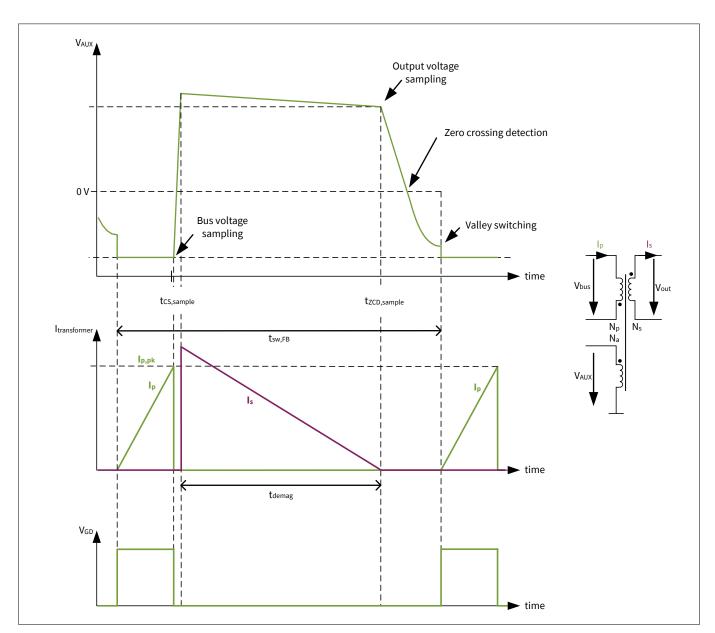

Figure 13 shows typical current and voltage waveforms of the FB application operating in QRM1.

In **DCM**, the next switching cycle will not start at the first valley of V<sub>AUX</sub>, but is instead delayed. As a consequence, the switching losses in **DCM** will be higher.

The primary peak current  $I_{p,pk}$ , the period of conduction of the output diode  $t_{demag}$  and the switching period  $t_{sw,FB}$  are used to calculate the average output current.

The voltage signal V<sub>AUX</sub> of the auxiliary winding of the transformer contains information on the reflected output voltage V<sub>out</sub>. The reflected output voltage is measured at the ZCD pin using a resistor divider.

# infineon

#### **Functional Description**

Figure 13 Typical Waveforms of a Flyback Converter

## 3.2.1.1 Primary Side Current Sensing

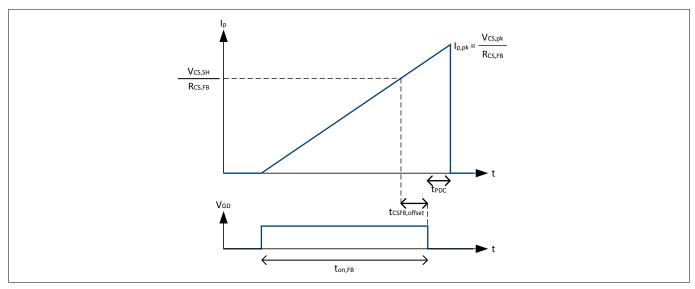

The primary side peak current  $I_{p,pk}$  is controlled by the control loop using the  $V_{CS,OCP1}$  level at the CSFB pin. This control scheme ensures suppression of any variation in the bus voltage.

Several delays exist from the time at which the  $\mathit{OCP1}$  level  $V_{CS,OCP1}$  is exceeded at the CSFB pin until the gate switches off and the transformer current finally reaches its peak value. For a higher accuracy, the primary peak current  $V_{CS,SH}$  is sampled a fixed time before turn-off of the gate. The primary side peak current is used to calculate the secondary side current and for protection. The propagation delay compensation parameter  $t_{PDC}$  allows optimization of the accuracy of the primary side peak current:

$$I_{p, \, pk} = \frac{V_{CS, \, SH}}{R_{CS, \, FB}} \cdot \frac{t_{on, \, FB} + t_{PDC}}{t_{on, \, FB} - t_{CSFB, \, offset}}$$

#### **Equation 2**

### **XDP<sup>™</sup> Digital Power**

### **Functional Description**

Note: If an RC low pass filter is added in front of the CSFB pin, the related low pass filter delay has to be included in t<sub>PDC</sub>.

Figure 14 Propagation Delay Compensation for accurate Primary Peak Current Calculation

### 3.2.1.2 Primary Side Output Voltage Sensing

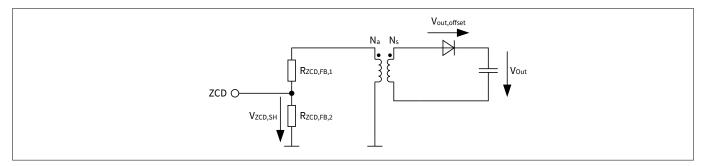

The output voltage is determined by measuring the reflected output voltage on the auxiliary winding. A resistor divider adapts the voltage to the operating range of the ZCD pin.

The output voltage is measured at the ZCD pin using the voltage  $V_{ZCD,SH}$  at the end of the demagnetization time at the time  $t_{ZCD,sample}$ . The voltage measured at the ZCD pin, the dimensioning of the resistor dividers  $R_{ZCD,FB,1}$  and  $R_{ZCD,FB,2}$ , transformer turns  $N_s$  and  $N_a$  as well as an offset  $V_{out,offset}$  (caused by the secondary diode, for example) are used to calculate the output voltage  $V_{out}$  as follows:

$$V_{\text{out}} = V_{\text{ZCD, SH}} \frac{{}^{R}\text{ZCD, FB, 1} + {}^{R}\text{ZCD, FB, 2}}{{}^{R}\text{ZCD, FB, 2}} \frac{{}^{N}\text{s}}{{}^{N}\text{a}} + V_{\text{out, offset}}$$

#### **Equation 3**

V<sub>out</sub> is used for *Primary Side Regulated (PSR)* control loops in *CV* and *LP* modes as well as for output over- and undervoltage protections.

Figure 15 Primary Side Output Voltage Sensing using ZCD S&H

Note: Any relation between VCC and ZCD in self-supplied applications can be decoupled – e.g. by adding a linear regulator for VCC.

**XDP<sup>™</sup> Digital Power**

#### **Functional Description**

Attention: Please note that the time ( $t_{demag}$ ) has to be longer than 2.0  $\mu$ s to ensure that the reflected output voltage can be sensed correctly at the ZCD pin.

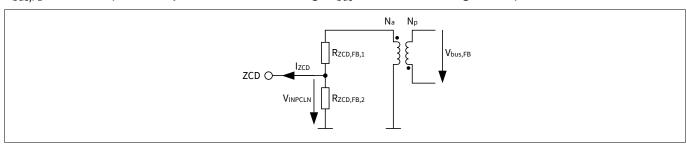

### 3.2.1.3 Flyback Bus Voltage Sensing

The **FB** can sense the bus voltage using the reflection of bus voltage on the auxiliary winding while the gate is turned on. A resistor divider adapts the negative voltage to the operating range of the ZCD pin. This second measurement path is required to protect against component failures in the VS measurement path (open loop protection for the **PFC** stage).

The reflected bus voltage appears as a negative voltage at  $V_{AUX}$ . This negative voltage is internally clamped at the ZCD pin to the negative voltage  $V_{INPCLN}$ . The internal clamping current  $I_{ZCD}$  is measured at the end of the ontime at the time  $t_{CS,sample}$ . The measured clamping current of the ZCD pin, the dimensioning of the resistor dividers  $R_{ZCD,FB,1}$  and  $R_{ZCD,FB,2}$  as well as the number of transformer turns  $N_a$  and  $N_p$  are used to calculate the bus voltage  $V_{bus,FB}$  as follows:

$$V_{\text{bus, FB}} = \left( \left( I_{\text{ZCD}} + \frac{V_{\text{INPCLN}}}{R_{\text{ZCD, FB, 2}}} \right) R_{\text{ZCD, FB, 1}} + V_{\text{INPCLN}} \right) \frac{N_p}{N_a}$$

#### **Equation 4**

V<sub>bus.FB</sub> is used for plausibility checks with the voltage V<sub>bus</sub> as measured using the VS pin.

Figure 16 Voltage Sensing using ZCD Clamp Current

#### 3.2.1.4 Output Current Calculation

The output current is calculated based on the primary side peak current and the timing of the switching cycle.

The output current  $I_{out}$  is calculated using the duration of conduction of the output diode  $t_{demag}$ , the switching period  $t_{sw,FB}$  as well as the number of transformer turns  $N_p$ ,  $N_s$  and the transformer coupling  $K_{coupling}$ . The following equation is valid both in *QRM1* and *DCM*:

$$I_{\text{out}} = \frac{1}{2}I_{p, \text{pk}} \cdot \frac{N_p}{N_s} \cdot K_{\text{coupling}} \cdot \frac{t_{\text{demag}}}{t_{\text{sw, FB}}}$$

#### **Equation 5**

The coupling of the transformer can be approximated using the transformer primary inductance  $L_p$  and the transformer primary leakage inductance  $L_{p,lk}$  as follows:

$$K_{\text{coupling}} \approx \frac{L_p}{L_p + L_{p, lk}}$$

#### **Equation 6**

The calculated current I<sub>out</sub> is used for the control loop in the modes **CC** and **LP**. The calculated current is also used for output overcurrent protection.

# XDP™ Digital Power

**Functional Description**

#### 3.2.1.5 **Output Control Scheme**

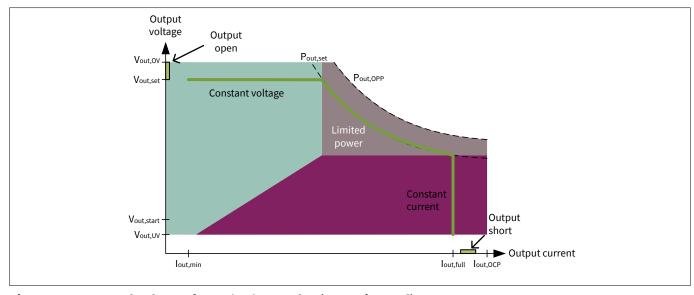

The XDPL8220 includes three different control schemes for a CC, CV or LP output.

Different use cases require the controller to operate according to different operation schemes:

- In the case of typical LED strings, the forward voltage of the LED string determines the output voltage of the driver. XDPL8220 operates in CC and drives a constant output current I<sub>out,full</sub> to the load. The forward voltage of the connected LED string has to be below a configurable maximum value Vout.set

- In the case of LED loads including a power stage (e.g. Infineon BCR linear regulators or Infineon DC/DC buck ILD2111), XDPL8220 operates in CV, ensuring a constant voltage V<sub>out,set</sub> to the load. The total output current drawn by the load has to be below a configurable maximum value Iout.full.

- In the case of a high output current setpoint Iout, full and an overly long LED string which exceeds the configurable power limit P<sub>out,set</sub>, XDPL8220 operates in *LP* to ensure that the power limit of the driver is not exceeded. The controller reduces the output current automatically, ensuring light output without any interruption even for overly long LED strings. The forward voltage of the connected LED string has to be below a configurable maximum value V<sub>out,set</sub>.

For every update of the control loop, the control scheme is selected on the basis of the current operation conditions (output voltage V<sub>out</sub> and output current I<sub>out</sub>) and their distance to the three limiting setpoints (V<sub>out,set</sub>, P<sub>out,set</sub> and I<sub>out,full</sub>):

- For **CC** schemes, the internal reference current I<sub>out,full</sub> is weighted according to thermal management and a dimming curve to yield I<sub>out.set</sub>. The calculated output current I<sub>out</sub> is compared with the weighted reference current I<sub>out,set</sub> to generate an error signal for the output current.

- For CV schemes, the sensed output voltage V<sub>out</sub> at the ZCD pin is compared to a reference voltage V<sub>out,set</sub> to generate an error signal for the output voltage.

- For LP schemes, the output current is limited to a maximum of I<sub>out,set</sub> = P<sub>out,set</sub> / V<sub>out</sub>.

Out of these three schemes, for each step the most critical error is selected (see *Figure 17*):

- 1. If any setpoint is exceeded, the largest error for power decrease is selected to bring the controller back to the desired operating point as quickly as possible.

- 2. If the current operating conditions are below all three setpoints, the smallest error for power increase is selected to avoid overshooting any setpoint.

The selected error signal is fed into a compensator to control the gate driver switching parameters (i.e. duty cycle and frequency) for the power MOSFET of the FB.

Control Scheme for CC/CV/LP Modes (Non-Dimmed)

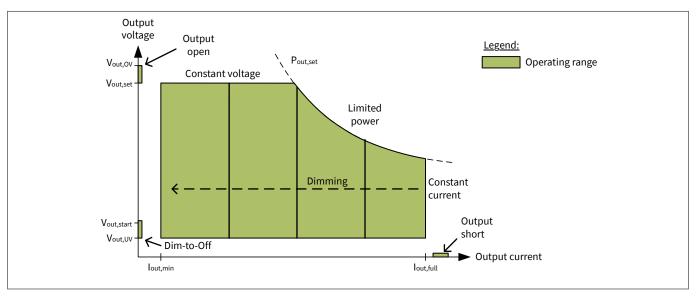

In dimming cases, the output current setpoint I<sub>out,set</sub> is located between I<sub>out,min</sub> and I<sub>out,full</sub> and varies according to the sensed **PWM** duty cycle D<sub>DIM</sub>. Dimming can be visualized by moving the vertical line for the output current setpoint in Figure 18 from right to left.

#### **XDP<sup>™</sup> Digital Power**

#### **Functional Description**

Note: An operation in limited power mode can cause dimmer dead-travel until the controller enters constant current mode.

Figure 18 Control Scheme for CC/CV/LP Modes (including Dimming)

One or more of the output control schemes can be deactivated by configuration of the setpoints. Some examples are given below:

- The *LP* scheme is not active for P<sub>out,set</sub> > V<sub>out,set</sub> \* I<sub>out,full</sub>. For such a configuration, the controller will only select between a *CC* and *CV* scheme.

- The CV scheme is not active for V<sub>out.set</sub> = V<sub>out.OV</sub> as the output overvoltage protection will be triggered.

- The CC scheme is not active for I<sub>out,full</sub> = I<sub>out,OC</sub> as the output overcurrent protection will be triggered.

#### 3.2.1.6 Multimode Scheme

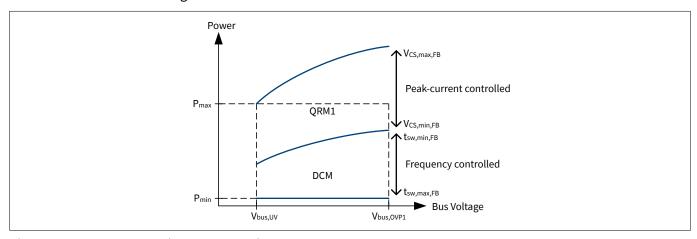

The control loop of XDPL8220 uses two different switching modes. **QRM1** is optimized for high efficiency at high loads while **DCM** is used in light load conditions.

Figure 19 Flyback Multimode Operation Scheme

- **QRM1**: This mode maximizes the efficiency by switching on the 1st valley of the V<sub>AUX</sub> signal. This ensures zero current switching with a minimum of switching losses. The power is controlled by regulating the primary peak current using V<sub>CS.OCP1</sub>.

- **DCM**: This mode is used if V<sub>CS,OCP1</sub> has reached its minimum value V<sub>CS,min,FB</sub>. To allow lower output power, the controller extends the switching period later than the 1st valley.

#### **XDP<sup>™</sup> Digital Power**

#### **Functional Description**

The minimum power is limited by the transformer primary inductance  $L_p$ , maximum switching period  $t_{sw,max,FB}$  and minimum primary peak current  $I_{p,pk,min}$ :

$$P_{\min} = \frac{1}{2} \cdot L_p \cdot I_{p, \text{pk}, \min}^2 \cdot \frac{1}{t_{\text{sw}, \text{max}, FB}}$$

#### **Equation 7**

The minimum primary peak current I<sub>p.pk.min</sub> is restricted by:

$$I_{p, \text{pk, min}} = t_{\text{demag, min}} \cdot \frac{N_p}{N_s} \cdot \frac{V_{\text{out, OV}}}{L_p}$$

#### **Equation 8**

Note:

If the load drops below the minimum load of  $P_{\min}$ , the output voltage will rise up to the output overvoltage threshold  $V_{\text{out,OV}}$  and trigger the protection. An auto-restart can be used to keep the output voltage close to  $V_{\text{out,OV}}$  until the load increases again.

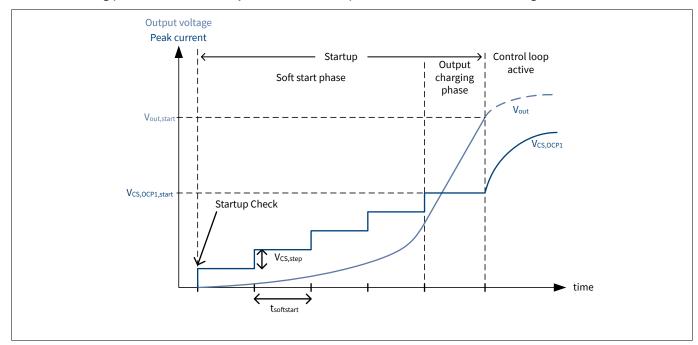

### 3.2.2 Flyback Startup

After startup, the **FB** of the XDPL8220 initiates a soft start to minimize the switching stress for the power MOSFET and secondary diode.

The cycle-by-cycle current limit is increased in steps of  $V_{CS,step}$  with a configurable duration  $t_{softstart}$  for each step. After the final  $V_{CS,OCP1,start}$  limit level has been reached, the output will be charged until the minimum output voltage  $V_{out,start}$ , which ensures self-supply has been reached. At this condition, *Continuous Conduction Mode (CCM)* protection as well as output undervoltage protection are activated and the control loop takes over. The starting point for the control loop is to operate in DCM at lowest switching frequency and shortest on-time. These switching parameters avoid any overshoot of output current for short LED string in dimmed conditions.

Figure 20 Flyback Startup Sequence

**XDP<sup>™</sup> Digital Power**

**Functional Description**

#### 3.2.3 Protection Features

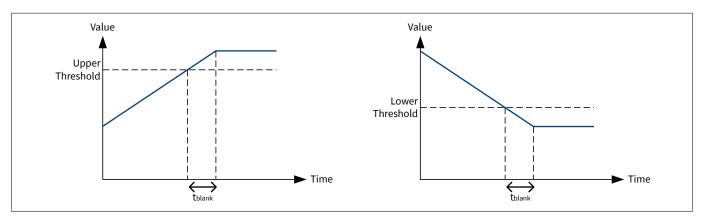

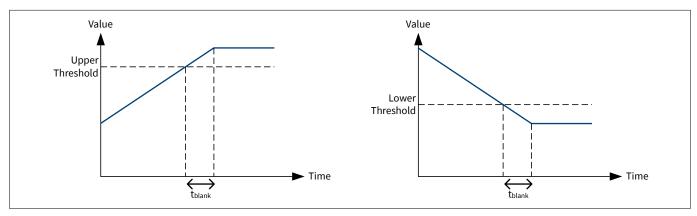

Protections ensure the operation of the controller under restricted conditions. Protections are triggered if fault conditions are present longer than the blanking times configured for each protection<sup>3</sup>. The controller will react to a triggered protection as configured.

Attention: The controller may continue operation after exceeding protection thresholds because of blanking times. All protection thresholds have to be set with respect to tolerances, blanking times and worst case transients.

Figure 21 Blanking Times cause Excess of Threshold

## 3.2.3.1 Primary Overcurrent Protection

The primary side overcurrent protection implemented in hardware covers fault conditions like a short in the transformer primary winding or an open CS pin.

The primary side current is compared to a configurable overcurrent protection threshold  $V_{CS,OCP2}$ . If the threshold is exceeded for longer than the blanking time  $t_{OCP2,FB}$ , the protection will be triggered.

## 3.2.3.2 Output Undervoltage Protection

In the case of a short in the output, the output voltage may drop to a very low level. Detection of undervoltage in the output voltage V<sub>out</sub> is enabled by measurement of the reflected voltage at the ZCD pin.

During operation, the output voltage is compared to a configurable undervoltage protection threshold  $V_{out,UV}$ . If the threshold is exceeded for longer than the blanking time  $t_{blank,out,UV}$ , the protection will be triggered. This protection threshold  $V_{out,UV}$  is disabled during startup.

During startup, the protection operates differently: In case the FB cannot charge the output voltage to  $V_{out,start}$  during a timeout of  $t_{start,max,FB}$ , the protection will be triggered. This timeout starts when the FB is started.

Note: The startup threshold  $V_{\text{out,start}}$  has to be configured over and above the undervoltage threshold  $V_{\text{out,UV}}$  to allow undershoots at startup which may occur, especially for resistive loads.

## 3.2.3.3 Output Overvoltage Protection

In case of a open output, the output voltage may rise to a high level. Overvoltage detection of the output voltage V<sub>out</sub> is provided by measurement at the ZCD pin.

The output voltage is compared to a configurable overvoltage protection threshold  $V_{out,OV}$ . If the threshold is exceeded for longer than the blanking time  $t_{blank,out,OV}$ , the protection will be triggered.

<sup>&</sup>lt;sup>3</sup> except VCC undervoltage protection

#### **Functional Description**

The blanking time  $t_{blank,Vout,OV}$  should be set to the minimum value to minimize overshoots of the Note:

output voltage above the protection threshold.

This protection is usually triggered if the output is open or the output load drops below the minimum Note:

$load P_{min}$ .

#### **Output Overcurrent Protection** 3.2.3.4

Overcurrent detection in the output current I<sub>out</sub> is provided on the basis of the calculated output current.

The calculated output current is compared to a configurable overcurrent protection threshold I<sub>out.OC</sub>. If the threshold is exceeded for longer than the blanking time t<sub>blank.out.OC</sub>, the protection will be triggered.

#### **Output Overpower Protection** 3.2.3.5

Overpower detection in the output power P<sub>out</sub> is provided on the basis of the calculated output power.

The calculated output power is compared to a configurable overpower protection threshold Pout.OP. If the threshold is exceeded for longer than the blanking time t<sub>blank.out.OP</sub>, the protection will be triggered.

#### 3.2.3.6 **Other Flyback Protections**

XDPL8220 includes additional protections to ensure the integrity and correct flow of the firmware.

- A hardware weak pull-up protects against an open CSFB pin.

- A firmware watchdog protects against the CSFB pin becoming shorted to GND.

- A firmware state monitor supervises correct operation of the flyback in **QRM1** or **DCM**. A protection is triggered if the flyback enters **CCM**.

- A firmware check ensures that the **PFC** has already boosted the bus voltage sufficiently before the **FB** starts.

- A firmware plausibility check ensures that the bus voltage measurement using the VS pin is correct.

#### XDP™ Digital Power

**Functional Description**

#### 3.3 **General Controller Features**

XDPL8220 provides general features for firmware task scheduling, VCC control and temperature control which are independent of the target application.

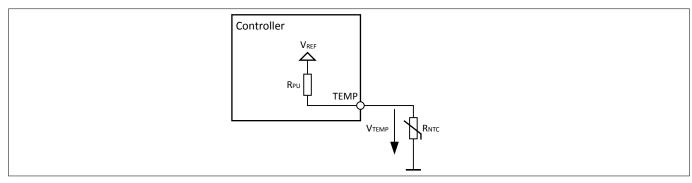

#### **External Temperature Sensing** 3.3.1

The external temperature is measured by measuring the voltage of an NTC with respect to the internal V<sub>RFF</sub> voltage.

**External Temperature Sensing using NTC**

The controller calculates the resistance of the NTC based on the measured voltage V<sub>Temp</sub>, the internal reference voltage V<sub>RFF</sub> and the internal pull-up resistance R<sub>PU</sub>:

$$R_{\rm NTC} = \frac{v_{\rm Temp} \cdot R_{\rm PU}}{v_{\rm REF} - v_{\rm Temp}}$$

#### **Equation 9**

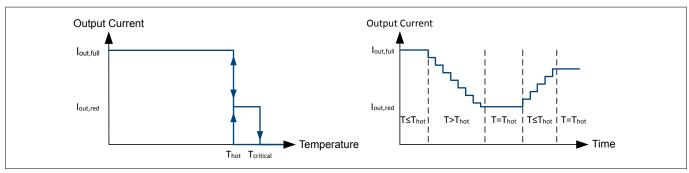

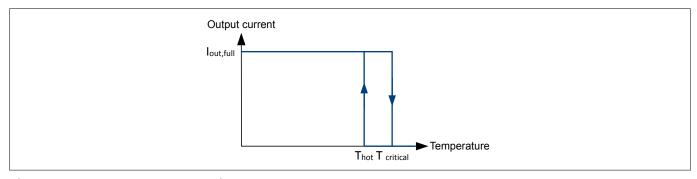

#### 3.3.2 Adaptive Temperature Protection

XDPL8220 offers adaptive temperature protection using internal and/or external temperature sensors. This feature reduces the output current according to temperature to protect the load and driver against overtemperature.

Whenever the temperature T<sub>hot</sub> is exceeded, the current is gradually reduced from the maximum current I<sub>out.set</sub>, as shown in *Figure 23*. If the temperature drops below T<sub>hot</sub>, the output current is increased again. This allows the controller to ensure operation at or below a temperature of T<sub>hot</sub>.

If a reduction down to a minimum current I<sub>out,red</sub> is not able to compensate for any continued increase in temperature, XDPL8220 will eventually trigger overtemperature protection if T<sub>critical</sub> is exceeded. If the controller is configured to react with auto-restart to the overtemperature protection, it will only restart after the temperature dropped below That.

Figure 23 **Adaptive Temperature Protection**

#### **Functional Description**

Note:

Please note that the internal temperature sensor can only protect external components which have sufficient thermal coupling to XDPL8220. The external temperature sensor can be used to protect the temperature of external components (e.g. power MOSFETs or linear regulators).

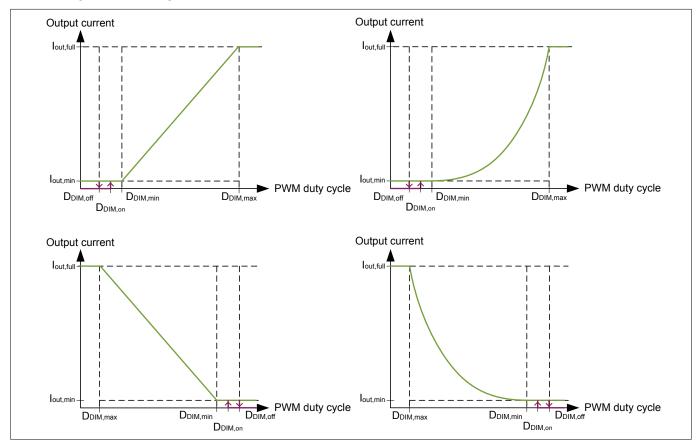

#### 3.3.3 **PWM Dimming Interface**

The duty cycle sensed at the PWM pin is used to determine the output current level. The XDPL8220 can be configured to use either a linear or a quadratic dimming curve. Either normal or inverted dimming curves can be selected.

Figure 24 shows the relationship of the PWM duty cycle to the output current target value. Configurable levels D<sub>DIM,min</sub> and D<sub>DIM,max</sub> ensure that the minimum current I<sub>out,min</sub> and maximum current I<sub>out,set</sub> can always be achieved, thereby making the application robust against component tolerances.

An optional hysteresis can be enabled for the sensing of the PWM signal. This hysteresis can suppress jitter in the PWM signal. Any change of the PWM duty cycle within the hysteresis will not affect the output current.

Figure 24 **Selectable Dimming Curves**

Using the optional Dim-to-Off feature, the light output can be stopped without removal of input voltage. In Dimto-Off, the controller will enter auto-restart operation to minimize power consumption. The auto-restart recharges the output voltage to a minimum output voltage of V<sub>out,start</sub> to measure the PWM duty cycle. With this feature, the output voltage can be maintained in a specific range by configuration of the startup voltage V<sub>out,start</sub> and auto-restart time t<sub>AR</sub>, and by dimensioning of an active or passive output bleeder. If V<sub>out,start</sub> is configured to be low enough below the minimum forward voltage of the LED string, the LEDs will show no light in this state.

Either an active or passive output bleeder is required to allow the controller to maintain the output Note: voltage if the Dim-to-Off feature is enabled.

#### **Functional Description**

Dim-to-Off is entered if the *PWM* duty cycle exceeds the configurable threshold D<sub>DIM,off</sub> (see purple line in *Figure* 24). As soon as the duty cycle exceeds D<sub>DIM,on</sub>, the controller will start to continuously regulate output voltage or output current again.

#### 3.3.4 Protection Features

Protections ensure the operation of the controller under restricted conditions. Protections are triggered if fault conditions are present longer than the blanking times configured for each protection<sup>4</sup>. The controller will react to a triggered protection as configured.

Attention: The controller may continue operation after exceeding protection thresholds because of blanking times. All protection thresholds have to be set with respect to tolerances, blanking times and worst case transients.

Figure 25 Blanking Times cause Excess of Threshold

## 3.3.4.1 Overtemperature Protection

Overtemperature protection initiates a shutdown once the critical temperature level T<sub>critical</sub> is exceeded.

*Figure 26* shows the temperature hysteresis formed by the critical temperature  $T_{critical}$  and maximum turn-on threshold  $T_{hot}$  if auto-restart is enabled for temperature protection.

If latch mode is selected instead, the IC will turn off and only restart after recycling of input power with a temperature below  $T_{critical}$ .

Figure 26 Temperature Protection

<sup>&</sup>lt;sup>4</sup> except VCC undervoltage protection

infineon

**Functional Description**

#### 3.3.4.2 VCC Undervoltage Protection

A *Undervoltage Lockout (UVLO)* is implemented in hardware. It ensures defined enabling and disabling of the *Integrated Circuit (IC)* operation depending on the supply voltage V<sub>VCC</sub> at the VCC pin in accordance with defined thresholds.

The  $\it{UVLO}$  contains a hysteresis with the voltage thresholds  $V_{VCC,on}$  for enabling the  $\it{IC}$  and  $V_{VCC,off}$  for disabling the IC. Once the mains input voltage is applied, current flows through an external resistor into the HV pin via the integrated depletion cell and diode to the VCC pin. The  $\it{IC}$  is enabled once  $V_{VCC}$  exceeds the threshold  $V_{VCC,on}$  and enters normal operation if no fault condition is detected. In this phase,  $V_{VCC}$  will drop until either external supply or the self-supply via the auxiliary winding takes over the supply at the VCC pin.

In the case of output short or strong capacitive loading, the auxiliary winding cannot provide power to  $V_{VCC}$ . A timeout of  $t_{start,max}$  is available to respond to this failure condition.

Note: The self-supply via the auxiliary winding must be in place before the output short timeout occurs or before  $V_{VCC}$  falls below the  $V_{VCC.off}$  threshold. Otherwise, the system will perform a fast restart.

Note: It is possible to supply VCC externally from an auxiliary power supply. In this case, the VCC also needs initially to ramp to V<sub>VCC.on</sub> to enable the IC.

### 3.3.4.3 VCC Overvoltage Protection

Overvoltage protection ensures that the voltage at the VCC pin is not exceeded.

The VCC voltage is compared to a configurable overvoltage protection threshold  $V_{VCC,OV}$ . If the threshold is exceeded for longer than the blanking time  $t_{blank,VCC,OV}$ , the protection will be triggered.

Note: The reaction to this protection is fixed to stop mode to ensure a discharge of VCC.

#### 3.3.4.4 Other General Controller Protections

XDPL8220 includes several protections to ensure the integrity and correct flow of the firmware.

- A hardware watchdog checks correct execution of firmware. A protection is triggered in the event that the firmware does not service the watchdog within a defined period.

- A hardware *Random Access Memory (RAM)* parity check triggers a protection if a bit in the memory changes unintentionally.

- A hardware clock check watchdog checks that no clock oscillator is failing.

- A firmware *Cyclic Redundancy Check (CRC)* at each startup verifies the integrity of firmware code and its parameters.

- A firmware task execution watchdog triggers a protection if the firmware tasks are not executed as expected.

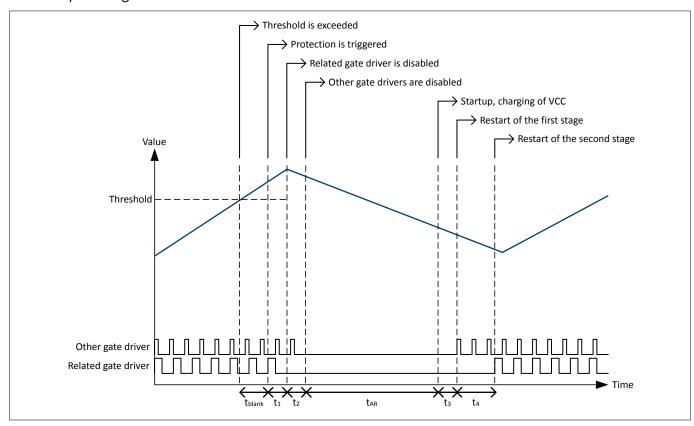

#### 3.3.5 Protection Reactions

The reaction to each protection can be separately selected. Available reactions may include auto restart, fast auto restart, latch or stop mode.

Figure 27 depicts the timing of an auto-restart reaction:

- **1.** If a protection threshold is exceeded for longer than the related blanking time t<sub>blank</sub>, the protection is triggered.

- **2.** Within a maximum  $t_1 = 4 * 32 \mu s$ , the gate driver of the power stage related to the protection is disabled.

- 3. Within a maximum  $t_2 = 4 * 32 \mu s$ , the gate drivers of other stages are disabled.

- **4.** The reaction depends on the configuration of the protection:

- In case of latch mode, the application will enter latch mode at this time. No further steps are done, the reaction ends here.

#### **Functional Description**

- In case of stop mode, the application will stop and enter UART parametrization mode which allows to read out the error code. No further steps are done, the reaction ends here.

- In case of a (fast) auto-restart reaction, the controller will enter a power saving mode for the auto-restart time t<sub>AR</sub> or t<sub>AR,fast</sub> respectively.

- **5.** The auto restart may include a new VCC charging cycle. The time t<sub>3</sub> typically depends on the input voltage.

- 6. The first power stage will enable its gate driver according to its startup sequence (soft start) again.

- 7. The second power stage will enable its gate driver according to its startup sequence (soft start) again. The startup of a subsequent power stage may be delayed by a time t₄ depending on any startup condition for the subsequent stage.

Figure 27 **Protection Reaction for auto-restart**

#### 3.3.5.1 Auto restart

When auto restart mode is activated, XDPL8220 stops switching at the GD pins. After a configurable auto restart time t<sub>AR</sub>, XDPL8220 initiates a new startup with soft start.

During the time in which the gate is not switching, the internal HV startup cell is automatically enabled and disabled to keep the VCC voltage between the V<sub>UVLO</sub> and V<sub>OVLO</sub> thresholds for the supply of XDPL8220.

#### 3.3.5.2 **Fast Auto Restart**

When fast auto restart mode is activated, XDPL8220 stops switching at the GD pins. After a configurable fast auto restart time t<sub>AR.fast</sub>, XDPL8220 initiates a new startup with soft start.

During the time in which the gate is not switching, the internal HV startup cell is automatically enabled and disabled to keep the VCC voltage between the V<sub>UVLO</sub> and V<sub>OVLO</sub> thresholds for the supply of XDPL8220.

**XDP<sup>™</sup> Digital Power**

**Functional Description**

#### 3.3.5.3 **Latch Mode**

When latch mode is activated, XDPL8220 stops switching at the GD pins. The device stays in this state until input voltage is completely removed and the VCC voltage drops below the V<sub>UVI O</sub> threshold. Only then can XDPL8220 be restarted by applying input voltage.

To maintain this state, the internal HV startup cell is automatically enabled and disabled to keep the VCC voltage between the V<sub>UVLO</sub> and V<sub>OVLO</sub> thresholds for the supply of XDPL8220. The current consumption is reduced to a minimum.

#### 3.3.5.4 **Stop Mode**

When stop mode is activated, XDPL8220 stops switching at the GD pins. XDPL8220 enters **UART** communication mode to allow debugging of the system state.

Note:

The VCC for XDPL8220 needs to be supplied by an external source. Without an external supply, VCC will drain to V<sub>UVLO</sub> and XDPL8220 performs a restart.

**Design Support**

## 4 Design Support

XDPL8220 is a configurable digital platform product. It can be configured to meet a wide range of application requirements.

### 4.1 Design Procedure

Infineon provides support of the design procedure for lighting applications using Infineon's digital platform *IC*s. A lighting application is designed in a few simple steps using Infineon's digital platform *IC*s as follows:

- **1.** The Infineon XDPL8220 reference board and the *XDPL8220 Reference Board Test Report* demonstrate the features and performance of the XDPL8220 in a typical application.

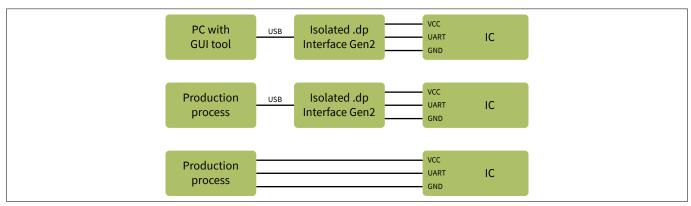

- 2. Parameters of the XDPL8220 reference board can easily be fitted to any application's requirements. The isolated .dp Interface Gen2 is connected to XDPL8220 via Universal Serial Bus (USB). The GUI tool .dp Vision is included with the .dp Interface Gen2. .dp Vision allows interactive changing of parameters. The usage of .dp Vision is explained in the .dp Vision User Manual.

- **3.** To further adapt the XDPL8220 to application requirements, customers can design their own specific boards. The steps used to design a board are explained in the *XDPL8220 Design Guide*. .dp Vision can be used together with the .dp Interface Gen2 to connect to customer-specific designs based on XDPL8220. This setup can be used for rapid prototyping. The tooling allows fine-tuning of parameters and development of multiple parameter sets e.g. to reuse the same for different product variants of an application.

- **4.** For mass production, the *XDPL8220 Programming Manual* documents the necessary interfacing and procedures to integrate the parameter configuration of XDPL8220 into the production line. *Figure 28* shows two options to easily apply the configuration of the *IC* during production tests:

- One option is to use the isolated .dp Interface Gen2, which can be accessed with USB commands.

- Another option is to directly use the *UART* interface of the XDPL8220. The correct VCC voltage and *UART* communication have to be controlled by the production process in this case.

Figure 28 Setup for Parametrization using .dp Interface Gen2 for Interactive Development (top) and Production (middle and bottom)

## 4.2 List of Configurable Parameters

This list provides information about configurable parameters, including their permitted range and granularity. Typical example values are also provided.

**Table 2** Parameters for Hardware Configuration

| Symbol         | Description                       | Example | Minimum<br>Value | Maximum<br>Value | Granularity |

|----------------|-----------------------------------|---------|------------------|------------------|-------------|

| N <sub>a</sub> | <b>FB</b> auxiliary winding turns | 34      | 1                | 300              | 1           |

| N <sub>p</sub> | <b>FB</b> primary winding turns   | 60      | 1                | 300              | 1           |

**Design Support**

Table 2 **Parameters for Hardware Configuration (continued)**

| Symbol                  | Description                                                    | Example    | Minimum<br>Value | Maximum<br>Value   | Granularity    |

|-------------------------|----------------------------------------------------------------|------------|------------------|--------------------|----------------|

| $\overline{N_s}$        | <b>FB</b> secondary winding turns                              | 44         | 1                | 300                | 1              |

| R <sub>CS,FB</sub>      | FB current sense resistance                                    | 410/2048 Ω | 200/2048 Ω       | 3 Ω                | 1/2048 Ω       |

| R <sub>ZCD,FB,1</sub>   | <b>FB</b> ZCD upper resistor                                   | 120 kΩ     | 50 Ω             | 200 kΩ             | 50 Ω           |

| R <sub>ZCD,FB,2</sub>   | <b>FB</b> ZCD shunt resistor                                   | 7.5 kΩ     | 50 Ω             | 100 kΩ             | 50 Ω           |

| R <sub>VS,1</sub>       | VS upper resistor for bus voltage measurement                  | 9.96 ΜΩ    | 500 kΩ           | 15 ΜΩ              | 500 Ω          |

| R <sub>VS,2</sub>       | VS shunt resistor for bus voltage measurement                  | 52.3 kΩ    | 22 kΩ            | 100 kΩ             | 50 Ω           |

| R <sub>HV</sub>         | HV resistor                                                    | 100 kΩ     | 47 kΩ            | 130 kΩ             | 50 Ω           |

| V <sub>out,offset</sub> | Output voltage offset (e.g. voltage drop from secondary diode) | -0.625 V   | -4.000 V         | 4.000 V            | 0.125 V        |

| $V_{GBFB}$              | FB gate driver voltage high level                              | 10.5 V     | 4.5 V            | 15 V <sup>1)</sup> | 1.5 V          |

| I <sub>GBFB</sub>       | FB gate driver strength                                        | 100 mA     | 100 mA           | 500 mA             | Selected steps |

| $V_{GBPFC}$             | PFC gate driver voltage high level                             | 10.5 V     | 4.5 V            | 15 V <sup>2)</sup> | 1.5 V          |

| I <sub>GBPFC</sub>      | PFC gate driver strength                                       | 100 mA     | 30 mA            | 150 mA             | Selected steps |

#### Table 3 **Parameters for PFC Protections**

| Symbol                      | Description                                                             | Example | Minimum<br>Value            | Maximum<br>Value             | Granularity           |

|-----------------------------|-------------------------------------------------------------------------|---------|-----------------------------|------------------------------|-----------------------|

| t <sub>blank,Vbus,OVP</sub> | Blanking time for bus overvoltage threshold, level 2                    | 200 ns  | 0 s                         | 640 ns                       | 1 / f <sub>mclk</sub> |

| t <sub>blank,Vbus,OVP</sub> | Blanking time for bus overvoltage threshold, level 1                    | 400 us  | 0 s                         | 1 ms                         | t <sub>slot</sub>     |

| V <sub>bus,OVP1</sub>       | Bus overvoltage threshold, level 1                                      | 490 V   | V <sub>bus,stdy,entr,</sub> | 600 V <sup>3)</sup>          | 1/16 V                |

| t <sub>blank,Vbus,UV</sub>  | Blanking time for bus undervoltage threshold                            | 500 us  | 0 s                         | 1 ms                         | t <sub>slot</sub>     |

| V <sub>bus,UV</sub>         | Bus undervoltage threshold                                              | 300 V   | V <sub>bus,start,PFC</sub>  | V <sub>bus,stdy,entr,U</sub> | 1/16 V                |

| t <sub>start,max,PFC</sub>  | Maximum <b>PFC</b> soft start time to settle the bus voltage at startup | 200 ms  | 0 s                         | 500 ms                       | t <sub>slot</sub>     |

| t <sub>blank,Vin,OV</sub>   | Blanking time for input overvoltage threshold                           | 100 ms  | 0 s                         | 200 ms                       | t <sub>slot</sub>     |

| t <sub>blank,Vin,UV</sub>   | Blanking time for input undervoltage threshold                          | 100 ms  | 0 s                         | 200 ms                       | t <sub>slot</sub>     |

Limited by VCC - 0.5 V

Limited by VCC - 0.5 V

<sup>&</sup>lt;sup>3</sup> Limited by the voltage rating of the bus capacitors

**Design Support**

Table 3

Parameters for PFC Protections (continued)

| Symbol                              | Description                                                                                                                                       | Example  | Minimum<br>Value          | Maximum<br>Value          | Granularity           |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|---------------------------|-----------------------|

| $V_{\text{in,OV}}$                  | Input overvoltage threshold                                                                                                                       | 319 Vrms | V <sub>in,start,max</sub> | 424 Vrms                  | 1/16 Vrms             |

| $V_{in,UV}$                         | Input undervoltage threshold                                                                                                                      | 76 Vrms  | 0 V                       | V <sub>in,start,min</sub> | 1/16 Vrms             |

| V <sub>in,start,max</sub>           | Maximum input voltage at startup                                                                                                                  | 307 Vrms | V <sub>in,start,min</sub> | V <sub>in,OV</sub>        | 1/16 Vrms             |

| V <sub>in,start,min</sub>           | Minimum input voltage at startup                                                                                                                  | 88 Vrms  | $V_{in,UV}$               | V <sub>in,start,max</sub> | 1/16 Vrms             |

| t <sub>blank,OCP2,PFC</sub>         | Blanking time for the peak current limitation, level 2                                                                                            | 200 ns   | 1 / f <sub>mclk</sub>     | 600 ns                    | 1 / f <sub>mclk</sub> |

| t <sub>blank,OCP1,PFC</sub>         | Blanking time for the peak current limitation, level 1                                                                                            | 200 ns   | 1 / f <sub>mclk</sub>     | 600 ns                    | 1 / f <sub>mclk</sub> |

| V <sub>CS,OCP1, PFC</sub>           | Maximum peak current voltage                                                                                                                      | 0.75 V   | 0.1 V                     | 1.08 V                    | 0.125 mV              |

| $t_{blank,CCM,PFC}$                 | Blanking time for CCM protection                                                                                                                  | 12 ms    | 0 s                       | 30 ms                     | t <sub>slot</sub>     |

| Protection <sub>PF</sub>            | Bit-coded enabling per protection: If set to 1, protection is enabled.                                                                            |          | 0                         | 65535                     | One-hot coded         |

| Protection <sub>PF</sub><br>C,conf1 | Bit-coded reaction per protection: If set to 1, auto-restart is selected. If set to 0, either latch mode or stop is selected.                     |          | 0                         | 65535                     | One-hot<br>coded      |

| Protection <sub>PF</sub><br>C,conf2 | Bit-coded reaction per protection: If set to 1, fast auto restart or stop is selected. If set to 0, normal auto-restart or latch mode is enabled. |          | 0                         | 65535                     | One-hot<br>coded      |

| Protection <sub>PF</sub><br>C,conf3 | Bit-coded reaction per protection: If set to 1, limited number of restarts are enabled. If set to zero, unlimited restarts will be done.          |          | 0                         | 65535                     | One-hot<br>coded      |

| Protection <sub>PF</sub><br>C,conf4 | Bit-coded reaction per protection: If set to 1, VCC charging will be enabled for auto-restarts.                                                   |          | 0                         | 65535                     | One-hot<br>coded      |

## Table 4 Parameters for Flyback Protections

| Symbol                     | Description                                                         | Example | Minimum<br>Value       | Maximum<br>Value       | Granularity       |

|----------------------------|---------------------------------------------------------------------|---------|------------------------|------------------------|-------------------|

| V <sub>out,UV</sub>        | Output undervoltage threshold                                       | 15 V    | 0 V                    | V <sub>out,start</sub> | 0.125 V           |

| t <sub>blank,Vout,UV</sub> | Blanking time for output undervoltage                               | 500 us  | 0 s                    | 1 ms                   | t <sub>slot</sub> |

| t <sub>start,max,FB</sub>  | Maximum <b>FB</b> startup time to detect an output short at startup | 5 ms    | 0 s                    | 200 ms                 | t <sub>slot</sub> |

| $V_{out,OV}$               | Output overvoltage threshold                                        | 55 V    | V <sub>out,start</sub> | 200 V                  | 0.125 V           |

| t <sub>blank,Vout,OV</sub> | Blanking time for output overvoltage                                | 500 us  | 0 s                    | 1 ms                   | t <sub>slot</sub> |

| t <sub>blank,CCM</sub>     | Blanking time for CCM protection                                    | 500 us  | 0 s                    | 1 ms                   | t <sub>slot</sub> |

| I <sub>out,OC</sub>        | Output overcurrent threshold                                        | 3 A     | I <sub>out,full</sub>  | 10 A                   | 0.5 mA            |

| t <sub>blank,lout,OC</sub> | Blanking time for output overcurrent                                | 500 us  | 0 s                    | 1 ms                   | t <sub>slot</sub> |

| P <sub>out,OP</sub>        | Output overpower threshold                                          | 120 W   | P <sub>out,set</sub>   | 300 W                  | 0.5 W             |

| t <sub>blank,Pout,OP</sub> | Blanking time for output overpower                                  | 500 us  | 0 s                    | 1 ms                   | t <sub>slot</sub> |

**Design Support**

**Parameters for Flyback Protections (continued)** Table 4

| Symbol                          | Description                                                                                                                                       | Example | Minimum<br>Value | Maximum<br>Value | Granularity       |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|------------------|-------------------|

| t <sub>blank,Vbus,FB</sub>      | Blanking time for bus voltage plausibility check                                                                                                  | 500 us  | 0 s              | 1 ms             | t <sub>slot</sub> |

| t <sub>blank,CSFB2GN</sub>      | Blanking time for the CSFB-to-GND-<br>short check                                                                                                 | 100 us  | 0 s              | 500 us           | t <sub>slot</sub> |

| t <sub>blank,TOSC,FB</sub>      | Blanking time for the t <sub>OSC,FB</sub> being overly long check                                                                                 | 40 ms   | 0 ms             | 100 ms           | 20 ms             |

| Protection <sub>FB,</sub>       | Bit-coded enabling per protection: If set to 1, protection is enabled.                                                                            |         | 0                | 65535            | One-hot coded     |

| Protection <sub>FB</sub> ,      | Bit-coded reaction per protection: If set to 1, auto-restart is selected. If set to 0, either latch mode or stop is selected.                     |         | 0                | 65535            | One-hot<br>coded  |

| Protection <sub>FB,</sub> conf2 | Bit-coded reaction per protection: If set to 1, Fast Auto-restart or Stop is selected. If set to 0, normal Auto-restart or latch mode is enabled) |         | 0                | 65535            | One-hot<br>coded  |

| Protection <sub>FB,</sub> conf3 | Bit-coded reaction per protection: If set to 1, limited number of restarts are enabled. If set to zero, unlimited restarts are enabled.           |         | 0                | 65535            | One-hot<br>coded  |

| Protection <sub>FB</sub> ,      | Bit-coded reaction per protection: If set to 1, VCC charging will be enabled for auto-restarts.                                                   |         | 0                | 65535            | One-hot<br>coded  |

#### Table 5 **Parameters for General Protections**

| Symbol                           | Description                                                                                                                                       | Example | Minimum<br>Value | Maximum<br>Value | Granularity       |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|------------------|-------------------|

| V <sub>VCC,OV</sub>              | VCC overvoltage threshold                                                                                                                         | 24.75 V | 6 V              | 24.75 V          | 0.125 V           |