## **PMS**

Pressure Monitoring Sensor

## SP27

High integrated single-chip pressure sensor with a low power embedded micro-controller

SP27 Version A5

1300kPa

## Datasheet

Revision 1.0, 2012-02-07

# Sense & Control

Edition 2012-02-07

Published by Infineon Technologies AG 81726 Munich, Germany © 2016 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

SP27 High integrated single-chip pressure sensor with a low power embedded micro-controller CONFIDENTIAL

Revision History: 2012-02-07, Revision 1.0

| D        | D!-!      | D!-! 4     | <b>.</b> . |

|----------|-----------|------------|------------|

| Previous | Revision: | Revision ( | J. 1       |

| Page    | Subjects (major changes since last revision)   |

|---------|------------------------------------------------|

| Page 80 | I2C Command - Measure Pressure Function Update |

|         |                                                |

|         |                                                |

|         |                                                |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

#### Trademarks of Infineon Technologies AG

AURIX™, C166™, CanPAK™, CIPOS™, CIPURSE™, EconoPACK™, CoolMOS™, CoolSET™, CORECONTROL™, CROSSAVE™, DAVE™, EasyPIM™, EconoBRIDGE™, EconoDUAL™, EconoPIM™, EiceDRIVER™, eupec™, FCOS™, HITFET™, HybridPACK™, I²RF™, ISOFACE™, IsoPACK™, MIPAQ™, ModSTACK™, my-d™, NovalithIC™, OptiMOS™, ORIGA™, PRIMARION™, PrimePACK™, PrimeSTACK™, PRO-SIL™, PROFET™, RASIC™, ReverSave™, SatRIC™, SIEGET™, SINDRION™, SIPMOS™, SmartLEWIS™, SOLID FLASH™, TEMPFET™, thinQ!™, TRENCHSTOP™, TriCore™.

#### Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-ig™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hildraeve Incorporated, IEC™ of Commission Electrotechnique Internationale, IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2011-02-24

#### **Table of Contents**

## **Table of Contents**

|                        | Table of Contents                               | . 4 |

|------------------------|-------------------------------------------------|-----|

|                        | List of Figures                                 | . 6 |

|                        | List of Tables                                  | . 7 |

|                        | Introduction                                    |     |

|                        | Overview                                        |     |

| 1.2                    | Features                                        | . 8 |

|                        | Functional Description                          |     |

|                        | General                                         |     |

|                        | Pin Configuration                               |     |

|                        | Pin Description                                 |     |

|                        | Block Diagram                                   |     |

|                        | Operating Modes and States                      |     |

| 2.5.1                  | Operating Modes                                 |     |

| 2.5.2                  | Resets and Operating Mode Selection             |     |

| 2.5.3                  | NORMAL Mode Operation                           |     |

| 2.5.3.1                | INIT State                                      |     |

| 2.5.3.2                | RUN State                                       |     |

| 2.5.3.3                | IDLE State                                      |     |

| 2.5.3.4                | POWER DOWN State                                |     |

| 2.5.3.5                | State Transitions                               |     |

| 2.5.3.6                | Status of SP27 Blocks in Different States       |     |

|                        | Fault Protection                                |     |

| 2.6.1                  | Watchdog Timer                                  |     |

| 2.6.2                  | ADC Measurement Overflow & Underflow            |     |

| 2.6.3                  | ADC Selftest                                    |     |

| 2.6.4                  | Bond Wire Surveillance                          |     |

|                        | Functional Block Description                    |     |

| 2.7.1                  | Sensors and Data Acquisition                    |     |

| 2.7.1.1                | Pressure Sensor                                 |     |

| 2.7.1.2                | Temperature Sensor                              |     |

| 2.7.1.3                | Data Acquisition                                |     |

| 2.7.2                  | Memory Organization                             |     |

| 2.7.2.1                | ROM                                             |     |

| 2.7.2.1.1<br>2.7.2.1.2 | ROM Library Functions and Reset/Wakeup Handlers |     |

| 2.7.2.1.2<br>2.7.2.2   | ROM Protections                                 |     |

|                        | FLASH                                           |     |

| 2.7.2.2.1              | FLASH Organization                              |     |

| 2.7.2.2.2<br>2.7.2.3   | FLASH Protection                                |     |

|                        | RAM                                             |     |

|                        | Special Function Registers                      |     |

|                        | Microcontroller                                 |     |

| 3.2                    | General Purpose Registers                       |     |

|                        | System Configuration Registers                  |     |

| 3.4                    | System Controller                               |     |

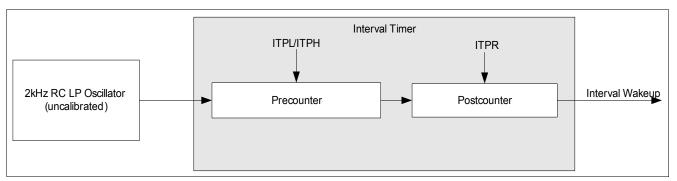

| 3.5                    | Interval Timer                                  |     |

| 3.6                    | Interval Timer Precounter / Calibration         |     |

| 3 7                    | Clock Controller                                | 47  |

| CONFIDENTIAL | Table of Contents |

|--------------|-------------------|

|              |                   |

| 3.8        | 16 Bit CRC (Cyclic Redundancy Check) Generator/Checker |      |

|------------|--------------------------------------------------------|------|

| 3.9        | Pseudo Random Number Generator                         |      |

| 3.10       | Timer Unit                                             |      |

| 3.11       | General Purpose Input/Output (GPIO)                    | . 64 |

| 3.12       | I <sup>2</sup> C Interface                             | . 71 |

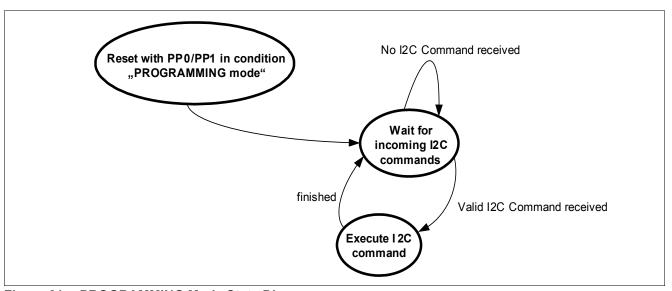

| 3.12.1     | Programming mode Operation                             | . 74 |

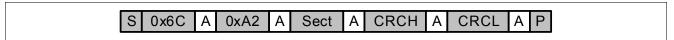

| 3.12.1.1   | FLASH Write Line                                       | . 75 |

| 3.12.1.2   | FLASH Erase                                            | . 75 |

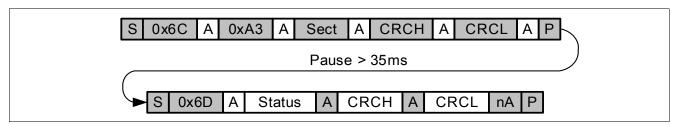

| 3.12.1.3   | FLASH Check Erase Status                               | . 76 |

| 3.12.1.4   | FLASH Read Line                                        | . 77 |

| 3.12.1.5   | Read Status                                            | . 78 |

| 3.12.1.6   | FLASH Check CRC                                        | . 79 |

| 3.12.1.7   | FLASH Set User Configuration Sector Lock               |      |

| 3.12.1.8   | Measure Pressure                                       |      |

| 3.12.1.9   | Measure Temperature                                    |      |

| 3.12.2     | DEBUG Mode Operation                                   |      |

| 3.12.2.1   | Debug Special Function Register                        |      |

| 3.12.2.1   | Debugging Functionality                                |      |

| 3.12.2.2   | Debugger Commands                                      |      |

| 3.12.2.3   |                                                        |      |

|            |                                                        |      |

| 3.12.2.3.  |                                                        |      |

| 3.12.2.3.  | ,                                                      |      |

| 3.12.2.3.4 | ,                                                      |      |

| 3.12.2.3.  |                                                        |      |

| 3.12.2.3.0 | <b>5</b>                                               |      |

| 3.12.2.3.  | <b>5</b> 1                                             |      |

| 3.12.2.3.  | •                                                      |      |

| 3.12.2.3.  | 9 Run to Next Breakpoint                               | . 86 |

| 4          | Specification                                          |      |

| 4.1        | Absolute Maximum Ratings                               | . 87 |

| 4.2        | Operating Range                                        | . 89 |

| 4.3        | Characteristics                                        | . 90 |

| 4.3.1      | Pressure Sensor (1300kPa variant)                      | . 90 |

| 4.3.2      | Temperature Sensor                                     | . 91 |

| 4.3.3      | Supply Currents                                        | . 92 |

| 4.3.4      | 12 MHz RC HF Oscillator                                | . 93 |

| 4.3.5      | 2 kHz RC LP Oscillator                                 | . 93 |

| 4.3.6      | Interval Timer                                         |      |

| 4.3.7      | Voltage Regulator                                      |      |

| 4.3.8      | Power On Reset / Brown Out Reset                       |      |

| 4.3.9      | FLASH Memory                                           |      |

| 4.3.10     | Watchdog Timer                                         |      |

| 4.3.11     | Digital I/O pins                                       |      |

| 4.3.11     | I <sup>2</sup> C Interface                             |      |

|            |                                                        |      |

| 5          | Package Information                                    |      |

| 5.1        | Package Outline                                        |      |

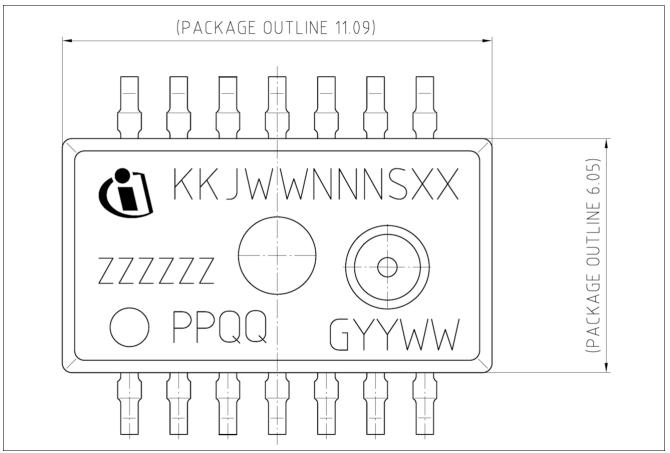

| 5.2        | Identification Code                                    | 100  |

| 5.2.1      | Identification Code Definition                         | 100  |

|            | References                                             | 101  |

**List of Figures**

## **List of Figures**

| igure 1   | Pin Configuration PG-DSOSP-14-6 (Top View, Figure not to Scale) |    |

|-----------|-----------------------------------------------------------------|----|

| igure 2   | SP27 Block Diagram                                              |    |

| igure 3   | Available Operating Modes if Lockbyte 2 is not Set              |    |

| igure 4   | Available Operating Modes if Lockbyte 2 is Set                  |    |

| igure 5   | Power On Reset / Brown Out Reset / Operating Mode Selection     | 15 |

| igure 6   | NORMAL Mode State Diagram                                       | 16 |

| igure 7   | Memory Map                                                      | 20 |

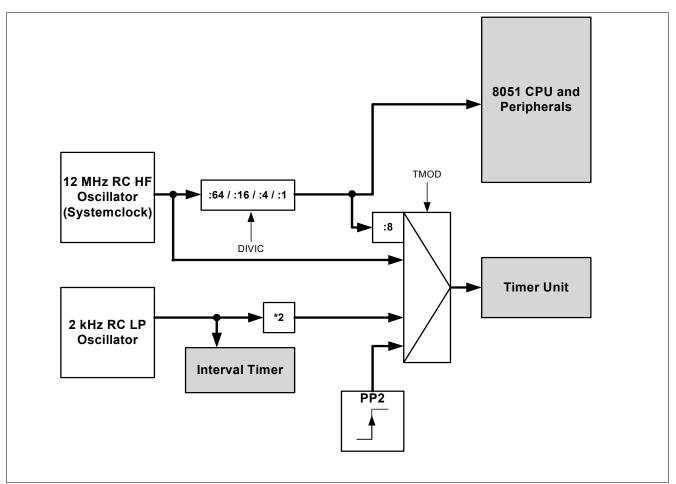

| igure 8   | Interval Timer Block Diagram                                    | 43 |

| igure 9   | SP27 Clock Concept                                              |    |

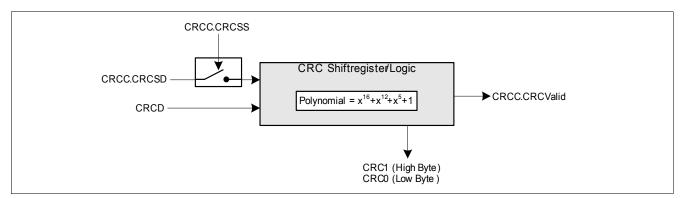

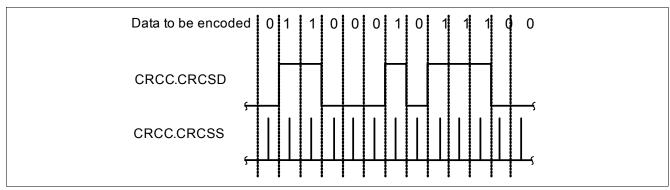

| igure 10  | CRC (Cyclic Redundancy Check) Generator/Checker                 | 49 |

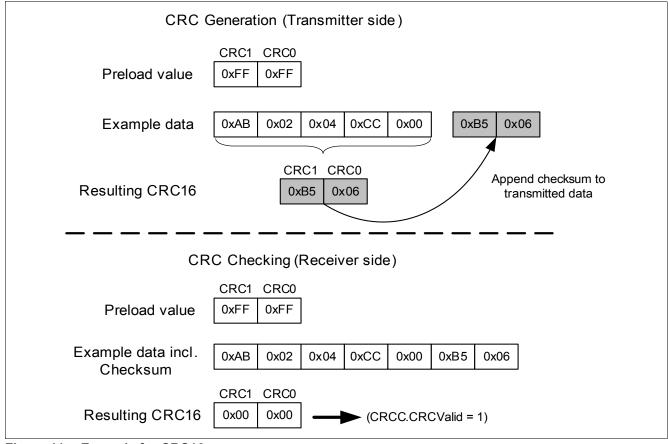

| igure 11  | Example for CRC16 usage                                         | 49 |

| igure 12  | Example for serial CRC generation/checking                      | 50 |

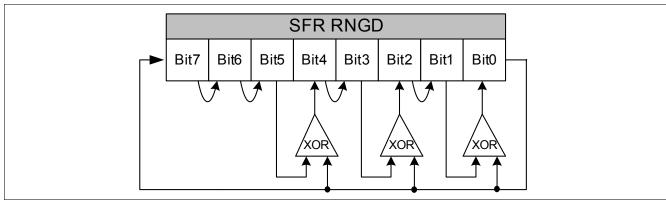

| igure 13  | Shift Register Implementation                                   | 54 |

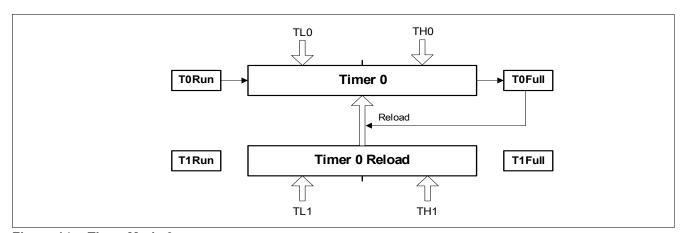

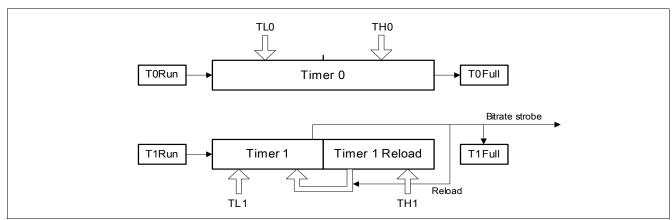

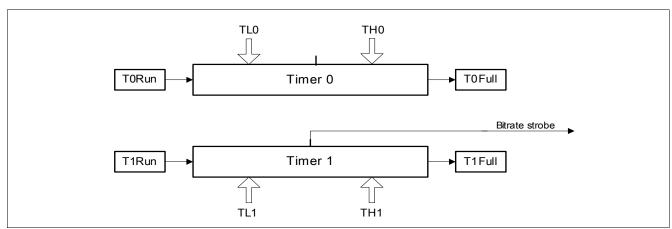

| igure 14  | Timer Mode 0                                                    | 55 |

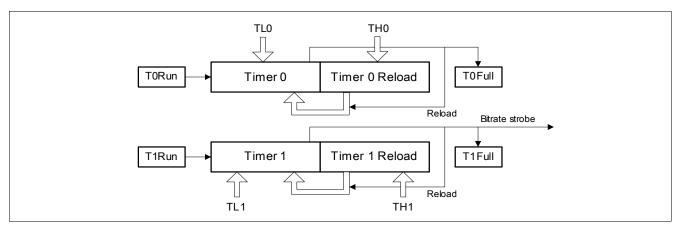

| igure 15  | Timer Mode 1                                                    | 56 |

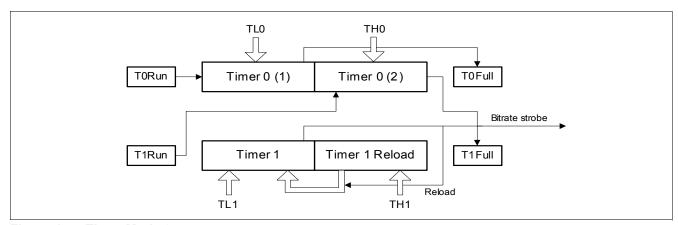

| igure 16  | Timer Mode 2                                                    | 56 |

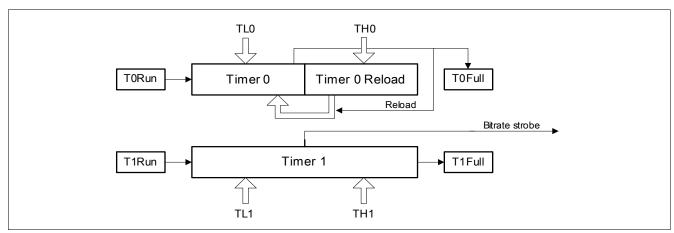

| igure 17  | Timer Mode 3                                                    | 57 |

| igure 18  | Timer Mode 5                                                    | 58 |

| igure 19  | Timer Mode 6                                                    | 59 |

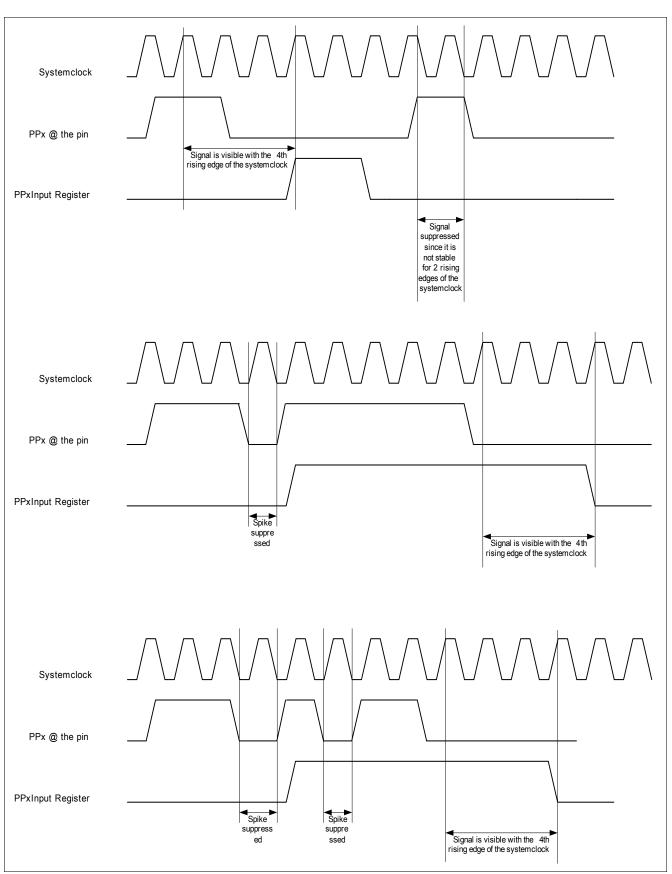

| igure 20  | Synchronization Stage & Spike Suppression Examples              | 65 |

| igure 21  | PROGRAMMING Mode State Diagram                                  |    |

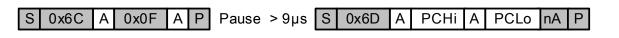

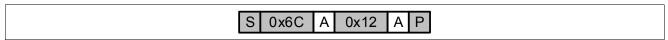

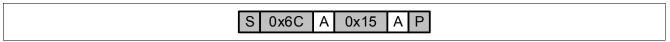

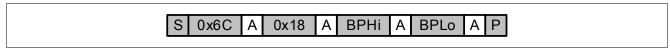

| igure 22  | I <sup>2</sup> C Legend - PROGRAMMING Mode                      |    |

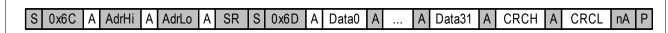

| igure 23  | FLASH Write Line I2C Command                                    |    |

| igure 24  | FLASH Erase Command                                             | 75 |

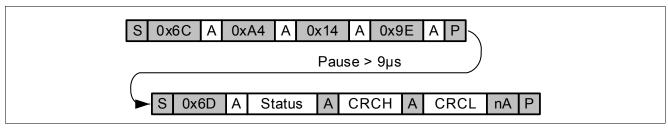

| igure 25  | FLASH Check Erase Status Command                                |    |

| igure 26  | FLASH Read Line Command                                         |    |

| igure 27  | FLASH Read Status Command                                       |    |

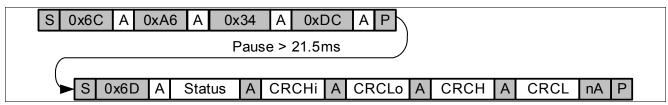

| igure 28  | FLASH Check CRC                                                 |    |

| igure 29  | FLASH Set User Configuration Sector Lock                        |    |

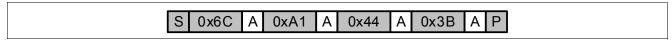

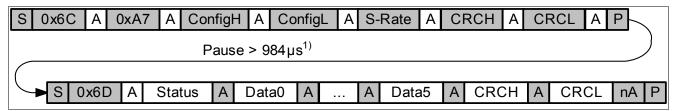

| igure 30  | Measure Pressure                                                |    |

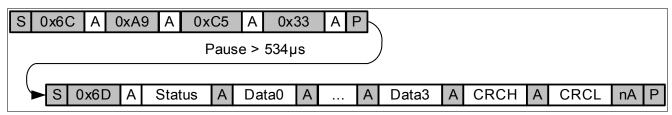

| igure 31  | Measure Temperature                                             |    |

| igure 32  | I <sup>2</sup> C Legend - DEBUG Mode                            |    |

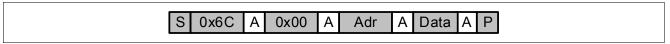

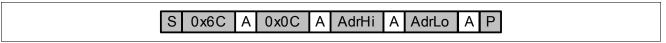

| igure 33  | DEBUG SetSFR Command                                            |    |

| Figure 34 | DEBUG ReadSFR Command                                           |    |

| igure 35  | DEBUG SetMemory Command                                         |    |

| igure 36  | DEBUG ReadMemory Command                                        |    |

| igure 37  | DEBUG SetPC Command                                             |    |

| igure 38  | DEBUG ReadPC Command.                                           |    |

| igure 39  | DEBUG SingleStep Command                                        |    |

| igure 40  | DEBUG Run Interruptible Command                                 |    |

| igure 41  | DEBUG Run to Next Breakpoint Command                            |    |

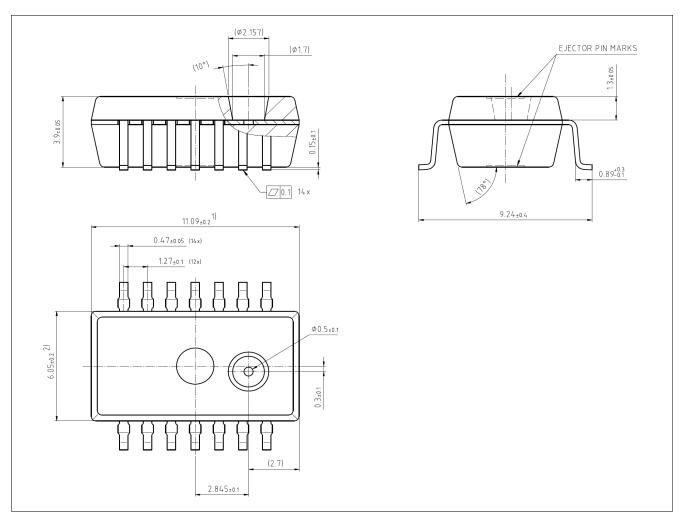

| igure 42  | PG-DSOSP-14-6 Package Dimensions                                |    |

| igure 43  | PG-DSOSP-14-6 marking.                                          |    |

|           |                                                                 |    |

CONFIDENTIAL List of Tables

## **List of Tables**

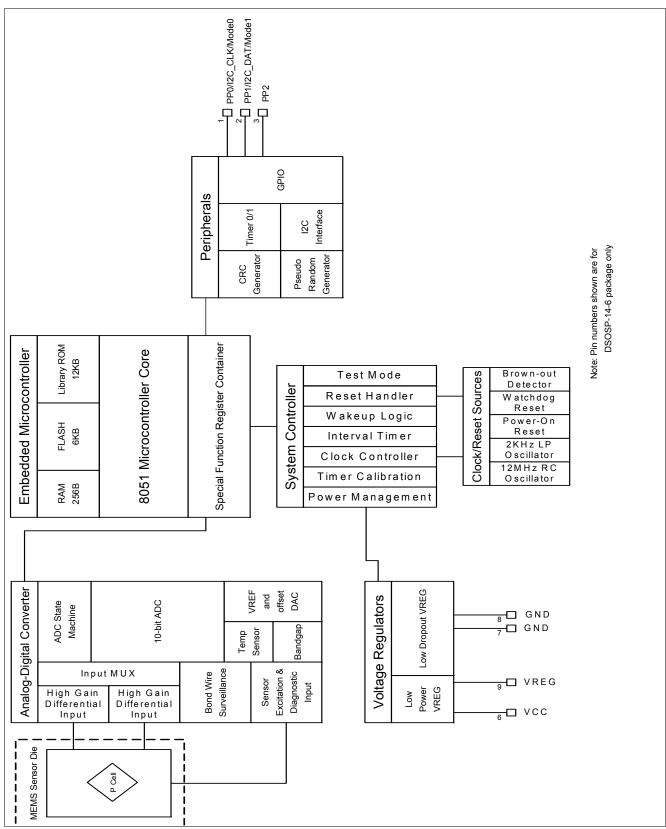

| Table 1  | IPin Description                                            | 11 |

|----------|-------------------------------------------------------------|----|

| Table 2  | SP27 - Operating Modes                                      | 13 |

| Table 3  | State Transitions in NORMAL Mode                            | 17 |

| Table 4  | Status of SP27 Blocks in Different States                   | 17 |

| Table 5  | Register Naming Convention Wakeup / Reset Value             | 24 |

| Table 6  | Registers Overview                                          | 24 |

| Table 7  | Registers Access Types                                      | 26 |

| Table 8  | Register 0 to F                                             | 32 |

| Table 9  | GPIO Port Configuration                                     | 64 |

| Table 10 | External Wakeup Configuration                               | 66 |

| Table 11 | I/O Port 1 - Alternative Functionality                      | 66 |

| Table 12 | FLASH Write Line Parameters                                 | 75 |

| Table 13 | FLASH Erase Parameters                                      | 75 |

| Table 14 | FLASH Check Erase Parameters                                | 76 |

| Table 15 | FLASH Check Erase Return values                             | 76 |

| Table 16 | FLASH Read Line Parameters                                  | 77 |

| Table 17 | FLASH Read Line Return values                               | 77 |

| Table 18 | FLASH Read Status Return values                             | 78 |

| Table 19 | FLASH Check CRC Return values                               | 79 |

| Table 20 | Measure Pressure Parameters                                 | 80 |

| Table 21 | Measure Pressure Return Values                              | 81 |

| Table 22 | Measure Temperature Return values                           | 82 |

| Table 23 | DEBUG mode SFRs                                             | 83 |

| Table 24 | Absolute Maximum Ratings                                    | 87 |

| Table 25 | Operating Range                                             | 89 |

| Table 26 | Pressure Sensor (1300 kPa variant), V <sub>CC</sub> = 3.3 V | 90 |

| Table 27 | Temperature Sensor, V <sub>CC</sub> = 3.3 V                 | 91 |

| Table 28 | Supply Currents                                             | 92 |

| Table 29 | 12 MHz RC HF Oscillator                                     | 93 |

| Table 30 | 2 kHz RC LP Oscillator                                      | 93 |

| Table 31 | Interval Timer                                              | 94 |

| Table 32 | Voltage Regulator                                           | 95 |

| Table 33 | Power On Reset / Brown Out Reset                            | 96 |

| Table 34 | FLASH Memory                                                | 97 |

| Table 35 | Watchdog Timer                                              | 98 |

| Table 36 | Digital I/O pins                                            | 98 |

| Table 37 | I <sup>2</sup> C Interface                                  | 98 |

### **Pressure Monitoring Sensor**

**SP27**

#### **SP27**

#### 1 Introduction

#### 1.1 Overview

The SP27 is a sensor for pressure measurements designed for PMS applications. With its microcontroller and integrated peripherals, the SP27 offers a single package solution for PMS applications. It requires only few external components. The SP27 features

- Pressure sensor for ambient pressure measurement

- Temperature sensor

- 8051 based microcontroller

- · Advanced system controller to minimize power consumption

Measurements of pressure and temperature are performed under software control, and the data can be formatted and prepared to be sent by the microcontroller.

An intelligent wakeup mechanism is available to reduce power consumption. An Interval Timer controls the timing of measurements. The circuitry can be programmed to wakeup at regular intervals. Additionally, wakeup is possible by an external wakeup source connected to a General Purpose Input/Output (GPIO).

The integrated microcontroller is instruction set compatible to the standard 8051 processor.

On-chip FLASH memory is integrated to store:

- The customer specific application program code

- A unique ID-Number

- · The calibration data for the sensors

Additional on-chip ROM memory is available that holds the ROM library functions (developed by Infineon) which covers standard tasks used by the application. The available ROM Library functions are described in a separate document (see [1]).

#### 1.2 Features

Main features:

- Operating temperature range -40 to +125 °C

- Low supply current

- Pressure sensor for 1300kPa range

- Temperature sensor

- 8051 instruction set compatible microcontroller (cycle-optimized)

- 6 kByte FLASH memory (for application code)

- 16 kByte ROM (for ROM library functions)

- 256 Bytes RAM

| Product Name | Product Type               | Ordering Code  | Package       |

|--------------|----------------------------|----------------|---------------|

| SP27         | Pressure Monitoring Sensor | SP270-25-256-0 | PG-DSOSP-14-6 |

CONFIDENTIAL Introduction

- Wakeup from POWER DOWN state using the Interval Timer or an external wakeup source connected via a GPIO pin

- I<sup>2</sup>C programming/debugging interface

- 16 Bit Hardware CRC generator

- 8 Bit Pseudo Random Number Generator

- Watchdog timer

- 3 bidirectional GPIO pins

## **2** Functional Description

## 2.1 General

## 2.2 Pin Configuration

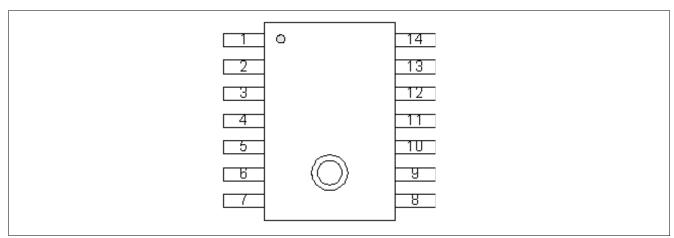

Figure 1 Pin Configuration PG-DSOSP-14-6 (Top View, Figure not to Scale)

## 2.3 Pin Description

## 2.4 Block Diagram

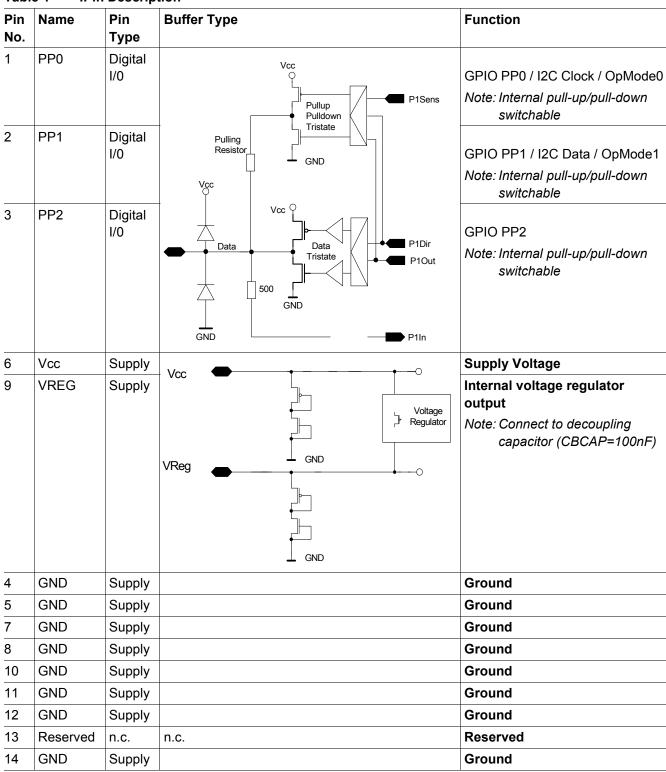

Figure 2 SP27 Block Diagram

## 2.5 Operating Modes and States

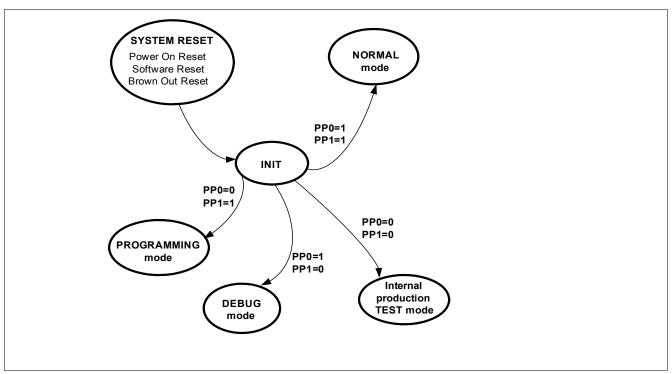

The SP27 can be operated in four different operating modes.

- NORMAL mode

- · PROGRAMMING mode

- DEBUG mode

- (internal production TEST mode)

The operating mode selection is done at Power On Reset by setting the GPIO pins PP0 and PP1 according to the following table:

Table 2 SP27 - Operating Modes

| PP0 | PP1 | Operating mode                              | Device controlled by                            |

|-----|-----|---------------------------------------------|-------------------------------------------------|

| 1   | 1   | NORMAL mode                                 | FLASH Program at 4000 <sub>H</sub>              |

| 0   | 1   | PROGRAMMING mode                            | ROM firmware / external I <sup>2</sup> C Master |

| 1   | 0   | DEBUG mode                                  | ROM firmware / external I <sup>2</sup> C Master |

| 0   | 0   | Internal production test mode <sup>1)</sup> | ROM firmware / external I <sup>2</sup> C Master |

<sup>1)</sup> IMPORTANT: Do not enter this mode since unpredictable behavior of the device might result

Note: Since PP0 and PP1 have their internal pull-up resistors enabled at Power On Reset, the default startup mode is NORMAL mode if the PP0 and PP1 pins are left unconnected.

Datasheet 13 Revision 1.0, 2012-02-07

#### 2.5.1 Operating Modes

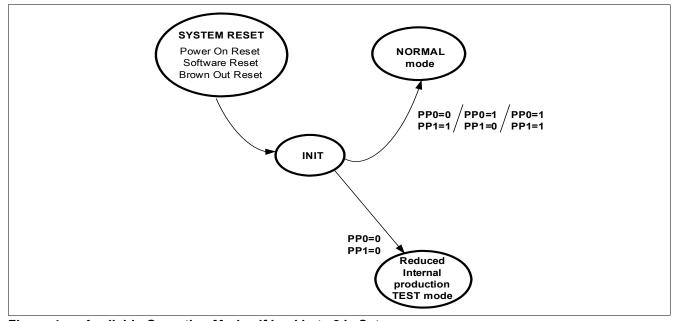

The operating modes depend on the setting of Lockbyte 2, which protects the FLASH Sector 0 (Code Sector) against overwriting, erasing and read-out to prevent reverse engineering of the application code. **Figure 3** shows the mode diagram if the Lockbyte 2 is not set.

Figure 3 Available Operating Modes if Lockbyte 2 is not Set

For security reasons some operating modes are not accessible anymore after the Lockbyte 2 (see "FLASH" on Page 22) is set. Figure 4 shows the behavior of the SP27 once the Lockbyte 2 is set. All mode selections (except the internal production TEST mode) lead to NORMAL mode.

Figure 4 Available Operating Modes if Lockbyte 2 is Set

#### 2.5.2 Resets and Operating Mode Selection

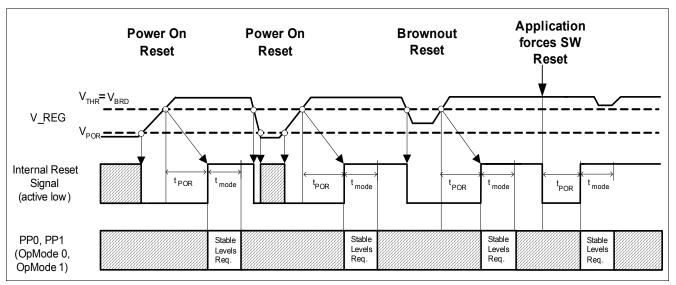

Figure 5 Power On Reset / Brown Out Reset / Operating Mode Selection

Three kinds of resets can occur which cause an operating mode selection:

- The Power On Reset circuit is activated if  $V_{\mathsf{REG}}$  rises above  $V_{\mathsf{POR}}$ . The internal blocks are held in RESET state until  $V_{\mathsf{REG}}$  has risen above  $V_{\mathsf{THR}}$ .

- The Brown Out Reset circuit is activated if  $V_{\mathsf{REG}}$  drops below  $V_{\mathsf{BRD}}$ . The internal blocks are held in RESET state until  $V_{\mathsf{REG}}$  has risen above  $V_{\mathsf{BRD}}$  again.

- The SP27's Software Reset can be forced by SP27 setting SRF bit CFG2.0[RESET].

When the Internal Reset state is released (after  $t_{POR}$  is elapsed), a further period  $t_{MODE}$  is required for reading the states applied to PP0 and PP1 to determine the operation mode of the device according to **Table 2** "SP27 - Operating Modes" on Page 13. The levels on these pins must be stable during the whole  $t_{MODE}$  period. After  $t_{MODE}$  has elapsed, the device starts operation in the selected mode.

The Watchdog Reset is a special case and it does not result in a mode selection. The Watchdog Reset affects only the CPU core and forces a program restart.

#### 2.5.3 NORMAL Mode Operation

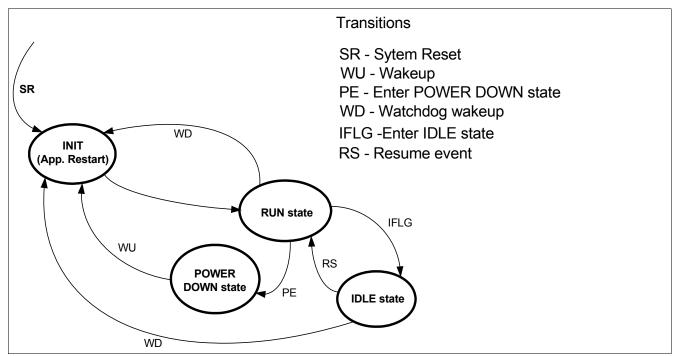

After a startup in NORMAL mode the system controller handles the different states as shown in the state transition diagram below.

Figure 6 NORMAL Mode State Diagram

#### 2.5.3.1 INIT State

The INIT state is entered after every System Reset (either Power On Reset, Brown Out Reset or Software Reset) to determine the desired operation mode (see "Operating Modes" on Page 14) and to initialize the SP27. The INIT state is entered as well if a wakeup or watchdog timeout occurs, but no operation mode selection is done after a wakeup and RUN state is entered immediately.

#### 2.5.3.2 RUN State

In RUN state, the microcontroller is executing the application program from the FLASH. In this state the watchdog is active to prevent software-deadlocks. The microcontroller (CPU) clock source is always based on the 12MHz RC HF Oscillator.

#### 2.5.3.3 IDLE State

In IDLE state the microcontroller clock is stopped to reduce the current consumption, while the peripherals Timer 0, ADC can continue normal operation.

After a resume event is triggered by one of the enabled peripherals, the microcontroller continues the operation where it was interrupted. The resume event source can be identified by reading SFR REF (see "Resume Event Flag Register" on Page 42).

#### 2.5.3.4 POWER DOWN State

In POWER DOWN state, the system controller takes control of the SP27 microcontroller and most peripherals are switched off.

In POWER DOWN state the active peripherals (Interval Timer...) are clocked by the 2kHz RC LP Oscillator.

After a wakeup occurred, the wakeup source can be identified by reading SFR WUF (see "Wakeup Flag Register" on Page 39).

#### 2.5.3.5 State Transitions

With reference to Figure 6 "NORMAL Mode State Diagram" on Page 16, the following state transitions can occur:

Table 3 State Transitions in NORMAL Mode

| State transition                                                                                    | Description                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RUN state<br>=> IDLE state                                                                          | The application program can set SFR bit CFG0.5 [IDLE] to enter IDLE state.  (see "Configuration Register 0" on Page 34)  Note: If no peripheral that can create a RESUME event is active, IDLE state will not be entered and the application will continue uninterrupted. |

| IDLE state<br>=> RUN state                                                                          | A peripheral unit (Timer 0, ADC) creates a resume event. The application automatically resumes where it was interrupted when entering IDLE state (see "Resume Event Flag Register" on Page 42)                                                                            |

| IDLE state  => INIT state  RUN state  => INIT state  RUN state  => INIT state  Register" on Page 39 |                                                                                                                                                                                                                                                                           |

| RUN state => POWER DOWN state                                                                       | The application program can call a ROM Library function to enter POWER DOWN state.                                                                                                                                                                                        |

| INIT state => RUN state                                                                             | This state change is initiated automatically by the system controller as soon as the initialization is finished.                                                                                                                                                          |

#### 2.5.3.6 Status of SP27 Blocks in Different States

Depending on the current state in NORMAL mode the internal blocks of the SP27 are active, inactive or are not supplied with supply voltage to minimize the current consumption. The following table gives an overview over of the individual blocks in the different states.

Table 4 Status of SP27 Blocks in Different States

| Unit                                                              | Run state                     | IDLE state | POWER DOWN state        |

|-------------------------------------------------------------------|-------------------------------|------------|-------------------------|

| Power On Reset                                                    | Active <sup>1)</sup>          | Active     | Active                  |

| Brown Out Detector                                                | Active                        | Active     | Inactive                |

| Voltage Regulator ( $V_{REG}$ )                                   | Active                        | Active     | Active                  |

| System controller                                                 | Active                        | Active     | Active                  |

| Microcontroller                                                   | Active                        | Inactive   | No supply <sup>2)</sup> |

| Timer                                                             | Active                        | Active     | No supply               |

| Peripheral modules CRC,<br>I2C, Pseudo Random<br>Number Generator | Selectable inactive or active | Inactive   | No supply               |

| Watchdog timer                                                    | Active                        | Active     | No supply               |

| Upper 128Bytes RAM                                                | Active                        | Inactive   | No supply               |

Table 4 Status of SP27 Blocks in Different States (cont'd)

| Unit                   | Run state             | IDLE state  | POWER DOWN state      |

|------------------------|-----------------------|-------------|-----------------------|

| Lower 128Bytes RAM     | Active                | Inactive    | Selectable            |

|                        |                       |             | No supply or inactive |

| FLASH                  | Active                | Inactive    | No supply             |

| ROM                    | Active                | Inactive    | No supply             |

| 2kHz RC LP Oscillator  | Active                | Active      | Active                |

| 12MHz RC HF Oscillator | Active                | Active      | No supply             |

| Interval Timer         | Active                | Active      | Active                |

| Sensor                 | Handled by            | Handled by  | No supply             |

|                        | ROM Library functions | ROM Library |                       |

|                        |                       | functions   |                       |

<sup>1)</sup> Active: block is powered, active and keeps its register contents.

#### 2.6 Fault Protection

The SP27 features multiple fault protections which prevent the application from unexpected behavior and deadlocks. This chapter gives a brief overview of the available fault protections. Detailed explanation of the usage can be found later in this document and in [1].

#### 2.6.1 Watchdog Timer

For operation security a watchdog timer is available to avoid application software deadlocks. The watchdog timer is only active in NORMAL mode and DEBUG mode and must be reset periodically by the application, otherwise the timer generates a wakeup and forces a restart of SP27 application program. Setting SFR bit CFG2.1[WDRES] resets the watchdog timer (see "Configuration Register 2" on Page 36)

The watchdog timeout period is fixed (see **Table 35 "Watchdog Timer" on Page 98**). The accuracy depends on the accuracy of the 2kHz RC LP Oscillator which is used to clock the watchdog timer.

Upon wakeup the watchdog timer is automatically reset. The watchdog timer is not, however, automatically reset upon entry into IDLE state. Therefore care must be taken so that the application does not remain in IDLE state longer than the minimum watchdog timeout period.

#### 2.6.2 ADC Measurement Overflow & Underflow

The ROM Library functions which perform measurements will return the over/underflow status in a status byte with the measurement result. (see [1])

#### 2.6.3 ADC Selftest

A dedicated ROM Library function is able to perform a selftest of the ADC (see [1]).

#### 2.6.4 Bond Wire Surveillance

The continuity of the bond wire connection between the ASIC die and the sensor die is checked as part of every pressure measurement. The ROM library routines which perform the measurements will return the bond wire status in a status byte with the measurement result (see [1]).

<sup>2)</sup> No supply: block is not powered, cannot be used and all register content is lost.

### 2.7 Functional Block Description

#### 2.7.1 Sensors and Data Acquisition

The SP27 has two sensors to acquire environmental data:

#### 2.7.1.1 Pressure Sensor

The pressure sensor consists of a single-crystal silicon, bulk micro machined membrane with an integrated full Wheatstone piezo-resistive bridge. The piezo-resistors are placed inside a vacuum reference chamber, whilst the pressure media to be measured in the application is applied to the opposite side of the membrane. This gives good long-term properties as the measurement bridge is protected from the environment. Pressure measurement is performed by a dedicated ROM library function (see [1]).

#### 2.7.1.2 Temperature Sensor

The temperature sensor is placed on the ASIC. This is read by the ADC referenced to a fixed (band gap) voltage. Temperature measurement is performed by a dedicated ROM library function (see [1]).

### 2.7.1.3 Data Acquisition

The analog data is acquired and digitized by the internal 10 Bit ADC.

Measurement routines for acquiring the environmental data are available within the ROM library functions that are described in [1].

Characteristic of the individual sensors can be found in "Characteristics" on Page 90.

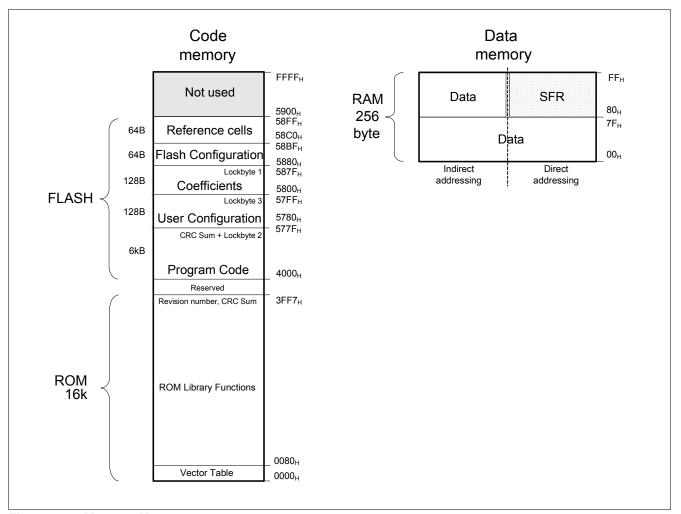

## 2.7.2 Memory Organization

Figure 7 Memory Map

The following memory blocks are implemented:

- 16 kByte ROM memory

- 6 kByte FLASH memory

- · 256 Byte RAM memory

- 128 Byte SFR register

#### 2.7.2.1 ROM

A 16 kB ROM memory is located in the address range 0000<sub>H</sub> to 3FF7<sub>H</sub>.

#### 2.7.2.1.1 ROM Library Functions and Reset/Wakeup Handlers

The ROM contains the reset handler, operation mode handler, wakeup handler, internal test and debug routines and the ROM Library functions (see in [1]).

#### 2.7.2.1.2 ROM Protections

To protect the ROM code against readout a hardware mechanism is implemented, thus no read operations can be performed on the ROM.

Direct jumping into the ROM area is prevented by a hardware mechanism, thus access to the ROM library functions is granted only via a vector table at the bottom of the ROM address space.

#### 2.7.2.2 FLASH

#### 2.7.2.2.1 FLASH Organization

The FLASH is divided into five sectors. Each sector can be erased and written individually.

Sectors 0 and 1 are accessible for customer usage.

Sectors 2, 3 and 4 are written in the Infineon production site and cannot be erased or re-written by the customer.

- 4000<sub>H</sub> -- 577F<sub>H</sub> (6016 Bytes) Code sector (0): The code sector contains the application software including a CRC16 Checksum (to be written to 577D<sub>H</sub> -- 577E<sub>H</sub>) and the Lockbyte 2 (to be written to 577F<sub>H</sub>).

- 5780<sub>H</sub> -- 57FF<sub>H</sub> (128 Bytes) User Configuration sector (1): The User Configuration sector can store individual device configuration data. It also contains the Lockbyte 3 (to be written to 57FF<sub>H</sub>).

- 5800<sub>H</sub> -- 587F<sub>H</sub> (128 Bytes) Coefficients sector (2): This sector is written during the sensor calibration process and contains calibration coefficients, the unique Sensor ID and Lockbyte 1 (to be written to 587F<sub>H</sub>).

- 5880<sub>H</sub> -- 58BF<sub>H</sub> (64 Bytes) FLASH Configuration sector (3): This sector contains the FLASH driver parameters and other device configuration parameters.

- 58C0<sub>H</sub> -- 58FF<sub>H</sub> (64 Bytes) Reference Cell sector (4): This sector contains the reference cells for FLASH reading.

#### 2.7.2.2.2 FLASH Protection

To protect the FLASH against unauthorized access three FLASH Lockbytes are available.

Note: The Lockbytes are set, if the value in the appropriate FLASH address is programmed to D1<sub>H</sub>. Setting the Lockbyte to 00<sub>H</sub> will result in a unlocked FLASH area. Any other value must not be written to these locations. After programming a Lockbyte, the SP27 has to be reset before the FLASH lock takes effect.

Lockbyte 1 (587F<sub>H</sub>)

This Lockbyte protects the FLASH sectors 2, 3 and 4 against overwriting and erasing. This Lockbyte is programmed at the Infineon production site.

Lockbyte 2 (577F<sub>H</sub>)

This Lockbyte protects the FLASH sector 0 (Code Sector) against overwriting, erasing (except reduced internal production test mode) and read-out to prevent reverse engineering of the application code.

This Lockbyte has to be set at the end of the programming sequence of the Code Sector via the I<sup>2</sup>C Interface (when writing the highest FLASH Line starting at 5760<sub>H</sub>). Once it is set, the available operating modes are reduced according to Figure 4 "Available Operating Modes if Lockbyte 2 is Set" on Page 14.

Lockbyte 3 (57FF<sub>H</sub>)

This Lockbyte protects the FLASH sector 1 (User Configuration Sector) against overwriting and erasing (except reduced internal production test mode).

The Lockbyte can be set either via I<sup>2</sup>C in PROGRAMMING mode in the same programming sequence as Lockbyte 2 is set, or by using a dedicated ROM Library function in NORMAL mode by the application software (see [1]).

#### 2.7.2.3 RAM

The RAM is available as volatile data storage for the application program. Some RAM locations are required by the ROM Library Functions and therefore not freely available for use by the application program. For more details please refer to the ROM Library function guide [1].

The upper 128 bytes of RAM are switched off in POWER DOWN state and lose their contents.

The lower 128 bytes of RAM can be powered during POWER DOWN state. This is selectable using SFR bit CFG2.4[PDLMB].

If not powered in these states, this RAM loses the content, otherwise it can be used as battery buffered storage like the General Purpose Registers (see "General Purpose Registers" on Page 32).

Note: The RAM is not reset at a System Reset or watchdog timeout.

After a Brown Out Reset this feature may be used to possibly recover data.

After Power On Reset the application has to initialize the RAM if needed.

## 3 Special Function Registers

Special Function Registers (SFR) are used to control and monitor the state of the SP27 and its peripherals. The following table shows the naming convention for the SFR descriptions that are used throughout this document

Table 5 Register Naming Convention Wakeup / Reset Value

| State     | Symbol | Description                      |

|-----------|--------|----------------------------------|

| Low       | 0      | Register value is 0 <sub>B</sub> |

| High      | 1      | Register value is 1 <sub>B</sub> |

| Undefined | X      | Register value is undefined      |

| Unchanged | U      | Register value is unchanged      |

**Table 6** provides links within this document to detailed description of the application relevant SFRs. In addition to register names and offset addresses, this table indicates how each SFR behaves after wakeup and reset events. The Wakeup Value column applies in the case of a wakeup event, which includes a watchdog timeout. The Reset Value column applies in the case of a Power On Reset, Brownout Reset or Software Reset event.

Table 6 Registers Overview

| Register Short<br>Name | Register Long Name          | Offset<br>Address | Wakeup Value    | Reset Value     |

|------------------------|-----------------------------|-------------------|-----------------|-----------------|

| Microcontroller        |                             | 1                 |                 |                 |

| ACC                    | Accumulator                 | E0 <sub>H</sub>   | 00 <sub>H</sub> | 00 <sub>H</sub> |

| В                      | Register B                  | F0 <sub>H</sub>   | 00 <sub>H</sub> | 00 <sub>H</sub> |

| DPH                    | Data Pointer (high)         | 83 <sub>H</sub>   | 00 <sub>H</sub> | 00 <sub>H</sub> |

| DPL                    | Data Pointer (low)          | 82 <sub>H</sub>   | 00 <sub>H</sub> | 00 <sub>H</sub> |

| PSW                    | Program Status Word         | D0 <sub>H</sub>   | 00 <sub>H</sub> | 00 <sub>H</sub> |

| SP                     | Stack Pointer               | 81 <sub>H</sub>   | 07 <sub>H</sub> | 07 <sub>H</sub> |

| General Purpose        | Registers <sup>1)</sup>     | ·                 |                 |                 |

| GPR0                   | General Purpose Register 0  | B8 <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR1                   | General Purpose Register 1  | B0 <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR2                   | General Purpose Register 2  | A8 <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR3                   | General Purpose Register 3  | F1 <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR4                   | General Purpose Register 4  | F2 <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR5                   | General Purpose Register 5  | F3 <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR6                   | General Purpose Register 6  | F5 <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR7                   | General Purpose Register 7  | F6 <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR8                   | General Purpose Register 8  | F7 <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR9                   | General Purpose Register 9  | F9 <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

| GPRA                   | General Purpose Register 10 | FA <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

| GPRB                   | General Purpose Register 11 | FB <sub>H</sub>   | UU <sub>H</sub> | XX <sub>H</sub> |

**CONFIDENTIAL**

**Special Function Registers**

Table 6 Registers Overview (cont'd)

| Register Short<br>Name | Register Long Name                             | Offset<br>Address | Wakeup Value          | Reset Value           |

|------------------------|------------------------------------------------|-------------------|-----------------------|-----------------------|

| GPRC                   | General Purpose Register 12                    | FC <sub>H</sub>   | UU <sub>H</sub>       | XX <sub>H</sub>       |

| GPRD                   | General Purpose Register 13                    | FD <sub>H</sub>   | UU <sub>H</sub>       | $XX_H$                |

| GPRE                   | General Purpose Register 14                    | FE <sub>H</sub>   | UU <sub>H</sub>       | $XX_H$                |

| GPRF                   | General Purpose Register 15                    | FF <sub>H</sub>   | UU <sub>H</sub>       | $XX_H$                |

| System Configurati     | on Registers                                   |                   | ,                     |                       |

| CFG0                   | Configuration Register 0                       | F8 <sub>H</sub>   | 0000U000 <sub>B</sub> | 00 <sub>H</sub>       |

| CFG1                   | Configuration Register 1                       | E8 <sub>H</sub>   | 000U000U <sub>B</sub> | 00 <sub>H</sub>       |

| CFG2                   | Configuration Register 2                       | D8 <sub>H</sub>   | 000U1000 <sub>B</sub> | 18 <sub>H</sub>       |

| DSR                    | Diagnosis and Status Register                  | D9 <sub>H</sub>   | 0XUU00XU <sub>B</sub> | 0XXX0000 <sub>B</sub> |

| System Controller      |                                                |                   | ,                     |                       |

| WUF                    | Wakeup Flag Register                           | C0 <sub>H</sub>   | XX <sub>H</sub>       | 00 <sub>H</sub>       |

| WUM                    | Wakeup Mask Register                           | C1 <sub>H</sub>   | UU <sub>H</sub>       | FF <sub>H</sub>       |

| REF                    | Resume Event Flag Register                     | D1 <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| Interval Timer         |                                                |                   |                       |                       |

| ITPR                   | Interval Timer Period Register                 | BC <sub>H</sub>   | UU <sub>H</sub>       | 01 <sub>H</sub>       |

| Interval Timer Prece   | ounter / Calibration                           |                   |                       |                       |

| ITPH                   | Interval Timer Precounter Register (High Byte) | BB <sub>H</sub>   | 0000UUUU <sub>B</sub> | 03 <sub>H</sub>       |

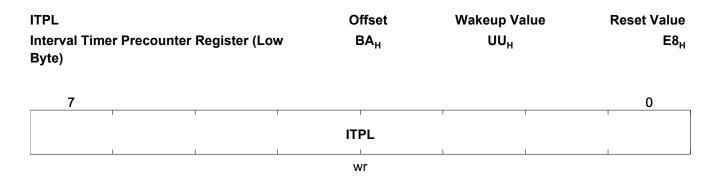

| ITPL                   | Interval Timer Precounter Register (Low Byte)  | BA <sub>H</sub>   | UU <sub>H</sub>       | E8 <sub>H</sub>       |

| Clock Controller       |                                                |                   | 1                     | 1                     |

| DIVIC                  | Internal Clock Divider                         | B9 <sub>H</sub>   | 000000UU <sub>B</sub> | 00 <sub>H</sub>       |

| 16 Bit CRC (Cyclic     | Redundancy Check) Generator/Checker            |                   | <u>'</u>              | 1                     |

| CRCC                   | CRC Control Register                           | A9 <sub>H</sub>   | 02 <sub>H</sub>       | 02 <sub>H</sub>       |

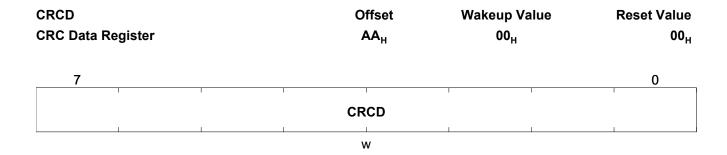

| CRCD                   | CRC Data Register                              | AA <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| CRC0                   | CRC Preload/Result Register 0 (low byte)       | AC <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| CRC1                   | CRC Preload/Result Register 1 (high byte)      | $AD_H$            | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| Pseudo Random Nu       | umber Generator                                |                   | 1                     | 1                     |

| RNGD                   | Random Number Generator Data Register          | $AB_H$            | UU <sub>H</sub>       | 55 <sub>H</sub>       |

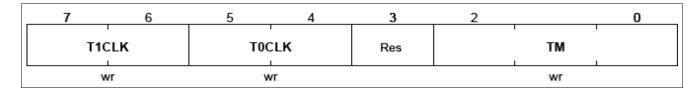

| Timer Unit             |                                                |                   |                       |                       |

| TCON                   | Timer Control Register                         | 88 <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| TMOD                   | Timer Mode Register                            | 89 <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| TH0                    | Timer 0 Register High Byte                     | 8C <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| TL0                    | Timer 0 Register Low Byte                      | 8A <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| TH1                    | Timer 1 Register High Byte                     | 8D <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

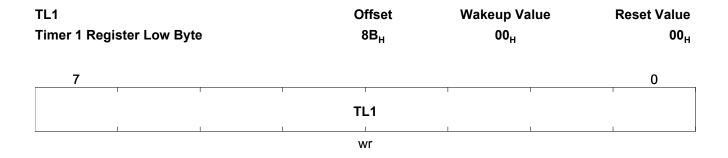

| TL1                    | Timer 1 Register Low Byte                      | 8B <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| General Purpose In     | ·                                              |                   |                       | 1                     |

| P1DIR                  | IO-Port 1 Direction Register                   | 91 <sub>H</sub>   | UU <sub>H</sub>       | FF <sub>H</sub>       |

Table 6 Registers Overview (cont'd)

| Register Short<br>Name     | Register Long Name                   | Offset<br>Address | Wakeup Value          | Reset Value           |

|----------------------------|--------------------------------------|-------------------|-----------------------|-----------------------|

| P1IN                       | IO-Port 1 Data In Register           | 92 <sub>H</sub>   | 00000XXX <sub>B</sub> | 00000XXX <sub>B</sub> |

| P1OUT                      | IO-Port 1 Data Out Register          | 90 <sub>H</sub>   | UU <sub>H</sub>       | FF <sub>H</sub>       |

| P1SENS                     | IO-Port 1 Sensitivity Register       | 93 <sub>H</sub>   | 00000UUU <sub>B</sub> | 00 <sub>H</sub>       |

| I <sup>2</sup> C Interface |                                      |                   |                       |                       |

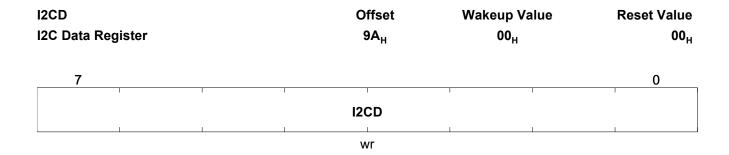

| I2CD                       | I2C Data Register                    | 9A <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| I2CS                       | I2C Status Register                  | 9B <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| <b>Debug Special Fu</b>    | nction Register                      | ,                 | '                     |                       |

| DBCH0                      | Debug Compare Register 0 (high byte) | 95 <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| DBCL0                      | Debug Compare Register 0 (low byte)  | 94 <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| DBCH1                      | Debug Compare Register 1 (high byte) | 9D <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| DBCL1                      | Debug Compare Register 1 (low byte)  | 9C <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| DBTH0                      | Debug Target Register 0 (high byte)  | 97 <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| DBTL0                      | Debug Target Register 0 (low byte)   | 96 <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| DBTH1                      | Debug Target Register 1 (high byte)  | 9F <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

| DBTL1                      | Debug Target Register 1 (low byte)   | 9E <sub>H</sub>   | 00 <sub>H</sub>       | 00 <sub>H</sub>       |

<sup>1)</sup> Reset Value for GRP0 - GPRF is typically undefined (X) except in the case of Software Reset, which leaves the GPR content unchanged (U).

The register is addressed bytewise.

Table 7 Registers Access Types

| Mode         | Symbol                  | Description Hardware (HW)                                                                   | Description Software (SW)                                                                                                                    |

|--------------|-------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Basic Acces  | s Types                 |                                                                                             |                                                                                                                                              |

| write/read   | wr                      | Register is used as input for the HW                                                        | Register is read and writable by SW                                                                                                          |

| read only    | r                       | Register is written by HW                                                                   | Value written by SW is ignored by HW; that is, SW may write any value to this field without affecting HW behavior                            |

| write only   | w                       | Register is written by software and affects hardware behavior with every write by software. | Register is writable by SW. When read, the register does not return the value that has been written previously, but the reset value instead. |

| UNUSED       | -                       | Register is not used by HW.                                                                 | Value written by SW is ignored by HW; that is, SW may write any value to this field without affecting HW behavior.                           |

| Reserved     |                         | Register is used as input for internal HW; Access Type is not documented.                   | Value must be kept by SW. SW read or write any value to this field affecting HW behavior.                                                    |

| Special Acce | ess Types <sup>1)</sup> |                                                                                             | '                                                                                                                                            |

## Table 7 Registers Access Types (cont'd)

| Mode                  | Symbol | Description Hardware (HW)                                                                 | Description Software (SW)                                                                   |

|-----------------------|--------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Read<br>self clearing | rc     | Register is used as input for the HW, the register will be cleared due to a HW mechanism. | Reading from the register generates a strobe signal for the HW. Register is readable by SW. |

| Write self clearing   | wc     | Register is used as input for the HW, the register will be cleared due to a HW mechanism. | Writing to the register generates a strobe signal for the HW. Register is writable by SW.   |

<sup>1)</sup> Optional types

#### 3.1 Microcontroller

The SP27 incorporates an 8051 instruction set compatible microcontroller. It offers an 8-bit data path, several addressing modes (direct, register, register indirect, immediate, index), and accesses the built-in peripherals through SFRs. To handle the sequential nature of PMS applications efficiently, wakeup and resume mechanisms are implemented instead of an interrupt controller.

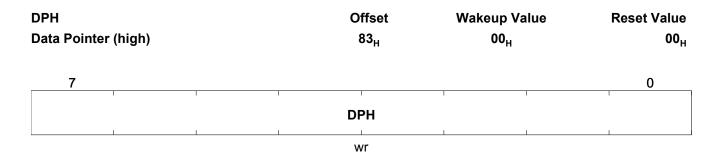

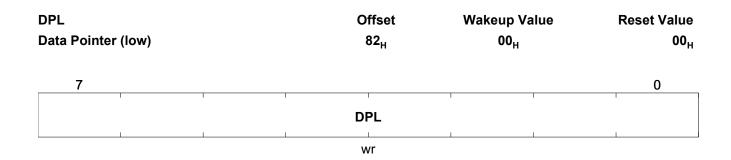

The microcontroller incorporates the following basic SFRs: Accumulator (ACC), Register B (B) and Program Status Word (PSW) are bit addressable registers used to perform arithmetical and logical operations. The Stack Pointer (SP) and Data Pointer (DPTR) are included to allow basic programming structures. The Data Pointer (DPTR) is determined by SFR DPH and SFR DPL.

SFR PSW holds the status of basic arithmetic operations.

#### **Accumulator**

| ACC<br>Accumulator |   |    | ffset<br>E0 <sub>H</sub> | Wakeup Va<br>00 <sub>H</sub> | lue | Reset Value 00 <sub>H</sub> |

|--------------------|---|----|--------------------------|------------------------------|-----|-----------------------------|

| 7                  |   |    |                          |                              |     | 0                           |

|                    |   | AC | cc                       |                              |     |                             |

|                    | I | W  | /r                       |                              |     |                             |

| Field | Bits | Туре | Description            |

|-------|------|------|------------------------|

| ACC   | 7:0  | wr   | Accumulator            |

|       |      |      | Reset: 00 <sub>H</sub> |

#### Register B

| B<br>Register B |   | ( | Offset<br>F0 <sub>H</sub> | Wakeup Va<br>00 <sub>H</sub> | lue | Reset Value<br>00 <sub>H</sub> |

|-----------------|---|---|---------------------------|------------------------------|-----|--------------------------------|

| 7               | I | T |                           | 1 1                          |     | 0                              |

|                 |   |   | В                         |                              |     |                                |

|                 | l |   | wr                        |                              |     |                                |

| Field | Bits | Туре | Description                              |

|-------|------|------|------------------------------------------|

| В     | 7:0  | wr   | Register B 7-0<br>Reset: 00 <sub>H</sub> |

#### **Data Pointer (high)**

**CONFIDENTIAL**

**Special Function Registers**

| Field | Bits | Туре | Description                                |

|-------|------|------|--------------------------------------------|

| DPH   | 7:0  | wr   | Data Pointer (high) Reset: 00 <sub>H</sub> |

#### **Data Pointer (low)**

| Field | Bits | Type | Description                               |

|-------|------|------|-------------------------------------------|

| DPL   | 7:0  | wr   | Data Pointer (low) Reset: 00 <sub>H</sub> |

## **Program Status Word**

| PSW<br>Program Sta | tus Word |    |   | fset<br>10 <sub>H</sub> | Wakeup Va<br>00 <sub>H</sub> | lue | Reset Value<br>00 <sub>H</sub> |  |

|--------------------|----------|----|---|-------------------------|------------------------------|-----|--------------------------------|--|

| 7                  | 6        | 5  | 4 | 3                       | 2                            | 1   | 0                              |  |

| CY                 | AC       | F0 | R | S                       | ov                           | F1  | Р                              |  |

| wr                 | wr       | wr | W | r                       | wr                           | wr  | r                              |  |

| Field | Bits | Туре | Description                                                                                                                                                                                                                                                                                  |

|-------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CY    | 7    | wr   | Carry<br>Reset: 0 <sub>H</sub>                                                                                                                                                                                                                                                               |

| AC    | 6    | wr   | Auxiliary Carry Carry-out for BCD operations Reset: 0 <sub>H</sub>                                                                                                                                                                                                                           |

| F0    | 5    | wr   | Flag 0 Available for general purpose use. Reset: 0 <sub>H</sub>                                                                                                                                                                                                                              |

| RS    | 4:3  | wr   | Register Bank Select  00 <sub>B</sub> Bank 0 (00 <sub>H</sub> - 07 <sub>H</sub> )  01 <sub>B</sub> Bank 1(08 <sub>H</sub> - 0F <sub>H</sub> )  10 <sub>B</sub> Bank 2(10 <sub>H</sub> - 17 <sub>H</sub> )  11 <sub>B</sub> Bank 3(18 <sub>H</sub> - 1F <sub>H</sub> )  Reset: 0 <sub>H</sub> |

| OV    | 2    | wr   | Overflow<br>Reset: 0 <sub>H</sub>                                                                                                                                                                                                                                                            |

| F1    | 1    | wr   | Flag 1 Available for general purpose use. Reset: 0 <sub>H</sub>                                                                                                                                                                                                                              |

| P     | 0    | r    | Parity Set or cleared each instruction cycle to indicate an odd or even number of 1 bits in the accumulator Reset: 0 <sub>H</sub>                                                                                                                                                            |

CONFIDENTIAL

**Special Function Registers**

#### **Stack Pointer**

| SP            | Offset          | Wakeup Value    | Reset Value     |

|---------------|-----------------|-----------------|-----------------|

| Stack Pointer | 81 <sub>H</sub> | 07 <sub>H</sub> | 07 <sub>H</sub> |

|               |                 |                 |                 |

| 7             |                 |                 | 0               |

|               | SP              |                 |                 |

|               | wr              |                 |                 |

| Field | Bits | Type | Description                                                                                                                                          |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP    | 7:0  | wr   | Stack Pointer (SP)                                                                                                                                   |

|       |      |      | SP is incremented before data is pushed and decremented after data is popped. SP always points to the last valid stack byte.  Reset: 07 <sub>H</sub> |

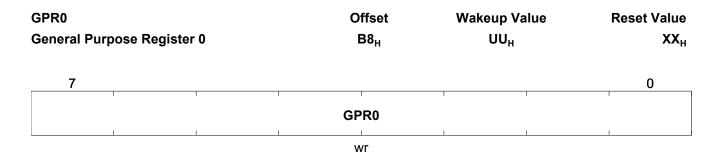

## 3.2 General Purpose Registers

The SP27 incorporates 16 general purpose registers that can be used by the application to store data beyond a POWER DOWN state period. The GPR Registers are not cleared after a System Reset. After a Power On Reset, the GPR contents will be undefined.

#### General Purpose Register 0

| Field | Bits | Туре | Description            |

|-------|------|------|------------------------|

| GPR0  | 7:0  | wr   | General Purpose        |

|       |      |      | Reset: XX <sub>H</sub> |

General Purpose Registers 0 - F are freely available for application program use. GPR0, GPR1, GPR2 are located at Offset Addresses that make them well suited for bit manipulation. Placing bit variables in these GPRs will result in more efficient CPU operation.

Table 8 Register 0 to F<sup>1)</sup>

| Register Short Name | Register Long Name          | Offset Address  | Wakeup Value    | Reset Value     |

|---------------------|-----------------------------|-----------------|-----------------|-----------------|

| GPR0                | General Purpose Register 0  | B8 <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR1                | General Purpose Register 1  | B0 <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR2                | General Purpose Register 2  | A8 <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR3                | General Purpose Register 3  | F1 <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR4                | General Purpose Register 4  | F2 <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR5                | General Purpose Register 5  | F3 <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR6                | General Purpose Register 6  | F5 <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR7                | General Purpose Register 7  | F6 <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR8                | General Purpose Register 8  | F7 <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPR9                | General Purpose Register 9  | F9 <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPRA                | General Purpose Register 10 | FA <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPRB                | General Purpose Register 11 | FB <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPRC                | General Purpose Register 12 | FC <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPRD                | General Purpose Register 13 | FD <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

Table 8 Register 0 to F<sup>1)</sup> (cont'd)

| Register Short Name | Register Long Name          | Offset Address  | Wakeup Value    | Reset Value     |

|---------------------|-----------------------------|-----------------|-----------------|-----------------|

| GPRE                | General Purpose Register 14 | FE <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

| GPRF                | General Purpose Register 15 | FF <sub>H</sub> | UU <sub>H</sub> | XX <sub>H</sub> |

<sup>1)</sup> Reset Value for GRP0 - GPRF is typically undefined (X) except in the case of Software Reset, which leaves the GPR content unchanged (U).

## 3.3 System Configuration Registers

The system configuration registers can be used for:

- Initiating state transitions (SFR CFG0)

- Enabling or disabling peripherals (SFR CFG1 and SFR CFG2)

- Monitoring the operation mode, the system state and peripherals (SFR DSR)

#### **Configuration Register 0**

| CFG0<br>Configuration | FG0 Offset Wakeup Value onfiguration Register 0 F8 <sub>H</sub> 0000U000 <sub>B</sub> |      |     |     |     | Reset Value<br>00 <sub>H</sub> |     |

|-----------------------|---------------------------------------------------------------------------------------|------|-----|-----|-----|--------------------------------|-----|

| 7                     | 6                                                                                     | 5    | 4   | 3   | 2   | 1                              | 0   |

| PDWN                  | Res                                                                                   | IDLE | Res | FTM | Res | UNUSED                         | Res |

| wr                    |                                                                                       | wr   |     | wr  |     | -                              |     |

| Field  | Bits | Туре | Description                                                                                                                                                                                                                                                                                           |

|--------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDWN   | 7    | wr   | Enter POWER DOWN State  If set to 1 by software the POWER DOWN state is entered; This bit is automatically reset to 0 by the system controller after a wakeup. Entering POWER DOWN state is handled by a ROM Library function. It is not recommended to set this bit manually.  Reset: 0 <sub>H</sub> |

| Res    | 6    | -    | Reserved This bit must be set to $0_B$ . Reset: $0_H$                                                                                                                                                                                                                                                 |

| IDLE   | 5    | wr   | Enter IDLE State If set to 1 by software the IDLE state is entered; This bit is automatically reset to 0 by the system controller after a resume event occurs.  Reset: 0 <sub>H</sub>                                                                                                                 |

| Res    | 4    | -    | Reserved This bit must be set to 0 <sub>B</sub> Reset: 0 <sub>H</sub>                                                                                                                                                                                                                                 |

| FTM    | 3    | wr   | Enable Functional Test Mode This mode is used only during internal device testing.  0 <sub>B</sub> FTM disabled 1 <sub>B</sub> FTM enable Reset: 0 <sub>H</sub>                                                                                                                                       |

| Res    | 2    |      | Reserved This bit must be set to $0_B$ . Reset: $0_H$                                                                                                                                                                                                                                                 |

| UNUSED | 1    | -    | UNUSED<br>Reset: 0 <sub>H</sub>                                                                                                                                                                                                                                                                       |

## **CONFIDENTIAL**

## **Special Function Registers**

| Field | Bits | Туре | Description                              |

|-------|------|------|------------------------------------------|

| Res   | 0    |      | Reserved                                 |

|       |      |      | This bit must be set to 0 <sub>B</sub> . |

|       |      |      | Reset: 0 <sub>H</sub>                    |

## **Configuration Register 1**

| CFG1<br>Configuration | on Register 1 |       |     | ffset<br>E8 <sub>H</sub> | Wakeup Va<br>000U000U |        | Reset Value<br>00 <sub>H</sub> |  |

|-----------------------|---------------|-------|-----|--------------------------|-----------------------|--------|--------------------------------|--|

| 7                     | 6             | 5     | 4   | 3                        | 2                     | 1      | 0                              |  |

| Res                   | I2CEN         | RNGEN | Res | Res                      | ITRD                  | ITINIT | ITEN                           |  |

|                       | wr            | wc    |     |                          | wr                    | r      | wr                             |  |

| Field | Bits | Туре | Description                                                                                                                                                                                                                                                                               |

|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Res   | 7    |      | Reserved This bit must be set to $0_B$ . Reset: $0_H$                                                                                                                                                                                                                                     |

| I2CEN | 6    | wr   | I2C Enable  0 <sub>B</sub> Standard I/O Port functionality  1 <sub>B</sub> I2C functionality on Pins PP0/SCL and PP1/SDA  Reset: 0 <sub>H</sub>                                                                                                                                           |

| RNGEN | 5    | wc   | Random Number Generator Enable  0 <sub>B</sub> Cleared automatically after random number is generated  1 <sub>B</sub> Initiates generation of a new pseudo random number  Reset: 0 <sub>H</sub>                                                                                           |

| Res   | 4    | -    | Reserved This bit must be set to $0_B$ Reset: $0_H$                                                                                                                                                                                                                                       |

| Res   | 3    |      | Reserved This bit must be set to $0_B$ . Reset: $0_H$                                                                                                                                                                                                                                     |

| ITRD  | 2    | Wr   | Interval Timer Read Enable To safely read SFR ITPR, this bit should be set to 1 prior to reading ITPR. After the ITPR contents are read, this bit should be checked.  0 <sub>B</sub> SFR ITPR read result is not valid 1 <sub>B</sub> SFR ITPR read result is valid Reset: 0 <sub>H</sub> |

| Field  | Bits | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |