### 1 Applications

- Desktop and Server VR buck-converter

- Single Phase and Multiphase POL

- CPU/GPU Regulation in Notebook, Desktop Graphics Cards, DDR Memory, Graphic Memory

- High Power Density Voltage Regulator Modules (VRM)

- Qualified for DCDC industrial applications based on JEDEC (JESD47, JESD22, J-STD20)

#### 2 Features

- For synchronous buck converter step down voltage applications

- Maximum average current of 25 A

- Input voltage range +4.5 V to +16 V

- Power MOSFETs rated 25 V

- Fast switching technology for improved performance at high switching frequencies (> 500 kHz)

- Remote driver disable function

- Includes bootstrap diode

- Undervoltage lockout

- · Shoot through protection

- +5 V high side and low side MOSFETs driving voltage

- Compatible to standard +3.3 V PWM controller integrated circuits

- Tri-state PWM input functionality

- Small package: PG-IQFN-30-2 (4 x 4 x 1 mm<sup>3</sup>)

- RoHS compliant

- Thermal warning

Table 1 Product Identification

| Part Number | Temp Range   | Package                                   | Marking |

|-------------|--------------|-------------------------------------------|---------|

| TDA21242    | -40 to 125°C | PG-IQFN-30-2 (4 x 4 x 1 mm <sup>3</sup> ) | 21242   |

Figure 1 Picture of the Product

# 3 Description

## 3.1 Pinout

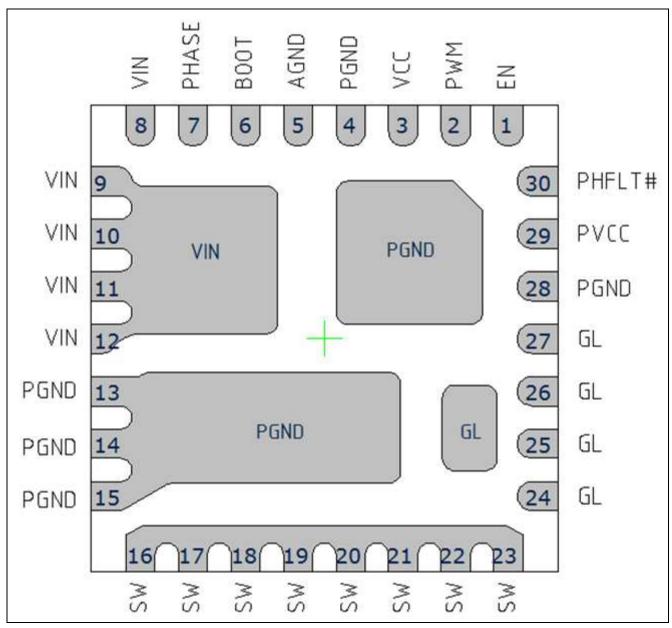

Figure 2 Pinout, Numbering and Name of Pins (transparent top view)

## Table 2 I/O Signals

| Pin No. | Name   | Pin Type | Buffer Type  | Function                                                                                                                                          |

|---------|--------|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | PWM    | I        | +3.3 V logic | PWM drive logic input                                                                                                                             |

|         |        |          |              | The tri-state PWM input is compatible with 3.3 V.                                                                                                 |

| 6       | BOOT   | 1        | Analog       | Bootstrap voltage pin                                                                                                                             |

|         |        |          |              | Connect to BOOT capacitor                                                                                                                         |

| 7       | PHASE  | 1        | Analog       | Switch node (reference for Boot voltage)                                                                                                          |

|         |        |          |              | internally connected to SW pin, connect to BOOT capacitor                                                                                         |

| 16 – 23 | SW     | 0        | Analog       | Switch node output                                                                                                                                |

|         |        |          |              | High current output switching node                                                                                                                |

| 24 - 27 | GL     | 0        | Analog       | Low-Side Gate                                                                                                                                     |

|         |        |          |              | Test point for Low Side MOSFET gate signal                                                                                                        |

| 30      | PHFLT# | 0        | +3.3 V logic | Thermal Warning                                                                                                                                   |

|         |        |          |              | Connect through a resistor to 3.3V. When the thermal protection threshold is tripped, the PHFLT# pin is being pulled low. Leave open if not used. |

| 1       | EN     | 1        | +3.3 V logic | Enable signal (active high)                                                                                                                       |

|         |        |          |              | Connect to GND to disable the IC.                                                                                                                 |

## Table 3 Power Supply

| Pin No.          | Name | Pin Type | Function                                    |

|------------------|------|----------|---------------------------------------------|

| 8 - 12, Vin pins | VIN  | POWER    | Input voltage                               |

| and pad          |      |          | Supply of the drain of the high-side MOSFET |

| 29               | PVCC | POWER    | FET gate supply voltage                     |

|                  |      |          | High- and low-side gate drive supply        |

| 3                | VCC  | POWER    | Logic supply voltage                        |

|                  |      |          | Bias voltage for the internal logic         |

### Table 4 Ground Pins

| Pin No.            | Name | Pin Type | Function                                                                                      |

|--------------------|------|----------|-----------------------------------------------------------------------------------------------|

| 5                  | AGND | GND      | Control signal ground                                                                         |

|                    |      |          | Should be connected to PGND externally                                                        |

|                    |      |          |                                                                                               |

| 4, 13 – 15, 28     | PGND | GND      | Power ground                                                                                  |

| PGND pins and pads |      |          | All these pins must be connected to the power GND plane through multiple low inductance vias. |

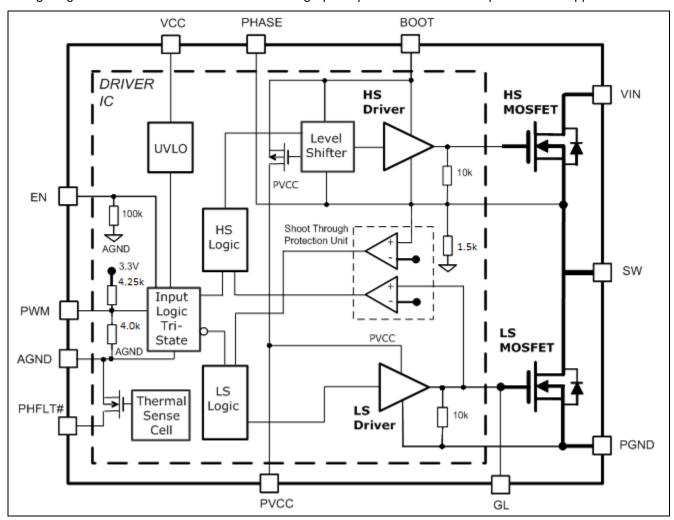

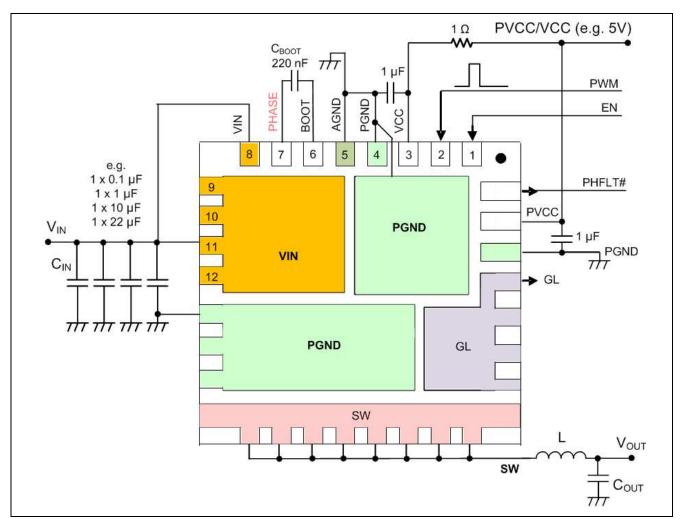

### 3.2 General Description

The Infineon TDA21242 is a multichip module that incorporates Infineon's premier MOSFET technology for a single high-side and a single low-side MOSFET coupled with a robust, high performance, high switching frequency gate driver in a single PG-IQFN-30-2 package. The optimized gate timing allows for significant light load efficiency improvements over discrete solutions.

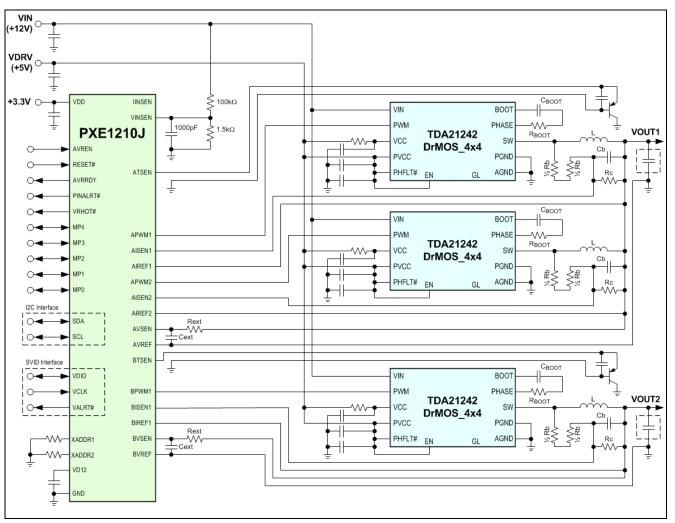

When combined with Infineon's family of digital multi-phase controllers, the TDA21242 forms a complete corevoltage regulator solution for advanced micro and graphics processors as well as point-of-load applications.

Figure 3 Simplified Block Diagram

## 4 Electrical Specification

### 4.1 Absolute Maximum Ratings

Note:  $T_A = 25^{\circ}C$

Stresses above those listed in Table 5 "Absolute Maximum Ratings" may cause permanent damage to the device. These are absolute stress ratings only and operation of the device is not implied or recommended at these or any other conditions in excess of those given in the operational sections of this specification. Exposure over values of the recommended ratings (Table 8) for extended periods may adversely affect the operation and reliability of the device.

Table 5 Absolute Maximum Ratings

| Parameter                         | Symbol                                   |                 | Values | ;               | Unit                                  | Note / Test Condition               |

|-----------------------------------|------------------------------------------|-----------------|--------|-----------------|---------------------------------------|-------------------------------------|

|                                   |                                          | Min.            | Тур.   | Max.            |                                       |                                     |

| Maximum average load current      | I <sub>OUT</sub>                         | _               | _      | 25              | Α                                     |                                     |

| Input Voltage                     | V <sub>IN</sub> (DC)                     | -0.30           | _      | 21              |                                       |                                     |

| Logic supply voltage              | V <sub>VCC</sub> (DC)                    | -0.30           | _      | 8               |                                       |                                     |

| High- and low-side driver voltage | V <sub>PVCC</sub> (DC)                   | -0.30           | _      | 8               |                                       |                                     |

| Switch / Phase node voltage       | V <sub>SW/PHASE</sub> (DC)               | -1              | _      | 25              |                                       |                                     |

|                                   | V <sub>PHASE</sub> (AC)                  | -8 <sup>1</sup> | _      | _               |                                       | Driver limitation                   |

| HS-MOSFET voltage spike           | V <sub>IN</sub> -V <sub>PHASE</sub> (AC) | _               | _      | 32 <sup>2</sup> |                                       | 2 ns above 25 V                     |

| LS-MOSFET voltage spike           | $V_{SW}$ - $V_{PGND}$ (AC)               | _               | -      | 32 <sup>2</sup> | V                                     |                                     |

| BOOT voltage                      | V <sub>BOOT</sub> (DC)                   | -0.3            | _      | 25              | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |                                     |

|                                   | V <sub>BOOT</sub> (AC)                   | _               | _      | 30 <sup>1</sup> |                                       |                                     |

|                                   | V <sub>BOOT-PHASE</sub> (DC)             | -0.3            | _      | 8               |                                       |                                     |

| EN voltage                        | $V_{EN}$                                 | -0.3            | _      | 4               |                                       | Maximum value valid for             |

| PWM voltage                       | $V_{PWM}$                                | -0.3            | _      | 4               |                                       | operation up to 1h accumulated over |

| PHFLT#                            | $V_{	ext{PHFLT}\#}$                      | -0.3            | _      | 4               |                                       | lifetime, else the                  |

|                                   |                                          |                 |        |                 |                                       | maximum value is 3.6V               |

| Junction temperature              | $T_{Jmax}$                               | -40             | _      | 150             | °C                                    |                                     |

| Storage temperature               | T <sub>STG</sub>                         | -55             | _      | 150             | 1-0                                   |                                     |

Note: All rated voltages are relative to voltages on the AGND and PGND pins unless otherwise specified.

<sup>&</sup>lt;sup>1</sup> AC is limited to 10 ns

<sup>&</sup>lt;sup>2</sup> AC is limited to 2 ns

#### 4.2 **Thermal Characteristics**

Table 6 **Thermal Characteristics**

| Parameter                                                                | Symbol           |      | Values | ;    | Unit | Note / Test |

|--------------------------------------------------------------------------|------------------|------|--------|------|------|-------------|

|                                                                          |                  | Min. | Тур.   | Max. |      | Condition   |

| Thermal resistance to case (soldering point)                             | $\theta_{JC}$    | _    | _      | 1    | K/W  | _           |

| Thermal resistance to top of package                                     | $\theta_{JCtop}$ | _    | _      | 36   |      | _           |

| Thermal resistance to ambient                                            | $\theta_{JA}$    | _    | 13     | _    |      | Still air   |

| $(P_{loss} = 4.5 \text{ W}, T_A = 70 \text{ °C}, 8 \text{ layer server}$ | 0/1              |      |        |      |      |             |

| board with 2 oz copper per layer)                                        |                  |      |        |      |      |             |

#### **Recommended Operating Conditions and Electrical Characteristics** 4.3

Note:  $V_{DRV} = V_{CIN} = 5 V$ ,  $T_A = 25^{\circ}C$

Table 7 **Recommended Operating Conditions**

| Parameter             | Symbol            |      | Values | S               | Unit | Note / Test Condition               |

|-----------------------|-------------------|------|--------|-----------------|------|-------------------------------------|

|                       |                   | Min. | Тур.   | Max.            | 1    |                                     |

| Input voltage         | V <sub>IN</sub>   | 5    | _      | 16 <sup>3</sup> | V    | For telecom applications see note 3 |

| MOSFET driver voltage | V <sub>PVCC</sub> | 4.5  | 5      | 7               |      |                                     |

| Logic supply voltage  | V <sub>VCC</sub>  | 4.5  | 5      | 7               |      |                                     |

| Frequency of the PWM  | f <sub>SW</sub>   | _    | _      | 1.0             | MHz  |                                     |

| Junction temperature  | T <sub>iOP</sub>  | -40  | _      | 125             | °C   |                                     |

$<sup>^3</sup>$  In telecom applications the recommended maximum voltage for V<sub>IN</sub> is 13.2V unless a boot resistor is used (see Figure 6) to limit the voltage spike V<sub>PHASE</sub>-V<sub>PGND</sub> (AC) to 26V.

Table 8 Voltage Supply And Biasing Current

| Parameter            | Symbol                              |      | Values |      | Unit | Note / Test Condition                      |

|----------------------|-------------------------------------|------|--------|------|------|--------------------------------------------|

|                      |                                     | Min. | Тур.   | Max. |      |                                            |

| UVLO BOOT rising     | $V_{\text{UVLOBOOT}_{\text{R}}}$    | _    | 4.0    | _    | .,   | V <sub>BOOT</sub> -V <sub>SW</sub> rising  |

| UVLO BOOT falling    | $V_{UVLOBOOT\_F}$                   | _    | 3.8    | _    | V    | V <sub>BOOT</sub> -V <sub>SW</sub> falling |

| UVLO rising          | $V_{\text{UVLO}_{R}}$               | _    | _      | 4.2  | v    | VCC rising                                 |

| UVLO falling         | $V_{UVLO_{F}}$                      | 3.7  | _      | -    | ] V  | VCC falling                                |

| Driver current       | I <sub>PVCC_300kHz</sub>            | _    | 4.5    | _    | А    | EN = 3.3 V, f <sub>SW</sub> = 300 kHz      |

|                      | I <sub>PVCC_1MHz</sub>              | _    | 15     | _    | mA   | EN = 3.3 V, f <sub>SW</sub> = 1 MHz        |

|                      | I <sub>PVCC_PWML</sub>              | _    | 710    | -    |      | EN = 3.3 V, PWM = 0V                       |

|                      | I <sub>PVCC_PWMH</sub>              | _    | 210    | _    | μA   | EN = 0V, PWM=3.3V,                         |

| IC current (control) | I <sub>VCC_PWML</sub>               | _    | 1      | _    | mA   | EN = 3.3 V, PWM = 0 V                      |

|                      | I <sub>vcc_o</sub>                  | _    | 630    | -    |      | EN = 3.3 V, PWM = Open                     |

| IC quiescent         | I <sub>CC</sub> + I <sub>PVCC</sub> | _    | 840    | _    | μA   | EN = 0V, PWM = Open                        |

| Pre-Bias at SW       | V <sub>SW_0</sub>                   |      | 160    | 180  | mV   | VCC and PVCC present                       |

Table 9 Logic Inputs And Threshold

| Parame | ter                                          | Symbol                 |     | Values |     | Unit | Note / Test Condition    |

|--------|----------------------------------------------|------------------------|-----|--------|-----|------|--------------------------|

|        |                                              | Min. Typ. Max.         |     |        |     |      |                          |

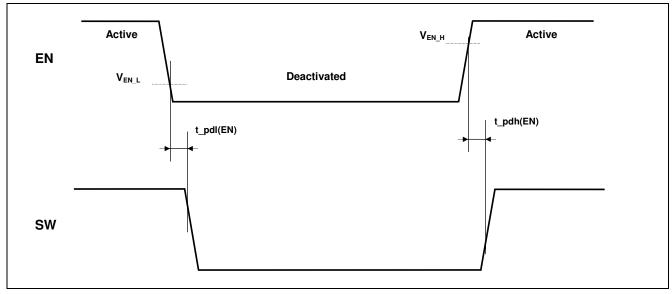

| EN     | Input low                                    | V <sub>EN_L</sub>      | _   | _      | 0.8 | V    | V <sub>EN</sub> falling  |

|        | Input high                                   | V <sub>EN_H</sub>      | 2.0 | _      | _   | V    | V <sub>EN</sub> rising   |

|        | Sink current                                 | I <sub>EN</sub>        | _   | 10     | _   | μA   | V <sub>EN</sub> = 1 V    |

| PWM    | Input low                                    | $V_{PWM\_L}$           | _   | _      | 0.6 | V    | V <sub>PWM</sub> falling |

|        | Input high                                   | $V_{PWM\_H}$           | 2.6 | _      | _   | V    | V <sub>PWM</sub> rising  |

|        | Input resistance                             | R <sub>IN-PWM</sub>    | _   | 2      | _   | kΩ   | V <sub>PWM</sub> = 1 V   |

|        | Open voltage                                 | $V_{PWM\_O}$           | _   | 1.6    | _   |      | $V_{PWM\_O}$             |

|        | Tri-state<br>shutdown<br>window <sup>4</sup> | V <sub>PWM_S</sub>     | 1.2 | _      | 2.0 | V    |                          |

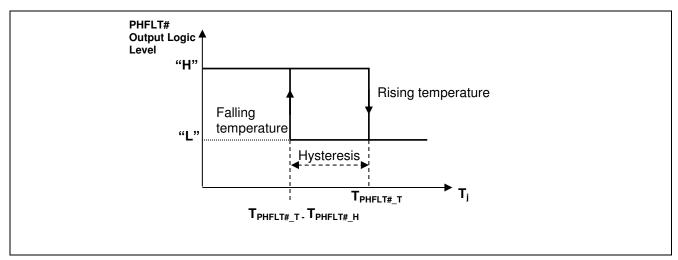

| PHFLT# | Warning<br>Temperature <sup>5</sup>          | T <sub>PHFLT#_T</sub>  | _   | 140    | _   | °C   |                          |

|        | Thermal warning accuracy5                    | dT <sub>PHFLT#_T</sub> | -10 | _      | 10  | K    |                          |

|        | Hysteresis5                                  | T <sub>PHFLT#_H</sub>  | _   | 10     | _   |      |                          |

|        | On resistance                                | R <sub>PHFLT#_PD</sub> | _   | 37.5   | 80  | Ω    | I <sub>LOAD</sub> = 8mA  |

|        | Leakage current                              | I <sub>PHFLT#_LK</sub> | _   | 0.1    | 5   | μΑ   |                          |

<sup>&</sup>lt;sup>4</sup> Maximum voltage range for tri-state

<sup>&</sup>lt;sup>5</sup> The thresholds for temperature warning are verified by design and not subject to production test.

Table 10 Timing Characteristics

| Parameter                                | Symbol        |      | Values | S    | Unit | Note / Test Condition                             |

|------------------------------------------|---------------|------|--------|------|------|---------------------------------------------------|

|                                          |               | Min. | Тур.   | Max. |      |                                                   |

| PWM tri-state to SW rising delay         | t_pts         | _    | 15     | _    |      |                                                   |

| PWM tri-state to SW falling delay        | t_pts2        | _    | 15     | _    |      |                                                   |

| SW Shutdown hold-Off time from PWM low   | t_tsshd       | _    | 50     | _    |      |                                                   |

| SW Shutdown hold-Off time from PWM high  | t_tssh        | _    | 50     | _    |      |                                                   |

| PWM to SW turn-off propagation delay     | t_pdlu        | _    | 20     | _    |      |                                                   |

| PWM to SW turn-on propagation delay      | t_pdll        | _    | 10     | _    | ns   |                                                   |

| DR_EN turn-off propagation delay falling | t_pdl_DR_EN   | _    | 20     | _    |      |                                                   |

| DR_EN turn-on propagation delay rising   | t_pdh_DR_EN   | _    | 20     | _    |      |                                                   |

| UVLO-BOOT-on time                        | t_UVLOBOOTon  | _    | 200    | _    |      | Pulse pattern issued to GL in                     |

| UVLO-BOOT-off time                       | t_UVLOBOOToff | _    | 200    | _    |      | UVLO-BOOT                                         |

| PWM minimum pulse width                  | ton_min_PWM   | _    | 25     | _    |      | When PWM change is recognized, the output remains |

| PWM minimum off time                     | toff_min_PWM  | _    | 30     | _    |      | in the new state for these minimum times.         |

# 5 Theory of Operation

The TDA21242 incorporates a high performance gate driver, one high-side power MOSFET and one low-side power MOSFET in a single PG-IQFN-30-2 package. The advantages of this arrangement are found in the areas of increased performance, increased efficiency and lower overall package and layout inductance. This module is ideal for use in Synchronous Buck Regulators.

The power MOSFETs are optimized for 5 V gate drive enabling excellent high load and light load efficiency. The gate driver is a robust high-performance driver rated at the switching node for DC voltages ranging from -1 V to +21 V. The power density for transmitted power of this approach is approximately 50 W within a 16 mm<sup>2</sup> area.

#### 5.1 Driver Characteristics

The gate driver of the TDA21242 has 2 voltage inputs, VCC and PVCC. VCC is the 5 V logic supply for the driver. PVCC sets the driving voltage for the high side and low side MOSFETs. The reference for the gate driver control circuit (VCC) is AGND. To decouple the sensitive control circuitry (logic supply) from a noisy environment a ceramic capacitor must be placed between VCC and AGND close to the pins. PVCC needs also to be decoupled using a ceramic capacitor (MLCC) between PVCC and PGND in close proximity to the pins. PGND serves as reference for the power circuitry including the driver output stage.

Referring to the block diagram page 4, VCC is internally connected to the UVLO circuit. It will force shut-down for insufficient VCC voltage. PVCC supplies the floating high-side drive – consisting of an active boot circuit - and the low side drive circuit. During undervoltage both GH and GL are driven low actively; further passive pull-down (10  $k\Omega$ ) is placed across gate-source of both FETs.

An additional UVLO circuitry, sensing the BOOT voltage level, is implemented to enable a recharge of the boot capacitor when its voltage is too low for a complete turn-on of the HS-MOSFET.

Proper response of the driver to the PWM signal is only guaranteed when UVLO and UVLO BOOT have been cleared by their respective supply voltages (Table 8). Therefore, it is strongly recommended to only issue pulses to PWM when no UVLO conditions are present. The power down sequence should set PWM to HiZ with regard to the internal threshold before ramping down VIN, PVCC and VCC respectively.

#### 5.2 Inputs to the Internal Control Circuits

The PWM is the control input to the IC from an external PWM controller and is compatible with 3.3 V.

The PWM input has tri-state functionality. When the voltage remains in the specified PWM-shutdown-window for at least the PWM-shutdown-holdoff time t\_tsshd, the operation will be suspended by keeping both MOSFET gate outputs low. Once left open, the pin is held internally at a level of  $V_{PWM O} = 1.6 \text{ V}$  level.

Table 11 PWM Pin Functionality

| PWM logic level                         | Driver output       |

|-----------------------------------------|---------------------|

| Low                                     | GL= High, GH = Low  |

| High                                    | GL = Low, GH = High |

| Open (left floating, or High impedance) | GL = Low, GH = Low  |

The PWM threshold voltages VPMW\_O, VPWM\_H, VPWM\_L do not vary over the wide range of VCIN supply voltages (4.5 V to 8 V).

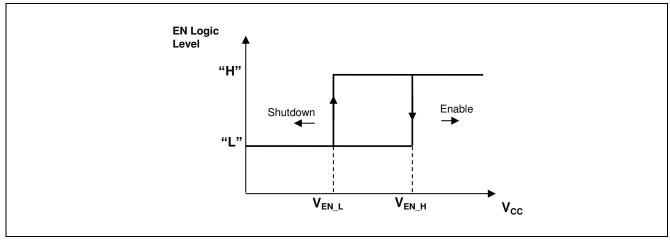

The EN is an active high signal. When EN is being pulled low, the power stage will be disabled.

Figure 4 Enable (EN) signal logic levels

Table 12 EN Pin Functionality

| EN logic level                          | Driver output                     |

|-----------------------------------------|-----------------------------------|

| Low                                     | Shutdown : GL = GH = Low          |

| High                                    | Enable : GL = Active, GH = Active |

| Open (left floating, or High impedance) | Shutdown : GL = GH = Low          |

#### 5.3 Thermal protection

The **PHFLT#** pin is a digital monitoring output for the thermal warning. It does not affect the operation of the driver nor does it shut down the device.

When the driver junction temperature exceeds the thermal warning threshold of 140 °C (typ) the open drain output PHFLT# will be pulled low. Externally PHFLT# has to be connected to a supply (e.g. +3.3 V) by a resistor in the range of 10 k $\Omega$ . When the temperature of the driver junction decreases below the level of thermal warning threshold minus hysteresis (10 K typ.), the pin **PHFLT#** is released. V<sub>PHFLT#</sub> is being pulled up by the external resistance. If the thermal warning feature is not used the pin can be left floating.

Figure 5 Thermal warning

#### 5.4 Shoot Through Protection

The TDA21242 driver includes gate drive functionality to protect against shoot through. In order to protect the power stage from overlap, both high-side and low-side MOSFETs being on at the same time, the adaptive control circuitry monitors specific voltages. When the PWM signal transitions to low, the high-side MOSFET will begin to turn off after the propagation delay time t\_pdlu. When V<sub>GS</sub> of the high-side MOSFET is discharged below 1 V (a threshold below which the high-side MOSFET is off), a secondary delay t\_pdhl is initiated. After that delay the low-side MOSFET turns on regardless of the state of the "SW" pin. It ensures that the converter can sink current efficiently and the bootstrap capacitor will be refreshed appropriately during each switching cycle. See Figure 8 for more detail.

#### 5.5 UVLO – BOOT Protection

After long tristate conditions the voltage of the boot capacitor may be too small to completely enhance the HS-MOSFET when PWM enables GH directly after. Therefore, a monitoring circuit is being implemented to detect a lower threshold at which GH can safely be turned on. If the voltage across the boot capacitor has been dropping to this threshold a boot refresh circuit engages until an upper threshold has been reached.

The recharge is being done by intervals of repetitively pulling GL high for t\_UVLOBOOTon followed by t\_UVLOBOOToff driving GL low to reset the output current to zero. When the voltage across the boot capacitor has reached an upper threshold the recharge cycles stop.

The PWM input always takes priority over the boot refresh circuit when it is logic "H" or logic "L".

## 6 Application

### 6.1 Implementation

Figure 6 Pin Interconnection Outline (example, transparent top view)

Note:

- 1. Pin PHASE is internally connected to SW node

- 2. It is recommended to place a RC filter between VCC and PVCC as shown.

## 6.2 Typical Application

Figure 7 2+1 - phase voltage regulator - typical application (simplified schematic)

# 7 Gate Driver Timing Diagram

Figure 8 Adaptive Gate Driver Timing Diagram

Figure 9 EN Timing Diagram

# 8 Performance Curves – Typical Data

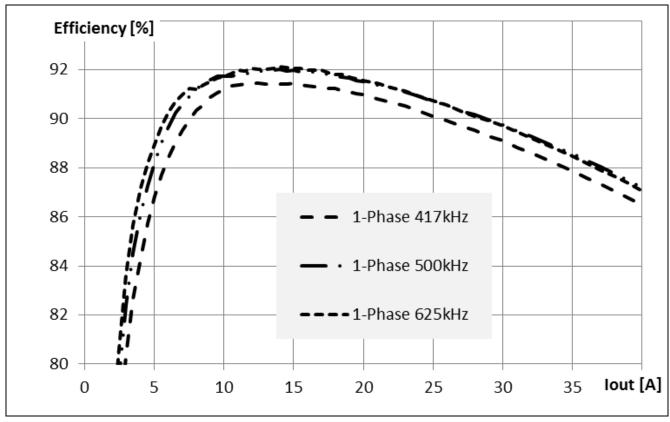

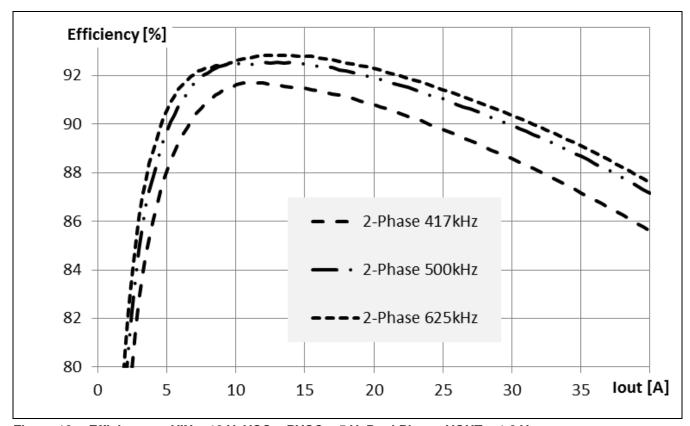

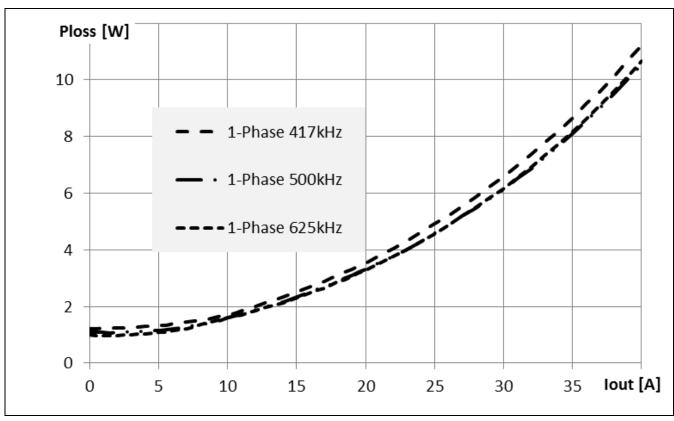

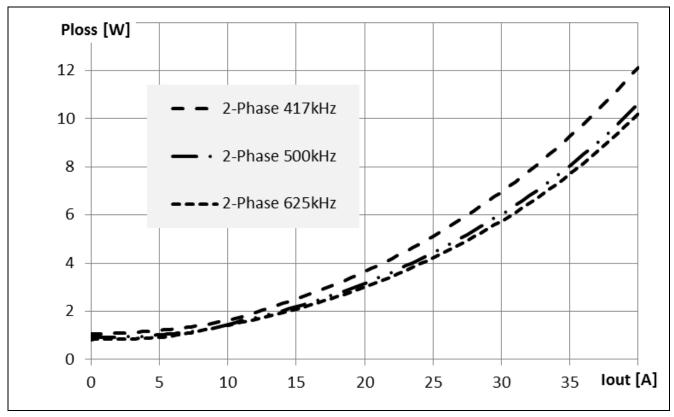

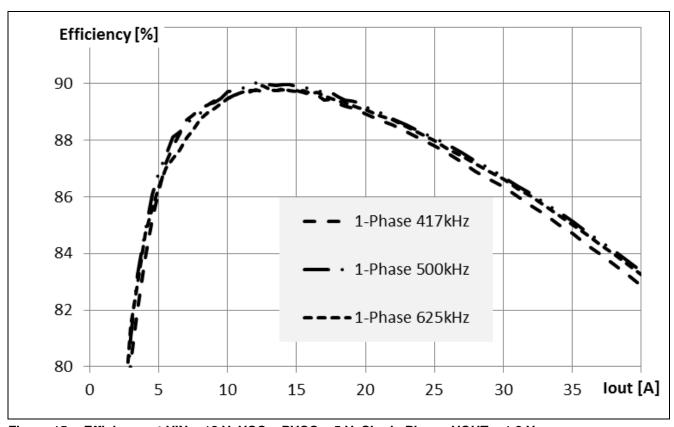

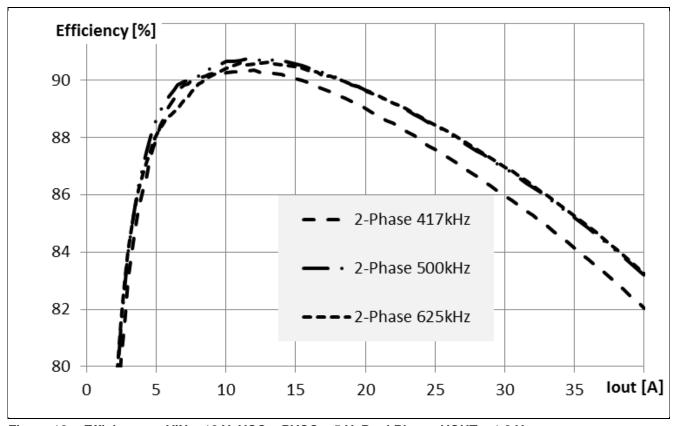

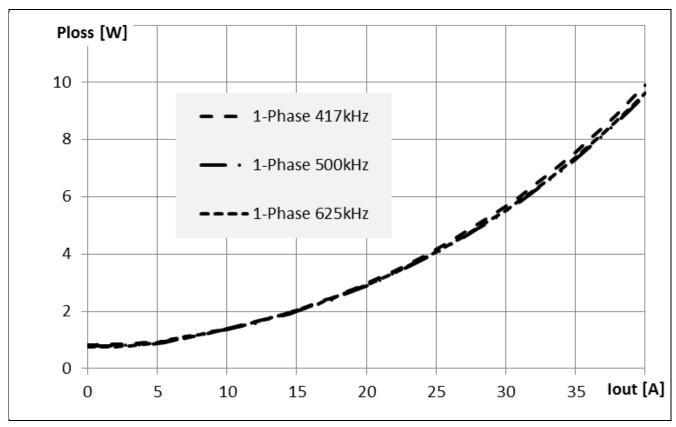

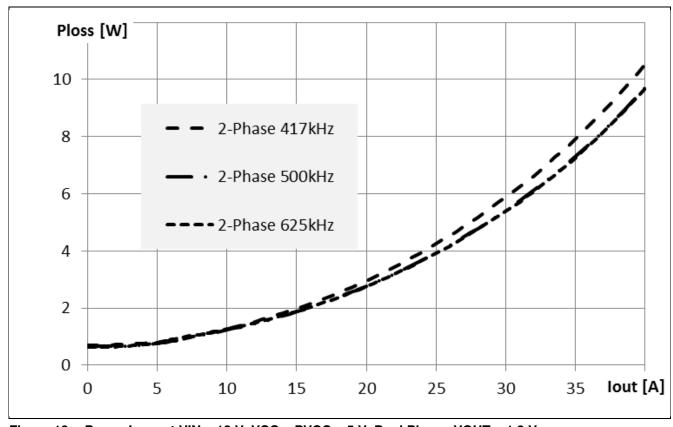

Operating conditions (unless otherwise specified): VIN = +12 V, VCC = PVCC = +5 V, VOUT = +1.8 V, fsw = 600 kHz, 150nH (Cooper, FP0906R1-R15, DCR = 0.29 m $\Omega$ ) inductor, TA = 25 °C, airflow = 300 LFM, no heatsink. Efficiency and power loss reported herein include only TDA21242 losses for a single phase on an 8-layer server board.

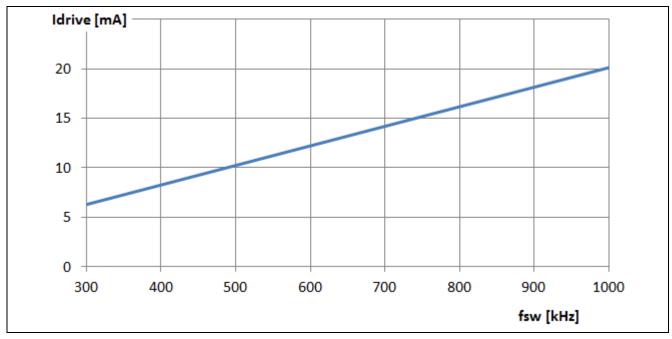

### 8.1 Driver Current versus Switching Frequency

Figure 10 Driver Current over Switching Frequency in CCM Operation

### 8.2 Efficiency and Power Loss

Figure 11 Efficiency at VIN = 12 V, VCC = PVCC = 5 V, Single Phase, VOUT = 1.8 V

Figure 12 Efficiency at VIN = 12 V, VCC = PVCC = 5 V, Dual Phase, VOUT = 1.8 V

Figure 13 Power Loss at VIN = 12 V, VCC = PVCC = 5 V, Single Phase, VOUT = 1.8 V

Figure 14 Power Loss at VIN = 12 V, VCC = PVCC = 5 V, Dual Phase, VOUT = 1.8 V

Figure 15 Efficiency at VIN = 12 V, VCC = PVCC = 5 V, Single Phase, VOUT = 1.2 V

Figure 16 Efficiency at VIN = 12 V, VCC = PVCC = 5 V, Dual Phase, VOUT = 1.2 V

Figure 17 Power Loss at VIN = 12 V, VCC = PVCC = 5 V, Single Phase, VOUT = 1.2 V

Figure 18 Power Loss at VIN = 12 V, VCC = PVCC = 5 V, Dual Phase, VOUT = 1.2 V

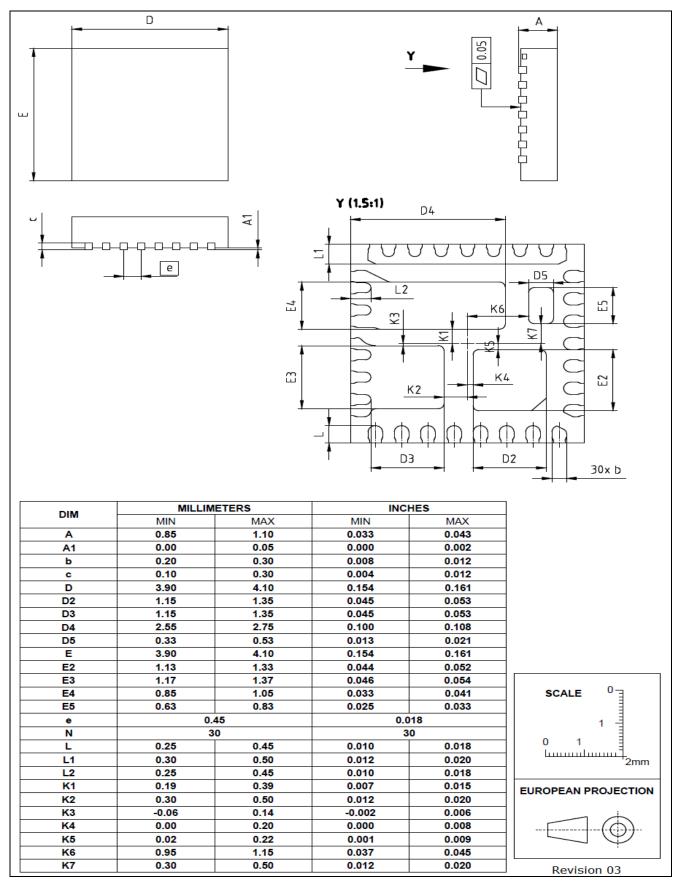

# 9 Mechanical Drawing PG-IQFN-30-2

Figure 19 Mechanical Dimensions – Top and Side Views (in mm)

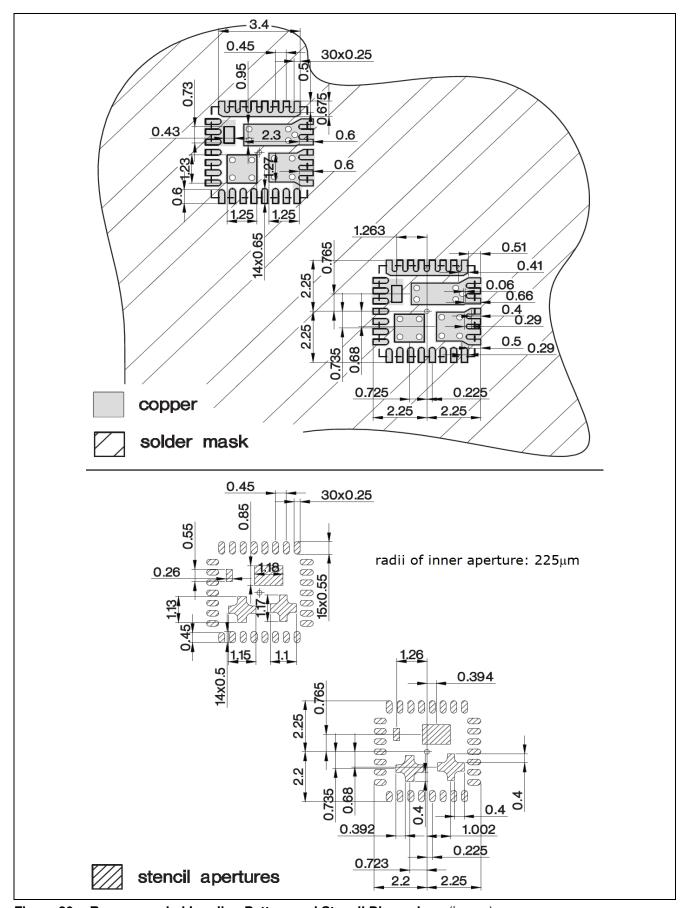

Figure 20 Recommended Landing Pattern and Stencil Dimensions (in mm)

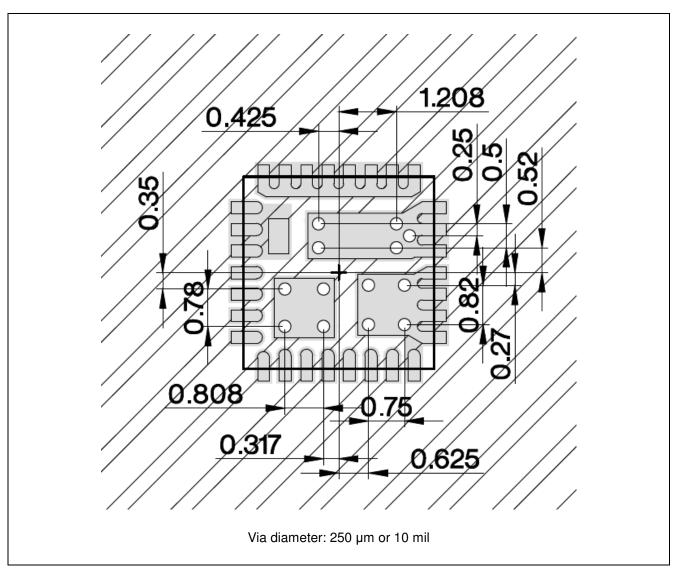

Figure 21 Recommended Via Pattern (in mm)

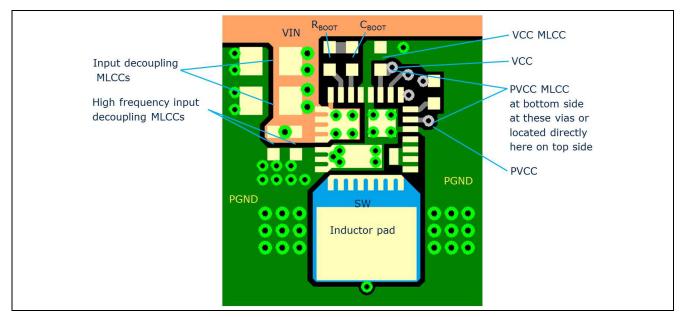

### 10 Board Layout Recommendations

The PCB (printed circuit board) layout design follows the listed industry standards:

- Recommended vias: 10 mil<sup>6</sup> hole with 20 mil via pad diameter, 12 mil hole with 24 mil via pad diameter

- Minimum (typical) via to via center distance: 18 mil (18 ... 25 mil)

- Minimum feature width: 5 mil

- Minimum (typical) clearance: 5 mil (15 ... 20 mil)

Commonly, 10 mil via drill diameters are used for PCBs up to 150 mil thicknesses (usually 22 layers). For thicker boards, 12 mil vias are recommended. To reduce voltage spikes caused by parasitic circuit inductance, all primary decoupling capacitors for VIN, PVCC, BOOT and VCC should be of MLCC type, X6S or X7R rated and located at the same board side as the powerstage close to their respective pins. This is especially important for the VIN to PGND MLCCs.

Electrical and thermal connection of the powerstage to the PCB is crucial for achieving high efficiency. Therefore, vias in VIN and PGND pads are required in the pad areas to connect most effectively to other power and PGND layers. Bigger value MLCC input capacitors should be placed at the bottom side of the PCB close to the vias of the powerstage's VIN and PGND pads. To reduce the stray inductance in the current commutation loop it is strongly recommended to have the 2<sup>nd</sup> layers from the top and the bottom of the board to be monolithic ground planes. All logic and signal connections between powerstage and controller should be embedded between two ground layers. The routing of the current sense lines back to the controller has to be done differentially, for example with 5 mil spacing and 10 – 15 mil distances to other potentials. If the PCB features more than 10 layers, the passive components associated with the current sense lines should be located only at the top side of the board. All resistors and capacitors near the powerstage should be in 0402 case size. For minimizing distribution loss to the load and maintaining signal integrity, have multiple layers/planes in parallel and ensure that the copper cross section for PGND is at least as big as it is for Vout.

Figure 22 Generic Board Design

<sup>&</sup>lt;sup>6</sup> Unit conversion: 1 mil = 25.4 μm

### DrMOS4x4 TDA21242

#### **Revision History**

TDA21242

Revision: 2017-03-07, Rev. 2.1

#### **Previous Revision**

| Revision | Date       | Subjects (major changes since last revision) |

|----------|------------|----------------------------------------------|

| 2.0      | 2016-11-10 | Release of final version                     |

| 2.1      | 2017-03-07 | update of marking info                       |

#### Trademarks of Infineon Technologies AG

AURIX™, C166™, CanPAK™, CIPOS™, CoolGaN™, CoolMOS™, CoolSeT™, CoolSiC™, CORECONTROL™, CROSSAVE™, DAVE™, DI-POL™, DrBlade™, EasyPIM™, EconoBRIDGE™, EconoPACK™, EconoPIM™, EiceDRIVER™, eupec™, FCOS™, HITFET™, HybridPACK™, Infineon™, ISOFACE™, IsoPACK™, i-Wafer™, MIPAQ™, ModSTACK™, my-d™, NovalithIC™, OmniTune™, OPTIGA™, OptiMOS™, ORIGA™, POWERCODE™, PRIMARION™, PrimePACK™, PrimeSTACK™, PROFET™, PRO-SIL™, RASIC™, REAL3™, ReverSave™, SatRIC™, SIEGET™, SIPMOS™, SmartLEWIS™, SOLID FLASH™, SPOC™, TEMPFET™, thinQ!™, TRENCHSTOP™, TriCore™.

Trademarks updated August 2015

#### Other Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: erratum@infineon.com

Published by Infineon Technologies AG 81726 München, Germany © 2017 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

The Infineon Technologies component described in this Data Sheet may be used in life-support devices or systems and/or automotive, aviation and aerospace applications or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support, automotive, aviation and aerospace device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Voltage Regulators category:

Click to view products by Infineon manufacturer:

Other Similar products are found below:

FAN53610AUC33X FAN53611AUC123X FAN48610BUC33X FAN48610BUC45X FAN48617UC50X R3 430464BB MIC45116-1YMPT1 KE177614 MAX809TTR NCV891234MW50R2G NCP81103MNTXG NCP81203PMNTXG NCP81208MNTXG NCP81109GMNTXG

SCY1751FCCT1G NCP81109JMNTXG AP3409ADNTR-G1 LTM8064IY LT8315EFE#TRPBF NCV1077CSTBT3G XCL207A123CR-G

MPM54304GMN-0002 MPM54304GMN-0003 XDPE132G5CG000XUMA1 DA9121-B0V76 LTC3644IY#PBF LD8116CGL

HG2269M/TR OB2269 XD3526 U6215A U6215B U6620S LTC3803ES6#TR LTC3803ES6#TRM LTC3412IFE LT1425IS

MAX25203BATJA/VY+ MAX77874CEWM+ XC9236D08CER-G ISL95338IRTZ MP3416GJ-P BD9S201NUX-CE2 MP5461GC-Z

MPQ4415AGQB-Z MPQ4590GS-Z MCP1642B-18IMC MCP1642D-ADJIMC MCP1642D-18IMC