# Wireless Components

ASK/FSK Single Conversion Receiver TDA 5211 Version 2.0

Specification May 2001

| Revision History                        |                                 |                                                                                                                                                                                         |  |

|-----------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Current Vers                            | sion: 2.0 as of 18              | .05.01                                                                                                                                                                                  |  |

| Previous Ve                             | ersion: 1.1, Dec. 2             | 000                                                                                                                                                                                     |  |

| Page<br>(in previ-<br>ous Ver-<br>sion) | Page<br>(in current<br>Version) | Subjects (major changes since last revision)                                                                                                                                            |  |

| 3-12                                    | 3-12                            | Sec. 3.4.8: max. datarate changed, Sec. 3.4.9: max. output current changed                                                                                                              |  |

| 4-4                                     | 4-4                             | value of a changed to 1.414                                                                                                                                                             |  |

| 4-13                                    | 4-13                            | value for C2 changed to 22nF according to bill of materials, $\tau_2$ and $T_2$ changed                                                                                                 |  |

| 5-3                                     | 5-3                             | min. supply current limits added, max. limits changed                                                                                                                                   |  |

| 5-4                                     | 5-4                             | supply current max. limit changed, min. limit added                                                                                                                                     |  |

| 5-5                                     | 5-5                             | 3VOUT min. & max. limits changed, TAGC typ. & max. values changed                                                                                                                       |  |

| 5-6                                     | 5-6                             | Section "SLICER" reworked, max. datarate at given load capacitance quoted, high output voltage limits changed, precharge current: min., max. limits changed                             |  |

| 5-7                                     | 5-7                             | PDO load and leakage currents limits and typ. values changed, FSK demodulation gain min. limit changed                                                                                  |  |

| 5-9                                     | 5-9                             | PDWN-current max. limit changed, supply currents min. limits added, max. limits changed, 3VOUT min. & max. limits changed, I <sub>TAGC_out</sub> limits changed                         |  |

| 5-10                                    | 5-10                            | Section "SLICER" reworked, max. datarate at given load capacitance quoted, high output voltage limits changed, precharge current: min., max. limits changed, PDO output voltage removed |  |

| 5-15                                    | 5-15                            | C18 value changed                                                                                                                                                                       |  |

ABM®, AOP®, ARCOFI®, BA, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®-54, FALC®-56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®-2, SICOFI®-4, SICOFI®-4, SICOFI®-4, SICOFI®-4, SLICOFI® are registered trademarks of Infineon Technologies AG.

ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of Infineon Technologies AG.

#### Edition 05.01

Published by Infineon Technologies AG, Balanstraße 73, 81541 München

© Infineon Technologies AG May 2001.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

**Product Info**

# **Product Info**

#### **General Description**

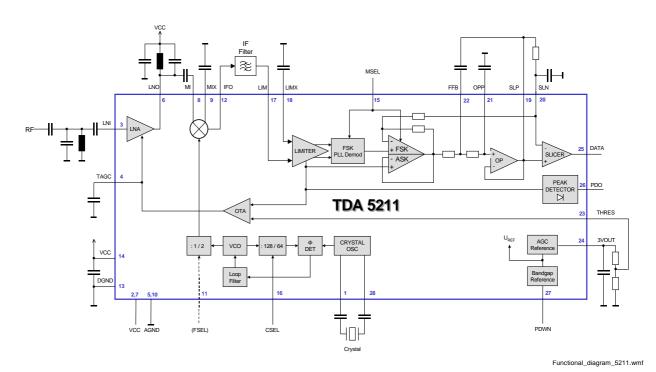

The IC is a very low power consumption single chip FSK/ASK Superheterodyne Receiver (SHR) for the frequency band 310 to 350 MHz that is pin compatible with the ASK Receiver TDA5201. The IC offers a high level of integration and needs only a few external components. The device contains a low noise amplifier (LNA), a double balanced mixer, a fully integrated VCO, a PLL synthesiser, a crystal oscillator, a limiter with RSSI generator, a PLL FSK demodulator, a data filter, a data comparator (slicer) and a peak detector. Additionally there is a power down feature to save battery life.

#### **Package**

#### **Features**

- Low supply current (Is = 5.7 mA typ. in FSK mode, Is = 5 mA typ. in ASK mode)

- Supply voltage range 5V ±10%

- Power down mode with very low supply current (50nA typ.)

- FSK and ASK demodulation capability

- Fully integrated VCO and PLL Synthesiser

- ASK sensitivity better than

-110 dBm over specified temperature range (- 40 to +105°C)

- Selectable frequency ranges 310-330 MHz and 330-350 MHz

- Limiter with RSSI generation, operating at 10.7MHz

- Selectable reference frequency

- 2nd order low pass data filter with external capacitors

- Data slicer with self-adjusting threshold

- FSK sensitivity better than

-102 dBm over specified temperature range (- 40 to +105°C)

#### **Applications**

- Keyless Entry Systems

- Remote Control Systems

- Alarm Systems

- Low Bitrate Communication Systems

#### **Ordering Information**

| Туре              | Ordering Code | Package      |  |

|-------------------|---------------|--------------|--|

| TDA 5211          | Q67037-A1147  | P-TSSOP-28-1 |  |

| samples available |               |              |  |

| 1 | Table  | of Contents                 | i  |

|---|--------|-----------------------------|----|

| 2 | Produ  | ct Description              | 1  |

|   | 2.1    | Overview                    | 2  |

|   | 2.2    | Application                 | 2  |

|   | 2.3    | Features                    | 2  |

|   | 2.4    | Package Outlines            | 3  |

| 3 | Funct  | ional Description           | 1  |

|   | 3.1    | Pin Configuration           | 2  |

|   | 3.2    | Pin Definition and Function | 3  |

|   | 3.3    | Functional Block Diagram    | 9  |

|   | 3.4    | Functional Blocks           | 9  |

|   | 3.4.1  | Low Noise Amplifier (LNA)   | 9  |

|   | 3.4.2  | Mixer                       | 10 |

|   | 3.4.3  | PLL Synthesizer             | 10 |

|   | 3.4.4  | Crystal Oscillator          | 10 |

|   | 3.4.5  | Limiter                     | 11 |

|   | 3.4.6  | FSK Demodulator             | 11 |

|   | 3.4.7  | Data Filter                 | 12 |

|   | 3.4.8  | Data Slicer                 | 12 |

|   | 3.4.9  | Peak Detector               | 12 |

|   | 3 4 10 | Bandgan Reference Circuitry | 12 |

| 4 | Appli | cations                                           | 1  |

|---|-------|---------------------------------------------------|----|

|   | 4.1   | Choice of LNA Threshold Voltage and Time Constant | 2  |

|   | 4.2   | Data Filter Design                                | 4  |

|   | 4.3   | Quartz Load Capacitance Calculation               | 5  |

|   | 4.4   | Quartz Frequency Calculation                      | 6  |

|   | 4.5   | Data Slicer Threshold Generation                  | 7  |

|   | 4.6   | ASK/FSK Switch Functional Description             | 8  |

|   | 4.6.1 | FSK Mode                                          | 8  |

|   | 4.6.2 | ASK Mode                                          | 10 |

|   | 4.7   | Principle of the Precharge Circuit                | 11 |

|   |       |                                                   |    |

| 5 | Refer | ence                                              | 1  |

|   | 5.1   | Electrical Data                                   | 2  |

|   | 5.1.2 | Operating Range                                   | 3  |

|   | 5.1.3 | AC/DC Characteristics at TAMB = 25°C              | 4  |

|   | 5.1.4 | AC/DC Characteristics at TAMB = -40 to 105°C      | 9  |

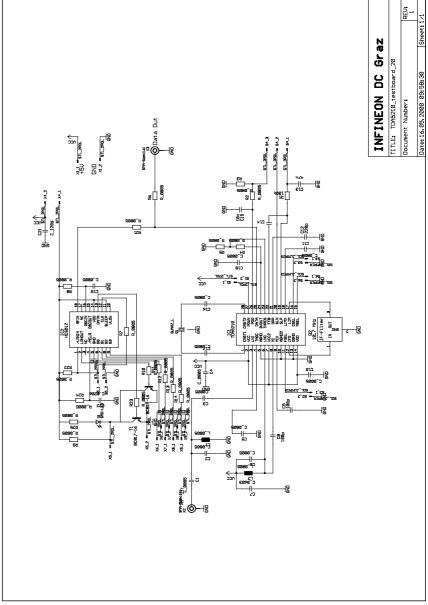

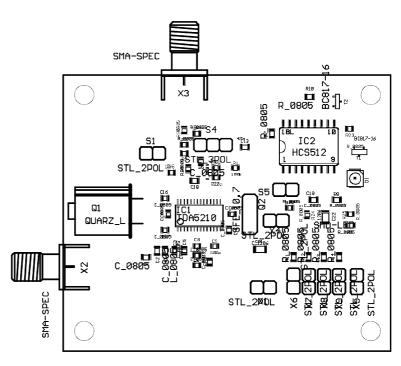

|   | 5.2   | Test Circuit                                      | 12 |

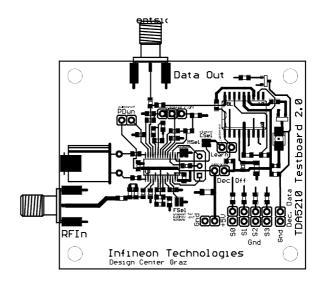

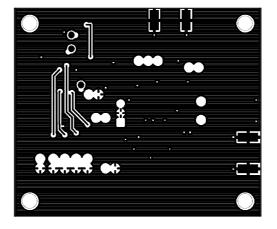

|   | 5.3   | Test Board Layouts                                | 13 |

|   |       |                                                   |    |

|   | 5.4   | Bill of Materials                                 | 15 |

# Product Description

2.4

# Contents of this Chapter 2.1 Overview. 2-2 2.2 Application 2-2 2.3 Features 2-2

#### 2.1 Overview

The IC is a very low power consumption single chip FSK/ASK Superheterodyne Receiver (SHR) for receive frequencies between 310 and 350 MHz that is pin compatible to the ASK Receiver TDA5201. The IC offers a high level of integration and needs only a few external components. The device contains a low noise amplifier (LNA), a double balanced mixer, a fully integrated VCO, a PLL synthesiser, a crystal oscillator, a limiter with RSSI generator, a PLL FSK demodulator, a data filter, a data comparator (slicer) and a peak detector. Additionally there is a power down feature to save battery life.

# 2.2 Application

- Keyless Entry Systems

- Remote Control Systems

- Alarm Systems

- Low Bitrate Communication Systems

#### 2.3 Features

- Low supply current (I<sub>s</sub> = 5.7 mA typ.FSK mode, 5mA typ. ASK mode)

- Supply voltage range 5V ±10%

- Power down mode with very low supply current (50nA typ.)

- FSK and ASK demodulation capability

- Fully integrated VCO and PLL Synthesiser

- RF input sensitivity ASK -113dBm typ. at 25°C, better than -110dBm over complete specified operating temperature range (-40 to +105°C)

- RF input sensitivity FSK -105dBm typ. at 25°C, better than -102dBm over complete specified operating temperature range (-40 to +105°C)

- Receive frequency range between 310 and 350 MHz

- Selectable reference frequency

- Limiter with RSSI generation, operating at 10.7MHz

- 2nd order low pass data filter with external capacitors

- Data slicer with self-adjusting threshold

# 2.4 Package Outlines

- 1) Does not include plastic or metal protrusion of 0.15 max. per side

- 2) Does not include dambar protrusion

P\_TSSOP\_28.EPS

Figure 2-1 P-TSSOP-28-1 package outlines

3.4

# Contents of this Chapter3.1 Pin Configuration3-23.2 Pin Definition and Function3-33.3 Functional Block Diagram3-9

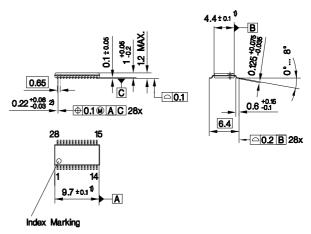

# 3.1 Pin Configuration

Pin\_Configuration\_5211.wmf

Figure 3-1 IC Pin Configuration

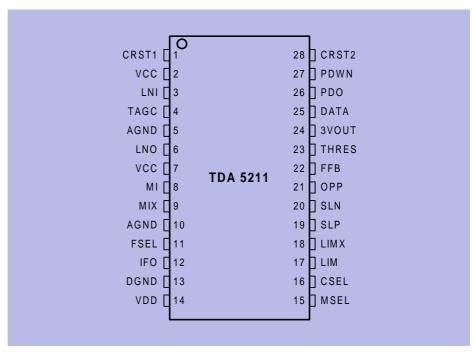

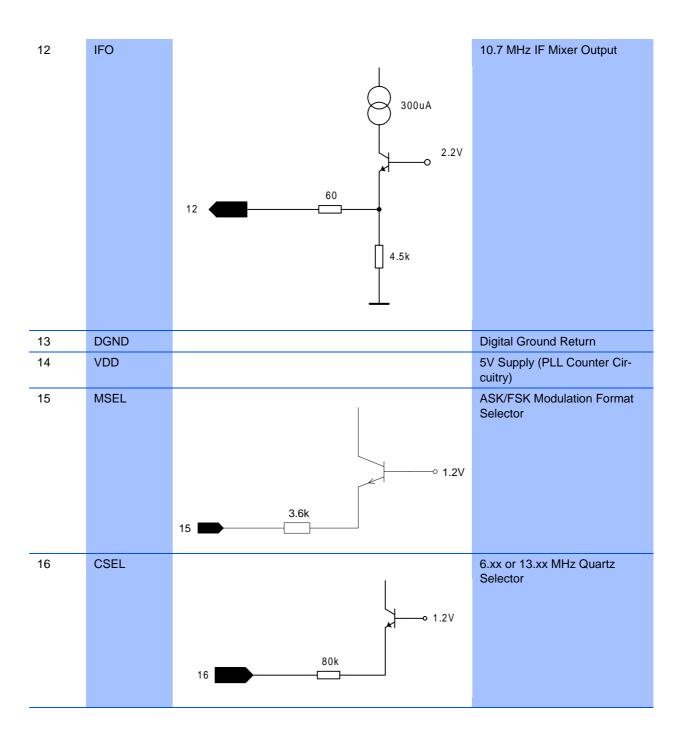

# 3.2 Pin Definition and Function

In the subsequent table the internal circuits connected to the pins of the device are shown. ESD-protection circuits are omitted to ease reading.

.

| Table 3- | Pin Definition | and Function             |                              |

|----------|----------------|--------------------------|------------------------------|

| Pin No.  | Symbol         | Equivalent I/O-Schematic | Function                     |

| 1        | CRST1          | 4.15V<br>50uA            | External Crystal Connector 1 |

| 2        | VCC            |                          | 5V Supply                    |

| 3        | LNI            | 57uA 3 500uA             | LNA Input                    |

| 4  | TAGC | 4.3V               | AGC Time Constant Control       |

|----|------|--------------------|---------------------------------|

|    |      | 3uA<br>1k<br>1.4uA |                                 |

| 5  | AGND |                    | Analogue Ground Return          |

| 6  | LNO  |                    | LNA Output                      |

|    |      | 5V                 |                                 |

|    |      |                    |                                 |

|    |      | <br>               |                                 |

|    |      |                    |                                 |

|    |      |                    |                                 |

|    |      | 6                  |                                 |

|    |      |                    |                                 |

|    |      | <u> </u>           |                                 |

|    |      |                    |                                 |

|    |      |                    |                                 |

| 7  | VCC  |                    | 5V Supply                       |

| 8  | MI   |                    | Mixer Input                     |

|    |      | 1.7V<br>የ          |                                 |

|    |      |                    |                                 |

|    |      | 2k 2k              |                                 |

| 9  | MIX  |                    | Complementary Mixer Input       |

|    |      | 9                  |                                 |

|    |      |                    |                                 |

|    |      | 400uA              |                                 |

|    |      |                    |                                 |

| 10 | AGND |                    | Analogue Ground Return          |

| 11 | FSEL |                    | not applicable - has to be left |

|    |      |                    | open                            |

| 17 | LIM  | 2.4V              | Limiter Input               |

|----|------|-------------------|-----------------------------|

| 18 | LIMX | 17                | Complementary Limiter Input |

|    |      | 15k               |                             |

| 19 | SLP  | 19 15uA 15uA 80µA | Data Slicer Positive Input  |

| 20 | SLN  | 20 10k            | Data Slicer Negative Input  |

| 21 | OPP  | 21 200 21         | OpAmp Noninverting Input    |

| 22 | FFB   | 5uA                                     | Data Filter Feedback Pin |

|----|-------|-----------------------------------------|--------------------------|

|    |       | 22 100k                                 |                          |

| 23 | THRES | 5uA                                     | AGC Threshold Input      |

|    |       | 23 10k                                  |                          |

| 24 | 3VOUT | 24 20k 3.1V                             | 3V Reference Output      |

| 25 | DATA  | 25 ———————————————————————————————————— | Data Output              |

| 26 | PDO   | 26            | Peak Detector Output         |

|----|-------|---------------|------------------------------|

| 27 | PDWN  | 220k          | Power Down Input             |

| 28 | CRST2 | 4.15V<br>50uA | External Crystal Connector 2 |

# 3.3 Functional Block Diagram

Figure 3-2 Main Block Diagram

### 3.4 Functional Blocks

### 3.4.1 Low Noise Amplifier (LNA)

The LNA is an on-chip cascode amplifier with a voltage gain of 15 to 20dB. The gain figure is determined by the external matching networks situated ahead of LNA and between the LNA output **LNO** (Pin 6) and the Mixer Inputs **MI** and **MIX** (Pins 8 and 9). The noise figure of the LNA is approximately 3dB, the current consumption is 500µA. The gain can be reduced by approximately 18dB. The switching point of this AGC action can be determined externally by applying a threshold voltage at the **THRES** pin (Pin 23). This voltage is compared internally with the received signal (RSSI) level generated by the limiter circuitry. In case that the RSSI level is higher than the threshold voltage the LNA gain is reduced and vice versa. The threshold voltage can be generated by attaching a voltage divider between the **3VOUT** pin (Pin 24) which provides a temperature stable 3V output generated from the internal bandgap voltage and the **THRES** pin as described in Section 4.1. The time constant of the AGC action can be deter-

mined by connecting a capacitor to the **TAGC** pin (Pin 4) and should be chosen along with the appropriate threshold voltage according to the intended operating case and interference scenario to be expected during operation. The optimum choice of AGC time constant and the threshold voltage is described in Section 4.1.

#### 3.4.2 Mixer

The Double Balanced Mixer downconverts the input frequency (RF) in the range of 310-350MHz to the intermediate frequency (IF) at 10.7MHz with a voltage gain of approximately 21dB by utilising either high- or low-side injection of the local oscillator signal. In case the mixer is interfaced only single-ended, the unused mixer input has to be tied to ground via a capacitor. The mixer is followed by a low pass filter with a corner frequency of 20MHz in order to suppress RF signals to appear at the IF output (**IFO** pin). The IF output is internally consisting of an emitter follower that has a source impedance of approximately  $330\Omega$  to facilitate interfacing the pin directly to a standard 10.7MHz ceramic filter without additional matching circuitry.

#### 3.4.3 PLL Synthesizer

The Phase Locked Loop synthesizer consists of a VCO, an asynchronous divider chain, a phase detector with charge pump and a loop filter and is fully implemented on-chip. The VCO is including spiral inductors and varactor diodes. The **FSEL** pin (Pin11) has to be left open. The tuning range of the VCO was designed to guarantee over production spread and the specified temperature range a receive frequency range between 310 and 350MHz depending on whether high- or low-side injection of the local oscillator is used. The oscillator signal is fed both to the synthesiser divider chain and to a divider that is dividing the signal by 2 before it is applied to the downconverting mixer. Local oscillator high side injection has to be used for receive frequencies between approximately 310 and 330 MHz, low side injection for receive frequencies between 330 and 350MHz - see also Section 4.4..

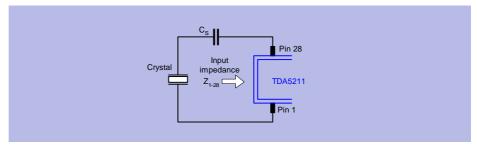

#### 3.4.4 Crystal Oscillator

The on-chip crystal oscillator circuitry allows for utilisation of quartzes both in the 5 and 10MHz range as the overall division ratio of the PLL can be switched between 32 and 64 via the **CSEL** (Pin 16) pin according to the following table.

| Table 3-2 CSEL Pin Operating States |                   |

|-------------------------------------|-------------------|

| CSEL                                | Crystal Frequency |

| Open                                | 5.xx MHz          |

| Shorted to ground                   | 10.xx MHz         |

The calculation of the value of the necessary quartz load capacitance is shown in Section 4.3, the quartz frequency calculation is explained in Section 4.4.

#### 3.4.5 Limiter

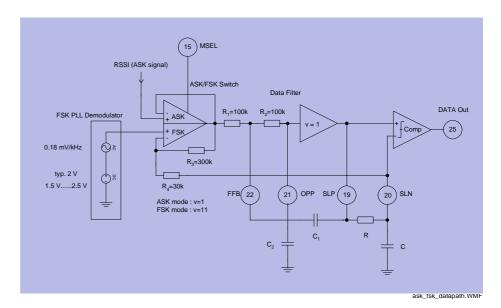

The Limiter is an AC coupled multistage amplifier with a cumulative gain of approximately 80 dB that has a bandpass-characteristic centred around 10.7 MHz. It has a typical input impedance of 330  $\Omega$  to allow for easy interfacing to a 10.7 MHz ceramic IF filter. The limiter circuit also acts as a Receive Signal Strength Indicator (RSSI) generator which produces a DC voltage that is directly proportional to the input signal level as can be seen in Figure 4-2. This signal is used to demodulate ASK-modulated receive signals in the subsequent baseband circuitry. The RSSI output is applied to the modulation format switch, to the Peak Detector input and to the AGC circuitry.

In order to demodulate ASK signals the MSEL pin has to be left open as described in the next chapter.

#### 3.4.6 FSK Demodulator

To demodulate frequency shift keyed (FSK) signals a PLL circuit is used that is contained fully on chip. The Limiter output differential signal is fed to the linear phase detector as is the output of the 10.7 MHz center frequency VCO. The demodulator gain is typically 140µV/kHz. The passive loop filter output that is comprised fully on chip is fed to both the VCO and the modulation format switch described in more detail below. This signal is representing the demodulated signal with low frequencies applied to the demodulator demodulated to logic ones and high frequencies demodulated to logic zeroes. However this is only valid in case the local oscillator is low-side injected to the mixer which is applicable to receive frequencies above 330MHz (e.g. 345MHz). In case of receive frequencies below 330MHz (e.g.315MHz) high frequencies are demodulated as logical ones due to a sign inversion in the downconversion mixing process. See also Section 4.4.

The modulation format switch is actually a switchable amplifier with an AC gain of 11 that is controlled by the **MSEL** pin (Pin 15) as shown in the following table. This gain was chosen to facilitate detection in the subsequent circuits. The DC gain is 1 in order not to saturate the subsequent Data Filter wih the DC offset produced by the demodulator in case of large frequency offsets of the IF signal. The resulting frequency characteristic and details on the principle of operation of the switch are described in Section 4.6.

| Table 3-3 MSEL Pin Operating States |                   |

|-------------------------------------|-------------------|

| MSEL                                | Modulation Format |

| Open                                | ASK               |

| Shorted to ground                   | FSK               |

The demodulator circuit is switched off in case of reception of ASK signals.

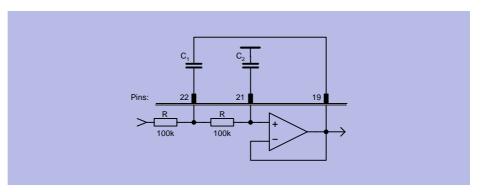

#### 3.4.7 Data Filter

The data filter comprises an OP-Amp with a bandwidth of 100kHz used as a voltage follower and two  $100k\Omega$  on-chip resistors. Along with two external capacitors a 2nd order Sallen-Key low pass filter is formed. The selection of the capacitor values is described in Section 4.2.

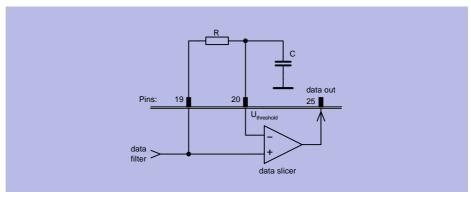

#### 3.4.8 Data Slicer

The data slicer is a fast comparator with a bandwidth of 100 kHz. This allows for a maximum receive data rate of up to 100kBaud. The maximum achievable data rate also depends on the IF Filter bandwidth and the local oscillator tolerance values. Both inputs are accessible. The output delivers a digital data signal (CMOS-like levels) for sbsequent circuits. The self-adjusting threshold on pin 20 its generated by RC-term or peak detector depending on the baseband coding scheme. The data slicer threshold generation alternatives are described in more detail in Section 4.5.

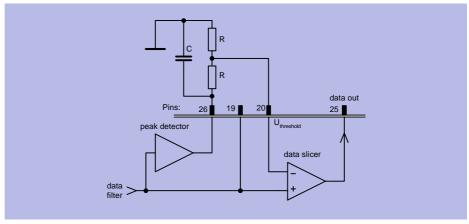

#### 3.4.9 Peak Detector

The peak detector generates a DC voltage which is proportional to the peak value of the receive data signal. An external RC network is necessary. The input is connected to the output of the RSSI-output of the Limiter, the output is connected to the **PDO** pin (Pin 26 ). This output can be used as an indicator for the received signal strength to use in wake-up circuits and as a reference for the data slicer in ASK mode. The output current is typically  $950\mu A$ , the discharge current is lower than  $2\mu A$ . Note that the RSSI level is also output in case of FSK mode.

#### 3.4.10 Bandgap Reference Circuitry

A Bandgap Reference Circuit provides a temperature stable reference voltage for the device. A power down mode is available to switch off all subcircuits which is controlled by the PWDN pin (Pin 27) as shown in the following table. The supply current drawn in this case is typically 50nA.

| Table 3-4 PDWN Pin Operating States |                 |

|-------------------------------------|-----------------|

| PDWN                                | Operating State |

| Open or tied to ground              | Powerdown Mode  |

| Tied to Vs                          | Receiver On     |

#### **Contents of this Chapter**

| 4.1 | Choice of LNA Threshold Voltage and Time Constant | 4-2  |

|-----|---------------------------------------------------|------|

| 4.2 | Data Filter Design                                | 4-4  |

| 4.3 | Quartz Load Capacitance Calculation               | 4-5  |

| 4.4 | Quartz Frequency Calculation                      | 4-6  |

| 4.5 | Data Slicer Threshold Generation                  | 4-7  |

| 4.6 | ASK/FSK Switch Functional Description             | 4-8  |

| 47  | Principle of the Precharge Circuit                | 4-11 |

### 4.1 Choice of LNA Threshold Voltage and Time Constant

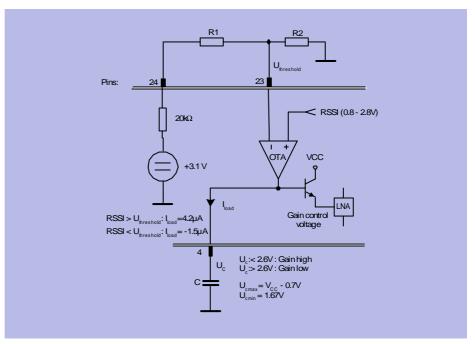

In the following figure the internal circuitry of the LNA automatic gain control is shown.

LNA\_autom.wmf

Figure 4-1 LNA Automatic Gain Control Circuitry

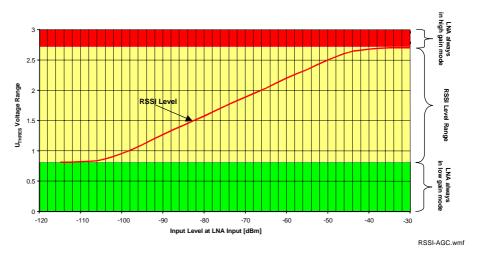

The LNA automatic gain control circuitry consists of an operational transimpedance amplifier that is used to compare the received signal strength signal (RSSI) generated by the Limiter with an externally provided threshold voltage  $U_{thres}$ . As shown in the following figure the threshold voltage can have any value between approximately 0.8 and 2.8V to provide a switching point within the receive signal dynamic range.

This voltage  $U_{thres}$  is applied to the **THRES** pin (Pin 23) The threshold voltage can be generated by attaching a voltage divider between the **3VOUT** pin (Pin 24) which provides a temperature stable 3V output generated from the internal bandgap voltage and the **THRES** pin. If the RSSI level generated by the Limiter is higher than  $U_{thres}$ , the OTA generates a positive current  $I_{load}$ . This yields a voltage rise on the **TAGC** pin (Pin 4). Otherwise, the OTA generates a negative current. These currents do not have the same values in order to achieve a fast-attack and slow-release action of the AGC and are used to charge an external capacitor which finally generates the LNA gain control voltage.

Figure 4-2 RSSI Level and Permissive AGC Threshold Levels

The switching point should be chosen according to the intended operating scenario. The determination of the optimum point is described in the accompanying Application Note, a threshold voltage level of 1.8V is apparently a viable choice. It should be noted that the output of the **3VOUT** pin is capable of driving up to  $50\mu\text{A}$ , but that the **THRES** pin input current is only in the region of 40nA. As the current drawn out of the **3VOUT** pin is directly related to the receiver power consumption, the power divider resistors should have high impedance values. The sum of R1 and R2 has to be  $600k\Omega$  in order to yield 3V at the **3VOUT** pin. R1 can thus be chosen as  $240k\Omega$ , R2 as  $360k\Omega$  to yield an overall **3VOUT** output current of  $5\mu\text{A}^1$  and a threshold voltage of 1.8V

**Note:** If the LNA gain shall be kept in either high or low gain mode this has to be accomplished by tying the **THRES** pin to a fixed voltage. In order to achieve high gain mode operation, a voltage higher than 2.8V shall be applied to the **THRES** pin, such as a short to the **3VOLT** pin. In order to achieve low gain mode operation a voltage lower than 0.7V shall be applied to the **THRES**, such as a short to ground.

As stated above the capacitor connected to the **TAGC** pin is generating the gain control voltage of the LNA due to the charging and discharging currents of the OTA and thus is also responsible for the AGC time constant. As the charging and discharging currents are not equal two different time constants will result. The time constant corresponding to the charging process of the capacitor shall be chosen according to the data rate. According to measurements performed at Infineon the capacitor value should be greater than 47nF.

1. note the  $20k\Omega$  resistor in series with the 3.1V internal voltage source

# 4.2 Data Filter Design

Utilising the on-board voltage follower and the two  $100k\Omega$  on-chip resistors a 2nd order Sallen-Key low pass data filter can be constructed by adding 2 external capacitors between pins 19 (SLP) and 22 (FFB) and to pin 21 (OPP) as depicted in the following figure and described in the following formulas<sup>1</sup>.

Filter Design.wmf

Figure 4-3 Data Filter Design

(1)(2)

$$C1 = \frac{2Q\sqrt{b}}{R2\Pi f_{3dB}} \qquad C2 = \frac{\sqrt{b}}{4QR\Pi f_{3dB}}$$

with

$$Q = \frac{\sqrt{b}}{a}$$

(3)the quality factor of the poles

where

in case of a Bessel filter a = 1.3617, b = 0.618 and thus Q = 0.577

and in case of a Butterworth filtera = 1.414, b = 1 and thus Q = 0.71

Example: Butterworth filter with  $f_{3dB} = 5kHz$  and  $R = 100k\Omega$ :

$$C_1 = 450pF, C_2 = 225pF$$

1. taken from Tietze/Schenk: Halbleiterschaltungstechnik, Springer Berlin, 1999

### 4.3 Quartz Load Capacitance Calculation

The value of the capacitor necessary to achieve that the quartz oscillator is operating at the intended frequency is determined by the reactive part of the negative resistance of the oscillator circuit as shown in Section 5.1.3 and by the quartz specifications given by the quartz manufacturer.

Quartz load 5211 wm

Figure 4-4 Determination of Series Capacitance Value for the Quartz Oscillator

Crystal specified with load capacitance

$$C_S = \frac{1}{\frac{1}{C_I} + 2\pi f X_L}$$

with C<sub>I</sub> the load capacitance (refer to the quartz crystal specification).

Example:

10.18 MHz:

$$C_L = 12 \text{ pF}$$

$X_L = 870 \Omega$   $C_S = 7.2 \text{ pF}$

This value may be obtained by putting two capacitors in series to the quartz, such as 18pF and 22pF in the 5.1MHz case and 18pF and 12pF in the 10.2MHz case.

# 4.4 Quartz Frequency Calculation

As described in Section 3.4.3 the operating range of the on-chip VCO is wide enough to guarantee a receive frequency range between 310 and 350MHz. The VCO signal is divided by 2 before applied to the mixer. This local oscillator signal can be used to downconvert the RF signals both with high- or low-side injection at the mixer. High-side injection of the local oscillator has to be used for receive frequencies between 310 and 330 MHz. In this case the local oscillator frequency is calculated by adding the IF frequency (10.7 MHz) to the RF frequency. In this case the higher frequency of a FSK-modulated signal is demodulated as a logical one (high).

Low-side injection has to be used for receive frequencies between 330 and 350 MHz. The local oscillator frequency is calculated by subtracting the IF frequency (10.7 MHz) from the RF frequency then. Please note that in this case sign-inversion occurs and the higher frequency of a FSK-modulated signal is demodulated as a logical zero (low). The overall division ratios in the PLL are 64 or 32 depending on whether the CSEL-pin is left open or tied to ground.

Therefore the quartz frequency may be calculated by using the following formula:

$$f_{QU} = (f_{RF} \pm 10.7) / r$$

with  $f_{RF}$  receive frequency

$f_{LO}$  local oscillator (PLL) frequency ( $f_{RF} \pm 10.7$ )

f<sub>QU</sub> quartz oscillator frequency

r ratio of local oscillator (PLL) frequency and quartz frequency as shown in the subsequent table

| Table 4-1 PLL Division Ratio Dependence on States of CSEL |                                               |  |  |  |  |

|-----------------------------------------------------------|-----------------------------------------------|--|--|--|--|

| CSEL                                                      | Ratio r = (f <sub>LO</sub> /f <sub>QU</sub> ) |  |  |  |  |

| open                                                      | 64                                            |  |  |  |  |

| GND                                                       | 32                                            |  |  |  |  |

This yields the following examples:

CSEL tied to GND:

$$f_{\text{QU}} = (315MHz + 10.7MHz)/32 = 10.1781MHz$$

$f_{\text{OU}} = (345MHz - 10.7MHz)/32 = 10.4469MHz$

CSEL open:

$$f_{\text{QU}} = (315 \, MHz + 10.7 \, MHz) / 64 = 5.0891 \, MHz$$

$f_{\text{OU}} = (345 \, MHz - 10.7 \, MHz) / 64 = 5.2234 \, MHz$

#### 4.5 Data Slicer Threshold Generation

The threshold of the data slicer can be generated using an external R-C integrator as shown in Figure 4-5. The cut-off frequency of the R-C integrator has to be lower than the lowest frequency appearing in the data signal. In order to keep distortion low, the minimum value for R is  $20k\Omega$ .

Data\_slice1.wmf

Figure 4-5 Data Slicer Threshold Generation with External R-C Integrator

In case of ASK operation another possibility for threshold generation is to use the peak detector in connection with two resistors and one capacitor as shown in the following figure. The component values are depending on the coding scheme and the protocol used.

Data\_slice2.wmf

Figure 4-6 Data Slicer Threshold Generation Utilising the Peak Detector

# 4.6 ASK/FSK Switch Functional Description

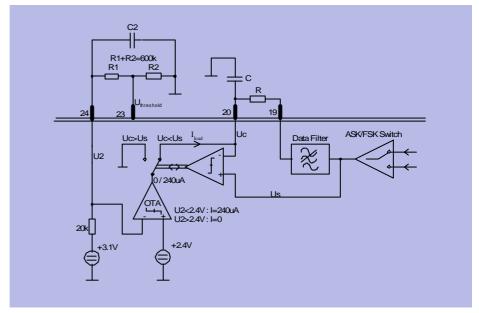

The TDA5211 is containing an ASK/FSK switch which can be controlled via Pin 15 (MSEL). This switch is actually consisting of 2 operational amplifiers that are having a gain of 1 in case of the ASK amplifier and a gain of 11 in case of the FSK amplifier in order to achieve an appropriate demodulation gain characteristic. In order to compensate for the DC-offset generated especially in case of the FSK PLL demodulator there is a feedback connection between the threshold voltage of the bit slicer comparator (Pin 20) to the negative input of the FSK switch amplifier. This is shown in the following figure.

Figure 4-7 ASK/FSK mode datapath

#### 4.6.1 FSK Mode

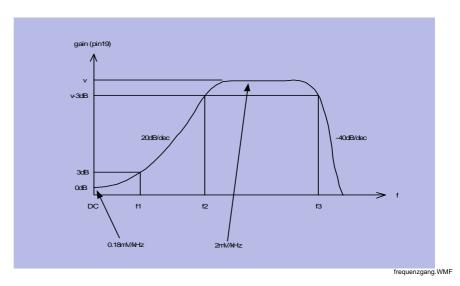

The FSK datapath has a bandpass characterisite due to the feedback shown above (highpass) and the data filter (lowpass). The lower cutoff frequency f2 is determined by the external RC-combination. The upper cutoff frequency f3 is determined by the data filter bandwidth.

The demodulation gain of the FSK PLL demodulator is  $140\mu V/kHz$ . This gain is increased by the gain v of the FSK switch, which is 11. Therefore the resulting dynamic gain of this circuit is 1.5mV/kHz within the bandpass. The gain for the DC content of FSK signal remains at  $140\mu V/kHz$ . The cutoff frequencies of the bandpass have to be chosen such that the spectrum of the data signal is influenced in an acceptable amount.

In case that the user data is containing long sequences of logical zeroes the effect of the drift-off of the bit slicer threshold voltage can be lowered if the offset voltage inherent at the negative input of the slicer comparator (Pin20) is used. The comparator has no hysteresis built in.

This offset voltage is generated by the bias current of the negative input of the comparator (i.e. 20nA) running over the external resistor R. This voltage raises the voltage appearing at pin 20 (e.g. 1mV with R =  $100k\Omega$ ). In order to obtain benefit of this asymmetrical offset for the demodulation of long zeros the lower of the two FSK frequencies should be chosen in the transmitter as the zero-symbol frequency.

In the following figure the shape of the above mentioned bandpass is shown.

Figure 4-8 Frequency characterstic in case of FSK mode

The cutoff frequencies are calculated with the following formulas:

$$f_1 = \frac{1}{2\pi \frac{R \cdot 330k\Omega}{R + 330k\Omega} \cdot C}$$

$$f_2 = v \cdot f_1 = 11 \cdot f_1$$

$$f_3 = f_{3dR}$$

f<sub>3</sub> is the 3dB cutoff frequency of the data filter - see Section 4.2.

Example:

$$R = 100k\Omega$$

,  $C = 47nF$

This leads  $tof_1 = 44Hz$  and  $f_2 = 485Hz$

#### 4.6.2 ASK Mode

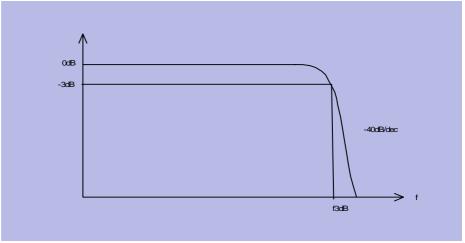

In case the receiver is operated in ASK mode the datapath frequency charactersitic is dominated by the data filter alone, thus it is lowpass shaped. The cutoff frequency is determined by the external capacitors C12 and C14 and the internal 100k resistors as described in Section 4.2

freq\_ask.WMF

Figure 4-9 Frequency charcteristic in case of ASK mode

# 4.7 Principle of the Precharge Circuit

In case the data slicer threshold shall be generated with an external RC network as described in Section 4.5 it is necessary to use large values for the capacitor C attached to the **SLN** pin (pin 20) in order to achieve long time constants. This results also from the fact that the choice of the value for R connected between the **SLP** and **SLN** pins (pins 19 and 20) is limited by the  $330k\Omega$  resistor appearing in parallel to R as can be seen in Figure 4-7. Apart from this a resistor value of  $100k\Omega$  leads to a voltage offset of 1mv at the comparator input as described in Section 4.6.1. The resulting startup time constant  $\tau_1$  can be calculated with:

$$\tau_1 = (R // 330k\Omega) \cdot C$$

In case R is chosen to be  $100k\Omega$  and C is chosen as 47nF this leads to

$$\tau_1$$

= (100k $\Omega$  // 330k $\Omega$ ) · 47nF = 77k $\Omega$  · 47nF = 3.6ms

When the device is turned on this time constant dominates the time necessary for the device to be able to demodulate data properly. In the powerdown mode the capacitor is only discharged by leakage currents.

In order to reduce the turn-on time in the presence of large values of C a precharge circuit was included in the TDA5211 as shown in the following figure.

precharge.WMF

Figure 4-10 Principle of the precharge circuit

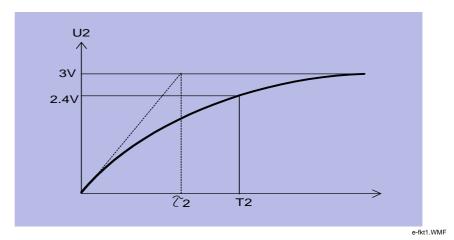

This circuit charges the capacitor C with an inrush current  $I_{load}$  of typically 220µA for a duration of  $T_2$  until the voltage  $U_c$  appearing on the capacitor is equal to the voltage  $U_s$  at the input of the data filter. This voltage is limited to 2.5V. As soon as these voltages are equal or the duration  $T_2$  is exceeded the precharge circuit is disabled.

$\tau_2$  is the time constant of the charging process of C which can be calculated as

$$\tau_2 \approx 20 k\Omega \cdot C2$$

as the sum of R1 and R2 is sufficiently large and thus can be neglected. T2 can then be calculated according to the following formula:

$$T_2 = \tau_2 \ln \left( \frac{1}{1 - \frac{2.4V}{3V}} \right) \approx \tau_2 \cdot 1.6$$

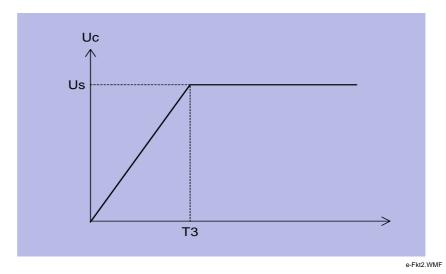

The voltage transient during the charging of C2 is shown in the following figure:

Figure 4-11 Voltage appearing on C2 during precharging process

The voltage appearing on the capacitor C connected to pin 20 is shown in the following figure. It can be seen that due to the fact that it is charged by a constant current source it exhibits is a linear increase in voltage which is limited to  $U_{Smax} = 2.5V$  which is also the approximate operating point of the data filter input. The time constant appearing in this case can be denoted as T3, which can be calculated with

$$T3 = \frac{U_{\text{Smax}} \cdot C}{220 \mu A} = \frac{2.5 V}{220 \mu A} \cdot C$$

Figure 4-12 Voltage transient on capacitor C attached to pin 20

As an example the choice of C2 = 22nF and C = 47nF yields

$\tau_2 = 0.44 ms$

$T_2 = 0.71 \text{ms}$

$T_3 = 0.53 ms$

This means that in this case the inrush current could flow for a duration of 0.64ms but stops already after 0.49ms when the  $U_{Smax}$  limit has been reached. T3 should always be chosen to be shorter than T2.

It has to be noted finally that during the turn-on duration T2 the overall device power consumption is increased by the 220µA needed to charge C.

The precharge circuit may be disabled if C2 is not equipped. This yields a T2 close to zero. Note that the sum of R4 and R5 has to be  $600k\Omega$  in order to produce 3V at the THRES pin as this voltage is internally used also as the reference for the FSK demodulator.

# 5 Reference

5.4

# Contents of this Chapter5.1 Electrical Data..5-25.2 Test Circuit.5-115.3 Test Board Layouts..5-12

Reference

# 5.1 Electrical Data

# 5.1.1 Absolute Maximum Ratings

#### **WARNING**

The maximum ratings may not be exceeded under any circumstances, not even momentarily and individually, as permanent damage to the IC will result.

| Table 5-1 Absolute Maximum Ratings, Ambient temperature T <sub>AMB</sub> =-40°C + 105°C |                                                                              |                   |              |            |          |                                                             |  |  |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------|--------------|------------|----------|-------------------------------------------------------------|--|--|

| #                                                                                       | Parameter                                                                    | Symbol            | Limit Values |            | Unit     | Remarks                                                     |  |  |

|                                                                                         |                                                                              |                   | min          | max        |          |                                                             |  |  |

| 1                                                                                       | Supply Voltage                                                               | Vs                | -0.3         | 5.5        | V        |                                                             |  |  |

| 2                                                                                       | Junction Temperature                                                         | Tj                | -40          | +150       | °C       |                                                             |  |  |

| 3                                                                                       | Storage Temperature                                                          | T <sub>s</sub>    | -40          | +125       | °C       |                                                             |  |  |

| 4                                                                                       | Thermal Resistance                                                           | R <sub>thJA</sub> |              | 114        | K/W      |                                                             |  |  |

| 5                                                                                       | ESD integrity, all pins excl. Pins 1,3, 6, 28<br>ESD integrity Pins 1,3,6,28 | V <sub>ESD</sub>  |              | +2<br>+1.5 | kV<br>kV | HBM<br>according to<br>MIL STD<br>883D,<br>method<br>3015.7 |  |  |

Reference

# 5.1.2 Operating Range

Within the operational range the IC operates as explained in the circuit description. The AC/DC characteristic limits are not guaranteed. Currents flowing into the device are denoted as positive currents and v.v.

Supply voltage: VCC = 4.5V .. 5.5V

| Table 5-2 Operating Range, Ambient temperature T <sub>AMB</sub> = -40°C + 105°C |                                                         |                                    |              |                |            |                                                                                                                       |   |      |  |  |

|---------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------|--------------|----------------|------------|-----------------------------------------------------------------------------------------------------------------------|---|------|--|--|

| #                                                                               | Parameter                                               | Symbol                             | Limit Values |                | Unit       | nit Test Conditions                                                                                                   |   | Item |  |  |

|                                                                                 |                                                         |                                    | min          | max            |            |                                                                                                                       |   |      |  |  |

| 1                                                                               | Supply Current                                          | I <sub>SF</sub><br>I <sub>SA</sub> | 3.9<br>3.2   | 7.5<br>6.8     | mA<br>mA   | $f_{RF} = 315MHz$ , FSK Mode $f_{RF} = 315MHz$ , ASK Mode                                                             |   |      |  |  |

| 2                                                                               | Receiver Input Level<br>ASK<br>FSK, frequ. dev. ± 50kHz | RF <sub>in</sub>                   | -110<br>-102 | -13<br>-13     | dBm<br>dBm | @ source impedance $50\Omega$ , BER 2E-3, average power level, Manchester encoded datarate 4kBit, 280kHz IF Bandwidth | • |      |  |  |

| 3                                                                               | LNI Input Frequency                                     | f <sub>RF</sub>                    | 310          | 350            | MHz        |                                                                                                                       |   |      |  |  |

| 4                                                                               | MI/X Input Frequency                                    | f <sub>MI</sub>                    | 310          | 350            | MHz        |                                                                                                                       |   |      |  |  |

| 5                                                                               | 3dB IF Frequency Range<br>ASK<br>FSK                    | f <sub>IF -3dB</sub>               | 5<br>10.4    | 23<br>11       | MHz        |                                                                                                                       | • |      |  |  |

| 6                                                                               | Powerdown Mode On                                       | PWDN <sub>ON</sub>                 | 0            | 0.8            | V          |                                                                                                                       |   |      |  |  |

| 7                                                                               | Powerdown Mode Off                                      | PWDN <sub>OFF</sub>                | 2            | V <sub>S</sub> | V          |                                                                                                                       |   |      |  |  |

| 8                                                                               | Gain Control Voltage,<br>LNA high gain state            | V <sub>THRES</sub>                 | 2.8          | V <sub>S</sub> | V          |                                                                                                                       |   |      |  |  |

| 9                                                                               | Gain Control Voltage,<br>LNA low gain state             | V <sub>THRES</sub>                 | 0            | 0.7            | V          |                                                                                                                       |   |      |  |  |

<sup>■</sup> This value is guaranteed by design.

#### 5.1.3 AC/DC Characteristics at T<sub>AMB</sub> = 25°C

Table 5-3 AC/DC Characteristics with T<sub>A</sub> 25 °C, V<sub>VCC</sub> = 4.5 ... 5.5 V

AC/DC characteristics involve the spread of values guaranteed within the specified voltage and ambient temperature range. Typical characteristics are the median of the production. Currents flowing into the device are denoted as positive currents and vice versa.

The device performance parameters marked with were measured on an Infineon evaluation board as described in Section 5.2.

|     | Parameter                                                             | Symbol                   | L         | ₋imit Valu  | es  | Unit | Test Conditions                                                             | L | Item |  |

|-----|-----------------------------------------------------------------------|--------------------------|-----------|-------------|-----|------|-----------------------------------------------------------------------------|---|------|--|

|     |                                                                       |                          | min       | typ         | max |      |                                                                             |   |      |  |

| Su  | pply                                                                  |                          |           |             |     |      |                                                                             |   |      |  |

| Su  | pply Current                                                          |                          |           |             |     |      |                                                                             |   |      |  |

| 1   | Supply current, standby mode                                          | I <sub>S PDWN</sub>      |           | 50          | 100 | nA   | Pin 27 (PDWN)<br>open or tied to 0 V                                        |   |      |  |

| 2   | Supply current, device operating in FSK mode                          | I <sub>SF</sub>          | 4.9       | 5.7         | 6.5 | mA   | Pin 11 (FSEL)<br>open, Pin 15<br>(MSEL) tied to GND                         |   |      |  |

| 3   | Supply current, device operating in ASK mode                          | I <sub>SA</sub>          | 4.2       | 5           | 5.8 | mA   | Pin 11 (FSEL)<br>open, Pin 15<br>(MSEL) open                                |   |      |  |

| LN  | LNA                                                                   |                          |           |             |     |      |                                                                             |   |      |  |

| Siç | gnal Input LNI (PIN 3),  V <sub>T</sub>                               | HRES > 2.8V,             | high gaiı | n mode      |     |      |                                                                             |   |      |  |

| 1   | Average Power Level<br>at BER = 2E-3<br>(Sensitivity)                 | RF <sub>in</sub>         |           | -113        |     | dBm  | Manchester<br>encoded datarate<br>4kBit, 280kHz IF<br>Bandwidth             | • |      |  |

| 2   | Average Power Level<br>at BER = 2E-3<br>(Sensitivity) FSK             | RF <sub>in</sub>         |           | -105        |     | dBm  | Manchester enc.<br>datarate 4kBit,<br>280kHz IF Bandw.,<br>± 50kHz pk. dev. | • |      |  |

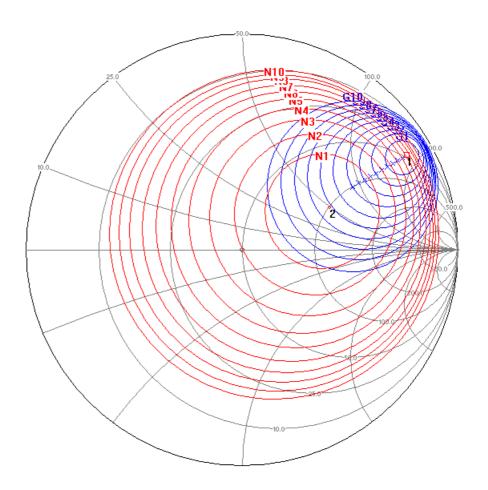

| 3   | Input impedance,<br>f <sub>RF</sub> = 315 MHz                         | S <sub>11 LNA</sub>      | 0.8       | 395 / -25.5 | deg |      |                                                                             | • |      |  |

| 4   | Input level @ 1dB C.P. f <sub>RF</sub> =315 MHz                       | P1dB <sub>LNA</sub>      |           | -14         |     | dBm  |                                                                             | • |      |  |

| 5   | Input 3 <sup>rd</sup> order intercept point f <sub>RF</sub> = 315 MHz | IIP3 <sub>LNA</sub>      |           | -10         |     | dBm  | f <sub>in</sub> = 315 & 317MHz                                              | • |      |  |

| 6   | LO signal feedthrough at antenna port                                 | LO <sub>LNI</sub>        |           | -119        |     | dBm  |                                                                             | • |      |  |

| Siç | gnal Output LNO (PIN 6),                                              | V <sub>THRES</sub> > 2.8 | V, high g | ain mode    |     |      |                                                                             |   |      |  |

| 1   | Gain f <sub>RF</sub> = 315 MHz                                        | S <sub>21 LNA</sub>      | 1.5       | 577 / 150.3 | deg |      |                                                                             |   |      |  |

| 2   | Output impedance,<br>f <sub>RF</sub> = 315 MHz                        | S <sub>22 LNA</sub>      | 0.8       | 397 / -10.3 | deg |      |                                                                             | • |      |  |

|     | Parameter                                                             | Symbol                |          | Limit Valu  | ies | Unit | Test Conditions                                      | L | Item |  |  |

|-----|-----------------------------------------------------------------------|-----------------------|----------|-------------|-----|------|------------------------------------------------------|---|------|--|--|

|     |                                                                       |                       | min      | typ         | max |      |                                                      |   |      |  |  |

| 3   | Voltage Gain Antenna<br>to MI f <sub>RF</sub> = 315 MHz               | G <sub>AntMI</sub>    |          | 21          |     | dB   |                                                      | • |      |  |  |

| 4   | Noise Figure                                                          | NF <sub>LNA</sub>     |          | 2           |     | dB   | excluding matching<br>network loss - see<br>Appendix | • |      |  |  |

| Sig | Signal Input LNI, V <sub>THRES</sub> = GND, low gain mode             |                       |          |             |     |      |                                                      |   |      |  |  |

| 1   | Input impedance,<br>f <sub>RF</sub> = 315 MHz                         | S <sub>11 LNA</sub>   | 0.9      |             | •   |      |                                                      |   |      |  |  |

| 2   | Input level @ 1dB C. P. f <sub>RF</sub> = 315 MHz                     | P1dB <sub>LNA</sub>   |          | -7          |     | dBm  | matched input                                        | • |      |  |  |

| 3   | Input 3 <sup>rd</sup> order intercept point f <sub>RF</sub> = 315 MHz | IIP3 <sub>LNA</sub>   |          | -13         |     | dBm  | f <sub>in</sub> = 315 & 317MHz                       | • |      |  |  |

| Siç | gnal Output LNO, V <sub>THRES</sub>                                   | = GND, low            | gain mod | le          |     |      |                                                      |   |      |  |  |

| 1   | Gain f <sub>RF</sub> = 315 MHz                                        | S <sub>21 LNA</sub>   | 0.1      | 93 / 153.7  | deg |      |                                                      | • |      |  |  |

| 2   | Output impedance,<br>f <sub>RF</sub> = 315 MHz                        | S <sub>22 LNA</sub>   | 0.9      | 907 / -10.5 | deg |      | •                                                    |   |      |  |  |

| 3   | Voltage Gain Antenna<br>to MI f <sub>RF</sub> = 315 MHz               | G <sub>AntMI</sub>    |          | 2           |     | dB   |                                                      | • |      |  |  |

| Siç | gnal 3VOUT (PIN 24)                                                   |                       |          |             |     |      |                                                      |   |      |  |  |

| 1   | Output voltage                                                        | V <sub>3VOUT</sub>    | 2.9      | 3.1         | 3.3 | V    | 3VOUT Pin open                                       |   |      |  |  |

| 2   | Current out                                                           | I <sub>3VOUT</sub>    | -3       | -5          | -10 | μΑ   | see Section 4.1                                      |   |      |  |  |

| Siç | nal THRES (PIN 23)                                                    |                       |          |             |     |      |                                                      |   |      |  |  |

| 1   | Input Voltage range                                                   | V <sub>THRES</sub>    | 0        |             | VS  | V    | see Section 4.1                                      |   |      |  |  |

| 2   | LNA low gain mode                                                     | V <sub>THRES</sub>    | 0        |             | 0.3 | V    |                                                      |   |      |  |  |

| 3   | LNA high gain mode                                                    | V <sub>THRES</sub>    | 3.3      |             | VS  | V    | or shorted to VCC                                    |   |      |  |  |

| 4   | Current in                                                            | I <sub>THRES_in</sub> |          | 5           |     | nA   |                                                      |   |      |  |  |

| Siç | gnal TAGC (PIN 4)                                                     |                       |          |             |     |      |                                                      |   |      |  |  |

| 1   | Current out,<br>LNA low gain state                                    | I <sub>TAGC_out</sub> | -3.6     | -4.2        | -5  | μA   | RSSI > V <sub>THRES</sub>                            |   |      |  |  |

| 2   | Current in,<br>LNA high gain state                                    | I <sub>TAGC_in</sub>  | 1        | 1.6         | 2.2 | μΑ   | RSSI < V <sub>THRES</sub>                            |   |      |  |  |

|     | XER                                                                   |                       |          |             |     |      |                                                      |   |      |  |  |

|     | gnal Input MI/MIX (PINS 8/                                            | •                     |          |             |     |      |                                                      |   |      |  |  |

| 1   | Input impedance,<br>f <sub>RF</sub> = 315 MHz                         | S <sub>11 MIX</sub>   | 9.0      | 954 / -10.9 | deg |      |                                                      |   |      |  |  |

| 2   | Input 3 <sup>rd</sup> order intercept point                           | IIP3 <sub>MIX</sub>   |          | -25         |     | dBm  |                                                      |   |      |  |  |

| Та  | ble 5-3 AC/DC Character                                            | ristics with T <sub>A</sub> | 25 °C, V                 | vcc = 4.5          | 5.5 V (c                 | ontinue | d)                           |   |      |  |

|-----|--------------------------------------------------------------------|-----------------------------|--------------------------|--------------------|--------------------------|---------|------------------------------|---|------|--|

|     | Parameter                                                          | Symbol                      | l                        | Limit Valu         | es                       | Unit    | Test Conditions              | L | Item |  |

|     |                                                                    |                             | min                      | typ                | max                      |         |                              |   |      |  |

| Siç | gnal Output IFO (PIN 12)                                           |                             |                          |                    |                          |         |                              |   |      |  |

| 1   | Output impedance                                                   | Z <sub>IFO</sub>            |                          | 330                |                          | Ω       |                              |   |      |  |

| 2   | Conversion Voltage<br>Gain f <sub>RF</sub> = 315 MHz               | G <sub>MIX</sub>            |                          | 21                 |                          | dB      |                              | • |      |  |

| 3   | Noise Figure, SSB<br>(~DSB NF+3dB)                                 | NF <sub>MIX</sub>           |                          | 13                 |                          | dB      |                              | • |      |  |

| 4   | RF to IF isolation                                                 | A <sub>RF-IF</sub>          |                          | 46                 |                          | dB      |                              |   |      |  |

| LIN | LIMITER                                                            |                             |                          |                    |                          |         |                              |   |      |  |

| Siç | gnal Input LIM/X (PINS 17                                          | /18)                        |                          |                    |                          |         |                              |   |      |  |

| 1   | Input Impedance                                                    | $Z_{LIM}$                   | 264                      | 330                | 396                      | Ω       |                              | • |      |  |

| 2   | RSSI dynamic range                                                 | DR <sub>RSSI</sub>          | 60                       |                    | 80                       | dB      |                              |   |      |  |

| 3   | RSSI linearity                                                     | LIN <sub>RSSI</sub>         |                          | ±1                 |                          | dB      |                              |   |      |  |

| 4   | Operating frequency (3dB points)                                   | f <sub>LIM</sub>            | 5                        | 10.7               | 23                       | MHz     |                              | • |      |  |

| DA  | TA FILTER                                                          |                             |                          |                    |                          |         |                              |   |      |  |

| 1   | Useable bandwidth                                                  | BW <sub>BB FILT</sub>       |                          |                    | 100                      | kHz     |                              |   |      |  |

| 2   | RSSI Level at Data Filter Output SLP,<br>RF <sub>IN</sub> =-103dBm | RSSI <sub>low</sub>         | 0.3                      |                    | 1                        | V       | LNA in high gain mode        |   |      |  |

| 3   | RSSI Level at Data Filter Output SLP,<br>RF <sub>IN</sub> =-30dBm  | RSSI <sub>high</sub>        | 1.8                      |                    | 3                        | V       | LNA in high gain mode        |   |      |  |

| SL  | ICER                                                               |                             |                          |                    |                          |         |                              |   |      |  |

|     | gnal Output DATA (PIN 25                                           | 5)                          |                          |                    |                          |         |                              |   |      |  |

| 1   | Maximum Datarate                                                   | DR <sub>max</sub>           |                          |                    | 100                      | kBps    | NRZ, 20pF capacitive loading | • |      |  |

| 2   | LOW output voltage                                                 | V <sub>SLIC_L</sub>         | 0                        |                    | 0.1                      | V       |                              |   |      |  |

| 3   | HIGH output voltage                                                | V <sub>SLIC_H</sub>         | V <sub>S</sub> -<br>1.3V | V <sub>S</sub> -1V | V <sub>S</sub> -<br>0.7V | V       |                              |   |      |  |

| Sli | cer, Signal Output DATA                                            | (PIN 20)                    |                          |                    |                          |         |                              |   |      |  |

| 1   | Precharge Current Out                                              | I <sub>PCH_SLN</sub>        | -100                     | -220               | -300                     | μΑ      | see Section 4.7              |   |      |  |

|     |                                                                    |                             |                          |                    |                          |         |                              |   |      |  |

|     | Parameter                                          | Symbol               | L    | imit Valu       | es             | Unit       | Test Conditions                    | L | Item |

|-----|----------------------------------------------------|----------------------|------|-----------------|----------------|------------|------------------------------------|---|------|

|     |                                                    |                      | min  | typ             | max            |            |                                    |   |      |

| È   | AK DETECTOR                                        |                      |      |                 |                |            |                                    |   |      |

| Się | gnal Output PDO (PIN 26)                           |                      |      |                 |                |            |                                    |   |      |

| 1   | Load current                                       | I <sub>load</sub>    | -600 | -950            | -1300          | μΑ         |                                    |   |      |

| 2   | Leakage current                                    | I <sub>leakage</sub> | 0    | 200             | 1000           | nA         |                                    |   |      |

| CR  | YSTAL OSCILLATOR                                   |                      |      |                 |                |            |                                    |   |      |

| Siç | gnals CRSTL1, CRISTL 2,                            | (PINS 1/28)          |      |                 |                |            |                                    |   |      |

| 1   | Operating frequency                                | f <sub>CRSTL</sub>   | 5    |                 | 11             | MHz        | fundamental mode, series resonance |   |      |

| 2   | Input Impedance<br>@ ~5MHz                         | Z <sub>1-28</sub>    |      | -850 +<br>j 625 |                | Ω          |                                    | • |      |

| 3   | Input Impedance<br>@ ~10MHz                        | Z <sub>1-28</sub>    |      | -700 +<br>j 865 |                | Ω          |                                    | • |      |

| 4   | Serial Capacity @ ~5MHz                            | C <sub>S 5</sub> =C1 |      | 9.7             |                | pF         |                                    |   |      |

| 5   | Serial Capacity @ ~10MHz                           | C <sub>S10</sub> =C1 |      | 7.2             |                | pF         |                                    |   |      |

| AS  | K/FSK Signal Switch                                |                      |      |                 |                |            |                                    |   |      |

| Siç | gnal MSEL (PIN 15)                                 |                      |      |                 |                |            |                                    |   |      |

| 1   | ASK Mode                                           | V <sub>MSEL</sub>    | 1.4  |                 | 4              | V          | or open                            |   |      |

| 2   | FSK Mode                                           | V <sub>MSEL</sub>    | 0    |                 | 0.2            | V          | or tied to ground                  |   |      |

| FS  | K DEMODULATOR                                      |                      |      |                 |                |            |                                    |   |      |

| 1   | Demodulation Gain                                  | G <sub>FMDEM</sub>   | 85   | 140             | 225            | μV/<br>kHz |                                    |   |      |

| 2   | Useable IF Bandwidth                               | BW <sub>IFPLL</sub>  | 10.2 | 10.7            | 11.2           | MHz        |                                    |   |      |

| PC  | WER DOWN MODE                                      |                      |      |                 |                |            |                                    |   |      |

| Siç | gnal PDWN (PIN 27)                                 |                      |      |                 |                |            |                                    |   |      |

| 1   | Powerdown Mode On                                  | PWDN <sub>ON</sub>   | 0    |                 | 0.8            | V          |                                    |   |      |

| 2   | Powerdown Mode Off                                 | PWDN <sub>Off</sub>  | 2.8  |                 | V <sub>S</sub> | V          |                                    |   |      |

| 3   | Input bias current<br>PDWN                         | I <sub>PDWN</sub>    |      | 19              |                | μA         | Power On Mode                      |   |      |

| 4   | Start-up Time until valid<br>IF signal is detected | T <sub>SU</sub>      |      |                 | 1              | ms         |                                    |   |      |

| Та  | Table 5-3 AC/DC Characteristics with T <sub>A</sub> 25 °C, V <sub>VCC</sub> = 4.5 5.5 V (continued) |                   |     |           |     |      |                  |   |      |  |  |

|-----|-----------------------------------------------------------------------------------------------------|-------------------|-----|-----------|-----|------|------------------|---|------|--|--|

|     | Parameter                                                                                           | Symbol            | L   | imit Valu | es  | Unit | Test Conditions  | L | Item |  |  |

|     |                                                                                                     |                   | min | typ       | max |      |                  |   |      |  |  |

| PL  | PLL DIVIDER                                                                                         |                   |     |           |     |      |                  |   |      |  |  |

| Sig | gnal CSEL (PIN 16)                                                                                  |                   |     |           |     |      |                  |   |      |  |  |

| 1   | f <sub>CRSTL</sub> range 5.xxMHz                                                                    | V <sub>CSEL</sub> | 1.4 |           | 4   | V    | or open          |   |      |  |  |

| 2   | f <sub>CRSTL</sub> range<br>10.xxMHz                                                                | V <sub>CSEL</sub> | 0   |           | 0.2 | V    |                  |   |      |  |  |

| 3   | Input bias current<br>CSEL                                                                          | I <sub>CSEL</sub> | -3  | -5        | -7  | μA   | CSEL tied to GND |   |      |  |  |

Measured only in lab.

## 5.1.4 AC/DC Characteristics at T<sub>AMB</sub> = -40 to 105°C

Currents flowing into the device are denoted as positive currents and vice versa.

| Та  | ble 5-4 AC/DC Character                                             |                       |     |            |                    |      |                                                            |   |      |

|-----|---------------------------------------------------------------------|-----------------------|-----|------------|--------------------|------|------------------------------------------------------------|---|------|

|     | Parameter                                                           | Symbol                | l   | _imit Valu | es                 | Unit | Test Conditions                                            | L | Item |

|     |                                                                     |                       | min | typ        | max                |      |                                                            |   |      |

| Su  | pply                                                                |                       |     |            |                    |      |                                                            |   |      |

| Su  | pply Current                                                        |                       |     |            |                    |      |                                                            |   |      |

| 1   | Supply current, standby mode                                        | I <sub>S PDWN</sub>   |     | 50         | 400                | nA   | Pin 27 (PDWN)<br>open or tied to 0 V                       |   |      |

| 2   | Supply current, device operating in FSK mode                        | I <sub>SF</sub>       | 3.9 | 5.7        | 7.5                | mA   | Pin 11 (FSEL) tied<br>to GND, Pin 15<br>(MSEL) tied to GND |   |      |

| 3   | Supply current, device operating in ASK mode                        | I <sub>SA</sub>       | 3.2 | 5          | 6.8                | mA   | Pin 11 (FSEL)<br>open, Pin 15<br>(MSEL) open               |   |      |

| Siç | gnal 3VOUT (PIN 24)                                                 |                       |     |            |                    |      |                                                            |   |      |

| 1   | Output voltage                                                      | V <sub>3VOUT</sub>    | 2.9 | 3.1        | 3.3                | V    | 3VOUT Pin open                                             |   |      |

| 2   | Current out                                                         | I <sub>3VOUT</sub>    | -3  | -5         | -10                | μA   | see Section 4.1                                            |   |      |

| Siç | nal THRES (PIN 23)                                                  |                       |     |            |                    |      |                                                            |   |      |

| 1   | Input Voltage range                                                 | V <sub>THRES</sub>    | 0   |            | V <sub>S</sub> -1V | V    | see Section 4.1                                            |   |      |