# Dual SYNC Buck Controller with SPI Interface Infineon LITIX™ Power Flex

| Package    | PG-VQFN-48  |

|------------|-------------|

| Marking    | TLD55012QV  |

| Sales Name | TLD5501-2QV |

### 1 Overview

#### **Features**

- Dual-Channel synchronous DC/DC Controller for HIGH POWER LED drivers

- Wide LED forward voltage Range (2 V up to 50 V)

- Wide VIN Range (IC 4.5 V to 40 V, Power 4.5 V to 55 V)

- Switching Frequency Range from 200 kHz to 700 kHz

- SPI for diagnostics and control

- Maximum Efficiency in every condition (up to 96%)

- Constant Current (LED) and Constant Voltage Regulation

- Limp Home Function (Fail Safe Mode)

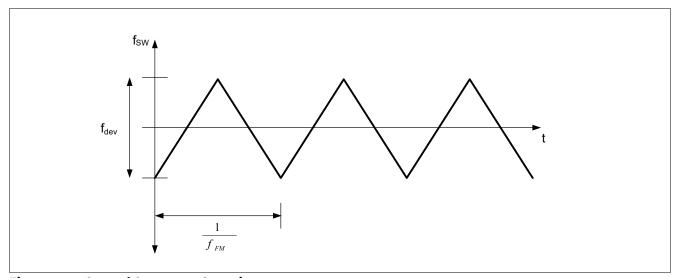

- EMC optimized device: Features an auto Spread Spectrum

- LED current sense with dedicated monitor Output

- · Advanced protection features for device and load

- Enhanced Dimming features: Analog and PWM dimming

- LED current accuracy +/- 3%

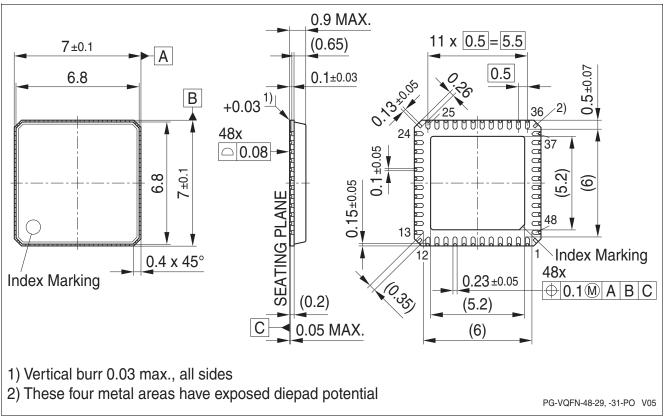

- Available in a small thermally enhanced PG-VQFN-48 package

- Automotive AEC Q100 Grade 1 (-40°C to 125°C) qualified

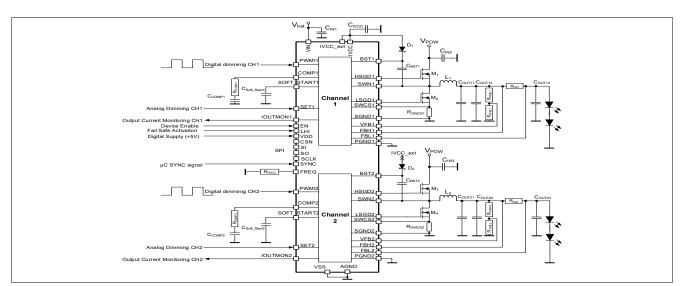

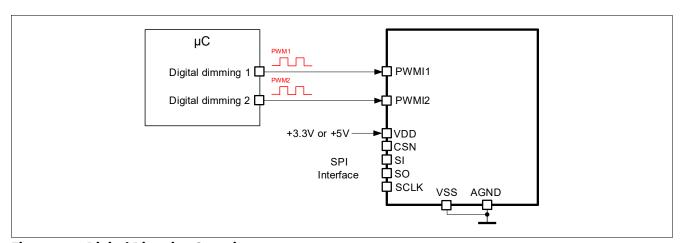

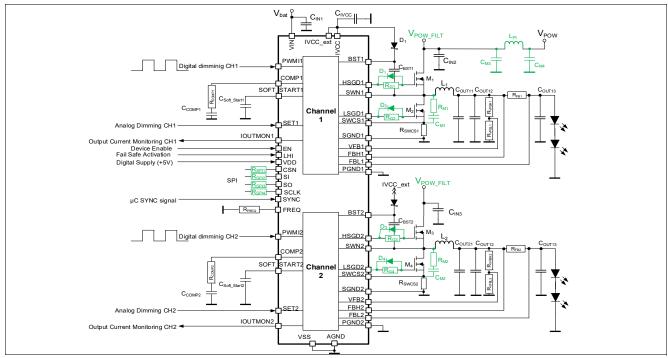

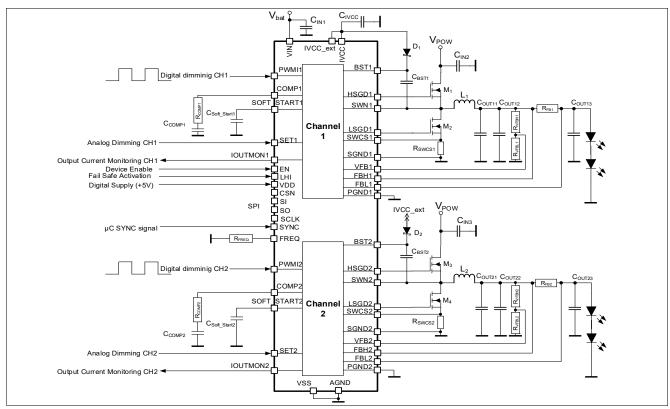

Figure 1 Application Drawing - TLD5501-2QV as current regulator

#### **Dual SYNC Buck Controller with SPI Interface**

#### Overview

#### **Description**

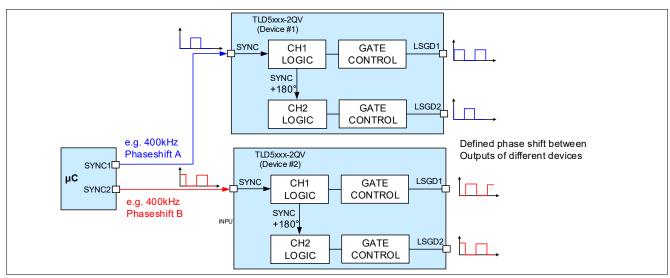

The TLD5501-2QV is a synchronous DUAL Channel DC/DC buck controller with built in protection features and SPI interface. This concept is beneficial for driving high power LEDs with maximum system efficiency and minimum number of external components. The TLD5501-2QV offers both analog and digital (PWM) dimming. The switching frequency is adjustable in the range of 200 kHz to 700 kHz. It can be synchronized to an external clock source. A built in programmable Spread Spectrum switching frequency modulation and the forced continuous current regulation mode improve the overall EMC behavior. Furthermore the current mode regulation scheme provides a stable regulation loop maintained by small external compensation components. The adjustable soft start feature limits the current peak as well as voltage overshoot at start-up. The TLD5501-2QV is suitable for use in the harsh automotive environment.

#### Table 1 Product Summary

| Power Stage input voltage range                                                        | $V_{POW}$              | 4.5 V 55 V      |

|----------------------------------------------------------------------------------------|------------------------|-----------------|

| Device Input supply voltage range                                                      | $V_{VIN}$              | 4.5 V 40 V      |

| Maximum output voltage (depending by the application conditions)                       | $V_{OUT(max)}$         | 50 V            |

| Switching Frequency range                                                              | $f_{\sf SW}$           | 200 kHz 700 kHz |

| Typical NMOS driver on-state resistance at $T_j = 25$ °C (Gate Pull Up)                | R <sub>DS(ON_PU)</sub> | 2.3 Ω           |

| Typical NMOS driver on-state resistance at $T_j = 25^{\circ}\text{C}$ (Gate Pull Down) | R <sub>DS(ON_PD)</sub> | 1.2 Ω           |

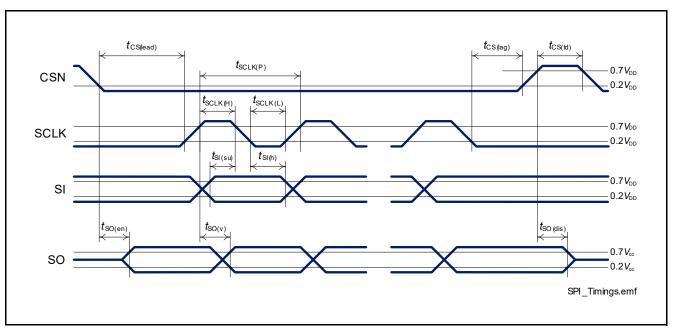

| SPI clock frequency                                                                    | f <sub>SCLK(MAX)</sub> | 5 MHz           |

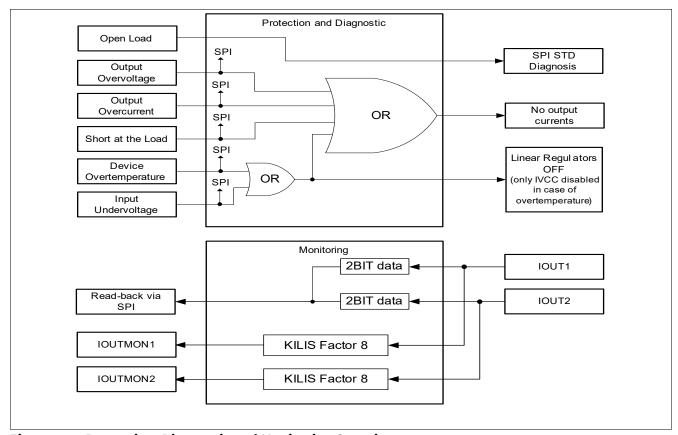

#### **Protective Functions**

- Over load protection of external MOSFETs

- Shorted load, output overvoltage and overcurrent protection

- Input undervoltage protection

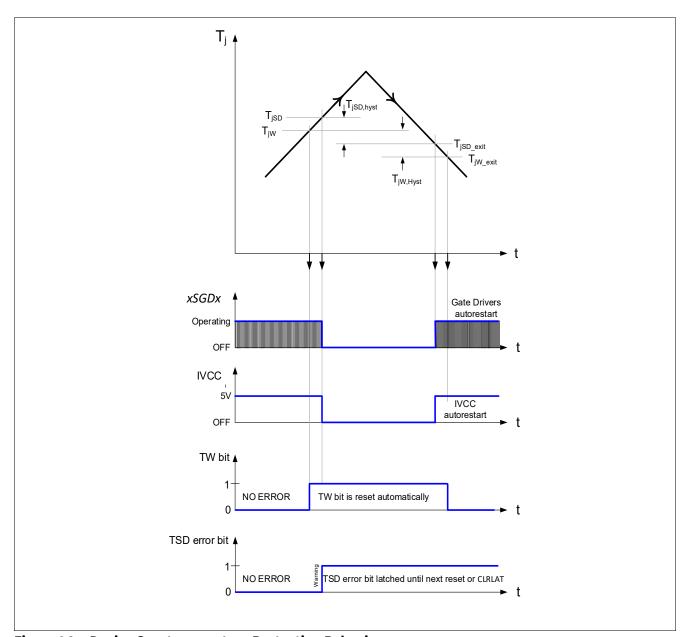

- · Thermal shutdown of device with autorestart behavior

- Electrostatic discharge protection (ESD)

#### **Diagnostic Functions**

- Latched diagnostic information via SPI

- Open load detection in ON-state

- Device Overtemperature shutdown and Temperature Prewarning

- Smart monitoring and advanced functions provide I<sub>LED</sub> information

#### **Limp Home Function**

Limp Home activation via LHI pin

#### **Applications**

- Especially designed for driving high power LEDs in automotive applications

- Automotive Exterior Lighting: full LED headlamp assemblies (Low Beam, High Beam, Matrix Beam, Pixel Light)

- General purpose current/voltage controlled DC/DC buck LED driver

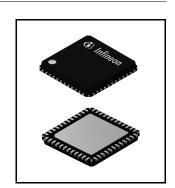

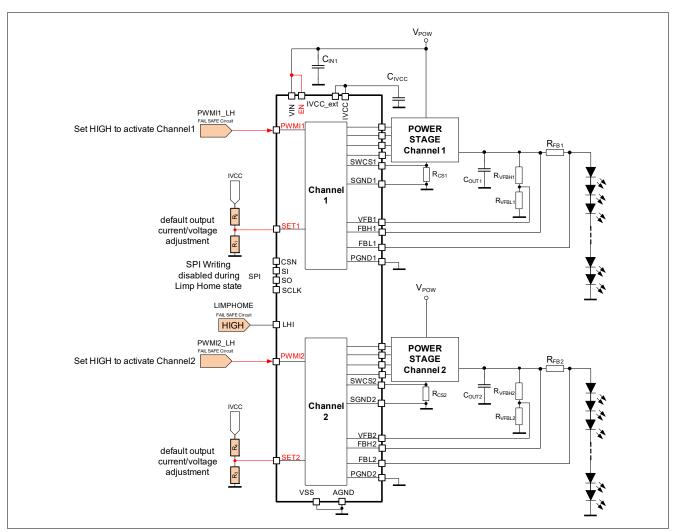

**Block Diagram**

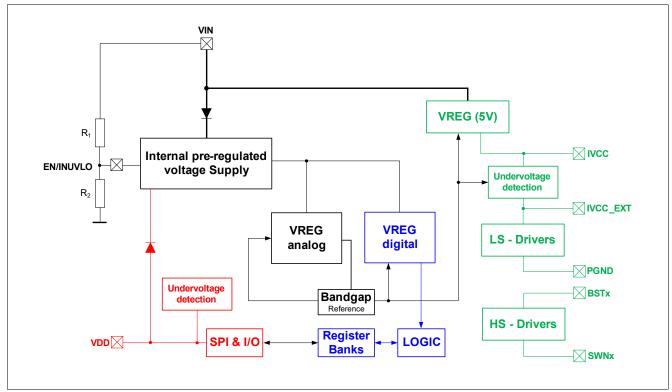

# 2 Block Diagram

Figure 2 Block Diagram - TLD5501-2QV

**Pin Configuration**

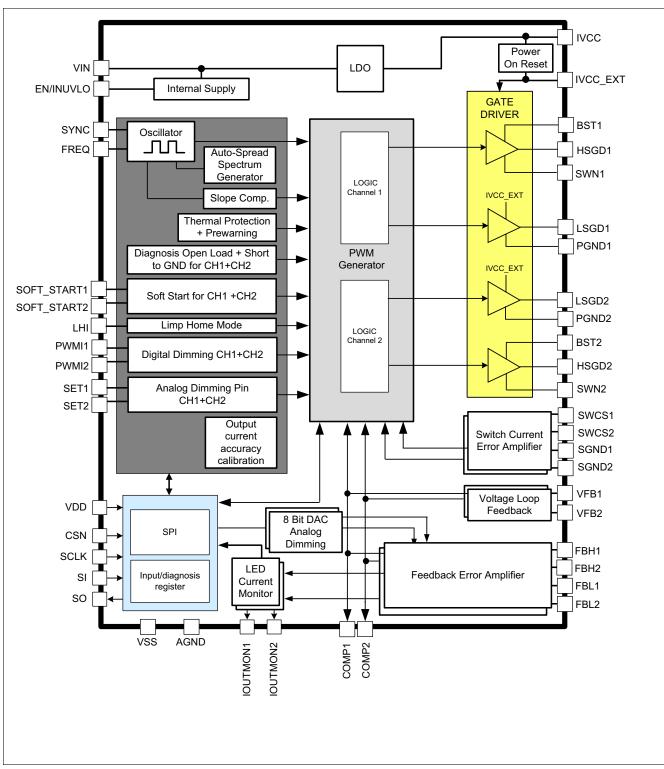

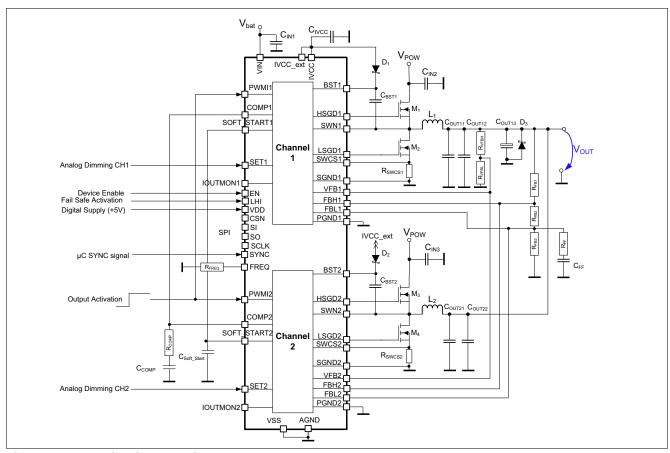

# **3** Pin Configuration

# 3.1 Pin Assignment

Figure 3 Pin Configuration - TLD5501-2QV

**Pin Configuration**

#### **Pin Definitions and Functions** 3.2

Table 2 **Pin Definitions and Functions**

| Pin          | Symbol        | I/O      | 1)                                                                                                           | Function                                                                                                                                                                                                       |

|--------------|---------------|----------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Powe         | r Supply      | <u>'</u> |                                                                                                              |                                                                                                                                                                                                                |

| 16,34,<br>35 | n.c.          | -        |                                                                                                              | Not connected tie to AGND on the layout                                                                                                                                                                        |

| 37           | VIN           | -        |                                                                                                              | Power Supply Voltage Supply for internal biasing                                                                                                                                                               |

| 31           | VDD           | -        |                                                                                                              | <b>Digital GPIO Supply Voltage</b> Connect to reverse voltage protected 5 V or 3.3 V supply                                                                                                                    |

| 45           | IVCC_EXT      | I        | PD                                                                                                           | External LDO input Input to alternatively supply internal Gate Drivers via an external LDO. Connect to IVCC pin to use internal LDO to supply gate drivers. Must not be left open                              |

| 5, 8         | PGND1, 2      | -        |                                                                                                              | <b>Power Ground</b> Ground for power potential. Connect externally close to the chip                                                                                                                           |

| 26           | VSS           | -        |                                                                                                              | Digital GPIO Ground Ground for GPIO pins                                                                                                                                                                       |

| 22           | AGND          | -        |                                                                                                              | Analog Ground Ground Reference                                                                                                                                                                                 |

| -            | EP            | -        | - <b>Exposed Pad</b> Connect to external heatspreading Cu area (e.g. inner multilayer PCB with thermal vias) |                                                                                                                                                                                                                |

| Gate I       | Driver Stages |          |                                                                                                              |                                                                                                                                                                                                                |

| 2            | HSGD1         | 0        |                                                                                                              | <b>Highside Gate Driver Output 1</b> Drives the top n-channel MOSFET with a voltage equal to $V_{\text{IVCC\_EXT}}$ superimposed on the switch node voltage SWN1. Connect to gate of external switching MOSFET |

| 11           | HSGD2         | 0        |                                                                                                              | <b>Highside Gate Driver Output 2</b> Drives the top n-channel MOSFET with a voltage equal to $V_{\text{IVCC\_EXT}}$ superimposed on the switch node voltage SWN2. Connect to gate of external switching MOSFET |

| 6            | LSGD1         | 0        |                                                                                                              | <b>Lowside Gate Driver Output 1</b> Drives the lowside n-channel MOSFET between GND and $V_{\rm IVCC\_EXT}$ . Connect to gate of external switching MOSFET                                                     |

| 7            | LSGD2         | 0        |                                                                                                              | <b>Lowside Gate Driver Output 2</b> Drives the lowside n-channel MOSFET between GND and $V_{\rm IVCC\_EXT}$ . Connect to gate of external switching MOSFET                                                     |

| 4            | SWN1          | Ю        |                                                                                                              | Switch Node 1                                                                                                                                                                                                  |

| 9            | SWN2          | Ю        |                                                                                                              | Switch Node 2                                                                                                                                                                                                  |

| 39           | IVCC          | 0        |                                                                                                              | Internal LDO output Used for internal biasing and gate driver supply. Bypass with external capacitor close to the pin. Pin must not be left open                                                               |

### **Dual SYNC Buck Controller with SPI Interface**

### **Pin Configuration**

Table 2 **Pin Definitions and Functions**

| Pin   | Symbol        | I/O | 1) | Function                                                                                                                                                                                                     |

|-------|---------------|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input | s and Outputs |     |    |                                                                                                                                                                                                              |

| 38    | LHI           | I   | PD | Limp Home Input Pin Used to enter in Limp Home state during Fail Safe condition.                                                                                                                             |

| 23    | TEST2         | -   |    | <b>Test Pin</b> Used for Infineon end of line test, connect to GND in application                                                                                                                            |

| 36    | EN/INUVLO     | I   | PD | Enable/Input Under Voltage Lock Out Used to put the device in a low current consumption mode, with additional capability to fix an undervoltage threshold via external components. Pin must not be left open |

| 25    | FREQ          | I   |    | Frequency Select Input Connect external resistor to GND to set frequency                                                                                                                                     |

| 24    | SYNC          | I   | PD | Synchronization Input Apply external clock signal for synchronization                                                                                                                                        |

| 32    | PWMI1         | I   | PD | Control Input CH1 Digital input 5 V or 3.3 V                                                                                                                                                                 |

| 33    | PWMI2         | I   | PD | Control Input CH2 Digital input 5 V or 3.3 V                                                                                                                                                                 |

| 1     | FBH1          | I   |    | Output current Feedback Positive for CH1 Non inverting Input (+) CH1                                                                                                                                         |

| 12    | FBH2          | I   |    | Output current Feedback Positive for CH2 Non inverting Input (+) CH2                                                                                                                                         |

| 48    | FBL1          | I   |    | Output current Feedback Negative for CH1 Inverting Input (-) CH1                                                                                                                                             |

| 13    | FBL2          | I   |    | Output current Feedback Negative for CH2 Inverting Input (-) CH2                                                                                                                                             |

| 3     | BST1          | 10  |    | Bootstrap capacitor Used for internal biasing and to drive the Highside Switch HSGD1. Bypass to SWN1 with external capacitor close to the pin. Pin must not be left open                                     |

| 10    | BST2          | Ю   |    | Bootstrap capacitor Used for internal biasing and to drive the Highside Switch HSGD2. Bypass to SWN2 with external capacitor close to the pin. Pin must not be left open                                     |

| 46    | SWCS1         | I   |    | Current Sense Input for CH1 Inductor current sense CH1 - Non Inverting Input (+)                                                                                                                             |

| 15    | SWCS2         | I   |    | Current Sense Input for CH2 Inductor current sense CH2 - Non Inverting Input (+)                                                                                                                             |

| 47    | SGND1         | I   |    | Current Sense Ground for CH1 Inductor current sense CH1 - Inverting Input (-). Route as Differential net with SWCS1 on the Layout                                                                            |

| 14    | SGND2         | I   |    | Current Sense Ground for CH2 Inductor current sense CH2 - Inverting Input (-). Route as Differential net with SWCS2 on the Layout                                                                            |

### **Dual SYNC Buck Controller with SPI Interface**

# **Pin Configuration**

**Pin Definitions and Functions** Table 2

| rgin adjustment  |

|------------------|

| rgin adjustment  |

| art ramp default |

| art ramp default |

| r CH1            |

| r CH2            |

|                  |

|                  |

| a voltage.       |

| a voltage.       |

|                  |

|                  |

|                  |

|                  |

|                  |

| _                |

<sup>1)</sup> O: Output, I: Input,

PD: pull-down circuit integrated,

PU: pull-up circuit integrated

#### **General Product Characteristics**

# 4 General Product Characteristics

# 4.1 Absolute Maximum Ratings

Table 3 Absolute Maximum Ratings<sup>1)</sup>  $T_{\rm J} = -40^{\circ}{\rm C~to~+150^{\circ}C;~all~voltages~with~respect~to~AGND,~(unless~otherwise~specified)}$

| Parameter                                                        | Symbol                            |      | Value | s    | Unit | Note or<br>Test Condition                       | Number   |

|------------------------------------------------------------------|-----------------------------------|------|-------|------|------|-------------------------------------------------|----------|

|                                                                  |                                   | Min. | Тур.  | Max. |      |                                                 |          |

| Supply Voltages                                                  | ı                                 |      |       |      |      |                                                 | 1        |

| VIN<br>Supply Input                                              | $V_{ m VIN}$                      | -0.3 | _     | 60   | V    | -                                               | P_4.1.1  |

| VDD<br>Digital supply voltage                                    | $V_{\mathrm{VDD}}$                | -0.3 | -     | 6    | V    | -                                               | P_4.1.2  |

| IVCC<br>Internal Linear Voltage Regulator<br>Output voltage      | V <sub>IVCC</sub>                 | -0.3 | _     | 6    | V    | _                                               | P_4.1.3  |

| IVCC_EXT External Linear Voltage Regulator Input voltage         | $V_{IVCC\_EXT}$                   | -0.3 | _     | 6    | V    | _                                               | P_4.1.4  |

| Gate Driver Stages                                               | ı                                 | 1    |       |      |      |                                                 | 1        |

| LSGD1,2 - PGND1,2<br>Lowside Gatedriver voltage                  | V <sub>LSGD1,2</sub> -PGND1,2     | -0.3 | _     | 5.5  | V    | -                                               | P_4.1.54 |

| HSGD1,2 - SWN1,2<br>Highside Gatedriver voltage                  | V <sub>HSGD1,2-SWN1,2</sub>       | -0.3 | _     | 5.5  | V    | Differential signal<br>(not referred to<br>GND) | P_4.1.55 |

| SWN1, SWN2<br>switching node voltage                             | V <sub>SWN1,2</sub>               | -1   | -     | 60   | V    | -                                               | P_4.1.6  |

| (BST1-SWN1), (BST2-SWN2)<br>Boostrap voltage                     | V <sub>BST1,2-SWN1,2</sub>        | -0.3 | -     | 6    | V    | Differential signal<br>(not referred to<br>GND) | P_4.1.7  |

| BST1, BST2<br>Boostrap voltage related to GND                    | V <sub>BST1, 2</sub>              | -0.3 | _     | 65   | V    | -                                               | P_4.1.8  |

| SWCS1,2<br>Switch Current Sense Input<br>voltages                | V <sub>SWCS1,2</sub>              | -0.3 | _     | 0.3  | V    | _                                               | P_4.1.42 |

| SGND1,2<br>Switch Current Sense GND voltages                     | V <sub>SGND1,2</sub>              | -0.3 | -     | 0.3  | V    | -                                               | P_4.1.43 |

| SWCS1,2-SGND1,2<br>Switch Current Sense differential<br>voltages | V <sub>SWCS1,2</sub> -<br>SGND1,2 | -0.5 | -     | 0.5  | V    | -                                               | P_4.1.44 |

| PGND1,2<br>Power GND voltage                                     | V <sub>PGND1,2</sub>              | -0.3 | -     | 0.3  | V    | -                                               | P_4.1.28 |

### **Dual SYNC Buck Controller with SPI Interface**

#### **General Product Characteristics**

Table 3 Absolute Maximum Ratings<sup>1)</sup> (cont'd)  $T_{\rm J} = -40^{\circ}\text{C to } +150^{\circ}\text{C; all voltages with respect to AGND, (unless otherwise specified)}$

| Parameter                                                          | Symbol                      |      | Value | S    | Unit | Note or                                   | Number   |

|--------------------------------------------------------------------|-----------------------------|------|-------|------|------|-------------------------------------------|----------|

|                                                                    |                             | Min. | Тур.  | Max. |      | <b>Test Condition</b>                     |          |

| High voltage Pins                                                  |                             |      |       | 1    |      |                                           | 1        |

| FBH1,2; FBL1,2<br>Feedback Error Amplifier voltages                | V <sub>FBH1,2; FBL1,2</sub> | -0.3 | _     | 60   | V    | -                                         | P_4.1.45 |

| FBH1,2-FBL1,2<br>Feedback Error Amplifier<br>differential voltages | V <sub>FBH1,2-FBL1,2</sub>  | -0.5 | _     | 0.5  | V    | Differential signal (not referred to GND) | P_4.1.47 |

| EN/INUVLO Device enable/input undervoltage lockout                 | V <sub>EN/INUVLO</sub>      | -0.3 | _     | 60   | V    | -                                         | P_4.1.16 |

| Digital (I/O) Pins                                                 |                             | -    | *     | *    |      |                                           |          |

| PWMI1,2<br>Digital Input voltages                                  | V <sub>PWMI1,2</sub>        | -0.3 | _     | 5.5  | V    | -                                         | P_4.1.49 |

| CSN<br>Voltage at Chip Select pin                                  | V <sub>CSN</sub>            | -0.3 | _     | 5.5  | V    | -                                         | P_4.1.18 |

| SCLK<br>Voltage at Serial Clock pin                                | V <sub>SCLK</sub>           | -0.3 | _     | 5.5  | V    | -                                         | P_4.1.19 |

| SI<br>Voltage at Serial Input pin                                  | V <sub>SI</sub>             | -0.3 | _     | 5.5  | V    | -                                         | P_4.1.20 |

| SO<br>Voltage at Serial Output pin                                 | V <sub>so</sub>             | -0.3 | -     | 5.5  | V    | -                                         | P_4.1.21 |

| SYNC<br>Synchronization Input voltage                              | V <sub>SYNC</sub>           | -0.3 | _     | 5.5  | V    | -                                         | P_4.1.22 |

| LHI<br>Limp Home Input Voltage                                     | V <sub>LHI</sub>            | -0.3 | _     | 5.5  | V    | -                                         | P_4.1.58 |

| LHI<br>Limp Home Input Current                                     | I <sub>LHI</sub>            | -5   | _     | -    | mA   | -                                         | P_4.1.60 |

| Analog Pins                                                        |                             |      |       |      |      |                                           |          |

| VFB1,2<br>Loop Input voltages                                      | V <sub>VFB1,2</sub>         | -0.3 | _     | 5.5  | V    | _                                         | P_4.1.50 |

| SET1,2<br>Analog dimming Input voltage                             | V <sub>SET1,2</sub>         | -0.3 | -     | 5.5  | V    | -                                         | P_4.1.56 |

| COMP1,2<br>Compensation Input voltages                             | V <sub>COMP1,2</sub>        | -0.3 | _     | 3.6  | V    | -                                         | P_4.1.52 |

| SOFT_START1,2<br>Softstart Voltages                                | V <sub>SOFT_START1,2</sub>  | -0.3 | -     | 3.6  | V    | -                                         | P_4.1.53 |

| FREQ Voltage at frequency selection pin                            | $V_{FREQ}$                  | -0.3 | -     | 3.6  | V    | -                                         | P_4.1.32 |

| IOUTMON1,2<br>Voltages at output monitor pins                      | V <sub>IOUTMON1,2</sub>     | -0.3 | -     | 5.5  | V    | -                                         | P_4.1.59 |

#### **Dual SYNC Buck Controller with SPI Interface**

#### **General Product Characteristics**

Table 3 Absolute Maximum Ratings<sup>1)</sup> (cont'd)  $T_1 = -40^{\circ}\text{C to } +150^{\circ}\text{C; all voltages with respect to AGND, (unless otherwise specified)}$

| Parameter                             | Symbol                      | Value | S    | Unit | Note or | Number                |          |

|---------------------------------------|-----------------------------|-------|------|------|---------|-----------------------|----------|

|                                       |                             | Min.  | Тур. | Max. |         | <b>Test Condition</b> |          |

| Temperatures                          |                             |       |      |      |         |                       |          |

| Junction Temperature                  | T <sub>j</sub>              | -40   | _    | 150  | °C      | _                     | P_4.1.35 |

| Storage Temperature                   | $T_{\rm stg}$               | -55   | -    | 150  | °C      | _                     | P_4.1.36 |

| ESD Susceptibility                    |                             |       |      |      | •       |                       |          |

| ESD Resistivity of all Pins           | $V_{\rm ESD,HBM}$           | -2    | _    | 2    | kV      | HBM <sup>2)</sup>     | P_4.1.37 |

| ESD Resistivity to GND                | $V_{\rm ESD,CDM}$           | -500  | -    | 500  | V       | CDM <sup>3)</sup>     | P_4.1.38 |

| ESD Resistivity of corner Pins to GND | V <sub>ESD,CDM_corner</sub> | -750  | _    | 750  | V       | CDM <sup>3)</sup>     | P_4.1.39 |

- 1) Not subject to production test, specified by design.

- 2) ESD susceptibility, Human Body Model "HBM" according to AEC Q100-002

- 3) ESD susceptibility, Charged Device Model "CDM" AECQ100-011

Note:

Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Integrated protection functions are designed to prevent IC destruction under fault conditions described in the datasheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

### 4.2 Functional Range

Table 4 Functional Range

| Parameter                               | Symbol           | Symbol Values |      |      | Unit | Note or                         | Number  |

|-----------------------------------------|------------------|---------------|------|------|------|---------------------------------|---------|

|                                         |                  | Min.          | Тур. | Max. |      | Test Condition                  |         |

| Device Extended Supply Voltage<br>Range | V <sub>VIN</sub> | 4.5           | -    | 40   | V    | (parameter deviations possible) | P_4.2.1 |

| Device Nominal Supply Voltage<br>Range  | $V_{ m VIN}$     | 8             | -    | 36   | V    | -                               | P_4.2.2 |

| Power Stage Voltage Range               | $V_{POW}$        | 4.5           | -    | 55   | V    | 1)                              | P_4.2.5 |

| Digital Supply Voltage                  | $V_{DD}$         | 3             | -    | 5.5  | V    | _                               | P_4.2.3 |

| Junction Temperature                    | T <sub>j</sub>   | -40           | -    | 150  | °C   | _                               | P_4.2.4 |

<sup>1)</sup> Not subject to production test, specified by design.

Note:

Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table

#### **Dual SYNC Buck Controller with SPI Interface**

#### **General Product Characteristics**

#### 4.3 Thermal Resistance

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to **www.jedec.org**.

#### Table 5

| Parameter           | Symbol            | Symbol Values |      | S    | Unit | Note or               | Number  |

|---------------------|-------------------|---------------|------|------|------|-----------------------|---------|

|                     |                   | Min.          | Тур. | Max. |      | <b>Test Condition</b> |         |

| Junction to Case    | $R_{thJC}$        | -             | 0.9  | -    | K/W  | 1) 2)                 | P_4.3.1 |

| Junction to Ambient | R <sub>thJA</sub> | _             | 25   | _    | K/W  | <sup>1) 3)</sup> 2s2p | P_4.3.2 |

- 1) Not subject to production test, specified by design.

- 2) Specified  $R_{thJC}$  value is simulated at natural convection on a cold plate setup (all pins and the exposed pad are fixed to ambient temperature). Ta = 25°C; The IC is dissipating 1 W.

- 3) Specified  $R_{thJA}$  value is according to JEDEC 2s2p (JESD 51-7) + (JESD 51-5) and JEDEC 1s0p (JESD 51-3) + heatsink area at natural convection on FR4 board; The device was simulated on a 76.2 x 114.3 x 1.5 mm board. The 2s2p board has 2 outer copper layers (2 x 70  $\mu$ m Cu) and 2 inner copper layers (2 x 35  $\mu$ m Cu). A thermal via (diameter = 0.3 mm and 25  $\mu$ m plating) array was applied under the exposed pad and connected the first outer layer (top) to the first inner layer and second outer layer (bottom) of the JEDEC PCB. Ta = 25°C; The IC is dissipating 1 W.

**Power Supply**

# 5 Power Supply

The TLD5501-2QV is supplied by the following pins:

- VIN (main supply voltage)

- VDD (digital supply voltage)

- IVCC\_EXT (supply for internal gate driver stages)

The VIN supply, in combination with the VDD supply, provides internal supply voltages for the analog and digital blocks. In situations where VIN voltage drops below VDD voltage, an increased current consumption may be observed at the VDD pin.

The SPI and IO interfaces are supplied by the VDD pin.

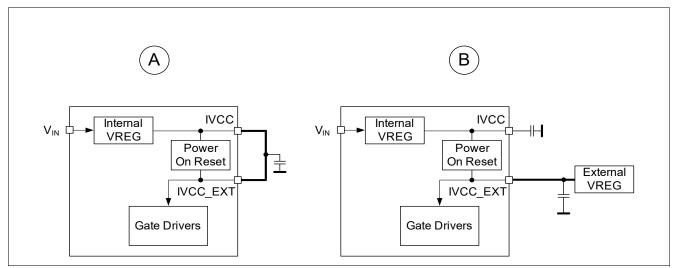

IVCC\_EXT is the supply for the low side driver stages. This supply is used also to charge, through external Schottky diodes, the bootstrap capacitors which provide supply voltages to the high side driver stages. If no external voltage is available this pin must be shorted to IVCC, which is the output of an internal 5 V LDO.

The supply pins VIN, VDD and IVCC\_EXT have undervoltage detections.

Undervoltage on VDD supply voltage prevents the activation of the gate driver stages and any SPI communication (the SPI registers are reset). Undervoltage on IVCC\_EXT or IVCC voltages forces a deactivation of the driver stages, thus stopping the switching activity, but has no effect on the SPI register settings.

Moreover the double function pin EN/INUVLO can be used as an input undervoltage protection by placing a resistor divider from VIN to GND .

If EN/INUVLO undervoltage is detected, it will turn-off the IVCC voltage regulator, stop switching, stop communications and reset all the registers.

**Figure 4** shows a basic concept drawing of the supply domains and interactions among pins VIN, VDD and IVCC/IVCC\_EXT.

Figure 4 Power Supply Concept Drawing

#### **Dual SYNC Buck Controller with SPI Interface**

### **Power Supply**

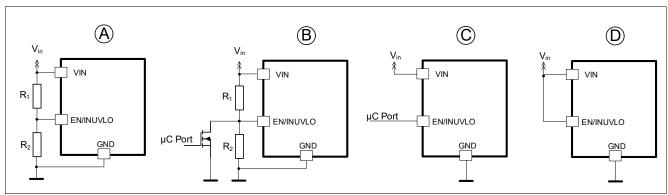

### Usage of EN/INUVLO pin in different applications

The pin EN/INUVLO is a double function pin and can be used to put the device into a low current consumption mode. An undervoltage threshold is fixed by placing an external resistor divider (A) in order to avoid low voltage operating conditions. This pin can be driven by a  $\mu$ C-port as shown in (B) (C).

Figure 5 Usage of EN/INUVLO pin in different applications

#### **Dual SYNC Buck Controller with SPI Interface**

#### **Power Supply**

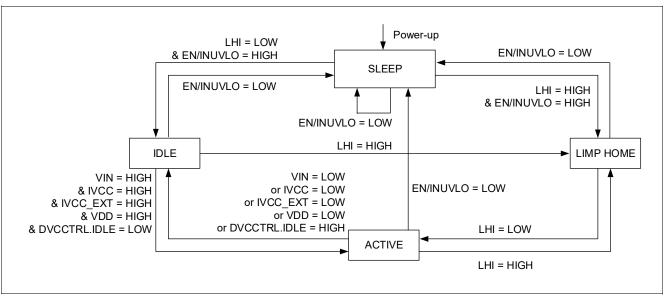

#### 5.1 Different Power States

TLD5501-2QV has the following power states:

- SLEEP state

- IDLE state

- LIMP HOME state

- ACTIVE state

The transition between the power states is determined according to these variables after a filter time of max. 3 clock cycles:

- VIN level

- EN/INUVLO level

- IVCC level

- IVCC\_EXT level

- VDD level

- LHI level

- DVCCTRL.IDLE bit state

The state diagram including the possible transitions is shown in Figure 6.

The Power-up condition is entered when the supply voltage  $V_{VIN}$  exceed its minimum supply voltage threshold  $V_{VIN}(ON)$ .

#### **SLEEP**

When the device is powered it enters the SLEEP state, all outputs are OFF and the SPI registers are reset, independently from the supply voltages at the pins VIN , VDD, IVCC, and IVCC\_EXT. The current consumption is low. Refer to parameters:  $I_{\text{VDD(SLEEP)}}$ , and  $I_{\text{Vin(SLEEP)}}$ .

The transition from SLEEP to ACTIVE state requires a specified time:  $t_{\text{ACTIVE}}$ .

#### **IDLE**

In IDLE state, the current consumption of the device can reach the limits given by parameter  $I_{\rm VDD}$  (P\_5.3.4). The internal voltage regulator is working. Not all diagnosis functions are available (refer to **Chapter 10** for additional informations). In this state there is no switching activity, independently from the supply voltages  $V_{\rm IN}$ ,  $V_{\rm DD}$ , IVCC and IVCC\_EXT. When  $V_{\rm DD}$  is available, the SPI registers are working and SPI communication is possible.

### **Limp Home**

The Limp Home state is beneficial to fulfill system safety requirements and provides the possibility to maintain a defined current/voltage level on the output via a backup control circuitry. The backup control circuitry turns on required loads during a malfunction of the  $\mu$ C. For detailed info, refer to **Chapter 8**.

When Limp Home state is entered, SPI registers are reset to their default values. In order to regulate the output current/voltage, it is necessary that  $V_{\rm IN}$  and IVCC\_EXT are present and above their undervoltage threshold. If also VDD is above its undervoltage threshold, SPI communication is possible but only in read mode.

#### **ACTIVE**

In active state the device will start switching activity to provide power at the output only when PWMI1,2 = HIGH or LOOPCTRL\_CH1, 2. PWM\_1, 2 = HIGH. To start the Highside gate drivers HSGD1,2 the voltage level  $V_{\rm BST1,2}$  -  $V_{\rm SWN1,2}$  needs to be above the threshold  $V_{\rm BST1,2}$  -  $V_{\rm SWN1,2\_UVth}$ . In order to recharge the bootstrap capacitor, sporadic switching activity could also be observed when PWMI1,2 = LOW and LOOPCTRL\_CH1,2.PWM\_1,2 =

#### **Dual SYNC Buck Controller with SPI Interface**

#### **Power Supply**

LOW. In ACTIVE state the device current consumption via  $V_{IN}$  and  $V_{DD}$  is dependent on the external MOSFET used and the switching frequency  $f_{SW}$ .

Figure 6 Simplified State Diagram

#### 5.2 Different Possibilities to RESET the device

There are several reset triggers implemented in the device.

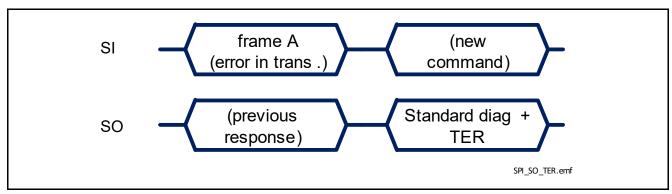

After any kind of reset, the Transmission Error Flag (TER) is set to HIGH.

#### **Under Voltage Reset:**

EN/INUVLO: When EN/INUVLO is below  $V_{\rm EN/INUVLOth}$  (P\_5.3.7), the SPI interface is not working and all the registers are reset to their default values. In addition, the device enters SLEEP mode and the current consumption is minimized.

VDD: When  $V_{\text{VDD}}$  is below  $V_{\text{VDD(UV)}}$  (P\_5.3.6), the SPI interface is not working and all the registers are reset to their default values.

#### **Reset via SPI command:**

There is a command (DVCCTRL.SWRST = HIGH) available to RESET all writeable registers to their default values. Note that the result coming from the Calibration routine, which is readable by the SPI when LOOPCTRL\_CH1, 2 = HIGH, is not reset by the SWRST.

#### **Reset via Limp Home:**

When Limp Home state is detected the registers are reset to the default values.

**Power Supply**

### **5.3** Electrical Characteristics

Table 6 EC Power Supply

$V_{\rm IN}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to AGND; (unless otherwise specified)

| Parameter                                 | Symbol                       |      | Value | S    | Unit | Note or<br>Test Condition                                                                                                                                                                                           | Number   |

|-------------------------------------------|------------------------------|------|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                           |                              | Min. | Тур.  | Max. |      |                                                                                                                                                                                                                     |          |

| Power Supply V <sub>IN</sub>              |                              |      |       |      |      |                                                                                                                                                                                                                     | ı        |

| Input Voltage Startup                     | $V_{\text{VIN(ON)}}$         | -    | _     | 4.7  | V    | $V_{IN}$ increasing;<br>$V_{EN/INUVLO}$ = HIGH;<br>$V_{DD}$ = 5 V;<br>IVCC = IVCC_EXT = 10 mA                                                                                                                       | P_5.3.1  |

| Input Undervoltage switch<br>OFF          | $V_{ m VIN(OFF)}$            | _    | _     | 4.5  | V    | $V_{\text{IN}}$ decreasing;<br>$V_{\text{EN/INUVLO}} = \text{HIGH};$<br>$V_{\text{DD}} = 5 \text{ V};$<br>IVCC = IVCC_EXT = 10 mA                                                                                   | P_5.3.14 |

| Device operating current                  | I <sub>VIN(ACTIVE)</sub>     | _    | 6.2   | 9    | mA   | <sup>1)</sup> ACTIVE mode;<br>V <sub>PWMI1,2</sub> = 0 V                                                                                                                                                            | P_5.3.2  |

| V <sub>IN</sub> Sleep mode supply current | I <sub>VIN(SLEEP)</sub>      | -    | -     | 1.5  | μΑ   | $V_{\text{EN/INUVLO}} = 0 \text{ V};$ $V_{\text{CSN}} = V_{\text{DD}} = 5 \text{ V};$ $V_{\text{IN}} = 13.5 \text{ V};$ $V_{\text{IVCC}} = V_{\text{IVCC}\_\text{EXT}} = 0 \text{ V}$                               | P_5.3.3  |

| Digital Power Supply V <sub>DD</sub>      |                              |      |       |      |      |                                                                                                                                                                                                                     |          |

| Digital supply current                    | $I_{\mathrm{VDD}}$           | _    | -     | 0.5  | mA   | $V_{IN} = 13.5 \text{ V};$<br>$f_{SCLK} = 0 \text{ Hz};$<br>$V_{PWMI1,2} = 0 \text{ V};$<br>$V_{EN} = V_{CSN} = V_{DD} = 5 \text{ V}$                                                                               | P_5.3.4  |

| Digital Supply Sleep mode current         | I <sub>VDD(SLEEP)</sub>      | _    | _     | 1.5  | μΑ   | $\begin{aligned} &V_{\text{EN/INUVLO}} = 0 \text{ V;} \\ &V_{\text{CSN}} = V_{\text{DD}} = 5 \text{ V;} \\ &V_{\text{IN}} = 13.5 \text{ V;} \\ &V_{\text{IVCC}} = V_{\text{IVCC\_EXT}} = 0 \text{ V} \end{aligned}$ | P_5.3.5  |

| Undervoltage shutdown threshold voltage   | $V_{\text{VDD(UV)}}$         | 1    | -     | 3    | V    | $V_{\text{CSN}} = V_{\text{DD}};$<br>$V_{\text{SI}} = V_{\text{SCLK}} = 0 \text{ V};$<br>SO from LOW to HIGH impedance                                                                                              | P_5.3.6  |

| EN/INUVLO Pin characteristi               | ics                          |      |       |      |      |                                                                                                                                                                                                                     |          |

| Input Undervoltage falling<br>Threshold   | V <sub>EN/INUVLOth</sub>     | 1.64 | 1.75  | 1.86 | V    | _                                                                                                                                                                                                                   | P_5.3.7  |

| EN/INUVLO Rising Hysteresis               | V <sub>EN/INUVLO(hyst)</sub> | _    | 90    | _    | mV   | 1)                                                                                                                                                                                                                  | P_5.3.8  |

| EN/INUVLO input Current<br>LOW            | I <sub>EN/INUVLO(LOW)</sub>  | 0.45 | 0.89  | 1.34 | μΑ   | $V_{\rm EN/INUVLO} = 0.8  \rm V$                                                                                                                                                                                    | P_5.3.9  |

| EN/INUVLO input Current<br>HIGH           | I <sub>EN/INUVLO(HIGH)</sub> | 1.1  | 2.2   | 3.3  | μΑ   | V <sub>EN/INUVLO</sub> = 2 V                                                                                                                                                                                        | P_5.3.10 |

### **Dual SYNC Buck Controller with SPI Interface**

### **Power Supply**

#### Table 6 **EC Power Supply** (cont'd)

$V_{\rm IN}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to AGND; (unless otherwise specified)

| Parameter                 | Symbol                         |      | Value       | S    | Unit | Note or<br>Test Condition                                                                                                                   | Number      |

|---------------------------|--------------------------------|------|-------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                           |                                | Min. | Тур.        | Max. |      |                                                                                                                                             |             |

| LHI Pin characteristics   |                                |      | "           |      |      |                                                                                                                                             | -           |

| LOW level                 | $V_{\mathrm{LHI}(\mathrm{L})}$ | 0    | -           | 0.8  | V    | _                                                                                                                                           | P_5.3.16    |

| HIGH level                | $V_{\rm LHI(H)}$               | 2.0  | -           | 5.5  | V    | -                                                                                                                                           | P_5.3.17    |

| L-Input pull-down current | I <sub>LHI(L)</sub>            | 6    | 12          | 18   | μΑ   | V <sub>LHI</sub> = 0.8 V                                                                                                                    | P_5.3.18    |

| H-Input pull-down current | I <sub>LHI(H)</sub>            | 15   | 30          | 45   | μΑ   | V <sub>LHI</sub> = 2.0 V                                                                                                                    | P_5.3.19    |

| Timings                   | ·                              | *    | <del></del> | *    | *    |                                                                                                                                             | <del></del> |

| SLEEP mode to ACTIVE time | t <sub>ACTIVE</sub>            | -    | -           | 0.7  | ms   | $V_{\text{IVCC}} = V_{\text{IVCC\_EXT}};$ $C_{\text{IVCC}} = 10 \mu\text{F};$ $V_{\text{IN}} = 13.5 \text{V};$ $V_{\text{DD}} = 5 \text{V}$ | P_5.3.11    |

<sup>1)</sup> Not subject to production test, specified by design

#### **Dual SYNC Buck Controller with SPI Interface**

### **Regulator Description**

# **6** Regulator Description

The TLD5501-2QV includes all of the functions necessary to provide constant current to the output as usually required to drive LEDs. A voltage mode regulation can also be implemented (Refer to **Chapter 6.5**).

In deep buck applications, due to duty cycle limitations ( $D_{\text{BUCK\_MIN}}$ ) the device will enter pulse skipping mode in order to keep regulating the average output current, the ouptut ripple may increase.

The minimum duty cycle is dependent by the  $f_{sw}$ .

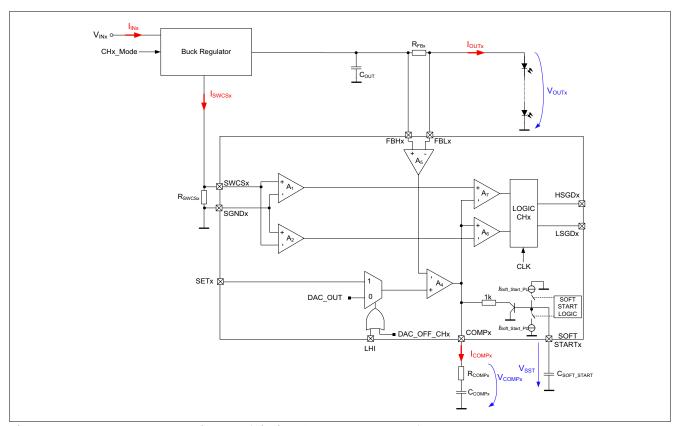

### 6.1 Regulator Diagram Description

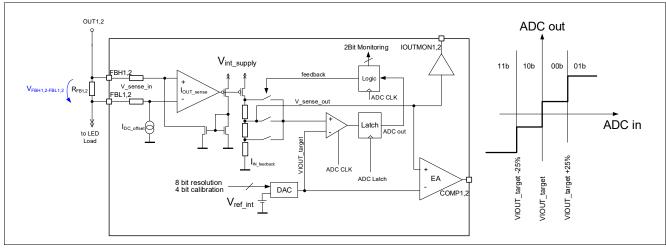

An analog current control loop (A5, A4 with complessive gain =  $IFBx_{gm}$ ) connected to the sensing pins FBL1,2, FBH1,2 regulates the output current.

The regulator function is implemented by a pulse width modulated (PWM) current mode controller. The error in the output current loop is used to determine the appropriate duty cycle to get a constant output current.

An external compensation network ( $R_{COMP}$ ,  $C_{COMP}$ ) is used to adjust the control loop to various application boundary conditions.

The inductor current for the current mode loop is sensed by the  $R_{SWCS}$  resistor.

$R_{SWCS}$  is used also to limit the maximum external switches / inductor current.

If the Voltage across  $R_{SWCS}$  exceeds its overcurrent threshold ( $V_{SWCS1,2\_buck}$ ) the device reduces the duty cycle in order to bring the switches current below the imposed limit.

The current mode controller has a built-in slope compensation as well to prevent sub-harmonic oscillations.

The control loop logic block (LOGIC\_CHx) provides a PWM signal to two internal gate drivers. The gate drivers (HSGD1,2 and LSGD1,2) are used to drive external MOSFETs. Once  $V_{\text{SOFT\_START1,2}}$  exceeds  $V_{\text{Soft\_start1,2\_LOFF}}$  or  $V_{\text{(FBH1,2-FBL1,2)\_VALID}}$  thresholds, TLD5501-2QV forces CCM regulation mode.

The control loop block diagram displayed in **Figure 7** shows a typical constant current application. The voltage across  $R_{FB}$  sets the output current.

The output current is fixed via the SPI parameter (LEDCURRADIM\_CH1, 2.ADIMVAL\_CH1,  $2 = 11110000_B = default$  at 100%) plus an offset trimming (LEDCURRCAL\_CH1, 2.CALIBVAL\_CH1,  $2 = 0000_B = default$  in the middle of the range). Refer to **Chapter 8.1** for more details.

### **Regulator Description**

Figure 7 Regulator Block Diagram (similar for both Channels) - TLD5501-2QV

#### **Dual SYNC Buck Controller with SPI Interface**

### **Regulator Description**

### 6.2 Adjustable Soft Start Ramp

The soft start routine has two functionalities:

- Fault management: fault mask and wait-before-retry time, on rising and falling edge of SOFT\_START1,2

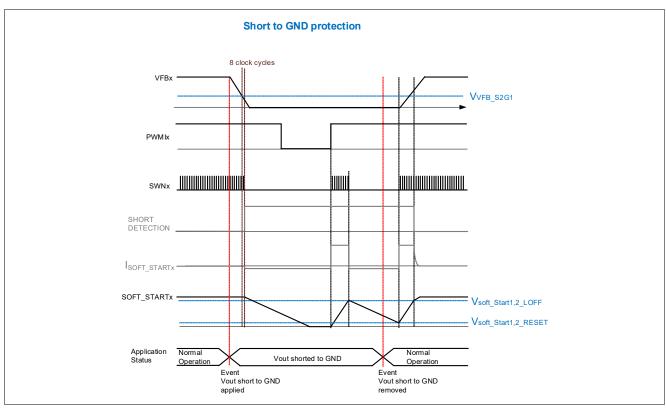

respectively (Figure 8 and Chapter 10.2)

- To limit the current through the inductor and the external MOSFET switches during initialization to minimize potential overshoots at the output.

The soft start routine is applied:

- At startup (first PWM rise after IDLE to ACTIVE transition)

- After Output Short to GND detection

- After channel stop via low analog dimming value (See Chapter 8)

The soft start timing is defined by a capacitor placed at the SOFT\_START pin and the pull-up and pull-down current sources  $(I_{Soft\_Start1,2\_PU},I_{Soft\_Start1,2\_PD})$ .

Minimum value for soft start capacitor has to be designed such that, at startup, the output voltage exceeds the short to ground threshold before the soft start voltage reaches  $V_{\text{SOFT\_START1,2\_LOFF}}$ . Minimum temperature and minimum input voltage shall be considered as worst case condition for previously mentioned dimensioning. Soft Start rising edge time is approximately:

$$t_{SOFT\_START1,2} = V_{Soft\_Start1,2\_LOFF} \cdot \frac{C_{Soft\_Start1,2}}{I_{Soft\_Start1,2\_PU}}$$

(6.1)

The Soft Start routine limits the inrush current by clamping the COMP pin through a buffer as in **Figure 7**. Therefore, this functionality is effective only when soft start capacitor is sufficiently larger than the COMP capacitor.

If a short on the output is detected, a pull-down current source  $I_{SOFT\_START1,2\_PD}$  (P\_6.4.59) is activated. This current brings down the  $V_{SOFT\_START1,2}$  until  $V_{SOFT\_START1,2\_RESET}$  (P\_6.4.61) is reached, then the pull-up current source  $I_{SOFT\_START1,2\_PU}$  (P\_6.4.58) turns on again, if PWMI1,2 is high, see **Figure 8**. If the fault condition hasn't been removed until  $V_{SOFT\_START1,2\_LOFF}$  (P\_6.4.60) is reached, the pull-down current source turns back on again, initiating a new cycle. This will continue until the fault is removed.

During rising edge of soft start, the internal PWM is extended until one of the 2 following conditions is reached:

- Until V<sub>SOFT\_START1,2</sub> exceeds V<sub>Soft\_Start1,2\_LOFF</sub> (P\_6.4.60)

- Until  $V_{\text{FBH1,2-FBL1,2}}$  exceeds  $V_{\text{(FBH1,2-FBL1,2)\_VALID}}$  (P\_6.6.1)

### **Regulator Description**

Figure 8 Soft Start timing diagram on a short to ground detected by the VFBx pin

### 6.3 Switching Frequency setup

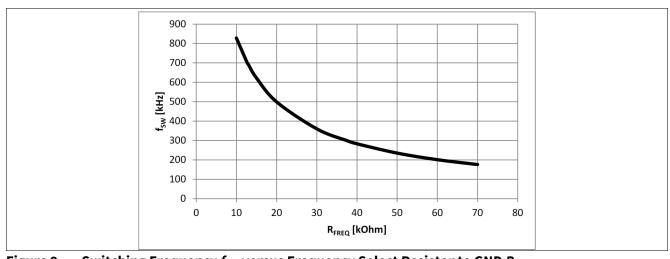

The switching frequency can be set from 200 kHz to 700 kHz by an external resistor connected from the FREQ pin to GND or by supplying a sync signal as specified in chapter **Chapter 11.2**. Select the switching frequency with an external resistor according to the graph in **Figure 9** or the following approximate formulas.

$$f_{SW}[kHz] = 5375 * (R_{FREO}[k\Omega])^{-0.8}$$

(6.2)

$$R_{FREO}[k\Omega] = 46023 * (f_{SW}[kHz])^{-1.25}$$

(6.3)

Figure 9 Switching Frequency  $f_{\rm SW}$  versus Frequency Select Resistor to GND  $R_{\rm FREQ}$

### **Regulator Description**

#### 6.4 Flexible current sense

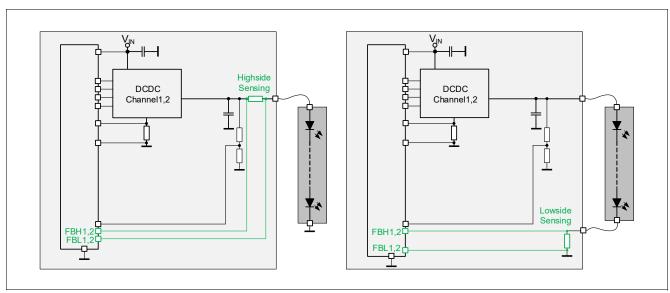

The flexible current sense implementation enables highside and lowside current sensing.

The Figure 10 displays the application examples for the highside and lowside current sense concept.

Figure 10 Highside and lowside current sensing - TLD5501-2QV

### **Regulator Description**

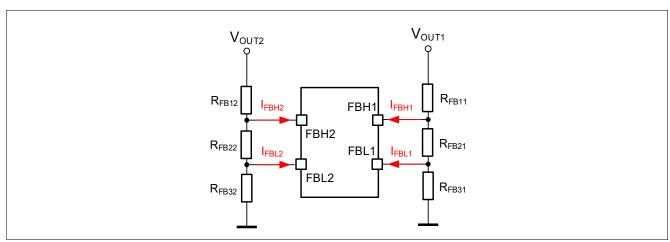

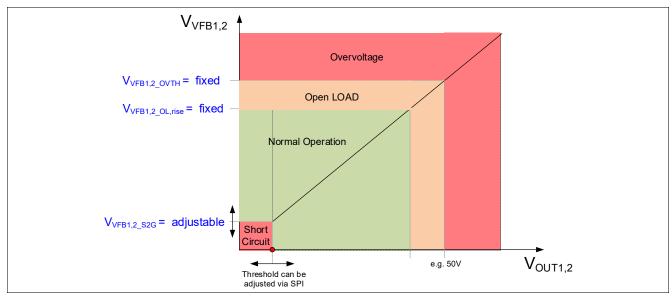

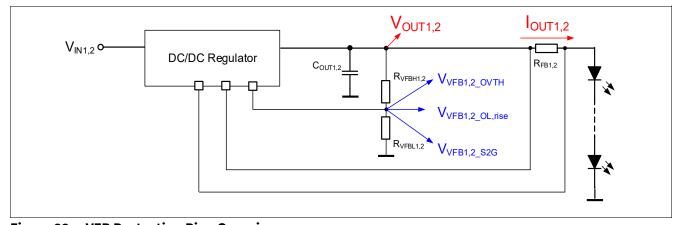

### 6.5 Programming Output Voltage (Constant Voltage Regulation)

For a voltage regulator, the output voltage can be set by selecting the values  $R_{FBx1}$ ,  $R_{FBx2}$  and  $R_{FBx3}$  according to the following **Equation (6.4)**:

$$V_{OUT1,2} = \left(I_{FBH1,2} + \frac{V_{FBH1,2-FBI1,2}}{R_{FB21,2}}\right) \cdot R_{FB11,2} + \left(\frac{V_{FBH1,2-FBI1,2}}{R_{FB21,2}} - I_{FBI1,2}\right) \cdot R_{FB31,2} + V_{FBH1,2-FBI1,2}$$

$$(6.4)$$

After the output voltage is fixed via the resistor divider, the value can be changed via the Analog Dimming bits ADIMVAL CH1, 2.

If Analog dimming is performed, due to the variations on the  $I_{\text{FBL}}$  ( $I_{\text{FBL1},2\_\text{HSS}}$  (P\_6.4.52) and  $I_{\text{FBL1},2\_\text{LSS}}$  (P\_6.4.54)) or  $I_{\text{FBH}}$  ( $I_{\text{FBH1},2\_\text{HSS}}$  (P\_6.4.51) and  $I_{\text{FBH1},2\_\text{LSS}}$  (P\_6.4.53)) current on the entire voltage spanning, a non linearity on the output voltage may be observed. To minimize this effect RFBx resistors should be properly dimensioned.

Figure 11 Programming Output Voltage (Constant Voltage Regulation)

Note:

In case of no load condition, if the voltage on the output is above  $V_{(FBH1,2-FBL1,2)\_VALID}$  threshold, the output capacitor may be discharged during the soft-start sequence. Proper sizing of external components (e.g. increasing the output capacitor or decreasing the inductor values) is recommended to avoid negative output voltage. Alternatively it is recommended to add a clamping diode on the output as shown in **Figure 38**.

### **Dual SYNC Buck Controller with SPI Interface**

### **Regulator Description**

#### **Electrical Characteristics** 6.6

**EC Regulator** Table 7

$V_{IN}$  = 8 V to 36 V,  $T_{J}$  = -40°C to +150°C, all voltages with respect to AGND (unless otherwise specified)

| Parameter                                                    | Symbol                              |       | Values | S     | Unit | Note or                                                                                                              | Number    |

|--------------------------------------------------------------|-------------------------------------|-------|--------|-------|------|----------------------------------------------------------------------------------------------------------------------|-----------|

|                                                              |                                     | Min.  | Тур.   | Max.  |      | Test Condition                                                                                                       |           |

| Regulator:                                                   | ı                                   | 1     |        |       |      |                                                                                                                      | 1         |

| V <sub>(FBH1,2-FBL1,2)</sub> thresholds                      | V <sub>(FBH1,2</sub> -FBL1,2)       | 145.5 | 150    | 154.5 | mV   | ADIM. ADIMVAL_CH $1$ , $2 = 11110000_B$ ; Differential signal (not referred to GND                                   | P_6.4.43  |

| V <sub>(FBH1,2-FBL1,2)</sub> thresholds @ analog dimming 10% | V <sub>(FBH1,2</sub> -FBL1,2)_10    | 12    | 15     | 18    | mV   | ADIM. ADIMVAL_CH $1, 2 = 00011000_B$ ; Differential signal (not referred to GND) Calibration Procedure not performed | P_6.4.47  |

| V(FBH-FBL) valid range<br>threshold                          | V <sub>(FBH1,2</sub> -FBL1,2)_VALID | 110   | 120    | 130   | mV   | $V_{\text{SET}} = 1.4 \text{ V or}$<br>ADIM.ADIMVAL_CH1,2<br>= 11110000 <sub>B</sub>                                 | P_6.6.1   |

| FBH1,2 Bias currents @ highside sensing setup                | I <sub>FBH1,2_HSS</sub>             | 65    | 100    | 156   | μΑ   | $V_{\text{FBL1,2}} = 7 \text{ V};$<br>$V_{\text{FBH1,2-FBL1,2}} = 150 \text{ mV}$                                    | P_6.4.51  |

| FBL1,2 Bias currents @ highside sensing setup                | I <sub>FBL1,2_HSS</sub>             | 17    | 30     | 45    | μΑ   | $V_{\text{FBL1,2}} = 7 \text{ V};$<br>$V_{\text{FBH1,2-FBL1,2}} = 150 \text{ mV}$                                    | P_6.4.52  |

| FBH1,2 Bias currents @ lowside sensing setup                 | I <sub>FBH1,2_LSS</sub>             | -7.5  | -4     | -2.5  | μΑ   | $V_{\text{FBL1,2}} = 0 \text{ V};$<br>$V_{\text{FBH1,2-FBL1,2}} = 150 \text{ mV}$                                    | P_6.4.53  |

| FBL1,2 Bias currents @ lowside sensing setup                 | I <sub>FBL1,2_LSS</sub>             | -45   | -30    | -20   | μΑ   | $V_{\text{FBL1,2}} = 0 \text{ V};$<br>$V_{\text{FBH1,2-FBL1,2}} = 150 \text{ mV}$                                    | P_6.4.54  |

| FBH-FBL High Side sensing entry threshold                    | V <sub>FBH_HSS_inc</sub>            | 1.9   | 2      | 2.1   | V    | <sup>1)</sup> V <sub>FBH1,2</sub> increasing                                                                         | P_6.9.1   |

| FBH-FBL High Side sensing exit threshold                     | V <sub>FBH_HSS_dec</sub>            | 1.65  | 1.75   | 1.85  | V    | <sup>1)</sup> V <sub>FBH1,2</sub> decreasing                                                                         | P_6.9.2   |

| OUT Current sense<br>Amplifier g <sub>m</sub>                | <i>IFBx</i> <sub>gm</sub>           | _     | 890    | -     | μS   | 1)                                                                                                                   | P_6.4.10  |

| Output Monitor Voltages                                      | V <sub>IOUTMON1,2</sub>             | 1.33  | 1.4    | 1.47  | V    | $V_{\text{FBH1,2-FBL1,2}} = 150 \text{ mV}$                                                                          | P_6.5.1   |

| Minimum BUCK Duty Cycle                                      | D <sub>BUCK_MIN</sub>               | -     | 4      | 5.5   | %    | $^{1)}f_{sw} = 300 \text{ kHz}$                                                                                      | P_6.8.2   |

| Maximum BUCK Duty Cycle                                      | D <sub>BUCK_MAX</sub>               | 90.5  | 92     | 94    | %    | $^{1)}f_{sw} = 300 \text{ kHz}$                                                                                      | P_6.5.2   |

| Switch Peak Over Current<br>Thresholds - BUCK                | V <sub>SWCS1,2_buck</sub>           | -60   | -50    | -40   | mV   | 1)                                                                                                                   | P_10.8.25 |

| Soft Start                                                   | •                                   |       | ·      |       |      |                                                                                                                      | •         |

| Soft Start1,2 pull up currents                               | / <sub>Soft_Start1,2_P</sub>        | 21    | 27     | 34    | μΑ   | $V_{\text{Soft\_Start1,2}} = 1 \text{ V}$                                                                            | P_6.4.58  |

### **Dual SYNC Buck Controller with SPI Interface**

### **Regulator Description**

Table 7 EC Regulator (cont'd)

$V_{\rm IN}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to AGND (unless otherwise specified)

| Parameter                                                       | Symbol                                            | Values |      |      | Unit | Note or                                                                                                  | Number   |

|-----------------------------------------------------------------|---------------------------------------------------|--------|------|------|------|----------------------------------------------------------------------------------------------------------|----------|

|                                                                 |                                                   | Min.   | Тур. | Max. |      | Test Condition                                                                                           |          |

| Soft Start1,2 pull down currents                                | / <sub>Soft_Start1,2_P</sub>                      | 2.1    | 2.7  | 3.4  | μΑ   | V <sub>Soft_Start1,2</sub> = 1 V                                                                         | P_6.4.59 |

| Soft Start1,2 Latch-OFF<br>Thresholds                           | V <sub>Soft_Start1,2_</sub>                       | 1.65   | 1.75 | 1.85 | V    | -                                                                                                        | P_6.4.60 |

| Soft Start1,2 Reset<br>Thresholds                               | V <sub>Soft_Start1,2_</sub><br>RESET              | 0.1    | 0.2  | 0.3  | V    | -                                                                                                        | P_6.4.61 |

| Soft Start1,2 Voltage during regulation                         | V <sub>Soft_Start1,2_</sub>                       | 1.9    | 2    | 2.1  | V    | <sup>1)</sup> No Faults                                                                                  | P_6.9.3  |

| Oscillator                                                      |                                                   |        |      |      |      |                                                                                                          |          |

| Switching Frequency                                             | $f_{\sf SW}$                                      | 285    | 300  | 315  | kHz  | $T_{\rm j}$ = 25°C;<br>$R_{\rm FREQ}$ = 37.4 k $\Omega$ ;<br>ENSPREAD = LOW                              | P_6.4.23 |

| SYNC Frequency                                                  | $f_{SYNC}$                                        | 200    | _    | 700  | kHz  | _                                                                                                        | P_6.4.24 |

| SYNC<br>Turn On Threshold                                       | V <sub>SYNC,ON</sub>                              | 2      | _    | -    | V    | -                                                                                                        | P_6.4.25 |

| SYNC<br>Turn Off Threshold                                      | V <sub>SYNC,OFF</sub>                             | _      | _    | 0.8  | V    | -                                                                                                        | P_6.4.26 |

| SYNC<br>High Input Current                                      | I <sub>SYNC,H</sub>                               | 15     | 30   | 45   | μΑ   | $V_{\text{SYNC}} = 2.0 \text{ V};$                                                                       | P_6.4.62 |

| SYNC<br>Low Input Current                                       | I <sub>SYNC,L</sub>                               | 6      | 12   | 18   | μΑ   | $V_{\text{SYNC}} = 0.8 \text{ V};$                                                                       | P_6.4.63 |

| Gate Driver for external Sv                                     | vitch                                             |        |      |      |      |                                                                                                          |          |

| Gate Driver undervoltage<br>threshold VBST1,2-<br>VSWN1,2_UVth  | V <sub>BST1,2</sub> -<br>V <sub>SWN1,2_UVth</sub> | 3.4    | -    | 4    | V    | V <sub>BST1,2</sub> - V <sub>SWN1,2</sub><br>decreasing;<br>Differential signal (not<br>referred to GND) | P_6.4.64 |

| HSGD1,2 NMOS driver onstate resistance (Gate Pull Up)           | R <sub>DS(ON_PU)HS</sub>                          | 1.4    | 2.3  | 3.7  | Ω    | $V_{\text{BST1,2}} - V_{\text{SWN1,2}} = 5 \text{ V};$<br>$I_{\text{source}} = 100 \text{ mA}$           | P_6.4.28 |

| HSGD1,2 NMOS driver on-<br>state resistance (Gate Pull<br>Down) | R <sub>DS(ON_PD) HS</sub>                         | 0.6    | 1.2  | 2.2  | Ω    | $V_{\text{BST1,2}} - V_{\text{SWN1,2}} = 5 \text{ V};$<br>$I_{\text{sink}} = 100 \text{ mA}$             | P_6.4.29 |

| LSGD1,2 NMOS driver onstate resistance (Gate Pull Up)           | R <sub>DS(ON_PU)LS</sub>                          | 1.4    | 2.3  | 3.7  | Ω    | $V_{\text{IVCC\_EXT}} = 5 \text{ V};$ $I_{\text{source}} = 100 \text{ mA}$                               | P_6.4.30 |

| LSGD1,2 NMOS driver on-<br>state resistance (Gate Pull<br>Down) | R <sub>DS(ON_PD)LS</sub>                          | 0.4    | 1.2  | 1.8  | Ω    | $V_{\text{IVCC\_EXT}} = 5 \text{ V};$ $I_{\text{sink}} = 100 \text{ mA}$                                 | P_6.4.31 |

### **Dual SYNC Buck Controller with SPI Interface**

### **Regulator Description**

### Table 7 EC Regulator (cont'd)

$V_{\rm IN}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to AGND (unless otherwise specified)

| Parameter                                 | Symbol                   | Values |      |      | Unit | Note or                                                                              | Number   |

|-------------------------------------------|--------------------------|--------|------|------|------|--------------------------------------------------------------------------------------|----------|

|                                           |                          | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                |          |

| HSGD1,2 Gate Driver peak sourcing current | I <sub>HSGD1,2_SRC</sub> | 380    | -    | -    | mA   | $V_{HSGD1,2} - V_{SWN1,2} = 1 V$<br>to 4 V;<br>$V_{BST1,2} - V_{SWN1,2} = 5 V$       | P_6.4.32 |

| HSGD1,2 Gate Driver peak sinking current  | I <sub>HSGD1,2_SNK</sub> | 410    | -    | -    | mA   | 1)<br>$V_{HSGD1,2} - V_{SWN1,2} = 4 V$<br>to 1 V;<br>$V_{BST1,2} - V_{SWN1,2} = 5 V$ | P_6.4.33 |

| LSGD1,2 Gate Driver peak sourcing current | I <sub>LSGD1,2_SRC</sub> | 370    | -    | _    | mA   | 1)<br>V <sub>LSGD1,2</sub> = 1 V to 4 V;<br>V <sub>IVCC_EXT</sub> = 5 V              | P_6.4.34 |

| LSGD1,2 Gate Driver peak sinking current  | I <sub>LSGD1,2_SNK</sub> | 550    | -    | -    | mA   | 1)<br>V <sub>LSGD1,2</sub> = 4 V to 1 V;<br>V <sub>IVCC_EXT</sub> = 5 V              | P_6.4.35 |

| LSGD1,2 OFF to HSGD1,2<br>ON delay        | t <sub>LSOFF</sub> -     | 15     | 30   | 40   | ns   | 1)                                                                                   | P_6.4.36 |

| HSGD1,2 OFF to LSGD1,2<br>ON delay        | t <sub>HSOFF-</sub>      | 35     | 65   | 95   | ns   | 1)                                                                                   | P_6.4.37 |

<sup>1)</sup> Not subject to production test, specified by design

**Digital Dimming Function**

# 7 Digital Dimming Function

PWM dimming is adopted to vary LEDs brightness with greatly reduced chromaticity shift. PWM dimming achieves brightness reduction by varying the duty cycle of a constant current in the LED string.

### 7.1 Description

A PWM signal can be transmitted to the TLD5501-2QV in two manners, as described below.

An HIGH PWM value, communicated in either of the two ways, always overrides a possible LOW from the other with a resulting enable of the gate drivers.

#### **PWM via direct interface**

The PWMI1,2 pin can be fed with a pulse width modulated (PWM) signals, this enables when HIGH and disables when LOW the gate drivers of the main switches.

#### **PWM via SPI**

A pulse width modulated (PWM) signal can be sent via SPI interface by changing the value of the LOOPCTRL\_CH1,2.PWM\_1,2 bit.

LOOPCTRL\_CH1,2.PWM\_1,2=HIGH/LOW respectively enables/disables the gate drivers of the main switches.

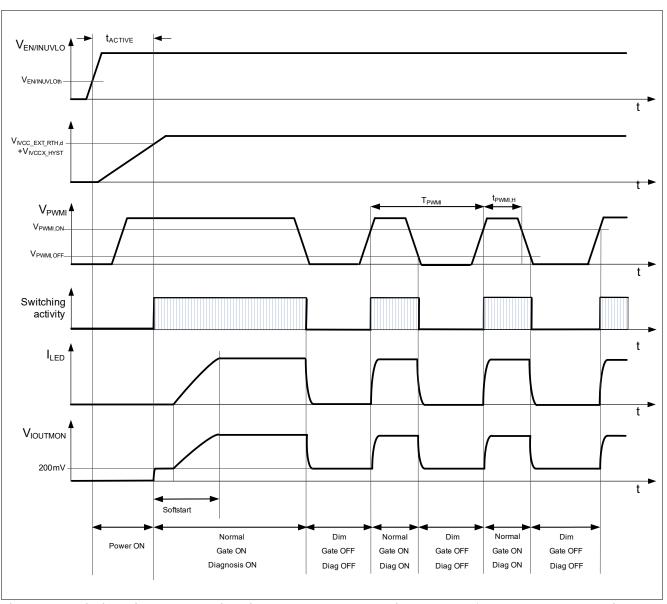

Figure 12 Digital Dimming Overview

To avoid unwanted output overshoots due to not soft start assisted startups, PWM dimming in LOW state should not be used to suspend the output current for long time intervals. To stop a single channel in a safe manner see **Chapter 8**. To stop both channels DVCCTRL.IDLE=HIGH or EN/INUVLO=LOW can be used.

### **Digital Dimming Function**

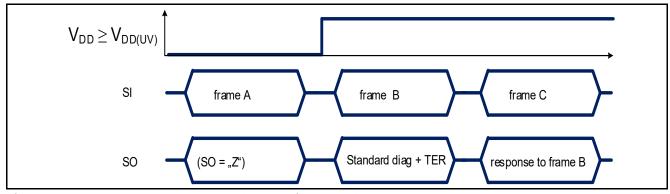

Timing Diagram LED Dimming and Start up behavior example (  $V_{

m VDD}$  and  $V_{

m VIN}$  stable in the Figure 13 functional range and not during startup)

#### **Dual SYNC Buck Controller with SPI Interface**

**Digital Dimming Function**

### 7.2 Electrical Characteristics

# Table 8 EC Digital Dimming

$V_{\rm IN}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to AGND; (unless otherwise specified)

| Parameter                      | Symbol                   | Values |      |      | Unit | Note or Test Condition       | Number   |

|--------------------------------|--------------------------|--------|------|------|------|------------------------------|----------|

|                                |                          | Min.   | Тур. | Max. |      |                              |          |

| PWMI Input:                    |                          |        |      |      |      |                              |          |

| PWMI1,2<br>Turn On Thresholds  | V <sub>PWMI1,2,ON</sub>  | 2      | -    | -    | V    | -                            | P_7.2.6  |

| PWMI1,2<br>Turn Off Thresholds | V <sub>PWMI1,2,OFF</sub> | -      | -    | 0.8  | V    | -                            | P_7.2.7  |

| PWMI1,2<br>High Input Currents | I <sub>PWMI1,2,H</sub>   | 15     | 30   | 45   | μΑ   | V <sub>PWMI1,2</sub> = 2.0 V | P_7.2.9  |

| PWMI1,2<br>Low Input Currents  | I <sub>PWMI1,2,L</sub>   | 6      | 12   | 18   | μΑ   | V <sub>PWMI1,2</sub> = 0.8 V | P_7.2.10 |

**Analog Dimming**

# 8 Analog Dimming

The analog dimming feature allows further control of the output current. This approach is used to:

- Reduce the default current in a narrow range to adjust to different binning classes of the used LEDs.

- Adjust the load current to enable the usage of one hardware for several LED types where different current levels are required.

- Reduce the current at high temperatures (protect LEDs from overtemperature).

### 8.1 Description

The analog dimming feature is adjusting the average load current level via the control of the feedback error Amplifier voltage ( $V_{FBH1,2-FBL1,2}$ ).

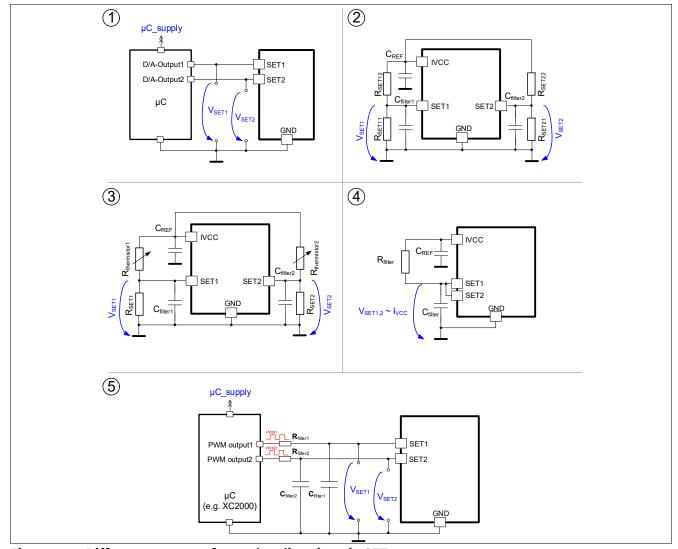

The LEDCURRCAL\_CH1, 2.DAC\_OFF\_CH1, 2 bit-field is used to switch the error amplifier reference from the internal DAC circuitry to the SET1,2 pin during the active state (refer to **Figure 7**). This provides customers higher dimming resolution via the  $\mu$ C and the SET1,2 pin (refer to picture 1 displayed in **Figure 17**).

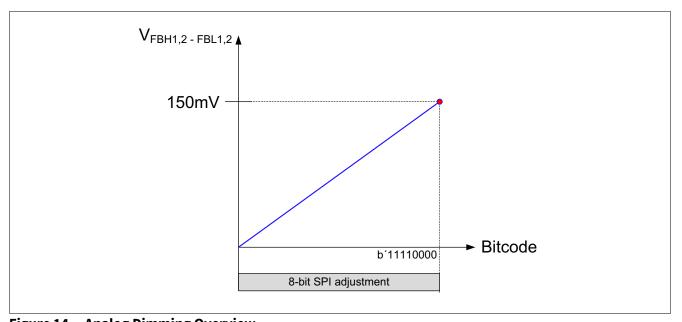

When LEDCURRCAL\_CH1, 2.DAC\_OFF\_CH1, 2 = LOW, the current adjustment is done via a 8BIT SPI parameter (LEDCURRADIM\_CH1, 2.ADIMVAL\_CH1, 2). Refer to Figure 14.

If LEDCURRADIM\_CH1, 2. ADIMVAL\_CH1, 2 is set to  $00000000_B$  the channel stops the switching activity and will restart with a soft start routine as soon as a different value is programmed.

Figure 14 Analog Dimming Overview

#### **Analog dimming adjustment during Limp Home state:**

To enter in Limp Home state the LHI pin must be HIGH.

Note: If the PWMI1,2 and the EN/INUVLO are not set to HIGH, it is not possible to enable switching during Limp Home state.

In Limp Home state the analog dimming control is done via the SET1,2 pins. A Resistor divider between IVCC/IVCC\_EXT, SET1,2 and GND is used to fix a default load current/voltage value (refer to **Figure 15** below).

### **Analog Dimming**

Figure 15 Limp Home state schematic overview

#### Using the SET1,2 pins to adjust the output currents:

For the calculation of the output current I<sub>OUT</sub> the following **Equation (8.1)** is used:

$$I_{OUT 1,2} = \frac{V_{FBH 1,2} - V_{FBL 1,2}}{R_{FB1,2}}$$

(8.1)

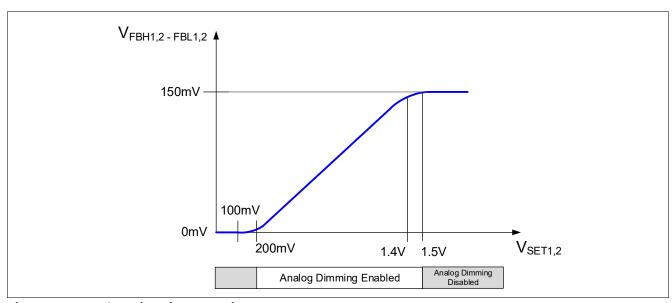

A decrease of the average output current can be achieved by controlling the voltage at the SET1,2 pin  $(V_{SET1,2})$  between 0.2 V and 1.4 V. The mathematical relation is given in the **Equation (8.2)** below:

$$I_{OUT 1,2} = \frac{V_{SET 1,2} - 200 \, mV}{R_{FB1,2} \cdot 8} \tag{8.2}$$

If  $V_{SET1,2}$  is 200 mV (typ.) the LED current is only determined by the internal offset voltages of the comparators. To assure the switching activity is stopped and  $I_{OUT} = 0$ ,  $V_{SET1,2}$  has to be < 100 mV, see **Figure 16**.

The channel is then ready to restart with the soft start routine when VSET1,2 is pulled above 200 mV.

### **Analog Dimming**

Figure 16 Analog Dimming Overview

Figure 17 Different use cases for analog dimming pin SET1,2

#### **Dual SYNC Buck Controller with SPI Interface**

#### **Analog Dimming**

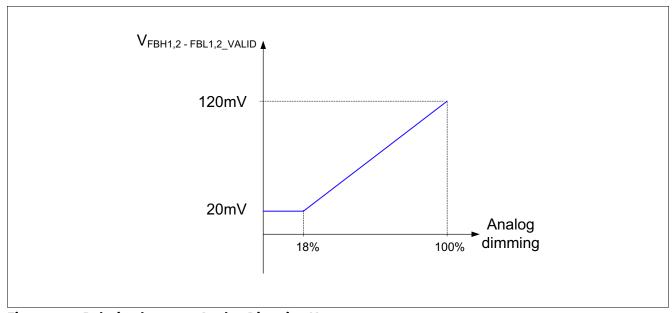

The relation between the analog dimming and the  $V_{(FBH1,2-FBL1,2)\_VALID}$  threshold is shown in **Figure 18**.

When SET1,2 pin is used to set the analog dimming, the  $V_{(FBH1,2-FBL1,2)\_VALID}$  threshold is a direct partition of the SET voltage.

Thus, in case the voltage on SET pin is above 100% of analog dimming the  $V_{(\text{FBH1},2\text{-}\text{FBL1},2)\_\text{VALID}}$  threshold could not be exceeded by the regulated voltage  $V_{(\text{FBH1},2\text{-}\text{FBL1},2)}$  with the following implications:

- The forced CCM mode is applied only once the  $V_{\mathsf{SOFT\_START1,2}}$  exceeds the  $V_{\mathsf{SOFT\_START1,2\_LOFF}}$

- During rising edge of the soft start the internal PWM is extended always until the  $V_{\text{SOFT\_START1,2}}$  exceeds the  $V_{\text{SOFT\_START1,2}}$  LOFF

Figure 18 Relation between Analog Dimming V<sub>(FBH1,2-FBL1,2) VALID</sub>

### 8.2 LED current calibration procedure

The LED current calibration procedure improves the accuracy during analog dimming. In order to be most effective, this routine has to be performed in the application, when the TLD5501-2QV temperature and the output voltage are the ones in which the driver has to be accurate. The output current must be 0 during the procedure run. The optimum should be to re-calibrate the output periodically every time the application has PWMI1,2=LOW for a sufficent long time .

Current calibration procedure:

- Power the Load with a low analog dimming value (for example 10%)

- Set PWMI1,2 = LOW and disconnect the Load at the same time (to avoid Vout drifts from operating conditions and bring the output current to 0)

- Quickly (to avoid Vout drifts)  $\mu$ C enables the calibration routine: LOOPCTRL\_CH1, 2 . ENCAL\_CH1, 2 = HIGH

- Quickly (to avoid Vout drifts) μC starts the calibration: LEDCURRCAL\_CH1, 2.SOCAL\_CH1, 2 = HIGH

- Waiting time (needed to internally perform the calibration routine) → aprox. 200 μs

- TLD5501-2QV will set the FLAG: LEDCURRCAL\_CH1, 2. EOCAL\_CH1, 2 = HIGH, when calibration routine

has finished

- · Reconnect the load

- The Output current is automatically adjusted to a low offset and more accurate analog dimming value

### **Dual SYNC Buck Controller with SPI Interface**

### **Analog Dimming**

Once the Calibration routine is correctly performed, the output current accuracy with analog dimming = 10% (LEDCURRADIM CH1, 2.ADIMVAL CH1, 2 = 24) is 10%.

The Calibration routine is not affecting the accuracy at 100% analog dimming.

The ENCAL\_CH1,2 Bits affect both device operation and CALIBVAL\_CH1,2 reading result:

- ENCAL\_CH1,2 = HIGH: the calibration result coming from the routine is used by internal circuitry and can be read back from CALIBVAL\_CH1,2

- ENCAL\_CH1,2 = LOW: SPI value written in CALIBVAL\_CH1,2 is used by internal circuitry and can be read back; calibration routine start is inhibited

As a result,  $\mu$ C can use a stored result from a previously performed calibration to directly impose the desired value without waiting for a new routine to finish.

#### 8.3 Electrical Characteristics

### Table 9 EC Analog Dimming

$V_{\rm IN}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to AGND; (unless otherwise specified)

| Parameter                     | Symbol                     | Values |      |      | Unit | Note or                                       | Number  |

|-------------------------------|----------------------------|--------|------|------|------|-----------------------------------------------|---------|

|                               |                            | Min.   | Тур. | Max. |      | Test Condition                                |         |

| Source currents on SET1,2 Pin | I <sub>SET1,2_source</sub> | _      | _    | 1    | μΑ   | $^{1)}V_{SET1,2} = 0.2 \text{ V to}$<br>1.4 V | P_8.3.5 |

<sup>1)</sup> Specified by design: not subject to production test

**Linear Regulator**

# 9 Linear Regulator

The TLD5501-2QV features an integrated voltage regulator for the supply of the internal gate driver stages. Furthermore an external voltage regulator can be connected to the IVCC\_EXT pin to achieve an alternative gate driver supply if required.

### 9.1 IVCC Description