#### 5V Low drop voltage post regulator

#### **Features**

- Output voltage tolerance ≤ ±2%

- 400 mA output current capability

- Low drop voltage

- Very low standby current consumption

- Input voltage up to 40 V

- Overvoltage protection up to 60 V (≤ 400 ms)

- · Reset function down to 1 V output voltage

- Adjustable reset time

- On/off logic

- Overtemperature protection

- Reverse polarity protection

- · Short-circuit proof

- Wide temperature range

- Suitable for use in automotive electronics

- Green Product (RoHS compliant)

### **Potential applications**

General automotive applications.

#### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

### **Description**

The TLE4267-2G is a low drop voltage regulator with a 5 V output voltage for automotive applications in a PG-TO220-7 package. It supplies an output current up to 400 mA. The device is short circuit-proof and has an overtemperature protection circuit. The device also has a reset output with a reset delay that can be set by an external capacitor. The two logic inputs, inhibit and hold, allow for implementation of a self-holding circuit without external components. When the device is turned off, the output voltage drops to 0 V and current consumption tends towards  $0\,\mu\text{A}$ .

| Туре       | Package    | Marking |

|------------|------------|---------|

| TLE4267-2G | PG-TO220-7 | 4267-2G |

### OPTIREG™ linear TLE4267-2G 5V Low drop voltage post regulator

### **Table of Contents**

| 1          | Block diagram                                          | 3  |

|------------|--------------------------------------------------------|----|

| 2          | Pin configuration                                      |    |

| 2.1<br>2.2 | Pin assignment                                         |    |

| 3          | General product characteristics                        | 5  |

| 3.1        | Absolute maximum ratings                               | 5  |

| 3.2        | Functional range                                       |    |

| 3.3        | Thermal resistance                                     | 6  |

| 4          | Block description and electrical characteristics       | 7  |

| 4.1        | Voltage regulation                                     | 7  |

| 4.1.1      | Electrical characteristics voltage regulation          | 7  |

| 4.1.2      | Typical performance characteristics voltage regulation |    |

| 4.2        | Reset function                                         |    |

| 4.2.1      | Electrical characteristics reset function              | 10 |

| 4.2.2      | Typical performance characteristics reset function     |    |

| 4.3        | Inhibit and hold functionality                         |    |

| 4.3.1      | Electrical characteristics inhibit and hold function   |    |

| 4.3.2      | Typical performance characteristics inhibit            | 14 |

| 5          | Application information                                | 15 |

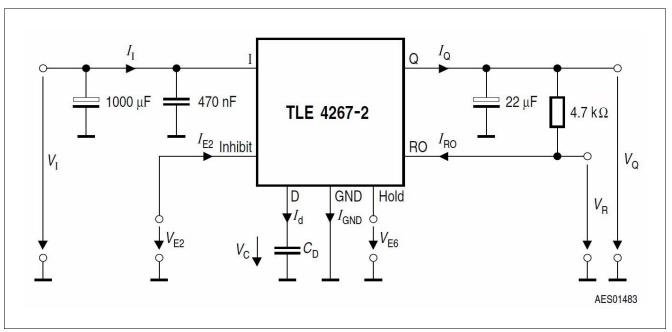

| 5.1        | Application diagram                                    | 15 |

| 5.2        | Selection of external components                       | 15 |

| 5.3        | Further application information                        | 16 |

| 6          | Package information                                    | 17 |

| 7          | Revision history                                       | 18 |

2

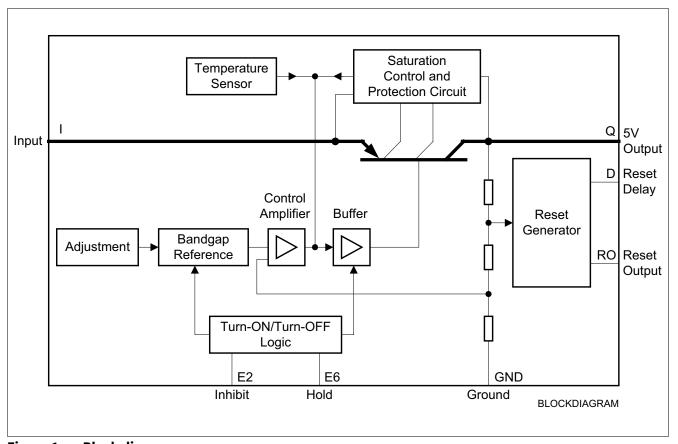

**Block diagram**

### 1 Block diagram

Figure 1 Block diagram

Pin configuration

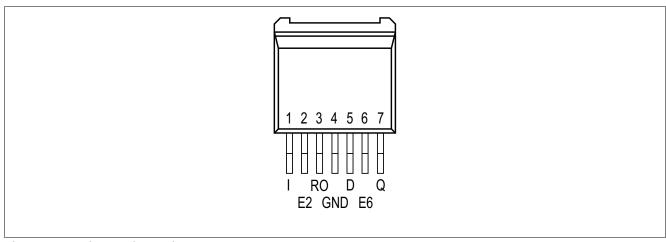

## 2 Pin configuration

#### 2.1 Pin assignment

Figure 2 Pin configuration

#### 2.2 Pin definitions and functions

Table 1 Pin definition and function

| Pin | Symbol | Function                                                                                                                                                           |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | I      | <b>Input;</b> it is recommended to place small ceramic capacitor close to the pin to GND in order to compensate line influences                                    |

| 2   | E2     | Inhibit; device is enabled by a high signal on this pin; internal pull-down resistor of 100 $k\Omega$                                                              |

| 3   | RO     | Reset output; open-collector output internally connected to the output via a resistor of 30 k $\Omega$                                                             |

| 4   | GND    | Ground; connected to exposed paddle                                                                                                                                |

| 5   | D      | Reset delay; connect via capacitor to GND                                                                                                                          |

| 6   | E6     | <b>Hold;</b> see <b>Table 8</b> for function; this input is connected to output voltage via a pull-up resistor of 50 k $\Omega$                                    |

| 7   | Q      | <b>Output voltage;</b> connect output capacitor $C_{\rm Q}$ to GND close to the pin, respecting the values specified for its capacitance and ESR in <b>Table 3</b> |

**General product characteristics**

### **3** General product characteristics

#### 3.1 Absolute maximum ratings

Table 2 Absolute maximum ratings 1)

$T_i = -40$ °C to +150°C; all voltages with respect to ground (unless otherwise specified)

| Parameter                       | Symbol               |      | Value | S    | Unit     | Note or                                     | Number   |

|---------------------------------|----------------------|------|-------|------|----------|---------------------------------------------|----------|

|                                 |                      | Min. | Тур.  | Max. |          | <b>Test Condition</b>                       |          |

| Input I                         |                      |      | - 11  | 1    | "        |                                             |          |

| Voltage                         | $V_{I}$              | -42  | _     | 42   | V        | -                                           | P_3.1.1  |

| Voltage                         | V <sub>I</sub>       | _    | _     | 60   | V        | <i>t</i> ≤ 400 ms                           | P_3.1.2  |

| Reset output RO                 | 1                    |      | 1     |      |          |                                             |          |

| Voltage                         | $V_{RO}$             | -0.3 | _     | 7    | V        | _                                           | P_3.1.3  |

| Reset delay                     |                      |      | - 11  | 1    | "        |                                             |          |

| Voltage                         | $V_{D}$              | -0.3 | -     | 42   | V        | _                                           | P_3.1.4  |

| Output O                        | 1                    |      | 1     |      |          |                                             |          |

| Voltage                         | $V_{Q}$              | -0.3 | -     | 7    | ٧        | _                                           | P_3.1.5  |

| Inhibit                         | <u> </u>             |      | 1     |      |          |                                             |          |

| Voltage                         | $V_{\rm E2}$         | -42  | _     | 42   | V        | _                                           | P_3.1.6  |

| Current                         | I <sub>E2</sub>      | -5   | _     | 5    | mA       | <i>t</i> ≤ 400 ms                           | P_3.1.7  |

| Hold E6                         |                      | *    | *     | •    | -        |                                             | <u>'</u> |

| Voltage                         | $V_{\rm E6}$         | -0.3 | _     | 7    | V        | -                                           | P_3.1.8  |

| GND                             | 1                    |      | 1     |      |          |                                             |          |

| Current                         | I <sub>GND</sub>     | -0.5 | -     | _    | Α        | -                                           | P_3.1.9  |

| Temperatures                    |                      |      | •     |      |          |                                             |          |

| Junction temperature            | $T_{\rm j}$          | -40  | _     | 150  | °C       | -                                           | P_3.1.10 |

| Storage temperature             | $T_{\rm stg}$        | -50  | _     | 150  | °C       | -                                           | P_3.1.11 |

| ESD susceptibility              |                      |      | - 11  | 1    | <b>"</b> |                                             |          |

| ESD robustness to GND           | $V_{\rm ESD,HBM}$    | -2   | -     | 2    | kV       | HBM <sup>2)</sup>                           | P_3.1.12 |

| ESD robustness to GND           | V <sub>ESD,CDM</sub> | -500 | -     | 500  | V        | CDM <sup>3)</sup> ;<br>all pins except 1, 7 | P_3.1.13 |

| ESD robustness pins 1, 7 to GND | $V_{\rm ESD,CDM}$    | -750 | _     | 750  | V        | CDM <sup>4)</sup>                           | P_3.1.14 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Human body model (HBM) robustness according to AEC-Q100-002.

<sup>3)</sup> Charge device model (CDM) robustness according to AEC-Q100-011, Rev-D; voltage level refers to test conditions (TC) mentioned in the standard.

<sup>4)</sup> Charge Device model (CDM) robustness according to AEC-Q100-011, Rev-D; voltage level refers to test conditions (TC) mentioned in the standard.

#### 5V Low drop voltage post regulator

#### **General product characteristics**

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent device destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### 3.2 Functional range

Table 3 Functional range

| Parameter                                        | Symbol      | Values |      | Unit | Note or | Number                |         |

|--------------------------------------------------|-------------|--------|------|------|---------|-----------------------|---------|

|                                                  |             | Min.   | Тур. | Max. |         | <b>Test Condition</b> |         |

| Input voltage range                              | $V_{I}$     | 5.5    | -    | 40   | V       | see diagram           | P_3.2.1 |

| Capacitance of output capacitor for stability    | $C_{Q}$     | 22     | _    | _    | μF      | 1)2)                  | P_3.2.2 |

| Equivalent series resistance of output capacitor | $ESR(C_Q)$  | -      | -    | 3    | Ω       | 1)                    | P_3.2.3 |

| Junction temperature                             | $T_{\rm j}$ | -40    | _    | 150  | °C      | -                     | P_3.2.4 |

<sup>1)</sup> Not subject to production test, specified by design

Note:

Within the functional or operating range, the device operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the electrical characteristics table.

#### 3.3 Thermal resistance

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to **www.jedec.org**.

Table 4 Thermal resistance

| Parameter          | Symbol     |      | Value | s    | Unit | Note or<br>Test Condition | Number  |

|--------------------|------------|------|-------|------|------|---------------------------|---------|

|                    |            | Min. | Тур.  | Max. |      |                           |         |

| Thermal resistance | ,          |      | -     | -    |      | <u>'</u>                  |         |

| Junction ambient   | $R_{thJA}$ | -    | _     | 65   | K/W  | 1)                        | P_3.3.1 |

| Junction-case      | $R_{thJC}$ | _    | -     | 6    | K/W  | 1)                        | P_3.3.2 |

| Junction-case      | $Z_{thJC}$ | -    | _     | 2    | K/W  | <sup>1)</sup> T < 1 ms    | P_3.3.3 |

<sup>1)</sup> Not subject to production test, specified by design

<sup>2)</sup> The minimum output capacitance requirement is applicable for a worst case capacitance tolerance of 30%

**Block description and electrical characteristics**

#### 4 Block description and electrical characteristics

#### 4.1 Voltage regulation

The TLE4267-2G regulates an input voltage  $V_1$  in the range of 5.5 V up to 40 V to a nominal output of  $V_Q$  = 5 V. The internal control amplifier compares a reference voltage to a voltage that is proportional to the output voltage and drives the base of the pass transistor accordingly via a buffer.

The accuracy of the internal reference is optimized by resistance adjustment internally. Saturation control as a function of the load current prevents an over-saturating of the power element.

#### 4.1.1 Electrical characteristics voltage regulation

Table 5 Electrical characteristics voltage regulation

$V_{\rm I}$  = 13.5 V; -40 °C <  $T_{\rm i}$  < 125 °C;  $V_{\rm E2}$  > 4 V (unless specified otherwise)

| Parameter                             | Symbol                 |      | Value | s    | Unit | Note or Test Condition                                                               | Number   |

|---------------------------------------|------------------------|------|-------|------|------|--------------------------------------------------------------------------------------|----------|

|                                       |                        | Min. | Тур.  | Max. |      |                                                                                      |          |

| Output voltage                        | $V_{Q}$                | 4.9  | 5     | 5.1  | V    | $5 \text{ mA} \le I_Q \le 400 \text{ mA};$<br>$6 \text{ V} \le V_1 \le 26 \text{ V}$ | P_4.2.1  |

| Output voltage                        | $V_{Q}$                | 4.9  | 5     | 5.1  | V    | $5 \text{ mA} \le I_Q \le 150 \text{ mA};$<br>$6 \text{ V} \le V_I \le 40 \text{ V}$ | P_4.2.2  |

| Output current limiting               | $I_{Q}$                | 500  | -     | _    | mA   | T <sub>j</sub> = 25 °C                                                               | P_4.2.3  |

| Current consumption $I_q = I_1 - I_Q$ | I <sub>q</sub>         | _    | _     | 50   | μΑ   | Device turned off                                                                    | P_4.2.4  |

| Current consumption $I_q = I_1 - I_Q$ | I <sub>q</sub>         | _    | 1.0   | 10   | μΑ   | $T_{\rm j}$ = 25 °C;<br>device turned off                                            | P_4.2.5  |

| Current consumption $I_q = I_1 - I_Q$ | I <sub>q</sub>         | _    | 1.3   | 4    | mA   | $I_Q = 5 \text{ mA};$<br>device turned on                                            | P_4.2.6  |

| Current consumption $I_q = I_1 - I_Q$ | I <sub>q</sub>         | -    | _     | 60   | mA   | I <sub>Q</sub> = 400 mA                                                              | P_4.2.7  |

| Current consumption $I_q = I_1 - I_Q$ | I <sub>q</sub>         | -    | _     | 80   | mA   | $I_{\rm Q} = 400 \text{ mA}$<br>$V_{\rm I} = 5 \text{ V}$                            | P_4.2.8  |

| Drop voltage                          | $V_{Dr}$               | _    | 0.3   | 0.6  | ٧    | $I_{\rm Q} = 400  {\rm mA}^{1)}$                                                     | P_4.2.9  |

| Load regulation                       | $\Delta V_{ m Q}$      | _    | -     | 50   | mV   | 5 mA ≤ I <sub>Q</sub> ≤ 400 mA                                                       | P_4.2.10 |

| Line regulation                       | $\Delta V_{ m Q}$      | _    | 15    | 25   | mV   | $V_1 = 6 \text{ V to } 36 \text{ V};$<br>$I_Q = 5 \text{ mA}$                        | P_4.2.11 |

| Power supply ripple rejection         | PSSR                   | _    | 54    | _    | dB   | $f_{\rm r} = 100 \text{ Hz}; V_{\rm r} = 0.5 V_{\rm pp}$                             | P_4.2.12 |

| Longterm stability                    | $\Delta V_{ m Q}$      | _    | 0     | -    | mV   | 1000 h                                                                               | P_4.2.13 |

| Overvoltage protection                |                        | '    | •     | •    |      |                                                                                      | •        |

| Turn-off voltage                      | $V_{\rm I,OV}$         | 42   | 44    | 46   | V    | V <sub>I</sub> increasing                                                            | P_4.2.14 |

| Turn-on voltage                       | V <sub>I,turn on</sub> | 36   | _     | _    | V    | V <sub>I</sub> decreasing after turn-off                                             | P_4.2.15 |

|                                       |                        |      | _     |      |      |                                                                                      |          |

<sup>1)</sup> Drop voltage =  $V_1$  -  $V_Q$  (measured when the output voltage  $V_Q$  has dropped 100 mV from the nominal value obtained at  $V_1$  = 13.5 V)

**Block description and electrical characteristics**

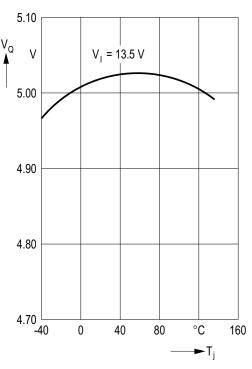

#### 4.1.2 Typical performance characteristics voltage regulation

# Output voltage $V_{\rm Q}$ versus temperature $T_{\rm j}$

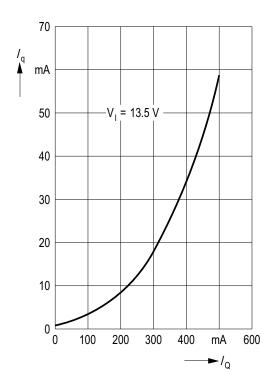

# Current consumption $I_q$ versus output current $I_Q$

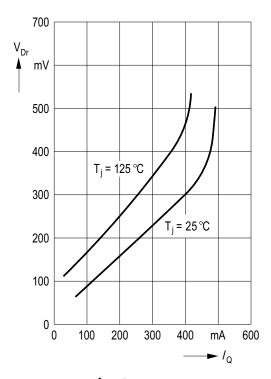

# Dropout voltage $V_{\rm DR}$ versus output current $I_{\rm O}$

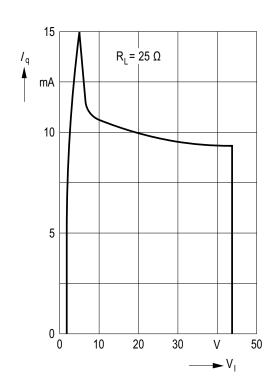

# Current consumption $I_q$ versus input voltage $V_l$

#### 5V Low drop voltage post regulator

#### **Block description and electrical characteristics**

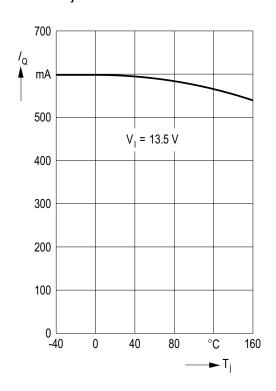

# Output current limiting $I_Q$ versus temperature $T_i$

# Output current limiting $I_Q$ versus input voltage $V_I$

#### 4.2 Reset function

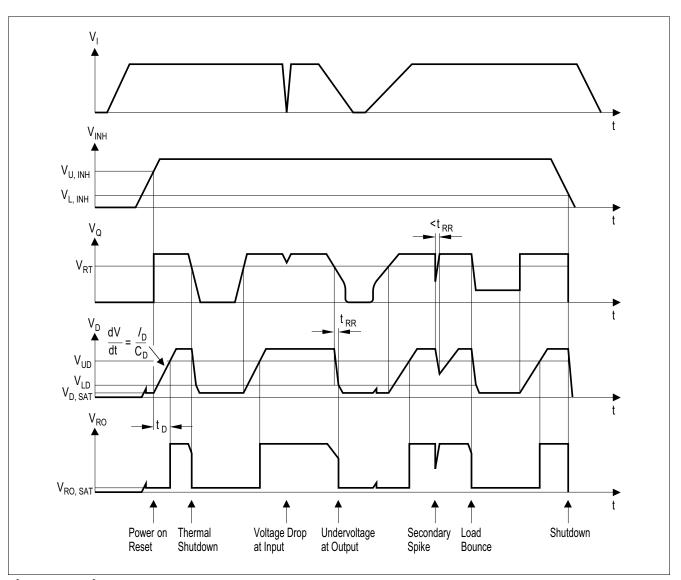

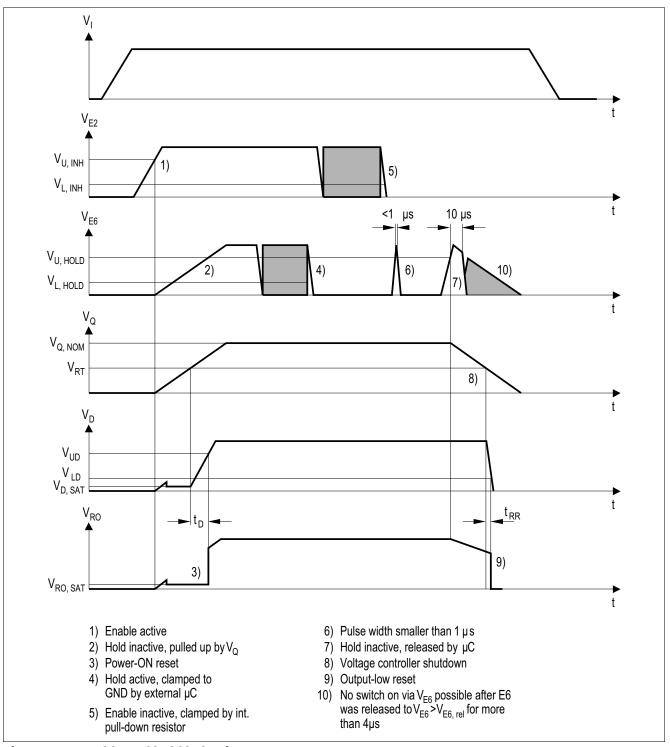

A reset signal is generated for an output voltage of  $V_{\rm Q} < V_{\rm RT}$ . The reset delay can be set with an external capacitor. The reset output  $R_{\rm O}$  is high state if the voltage on the delay capacitor  $C_{\rm D}$  is greater or equal  $V_{\rm UD}$ . The delay capacitance  $C_{\rm D}$  is charged with the current  $I_{\rm D}$  for output voltages greater than the reset threshold  $V_{\rm RT}$ . If the output voltage drops below than  $V_{\rm RT}$  a fast discharge of the delay capacitor  $C_{\rm D}$  sets in. As  $V_{\rm CD}$  drops below  $V_{\rm LD}$  the reset output  $R_{\rm O}$  is set to low (see **Figure 3**). The reset delay can be adjusted by dimensioning the capacitance of the external capacitor  $C_{\rm D}$ .

#### **Block description and electrical characteristics**

Figure 3 **Time response**

#### **Electrical characteristics reset function** 4.2.1

#### Table 6 **Electrical characteristics reset function**

$V_{\rm I}$  = 13.5 V; -40 °C <  $T_{\rm i}$  < 125 °C;  $V_{\rm E2}$  > 4 V (unless specified otherwise)

| Parameter                       | Symbol           | Values |      |      | Unit | Note or Test Condition                  | Number  |

|---------------------------------|------------------|--------|------|------|------|-----------------------------------------|---------|

|                                 |                  | Min.   | Тур. | Max. |      |                                         |         |

| Switching threshold             | $V_{RT}$         | 4.5    | 4.65 | 4.8  | V    | V <sub>Q</sub> decreasing               | P_4.3.1 |

| Reset high level                | _                | 4.5    | _    | _    | V    | R <sub>ext</sub> = ∞                    | P_4.3.2 |

| Saturation voltage              | $V_{\rm RO,SAT}$ | -      | 0.1  | 0.4  | V    | $R_{\rm R} = 4.7 \; {\rm k}\Omega^{1)}$ | P_4.3.3 |

| Internal pull-up resistor       | $R_{RO}$         | -      | 30   | -    | kΩ   | -                                       | P_4.3.4 |

| Saturation voltage              | $V_{D,SAT}$      | _      | 50   | 100  | mV   | $V_{\rm Q} < V_{\rm RT}$                | P_4.3.5 |

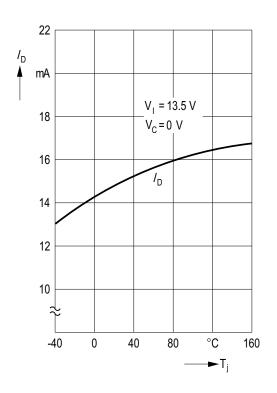

| Charge current                  | I <sub>D</sub>   | 8      | 15   | 25   | μΑ   | V <sub>D</sub> = 1.5 V                  | P_4.3.6 |

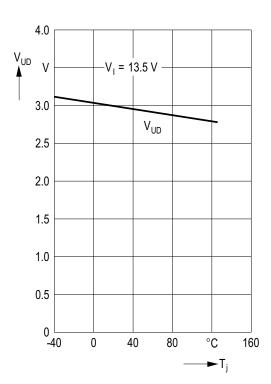

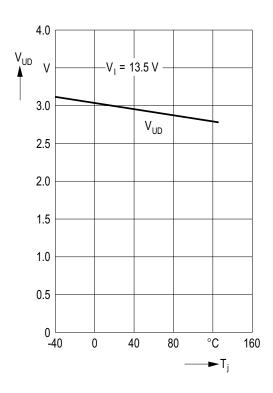

| Upper delay switching threshold | V <sub>UD</sub>  | 2.6    | 3    | 3.3  | V    | -                                       | P_4.3.7 |

#### 5V Low drop voltage post regulator

#### **Block description and electrical characteristics**

#### Table 6 Electrical characteristics (cont'd) reset function

$V_{\rm I}$  = 13.5 V; -40 °C <  $T_{\rm i}$  < 125 °C;  $V_{\rm E2}$  > 4 V (unless specified otherwise)

| Parameter                       | Symbol   | Value | Values |      | <b>Note or Test Condition</b> | Number                    |          |

|---------------------------------|----------|-------|--------|------|-------------------------------|---------------------------|----------|

|                                 |          | Min.  | Тур.   | Max. |                               |                           |          |

| Delay time                      | $t_{D}$  | _     | 20     | -    | ms                            | $C_{\rm D} = 100  \rm nF$ | P_4.3.8  |

| Lower delay switching threshold | $V_{LD}$ | -     | 0.43   | -    | V                             | -                         | P_4.3.9  |

| Reset reaction time             | $t_{RR}$ | _     | 2      | -    | μs                            | $C_{\rm D} = 100  \rm nF$ | P_4.3.10 |

<sup>1)</sup> The reset output is Low for  $1 \text{ V} < V_0 < V_{RT}$

#### 4.2.2 Typical performance characteristics reset function

# Charge current $I_D$ versus temperature $T_i$

# Delay switching threshold $V_{\rm UD}$ versus temperature $T_{\rm i}$

#### 5V Low drop voltage post regulator

#### **Block description and electrical characteristics**

#### 4.3 Inhibit and hold functionality

The device has two logic inputs, E2 and E6. A voltage of  $V_{\rm E2}$  greater than 4.0 V applied to E2 pin (Inhibit) during for example ignition, turns the device on.

Depending on the voltage on pin E6 (Hold) the device can stay in active state even if  $V_{\rm E2}$  goes to low level. This makes it simple to implement a self-holding circuit without external components. **Table 7** shows the truth table for the turn-on turn-off logic controlled by the inputs voltages on E2 (Inhibit) and E6 (Hold).

Table 7 Truth table for Turn-ON/Turn-OFF logic

| E2,<br>Inhibit 1) | E6,<br>Hold <sup>2)</sup> | $V_{Q}$ | Remarks                                                                                                                                                                                  |

|-------------------|---------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L                 | Х                         | OFF     | Initial state                                                                                                                                                                            |

| Н                 | Х                         | ON      | Regulator switched on via Inhibit, by ignition for example                                                                                                                               |

| Н                 | L                         | ON      | Hold clamped active to ground by controller while Inhibit is still high                                                                                                                  |

| X                 | L                         | ON      | Previous state remains, even ignition is shut off: self-holding state                                                                                                                    |

| L                 | L                         | ON      | Ignition shut off while regulator is in self-holding state                                                                                                                               |

| L                 | Н                         | OFF     | Regulator shut down by releasing of Hold while Inhibit remains Low, final state. No active clamping required by external self-holding circuit ( $\mu$ C) to keep regulator in off-state. |

<sup>1)</sup> E2, Inhibit: enable function, active high

<sup>2)</sup> E6, Hold: hold and release function, active low

#### **Block description and electrical characteristics**

Figure 4 Enable and hold behavior

**Block description and electrical characteristics**

#### 4.3.1 Electrical characteristics inhibit and hold function

Table 8

Electrical characteristics inhibit and hold function

$V_{\rm I}$  = 13.5 V; -40 °C <  $T_{\rm i}$  < 125 °C;  $V_{\rm E2}$  > 4 V (unless specified otherwise)

| Parameter          | Symbol            | Values |      |      | Unit | Note or Test Condition | Number  |

|--------------------|-------------------|--------|------|------|------|------------------------|---------|

|                    |                   | Min.   | Тур. | Max. |      |                        |         |

| Turn-on voltage    | $V_{\rm U,INH}$   | -      | 3    | 4    | V    | Device turned on       | P_4.4.1 |

| Turn-off voltage   | $V_{L,INH}$       | 2      | _    | _    | V    | Device turned off      | P_4.4.2 |

| Pull-down resistor | R <sub>INH</sub>  | 50     | 100  | 200  | kΩ   | -                      | P_4.4.3 |

| Hysteresis         | $\Delta V_{INH}$  | 0.2    | 0.5  | 0.8  | V    | -                      | P_4.4.4 |

| Input current      | I <sub>INH</sub>  | -      | 35   | 100  | μΑ   | V <sub>INH</sub> = 4 V | P_4.4.5 |

| Hold voltage       | $V_{\rm U,HOLD}$  | 30     | 35   | 40   | %    | Referred to $V_{Q}$    | P_4.4.6 |

| Turn-off voltage   | $V_{L,HOLD}$      | 60     | 70   | 80   | %    | Referred to $V_{Q}$    | P_4.4.7 |

| Pull-up resistor   | R <sub>HOLD</sub> | 20     | 50   | 100  | kΩ   | -                      | P_4.4.8 |

#### 4.3.2 Typical performance characteristics inhibit

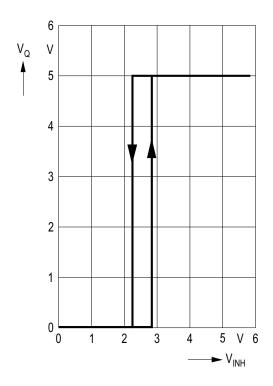

# Output voltage $V_{\rm Q}$ versus inhibit voltage $V_{\rm INH}$

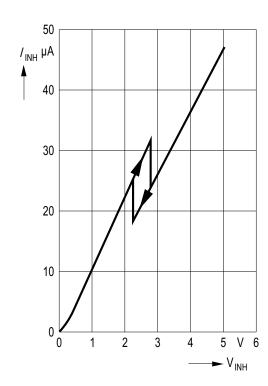

# Inhibit current $I_{\rm INH}$ versus inhibit voltage $V_{\rm INH}$

**Application information**

#### 5 Application information

Note:

The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

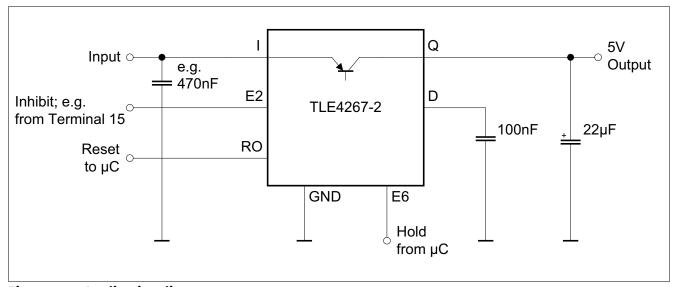

#### 5.1 Application diagram

Figure 5 Application diagram

Note:

This is a very simplified example of a application circuit. The function must be verified in the real application.

#### 5.2 Selection of external components

The input capacitor  $C_1$  is necessary for compensation of line influences. The resonant circuit consisting of lead inductance and input capacitance can be damped by a resistor of approx. 1  $\Omega$  in series with  $C_1$ .

The output capacitor  $C_Q$  is necessary for the stability of the regulating circuit. Stability is guaranteed at values of greater than 22  $\mu$ F and an ESR of less than 3  $\Omega$  within the operating temperature range. An example of a test circuit is shown in **Figure 6**.

#### **Application information**

Figure 6 Test circuit

Note: This is a very simplified example of a test circuit. The function must be verified in the real application.

#### 5.3 Further application information

• For further information you may contact <a href="http://www.infineon.com/">http://www.infineon.com/</a>

# infineon

**Package information**

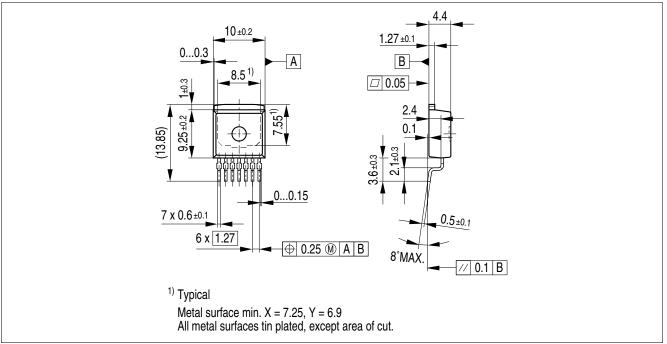

#### 6 Package information

Figure 7 PG-TO220-7<sup>1)</sup> (Plastic Small Outline Transistor)

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (that is Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

#### **Further information on packages**

https://www.infineon.com/packages

#### **5V Low drop voltage post regulator**

**Revision history**

### **7** Revision history

| Revision | Date       | Changes                                                                                   |

|----------|------------|-------------------------------------------------------------------------------------------|

| 1.1      | 2023-06-19 | Updated layout and template.                                                              |

|          |            | Text reformulations and restructuring (editorial)                                         |

|          |            | Moved the ESD rating from features into the absolute max ratings section                  |

|          |            | • Moved $C_Q$ and $C_{Q(ESR)}$ requirements from pin definition table to functional range |

|          |            | Removed reference to discontinued PG-TO263-7 package                                      |

| 1.0      | 2012-04-03 | Initial datasheet for TLE4267-2                                                           |

#### Trademarks

Edition 2023-06-19 Published by Infineon Technologies AG 81726 Munich, Germany

© 2024 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com

Document reference Z8F50779552

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LDO Voltage Regulators category:

Click to view products by Infineon manufacturer:

Other Similar products are found below:

AP7363-SP-13 NCV8664CST33T3G L79M05TL-E AP7362-HA-7 PT7M8202B12TA5EX TCR3DF185,LM(CT TLF4949EJ

NCP4687DH15T1G NCV8703MX30TCG LP2951CN NCV4269CPD50R2G AP7315-25W5-7 NCV47411PAAJR2G AP2111H-1.2TRG1

ZLDO1117QK50TC AZ1117ID-ADJTRG1 NCV4263-2CPD50R2G NCP706ABMX300TAG NCP114BMX075TCG MC33269T-3.5G

TLE4471GXT AP7315-33SA-7 NCV4266-2CST33T3G NCP715SQ15T2G NCV8623MN-50R2G NCV563SQ18T1G NCV8664CDT33RKG

NCV4299CD250R2G NCP715MX30TBG NCV8702MX25TCG TLE7270-2E NCV562SQ25T1G AP2213D-3.3TRG1 AP2202K-2.6TRE1

NCV8170BMX300TCG NCV8152MX300180TCG NCP700CMT45TBG AP7315-33W5-7 NCP154MX180300TAG AP2113AMTR-G1

NJW4104U2-33A-TE1 MP2013AGG-5-P NCV8775CDT50RKG NJM2878F3-45-TE1 S-19214B00A-V5T2U7 S-19214B50A-V5T2U7 S

19213B50A-V5T2U7 S-19214BC0A-E8T1U7\*1 S-19213B00A-V5T2U7 S-19213B33A-V5T2U7