## TLE42994

Low Dropout Fixed Voltage Regulator

TLE42994G TLE42994GM TLE42994E

## **Data Sheet**

Rev. 1.2, 2014-07-03

# **Automotive Power**

#### Low Dropout Fixed Voltage Regulator

#### **TLE42994**

### 1 Overview

#### **Features**

- Output Voltage 5 V ± 2%

- · Ouput Current up to 150 mA

- · Extreme Low Current Consumption In ON State

- Enable Function: Below 1 µA Current Consumption In OFF State

- · Early Warning

- Power-on and Undervoltage Reset with Programmable Delay Time

- Reset Low Down to  $V_{Q}$  = 1 V

- · Adjustable Reset Threshold

- · Very Low Dropout Voltage

- · Output Current Limitation

- · Reverse Polarity Protection

- · Overtemperature Protection

- · Suitable for Use in Automotive Electronics

- Wide Temperature Range from -40 °C up to 150 °C

- Input Voltage Range from -42 V to 45 V

- Green Product (RoHS compliant)

- AEC Qualified

#### **Description**

The TLE42994 is a monolithic integrated low dropout voltage regulator, especially designed for automotive applications that need to be in ON state during the car's engine is turned off. An input voltage up to 45 V is regulated to an output voltage of 5.0 V. The component is able to drive loads up to 150 mA. It is short-circuit protected by the implemented current limitation and has an integrated overtemperature shutdown. A reset signal is generated for an output voltage  $V_{\rm Q,rt}$  of typically 4.65 V. This threshold can be decreased by an external

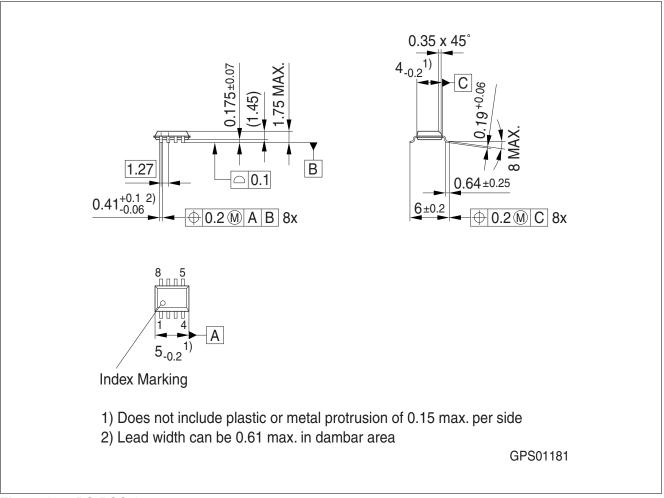

PG-DSO-8

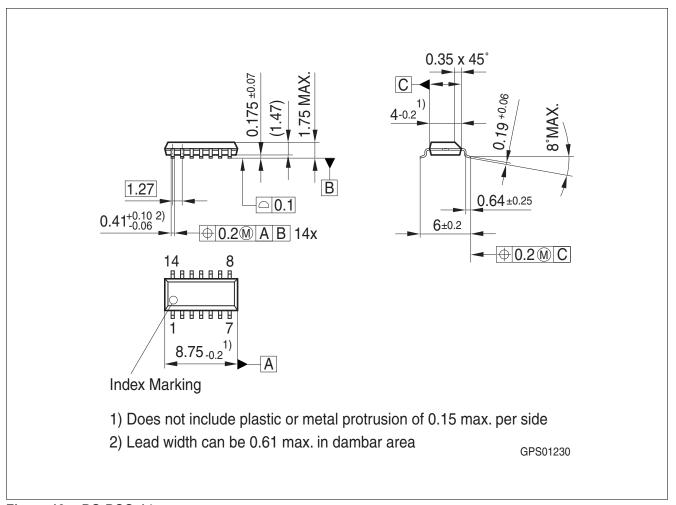

PG-DSO-14

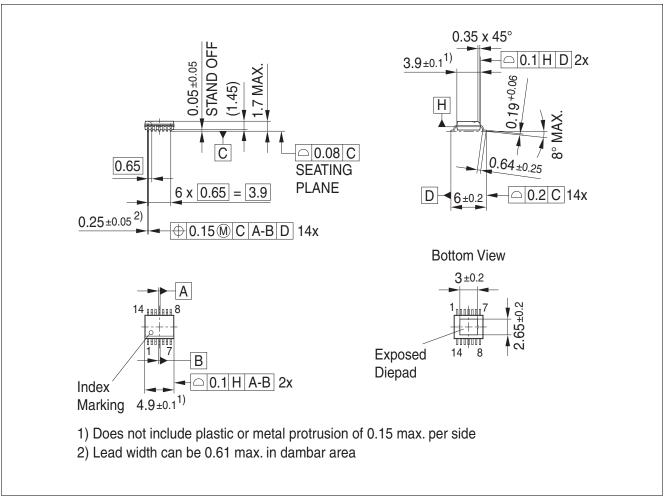

PG-SSOP-14 exposed pad

| Туре       | Package                | Marking |

|------------|------------------------|---------|

| TLE42994G  | PG-DSO-8               | 42994G  |

| TLE42994GM | PG-DSO-14              | 42994GM |

| TLE42994E  | PG-SSOP-14 exposed pad | 42994E  |

Data Sheet 2 Rev. 1.2, 2014-07-03

Overview

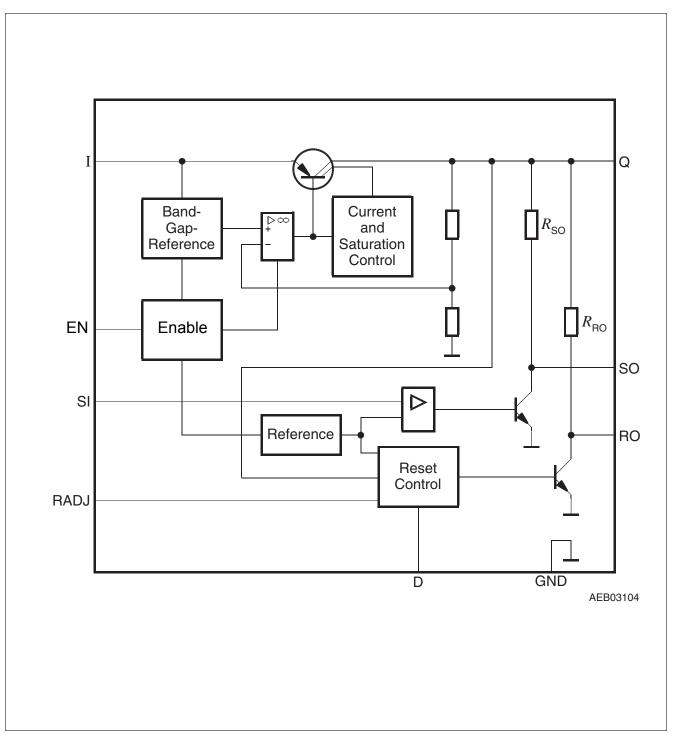

resistor divider. The power-on reset delay time can be programmed by the external delay capacitor. The additional sense comparator provides an early warning function: Any voltage (e.g. the input voltage) can be monitored, an under-voltage condition is indicated by setting the comparator's output to low. The TLE42994GM (PG-DSO-14 package) and TLE42994E (PG-SSOP-14 exposed pad package) include additionally an Enable function permitting enabling/disabling the regulator. In case the regulator is disabled it consumes less current than 1  $\mu$ A.

#### **Dimensioning Information on External Components**

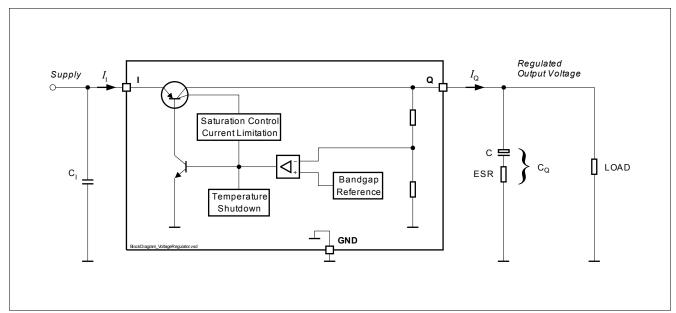

The input capacitor  $C_{l}$  is recommended for compensation of line influences. The output capacitor  $C_{Q}$  is necessary for the stability of the control loop.

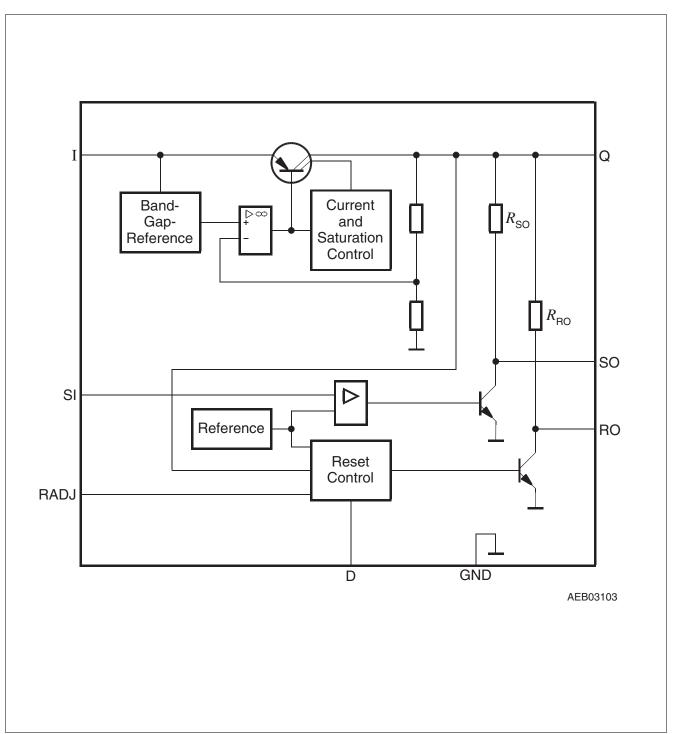

#### **Circuit Description**

The control amplifier compares a reference voltage to a voltage that is proportional to the output voltage and drives the base of the series transistor via a buffer. Saturation control as a function of the load current prevents any oversaturation of the power element. The component also has a number of internal circuits for protection against:

- Overload

- Overtemperature

- Reverse polarity

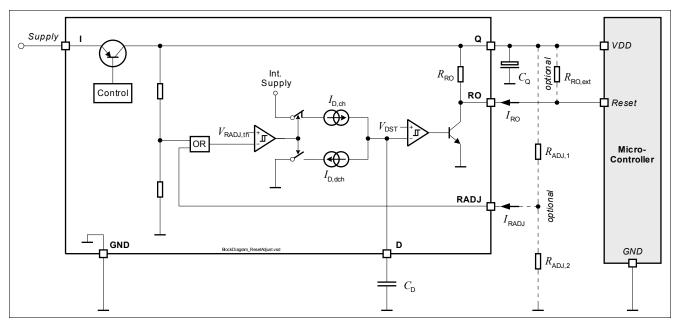

**Block Diagram**

## 2 Block Diagram

Figure 1 Block Diagram TLE42994G (package PG-DSO-8)

**Block Diagram**

Figure 2 Block Diagram TLE42994GM, TLE42994E (packages PG-DSO-14, PG-SSOP-14 exposed pad)

## 3 Pin Configuration

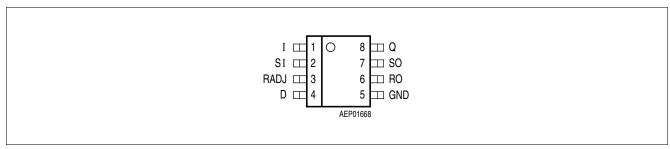

## 3.1 Pin Assignment TLE42994G (PG-DSO-8)

Figure 3 Pin Configuration (top view)

## 3.2 Pin Definitions and Functions TLE42994G (PG-DSO-8)

| Pin | Symbol | Function                                                                                                                                                             |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 1      | Input for compensating line influences, a capacitor to GND close to the IC terminals is recommended                                                                  |

| 2   | SI     | Sense Input connect the voltage to be monitored; connect to Q if the sense comparator is not needed                                                                  |

| 3   | RADJ   | Reset Threshold Adjust connect an external voltage divider to adjust reset threshold; connect to GND for using internal threshold                                    |

| 4   | D      | Reset Delay Timing connect a ceramic capacitor to GND for adjusting the reset delay time; leave open if the reset function is not needed                             |

| 5   | GND    | Ground                                                                                                                                                               |

| 6   | RO     | Reset Output open collector output; internally linked to the output via a 20 k $\Omega$ pull-up resistor; leave open if the reset function is not needed             |

| 7   | SO     | Sense Output open collector output; internally linked to the output via a 20 k $\Omega$ pull-up resistor; leave open if the sense comparator is not needed           |

| 8   | Q      | Output block to GND with a capacitor close to the IC terminals, respecting the values given for its capacitance $C_{\rm Q}$ and ESR in "Functional Range" on Page 12 |

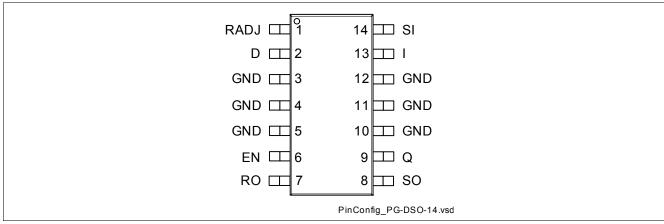

## 3.3 Pin Assignment TLE42994GM (PG-DSO-14)

Figure 4 Pin Configuration (top view)

## 3.4 Pin Definitions and Functions TLE42994GM (PG-DSO-14)

| Pin        | Symbol | Function                                                                                                                                                                       |

|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | RADJ   | Reset Threshold Adjust connect an external voltage divider to adjust reset threshold; connect to GND for using internal threshold                                              |

| 2          | D      | Reset Delay Timing connect a ceramic capacitor to GND for adjusting the reset delay time; leave open if the reset function is not needed                                       |

| 3, 4, 5    | GND    | Ground connect all pins to PCB and heatsink area                                                                                                                               |

| 6          | EN     | Enable high signal enables the regulator; low signal disables the regulator; connect to I if the Enable function is not needed                                                 |

| 7          | RO     | Reset Output open collector output; internally linked to the output via a $20k\Omega$ pull-up resistor; leave open if the reset function is not needed                         |

| 8          | SO     | Sense Output open collector output; internally linked to the output via a $20k\Omega$ pull-up resistor; leave open if the sense comparator is not needed                       |

| 9          | Q      | Output block to GND with a capacitor close to the IC terminals, respecting the values given for its capacitance $C_{\rm Q}$ and ESR in the table "Functional Range" on Page 12 |

| 10, 11, 12 | GND    | Ground connect all pins to PCB and heatsink area                                                                                                                               |

| Pin | Symbol | Function                                                                                            |

|-----|--------|-----------------------------------------------------------------------------------------------------|

| 13  | I      | Input for compensating line influences, a capacitor to GND close to the IC terminals is recommended |

| 14  | SI     | Sense Input connect the voltage to be monitored; connect to Q if the sense comparator is not needed |

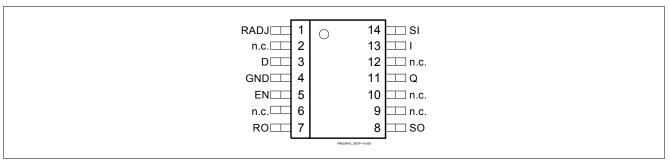

## 3.5 Pin Assignment TLE42994E (PG-SSOP-14 exposed pad)

Figure 5 Pin Configuration (top view)

## 3.6 Pin Definitions and Functions TLE42994E (PG-SSOP-14 exposed pad)

| Pin       | Symbol | Function                                                                                                                                                                       |

|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | RADJ   | Reset Threshold Adjust connect an external voltage divider to adjust reset threshold; connect to GND for using internal threshold                                              |

| 2, 6      | n.c.   | not connected leave open or connect to GND                                                                                                                                     |

| 3         | D      | Reset Delay Timing connect a ceramic capacitor to GND for adjusting the reset delay time; leave open if the reset function is not needed                                       |

| 4         | GND    | Ground connect all pins to PCB and heatsink area                                                                                                                               |

| 5         | EN     | Enable high signal enables the regulator; low signal disables the regulator; connect to I if the Enable function is not needed                                                 |

| 7         | RO     | Reset Output open collector output; internally linked to the output via a $20k\Omega$ pull-up resistor; leave open if the reset function is not needed                         |

| 8         | so     | Sense Output open collector output; internally linked to the output via a $20k\Omega$ pull-up resistor; leave open if the sense comparator is not needed                       |

| 9, 10, 12 | n.c.   | not connected leave open or connect to GND                                                                                                                                     |

| 11        | Q      | Output block to GND with a capacitor close to the IC terminals, respecting the values given for its capacitance $C_{\rm Q}$ and ESR in the table "Functional Range" on Page 12 |

| 13        | I      | Input for compensating line influences, a capacitor to GND close to the IC terminals is recommended                                                                            |

| Pin | Symbol | Function                                                                                                   |

|-----|--------|------------------------------------------------------------------------------------------------------------|

| 14  | SI     | Sense Input connect the voltage to be monitored; connect to Q if the sense comparator is not needed        |

| PAD | -      | Exposed Pad attach the exposed pad on package bottom to the heatsink area on circuit board; connect to GND |

**General Product Characteristics**

#### 4 General Product Characteristics

## 4.1 Absolute Maximum Ratings

#### Table 1 Absolute Maximum Ratings<sup>1)</sup>

-40 °C  $\leq T_{\rm j} \leq$  150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                | Symbol                            | Values  |      |                | Unit | Note / Test Condition                                  | Number  |

|--------------------------|-----------------------------------|---------|------|----------------|------|--------------------------------------------------------|---------|

|                          |                                   | Min.    | Тур. | Max.           |      |                                                        |         |

| Input I, Enable Input EN | , Sense Input S                   | SI      | 1    | 1              | l.   | 1                                                      | 1       |

| Voltage                  | $V_{I},V_{EN},V_{SI}$             | -40     | _    | 45             | V    | _                                                      | P_4.1.1 |

| Output Q, Reset Output   | RO, Sense Ou                      | tput SO | *    | - <del>!</del> |      | <del>'</del>                                           | -       |

| Voltage                  | $V_{\rm Q},V_{\rm RO},V_{\rm SO}$ | -0.3    | -    | 7              | V    | _                                                      | P_4.1.2 |

| Reset Delay D, Reset Th  | reshold RADJ                      |         |      |                |      |                                                        |         |

| Voltage                  | $V_{D},V_{RADJ}$                  | -0.3    | _    | 7              | V    | _                                                      | P_4.1.3 |

| Temperature              |                                   |         |      |                |      |                                                        |         |

| Junction Temperature     | $T_{\rm j}$                       | -40     | _    | 150            | °C   | _                                                      | P_4.1.4 |

| Storage Temperature      | $T_{ m stg}$                      | -50     | _    | 150            | °C   | _                                                      | P_4.1.5 |

| ESD Absorption           |                                   |         |      |                |      |                                                        |         |

| ESD Absorption           | $V_{ESD,HBM}$                     | -2      | _    | 2              | kV   | Human Body Model<br>(HBM) <sup>2)</sup>                | P_4.1.6 |

| ESD Absorption           | $V_{ESD,CDM}$                     | -500    | -    | 500            | V    | Charge Device Model (CDM) <sup>3)</sup>                | P_4.1.7 |

| ESD Absorption           | $V_{ESD,CDM}$                     | -750    | _    | 750            | V    | Charge Device Model (CDM) <sup>3)</sup> at corner pins | P_4.1.8 |

<sup>1)</sup> not subject to production test, specified by design

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

<sup>2)</sup> ESD susceptibility Human Body Model "HBM" according to AEC-Q100-002 - JESD22-A114

<sup>3)</sup> ESD susceptibility Charged Device Model "CDM" according to ESDA STM5.3.1

#### **General Product Characteristics**

## 4.2 Functional Range

Table 2 Functional Range

| Parameter                                     | Symbol       | Values |      |      | Unit | Note / Test Condition | Number  |

|-----------------------------------------------|--------------|--------|------|------|------|-----------------------|---------|

|                                               |              | Min.   | Тур. | Max. |      |                       |         |

| Input Voltage                                 | $V_1$        | 5.5    | _    | 45   | V    | _                     | P_4.2.1 |

| Output Capacitor's Requirements for Stability | $C_{Q}$      | 22     | -    | _    | μF   | _1)                   | P_4.2.2 |

| Output Capacitor's Requirements for Stability | $ESR(C_{Q})$ | _      | -    | 3    | Ω    | _2)                   | P_4.2.3 |

| Junction Temperature                          | $T_{\rm j}$  | -40    | _    | 150  | °C   | _                     | P_4.2.4 |

<sup>1)</sup> the minimum output capacitance requirement is applicable for a worst case capacitance tolerance of 30%

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

<sup>2)</sup> relevant ESR value at f = 10 kHz

#### **General Product Characteristics**

#### 4.3 Thermal Resistance

Table 3 Thermal Resistance

| Parameter                                 | Symbol      |      | Value | s    | Unit | Note / Test Condition                                                 | Number   |

|-------------------------------------------|-------------|------|-------|------|------|-----------------------------------------------------------------------|----------|

|                                           |             | Min. | Тур.  | Max. |      |                                                                       |          |

| TLE42994G (PG-DSO-8)                      |             |      |       |      | '    |                                                                       |          |

| Junction to Soldering Point <sup>1)</sup> | $R_{thJSP}$ | _    | _     | 60   | K/W  | measured to pin 5                                                     | P_4.3.1  |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | _    | 113   | _    | K/W  | FR4 2s2p board <sup>2)</sup>                                          | P_4.3.2  |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | _    | 185   | _    | K/W  | FR4 1s0p board, footprint only <sup>3)</sup>                          | P_4.3.3  |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | _    | 142   | _    | K/W  | FR4 1s0p board, 300mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> | P_4.3.4  |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | -    | 136   | -    | K/W  | FR4 1s0p board, 600mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> | P_4.3.5  |

| TLE42994GM (PG-DSO-14)                    |             |      |       |      | '    |                                                                       |          |

| Junction to Soldering Point <sup>1)</sup> | $R_{thJSP}$ | _    | _     | 30   | K/W  | measured to all GND pins                                              | P_4.3.6  |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | _    | 63    | _    | K/W  | FR4 2s2p board <sup>2)</sup>                                          | P_4.3.7  |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | _    | 112   | _    | K/W  | FR4 1s0p board, footprint only <sup>3)</sup>                          | P_4.3.8  |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | _    | 73    | -    | K/W  | FR4 1s0p board, 300mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> | P_4.3.9  |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | -    | 65    | -    | K/W  | FR4 1s0p board, 600mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> | P_4.3.10 |

| TLE42994E (PG-SSOP-14 e                   | xposed pag  | d)   |       | •    |      |                                                                       |          |

| Junction to Case <sup>1)</sup>            | $R_{thJC}$  | _    | 10    | _    | K/W  | _                                                                     | P_4.3.11 |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | _    | 47    | _    | K/W  | FR4 2s2p board <sup>2)</sup>                                          | P_4.3.12 |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | _    | 140   | _    | K/W  | FR4 1s0p board, footprint only <sup>3)</sup>                          | P_4.3.13 |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | _    | 63    | -    | K/W  | FR4 1s0p board, 300mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> | P_4.3.14 |

| Junction to Ambient <sup>1)</sup>         | $R_{thJA}$  | _    | 53    | -    | K/W  | FR4 1s0p board, 600mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> | P_4.3.15 |

<sup>1)</sup> not subject to production test, specified by design

<sup>2)</sup> Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm³ board with 2 inner copper layers (2 x 70µm Cu, 2 x 35µm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

<sup>3)</sup> Specified  $R_{\text{thJA}}$  value is according to JEDEC JESD 51-3 at natural convection on FR4 1s0p board; The Product (Chip+Package) was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with 1 copper layer (1 x 70µm Cu).

## 5 Block Description and Electrical Characteristics

## 5.1 Voltage Regulator

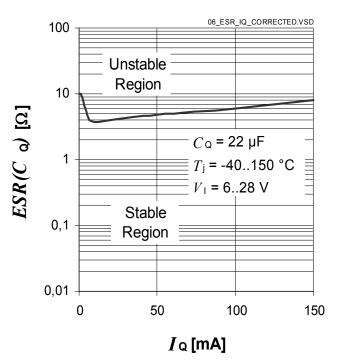

The output voltage  $V_{\rm Q}$  is controlled by comparing a portion of it to an internal reference and driving a PNP pass transistor accordingly. The control loop stability depends on the output capacitor  $C_{\rm Q}$ , the load current, the chip temperature and the poles/zeros introduced by the integrated circuit. To ensure stable operation, the output capacitor's capacitance and its equivalent series resistor ESR requirements given in the table "Functional Range" on Page 12 have to be maintained. For details see also the typical performance graph "Output Capacitor Series Resistor ESR( $C_{\rm Q}$ ) versus Output Current  $I_{\rm Q}$ " on Page 17. As the output capacitor also has to buffer load steps it should be sized according to the application's needs.

An input capacitor  $C_l$  is strongly recommended to compensate line influences. Connect the capacitors close to the component's terminals.

A protection circuitry prevents the IC as well as the application from destruction in case of catastrophic events. These safeguards contain an output current limitation, a reverse polarity protection as well as a thermal shutdown in case of overtemperature.

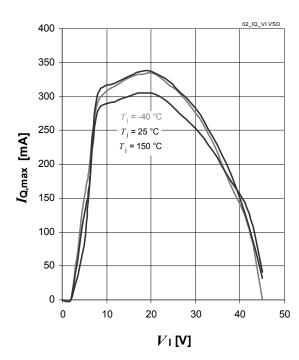

To avoid excessive power dissipation that could never be handled by the pass element and the package, the maximum output current is decreased at input voltages above  $V_1$  = 22 V.

The overtemperature shutdown circuit prevents the IC from immediate destruction under fault conditions (e.g. output continuously short-circuited) by switching off the power stage. After the chip has cooled down, the regulator restarts. This leads to an oscillatory behaviour of the output voltage until the fault is removed. However, junction temperatures above 150 °C are outside the maximum ratings and therefore significantly reduce the IC's lifetime.

The TLE42994 allows a negative supply voltage. In this fault condition, small currents are flowing into the IC, increasing its junction temperature. This has to be considered for the thermal design, respecting that the thermal protection circuit is not operating during reverse polarity conditions.

Figure 6 Voltage Regulator

#### Table 4 Electrical Characteristics Voltage Regulator

$V_1$  = 13.5 V, -40 °C ≤  $T_j$  ≤ 150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                              | Symbol                   | Values |      |      | Unit | Note / Test Condition                                                                  | Number  |

|--------------------------------------------------------|--------------------------|--------|------|------|------|----------------------------------------------------------------------------------------|---------|

|                                                        |                          | Min.   | Тур. | Max. |      |                                                                                        |         |

| Output Voltage                                         | $V_{Q}$                  | 4.9    | 5.0  | 5.1  | V    | 100 $\mu$ A < $I_Q$ < 100 mA 6 V < $V_I$ < 18 V                                        | P_5.1.1 |

| Output Voltage                                         | $V_{Q}$                  | 4.85   | 5.0  | 5.15 |      | 100 $\mu$ A < $I_{\rm Q}$ < 150 mA 6 V < $V_{\rm I}$ < 18 V                            | P_5.1.2 |

| Output Current Limitation                              | $I_{Q,max}$              | 150    | 400  | 500  | mA   | $V_{\rm Q}$ = 4.8V                                                                     | P_5.1.3 |

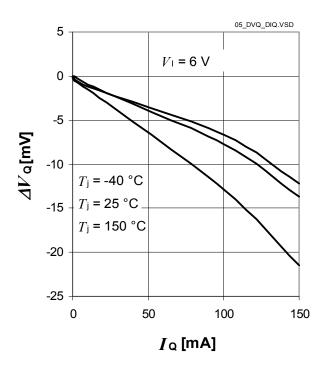

| Load Regulation steady-state                           | $\Delta V_{ m Q,\ load}$ | -30    | -5   | _    | mV   | $I_{\rm Q}$ = 1 mA to 100 mA $V_{\rm I}$ = 6 V                                         | P_5.1.4 |

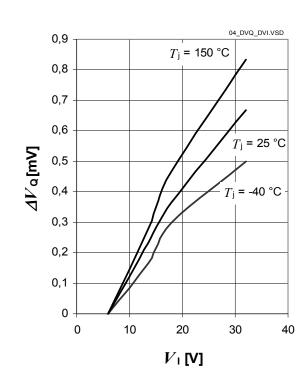

| Line Regulation<br>steady-state                        | $\Delta V_{ m Q,  line}$ | _      | 10   | 25   | mV   | $V_1 = 6 \text{ V to } 32 \text{ V}$<br>$I_Q = 1 \text{ mA}$                           | P_5.1.5 |

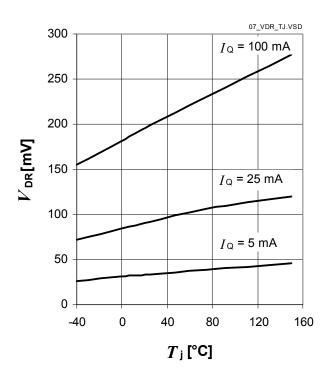

| Dropout Voltage <sup>1)</sup> $V_{dr} = V_{I} - V_{Q}$ | $V_{dr}$                 | _      | 220  | 500  | mV   | I <sub>Q</sub> = 100 mA                                                                | P_5.1.6 |

| Overtemperature Shutdown<br>Threshold                  | $T_{j,sd}$               | 151    | _    | 200  | °C   | $T_{\rm j}$ increasing <sup>2)</sup>                                                   | P_5.1.7 |

| Overtemperature Shutdown<br>Threshold Hysteresis       | $T_{ m j,sdh}$           | _      | 15   | _    | °C   | $T_{\rm j}$ decreasing <sup>2)</sup>                                                   | P_5.1.8 |

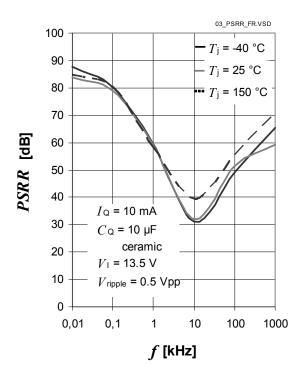

| Power Supply Ripple<br>Rejection <sup>3)</sup>         | PSRR                     | -      | 66   | -    | dB   | $f_{\text{ripple}}$ = 100 Hz<br>$V_{\text{ripple}}$ = 1 Vpp<br>$I_{\text{Q}}$ = 100 mA | P_5.1.9 |

<sup>1)</sup> measured when the output voltage  $V_{\rm Q}$  has dropped 100 mV from the nominal value obtained at  $V_{\rm I}$  = 13.5 V

<sup>2)</sup> not subject to production test, specified by design

<sup>3)</sup> not subject to production test, specified by design

## 5.2 Typical Performance Characteristics Voltage Regulator

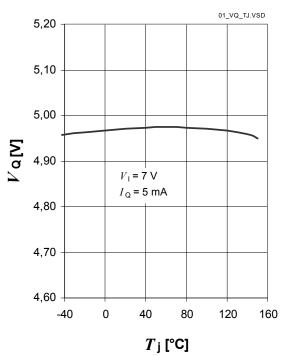

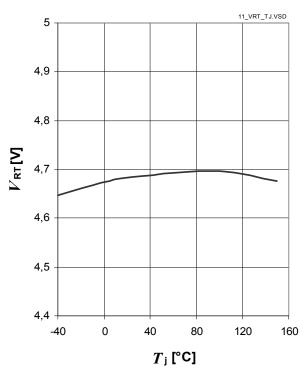

## Output Voltage $V_{\rm Q}$ versus Junction Temperature $T_{\rm J}$

Power Supply Ripple Rejection PSRR versus ripple frequency  $f_r$

# Output Current $I_{\rm Q}$ versus Input Voltage $V_{\rm I}$

Line Regulation  $\Delta V_{\rm Q,line}$  versus Input Voltage Change  $\Delta V_{\rm I}$

# Load Regulation $\Delta V_{\mathrm{Q,load}}$ versus Output Current Change $\Delta I_{\mathrm{Q}}$

Output Capacitor Series Resistor  $ESR(C_{\rm Q})$  versus Output Current  $I_{\rm Q}$

Dropout Voltage  $V_{\rm dr}$  versus Junction Temperature  $T_{\rm i}$

## 5.3 Current Consumption

#### Table 5 Electrical Characteristics Voltage Regulator

$V_{\rm I}$  = 13.5 V, -40 °C ≤  $T_{\rm j}$  ≤ 150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                   | Symbol  | Values |      |      | Unit | Note / Test Condition                                                         | Number  |

|---------------------------------------------|---------|--------|------|------|------|-------------------------------------------------------------------------------|---------|

|                                             |         | Min.   | Тур. | Max. |      |                                                                               |         |

| Current Consumption $I_{q} = I_{l} - I_{Q}$ | $I_{q}$ | -      | _    | 1    | μА   | $V_{\rm EN}$ = 0 V<br>TLE42994GM and<br>TLE42994E only<br>$T_{\rm j}$ = 25 °C | P_5.4.1 |

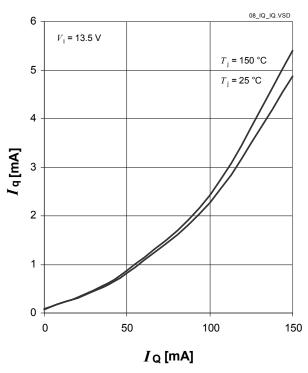

| Current Consumption $I_q = I_l - I_Q$       | $I_{q}$ | _      | 65   | 100  | μΑ   | Enable HIGH $I_Q$ = 100 $\mu$ A, $T_j$ = 25 °C                                | P_5.4.2 |

| Current Consumption $I_q = I_l - I_Q$       | $I_{q}$ | _      | 65   | 105  | μΑ   | Enable HIGH $I_Q = 100 \mu A, T_j \le 85 °C$                                  | P_5.4.3 |

| Current Consumption $I_q = I_l - I_Q$       | $I_{q}$ | _      | 0.17 | 0.5  | mA   | Enable HIGH $I_{\rm Q}$ = 10 mA                                               | P_5.4.4 |

| Current Consumption $I_q = I_l - I_Q$       | $I_{q}$ | _      | 0.7  | 2    | mA   | Enable HIGH $I_{\rm Q}$ = 50 mA                                               | P_5.4.5 |

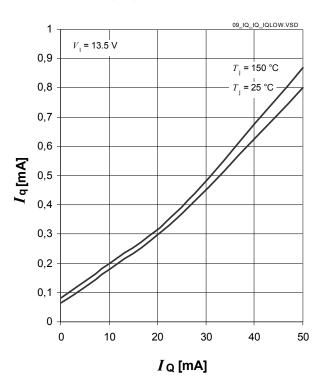

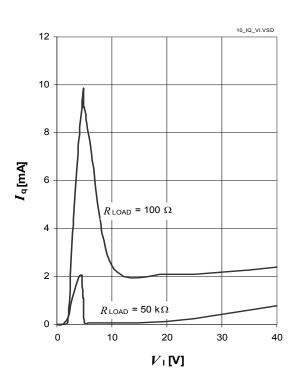

## 5.4 Typical Performance Characteristics Current Consumption

# Current Consumption $I_{\rm q}$ versus Output Current $I_{\rm Q}$

# Current Consumption $I_{\rm q}$ versus Output Current $I_{\rm Q}$ ( $I_{\rm Q}$ low)

Current Consumption  $I_{\rm q}$  versus Input Voltage  $V_{\rm l}$

## 5.5 Enable Function (only TLE42994GM and TLE42994E)

#### Table 6 Electrical Characteristics Voltage Regulator

$V_{\rm I}$  = 13.5 V, -40 °C ≤  $T_{\rm j}$  ≤ 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                | Symbol       | Values |      | Unit | Note / Test Condition | Number                |         |

|--------------------------|--------------|--------|------|------|-----------------------|-----------------------|---------|

|                          |              | Min.   | Тур. | Max. |                       |                       |         |

| Enable OFF Voltage Range | $V_{EN,OFF}$ | -      | _    | 8.0  | V                     | _                     | P_5.6.1 |

| Enable ON Voltage Range  | $V_{EN,ON}$  | 3.5    | _    | _    | V                     | _                     | P_5.6.2 |

| Enable OFF Input Current | $I_{EN,OFF}$ | _      | 0.5  | 2    | μΑ                    | $V_{EN}$ = 0 V        | P_5.6.3 |

| Enable ON Input Current  | $I_{EN,ON}$  | _      | 3    | 5    | μΑ                    | V <sub>EN</sub> = 5 V | P_5.6.4 |

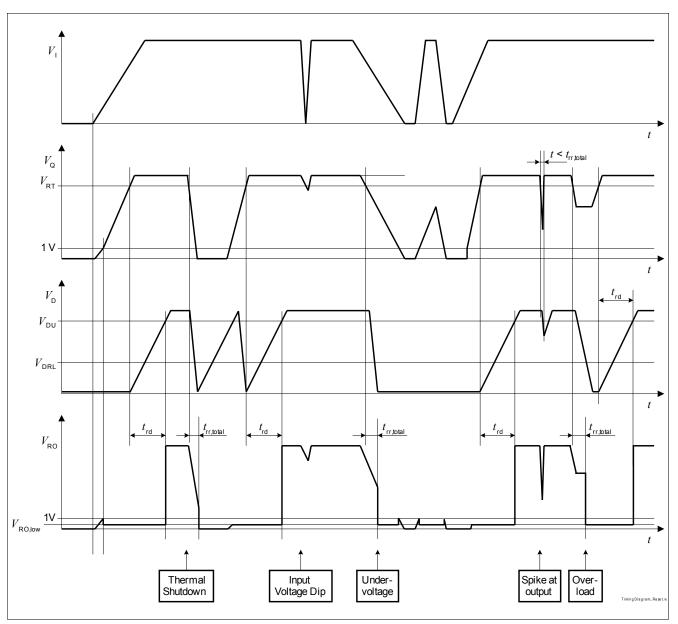

#### 5.6 Reset Function

The reset function provides several features:

#### **Output Undervoltage Reset:**

An output undervoltage condition is indicated by setting the Reset Output RO to "low". This signal might be used to reset a microcontroller during low supply voltage.

#### **Power-On Reset Delay Time:**

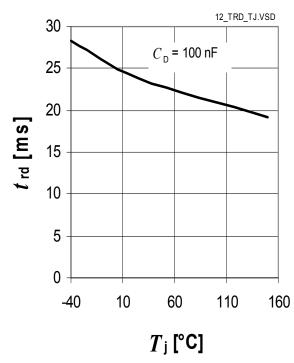

The power-on reset delay time trd allows a microcontoller and oscillator to start up. This delay time is the time frame from exceeding the reset switching threshold  $V_{\rm RT}$  until the reset is released by switching the reset output "RO" from "low" to "high". The power-on reset delay time  $t_{\rm rd}$  is defined by an external delay capacitor  $C_{\rm D}$  connected to pin D charged by the delay capacitor charge current  $I_{\rm D,ch}$  starting from  $V_{\rm D}$  = 0 V.

If the application needs a power-on reset delay time *t*rd different from the value given in **Power On Reset Delay Time**, the delay capacitor's value can be derived from the specified values in **Power On Reset Delay Time** and the desired power-on delay time:

$$C_{\rm D} = \frac{t_{\rm rd, new}}{t_{\rm rd}} \times 100 \rm nF$$

(1)

with

- $C_{\rm D}$ : capacitance of the delay capacitor to be chosen

- $t_{\rm rd,new}$ : desired power-on reset delay time

- $t_{\rm rd}$ : power-on reset delay time specified in this datasheet

For a precise calculation also take the delay capacitor's tolerance into consideration.

#### **Reset Reaction Time:**

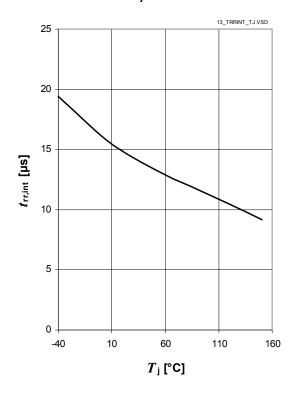

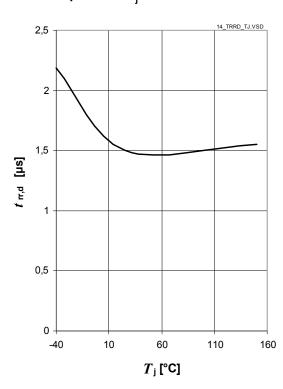

The reset reaction time avoids that short undervoltage spikes trigger an unwanted reset "low" signal. The reset reaction rime  $t_{\rm rr}$  considers the internal reaction time  $t_{\rm rr,int}$  and the discharge time  $t_{\rm rr,d}$  defined by the external delay capacitor  $C_{\rm D}$  (see typical performance graph for details). Hence, the total reset reaction time becomes:

$$t_{rr} = t_{rd, int} + t_{rr, d}$$

(2)

with

- t<sub>rr</sub>: reset reaction time

- t<sub>rr int</sub>: internal reset reaction time

- t<sub>rr.d</sub>: reset discharge

#### Optional Reset Output Pull-Up Resistor $R_{RO.ext}$ :

The Reset Output RO is an open collector output with an integrated pull-up resistor. If needed, an external pull-up resistor to the output Q can be added. In **Table 7 "Electrical Characteristics Reset Function" on Page 24** a minimum value for the external resistor  $R_{\text{RO,ext}}$  is given.

Data Sheet 21 Rev. 1.2, 2014-07-03

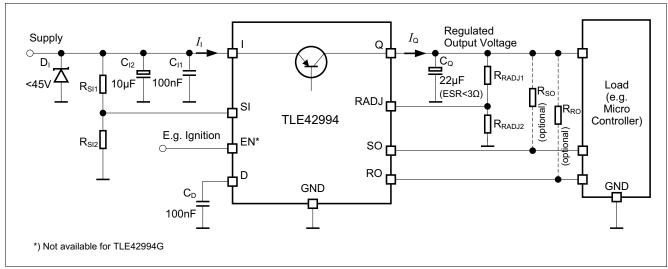

#### **Reset Adjust Function**

The undervoltage reset switching threshold can be adjusted according to the application's needs by connecting an external voltage divider ( $R_{\rm ADJ1}$ ,  $R_{\rm ADJ2}$ ) at pin RADJ. For selecting the default threshold connect pin RADJ to GND.

When dimensioning the voltage divider, take into consideration that there will be an additional current constantly flowing through the resistors.

With a voltage divider connected, the reset switching threshold  $V_{\mathrm{RT,new}}$  is calculated as follows:

$$V_{RT, \text{ new}} = \frac{R_{ADJ, 1} + R_{ADJ, 2}}{R_{ADJ, 2}} \times V_{RADJ, \text{ th}}$$

(3)

with

- ullet  $V_{

m RT,new}$ : the desired new reset switching threshold

- $R_{\rm ADJ1}$ ,  $R_{\rm ADJ2}$ : resistors of the external voltage divider

- $V_{\rm RADJ,th}$ : reset adjust switching threshold given in Table 7 "Electrical Characteristics Reset Function" on Page 24

Figure 7 Block Diagram Reset Function

Figure 8 Timing Diagram Reset

#### Table 7 Electrical Characteristics Reset Function

$V_1$  = 13.5 V, -40 °C ≤  $T_j$  ≤ 150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                            | Symbol                  | Values |      |      | Unit | Note / Test Condition                                                                                                   | Number  |

|------------------------------------------------------|-------------------------|--------|------|------|------|-------------------------------------------------------------------------------------------------------------------------|---------|

|                                                      |                         | Min.   | Тур. | Max. |      |                                                                                                                         |         |

| Output Undervoltage Reset                            | <u>'</u>                | 1      |      | '    | •    |                                                                                                                         |         |

| Default Output Undervoltage Reset                    | $V_{RT}$                | 4.5    | 4.65 | 4.8  | V    | $V_{\mathrm{Q}}$ decreasing                                                                                             | P_5.7.1 |

| Switching Thresholds                                 |                         |        |      |      |      |                                                                                                                         |         |

| Output Undervoltage Reset Thres                      |                         |        |      |      |      |                                                                                                                         |         |

| Reset Adjust                                         | $V_{\mathrm{RADJ,th}}$  | 1.26   | 1.36 | 1.44 | V    | $3.5 \text{ V} \le V_{Q} < 5 \text{ V}$                                                                                 | P_5.7.2 |

| Switching Threshold                                  |                         |        |      |      |      |                                                                                                                         |         |

| Reset Adjustment Range <sup>1)</sup>                 | $V_{\mathrm{RT,range}}$ | 3.50   | _    | 4.65 | V    | _                                                                                                                       | P_5.7.3 |

| Reset Output RO                                      |                         |        |      |      |      |                                                                                                                         |         |

| Reset Output Low Voltage                             | $V_{\mathrm{RO,low}}$   | _      | 0.1  | 0.4  | V    | 1 V $\leq V_{\rm Q} \leq V_{\rm RT}$<br>no external $R_{\rm RO,ext}$                                                    | P_5.7.4 |

| Reset Output Internal Pull-up Resistor to $V_{ m O}$ | $R_{RO}$                | 10     | 20   | 40   | kΩ   | -                                                                                                                       | P_5.7.5 |

| Optional Reset Output External                       | $R_{RO,ext}$            | 5.6    | _    | _    | kΩ   | $1 \text{ V} \leq V_{Q} \leq V_{RT}$ ;                                                                                  | P_5.7.6 |

| Pull-up Resistor to $V_{Q}$                          | T(O,CX                  |        |      |      |      | $V_{RO} \le 0.4 \text{ V}$                                                                                              | _       |

| Reset Delay Timing                                   |                         |        |      |      |      |                                                                                                                         |         |

| Delay Pin Output Voltage                             | $V_{D}$                 | _      | _    | 5    | V    | _                                                                                                                       | P_5.7.7 |

| Power On Reset Delay Time                            | $t_{rd}$                | 17     | 28   | 35   | ms   | $C_{\rm D}$ = 100 nF<br>Calculated Value:<br>$t_{\rm rd}$ = $C_{\rm D}$ * $V_{\rm DU}$ / $I_{\rm D,ch}$                 | P_5.7.8 |

| Upper Delay<br>Switching Threshold                   | $V_{DU}$                | _      | 1.85 | _    | V    | _                                                                                                                       | P_5.7.9 |

| Lower Delay<br>Switching Threshold                   | $V_{DL}$                | _      | 0.50 | _    | V    | -                                                                                                                       | P_5.7.1 |

| Delay Capacitor<br>Charge Current                    | $I_{D,ch}$              | _      | 8.0  | -    | μΑ   | V <sub>D</sub> = 1 V                                                                                                    | P_5.7.1 |

| Delay Capacitor<br>Reset Discharge Current           | $I_{D,dch}$             | _      | 70   | _    | mA   | <i>V</i> <sub>D</sub> = 1 V                                                                                             | P_5.7.1 |

| Delay Capacitor<br>Discharge Time                    | t <sub>rr, d</sub>      | _      | 1.9  | 3    | μs   | Calculated Value: $t_{\rm rr,  d} = C_{\rm D} * (V_{\rm DU} - V_{\rm DL}) / I_{\rm D, dch}$ $C_{\rm D} = 100 \; \rm nF$ | P_5.7.1 |

| Internal Reset Reaction Time                         | $t_{ m rr, int}$        | _      | 14   | 20   | μs   | $C_{\rm D}$ = 0 nF <sup>2)</sup>                                                                                        | P_5.7.1 |

| Reset Reaction Time                                  | $t_{\rm rr,\ total}$    | _      | 15.9 | 23   | μs   | Calculated Value:<br>$t_{\text{rr, total}} = t_{\text{rr, int}} + t_{\text{rr,d}}$<br>$C_{\text{D}} = 100 \text{ nF}$   | P_5.7.1 |

<sup>1)</sup>  $V_{\rm RT}$  is scaled linearly, in case the Reset Switching Threshold is modified

<sup>2)</sup> parameter not subject to production test; specified by design

## 5.7 Typical Performance Characteristics Reset

# Undervoltage Reset Switching Threshold $V_{\mathrm{RT}}$ versus Junction Temperature $T_{\mathrm{i}}$

Internal Reset Reaction Time  $t_{\rm rr,int}$  versus Junction Temperature  $T_{\rm j}$

# Power On Reset Delay Time $t_{\rm rd}$ versus Junction Temperature $T_{\rm i}$

Delay Capacitor Discharge Time  $t_{\rm rr,d}$  versus Junction Temperature  $T_{\rm j}$

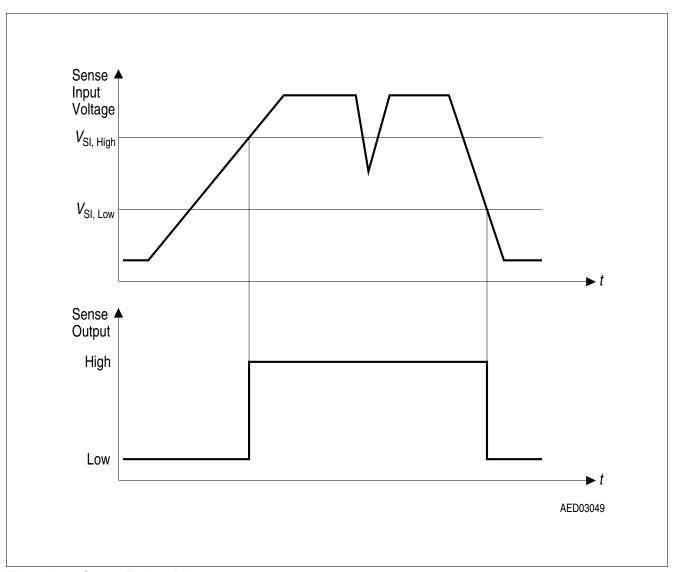

## 5.8 Early Warning Function

The additional sense comparator provides an early warning function: Any voltage (e.g. the input voltage) can be monitored, an undervoltage condition is indicated by setting the comparator's output to low.

Figure 9 Sense Timing Diagram

#### Table 8 Electrical Characteristics Early Warning Function

$V_{\rm I}$  = 13.5 V, -40 °C ≤  $T_{\rm j}$  ≤ 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                  | Symbol            | Values |      |      | Unit | Note / Test Condition                              | Number  |

|----------------------------|-------------------|--------|------|------|------|----------------------------------------------------|---------|

|                            |                   | Min.   | Тур. | Max. |      |                                                    |         |

| Sense Comparator Input     |                   |        |      | Į.   | ·    |                                                    |         |

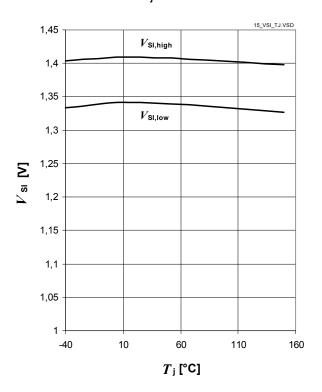

| Sense Threshold High       | $V_{SI,high}$     | 1.34   | 1.45 | 1.54 | V    | _                                                  | P_5.9.1 |

| Sense Threshold Low        | $V_{SI,low}$      | 1.26   | 1.36 | 1.44 | ٧    | _                                                  | P_5.9.2 |

| Sense Switching Hysteresis | $V_{SI,hy}$       | 50     | 90   | 130  | mV   | $V_{\rm SI,hy} = V_{\rm SI,high} - V_{\rm SI,low}$ | P_5.9.3 |

| Sense Input Current        | $I_{\mathrm{SI}}$ | -1     | -0.1 | 1    | μA   | _                                                  | P_5.9.4 |

#### Table 8 Electrical Characteristics Early Warning Function (cont'd)

$V_{\rm I}$  = 13.5 V, -40 °C ≤  $T_{\rm j}$  ≤ 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                      | Symbol       | Values |      |      | Unit | Note / Test Condition                                                                       | Number  |

|----------------------------------------------------------------|--------------|--------|------|------|------|---------------------------------------------------------------------------------------------|---------|

|                                                                |              | Min.   | Тур. | Max. |      |                                                                                             |         |

| Sense Comparator Output                                        |              | 1      | Į.   |      |      |                                                                                             |         |

| Sense Output Low Voltage                                       | $V_{SO,low}$ | _      | 0.1  | 0.4  | V    | $V_{\rm SI} < V_{\rm SI,low}$<br>$V_{\rm I} > 5.5  {\rm V}$<br>no external $R_{\rm SO,ext}$ | P_5.9.5 |

| Sense Output Internal Pull-up Resistor to $V_{\rm Q}$          | $R_{SO}$     | 10     | 20   | 40   | kΩ   | -                                                                                           | P_5.9.6 |

| Optional Sense Output External Pull-up Resistor to $V_{\rm Q}$ | $R_{SO,ext}$ | 5.6    | _    | _    | kΩ   | $V_1 > 5.5 \text{ V}$<br>$V_{SO} \le 0.4 \text{ V}$                                         | P_5.9.7 |

## 5.9 Typical Performance Characteristics Early Warning

# Sense Thresholds $V_{\rm SI,high},~V_{\rm SI,low}$ versus Junction Temperature $T_{\rm j}$

## **6** Application Information

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

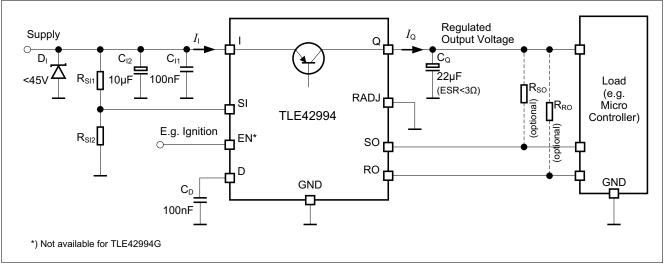

### 6.1 Application Diagram

Figure 10 Application Diagram with Selecting Default Reset Thresholds

Figure 11 Application Diagram with Reset Thresholds Adjustment

### 6.2 Selection of External Components

#### 6.2.1 Input Pin

The typical input circuitry for a linear voltage regulator is shown in the application diagram above.

A ceramic capacitor at the input, in the range of 100 nF to 470 nF, is recommended to filter out the high frequency disturbances imposed by the line e.g. ISO pulses 3a/b. This capacitor must be placed very close to the input pin of the linear voltage regulator on the PCB.

An aluminum electrolytic capacitor in the range of 10  $\mu$ F to 470  $\mu$ F is recommended as an input buffer to smooth out high energy pulses, such as ISO pulse 2a. This capacitor should be placed close to the input pin of the linear voltage regulator on the PCB.

An overvoltage suppressor diode can be used to further suppress any high voltage beyond the maximum rating of the linear voltage regulator and protect the device against any damage due to over-voltage.

The external components at the input are not mandatory for the operation of the voltage regulator, but they are recommended in case of possible external disturbances.

#### 6.2.2 Output Pin

An output capacitor is mandatory for the stability of linear voltage regulators.

The requirement to the output capacitor is given in "Functional Range" on Page 12. The graph "Output Capacitor Series Resistor  $ESR(C_Q)$  versus Output Current  $I_Q$ " on Page 17 shows the stable operation range of the device.

TLE42994 is designed to be stable with extremely low ESR capacitors. According to the automotive environment, ceramic capacitors with X5R or X7R dielectrics are recommended.

The output capacitor should be placed as close as possible to the regulator's output and GND pins and on the same side of the PCB as the regulator itself.

In case of rapid transients of input voltage or load current, the capacitance should be dimensioned in accordance and verified in the real application that the output stability requirements are fulfilled.

#### 6.3 Thermal Considerations

Knowing the input voltage, the output voltage and the load profile of the application, the total power dissipation can be calculated:

$$P_{D} = (V_{I} - V_{O}) \times I_{O} + V_{I} \times I_{G}$$

$$(4)$$

with

- P<sub>D</sub>: continuous power dissipation

- V<sub>I</sub>: input voltage

- V<sub>O</sub>: output voltage

- $I_{\Omega}$ : output current

- $I_{a}$ : quiescent current

The maximum acceptable thermal resistance  $R_{th,JA}$  can then be calculated:

$$R_{thJA, max} = \frac{T_{j, max} - T_a}{P_D}$$

(5)

with

- $T_{i,max}$ : maximum allowed junction temperature

- T<sub>a</sub>: ambient temperature

Based on the above calculation the proper PCB type and the necessary heat sink area can be determined with reference to the specification in "Thermal Resistance" on Page 13.

#### Example

Application conditions:

$$V_1 = 13.5 \text{ V}$$

$$V_{\rm O}$$

= 5 V

$$I_{\rm O}$$

= 50 mA

$$T_{\rm a}$$

= 125 °C

Calculation of  $R_{thJA,max}$ :

$$\begin{split} P_{\rm D} &= (V_{\rm I} - V_{\rm Q}) \bullet I_{\rm Q} + V_{\rm I} \bullet I_{\rm Q} \\ &= (13.5 \ {\rm V} - 5 \ {\rm V}) \bullet 50 \ {\rm mA} + 13.5 \ {\rm V} \bullet 2 \ {\rm mA} \\ &= 0.425 \ {\rm W} + 0.027 \ {\rm W} \\ &= 0.452 \ {\rm W} \\ R_{\rm thJA,max} &= (T_{\rm j,max} - T_{\rm a}) \ / \ P_{\rm D} \\ &= (150 \ {\rm ^{\circ}C} - 125 \ {\rm ^{\circ}C}) \ / \ 0.452 \ {\rm W} \\ &= 55.3 \ {\rm K/W} \end{split}$$

As a result, the PCB design must ensure a thermal resistance  $R_{\rm thJA}$  lower than 55.3 K/W. By considering TLE42994E (PG-SSOP-14 EP package) and according to "Thermal Resistance" on Page 13, at least 600 mm² heatsink area is needed on the FR4 1s0p PCB, or the FR4 2s2p board can be used.

### 6.4 Reverse Polarity Protection

TLE42994 is self protected against reverse polarity faults and allows negative supply voltage. External reverse polarity diode is not needed. However, the absolute maximum ratings of the device as specified in "Absolute Maximum Ratings" on Page 11 must be kept.

The reverse voltage causes several small currents to flow into the IC hence increasing its junction temperature. As the thermal shut down circuitry does not work in the reverse polarity condition, designers have to consider this in their thermal design.

**Package Outlines**

## 7 Package Outlines

Figure 12 PG-DSO-8

#### **Package Outlines**

Figure 13 PG-DSO-14

**Package Outlines**

Figure 14 PG-SSOP-14 exposed pad

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

Rev. 1.2, 2014-07-03

**Revision History**

## 8 Revision History

| Revision       | Date       | Changes                                                                                                                                                                                                                                                        |

|----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2            | 2014-07-03 | Application information added. PG-SSOP-14 EP package outline updated.                                                                                                                                                                                          |

| 1.1 2009-05-19 |            | Updated version Data Sheet:                                                                                                                                                                                                                                    |

|                |            | Typing error corrected in <b>Chapter 5.2</b> in conditions for graph "Output Capacitor Series Resistor ESR( $C_Q$ ) versus Output Current $I_Q$ " on Page 17: "10 $\mu$ F" corrected to "22 $\mu$ F", no change done in specification of electrical parameters |

| 1.0            | 2008-12-04 | initial version Data Sheet                                                                                                                                                                                                                                     |

Edition 2014-07-03

Published by Infineon Technologies AG 81726 Munich, Germany © 2014 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Linear Voltage Regulators category:

Click to view products by Infineon manufacturer:

Other Similar products are found below:

LV56831P-E LV5684PVD-XH MCDTSA6-2R L7815ACV-DG LV56801P-E TLE42794G L78L05CZ/1SX L78LR05DL-MA-E 636416C 714954EB LV5680P-E L78M15CV-DG L79M05T-E TLS202A1MBVHTSA1 L78LR05D-MA-E NCV317MBTG NTE7227 NCV78M09BDTRKG LV5680NPVC-XH LT1054CN8 ME6208A50M3G SL7533-8 ME6231A50M3G ME6231A50PG ME6231C50M5G AMS1117S-3.3 AMS1117-5.0 AMS1117S-5.0 AMS1117-3.3 MD5118 MD5121 MD5127 MD5128 MD5130 MD5144 MD5150 MD5115 MD5125 MD5136 MD5140 MD5110 MD52E18WB6 MD52E33WB6 MD52E15QA3 MD52E21QA3 MD52E25QA3 MD52E28QA3 MD52E30QA3 MD52E33QA3 MD52E36QA3