#### **GMR-Based Angle Sensor**

#### 1 Overview

#### **Features**

- Giant Magneto Resistance (GMR)-based principle

- Integrated magnetic field sensing for angle measurement

- 360° angle measurement with revolution counter and angle speed measurement

- Two separate highly accurate single bit SD-ADC

- 15 bit representation of absolute angle value on the output (resolution of 0.01°)

- 16 bit representation of sine / cosine values on the interface

- Max. 1.0° angle error over lifetime and temperature-range with activated auto-calibration

- Bi-directional SSC Interface up to 8 Mbit/s

- Supports Safety Integrity Level (SIL) with diagnostic functions and status information

- Interfaces: SSC, PWM, Incremental Interface (IIF), Hall Switch Mode (HSM), Short PWM Code (SPC, based on SENT protocol defined in SAE J2716)

- Output pins can be configured (programmed or pre-configured) as push-pull or open-drain

- Bus mode operation of multiple sensors on one line is possible with SSC or SPC interface

- 0.25 μm CMOS technology

- Automotive qualified: -40°C to 150°C (junction temperature)

- ESD > 4 kV (HBM)

- RoHS compliant (Pb-free package)

- Halogen-free

#### PRO-SIL™ Features

- Test vectors switchable to ADC input (activated via SSC interface)

- Inversion or combination of filter input streams (activated via SSC interface)

- Data transmission check via 8-bit Cyclic Redundancy Check (CRC) for SSC communication and 4-bit CRC nibble for SPC interface

- Built-in Self-test (BIST) routines for ISM, CORDIC, CCU, ADCs run at startup

- Two independent active interfaces possible

- Overvoltage and undervoltage detection

#### Sint Busea / ingle Se

Overview

#### Potential applications

The TLE5012B GMR-based angle sensor is designed for angular position sensing in automotive applications such as:

- Electrical commutated motor (e.g. used in Electric Power Steering (EPS))

- Rotary switches

- Steering angle measurements

- · General angular sensing

#### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

#### **Description**

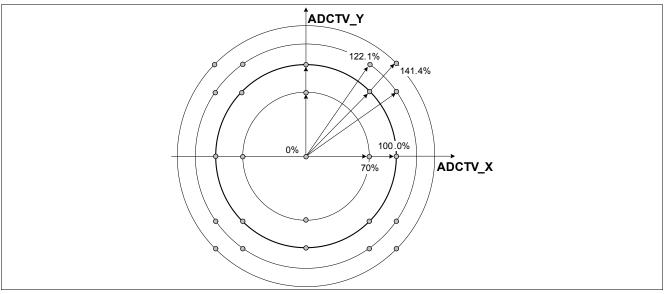

The TLE5012B is a 360° angle sensor that detects the orientation of a magnetic field. This is achieved by measuring sine and cosine angle components with monolithic integrated Giant Magneto Resistance (iGMR) elements. These raw signals (sine and cosine) are digitally processed internally to calculate the angle orientation of the magnetic field (magnet).

The TLE5012B is a pre-calibrated sensor. The calibration parameters are stored in laser fuses. At start-up the values of the fuses are written into flip-flops, where these values can be changed by the application-specific parameters. Further precision of the angle measurement over a wide temperature range and a long lifetime can be improved by enabling an optional internal autocalibration algorithm.

Data communications are accomplished with a bi-directional Synchronous Serial Communication (SSC) that is SPI-compatible. The sensor configuration is stored in registers, which are accessible by the SSC interface.

Additionally four other interfaces are available with the TLE5012B: Pulse-Width-Modulation (PWM) Protocol, Short-PWM-Code (SPC) Protocol, Hall Switch Mode (HSM) and Incremental Interface (IIF). These interfaces can be used in parallel with SSC or alone. Pre-configured sensor derivates with different interface settings are available (see Table 1 and Chapter 5).

Online diagnostic functions are provided to ensure reliable operation.

Table 1 Derivate ordering codes

| Product type   | Marking  | Ordering code | Package  |

|----------------|----------|---------------|----------|

| TLE5012B E1000 | 012B1000 | SP001166960   | PG-DSO-8 |

| TLE5012B E3005 | 012B3005 | SP001166964   | PG-DSO-8 |

| TLE5012B E5000 | 012B5000 | SP001166968   | PG-DSO-8 |

| TLE5012B E5020 | 012B5020 | SP001166972   | PG-DSO-8 |

| TLE5012B E9000 | 012B9000 | SP001166998   | PG-DSO-8 |

Note: See Chapter 5 for description of derivates.

#### TLE5012B GMR-Based Angle Sensor

# **Table of Contents**

| 1       | Overview                                                | 1    |

|---------|---------------------------------------------------------|------|

| 2       | Functional description                                  | 5    |

| 2.1     | Block diagram                                           | . 5  |

| 2.2     | Functional block description                            | . 5  |

| 2.2.1   | Internal power supply                                   | . 5  |

| 2.2.2   | Oscillator and PLL                                      | . 5  |

| 2.2.3   | SD-ADC                                                  | . 6  |

| 2.2.4   | Digital Signal Processing Unit                          | . 6  |

| 2.2.5   | Interfaces                                              | . 6  |

| 2.2.6   | Safety features                                         | . 6  |

| 2.3     | Sensing principle                                       | . 7  |

| 2.4     | Pin configuration                                       | . 9  |

| 2.5     | Pin description                                         | . 9  |

| 3       | Application circuits                                    | . 10 |

| 3.1     | IIF interface and SSC (IIF in push-pull configuration)  |      |

| 3.2     | HSM interface and SSC (HSM in push-pull configuration)  |      |

| 3.3     | HSM interface and SSC (HSM in open-drain configuration) |      |

| 3.4     | PWM interface (push-pull configuration)                 | 12   |

| 3.5     | PWM interface (open-drain configuration)                | 12   |

| 3.6     | SPC interface                                           | 13   |

| 3.7     | SSC interface (push-pull configuration)                 | 13   |

| 3.8     | SSC interface (open-drain configuration)                | 14   |

| 3.9     | Sensor supply in bus mode                               | 14   |

| 4       | Specification                                           | . 16 |

| 4.1     | Absolute maximum ratings                                |      |

| 4.2     | Operating range                                         |      |

| 4.3     | Characteristics                                         |      |

| 4.3.1   | Input/Output characteristics                            | 18   |

| 4.3.2   | ESD protection                                          | 20   |

| 4.3.3   | GMR parameters                                          | 20   |

| 4.3.4   | Angle performance                                       | 21   |

| 4.3.5   | Autocalibration                                         | 22   |

| 4.3.6   | Signal processing                                       | 23   |

| 4.3.7   | Clock supply (CLK timing definition)                    | 25   |

| 4.4     | Interfaces                                              |      |

| 4.4.1   | Synchronous Serial Communication (SSC)                  | 26   |

| 4.4.1.1 | SSC timing definition                                   | 26   |

| 4.4.1.2 | SSC data transfer                                       | 28   |

| 4.4.2   | Pulse Width Modulation (PWM) interface                  |      |

| 4.4.3   | Short PWM Code (SPC)                                    |      |

| 4.4.3.1 | Unit time setup                                         |      |

| 4.4.3.2 | Master trigger pulse requirements                       |      |

| 4.4.3.3 | Checksum nibble details                                 |      |

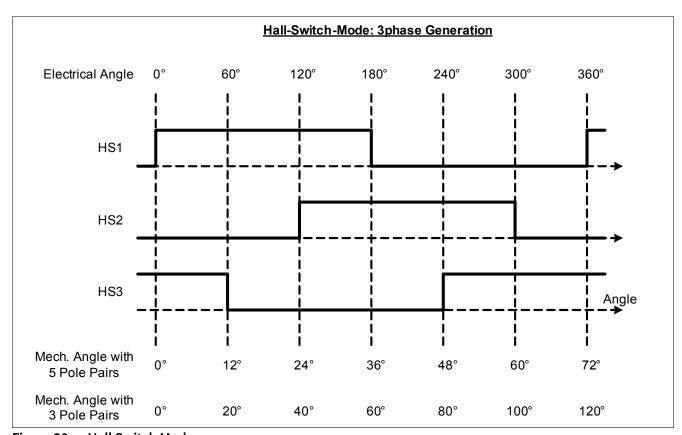

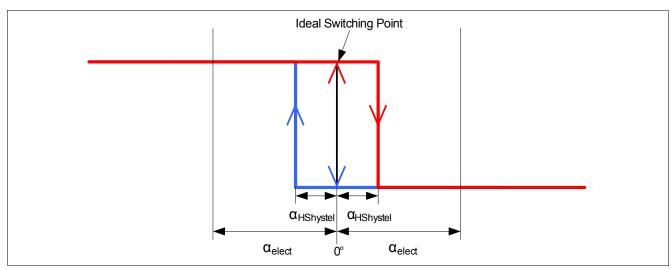

| 4.4.4   | Hall Switch Mode (HSM)                                  |      |

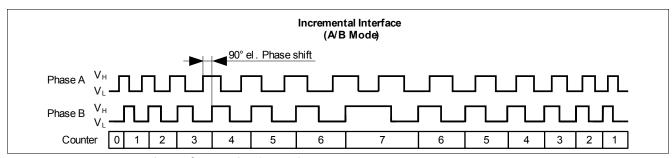

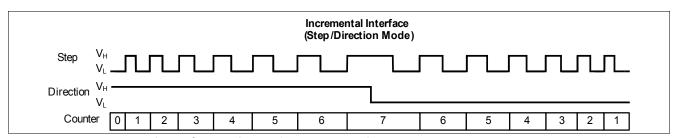

| 4.4.5   | Incremental Interface (IIF)                             | 40   |

#### **GMR-Based Angle Sensor**

| 7     | Revision history                       | 50 |

|-------|----------------------------------------|----|

| 6.5   | Marking                                | 49 |

| 6.4   | Packing                                | 49 |

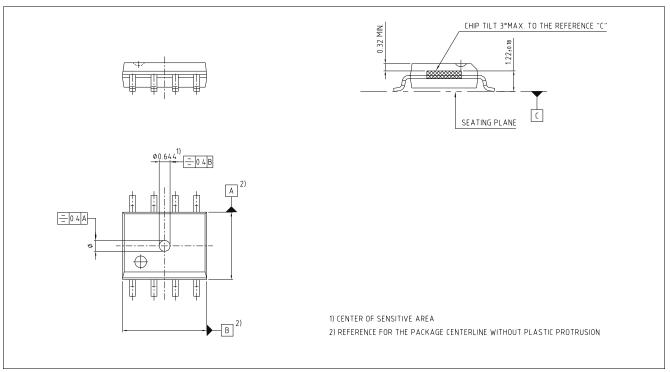

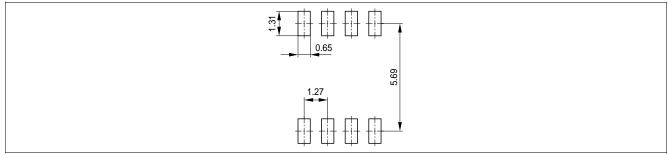

| 6.3   | Footprint                              | 48 |

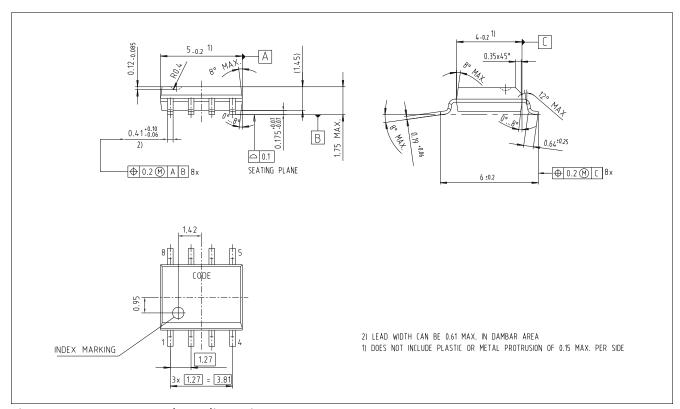

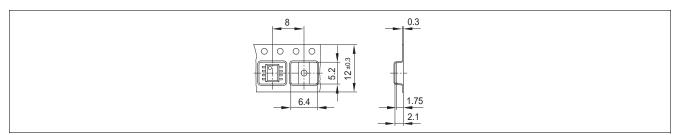

| 6.2   | Package outline                        | 47 |

| 6.1   | Package parameters                     | 47 |

| 6     | Package information                    | 47 |

| 5.5   | SPC-type: E9000                        | 46 |

| 5.4   | PWM-type: E5020                        |    |

| 5.3   | PWM-type: E5000                        | 45 |

| 5.2   | HSM-type: E3005                        | 45 |

| 5.1   | IIF-type: E1000                        |    |

| 5     | Pre-configured derivates               | 45 |

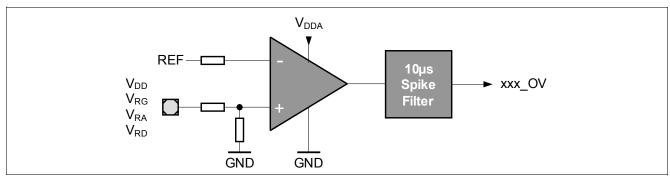

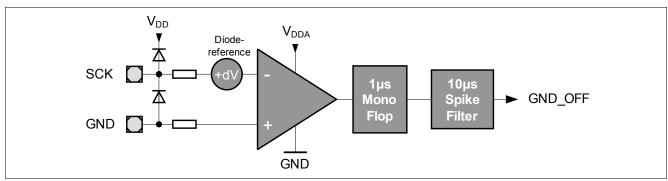

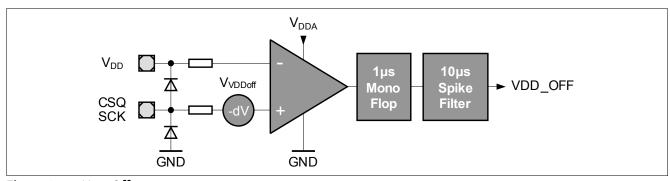

| 4.6.4 | V <sub>DD</sub> - Off comparator       | 44 |

| 4.6.3 | GND - Off comparator                   |    |

| 4.6.2 | $V_{	extsf{DD}}$ overvoltage detection |    |

| 4.6.1 | Internal supply voltage comparators    | 43 |

| 4.6   | Supply monitoring                      | 43 |

| 4.5.1 | ADC test vectors                       | 42 |

| 4.5   | Test mechanisms                        | 42 |

#### 2 Functional description

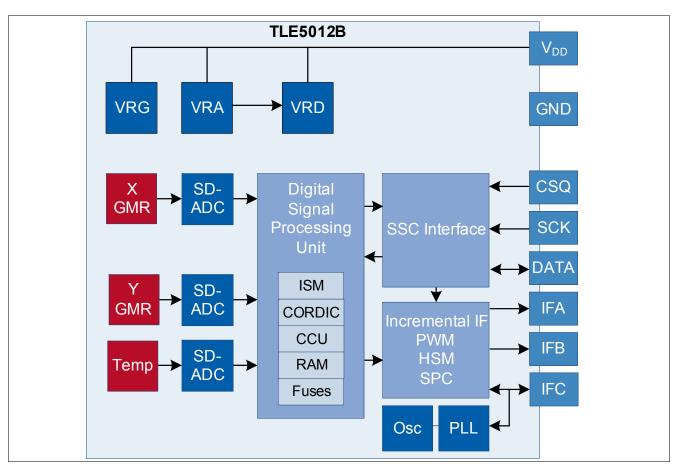

#### 2.1 Block diagram

Figure 1 TLE5012B block diagram

#### 2.2 Functional block description

#### 2.2.1 Internal power supply

The internal stages of the TLE5012B are supplied with several voltage regulators:

- GMR Voltage Regulator, VRG

- · Analog Voltage Regulator, VRA

- Digital Voltage Regulator, VRD (derived from VRA)

These regulators are directly connected to the supply voltage  $V_{DD}$ .

#### 2.2.2 Oscillator and PLL

The digital clock of the TLE5012B is given by the Phase-Locked Loop (PLL), which is by default fed by an internal oscillator. In order to synchronize the TLE5012B with other ICs in a system, the TLE5012B can be configured via SSC interface to use an external clock signal supplied on the IFC pin as source for the PLL, instead of the internal clock. External clock mode is only available in PWM or SPC interface configuration.

#### **GMR-Based Angle Sensor**

#### **Functional description**

#### 2.2.3 SD-ADC

The Sigma-Delta Analog-Digital-Converters (SD-ADC) transform the analog GMR voltages and temperature voltage into the digital domain.

#### 2.2.4 Digital Signal Processing Unit

The Digital Signal Processing Unit (DSPU) contains the:

- Intelligent State Machine (ISM), which does error compensation of offset, offset temperature drift, amplitude synchronicity and orthogonality of the raw signals from the GMR bridges, and performs additional features such as auto-calibration, prediction and angle speed calculation

- COordinate Rotation Digital Computer (CORDIC), which contains the trigonometric function for angle calculation

- Capture Compare Unit (CCU), which is used to generate the PWM and SPC signals

- · Random Access Memory (RAM), which contains the configuration registers

- Laser Fuses, which contain the calibration parameters for the error-compensation and the IC default configuration, which is loaded into the RAM at startup

#### 2.2.5 Interfaces

Bi-directional communication with the TLE5012B is enabled by a three-wire SSC interface. In parallel to the SSC interface, one secondary interface can be selected, which is available on the IFA, IFB, IFC pins:

- PWM

- Incremental Interface

- Hall Switch Mode

- Short PWM Code

By using pre-configured derivates (see Chapter 5), the TLE5012B can also be operated with the secondary interface only, without SSC communication.

#### 2.2.6 Safety features

The TLE5012B offers a multiplicity of safety features to support the Safety Integrity Level (SIL) and it is a PRO-SIL™ product.

Safety features are:

- Test vectors switchable to ADC input (activated via SSC interface)

- Inversion or combination of filter input streams (activated via SSC interface)

- Data transmission check via 8-bit Cyclic Redundancy Check (CRC) for SSC communication and 4-bit CRC nibble for SPC interface

- Built-in Self-test (BIST) routines for ISM, CORDIC, CCU, ADCs run at startup

- Two independent active interfaces possible

- Overvoltage and undervoltage detection

#### Disclaimer

PRO-SIL™ is a Registered Trademark of Infineon Technologies AG.

The PRO-SIL™ Trademark designates Infineon products which contain SIL Supporting Features.

SIL Supporting Features are intended to support the overall System Design to reach the desired SIL (according to IEC61508) or A-SIL (according to ISO26262) level for the Safety System with high efficiency.

#### **GMR-Based Angle Sensor**

#### **Functional description**

SIL respectively A-SIL certification for such a System has to be reached on system level by the System Responsible at an accredited Certification Authority.

SIL stands for Safety Integrity Level (according to IEC 61508)

A-SIL stands for Automotive-Safety Integrity Level (according to ISO 26262)

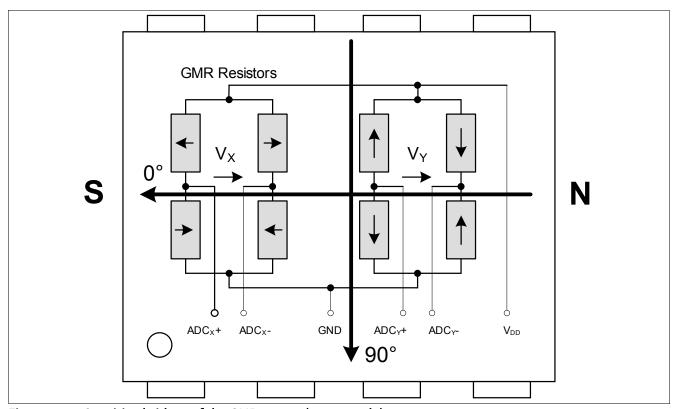

#### 2.3 Sensing principle

The Giant Magneto Resistance (GMR) sensor is implemented using vertical integration. This means that the GMR-sensitive areas are integrated above the logic part of the TLE5012B device. These GMR elements change their resistance depending on the direction of the magnetic field.

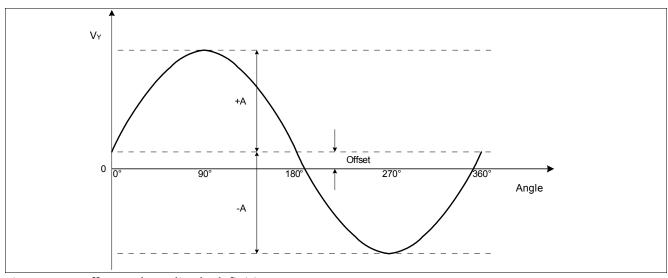

Four individual GMR elements are connected to one Wheatstone sensor bridge. These GMR elements sense one of two components of the applied magnetic field:

- X component, V<sub>x</sub> (cosine) or the

- Y component, V<sub>v</sub> (sine)

With this full-bridge structure the maximum GMR signal is available and temperature effects cancel out each other.

Figure 2 Sensitive bridges of the GMR sensor (not to scale)

Attention: Due to the rotational placement inaccuracy of the sensor IC in the package, the sensors 0° position may deviate by up to 3° from the package edge direction indicated in Figure 2.

In Figure 2, the arrows in the resistors represent the magnetic direction which is fixed in the reference layer. If the external magnetic field is parallel to the direction of the Reference Layer, the resistance is minimal. If they are anti-parallel, resistance is maximal.

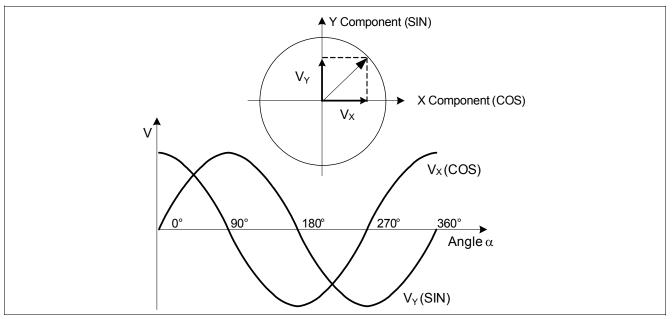

The output signal of each bridge is only unambiguous over 180° between two maxima. Therefore two bridges are oriented orthogonally to each other to measure 360°.

#### **Functional description**

With the trigonometric function ARCTAN2, the true 360° angle value is calculated out of the raw X and Y signals from the sensor bridges.

Figure 3 Ideal output of the GMR sensor bridges

**Functional description**

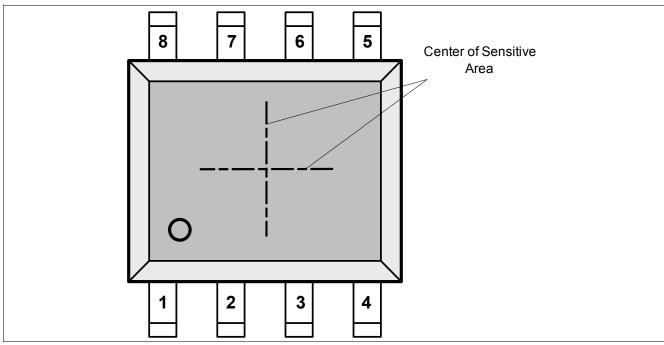

# 2.4 Pin configuration

Figure 4 Pin configuration (top view)

## 2.5 Pin description

Table 2 Pin Description

| Pin No. | Symbol                           | In/Out | Function                                                                                        |

|---------|----------------------------------|--------|-------------------------------------------------------------------------------------------------|

| 1       | IFC                              | I/O    | Interface C:                                                                                    |

|         | (CLK / IIF_IDX / HS3)            |        | External Clock <sup>1)</sup> / IIF Index / Hall Switch Signal 3                                 |

| 2       | SCK                              | I      | SSC Clock                                                                                       |

| 3       | CSQ                              | I      | SSC Chip Select                                                                                 |

| 4       | DATA                             | I/O    | SSC Data                                                                                        |

| 5       | IFA<br>(IIF_A / HS1 / PWM / SPC) | I/O    | Interface A: IIF Phase A / Hall Switch Signal 1 / PWM / SPC output (input for SPC trigger only) |

| 6       | V <sub>DD</sub>                  | -      | Supply Voltage                                                                                  |

| 7       | GND                              | -      | Ground                                                                                          |

| 8       | IFB<br>(IIF_B / HS2)             | 0      | Interface B: IIF Phase B / Hall Switch Signal 2                                                 |

<sup>1)</sup> External clock feature is not available in IIF or HSM interface mode.

## 3 Application circuits

The application circuits in this chapter show the various communication possibilities of the TLE5012B. The pin output mode configuration is device-specific and it can be either push-pull or open-drain. The bit IFAB\_OD (register IFAB, 0DH) indicates the output mode for the IFA, IFB and IFC pins. The SSC pins are by default push-pull (bit SSC\_OD, register MOD\_3, 09H). Every application circuits below are using otherwise specified SSC with push-pull configuration and the internal clock.

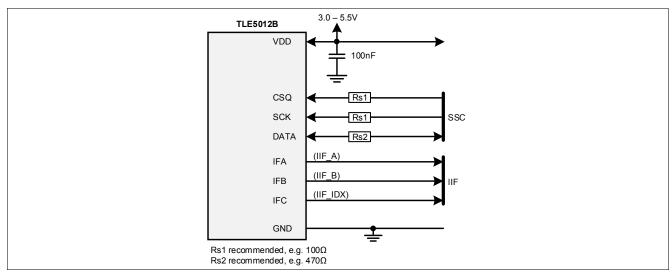

#### 3.1 IIF interface and SSC (IIF in push-pull configuration)

**Figure 5** shows a block diagram of a TLE5012B with Incremental Interface (IIF) and SSC interface. The derivate TLE5012B - E1000 is by default configured with push-pull IFA (IIF\_A), IFB (IIF\_B) and IFC (IIF\_IDX) pins. When the output pins are configurated as open-drain, three pull-up resistors should be added (e.g.  $2K2\Omega$ ) between the data lines and VDD.

Figure 5 Application circuit for TLE5012B with IIF interface and SSC

# **(infi**

**Application circuits**

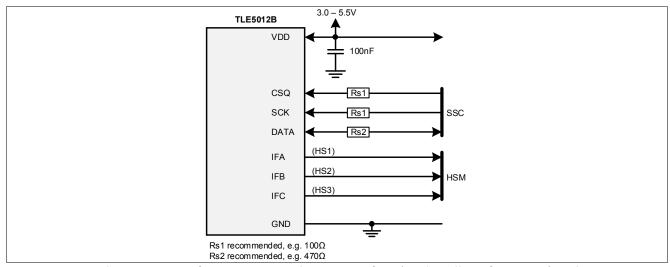

#### 3.2 HSM interface and SSC (HSM in push-pull configuration)

Figure 6 shows a block diagram of the TLE5012B with Hall Switch Mode (HSM) and SSC interface. The derivate TLE5012B - E3005 is by default configurated with push-pull IFA (HS1), IFB (HS2) and IFC (HS3) pins.

Figure 6 Application circuit for TLE5012B with HSM interface (push-pull configuration) and SSC

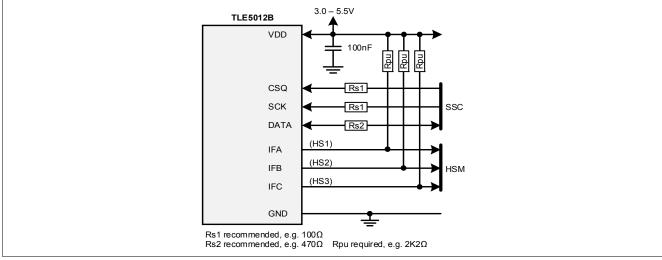

#### 3.3 HSM interface and SSC (HSM in open-drain configuration)

As shown in Figure 7 when IFA, IFB and IFC are configurated via the SSC interface as open drain pins, three pull-up resistors (Rpu) should be added on the output lines.

Figure 7 Application circuit for TLE5012B with HSM interface (open-drain configuration) and SSC

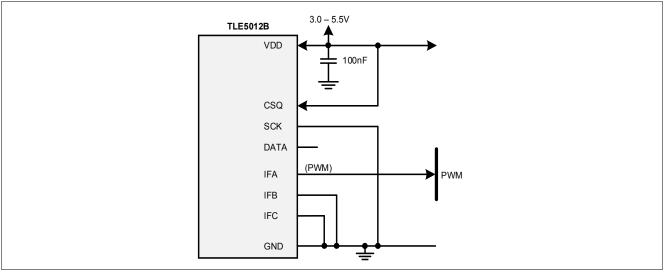

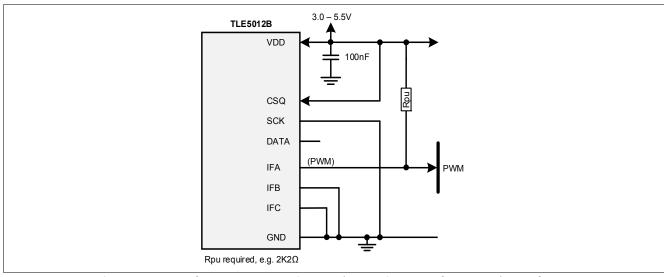

#### 3.4 PWM interface (push-pull configuration)

The TLE5012B can be configured with PWM only (Figure 8). The derivate TLE5012B - E5000 is by default configurated with push-pull configuration for IFA (PWM) pin. Internal pull-up resistors are always available for DATA and CSQ pins (see Table 7). It is recommended to connect CSQ pin to VDD to provide a high level and avoid unintentional activation of the SSC interface. DATA pin should be left open. The figure below shows a typical implementation of the TLE5012B - E5000.

Figure 8 Application circuit for TLE5012B with PWM (push-pull configuration) interface

#### 3.5 PWM interface (open-drain configuration)

The TLE5012B - E5020 is also a PWM derivate but with open drain for IFA (PWM) pin. A pull-up resistor (e.g.  $2.2 \, \mathrm{k}\Omega$ ) should be added between the IFA line and VDD, as shown in **Figure 9**. Internal pull-up resistors are always available for DATA and CSQ pins (see **Table 7**). It is recommended to connect CSQ pin to VDD to provide a strong level and avoid unintentional activation of the SSC interface. DATA pin should be left open. The figure below shows a typical implementation of the TLE5012B - E5020.

Figure 9 Application circuit for TLE5012B with PWM (open-drain configuration) interface

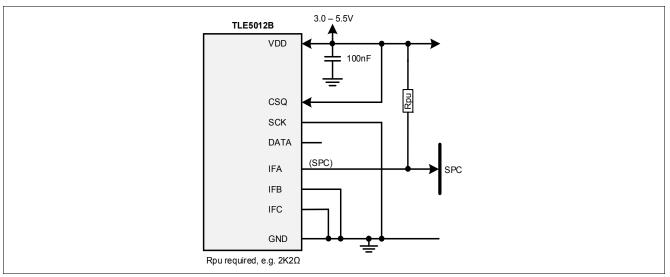

#### 3.6 SPC interface

The TLE5012B can be configured with SPC only (Figure 10). This is only possible with the TLE5012B - E9000 derivate, which is by default configurated with an open-drain IFA (SPC) pin.

In **Figure 10** the IFC (S\_NR[1]) and SCK (S\_NR[0]) pins are set to ground to generate the slave number (S\_NR) 0D (or 00B). In case of SCK (S\_NR[0]) needs to be set to VDD to generate another slave address, CSQ pin should be set to ground instead. Internal pull-up resistors are always available for DATA and CSQ pins (see **Table 7**). DATA pin should be left open. Since SCK and CSQ pins should have opposite level, it is not recommended to use the SSC interface in parallel.

Figure 10 Application circuit for TLE5012B with SPC interface

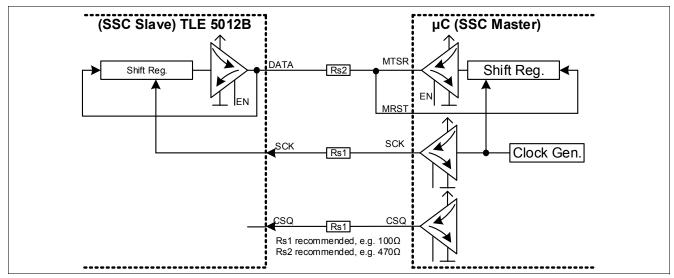

#### 3.7 SSC interface (push-pull configuration)

In Figure 5, Figure 6 and Figure 7 the SSC interface has the default push-pull configuration (see details in Figure 11). A series resistor on the DATA line is recommended to limit the current in erroneous cases (e.g. the sensor pushes high and the microcontroller pulls low at the same time or vice versa). Resistors on SCK and CSQ lines are recommended in case of disturbances or noise.

Figure 11 SSC interface with push-pull configuration (high-speed application)

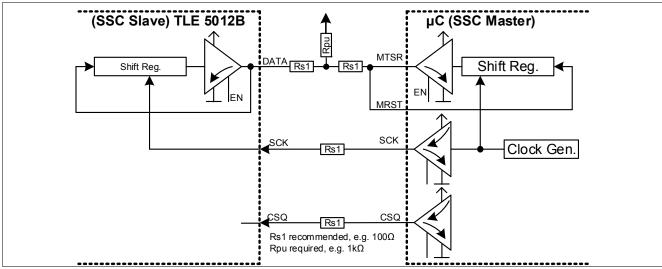

#### 3.8 SSC interface (open-drain configuration)

It is possible to use an open-drain configuration for the DATA line. This setup can be used to communicate with a microcontroller in a bus system, together with other SSC slaves (e.g. two TLE5012B devices for redundancy reasons). This mode can be activated using the bit SSC\_OD.

Even though, push-pull configuration in a bus system is also possible since the addressing of the sensor is performed with CSQ pin.

The open-drain configuration can be seen in **Figure 12**. Series resistors on the DATA line are recommended to limit the current in erroneous cases. Resistors on SCK and CSQ lines are recommended in case of disturbances or noise A pull-up resistor of typ. 1 k $\Omega$  is required on the DATA line.

Figure 12 SSC interface with open-drain configuration (bus systems)

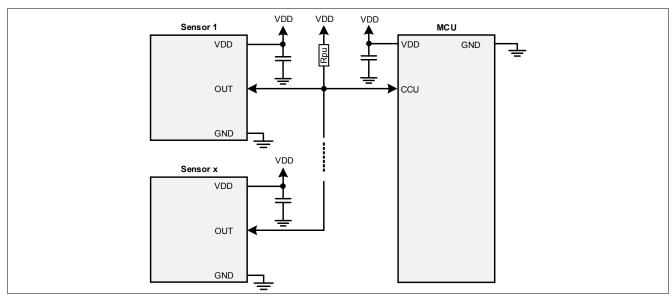

#### 3.9 Sensor supply in bus mode

When using two or more devices in a bus configuration (SSC or SPC interface). It is recommended to use the same supply for every sensors connected to the bus. In case of a power loss the unpowered device is sinking current through the OUT pin. Depending on the external circuitry the additional current flow might disturb the bus behavior.

The figure below (Figure 13) shows a typical implementation of a bus mode using SPC interface. External components such as EMC filter or additional series resistors are not represented for clarity purpose. Only the pull-up resistor Rpu is shown.

Figure 13 Sensors' supply in bus mode

**Specification**

#### **Specification** 4

#### 4.1 Absolute maximum ratings

Table 3 Absolute maximum ratings

| Parameter                                                           | Symbol            | Values |      |                       | Unit | Note or Test Condition             |

|---------------------------------------------------------------------|-------------------|--------|------|-----------------------|------|------------------------------------|

|                                                                     |                   | Min.   | Тур. | Max.                  |      |                                    |

| Voltage on $V_{\rm DD}$ pin with respect to ground ( $V_{\rm SS}$ ) | $V_{\mathrm{DD}}$ | -0.5   |      | 6.5                   | V    | Max 40 h/Lifetime                  |

| Voltage on any pin with respect to ground (V <sub>SS</sub> )        | V <sub>IN</sub>   | -0.5   |      | 6.5                   | V    |                                    |

|                                                                     |                   |        |      | V <sub>DD</sub> + 0.5 | ٧    |                                    |

| Junction temperature                                                | $T_{J}$           | -40    |      | 150                   | °C   |                                    |

|                                                                     |                   |        |      | 150                   | °C   | For 1000 h, not additive           |

| Magnetic field induction                                            | В                 |        |      | 200                   | mT   | Max. 5 min @ T <sub>A</sub> = 25°C |

|                                                                     |                   |        |      | 150                   | mT   | Max. 5 h @ T <sub>A</sub> = 25°C   |

| Storage temperature                                                 | $T_{\rm ST}$      | -40    |      | 150                   | °C   | Without magnetic field             |

Stresses above the max. values listed here may cause permanent damage to the device. Exposure Attention: to absolute maximum rating conditions for extended periods may affect device reliability. Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the device.

#### 4.2 **Operating range**

The following operating conditions must not be exceeded in order to ensure correct operation of the TLE5012B. All parameters specified in the following sections refer to these operating conditions, unless otherwise noted. Table 4 is valid for  $-40^{\circ}$ C <  $T_J$  < 150°C unless otherwise noted.

Table 4 Operating range and parameters

| Parameter                                                      | Symbol            | Values |      |      | Unit | Note or Test Condition         |

|----------------------------------------------------------------|-------------------|--------|------|------|------|--------------------------------|

|                                                                |                   | Min.   | Тур. | Max. |      |                                |

| Supply voltage                                                 | $V_{DD}$          | 3.0    | 5.0  | 5.5  | ٧    | 1)                             |

| Supply current                                                 | $I_{\mathrm{DD}}$ |        | 14   | 16   | mA   |                                |

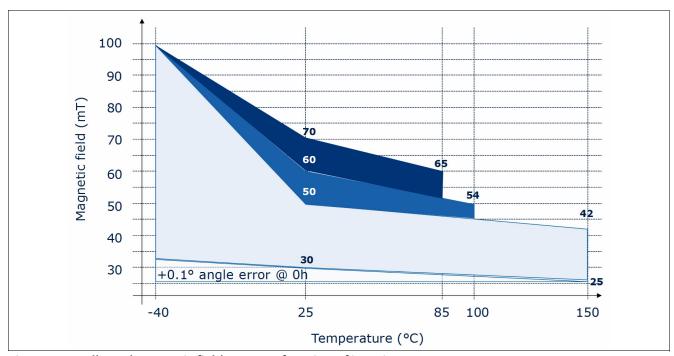

| Magnetic induction at                                          | B <sub>XY</sub>   | 30     |      | 50   | mT   | -40°C < T <sub>J</sub> < 150°C |

| $T_{\rm J} = 25^{\circ} {\rm C}^{2(3)}$                        |                   | 30     |      | 60   | mT   | -40°C < T <sub>J</sub> < 100°C |

|                                                                |                   | 30     |      | 70   | mT   | -40°C < T <sub>J</sub> < 85°C  |

| Extended magnetic induction range at $T_J = 25^{\circ}C^{2/3}$ | $B_{XY}$          | 25     |      | 30   | mT   | Additional angle error of 0.1° |

| Angle range                                                    | Ang               | 0      |      | 360  | 0    |                                |

| POR level                                                      | $V_{POR}$         | 2.0    |      | 2.9  | ٧    | Power-on reset                 |

| POR hysteresis                                                 | $V_{PORhy}$       |        | 30   |      | mV   |                                |

**Specification**

Table 4 Operating range and parameters (cont'd)

| Parameter                     | Symbol      |      | Values |      |    | Note or Test Condition                                                                                |

|-------------------------------|-------------|------|--------|------|----|-------------------------------------------------------------------------------------------------------|

|                               |             | Min. | Тур.   | Max. |    |                                                                                                       |

| Power-on time <sup>4)</sup>   | $t_{Pon}$   |      | 5      | 7    | ms | $V_{\rm DD} > V_{\rm DDmin};$                                                                         |

| Fast Reset time <sup>5)</sup> | $t_{Rfast}$ |      |        | 0.5  | ms | Fast reset is triggered by disabling startup BIST (S_BIST = 0), then enabling chip reset (AS_RST = 1) |

- 1) Directly blocked with 100-nF ceramic capacitor.

- 2) Values refer to a homogeneous magnetic field ( $B_{XY}$ ) without vertical magnetic induction ( $B_Z = 0 \text{ mT}$ ).

- 3) See Figure 14.

- During "Power-on time," write access is not permitted (except for the switch to External Clock which requires a readout as a confirmation that external clock is selected).

- 5) Not subject to production test verified by design/characterization.

The field strength of a magnet can be selected within the colored area of Figure 14. By limitation of the junction temperature, a higher magnetic field can be applied. In case of a maximum temperature  $T_J = 100^{\circ}$ C, a magnet with up to 60 mT at  $T_1 = 25$ °C is allowed.

It is also possible to widen the magnetic field range for higher temperatures. In that case, additional angle errors have to be considered.

Allowed magnetic field range as function of junction temperature. Figure 14

**Specification**

#### 4.3 Characteristics

#### 4.3.1 Input/Output characteristics

The indicated parameters apply to the full operating range, unless otherwise specified. The typical values correspond to a supply voltage  $V_{\rm DD}$  = 5.0 V and 25°C, unless individually specified. All other values correspond to -40 °C <  $T_{\rm J}$  < 150°C.

Within the register MOD\_3, the driver strength and the slope for push-pull communication can be varied depending on the sensor output. The driver strength is specified in Table 5 and the slope fall and rise time in Table 6.

Table 5 Input voltage and output currents

| Parameter                         | Symbol Values   |      | Unit | Note or Test Condition |    |                                             |

|-----------------------------------|-----------------|------|------|------------------------|----|---------------------------------------------|

|                                   |                 | Min. | Тур. | Max.                   |    |                                             |

| Input voltage                     | V <sub>IN</sub> | -0.3 |      | 5.5                    | V  |                                             |

|                                   |                 |      |      | V <sub>DD</sub> + 0.3  | V  |                                             |

| Output current (DATA-Pad)         | IQ              |      |      | -25                    | mA | PAD_DRV ='0x', sink current <sup>1)2)</sup> |

|                                   |                 |      |      | -5                     | mA | PAD_DRV ='10', sink current <sup>1)2)</sup> |

|                                   |                 |      |      | -0.4                   | mA | PAD_DRV ='11', sink current <sup>1)2)</sup> |

| Output current (IFA / IFB / IFC - | $I_{Q}$         |      |      | -15                    | mA | PAD_DRV ='0x', sink current <sup>1)2)</sup> |

| Pad)                              |                 |      |      | -5                     | mA | PAD_DRV ='1x', sink current <sup>1)2)</sup> |

<sup>1)</sup> Max. current to GND over open-drain output.

Table 6 Driver strength characteristic

| Parameter             | Symbol                       |      | Values |      |    | <b>Note or Test Condition</b>                   |

|-----------------------|------------------------------|------|--------|------|----|-------------------------------------------------|

|                       |                              | Min. | Тур.   | Max. |    |                                                 |

| Output rise/fall time | $t_{\rm fall}, t_{\rm rise}$ |      |        | 8    | ns | DATA, 50 pF,<br>PAD_DRV='00'1)2)                |

|                       |                              |      |        | 28   | ns | DATA, 50 pF,<br>PAD_DRV='01'1)2)                |

|                       |                              |      |        | 45   | ns | DATA, 50 pF,<br>PAD_DRV='10'1)2)                |

|                       |                              |      |        | 130  | ns | DATA, 50 pF,<br>PAD_DRV='11'1)2)                |

|                       |                              |      |        | 15   | ns | IFA/IFB, 20 pF,<br>PAD_DRV='0x' <sup>1)2)</sup> |

|                       |                              |      |        | 30   | ns | IFA/IFB, 20 pF,<br>PAD_DRV='1x' <sup>1)2)</sup> |

<sup>1)</sup> Valid for push-pull output

<sup>2)</sup> At  $V_{DD} = 5 \text{ V}$ .

<sup>2)</sup> Not subject to production test - verified by design/characterization

**Specification**

Electrical parameters for 4.5 V  $< V_{DD} < 5.5 \text{ V}$ Table 7

| Parameter                       | Symbol           | Values              |      | Unit                | Note or Test Condition |                                                                                                                                    |

|---------------------------------|------------------|---------------------|------|---------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|                                 |                  | Min.                | Тур. | Max.                |                        |                                                                                                                                    |

| Input signal low-level          | $V_{L5}$         |                     |      | 0.3 V <sub>DD</sub> | V                      |                                                                                                                                    |

| Input signal high level         | V <sub>H5</sub>  | 0.7 V <sub>DD</sub> |      |                     | V                      |                                                                                                                                    |

| Output signal low-level         | V <sub>OL5</sub> |                     |      | 1                   | V                      | DATA;<br>$I_Q = -25 \text{ mA (PAD_DRV='0x')},$<br>$I_Q = -5 \text{ mA (PAD_DRV='10')},$<br>$I_Q = -0.4 \text{ mA (PAD_DRV='11')}$ |

|                                 |                  |                     |      | 1                   | V                      | IFA,B,C;<br>I <sub>Q</sub> = -15 mA (PAD_DRV='0x'),<br>I <sub>Q</sub> = -5 mA (PAD_DRV='1x')                                       |

| Pull-up current <sup>1)</sup>   | I <sub>PU</sub>  | -10                 |      | -225                | μΑ                     | CSQ                                                                                                                                |

|                                 |                  | -10                 |      | -150                | μΑ                     | DATA                                                                                                                               |

| Pull-down current <sup>2)</sup> | I <sub>PD</sub>  | 10                  |      | 225                 | μΑ                     | SCK                                                                                                                                |

|                                 |                  | 10                  |      | 150                 | μΑ                     | IFA, IFB, IFC                                                                                                                      |

<sup>1)</sup> Internal pull-ups on CSQ and DATA pin are always enabled.

Electrical parameters for  $3.0 \text{ V} < \text{V}_{DD} < 3.6 \text{ V}$ Table 8

| Parameter                       | Symbol           | Values              |      |                     | Unit | Note or Test Condition                                                                                                              |

|---------------------------------|------------------|---------------------|------|---------------------|------|-------------------------------------------------------------------------------------------------------------------------------------|

|                                 |                  | Min.                | Тур. | Max.                |      |                                                                                                                                     |

| Input signal low-level          | $V_{L3}$         |                     |      | 0.3 V <sub>DD</sub> | V    |                                                                                                                                     |

| Input signal high level         | V <sub>H3</sub>  | 0.7 V <sub>DD</sub> |      |                     | V    |                                                                                                                                     |

| Output signal low-level         | V <sub>OL3</sub> |                     |      | 0.9                 | V    | DATA;<br>$I_Q = -15 \text{ mA (PAD_DRV='0x')},$<br>$I_Q = -3 \text{ mA (PAD_DRV='10')},$<br>$I_Q = -0.24 \text{ mA (PAD_DRV='11')}$ |

|                                 |                  |                     |      | 0.9                 | V    | IFA,IFB;<br>$I_Q = -10 \text{ mA (PAD\_DRV='0x')},$<br>$I_Q = -3 \text{ mA (PAD\_DRV='1x')}$                                        |

| Pull-up current <sup>1)</sup>   | I <sub>PU</sub>  | -3                  |      | -225                | μΑ   | csQ                                                                                                                                 |

|                                 |                  | -3                  |      | -150                | μΑ   | DATA                                                                                                                                |

| Pull-down current <sup>2)</sup> | I <sub>PD</sub>  | 3                   |      | 225                 | μΑ   | SCK                                                                                                                                 |

|                                 |                  | 3                   |      | 150                 | μΑ   | IFA, IFB, IFC                                                                                                                       |

<sup>1)</sup> Internal pull-ups on CSQ and DATA pin are always enabled.

<sup>2)</sup> Internal pull-downs on IFA, IFB and IFC are enabled during startup and in open-drain mode, internal pull-down on SCK is always enabled.

<sup>2)</sup> Internal pull-downs on IFA, IFB and IFC are enabled during startup and in open-drain mode, internal pull-down on SCK is always enabled.

**Specification**

#### **ESD** protection 4.3.2

Table 9 **ESD** protection

| Parameter   | Symbol    | Values |      | Unit | Note or Test Condition |                                     |

|-------------|-----------|--------|------|------|------------------------|-------------------------------------|

|             |           | Min.   | Тур. | Max. |                        |                                     |

| ESD voltage | $V_{HBM}$ |        |      | ±4.0 | kV                     | Human Body Model <sup>1)</sup>      |

|             | $V_{SDM}$ |        |      | ±0.5 | kV                     | Socketed Device Model <sup>2)</sup> |

<sup>1)</sup> Human Body Model (HBM) according to: AEC-Q100-002.

#### 4.3.3 **GMR** parameters

All parameters apply over  $B_{XY}$  = 30 mT and  $T_A$  = 25°C, unless otherwise specified.

Table 10 **Basic GMR parameters**

| Parameter                        | Symbol         | Values |      |        | Unit   | Note or Test Condition        |

|----------------------------------|----------------|--------|------|--------|--------|-------------------------------|

|                                  |                | Min.   | Тур. | Max.   |        |                               |

| X, Y output range                | $RG_{ADC}$     |        |      | ±23230 | digits | Operating range <sup>1)</sup> |

| X, Y amplitude <sup>2)</sup>     | $A_{X}, A_{Y}$ | 6000   | 9500 | 15781  | digits | At ambient temperature        |

|                                  |                | 3922   |      | 20620  | digits | Operating range               |

| X, Y synchronicity <sup>3)</sup> | k              | 87.5   | 100  | 112.49 | %      |                               |

| X, Y offset <sup>4)</sup>        | $O_X$ , $O_Y$  | -2048  | 0    | +2047  | digits |                               |

| X, Y orthogonality error         | j              | -11.25 | 0    | +11.24 | o      |                               |

| X, Y amplitude without magnet    | $X_0, Y_0$     |        |      | +4096  | digits | Operating range <sup>1)</sup> |

<sup>1)</sup> Not subject to production test - verified by design/characterization.

4)

$$O_Y = (Y_{MAX} + Y_{MIN}) / 2$$

;  $O_X = (X_{MAX} + X_{MIN}) / 2$

Offset and amplitude definition Figure 15

<sup>2)</sup> Socketed Device Model (SDM) according to: ESDA/ANSI/ESD SP5.3.2-2008.

<sup>2)</sup> See Figure 15.

<sup>3)</sup>  $k = 100 * (A_X/A_Y)$

**Specification**

#### 4.3.4 Angle performance

After internal calculation, the sensor has a remaining error, as shown in **Table 11**. The error value refers to  $B_7 = 0$  mT and the operating conditions given in **Table 4**.

The overall angle error represents the relative angle error. This error describes the deviation from the reference line after zero-angle definition. It is valid for a static magnetic field.

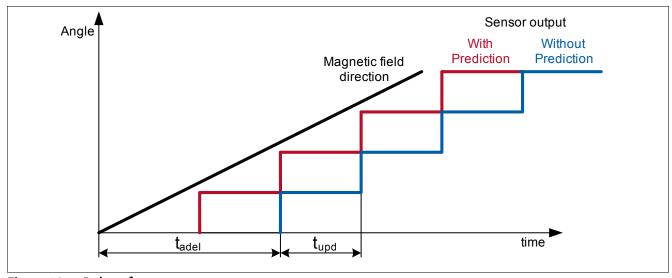

If the magnetic field is rotating during the measurement, an additional propagation error is caused by the angle delay time (see **Table 12**), which the sensor needs to calculate the angle from the raw sine and cosine values from the MR bridges. In fast-turning applications, prediction can be enabled to reduce this propagation error.

Table 11 Angle performance

| Parameter                                       | Symbol           |      | Values |      |   | Note or Test Condition                                                                                                                                                                 |

|-------------------------------------------------|------------------|------|--------|------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 |                  | Min. | Тур.   | Max. |   |                                                                                                                                                                                        |

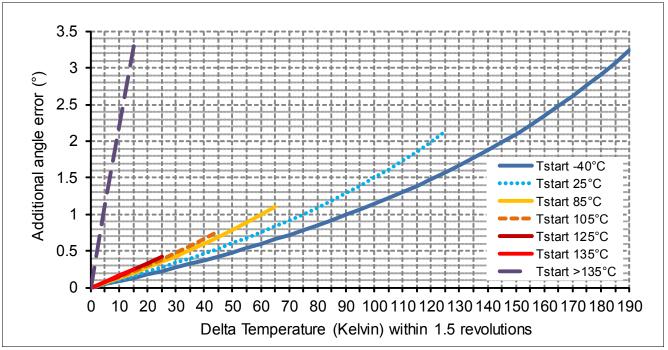

| Overall angle error (with autocalibration)      | α <sub>Err</sub> |      | 0.61)  | 1.0  | o | Including lifetime and temperature drift <sup>2)3)4)</sup> . Note: in case of temperature changes above 5 Kelvin within 1.5 revolutions refer to Figure 16 for additional angle error. |

| Overall angle error (without auto- calibration) | $\alpha_{Err}$   |      | 0.61)  | 1.3  | 0 | Including temperature drift <sup>2)3)5)</sup>                                                                                                                                          |

|                                                 |                  |      |        | 1.9  | 0 | Including lifetime and temperature drift <sup>2)3)4)</sup>                                                                                                                             |

- 1) At 25°C, B = 30 mT.

- 2) Including hysteresis error, caused by revolution direction change.

- 3) Relative error after zero angle definition.

- 4) Not subject to production test verified by design/characterization.

- 5) 0 h.

If autocalibration (see Chapter 4.3.5) is enabled and the temperature changes by more than 5 Kelvin during 1.5 revolutions an additional error has to be added to the specified angle error in Table 11. This error depends on the temperature change (Delta Temperature) as well as from the initial temperature (Tstart) as shown in Figure 16. Once the temperature stabilizes and the application completes 1.5 revolutions, then the angle error is as specified in Table 11.

For negative Delta Temperature changes (from higher to lower temperatures) the additional angle error will be smaller than the corresponding positive Delta Temperature changes (from lower to higher temperatures) shown in Figure 16. The Figure 16 applies to the worst case.

# infineon

**Specification**

Figure 16 Additional angle error for temperature changes above 5 Kelvin within 1.5 revolutions

#### 4.3.5 Autocalibration

The autocalibration enables online parameter calculation and therefore reduces the angle error due to temperature and lifetime drifts.

The TLE5012B is a pre-calibrated sensor, so autocalibration is only enabled in some devices by default. The update mode can be chosen with the AUTOCAL setting in the MOD\_2 register. The TLE5012B needs 1.5 revolutions to generate new autocalibration parameters. These parameters are continuously updated. The parameters are updated in a smooth way (one Least-Significant Bit within the chosen range or time) to avoid an angle jump on the output.

#### **AUTOCAL Modes:**

- 00: No autocalibration.

- 01: Autocalibration Mode 1. One LSB to final values within the update time t<sub>upd</sub> (depending on FIR\_MD setting).

- 10: Autocalibration Mode 2. Only one LSB update over one full parameter generation (1.5 revolutions). After update of one LSB, the autocalibration will calculate the parameters again.

- 11: Autocalibration Mode 3. One LSB to final values within an angle range of 11.25°.

**Specification**

4.3.6

Signal processing

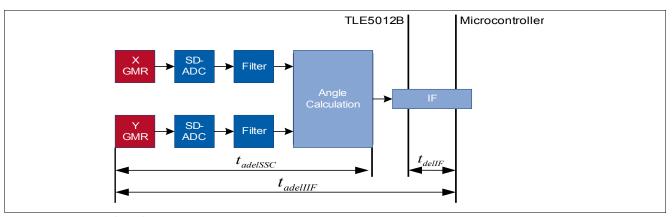

Figure 17 Signal path

The signal path of the TLE5012B is depicted in Figure 17. It consists of the GMR-bridge, ADC, filter and angle calculation. The delay time between a physical change in the GMR elements and a signal on the output depends on the filter and interface configurations. In fast turning applications, this delay causes an additional rotation speed dependent angle error.

The TLE5012B has an optional prediction feature, which serves to reduce the speed dependent angle error in applications where the rotation speed does not change abruptly. Prediction uses the difference between current and last two angle values to approximate the angle value which will be present after the delay time (see Figure 18). The output value is calculated by adding this difference to the measured value, according to Equation (4.1).

$$\alpha(t+1) = \alpha(t) + \alpha(t-1) - \alpha(t-2) \tag{4.1}$$

Figure 18 Delay of sensor output

#### **TLE5012B GMR-Based Angle Sensor**

**Specification**

Table 12 Signal processing

| Parameter                | Symbol               |      | Valu  | es   | Unit | <b>Note or Test Condition</b>        |

|--------------------------|----------------------|------|-------|------|------|--------------------------------------|

|                          |                      | Min. | Тур.  | Max. |      |                                      |

| Filter update period     | $t_{\sf upd}$        |      | 42.7  |      | μs   | FIR_MD = 1 <sup>1)</sup>             |

|                          |                      |      | 85.3  |      | μs   | FIR_MD = 2 <sup>1)</sup>             |

|                          |                      |      | 170.6 |      | μs   | FIR_MD = 3 <sup>1)</sup>             |

| Angle delay time without | $t_{ m adelSSC}$     |      | 85    | 95   | μs   | FIR_MD = 1 <sup>1)</sup>             |

| prediction <sup>2)</sup> |                      |      | 150   | 165  | μs   | FIR_MD = 2 <sup>1)</sup>             |

|                          |                      |      | 275   | 300  | μs   | FIR_MD = 3 <sup>1)</sup>             |

|                          | t <sub>adelIIF</sub> |      | 120   | 135  | μs   | FIR_MD = 1 <sup>1)</sup>             |

|                          |                      |      | 180   | 200  | μs   | $FIR\_MD = 2^{1)}$                   |

|                          |                      |      | 305   | 330  | μs   | FIR_MD = 3 <sup>1)</sup>             |

| Angle delay time with    | $t_{ m adelSSC}$     |      | 45    | 50   | μs   | FIR_MD = 1; PREDICT = 1 <sup>1</sup> |

| prediction <sup>2)</sup> |                      |      | 65    | 70   | μs   | FIR_MD = 2; PREDICT = 1 <sup>1</sup> |

|                          |                      |      | 105   | 115  | μs   | FIR_MD = 3; PREDICT = 1              |

|                          | t <sub>adelIIF</sub> |      | 75    | 90   | μs   | FIR_MD = 1; PREDICT = 1 <sup>1</sup> |

|                          |                      |      | 95    | 110  | μs   | FIR_MD = 2; PREDICT = 1 <sup>1</sup> |

|                          |                      |      | 135   | 150  | μs   | FIR_MD = 3; PREDICT = 1              |

| Angle noise (RMS)        | $N_{\rm Angle}$      |      | 0.08  |      | ٥    | FIR_MD = 1 <sup>1)</sup>             |

|                          |                      |      | 0.05  |      | 0    | FIR_MD = 2 <sup>1)</sup> (default)   |

|                          |                      |      | 0.04  |      | 0    | FIR_MD = 3 <sup>1)</sup>             |

<sup>1)</sup> Not subject to production test - verified by design/characterization.

All delay times specified in Table 12 are valid for an ideal internal oscillator frequency of 24 MHz. For the exact timing, the variation of the internal oscillator frequency has to be taken into account (see Chapter 4.3.7).

<sup>2)</sup> Valid at constant rotation speed.

**Specification**

#### 4.3.7 Clock supply (CLK timing definition)

The internal clock supply of the TLE5012B is subject to production-specific variations, which have to be considered for all timing specifications.

Table 13 Internal clock timing specification

| Parameter                     | Symbol    | Values |      |      | Unit | Note or Test Condition |

|-------------------------------|-----------|--------|------|------|------|------------------------|

|                               |           | Min.   | Тур. | Max. |      |                        |

| Digital clock                 | $f_{DIG}$ | 22.8   | 24   | 25.8 | MHz  |                        |

| Internal oscillator frequency | $f_{CLK}$ | 3.8    | 4.0  | 4.3  | MHz  |                        |

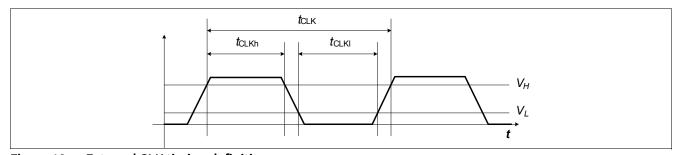

In order to fix the IC timing and synchronize the TLE5012B with other ICs in a system, it can be switched to operate with an external clock signal supplied to the IFC pin. The clock input signal must fulfill certain requirements:

- The high or low pulse width must not exceed the specified values, because the PLL needs a minimum pulse width and must be spike-filtered.

- The duty cycle factor should typically be 50%, but it can vary between 30% and 70%.

- The PLL is triggered at the positive edge of the clock. If more than 2 edges are missing, a chip reset is generated automatically and the sensor restarts with the internal clock. This is indicated by the S\_RST, and CLK\_SEL bits, and additionally by the Safety Word (see Chapter 4.4.1.2).

Figure 19 External CLK timing definition

Table 14 External clock specification

| Parameter                      | Symbol                     | Values |      |      | Unit | Note or Test Condition                |

|--------------------------------|----------------------------|--------|------|------|------|---------------------------------------|

|                                |                            | Min.   | Тур. | Max. |      |                                       |

| Input frequency                | $f_{CLK}$                  | 3.8    | 4.0  | 4.3  | MHz  |                                       |

| CLK duty cycle <sup>1)2)</sup> | <i>CLK</i> <sub>DUTY</sub> | 30     | 50   | 70   | %    |                                       |

| CLK rise time                  | t <sub>CLKr</sub>          |        |      | 30   | ns   | From V <sub>L</sub> to V <sub>H</sub> |

| CLK fall time                  | $t_{CLKf}$                 |        |      | 30   | ns   | From $V_{\rm H}$ to $V_{\rm L}$       |

- 1) Minimum duty cycle factor:  $t_{\text{CLKh(min)}} / t_{\text{CLK}}$  with  $t_{\text{CLK}} = 1 / f_{\text{CLK}}$

- 2) Maximum duty cycle factor:  $t_{CLKh(max)} / t_{CLK}$  with  $t_{CLK} = 1 / f_{CLK}$

**Specification**

#### 4.4 Interfaces

#### 4.4.1 Synchronous Serial Communication (SSC)

The 3-pin SSC interface consists of a bi-directional push-pull (tri-state on receive) or open-drain data pin (configurable with SSC\_OD bit) and the serial clock and chip-select input pins. The SSC Interface is designed to communicate with a microcontroller peer-to-peer for fast applications.

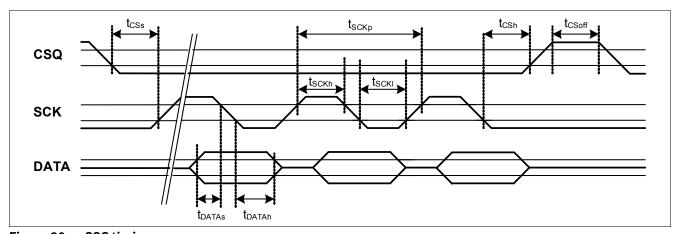

#### 4.4.1.1 SSC timing definition

Figure 20 SSC timing

#### SSC inactive time (CS<sub>off</sub>)

The SSC inactive time defines the delay time after a transfer before the TLE5012B can be selected again.

Table 15 SSC push-pull timing specification

|                       |                                                                                                                                                                                                                   | ymbol Values                                          |                                                       |                                                       | Note or Test Condition                                |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

|                       | Min.                                                                                                                                                                                                              | Тур.                                                  | Max.                                                  |                                                       |                                                       |

| $f_{\rm SSC}$         |                                                                                                                                                                                                                   | 8.0                                                   |                                                       | Mbit/s                                                | 1)                                                    |

| $t_{CSs}$             | 105                                                                                                                                                                                                               |                                                       |                                                       | ns                                                    | 1)                                                    |

| $t_{CSh}$             | 105                                                                                                                                                                                                               |                                                       |                                                       | ns                                                    | 1)                                                    |

| $t_{CSoff}$           | 600                                                                                                                                                                                                               |                                                       |                                                       | ns                                                    | SSC inactive time <sup>1)</sup>                       |

| $t_{\sf SCKp}$        | 120                                                                                                                                                                                                               | 125                                                   |                                                       | ns                                                    | 1)                                                    |

| $t_{\sf SCKh}$        | 40                                                                                                                                                                                                                |                                                       |                                                       | ns                                                    | 1)                                                    |

| t <sub>SCKI</sub>     | 30                                                                                                                                                                                                                |                                                       |                                                       | ns                                                    | 1)                                                    |

| t <sub>DATAs</sub>    | 25                                                                                                                                                                                                                |                                                       |                                                       | ns                                                    | 1)                                                    |

| t <sub>DATAh</sub>    | 40                                                                                                                                                                                                                |                                                       |                                                       | ns                                                    | 1)                                                    |

| t <sub>wr_delay</sub> | 130                                                                                                                                                                                                               |                                                       |                                                       | ns                                                    | 1)                                                    |

| $t_{CSupdate}$        | 1                                                                                                                                                                                                                 |                                                       |                                                       | μs                                                    | See Figure 24 <sup>1)</sup>                           |

|                       | 170                                                                                                                                                                                                               |                                                       |                                                       | ns                                                    | 1)                                                    |

|                       | $t_{\mathrm{CSs}}$ $t_{\mathrm{CSh}}$ $t_{\mathrm{CSoff}}$ $t_{\mathrm{SCKp}}$ $t_{\mathrm{SCKh}}$ $t_{\mathrm{SCKl}}$ $t_{\mathrm{DATAs}}$ $t_{\mathrm{DATAh}}$ $t_{\mathrm{wr\_delay}}$ $t_{\mathrm{CSupdate}}$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

<sup>1)</sup> Not subject to production test - verified by design/characterization.

## **GMR-Based Angle Sensor**

Specification

SSC open-drain timing specification Table 16

| Parameter        | Symbol                |      | Valu | Values |        | Note or Test Condition              |

|------------------|-----------------------|------|------|--------|--------|-------------------------------------|

|                  |                       | Min. | Тур. | Max.   |        |                                     |

| SSC baud rate    | $f_{SSC}$             |      | 2.0  |        | Mbit/s | Pull-up Resistor = $1 k\Omega^{1)}$ |

| CSQ setup time   | t <sub>CSs</sub>      | 300  |      |        | ns     | 1)                                  |

| CSQ hold time    | t <sub>CSh</sub>      | 400  |      |        | ns     | 1)                                  |

| CSQ off          | $t_{CSoff}$           | 600  |      |        | ns     | SSC inactive time <sup>1)</sup>     |

| SCK period       | t <sub>SCKp</sub>     | 500  |      |        | ns     | 1)                                  |

| SCK high         | t <sub>SCKh</sub>     |      | 190  |        | ns     | 1)                                  |

| SCK low          | t <sub>SCKI</sub>     |      | 190  |        | ns     | 1)                                  |

| DATA setup time  | $t_{DATAs}$           | 25   |      |        | ns     | 1)                                  |

| DATA hold time   | $t_{DATAh}$           | 40   |      |        | ns     | 1)                                  |

| Write read delay | t <sub>wr_delay</sub> | 130  |      |        | ns     | 1)                                  |

| Update time      | $t_{CSupdate}$        | 1    |      |        | μs     | See Figure 24 <sup>1)</sup>         |

| SCK off          | t <sub>SCKoff</sub>   | 170  |      |        | ns     | 1)                                  |

<sup>1)</sup> Not subject to production test - verified by design/characterization.

**Specification**

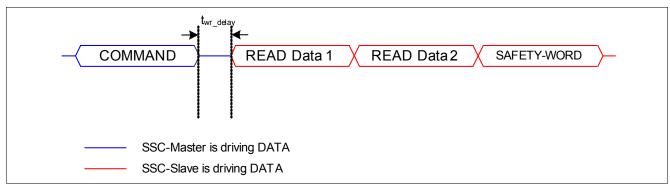

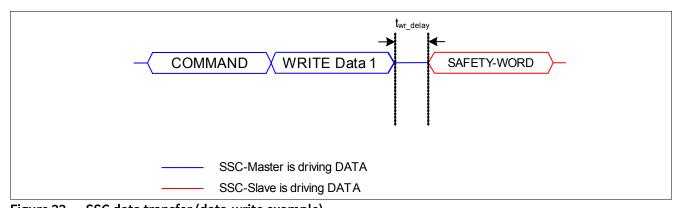

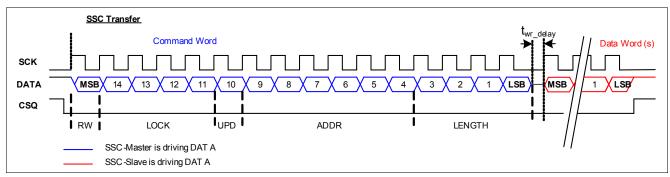

#### 4.4.1.2 SSC data transfer

The SSC data transfer is word-aligned. The following transfer words are possible:

- Command Word (to access and change operating modes of the TLE5012B)

- Data words (any data transferred in any direction)

- Safety Word (confirms the data transfer and provides status information)

Figure 21 SSC data transfer (data-read example)

Figure 22 SSC data transfer (data-write example)

#### **Command Word**

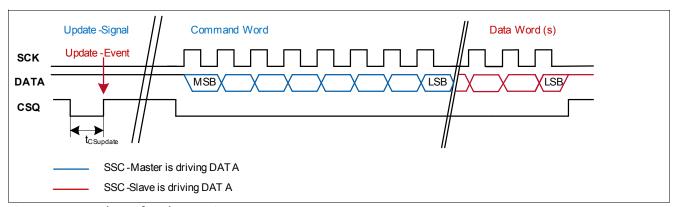

SSC Communication between the TLE5012B and a microcontroller is generally initiated by a command word. The structure of the command word is shown in Table 17. If an update is triggered by shortly pulling low CSQ without a clock on SCK a snapshot of all system values is stored in the update registers simultaneously. A read command with the UPD bit set then allows to readout this consistent set of values instead of the current values. Bits with an update buffer are marked by an "u" in the Type column in register descriptions. The initialization of such an update is described on page 30.

Table 17 Structure of the Command Word

| Name | Bits   | Description                                                                                                                                |

|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

| RW   | [15]   | Read - Write 0: Write 1: Read                                                                                                              |

| Lock | [1411] | 4-bit Lock Value<br>$0000_B$ : Default operating access for addresses 0x00:0x04<br>$1010_B$ : Configuration access for addresses 0x05:0x11 |

#### **GMR-Based Angle Sensor**

#### **Specification**

**Table 17** Structure of the Command Word (cont'd)

| Name | Bits | Description                                                                             |

|------|------|-----------------------------------------------------------------------------------------|

| UPD  | [10] | Update-Register Access 0: Access to current values 1: Access to values in update buffer |

| ADDR | [94] | 6-bit Address                                                                           |

| ND   | [30] | 4-bit Number of Data Words                                                              |

#### **Safety Word**

The safety word consists of the following bits:

Table 18 Structure of the Safety Word

| Name               | Bits       | Description                                                                                                                                                                 |  |  |  |

|--------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| STAT <sup>1)</sup> | Chip and I | Interface Status                                                                                                                                                            |  |  |  |

|                    | [15]       | Indication of chip reset or watchdog overflow (resets after readout) via SSC  0: Reset occurred  1: No reset                                                                |  |  |  |

|                    | [14]       | System error (e.g. overvoltage; undervoltage; V <sub>DD</sub> -, GND- off; ROM;) 0: Error occurred (S_VR; S_DSPU; S_OV; S_XYOL: S_MAGOL; S_FUSE; S_ROM; S_ADCT) 1: No error |  |  |  |

|                    | [13]       | Interface access error (access to wrong address; wrong lock) 0: Error occurred 1: No error                                                                                  |  |  |  |

| [12]               |            | Valid angle value (NO_GMR_A = 0; NO_GMR_XY = 0) 0: Angle value invalid 1: Angle value valid                                                                                 |  |  |  |

| RESP               | [118]      | Sensor number response indicator The sensor number bit is pulled low and the other bits are high                                                                            |  |  |  |

| CRC                | [70]       | Cyclic Redundancy Check (CRC)                                                                                                                                               |  |  |  |

<sup>1)</sup> When an error occurs, the corresponding status bit in the safety word remains "low" until the STAT register (address 00<sub>H</sub>) is read via SSC interface.

#### **Specification**

#### **Bit Types**

The types of bits used in the registers are listed here:

Table 19 Bit Types

| Abbreviation | Function | Description                                                                                                                                                                                                                                                                      |

|--------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r            | Read     | Read-only registers                                                                                                                                                                                                                                                              |

| W            | Write    | Read and write registers                                                                                                                                                                                                                                                         |

| u            | Update   | Update buffer for this bit is present. If an update is issued and the Update-Register Access bit (UPD in Command Word) is set, the immediate values are stored in this update buffer simultaneously. This allows a snapshot of all necessary system parameters at the same time. |

#### **Data communication via SSC**

Figure 23 SSC bit ordering (read example)

Figure 24 Update of update registers

The data communication via SSC interface has the following characteristics:

- The data transmission order is Most-Significant Bit (MSB) first, Last-Significant Bit (LSB) last.

- Data is put on the data line with the rising edge on SCK and read with the falling edge on SCK.

- The SSC Interface is word-aligned. All functions are activated after each transmitted word.

- After every data transfer with ND ≥ 1, the 16-bit Safety Word is appended by the TLE5012B.

- A "high" condition on the Chip Select pin (CSQ) of the selected TLE5012B interrupts the transfer immediately. The CRC calculator is automatically reset.

- After changing the data direction, a delay  $t_{wr\_delay}$  (see **Table 16**) has to be implemented before continuing the data transfer. This is necessary for internal register access.

#### **GMR-Based Angle Sensor**

#### **Specification**

- If in the Command Word the number of data is greater than 1 (ND > 1), then a corresponding number of

consecutive registers is read, starting at the address given by ADDR.

- In case an overflow occurs at address 3F<sub>H</sub>, the transfer continues at address 00<sub>H</sub>.

- If in the Command Word the number of data is zero (ND = 0), the register at the address given by ADDR is read, but no Safety Word is sent by the TLE5012B. This allows a fast readout of one register.

- At a rising edge of CSQ without a preceding data transfer (no SCK pulse, see Figure 24), the content of all

registers which have an update buffer is saved into the buffer. This procedure serves to take a snapshot of

all relevant sensor parameters at a given time. The content of the update buffer can then be read by

sending a read command for the desired register and setting the UPD bit of the Command Word to "1".

- After sending the Safety Word, the transfer ends. To start another data transfer, the CSQ has to be deselected once for at least t<sub>CSoff</sub>.

- By default, the SSC interface is set to push-pull. The push-pull driver is active only if the TLE5012B has to send data, otherwise the DATA pin is set to high-impedance.

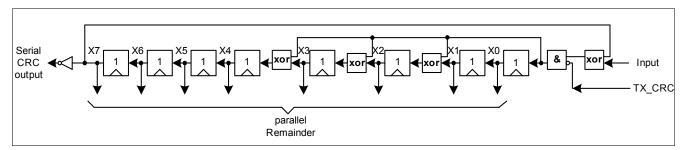

#### Cyclic Redundancy Check (CRC)

- This CRC is according to the J1850 Bus Specification.

- Every new transfer restarts the CRC generation.

- Every Byte of a transfer will be taken into account to generate the CRC (also the sent command(s)).

- Generator polynomial: X8+X4+X3+X2+1, but for the CRC generation the fast-CRC generation circuit is used (see Figure 25).

- The seed value of the fast CRC circuit is '111111111<sub>B</sub>'.

- The remainder is inverted before transmission.

Figure 25 Fast CRC polynomial division circuit

**Specification**

#### 4.4.2 Pulse Width Modulation (PWM) interface

The Pulse Width Modulation (PWM) interface can be selected via SSC (IF\_MD = '01').

The PWM update rate can be programmed within the register 0E<sub>H</sub> (IFAB\_RES) in the following steps:

- ~0.25 kHz with 12-bit resolution

- ~0.5 kHz with 12-bit resolution

- ~1.0 kHz with 12-bit resolution

- ~2.0 kHz with 12-bit resolution

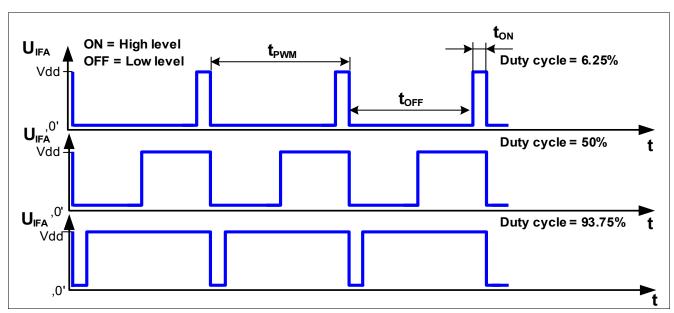

PWM uses a square wave with constant frequency whose duty cycle is modulated according to the last measured angle value (AVAL register).

**Figure 26** shows the principal behavior of a PWM with various duty cycles and the definition of timing values. The duty cycle of a PWM is defined by the following general formulas:

$$Duty Cycle = \frac{t_{on}}{t_{PWM}}$$

$$t_{PWM} = t_{on} + t_{off}$$

$$f_{PWM} = \frac{1}{t_{PWM}}$$

(4.2)

The duty cycle range between 0 - 6.25% and 93.75 - 100% is used only for diagnostic purposes. In case the sensor detects an error, the corresponding error bit in the Status register is set and the PWM duty cycle goes to the lower (0 - 6.25%) or upper (93.75 - 100%) diagnostic range, depending on the kind of error (see "Output duty cycle range" in Table 20). Except for an S\_ADCT error, an error is only indicated by the corresponding diagnostic duty-cycle as long as it persists, but at least once. However the value in the status register will remain until a read-out via the SSC interface or a chip reset is performed. An S\_ADCT error on the other side will be transmitted until the next chip reset. This fail-safe diagnostic function can be disabled via the MOD\_4 register.

Sensors with preset PWM are available as TLE5012B E50x0.

Figure 26 Typical example of a PWM signal

#### **GMR-Based Angle Sensor**

**Specification**

Table 20 PWM interface

| Parameter                | Symbol            |      | Values |       |    | Note or Test Condition                                                   |

|--------------------------|-------------------|------|--------|-------|----|--------------------------------------------------------------------------|

|                          |                   | Min. | Тур.   | Max.  |    |                                                                          |

| PWM output frequencies   | $f_{PWM1}$        | 232  | 244    | 262   | Hz | 1)                                                                       |

| (Selectable by IFAB_RES) | $f_{\text{PWM2}}$ | 464  | 488    | 525   | Hz | 1)                                                                       |

|                          | $f_{\text{PWM3}}$ | 929  | 977    | 1050  | Hz | 1)                                                                       |

|                          | $f_{PWM4}$        | 1855 | 1953   | 2099  | Hz | 1)                                                                       |

| Output duty cycle range  | DY <sub>PWM</sub> | 6.25 |        | 93.75 | %  | Absolute angle <sup>1)</sup>                                             |

|                          |                   |      | 2      |       | %  | Electrical Error (S_RST;<br>S_VR) <sup>1)</sup>                          |

|                          |                   |      | 98     |       | %  | System error (S_FUSE;<br>S_OV; S_XYOL; S_MAGOL;<br>S_ADCT) <sup>1)</sup> |

|                          |                   | 0    |        | 1     | %  | Short to GND <sup>1)</sup>                                               |

|                          |                   | 99   |        | 100   | %  | Short to V <sub>DD</sub> , power loss <sup>1)</sup>                      |

<sup>1)</sup> Not subject to production test - verified by design/characterization.

The PWM frequency is derived from the digital clock via:

$$f_{\text{PWM}} = \frac{f_{\text{DIG}} * 2^{\text{IFAB\_RES}}}{24 * 4096}$$

(4.3)

The min/max values given in **Table 20** take into account the internal digital clock variation specified in **Chapter 4.3.7**. If external clock is used, the variation of the PWM frequency can be derived from the variation of the external clock using **Equation (4.3)**.

**Specification**

#### 4.4.3 Short PWM Code (SPC)

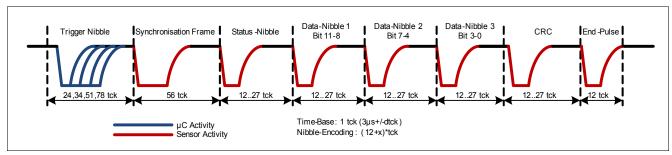

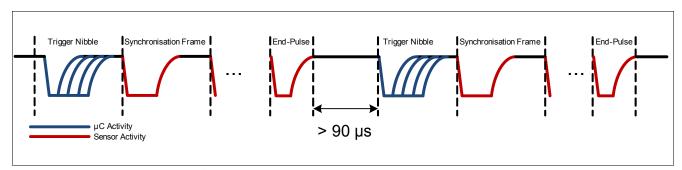

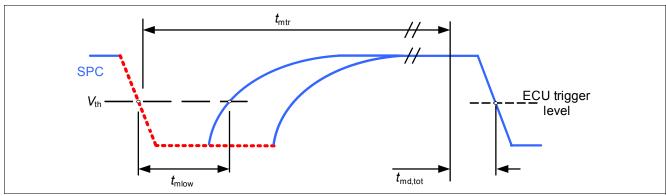

The Short PWM Code (SPC) is a synchronized data transmission based on the SENT protocol (Single Edge Nibble Transmission) defined by SAE J2716. As opposed to SENT, which implies a continuous transmission of data, the SPC protocol transmits data only after receiving a specific trigger pulse from the microcontroller. The required length of the trigger pulse depends on the sensor number, which is configurable. Thereby, SPC allows the operation of up to four sensors on one bus line.

SPC enables the use of enhanced protocol functionality due to the ability to select between various sensor slaves (ID selection). The slave number (S\_NR) can be given by the external circuit of SCK and IFC pin. In case of  $V_{DD}$  on SCK, the S\_NR[0] can be set to 1 and in the case of GND on SCK the S\_NR[0] is equal to 0. S\_NR[1] can be adjusted in the same way by the IFC pin.

As in SENT, the time between two consecutive falling edges defines the value of a 4-bit nibble, thus representing numbers between 0 and 15. The transmission time therefore depends on the transmitted data values. The single edge is defined by a 3 Unit Time (UT, see Chapter 4.4.3.1) low pulse on the output, followed by the high time defined in the protocol (nominal values, may vary depending on the tolerance of the internal oscillator and the influence of external circuitry). All values are multiples of a unit time frame concept. A transfer consists of the following parts (Figure 27):

- A trigger pulse by the master, which initiates the data transmission