## TLE7273-2

Low Dropout Voltage Regulator

**Automotive Power**

#### **Low Dropout Voltage Regulator**

TLE7273-2

#### 1 Overview

#### **Features**

- Output Voltage 5 V, 3.3 V or 2.6 V

- Output Voltage Tolerance ±2% Up To 180mA

- Ultra Low Quiescent Current Consumption < 36 μA</li>

- Enable Function

- Very Low Dropout Voltage

- · Reset With Adjustable Power-On delay

- Window Watchdog With Current Dependent Deactivation

- · Output Current Limitation

- Wide Operation Range Up To 45 V

- Wide Temperature Range From -40 °C To 150 °C

- · Overtemperature Shutdown

- Green Product (RoHS compliant)

- AEC Qualified

PG-DSO-14

PG-SSOP-14 Exposed Pad

#### **Description**

The TLE7273-2 is a monolithic voltage regulator with integrated window watchdog and reset dedicated for microcontroller supplies under harsh automotive environment conditions.

Due to its ultra low quiescent current, the TLE7273-2 is perfectly suited for applications that are permanently connected to battery. In addition, the regulator can be shut down via the Enable input causing the current consumption to drop below 3  $\mu$ A. The TLE7273-2 is equipped with an output current limitation and an overtemperature shutdown, protecting the device against overload, short circuit and over-temperature. It operates in the wide junction temperature range from -40 °C to 150 °C.

| Туре          | Package                | Marking       |

|---------------|------------------------|---------------|

| TLE7273-2GV50 | PG-DSO-14              | TLE7273-2GV50 |

| TLE7273-2GV33 | PG-DSO-14              | TLE7273-2GV33 |

| TLE7273-2GV26 | PG-DSO-14              | TLE7273-2GV26 |

| TLE7273-2EV50 | PG-SSOP-14 Exposed Pad | 7273 V50      |

Data Sheet 2 Rev. 1.2, 2009-04-28

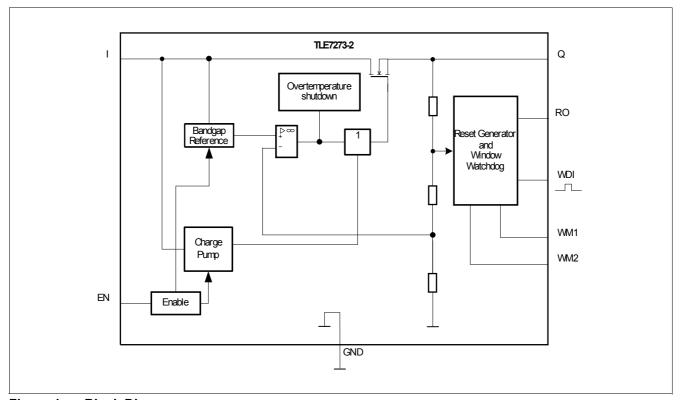

**Block Diagram**

### 2 Block Diagram

Figure 1 Block Diagram

**Pin Configuration**

### **3** Pin Configuration

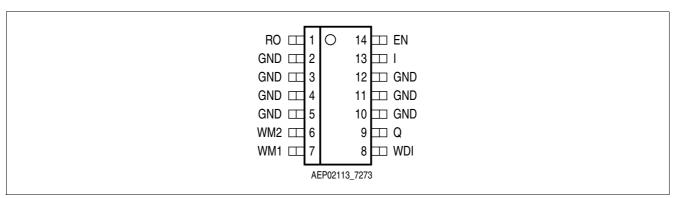

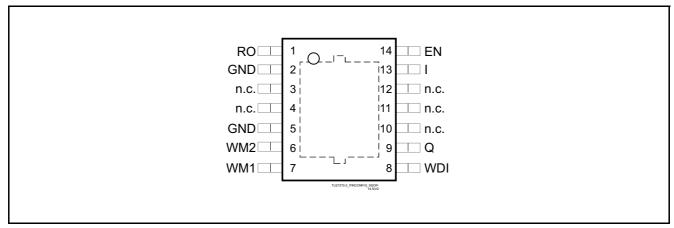

#### 3.1 Pin Assignment (PG-DSO-14)

Figure 2 Pin Assignment PG-DSO-14 (top view)

#### 3.2 Pin Definitions and Functions (PG-DSO-14)

Table 1 Pin Definitions and Functions

| Pin No.    | Symbol | Function                                                                                                                                                                |

|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | RO     | Reset Output TLE7273-2GV33, TLE7273-2GV26: open drain output; TLE7273-2GV50: integrated 20 k $\Omega$ pull-up resistor to output Q; leave open if not needed            |

| 2-5, 10-12 | GND    | Ground connect pin 2 and 3 to GND; connect pin 4-5 and 10-12 to heat sink area with GND potential                                                                       |

| 7          | WM1    | Watchdog Mode Bit 1 watchdog and reset mode selection, see "Window Watchdog State Diagram, Watchdog and Reset Modes" on Page 9; connect to Q or GND                     |

| 6          | WM2    | Watchdog Mode Bit 2 watchdog and reset mode selection, see "Window Watchdog State Diagram, Watchdog and Reset Modes" on Page 9; connect to Q or GND                     |

| 8          | WDI    | Watchdog Input trigger input for watchdog pulses; to turn off watchdog connect to GND and connect pin WM1 and WM2 to Q                                                  |

| 9          | Q      | Output Voltage block to GND with a ceramic capacitor close to the IC terminals, respecting the values given for its capacitance and ESR in "Functional Range" on Page 7 |

| 13         | I      | Input Voltage block to ground directly at the IC with a 100 nF ceramic capacitor                                                                                        |

| 14         | EN     | Enable Input low level disables the IC; integrated pull-down resistor to GND                                                                                            |

**Pin Configuration**

### 3.3 Pin Assignments (PG-SSOP-14 Exposed Pad)

Figure 3 Pin Assignment PG-SSOP-14 Exposed Pad (top view)

#### 3.4 Pin Definitions and Functions (PG-SSOP-14 Exposed Pad)

Table 2 Pin Definitions and Functions

| Pin No.          | Symbol | Function                                                                                                                        |

|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------|

| 1                | RO     | Reset Output integrated 20 k $\Omega$ pull-up resistor (TLE7273-2EV50); leave open if not needed                                |

| 2, 5             | GND    | Ground connect to GND                                                                                                           |

| 3, 4, 10, 11, 12 | n.c.   | not connected leave open or connect to GND                                                                                      |

| 6                | WM2    | Watchdog Mode Bit 2 watchdog and reset mode selection, see Figure 5; connect to $V_{\rm Q}$ or GND                              |

| 7                | WM1    | Watchdog Mode Bit 1 watchdog and reset mode selection, see Figure 5; connect to $V_{\rm Q}$ or GND                              |

| 8                | WDI    | Watchdog Input trigger input for watchdog pulses; pull down to GND if not needed and turn off the watchdog with WM1 and WM2 pin |

| 9                | Q      | Output Voltage block to GND with a ceramic capacitor $C_Q \ge 470$ nF close to IC terminal                                      |

| 13               | I      | Input Voltage block to ground directly at the IC with a 100 nF ceramic capacitor                                                |

| 14               | EN     | Enable Input low level disables the IC; integrated pull-down resistor                                                           |

| Pad              | -      | Exposed Pad connect to heatsink area; connect with GND on PCB                                                                   |

**General Product Characteristics**

#### 4 General Product Characteristics

#### 4.1 Absolute Maximum Ratings

Table 3 Absolute Maximum Ratings<sup>1)</sup>

$-40 \, ^{\circ}\text{C} < T_{i} < 150 \, ^{\circ}\text{C}$

| Pos.    | Parameter                                | Symbol             | Limit Values |          | Unit | Remarks                 |

|---------|------------------------------------------|--------------------|--------------|----------|------|-------------------------|

|         |                                          |                    | Min.         | Max.     |      |                         |

| Input I |                                          | П                  |              |          | 1    |                         |

| 4.1.1   | Voltage                                  | $V_1$              | -0.3         | 45       | V    | _                       |

| Output  | Q, Reset Output RO, Watchdog Mod         | de 2               |              | <u>'</u> |      |                         |

| 4.1.2   | Voltage                                  | $V_{Q}$            | -0.3         | 5.5      | V    | permanent               |

| 4.1.3   | Voltage                                  | $V_{Q}$            | -0.3         | 6.2      | V    | $t < 10 \text{ s}^{2)}$ |

| Enable  | Input EN                                 | •                  |              | <u>'</u> |      |                         |

| 4.1.4   | Voltage                                  | $V_{EN}$           | -1           | 45       | V    | _                       |

| 4.1.5   | Current                                  | $I_{EN}$           | -1           | 1        | mA   | _                       |

| Watcho  | dog Input WDI                            |                    |              |          |      |                         |

| 4.1.6   | Voltage                                  | $V_{RO}$           | -1           | 7        | V    | permanent               |

| Watch   | log Mode 1                               |                    | •            | •        | •    |                         |

| 4.1.7   | Voltage                                  | $V_{\mathrm{WM1}}$ | -0.3         | 5.5      | V    | permanent               |

| 4.1.8   | Voltage                                  | $V_{\mathrm{WM1}}$ | -0.3         | 6.2      | V    | $t < 10 \text{ s}^{2)}$ |

| 4.1.9   | Current                                  | $I_{WM1}$          | -5           | 5        | mA   | -                       |

| ESD St  | sceptibility                             |                    |              |          |      |                         |

| 4.1.10  | Human Body Model (HBM) <sup>3)</sup>     | Voltage            | -            | 3        | kV   | _                       |

| 4.1.11  | Charged Device Model (CDM) <sup>4)</sup> | Voltage            | -            | 1.5      | kV   | _                       |

| Tempe   | ratures                                  | •                  | •            |          | •    | ·                       |

| 4.1.12  | Junction Temperature                     | $T_{j}$            | -40          | 150      | °C   | _                       |

| 4.1.13  | Storage Temperature                      | $T_{\rm stg}$      | -50          | 150      | °C   | _                       |

<sup>1)</sup> not subject to production test, specified by design

Note: Maximum ratings are absolute ratings; exceeding any one of these values may cause irreversible damage to the integrated circuit. Integrated protection functions are designed to prevent IC destruction under fault conditions. Fault conditions are considered as outside normal operating range. Protections functions are not designed for continuous repetitive operation.

<sup>2)</sup> exposure to these absolute maximum ratings for extended periods (t > 10 s) may affect device reliability

<sup>3)</sup> ESD HBM Test according JEDEC JESD22-A114

<sup>4)</sup> ESD CDM Test according AEC/ESDA ESD-STM5.3.1-1999

#### **General Product Characteristics**

#### 4.2 Functional Range

| Pos.  | Parameter                           | Symbol       | Limi | t Values | Unit | Remarks                         |  |

|-------|-------------------------------------|--------------|------|----------|------|---------------------------------|--|

|       |                                     |              | Min. | Max.     |      |                                 |  |

| 4.2.1 | Input Voltage                       | $V_1$        | 5.5  | 45       | V    | TLE7273-2GV50,<br>TLE7273-2EV50 |  |

| 4.2.2 |                                     |              | 4.2  | 45       | V    | TLE7273-2GV33                   |  |

| 4.2.3 |                                     |              | 4.5  | 45       | V    | TLE7273-2GV26                   |  |

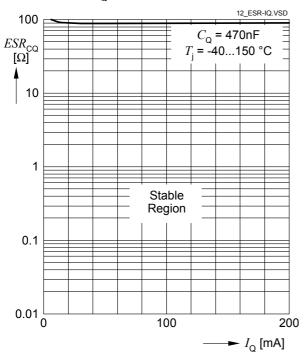

| 4.2.4 | Output Capacitor's Requirements for | $C_{Q}$      | 470  | _        | nF   | _1)                             |  |

| 4.2.5 | Stability                           | $ESR(C_{Q})$ | _    | 3        | Ω    | _2)                             |  |

<sup>1)</sup> the minimum output capacitance requirement is applicable for a worst case capacitance tolerance of 30%

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 4.3 Thermal Resistances

| Pos.   | Parameter                                 | Symbol               |      | Limit Val | ues      | Unit     | Remarks                                                |

|--------|-------------------------------------------|----------------------|------|-----------|----------|----------|--------------------------------------------------------|

|        |                                           |                      | Min. | Тур.      | Max.     |          |                                                        |

| Packa  | ge PG-DSO-14                              |                      |      |           |          |          |                                                        |

| 4.3.1  | Junction to Soldering Point <sup>1)</sup> | $R_{thJSP}$          | _    | 30        | _        | K/W      | measured to group of pins 3, 4, 5, 10, 11, 12          |

| 4.3.2  | Junction to Ambient <sup>1)</sup>         | $R_{thJA}$           | _    | 53        | _        | K/W      | 2)                                                     |

| 4.3.3  | _                                         |                      | _    | 105       | _        | K/W      | footprint only <sup>3)</sup>                           |

| 4.3.4  |                                           |                      | -    | 74        | _        | K/W      | 300 mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> |

| 4.3.5  |                                           |                      | _    | 65        | -        | K/W      | 600 mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> |

| Packa  | ge PG-SSOP-14 Exposed Pa                  | d                    | 1    |           | <u> </u> | <u> </u> | 1                                                      |

| 4.3.6  | Junction to Case <sup>1)</sup>            | $R_{\mathrm{thJSP}}$ | _    | 14        | _        | K/W      | measured to exposed pad                                |

| 4.3.7  | Junction to Ambient <sup>1)</sup>         | $R_{thJA}$           | _    | 47        | _        | K/W      | 2)                                                     |

| 4.3.8  |                                           |                      | _    | 141       | _        | K/W      | footprint only <sup>3)</sup>                           |

| 4.3.9  |                                           |                      | -    | 66        | _        | K/W      | 300 mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> |

| 4.3.10 |                                           |                      | _    | 56        | _        | K/W      | 600 mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> |

<sup>1)</sup> not subject to production test, specified by design

<sup>2)</sup> relevant ESR value at f = 10 kHz

<sup>2)</sup> Specified R<sub>thJA</sub> value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm³ board with 2 inner copper layers (2 x 70μm Cu, 2 x 35μm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

<sup>3)</sup> Specified  $R_{\text{thJA}}$  value is according to JEDEC JESD 51-3 at natural convection on FR4 1s0p board; The Product (Chip+Package) was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with 1 copper layer (1 x 70µm Cu).

#### 5 Block Description and Electrical Characteristics

#### 5.1 Description

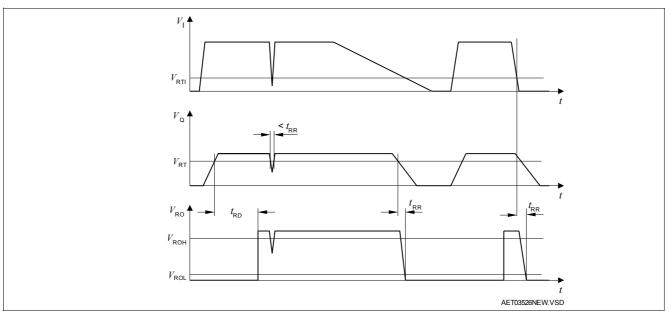

#### 5.1.1 Power On Reset and Reset Output

For an output voltage level of  $V_{\rm Q} \ge 1$  V, the reset output is held low. When the level of  $V_{\rm Q}$  reaches the reset threshold  $V_{\rm RT}$ , the signal at RO remains low for the power-up reset delay time  $t_{\rm RD}$ . The reset function and timing is illustrated in **Figure 4**. The reset reaction time  $t_{\rm RR}$  avoids wrong triggering caused by short "glitches" on the  $V_{\rm Q}$ -line. In case of  $V_{\rm Q}$  power down ( $V_{\rm Q} < V_{\rm RT}$  for  $t > t_{\rm RR}$ ) a logic low signal is generated at the pin RO to reset an external microcontroller.

The TLE7273-2GV50 and TLE7273-2EV50 feature an integrated pull-up resistor on the reset output while the TLE7273-2GV33 and TLE7273-2GV26 have an open drain output requiring an external pull-up resistor. When connected to a voltage level of 5 V, a recommended value for this external resistor is  $\geq$  5.6 k $\Omega$ .

But it's also possible calculating its value by using the following formula, based on the reset sink current (Example: external pull-up resistor connected to  $V_{\rm ext}$  = 5 V):

$$R_{\rm extmin} = \varDelta V \, / \, I_{\rm RO} = (V_{\rm ext} - V_{\rm ROmin}) \, / \, I_{\rm RO} = (5 \, \rm V - 0.25 \, \rm V) \, / \, 1.0 \, \, \rm mA = 4.75 \, \, k\Omega$$

At low output voltage levels  $V_{\rm Q}$  < 1 V the integrated pull-up resistor of the TLE7273-2GV50 is switched off setting the reset output high ohmic.

Figure 4 Reset Function and Timing Diagram

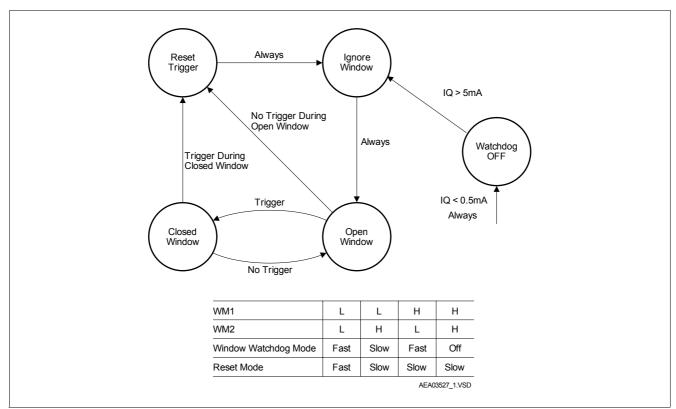

#### 5.1.2 Watchdog Operation

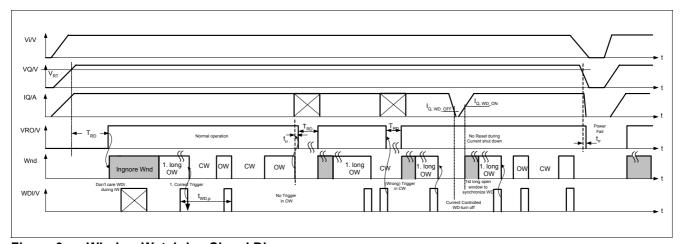

The watchdog uses a fraction of the charge pump oscillator's clock signal as timebase. The watchdog timebase can be adjusted using the pins WM1 and WM2 (see **Figure 5**). The watchdog can be turned off setting WM1 and WM2 to high level. The timing values refer to typ. values with WM1 and WM2 connected to GND (fast watchdog and reset timing).

**Figure 5** shows the state diagram of the window watchdog (WWD) and the watchdog and reset mode selection. After power-on, the reset output signal at the RO pin (microcontroller reset) is kept LOW for the reset delay time  $t_{\rm RD}$  of typ. 16 ms. With the LOW to HIGH transition of the signal at RO the device starts the ignore window time  $t_{\rm CW}$  (32 ms). During this window the signal at the WDI pin is ignored. Next the WWD starts the open window which

is in the very first turn after power up a long open window with tmax = 4 \*  $t_{OW}$ . In the following turns, the timing corresponds to the standard timing setting as described in the specification.

When a valid trigger signal is detected during the open window a closed window is initialized immediately. A trigger signal within the closed window is interpreted as a pretrigger failure and results in a reset. After the closed window the open window with the duration  $t_{\rm OW}$  is started again. The open window lasts at minimum until the trigger process has occurred, at maximum  $t_{\rm OW}$  is 32 ms (typ. value with fast timing).

A HIGH to LOW transition of the watchdog trigger signal at pin WDI is considered as a valid trigger pulse.

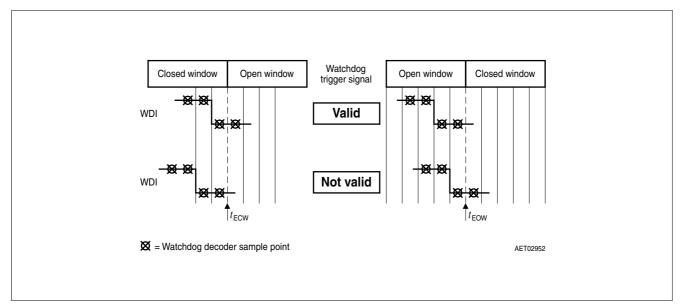

See Figure 7: To avoid wrong triggering due to parasitic glitches two HIGH samples followed by two LOW samples (sample period  $t_{\text{sam}}$  typ. 0.5 ms) are decoded as a valid trigger .

A reset is generated (RO goes LOW) if there is no trigger pulse during the open window or if a pretrigger occurs during the closed window. The triggering is correct also, if the first three samples (two HIGH one LOW) of the trigger pulse at pin WDI are inside the closed window and only the fourth sample (the second LOW sample) is taken in the open window.

After turning OFF the Watchdog by output current reduction, RO remains high. (see also the signal diagram in **Figure 6**). After turning ON the WWD again by exceeding the current threshold, the logic cycle starts again with the Ignore Window and goes then into the "1st. long open window". This 1st long OW is maximum 4 \*  $t_{\rm OW}$  long and allows the re-synchronisation between the micro controller and the WWD timing. The 1st. long OW is closed by the first valid trigger on WDI from the micro controller. This trigger ensures the synchronisation. As soon as this trigger is done, the micro controller timing must be stable and correspondent to  $t_{\rm WD}$ .

Figure 5 Window Watchdog State Diagram, Watchdog and Reset Modes

Data Sheet 9 Rev. 1.2, 2009-04-28

Figure 6 Window Watchdog Signal Diagram

Figure 7 Window Watchdog Definitions

#### 5.2 Electrical Characteristics

#### **Electrical Characteristics**

$V_{\rm i}$ =13.5 V; – 40 °C <  $T_{\rm i}$ < 150 °C; unless otherwise specified

| Pos.   | Parameter                                              | Symbol                     | Limit | Values | }     | Unit | Test Condition                                                                             |

|--------|--------------------------------------------------------|----------------------------|-------|--------|-------|------|--------------------------------------------------------------------------------------------|

|        |                                                        |                            | Min.  | Тур.   | Max.  | 1    |                                                                                            |

| Dutput | Q                                                      |                            |       |        | •     |      | ,                                                                                          |

| 5.2.1  | Output Voltage                                         | $V_{Q}$                    | 4.90  | 5.00   | 5.10  | V    | TLE7273-2GV50,<br>TLE7273-2EV50<br>1 mA < $I_{\rm Q}$ < 180 mA<br>6 V < $V_{\rm I}$ < 16 V |

| 5.2.2  | Output Voltage                                         | $V_{Q}$                    | 4.90  | 5.00   | 5.10  | V    | TLE7273-2GV50,<br>TLE7273-2EV50 $I_{\rm Q}$ = 10 mA 6 V < $V_{\rm I}$ < 45 V               |

| 5.2.3  | Output Voltage                                         | $V_{Q}$                    | 3.234 | 3.30   | 3.366 | V    | TLE7273-2GV33<br>1 mA $< I_Q <$ 180 mA<br>4.5 V $< V_I <$ 16 V                             |

| 5.2.4  | Output Voltage                                         | $V_{Q}$                    | 3.234 | 3.30   | 3.366 | V    | TLE7273-2GV33 $I_{\rm Q}$ = 10 mA 4.5 V < $V_{\rm I}$ < 45 V                               |

| 5.2.5  | Output Voltage                                         | $V_{Q}$                    | 2.548 | 2.60   | 2.652 | V    | TLE7273-2GV26<br>1 mA $< I_Q <$ 180 mA<br>4.5 V $< V_I <$ 16 V                             |

| 5.2.6  | Output Voltage                                         | $V_{Q}$                    | 2.548 | 2.60   | 2.652 | V    | TLE7273-2GV26 $I_{\rm Q}$ = 10 mA 4.5 V < $V_{\rm I}$ < 45 V                               |

| 5.2.7  | Output Current Limitation                              | $I_{Q}$                    | 200   | _      | 500   | mA   | $V_{\rm Q}$ = 2.0 V                                                                        |

| 5.2.8  |                                                        |                            | 200   | _      | 600   |      | $V_{\rm Q}$ = 0 V                                                                          |

| 5.2.9  | Dropout Voltage <sup>1)</sup> $V_{DR} = V_{I} - V_{Q}$ | $V_{DR}$                   | _     | 250    | 500   | mV   | $I_{\rm Q}$ = 180 mA<br>TLE7273-2GV50,<br>TLE7273-2EV50                                    |

| 5.2.10 | Load Regulation                                        | $\Delta V_{\mathrm{Q,Lo}}$ | ı     | 50     | 90    | mV   | 1 mA < $I_Q$ < 180 mA;                                                                     |

| 5.2.11 | Line Regulation                                        | $\Delta V_{Q,Li}$          | _     | 10     | 50    | mV   | $I_{\rm Q}$ = 1 mA;<br>10 V < $V_{\rm I}$ < 32 V                                           |

| 5.2.12 | Power Supply Ripple Rejection                          | PSRR                       | _     | 60     | _     | dB   | $f_{\rm r}$ = 100 Hz;<br>$V_{\rm r}$ = 0.5 $V_{\rm PP}$                                    |

| 5.2.13 | Reverse Output Current Clamping                        | $V_{Q}$                    | _     | _      | 5.5   | V    | $I_{\rm Q}$ = -1 mA, $V_{\rm EN}$ = 0 V                                                    |

|        | t Consumption                                          |                            |       |        |       |      |                                                                                            |

| 5.2.14 | Quiescent Current $I_{q} = I_{l} - I_{Q}$              | $I_{q}$                    | _     | 28     | 36    | μΑ   | $I_{\rm Q}$ = 100 μA;<br>$T_{\rm j}$ < 80°C                                                |

| 5.2.15 | Quiescent Current<br>Disabled                          | $I_{q}$                    | _     | 1      | 3     | μΑ   | $V_{\rm EN}$ = 0V;<br>$T_{\rm j}$ < 80°C                                                   |

| Enable | Input EN                                               |                            |       |        |       |      |                                                                                            |

| 5.2.16 | High Level Input Voltage                               | $V_{EN,H}$                 | 3.0   | _      | _     | V    | $V_{Q}$ on                                                                                 |

#### **Electrical Characteristics**

$V_{\rm i}$ =13.5 V; – 40 °C <  $T_{\rm i}$ < 150 °C; unless otherwise specified

| Pos.   | Parameter                                  | Symbol               | Limit Values |      |      | Unit | Test Condition                                                   |

|--------|--------------------------------------------|----------------------|--------------|------|------|------|------------------------------------------------------------------|

|        |                                            |                      | Min.         | Тур. | Max. |      |                                                                  |

| 5.2.17 | Low Level Input Voltage                    | $V_{EN,L}$           | _            | _    | 0.5  | V    | $V_{\rm Q}$ = 0.02 V; $I_{\rm Q}$ = 5 mA; $T_{\rm j}$ < 125 °C   |

| 5.2.18 |                                            |                      | _            | _    | 0.3  | V    | $V_{\rm Q}$ = 0.02 V; $I_{\rm Q}$ = 5 mA                         |

| 5.2.19 | High Level Input Current                   | $I_{EN,H}$           | _            | 3    | 4    | μΑ   | V <sub>EN</sub> = 5 V                                            |

| Watcho | dog Mode Bit 1                             |                      |              |      |      |      |                                                                  |

| 5.2.20 | High Level Input Voltage                   | $V_{\mathrm{WM1,H}}$ | 4.00         | _    | _    | V    | TLE7273-2GV50,<br>TLE7273-2EV50                                  |

| 5.2.21 |                                            |                      | 2.65         | _    | _    | V    | TLE7273-2GV33                                                    |

| 5.2.22 |                                            |                      | 2.30         | _    | _    | V    | TLE7273-2GV26                                                    |

| 5.2.23 | Low Level Input Voltage                    | $V_{\mathrm{WM1,L}}$ | _            | _    | 0.80 | V    |                                                                  |

| Watcho | dog Mode Bit 2                             |                      |              |      |      |      | 1                                                                |

| 5.2.24 | High Level Input Voltage                   | $V_{\mathrm{WM2,H}}$ | 4.00         | _    | _    | V    | TLE7273-2GV50,<br>TLE7273-2EV50                                  |

| 5.2.25 | _                                          |                      | 2.65         | _    | _    | V    | TLE7273-2GV33                                                    |

| 5.2.26 | _                                          |                      | 2.30         | _    | _    | V    | TLE7273-2GV26                                                    |

| 5.2.27 | Low Level Input Voltage                    | $V_{\mathrm{WM2,L}}$ | _            | _    | 0.80 | V    |                                                                  |

| Watcho | dog Input WDI                              | '                    | •            |      |      | 1    |                                                                  |

| 5.2.28 | High Level Input Voltage                   | $V_{\mathrm{WDI,H}}$ | 4.00         | _    | _    | V    | TLE7273-2GV50,<br>TLE7273-2EV50                                  |

| 5.2.29 |                                            |                      | 2.65         | _    | _    | V    | TLE7273-2GV33                                                    |

| 5.2.30 |                                            |                      | 2.30         | _    | _    | V    | TLE7273-2GV26                                                    |

| 5.2.31 | Low Level Input Voltage                    | $V_{\mathrm{WDI,L}}$ | _            | _    | 0.80 | V    |                                                                  |

| 5.2.32 | High Level Input Current                   | $I_{\mathrm{WDI,H}}$ | _            | 3    | 4    | μΑ   | <i>V</i> <sub>WDI</sub> = 5 V                                    |

| 5.2.33 | Low Level Input Current                    | $I_{WD,IL}$          | _            | 0.5  | 1    | μΑ   | $V_{\text{WDI}} = 0 \text{ V}$<br>$T_{\text{j}} < 80 \text{ °C}$ |

| 5.2.34 | Watchdog Sampling Time                     | $t_{sam}$            | 0.40         | 0.50 | 0.60 | ms   | Fast Watchdog Timing                                             |

| 5.2.35 |                                            |                      | 0.80         | 1.00 | 1.20 | ms   | Slow Watchdog Timing                                             |

| 5.2.36 | Ignore Window Time                         | $t_{IW}$             | 25.6         | 32.0 | 38.4 | ms   | Fast Watchdog Timing                                             |

| 5.2.37 |                                            |                      | 51.2         | 64.0 | 76.8 | ms   | Slow Watchdog Timing                                             |

| 5.2.38 | Open Window Time                           | $t_{\sf OW}$         | 25.6         | 32.0 | 38.4 | ms   | Fast Watchdog Timing                                             |

| 5.2.39 |                                            |                      | 51.2         | 64.0 | 76.8 | ms   | Slow Watchdog Timing                                             |

| 5.2.40 | Closed Window Time                         | $t_{\sf CW}$         | 25.6         | 32.0 | 38.4 | ms   | Fast Watchdog Timing                                             |

| 5.2.41 |                                            |                      | 51.2         | 64.0 | 76.8 | ms   | Slow Watchdog Timing                                             |

| 5.2.42 | Window Watchdog Trigger Time <sup>2)</sup> | $t_{\mathrm{WD}}$    | _            | 48   | _    | ms   | Fast Watchdog Timing                                             |

|        |                                            |                      |              |      |      |      |                                                                  |

#### **Electrical Characteristics**

$V_{\rm i}$ =13.5 V; – 40 °C <  $T_{\rm j}$ < 150 °C; unless otherwise specified

| Pos.    | Parameter                                        | Symbol          | Limit Values |      |      | Unit | Test Condition                                                                  |  |

|---------|--------------------------------------------------|-----------------|--------------|------|------|------|---------------------------------------------------------------------------------|--|

|         |                                                  |                 | Min.         | Тур. | Max. |      |                                                                                 |  |

| 5.2.44  | Watchdog Deactivation Current<br>Threshold       | $I_{Q,WD\_off}$ | 0.50         | _    | _    | mA   | $I_{\rm Q}$ decreasing $V_{\rm I}$ > 5.5V for TLE7273-2GV50, TLE7273-2EV50      |  |

|         |                                                  |                 |              |      |      |      | V <sub>I</sub> > 4.5V for TLE7273-<br>2GV33, TLE7273-2GV26                      |  |

| 5.2.45  | Watchdog Activating Current Threshold            | $I_{Q,WD\_on}$  | _            | _    | 5    | mA   | $I_{\rm Q}$ increasing $V_{\rm I}$ > 5.5V for TLE7273-2GV50, TLE7273-2EV50      |  |

|         |                                                  |                 |              |      |      |      | $V_1$ > 4.5V for TLE7273-2GV33, TLE7273-2GV26                                   |  |

| Reset 0 | Output RO                                        |                 |              | ·    |      |      |                                                                                 |  |

| 5.2.46  | Output Undervoltage Reset<br>Switching Threshold | $V_{RT}$        | 4.50         | 4.60 | 4.70 | V    | TLE7273-2GV50,<br>TLE7273-2EV50 $V_{\rm Q}$ decreasing                          |  |

| 5.2.47  |                                                  |                 | 3.00         | 3.07 | 3.13 | V    | TLE7273-2GV33 <sup>3)</sup> $V_1 > 4.5V$ ; $V_Q$ decreasing                     |  |

| 5.2.48  |                                                  |                 | 2.35         | 2.38 | 2.45 | V    | TLE7273-2GV26 <sup>3)</sup> $V_{\rm I}$ > 4.5V; $V_{\rm Q}$ decreasing          |  |

| 5.2.49  | Input Undervoltage Reset Switching               | $V_{RTI}$       | _            | 3.9  | 4.0  | V    | TLE7273-2GV26 <sup>3)</sup>                                                     |  |

| 5.2.50  | Threshold                                        |                 |              |      |      |      | TLE7273-2GV33 <sup>3)</sup>                                                     |  |

| 5.2.51  | _                                                |                 |              |      |      |      | $V_{\rm Q}$ > $V_{\rm RT}$ ; $V_{\rm I}$ decreasing                             |  |

| 5.2.52  | Output Undervoltage Reset Hysteresis             | $V_{RH}$        | _            | 45   | _    | mV   | TLE7273-2GV26                                                                   |  |

| 5.2.53  | Output Undervoltage Reset                        | $V_{RH}$        | _            | 60   | _    | mV   | TLE7273-2GV33                                                                   |  |

| 5.2.54  | Hysteresis                                       |                 | _            | 90   | _    | mV   | TLE7273-2GV50,<br>TLE7273-2EV50                                                 |  |

| 5.2.55  | Maximum<br>Reset Sink Current                    | $I_{RO,max}$    | 1.75         | -    | _    | mA   | TLE7273-2GV50,<br>TLE7273-2EV50<br>$V_{\rm Q}$ = 4.5 V;<br>$V_{\rm RO}$ =0.25 V |  |

| 5.2.56  |                                                  |                 | 1.3          | _    | _    | mA   | TLE7273-2GV33 $V_{\rm Q}$ = 3.0 V; $V_{\rm RO}$ = 0.25 V                        |  |

| 5.2.57  |                                                  |                 | 1.0          | _    | _    | mA   | TLE7273-2GV26 $V_{\rm Q}$ = 2.35V; $V_{\rm RO}$ = 0.25V                         |  |

#### **Electrical Characteristics**

$V_{\rm i}$ =13.5 V; – 40 °C <  $T_{\rm j}$ < 150 °C; unless otherwise specified

| Pos.   | Parameter                         | Symbol     | Limit Values |      |      | Unit | Test Condition                                                   |

|--------|-----------------------------------|------------|--------------|------|------|------|------------------------------------------------------------------|

|        |                                   |            | Min.         | Тур. | Max. |      |                                                                  |

| 5.2.58 | Reset Output Low Level Voltage    | $V_{ROL}$  | _            | 0.15 | 0.25 | V    | $V_{\rm Q} \ge 1 \text{ V};$<br>$I_{\rm RO} < 200  \mu\text{A}$  |

| 5.2.59 | Reset Output High Level Voltage   | $V_{ROH}$  | 4.5          | _    | _    | V    | TLE7273-2GV50,<br>TLE7273-2EV50                                  |

| 5.2.60 | Reset High Level Leakage Current  | $I_{ROLK}$ | _            | _    | 1    | μΑ   | TLE7273-2GV33<br>TLE7273-2GV26                                   |

| 5.2.61 | Integrated Reset Pull Up Resistor | $R_{RO}$   | 10           | 20   | 40   | kΩ   | TLE7273-2GV50, TLE7273-2EV50 internally connected to $V_{\rm Q}$ |

| 5.2.62 | Power-On Reset Delay Time         | $t_{RD}$   | 12.8         | 16.0 | 19.2 | ms   | Fast Reset Timing                                                |

| 5.2.63 |                                   |            | 25.6         | 32.0 | 38.4 | ms   | Slow Reset Timing                                                |

| 5.2.64 | Reset Reaction Time               | $t_{RR}$   | -            | 4    | 12   | μs   |                                                                  |

<sup>1)</sup> measured when the output voltage has dropped 100 mV from the nominal value obtained at  $V_{\rm I}$  = 13.5 V

Data Sheet 14 Rev. 1.2, 2009-04-28

<sup>2)</sup> recommendation for typical trigger time;  $t_{\rm WD}$  =  $t_{\rm CW}$  + 1/2\* $t_{\rm OW}$

<sup>3)</sup> reset output triggered when output voltage  $V_{\rm Q}$  is lower than output voltage reset switching threshold  $V_{\rm RT}$  or is also triggered, when input voltage is decreasing to  $V_{\rm I}$  < 4.0 V and  $V_{\rm Q}$  >  $V_{\rm RT}$

#### **Typical Performance Characteristics**

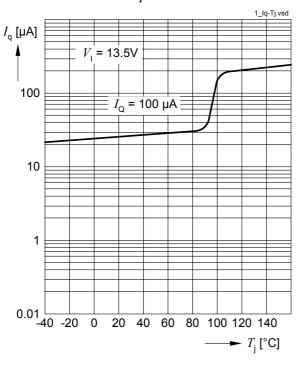

# Current Consumption $I_{\rm q}$ versus Junction Temperature $T_{\rm j}$ (EN=ON)

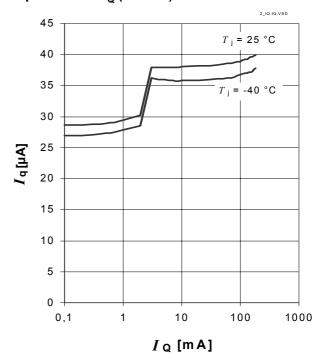

## Current Consumption $I_{\rm q}$ versus Output Current $I_{\rm Q}$ (EN=ON)

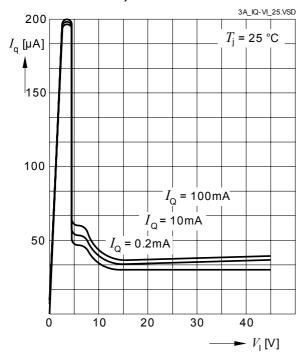

### Current Consumption $I_q$ versus Input Voltage $V_l$ at $T_i$ =25°C (EN=ON)

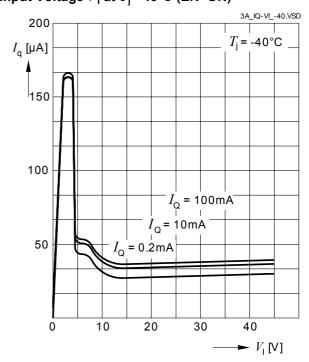

## Current Consumption $I_q$ versus Input Voltage $V_l$ at $T_l$ =-40°C (EN=ON)

Data Sheet 15 Rev. 1.2, 2009-04-28

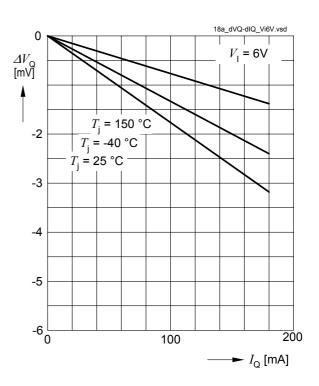

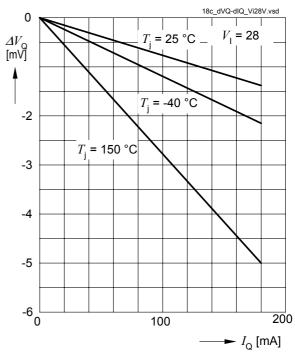

### Load Regulation d $V_{\mathrm{Q}}$ versus Output Current Change d $I_{\mathrm{Q}}$

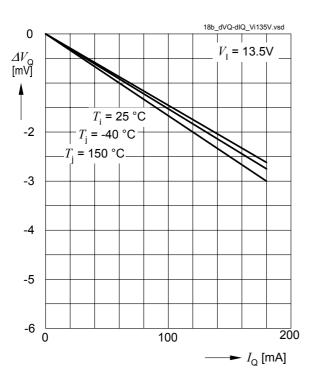

### Load Regulation $\mathrm{d}V_\mathrm{Q}$ versus Output Current Change $\mathrm{d}I_\mathrm{Q}$

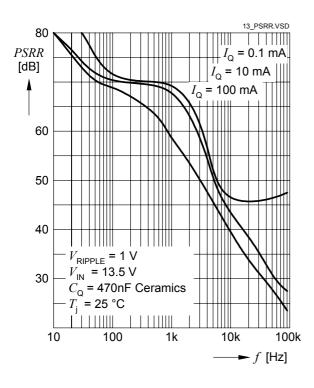

#### Power Supply Ripple Rejection PSRR

## Load Regulation d $V_{\rm Q}$ versus Output Current Change d $I_{\rm Q}$

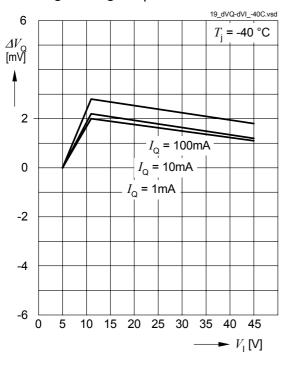

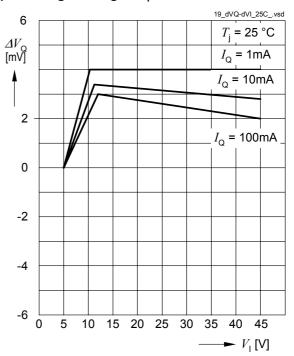

### Line Regulation d $V_{\mathrm{Q}}$ versus Input Voltage Change d $V_{\mathrm{I}}$

### Line Regulation d $V_{\rm Q}$ versus Input Voltage Change d $V_{\rm I}$

### Line Regulation d $V_{ m Q}$ versus Input Voltage Change d $V_{ m I}$

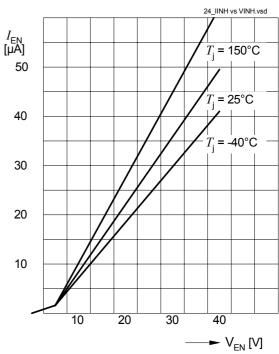

### Enable Input Current $I_{\mathrm{EN}}$ versus Enable Input Voltage $V_{\mathrm{EN}}$

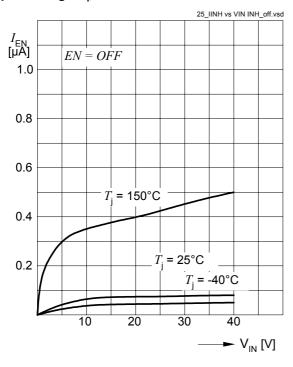

### Enable Input Current $I_{\rm EN}$ versus Input Voltage $V_{\rm I}$ , EN=Off

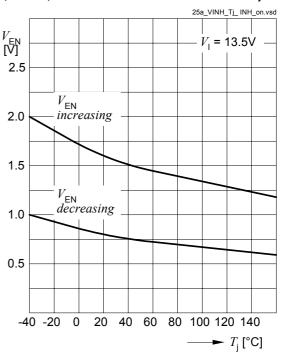

### Enable High Level / Low Level Input Voltage $V_{\rm EN,H}$ / $V_{\rm EN,L}$ versus Junction Temperature $T_{\rm i}$

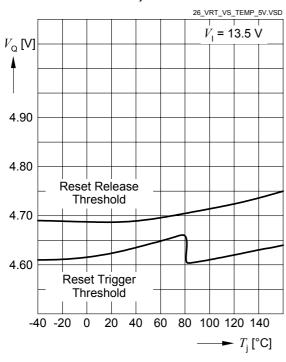

### Reset Threshold $V_{\rm RT}$ versus Junction Temperature $T_{\rm i}$ (5V-Version)

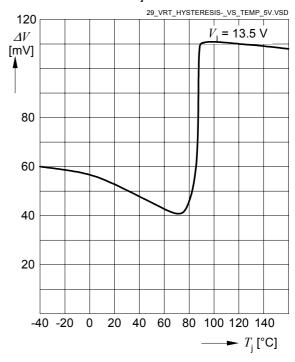

### Reset Hysteresis versus Junction Temperature $T_i$ (5V-Version)

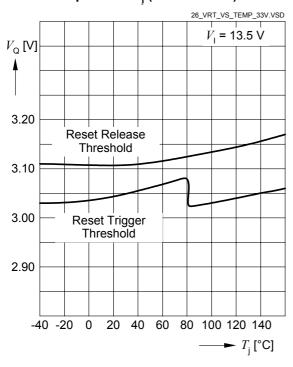

## Reset Threshold $V_{\rm RT}$ versus Junction Temperature $T_{\rm i}$ (3.3V-Version)

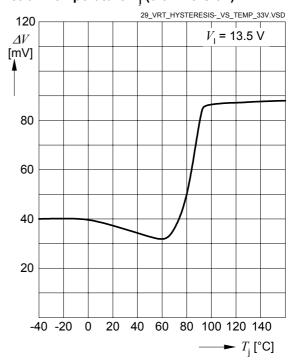

### Reset Hysteresis versus Junction Temperature $T_{\rm i}$ (3.3V-Version)

## Reset Threshold $V_{\mathrm{RT}}$ versus Junction Temperature $T_{\mathrm{i}}$ (2.6V-Version)

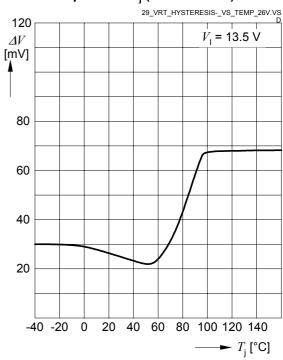

### Reset Hysteresis versus Junction Temperature $T_{\rm j}$ (2.6V-Version)

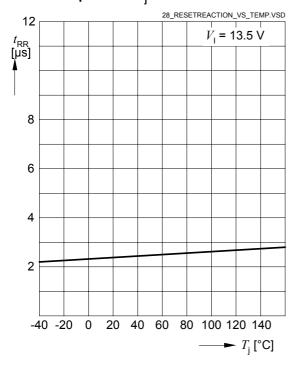

### Reset Reaction Time $t_{\rm rr}$ versus Junction Temperature $T_{\rm i}$

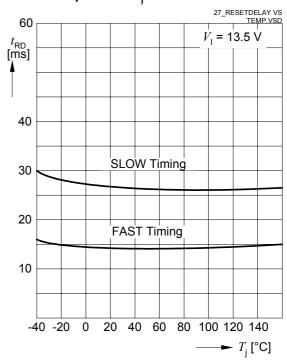

### Reset Delay $t_{\rm RD}$ Time versus Junction Temperature $T_{\rm i}$

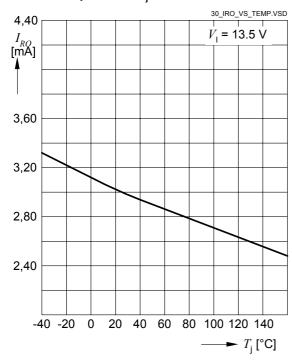

### Reset Output Sink Current $I_{\rm RO}$ versus Junction Temperature $T_{\rm i}$

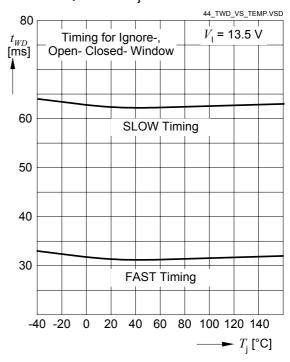

### Watchdog Timing $t_{WD}$ versus Junction Temperature $T_{\rm i}$

# Region of Stability $ESR(C_{\rm Q})$ versus Output Current $I_{\rm Q}$

Data Sheet 21 Rev. 1.2, 2009-04-28

**Package Outlines**

### 6 Package Outlines

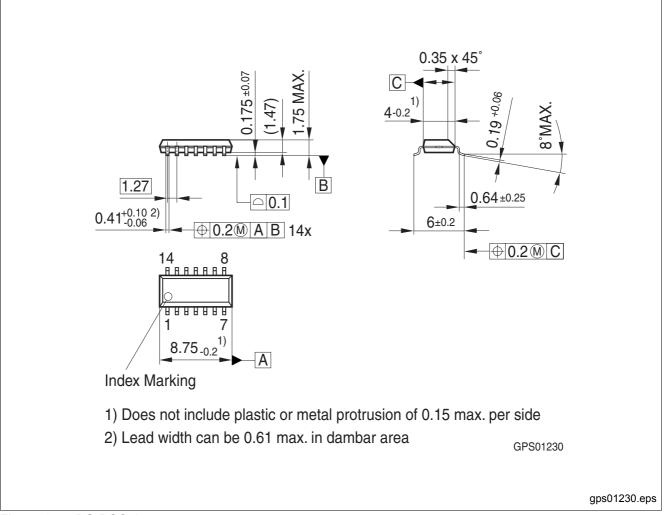

Figure 8 PG-DSO-14

#### **Package Outlines**

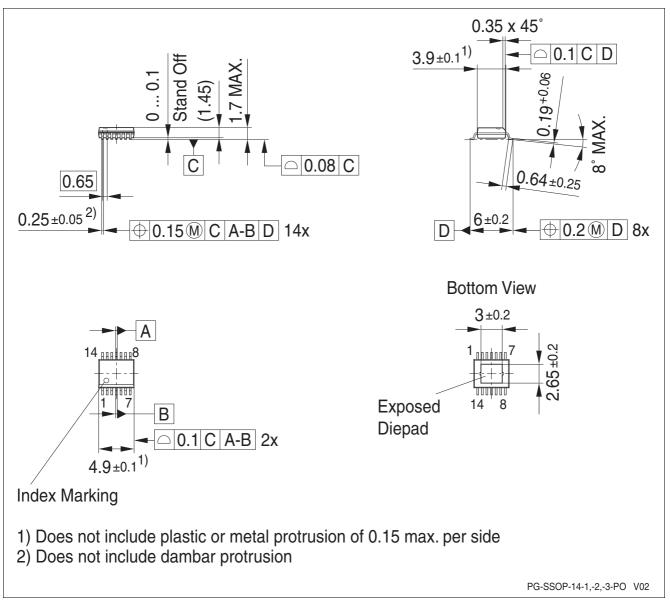

Figure 9 PG-SSOP-14 Exposed Pad

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

**Revision History**

### 7 Revision History

| Revision | Date       | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2      | 2009-04-28 | 2.6V version, 5V version in PG-SSOP-14 package and all related description added:                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |            | In "Features" on Page 2 "or 2.6 V" added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |            | In "Features" on Page 2 package drawing for PG-DSO-14 updated, package drawing for PG-SSOP-14 added                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |            | In "Overview" on Page 2 in table at the bottom type "TLE7273-2GV26" and "TLE7273-2EV50" added                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |            | In "Pin Definitions and Functions (PG-DSO-14)" on Page 4 in description for Pin 1 ", TLE7273-2GV26" added                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |            | "Pin Assignments (PG-SSOP-14 Exposed Pad)" on Page 5 and "Pin Definitions and Functions (PG-SSOP-14 Exposed Pad)" on Page 5 added;                                                                                                                                                                                                                                                                                                                                                                                            |

|          |            | In "Functional Range" on Page 7 Item 4.2.3 added, in Item 4.2.1 ", TLE7273-2EV50" added;                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |            | In "Thermal Resistances" on Page 7 values for PG-SSOP-14 package added: Item 4.3.6, Item 4.3.7, Item 4.3.8, Item 4.3.9 and Item 4.3.10 added                                                                                                                                                                                                                                                                                                                                                                                  |

|          |            | In "Power On Reset and Reset Output" on Page 8 "TLE7273-2EV50" in description added                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |            | In "Electrical Characteristics" on Page 11 all specific Items for 2.6V version added: Item 5.2.5, Item 5.2.6, Item 5.2.22, Item 5.2.26, Item 5.2.30, Item 5.2.48, Item 5.2.52 and Item 5.2.57 added; In Item 5.2.44, Item 5.2.45, Item 5.2.49, Item 5.2.50, Item 5.2.51 and Item 5.2.60 Conditions for 2.6V version added; In Item 5.2.1, Item 5.2.2, Item 5.2.9, Item 5.2.20, Item 5.2.24, Item 5.2.28, Item 5.2.44, Item 5.2.45, Item 5.2.46, Item 5.2.54, Item 5.2.55, Item 5.2.59 and Item 5.2.61 ", TLE7273-2EV50" added |

|          |            | In "Typical Performance Characteristics" on Page 15 Graphs "Reset Threshold VRT versus Junction Temperature Tj (3.3V-Version)" on Page 19, "Reset Threshold VRT versus Junction Temperature Tj (3.3V-Version)" on Page 19, "Reset Threshold VRT versus Junction Temperature Tj (2.6V-Version)" on Page 19 and "Reset Hysteresis versus Junction Temperature Tj (3.3V-Version)" on Page 19 added                                                                                                                               |

|          |            | In "Package Outlines" on Page 22 Oulines for PG-SSOP-14 added: Figure 9                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### **Revision History**

| Revision | Date       | Changes                                                                                                                                                                                                                                                                                                                    |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1      | 2008-07-25 | 3.3V version and all related description added:                                                                                                                                                                                                                                                                            |

|          |            | In "Features" on Page 2 "3.3V" added                                                                                                                                                                                                                                                                                       |

|          |            | In "Overview" on Page 2 in table at the bottom type "TLE7273-2GV33" added                                                                                                                                                                                                                                                  |

|          |            | In "Pin Definitions and Functions (PG-DSO-14)" on Page 4 in description for Pin 1 "TLE7273-2GV33: open drain output;" added                                                                                                                                                                                                |

|          |            | In "Functional Range" on Page 7 Item 4.2.2 added                                                                                                                                                                                                                                                                           |

|          |            | In "Power On Reset and Reset Output" on Page 8 description for dimensioning external pull-up resistor at RO added;                                                                                                                                                                                                         |

|          |            | In "Electrical Characteristics" on Page 11 all specific Items for 3.3V version added: Item 5.2.3, Item 5.2.4, Item 5.2.21, Item 5.2.25, Item 5.2.29, Item 5.2.47, Item 5.2.49, Item 5.2.50, Item 5.2.51, Item 5.2.53, Item 5.2.56 and Item 5.2.60 added; In Item 5.2.44 and Item 5.2.45 Conditions for 3.3V version added; |

| 1.0      | 2008-04-10 | final version data sheet                                                                                                                                                                                                                                                                                                   |

Edition 2009-04-28

Published by Infineon Technologies AG 81726 Munich, Germany © 2009 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LDO Voltage Regulators category:

Click to view products by Infineon manufacturer:

Other Similar products are found below:

AP7363-SP-13 L79M05TL-E PT7M8202B12TA5EX TCR3DF185,LM(CT TCR3DF24,LM(CT TCR3DF285,LM(CT TCR3DF31,LM(CT TCR3DF31,LM(CT TCR3DF45,LM(CT MP2013GQ-33-Z 059985X NCP4687DH15T1G 701326R TCR2EN28,LF(S NCV8170AXV250T2G TCR3DF27,LM(CT TCR3DF19,LM(CT TCR3DF125,LM(CT TCR2EN18,LF(S AP2112R5A-3.3TRG1 AP7315-25W5-7 IFX30081LDVGRNXUMA1 NCV47411PAAJR2G AP2113KTR-G1 AP2111H-1.2TRG1 ZLDO1117QK50TC AZ1117IH-1.8TRG1 AZ1117ID-ADJTRG1 TCR3DG12,LF MIC5514-3.3YMT-T5 MIC5512-1.2YMT-T5 MIC5317-2.8YM5-T5 SCD7912BTG NCP154MX180270TAG SCD33269T-5.0G NCV8170BMX330TCG NCV8170AMX120TCG NCP706ABMX300TAG NCP153MX330180TCG NCP114BMX075TCG MC33269T-3.5G CAT6243-ADJCMT5T TCR3DG33,LF AP2127N-1.0TRG1 TCR4DG35,LF LT1117CST-3.3 LT1117CST-5 TAR5S15U(TE85L,F) TAR5S18U(TE85L,F) TCR3UG19A,LF TCR4DG105,LF