# TLE7274-2

5-V Low Dropout Voltage Regulator

TLE7274-2E TLE7274-2D TLE7274-2G

## Data Sheet

Rev. 1.01, 2011-11-30

## Automotive Power

## 5-V Low Dropout Voltage Regulator

TLE7274-2

### 1 Overview

#### Features

- Ultra Low Current Consumption 20 μA

- Output Voltage 5 V ±2%

- Output Current up to 300 mA

- Very Low Dropout Voltage

- Output Current Limitation

- Overtemperature Shutdown

- Wide Temperature Range From -40 °C up to 150 °C

- Green Product (RoHS compliant)

- AEC Qualified

#### Description

The TLE7274-2 is a monolithic integrated low dropout voltage regulator for load currents up to 300 mA. An input voltage up to 42 V is regulated to  $V_{Q,nom}$  = 5.0 V with a precision of ±2%. The sophisticated design allows to achieve stable operation even with ceramic output capacitors down to 470 nF. The device is designed for the harsh environment of automotive applications. Therefore it is protected against overload, short circuit and overtemperature conditions by the implemented output current limitation and the overtemperature shutdown circuit. The TLE7274-2 can be also used in all other applications requiring a stabilized 5 V voltage.

Due to its ultra low quiescent current of typically 20  $\mu$ A the TLE7274-2 is dedicated for use in applications permanently connected to  $V_{BAT}$ . An integrated output sink current circuitry keeps the voltage at the Output pin Q below 5.5 V even in case of occuring reverse currents. Thus connected devices are protected from overvoltage damage. For applications requiring extremely low noise levels the Infineon voltage regulator family TLE 42XX and TLE 44XX is more suited than the TLE7274-2. A mV-range output noise on the TLE7274-2 caused by the charge pump operation is unavoidable due to the ultra low quiescent current concept.

| Туре       | Package                | Marking |

|------------|------------------------|---------|

| TLE7274-2E | PG-SSOP-14 Exposed Pad | 7274-2E |

| TLE7274-2D | PG-TO252-3             | 7274-2D |

| TLE7274-2G | PG-TO263-3             | 7274-2G |

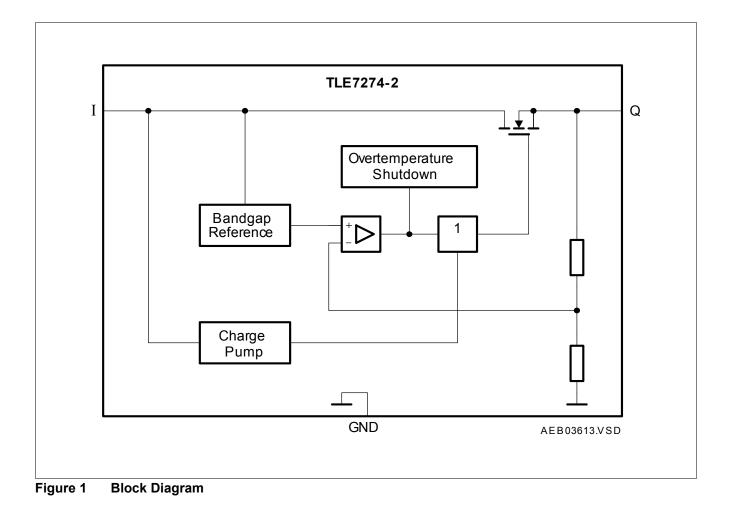

**Block Diagram**

## 2 Block Diagram

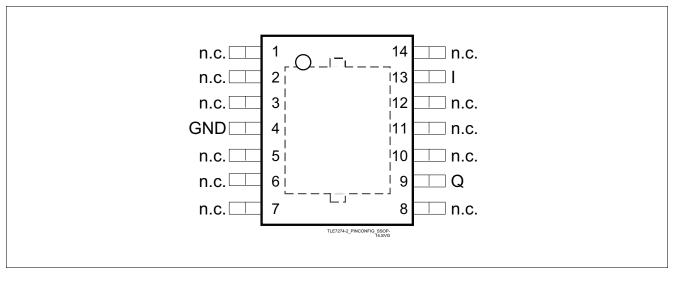

**Pin Configuration**

## 3 Pin Configuration

## 3.1 Pin Assignment PG-SSOP-14 Exposed Pad

Figure 2 Pin Configuration (top view)

## 3.2 Pin Definitions and Functions PG-SSOP-14 Exposed Pad

| Pin No.       | Symbol | Function                                                                                |

|---------------|--------|-----------------------------------------------------------------------------------------|

| 1,2,3,5,6,7   | n.c.   | non connected                                                                           |

|               |        | can be open or connected to GND                                                         |

| 4             | GND    | Ground                                                                                  |

| 8,10,11,12,14 | n.c.   | non connected                                                                           |

|               |        | can be open or connected to GND                                                         |

| 9             | Q      | Output                                                                                  |

|               |        | block to ground with a capacitor close to the IC terminals, respecting the values given |

|               |        | for its capacitance and ESR in "Functional Range" on Page 6                             |

| 13            | 1      | Input                                                                                   |

|               |        | block to ground directly at the IC with a ceramic capacitor                             |

| Pad           | -      | Exposed Pad                                                                             |

|               |        | connect to GND and heatsink area                                                        |

#### **Pin Configuration**

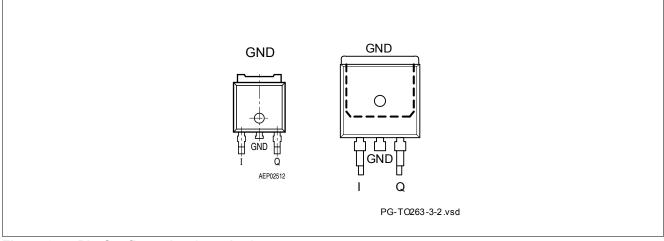

## 3.3 Pin Assignment PG-TO252-3, PG-TO263-3

### Figure 3 Pin Configuration (top view)

### 3.4 Pin Definitions and Functions PG-TO252-3, PG-TO263-3

| Pin No.   | Symbol | Function                                                                                |

|-----------|--------|-----------------------------------------------------------------------------------------|

| 1         | 1      | Input                                                                                   |

|           |        | block to ground directly at the IC with a ceramic capacitor                             |

| 2         | GND    | Ground                                                                                  |

|           |        | internally connected to heat slug                                                       |

| 3         | Q      | Output                                                                                  |

|           |        | block to ground with a capacitor close to the IC terminals, respecting the values given |

|           |        | for its capacitance and ESR in "Functional Range" on Page 6                             |

| Heat Slug | -      | Heat Slug                                                                               |

|           |        | internally connected to GND;                                                            |

|           |        | connect to GND and heatsink area                                                        |

## 4 General Product Characteristics

#### 4.1 Absolute Maximum Ratings

#### Absolute Maximum Ratings<sup>1)</sup>

#### $T_i$ = -40 °C to 150 °C; all voltages with respect to ground, (unless otherwise specified)

| Pos.    | Parameter                                | Symbol  | Limit Values |      | Unit     | Test Condition   |

|---------|------------------------------------------|---------|--------------|------|----------|------------------|

|         |                                          |         | Min.         | Max. |          |                  |

| Input I |                                          |         |              |      |          |                  |

| 4.1.1   | Voltage                                  | $V_1$   | -0.3         | 45   | V        | -                |

| Output  | Q                                        | +       |              | !    | <u>.</u> | -                |

| 4.1.2   | Voltage                                  | VQ      | -0.3         | 6    | V        | -                |

| 4.1.3   | Voltage                                  | VQ      | -0.3         | 6.2  | V        | $t < 10 \ s^{2}$ |

| Temper  | rature                                   | +       |              |      |          | +                |

| 4.1.4   | Junction temperature                     | Tj      | -40          | 150  | °C       | _                |

| 4.1.5   | 1.5 Storage temperature                  |         | -50          | 150  | °C       | -                |

| ESD Su  | sceptibility                             |         |              |      |          |                  |

| 4.1.6   | Human Body Model (HBM) <sup>3)</sup>     | Voltage | -            | 3    | kV       | _                |

| 4.1.7   | Charged Device Model (CDM) <sup>4)</sup> | Voltage | -            | 1.5  | kV       | _                |

1) not subject to production test, specified by design

2) exposure to these absolute maximum ratings for extended periods (t > 10 s) may affect device reliability

3) ESD susceptibility Human Body Model "HBM" according to AEC-Q100-002 - JESD22-A114

4) ESD susceptibility Charged Device Model "CDM" according to ESDA STM5.3.1

- Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

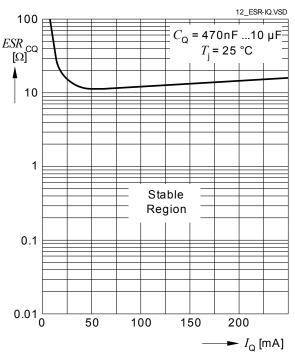

#### 4.2 Functional Range

| Pos.  | Parameter            | Symbol         | Lim  | it Values | Unit | Remarks |

|-------|----------------------|----------------|------|-----------|------|---------|

|       |                      |                | Min. | Max.      |      |         |

| 4.2.1 | Input voltage        | V <sub>1</sub> | 5.5  | 42        | V    | -       |

| 4.2.2 | Output Capacitor's   | CQ             | 470  | -         | nF   | 1)      |

| 4.2.3 | Requirements         | $ESR(C_Q)$     | _    | 10        | Ω    | 2)      |

| 4.2.4 | Junction temperature | Tj             | -40  | 150       | °C   | -       |

1) the minimum output capacitance requirement is applicable for a worst case capacitance tolerance of 30%

2) relevant ESR value at f = 10 kHz

Note: Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

#### **General Product Characteristics**

### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

| Pos.  | Parameter                         | Symbol              |      | Limit Val | ues      | Unit | Conditions                                         |

|-------|-----------------------------------|---------------------|------|-----------|----------|------|----------------------------------------------------|

|       |                                   |                     | Min. | Тур.      | Max.     |      |                                                    |

| TLE72 | 74-2E (PG-SSOP-14 Exposed         | Pad)                |      |           |          |      | I                                                  |

| 4.3.1 | Junction to Case <sup>1)</sup>    | R <sub>thJC</sub>   | -    | 14        | -        | K/W  | measured to exposed pad                            |

| 4.3.2 | Junction to Ambient <sup>1)</sup> | $R_{\mathrm{thJA}}$ | _    | 47        | _        | K/W  | 2)                                                 |

| 4.3.3 |                                   | R <sub>thJA</sub>   | _    | 141       | _        | K/W  | footprint only <sup>3)</sup>                       |

| 4.3.4 |                                   | R <sub>thJA</sub>   | -    | 66        | -        | K/W  | 300 mm <sup>2</sup> heatsink area <sup>3)</sup>    |

| 4.3.5 |                                   | R <sub>thJA</sub>   | -    | 56        | -        | K/W  | 600 mm <sup>2</sup> heatsink area <sup>3)</sup>    |

| TLE72 | 74-2D (PG-TO252-3)                |                     | - 1  | I         | <b>I</b> |      | -                                                  |

| 4.3.1 | Junction to Case <sup>1)</sup>    | R <sub>thJC</sub>   | _    | 6         | -        | K/W  | measured to tab                                    |

| 4.3.2 | Junction to Ambient <sup>1)</sup> | R <sub>thJA</sub>   | -    | 32        | _        | K/W  | 2)                                                 |

| 4.3.3 |                                   | $R_{\mathrm{thJA}}$ | -    | 115       | _        | K/W  | footprint only <sup>3)</sup>                       |

| 4.3.4 |                                   | R <sub>thJA</sub>   | -    | 62        | -        | K/W  | 300 mm <sup>2</sup> heatsink area <sup>3)</sup>    |

| 4.3.5 |                                   | R <sub>thJA</sub>   | -    | 47        | -        | K/W  | 600 mm <sup>2</sup> heatsink area <sup>3)</sup>    |

| TLE72 | 74-2G (PG-TO263-3)                |                     |      |           |          |      |                                                    |

| 4.3.1 | Junction to Case <sup>1)</sup>    | R <sub>thJC</sub>   | -    | 6         | -        | K/W  | measured to exposed pad                            |

| 4.3.2 | Junction to Ambient <sup>1)</sup> | $R_{thJA}$          | _    | 27        | _        | K/W  | 2)                                                 |

| 4.3.3 |                                   | R <sub>thJA</sub>   | -    | 75        | _        | K/W  | footprint only <sup>3)</sup>                       |

| 4.3.4 |                                   | R <sub>thJA</sub>   | -    | 47        | -        | K/W  | 300 mm <sup>2</sup> heatsink area <sup>3)</sup>    |

| 4.3.5 |                                   | R <sub>thJA</sub>   | -    | 38        | -        | K/W  | 600 mm <sup>2</sup> heatsink<br>area <sup>3)</sup> |

1) Not subject to production test, specified by design.

Specified R<sub>thJA</sub> value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm<sup>3</sup> board with 2 inner copper layers (2 x 70µm Cu, 2 x 35µm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

3) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD 51-3 at natural convection on FR4 1s0p board; The Product (Chip+Package) was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with 1 copper layer (1 x 70µm Cu).

### 5.1 Electrical Characteristics Voltage Regulator

#### **Electrical Characteristics**

| V <sub>1</sub> =13.5 | V; $T_{\rm j}$ = -40 °C to | o 150 °C; all voltage | es with res | pect to ground | (unles | s othe | rwise specified) |

|----------------------|----------------------------|-----------------------|-------------|----------------|--------|--------|------------------|

|                      |                            |                       |             |                |        |        |                  |

|        |                                             |                         | -            | -    | •    |      | • •                                                                     |  |

|--------|---------------------------------------------|-------------------------|--------------|------|------|------|-------------------------------------------------------------------------|--|

| Pos.   | Parameter                                   | Symbol                  | Limit Values |      |      | Unit | Measuring Condition                                                     |  |

|        |                                             |                         | Min.         | Тур. | Max. |      |                                                                         |  |

| Output | Q                                           |                         |              |      |      | 1    |                                                                         |  |

| 5.1.1  | Output Voltage                              | V <sub>Q</sub>          | 4.9          | 5.0  | 5.1  | V    | 0.1 mA < $I_Q$ <300 mA<br>6 V < $V_I$ < 16 V                            |  |

| 5.1.2  | Output Voltage                              | V <sub>Q</sub>          | 4.9          | 5.0  | 5.1  | V    | 0.1 mA < $I_Q$ <100 mA<br>6 V < $V_I$ < 40 V                            |  |

| 5.1.3  | Dropout Voltage                             | V <sub>dr</sub>         | -            | 250  | 500  | mV   | $I_{\rm Q} = 200 \text{ mA}$ $V_{\rm dr} = V_{\rm I} - V_{\rm Q}^{(1)}$ |  |

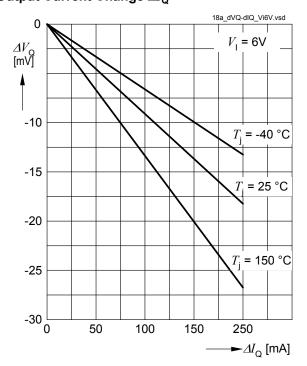

| 5.1.4  | Load Regulation                             | $\Delta V_{ m Q, \ lo}$ | - 40         | 15   | 40   | mV   | $I_{\rm Q}$ = 5 mA to 250 mA                                            |  |

| 5.1.5  | Line Regulation                             | $\Delta V_{Q, li}$      | - 20         | 5    | 20   | mV   | $V_{\rm I}$ = 10 V to 32 V<br>$I_{\rm Q}$ = 5 mA                        |  |

| 5.1.6  | Output Current Limitation                   | IQ                      | 301          | -    | -    | mA   | 1)                                                                      |  |

| 5.1.7  | Output Current Limitation                   | IQ                      | -            | -    | 800  | mA   | $V_{\rm Q} = 0 \rm V$                                                   |  |

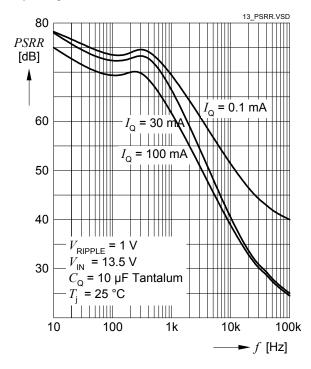

| 5.1.8  | Power Supply Ripple Rejection <sup>2)</sup> | PSRR                    | -            | 60   | -    | dB   | <i>f</i> <sub>r</sub> = 100 Hz; <i>V</i> <sub>r</sub> = 0.5 Vpp         |  |

| 5.1.9  | Temperature Output Voltage Drift            | $\frac{dV_{Q}}{dT}$     | -            | 0.5  | -    | mV/K | -                                                                       |  |

| Curren | t Consumption                               |                         |              |      |      | 1    |                                                                         |  |

| 5.1.10 | Quiescent Current<br>$I_q = I_1 - I_Q$      | Iq                      | -            | 20   | 30   | μA   | $I_{\rm Q} = 0.1 \text{ mA}$<br>$T_{\rm j} = 25 ^{\circ}\text{C}$       |  |

| 5.1.11 | Quiescent Current<br>$I_q = I_1 - I_Q$      | Iq                      | -            | -    | 40   | μA   | $I_{\rm Q}$ = 0.1 mA<br>$T_{\rm j} \le 80 \ ^{\circ}{\rm C}$            |  |

$|I_q - I_l - I_Q| = |T_j \le 80 \text{ °C}$ 1) Measured when the output voltage  $V_Q$  has dropped 100 mV from the nominal value obtained at  $V_l$  = 13.5 V.

2) not subject to production test, specified by design

## 5.2 Typical Performance Characteristics Voltage Regulator

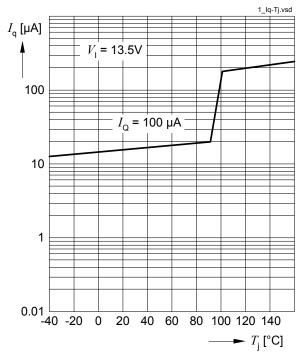

# Current Consumption $I_q$ versus Junction Temperature $T_J$

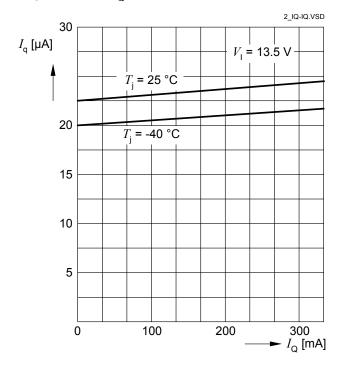

#### Current Consumption $I_q$ versus Output Current $I_Q$

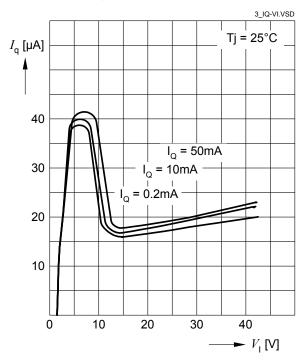

Current Consumption  $I_{\rm q}$  versus Input Voltage  $V_{\rm IQ}$

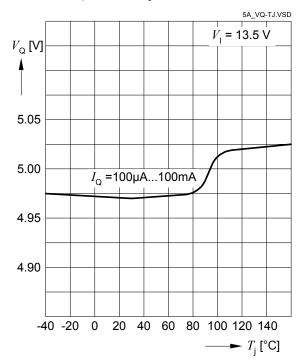

# Output Voltage $V_{Q}$ versus Junction Temperature $T_{J}$

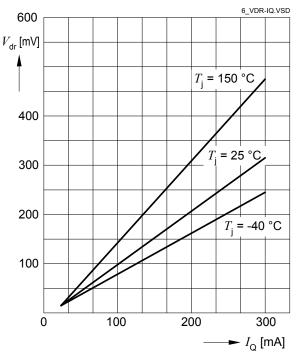

#### Dropout Voltage $V_{\rm dr}$ versus Output Current $I_{\rm Q}$

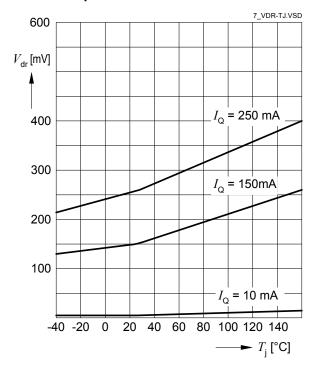

## Dropout Voltage $V_{\rm dr}$ versus Junction Temperature

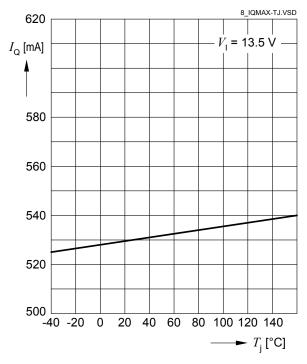

# Maximum Output Current $I_{Q}$ versus Junction Temperature $T_{j}$

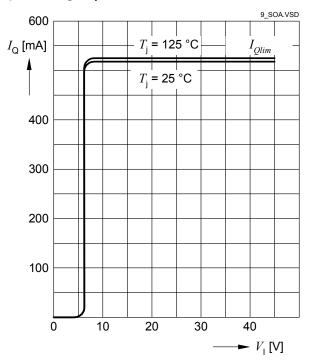

#### Maximum Output Current $I_{Q}$ versus Input Voltage $V_{I}$

#### **Region of Stability**

#### Power Supply Ripple Rejection PSRR versus Frequency f

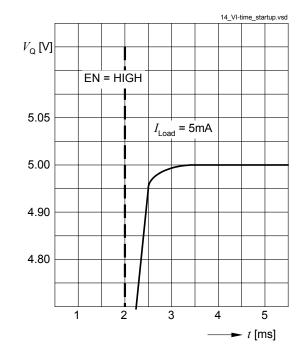

#### Output Voltage $V_{Q}$ Start-up behavior

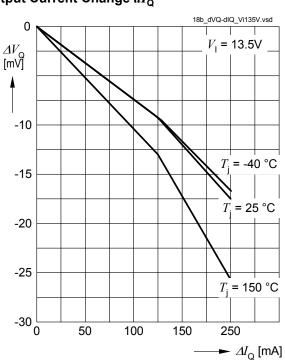

Load Regulation  $\Delta V_{Q}$  versus Output Current Change  $\Delta I_{Q}$

#### Load Regulation $\Delta V_{Q}$ versus Output Current Change $dI_{Q}$

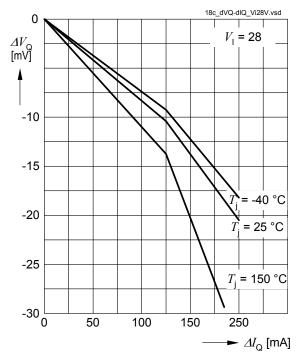

Load Regulation  $\Delta V_{Q}$  versus Output Current Change  $\Delta I_{Q}$

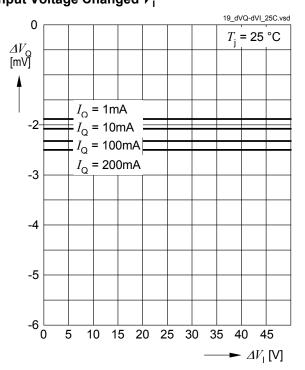

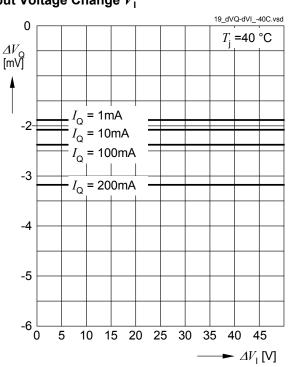

#### Line Regulation $\Delta V_{\rm Q}$ versus Input Voltage Changed $V_{\rm I}$

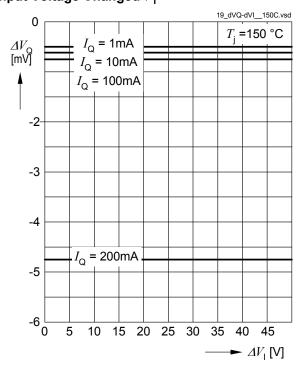

Line Regulation  $\Delta V_{Q}$  versus Input Voltage Changed  $V_{I}$

Line Regulation  $\Delta V_{Q}$  versus Input Voltage Change  $V_{I}$

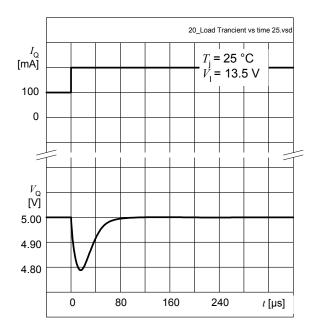

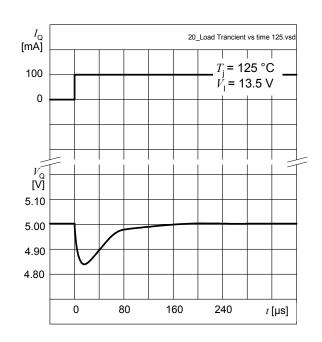

Load Transient Response Peak Voltage  $\Delta V_{Q}$

#### Load Transient Response Peak Voltage $\Delta V_{Q}$

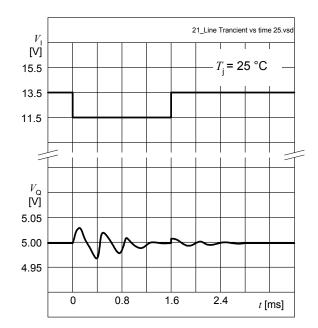

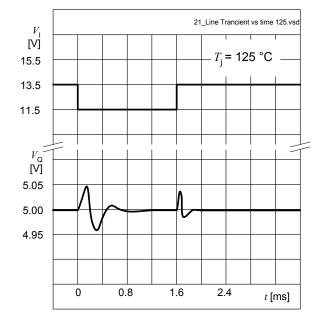

Line Transient Response Peak Voltage  $\Delta V_{\mathsf{Q}}$

ī

#### **Electrical Characteristics**

### Line Transient Response Peak Voltage ${}_{\Delta}V_{\sf Q}$

**Package Outlines**

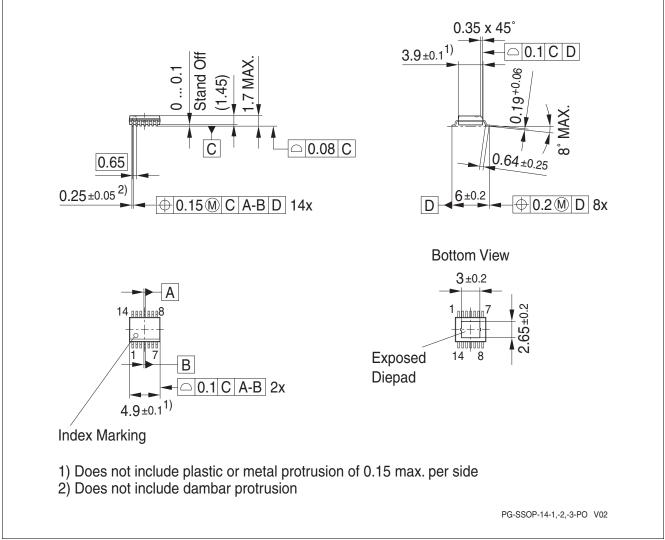

## 6 Package Outlines

## TLE7274-2

#### **Package Outlines**

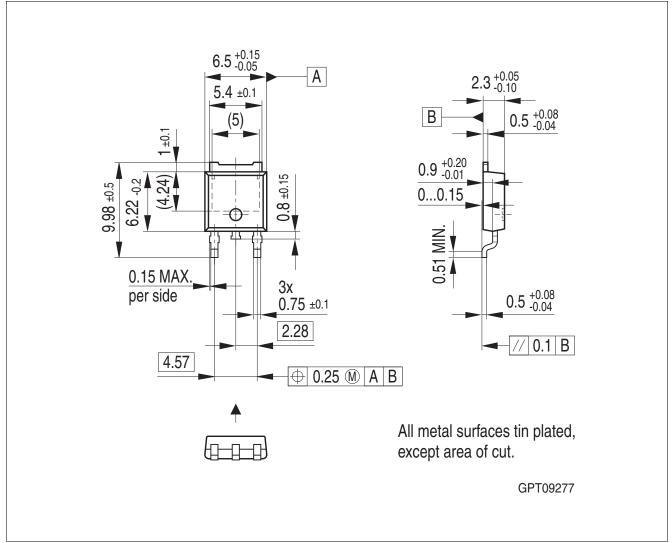

Figure 5 PG-TO252-3

#### **Package Outlines**

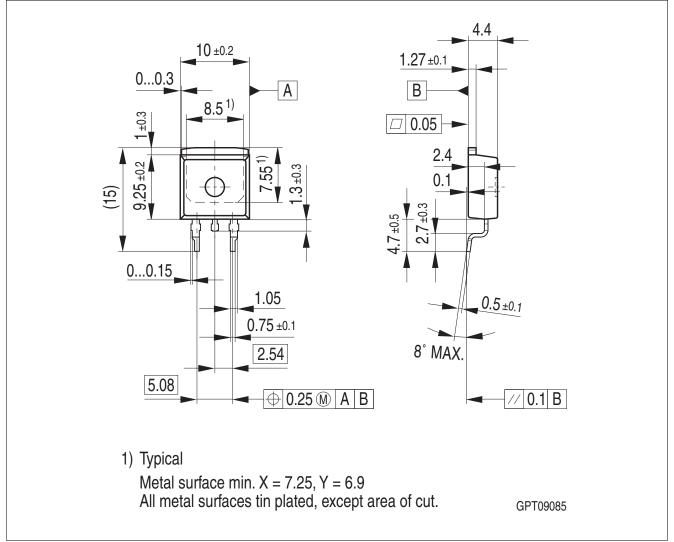

#### Figure 6 PG-TO263-3

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

For further information on alternative packages, please visit our website: http://www.infineon.com/packages.

## 7 Revision History

| Revision | Date       | Changes                                                                            |  |  |  |  |

|----------|------------|------------------------------------------------------------------------------------|--|--|--|--|

| 1.01     | 2011-11-30 | updated version data sheet: (no change in function or design of device)            |  |  |  |  |

|          |            | Package TO263-3 corrected to TO263-3-2.                                            |  |  |  |  |

|          |            | in "Overview" on Page 2 Package Drawing corrected.                                 |  |  |  |  |

|          |            | in "Pin Assignment PG-TO252-3, PG-TO263-3" on Page 5 Pin Assignment for            |  |  |  |  |

|          |            | TO263-3 corrected and Headlines added.                                             |  |  |  |  |

|          |            | in Figure 6 "PG-TO263-3" on Page 18 Package Outlines corrected                     |  |  |  |  |

|          |            | in "Electrical Characteristics Voltage Regulator" on Page 8, former Item           |  |  |  |  |

|          |            | 5.1.12 "Current Consumption, Regulator Disabled" removed, in Condition of          |  |  |  |  |

|          |            | Item 5.1.10 and Item 5.1.11 " $V_{EN}$ = 5 V" removed: Non relevant information as |  |  |  |  |

|          |            | TLE7270-2 does not implement Enable Feature                                        |  |  |  |  |

| 1.0      | 2009-06-01 | initial version data sheet                                                         |  |  |  |  |

Edition 2011-11-30

Published by Infineon Technologies AG 81726 Munich, Germany © 2011 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LDO Voltage Regulators category:

Click to view products by Infineon manufacturer:

Other Similar products are found below :

AP7363-SP-13 L79M05TL-E PT7M8202B12TA5EX TCR3DF185,LM(CT MP2013GQ-33-Z 059985X NCP4687DH15T1G 701326R TCR2EN28,LF(S NCV8170AXV250T2G TCR2EN18,LF(S AP7315-25W5-7 IFX30081LDVGRNXUMA1 NCV47411PAAJR2G AP2113KTR-G1 AP2111H-1.2TRG1 ZLDO1117QK50TC AZ1117IH-1.8TRG1 TCR3DG12,LF MIC5514-3.3YMT-T5 MIC5512-1.2YMT-T5 MIC5317-2.8YM5-T5 SCD7912BTG NCP154MX180270TAG SCD33269T-5.0G NCV8170BMX330TCG NCV8170AMX120TCG NCP706ABMX300TAG NCP153MX330180TCG NCP114BMX075TCG MC33269T-3.5G CAT6243-ADJCMT5T TCR3DG33,LF AP2127N-1.0TRG1 TCR4DG35,LF LT1117CST-3.3 LT1117CST-5 TAR5S15U(TE85L,F) TAR5S18U(TE85L,F) TCR3UG19A,LF TCR4DG105,LF NCV8170AMX360TCG MIC94310-NYMT-T5 TLE4268GSXUMA2 NCV8186BMN175TAG NCP715SQ15T2G MIC5317-3.0YD5-T5 NCV563SQ18T1G MIC5317-2.8YD5-T5 NCP715MX30TBG