# **TLE75008-ESD**

# SPIDER+ 12V SPI Driver for Enhanced Relay Control

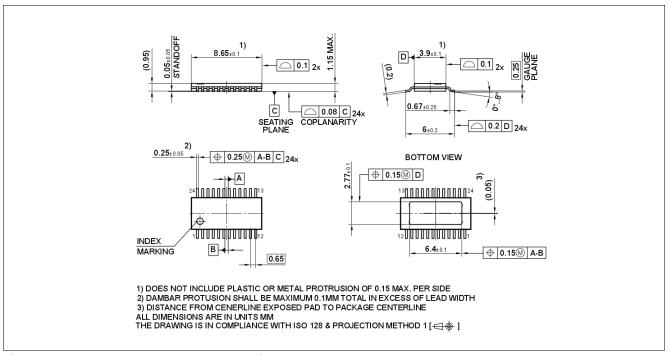

| Package | PG-TSDSO-24 |

|---------|-------------|

| Marking | TLE75008ESD |

### 1 Overview

#### **Applications**

- Low-side switches for 12 V in automotive or industrial applications such as lighting, heating, motor driving, energy and power distribution

- Especially designed for driving relays, LEDs and motors.

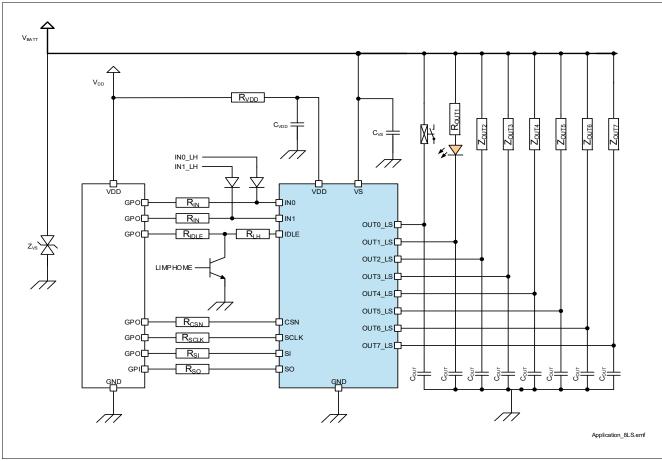

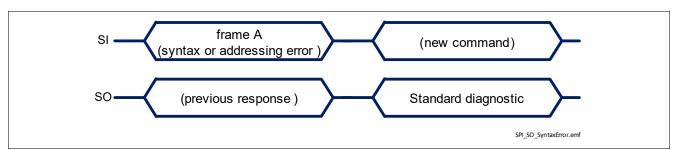

Figure 1 TLE75008-ESD Application Diagram

# **TLE75008-ESD**

# SPIDER+ 12V

#### **Overview**

#### **Basic Features**

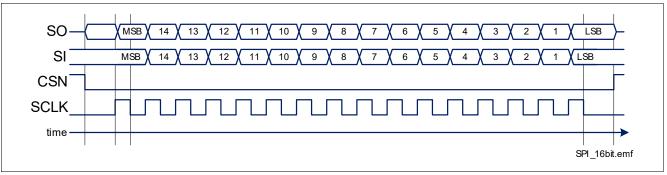

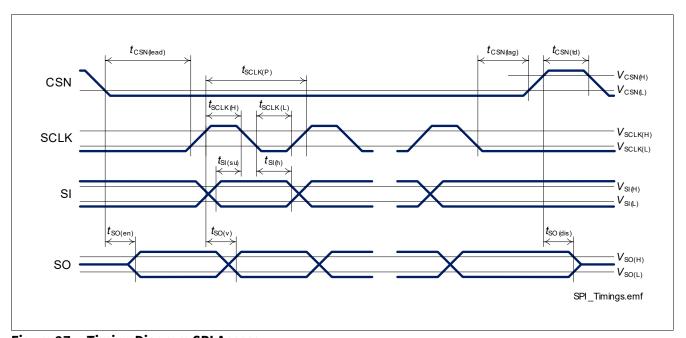

- 16-bit serial peripheral interface for control and diagnosis

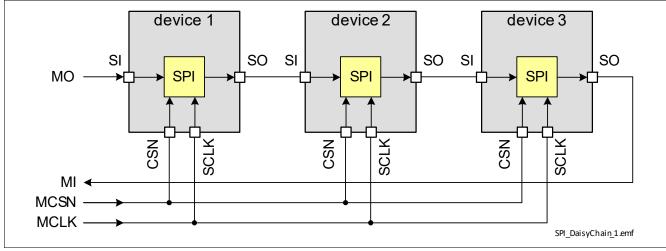

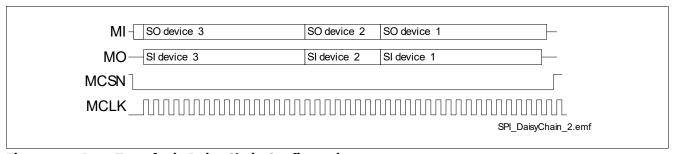

- Daisy Chain capability SPI also compatible with 8-bit SPI devices

- 2 CMOS compatible parallel input pins with Input Mapping functionality

- Cranking capability down to  $V_s = 3.0 \text{ V}$  (supports LV124)

- Digital supply voltage range compatible with 3.3 V and 5 V microcontrollers

- Very low quiescent current (with usage of IDLE pin)

- Limp Home mode (with usage of IDLE and IN pins)

- Green Product (RoHS compliant)

- **AEC Qualified**

#### **Protection Features**

- Reverse battery protection on  $V_s$  without external components

- Short circuit to ground and battery protection

- Stable behavior at under voltage conditions ("Lower Supply Voltage Range for Extended Operation")

- Over Current latch OFF

- Thermal shutdown latch OFF

- Overvoltage protection

- Loss of ground protection

- Loss of battery protection

- Electrostatic discharge (ESD) protection

#### **Diagnostic Features**

- Latched diagnostic information via SPI register

- Over Load detection at ON state

- Open Load detection at OFF state using Output Status Monitor function

- **Output Status Monitor**

- **Input Status Monitor**

#### **Application Specific Features**

- Fail-safe activation via Input pins in Limp-Home Mode

- SPI with Daisy Chain capability

- Safe operation at low battery voltage (cranking)

#### **Description**

The TLE75008-ESD is an eight channel low-side power switch in PG-TSDSO-24 package providing embedded protective functions. It is specially designed to control relays and LEDs in automotive and industrial applications.

A serial peripheral interface (SPI) is utilized for control and diagnosis of the loads as well as of the device. For direct control and PWM there are two input pins available connected to two outputs by default. Additional or different outputs can be controlled by the same input pins (programmable via SPI).

# infineon

#### Overview

Table 1 Product Summary

| Parameter                                                   | Symbol               | Values                                    |

|-------------------------------------------------------------|----------------------|-------------------------------------------|

| Analog supply voltage                                       | V <sub>S</sub>       | 3.0 V 28 V                                |

| Digital supply voltage                                      | $V_{DD}$             | 3.0 V 5.5 V                               |

| Minimum overvoltage protection                              | $V_{S(AZ)}$          | 42 V (see <b>Chapter 8.5</b> for details) |

| Maximum on-state resistance at $T_J = 150 ^{\circ}\text{C}$ | R <sub>DS(ON)</sub>  | 2.2 Ω                                     |

| Nominal load current ( $T_A = 85$ °C, all channels)         | I <sub>L(NOM)</sub>  | 330 mA                                    |

| Maximum Energy dissipation - repetitive                     | E <sub>AR</sub>      | 10 mJ @ I <sub>L(EAR)</sub> = 220 mA      |

| Minimum Drain to Source clamping voltage                    | $V_{\rm DS(CL)}$     | 42 V                                      |

| Maximum overload switch OFF threshold                       | I <sub>L(OVL0)</sub> | 2.3 A                                     |

| Maximum total quiescent current at $T_J \le 85$ °C          | I <sub>SLEEP</sub>   | 5 μΑ                                      |

| Maximum SPI clock frequency                                 | $f_{\sf SCLK}$       | 5 MHz                                     |

#### **Detailed Description**

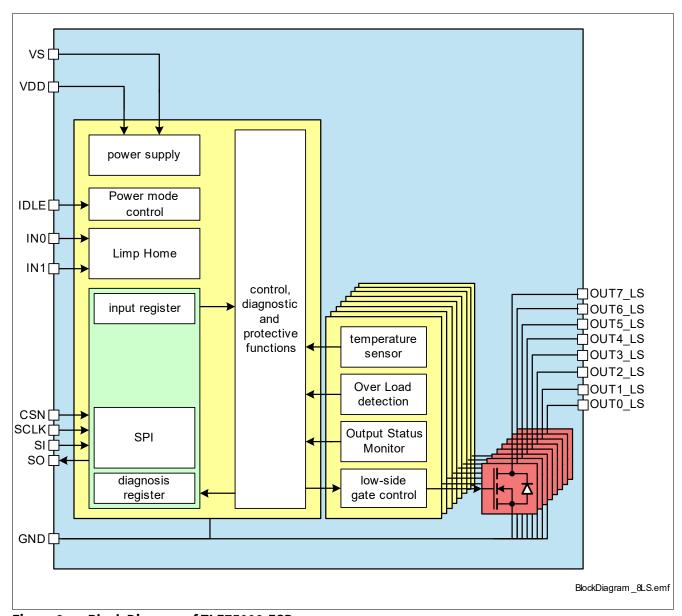

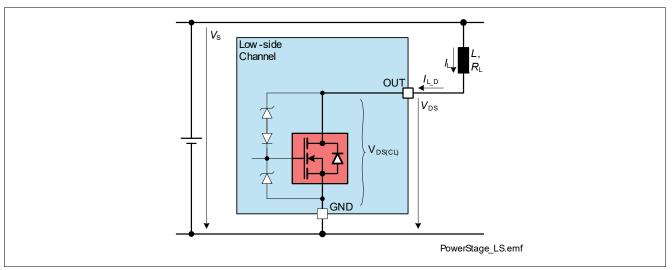

The TLE75008-ESD is an eight channel low-side switch providing embedded protective functions. The output stages incorporate eight low-side switches (typical  $R_{\rm DS(ON)}$  at  $T_{\rm J} = 25^{\circ}{\rm C}$  is 1  $\Omega$ ).

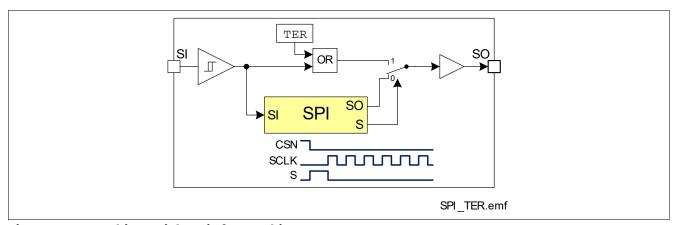

The 16-bit serial peripheral interface (SPI) is utilized to control and diagnose the device and the loads. The SPI interface provides daisy chain capability in order to assemble multiple devices (also devices with 8 bit SPI) in one SPI chain by using the same number of microcontroller pins.

This device is designed for low supply voltage operation, therefore being able to keep its state at low battery voltage ( $V_S \ge 3.0 \text{ V}$ ). The SPI functionality, including the possibility to program the device, is available only when the digital power supply is present (see **Chapter 6** for more details).

The TLE75008-ESD is equipped with two input pins that are connected to two outputs, making them controllable even when the digital supply voltage is not available. With the Input Mapping functionality it is possible to connect the input pins to different outputs, or assign more outputs to the same input pin. In this case more channels can be controlled with one signal applied to one input pin.

In Limp Home mode (Fail-Safe mode) the input pins are directly routed to channels 2 and 3. When IDLE pin is "low", it is possible to activate the two channels using the input pins independently from the presence of the digital supply voltage.

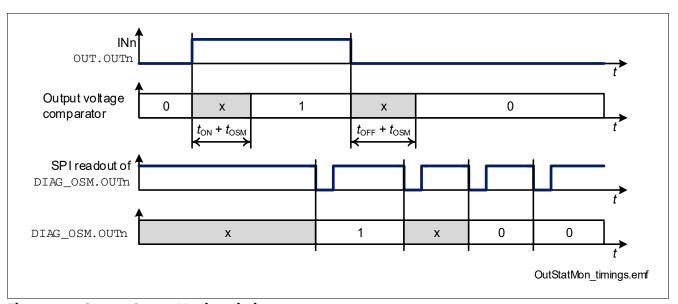

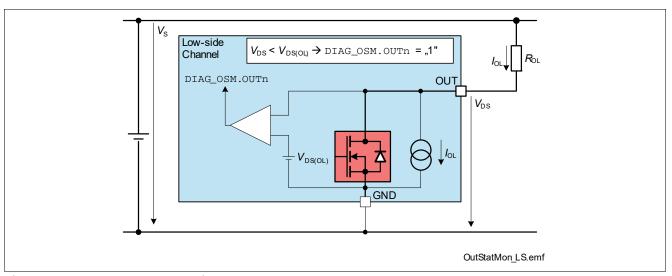

The device provides diagnosis of the load via Open Load at OFF state (with **DIAG\_OSM.OUTn** bits) and short circuit detection. For Open Load at OFF state detection, a internal current source  $l_{OI}$  can be activated via SPI.

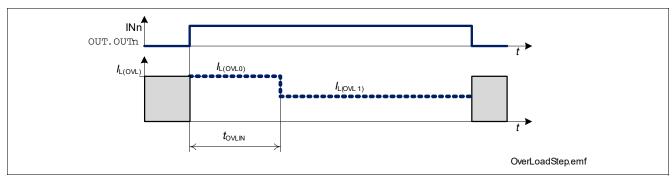

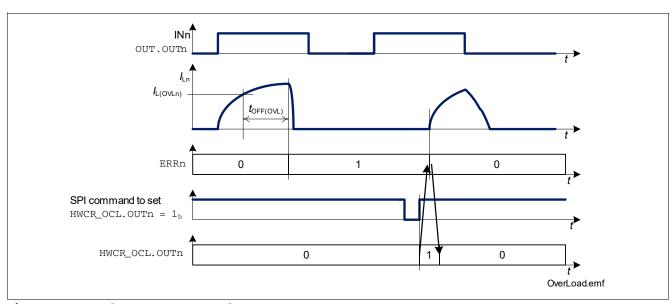

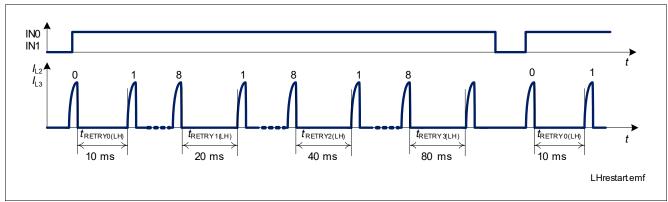

Each output stage is protected against short circuit. In case of Overload, the affected channel switches OFF when the Overload Detection Current  $I_{L(OVLn)}$  is reached and can be reactivated via SPI. In Limp Home mode operation, the channels connected to an input pin set to "high" restart automatically after Output Restart time  $t_{RETRY(LH)}$  is elapsed. Temperature sensors are available for each channel to protect the device against Over Temperature.

The power transistors are built by N-channel power MOSFET. The inputs are ground referenced TTL compatible. The device is monolithically integrated in Smart Power Technology.

**Block Diagram and Terms**

# 2 Block Diagram and Terms

# 2.1 Block Diagram

Figure 2 Block Diagram of TLE75008-ESD

#### **Block Diagram and Terms**

#### 2.2 Terms

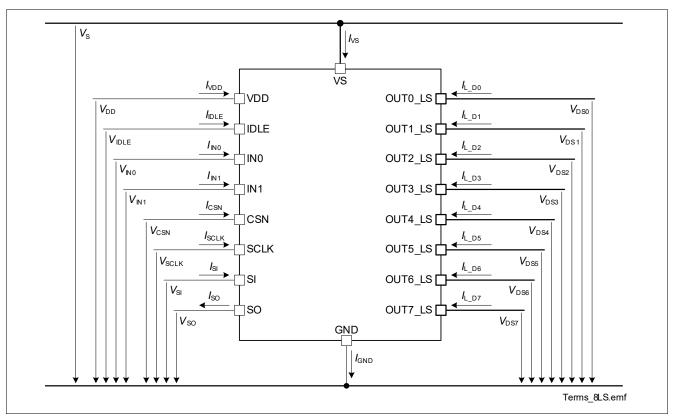

Figure 3 shows all terms used in this data sheet, with associated convention for positive values.

Figure 3 Voltage and Current definition

In all tables of electrical characteristics the channel related symbols without channel numbers are valid for each channel separately (e.g.  $V_{DS}$  specification is valid for  $V_{DS0}$  ...  $V_{DS7}$ ).

Furthermore, parameters relative to output current can be indicated without specifying whether the current is going into the Drain pin or going out of the Source pin, unless otherwise specified. For instance, nominal output current can be indicated in the following ways:  $I_{L(NOM)} I_{L_LS(NOM)} I_{L_D(NOM)}$

All SPI registers bits are marked as follows: ADDR.PARAMETER (e.g. HWCR.RST) with the exception of the bits in the Diagnosis frames which are marked only with PARAMETER (e.g. UVRVS).

#### **Pin Configuration**

# **3** Pin Configuration

# 3.1 Pin Assignment

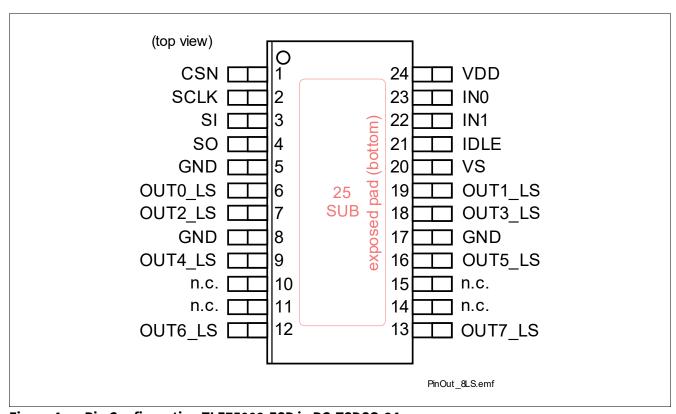

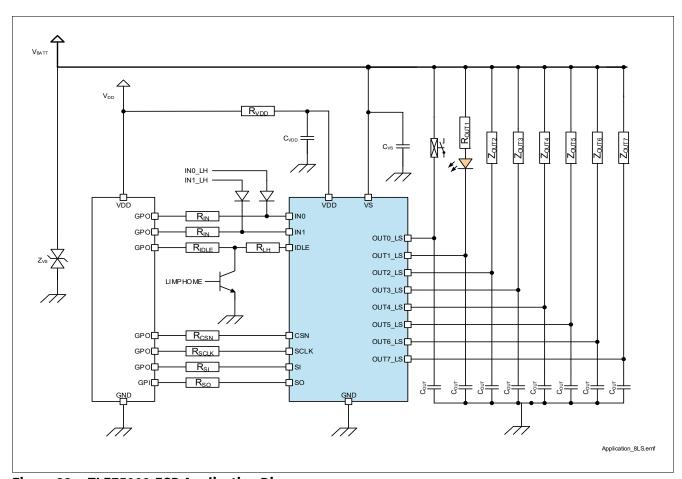

Figure 4 Pin Configuration TLE75008-ESD in PG-TSDSO-24

# **Pin Configuration**

# 3.2 Pin Definitions and Functions

| Pin         | Symbol       | I/O  | Function                                                                                                           |

|-------------|--------------|------|--------------------------------------------------------------------------------------------------------------------|

| Power Supp  | ply Pins     |      |                                                                                                                    |

| 20          | VS           | -    | Analog supply V <sub>S</sub> Positive supply voltage for power switches gate control (incl. protections)           |

| 24          | VDD          | -    | <b>Digital supply <math>V_{\rm DD}</math></b> Supply voltage for SPI with support function to $V_{\rm S}$          |

| 5, 8, 17    | GND          | _    | Ground Ground connection                                                                                           |

| SPI Pins    |              | •    |                                                                                                                    |

| 1           | CSN          | I    | Chip Select "low" active, integrated pull-up to $V_{\rm DD}$                                                       |

| 2           | SCLK         | I    | Serial Clock "high" active, integrated pull-down to ground                                                         |

| 3           | SI           | I    | Serial Input "high" active, integrated pull-down to ground                                                         |

| 4           | so           | 0    | Serial Output "Z" (tri-state) when CSN is "high"                                                                   |

| Input and S | tand-by Pins | - 11 |                                                                                                                    |

| 21          | IDLE         | 1    | Idle mode power mode control, "high" activates Idle mode, integrated pull-down to ground                           |

| 23          | INO          | I    | Input pin 0 connected to channel 2 by default and in Limp Home mode, "high" active, integrated pull-down to ground |

| 22          | IN1          | I    | Input pin 1 connected to channel 3 by default and in Limp Home mode, "high" active, integrated pull-down to ground |

| Power Oup   | ut Pins      |      |                                                                                                                    |

| 6           | OUT0_LS      | 0    | Drain of low-side power transistor (channel 0)                                                                     |

| 7           | OUT2_LS      | 0    | Drain of low-side power transistor (channel 2)                                                                     |

| 9           | OUT4_LS      | 0    | Drain of low-side power transistor (channel 4)                                                                     |

| 12          | OUT6_LS      | 0    | Drain of low-side power transistor (channel 6)                                                                     |

| 13          | OUT7_LS      | 0    | Drain of low-side power transistor (channel 7)                                                                     |

| 16          | OUT5_LS      | 0    | Drain of low-side power transistor (channel 5)                                                                     |

| 18          | OUT3_LS      | 0    | Drain of low-side power transistor (channel 3)                                                                     |

| 19          | OUT1_LS      | 0    | Drain of low-side power transistor (channel 1)                                                                     |

## **Pin Configuration**

| Pin            | Symbol         | I/O    | Function                                                                                                                                                                  |

|----------------|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Not Connected  | d pins / Cooli | ng Tab |                                                                                                                                                                           |

| 10, 11, 14, 15 | n.c.           | _      | Not Connected, internally not bonded                                                                                                                                      |

| 25             | GND            | -      | Exposed pad It is recommended to connect it to PCB ground for cooling and EMC - not usable as electrical GND pin. Electrical ground must be provided by pins 5, 8 and 17. |

# infineon

#### **General Product Characteristics**

# **4** General Product Characteristics

# 4.1 Absolute Maximum Ratings

Table 2 Absolute Maximum Ratings 1)

$T_{\rm J}$  = -40 °C to +150 °C

all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                   | Symbol               |       | Value | es.                  | Unit | Note or                                                                                                              | Number   |

|-------------------------------------------------------------|----------------------|-------|-------|----------------------|------|----------------------------------------------------------------------------------------------------------------------|----------|

|                                                             |                      | Min.  | Тур.  | Max.                 |      | <b>Test Condition</b>                                                                                                |          |

| Supply Voltages                                             | <u>'</u>             | •     | -     | +                    |      |                                                                                                                      |          |

| Analog Supply voltage                                       | $V_{S}$              | -0.3  | _     | 28                   | ٧    | _                                                                                                                    | P_4.1.1  |

| Digital Supply voltage                                      | $V_{DD}$             | -0.3  | -     | 5.5                  | ٧    | -                                                                                                                    | P_4.1.2  |

| Supply voltage for load dump protection                     | $V_{S(LD)}$          | -     | -     | 42                   | V    | 2)                                                                                                                   | P_4.1.3  |

| Supply voltage for short circuit protection (single pulse)  | V <sub>S(SC)</sub>   | 0     | -     | 28                   | V    | -                                                                                                                    | P_4.1.4  |

| Reverse polarity voltage                                    | -V <sub>S(REV)</sub> | _     | -     | 16                   | V    | $T_{J(0)} = 25$ °C<br>$t \le 2$ min<br>See <b>Chapter 11</b> for general setup.<br>$R_L = 70 \Omega$ on all channels | P_4.1.5  |

| Current through VS pin                                      | I <sub>VS</sub>      | -10   | _     | 10                   | mA   | t ≤ 2 min                                                                                                            | P_4.1.7  |

| Current through VDD pin                                     | I <sub>VDD</sub>     | -50   | -     | 10                   | mA   | t ≤ 2 min                                                                                                            | P_4.1.8  |

| Power Stages                                                |                      |       | ·     |                      |      |                                                                                                                      |          |

| Load current                                                | / <sub>L</sub>       | -     | _     | I <sub>L(OVL0)</sub> | Α    | single channel                                                                                                       | P_4.1.9  |

| Voltage at power transistor                                 | $V_{DS}$             | -0.3  | _     | 42                   | ٧    | _                                                                                                                    | P_4.1.10 |

| Maximum energy dissipation single pulse                     | E <sub>AS</sub>      | _     | -     | 50                   | mJ   | $T_{J(0)} = 25 ^{\circ}\text{C}$ $I_{L(0)} = 2^*I_{L(EAR)}$                                                          | P_4.1.13 |

| Maximum energy dissipation single pulse                     | E <sub>AS</sub>      | -     | -     | 25                   | mJ   | $T_{J(0)} = 150  ^{\circ}\text{C}$ $I_{L(0)} = 400  \text{mA}$                                                       | P_4.1.14 |

| Maximum energy dissipation repetitive pulses - $I_{L(EAR)}$ | E <sub>AR</sub>      | -     | _     | 10                   | mJ   | 4) $T_{J(0)} = 85 ^{\circ}\text{C}$ $I_{L(0)} = I_{L(EAR)}$ $2*10^6 ^{\circ}\text{cycles}$                           | P_4.1.15 |

| IDLE pin                                                    |                      |       |       |                      |      |                                                                                                                      |          |

| Voltage at IDLE pin                                         | $V_{IDLE}$           | -0.3  |       | 5.5                  | V    | -                                                                                                                    | P_4.1.23 |

| Current through IDLE pin                                    | I <sub>IDLE</sub>    | -0.75 |       | 0.75                 | mA   | _                                                                                                                    | P_4.1.25 |

#### **General Product Characteristics**

#### Absolute Maximum Ratings (cont'd)1) Table 2

$T_{\rm J}$  = -40 °C to +150 °C

all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                            | Symbol            | Values |          |                      | Unit                                  | Note or               | Number   |

|--------------------------------------|-------------------|--------|----------|----------------------|---------------------------------------|-----------------------|----------|

|                                      |                   | Min.   | Тур.     | Max.                 |                                       | <b>Test Condition</b> |          |

| Current through IDLE pin             | I <sub>IDLE</sub> | -10.0  |          | 2.0                  | mA                                    | <i>t</i> ≤ 2 min.     | P_4.1.26 |

| Input Pins                           |                   |        |          |                      |                                       |                       |          |

| Voltage at input pins                | V <sub>IN</sub>   | -0.3   |          | 5.5                  | V                                     | _                     | P_4.1.28 |

| Current through input pins           | I <sub>IN</sub>   | -0.75  |          | 0.75                 | mA                                    | -                     | P_4.1.30 |

| Current through input pins           | I <sub>IN</sub>   | -10.0  |          | 2.0                  | mA                                    | <i>t</i> ≤ 2 min.     | P_4.1.31 |

| SPI Pins                             |                   | ·      |          |                      |                                       |                       |          |

| Voltage at chip select pin           | $V_{\rm CSN}$     | -0.3   |          | 5.5                  | V                                     | -                     | P_4.1.33 |

| Current through chip select pin      | I <sub>CSN</sub>  | -0.75  |          | 0.75                 | mA                                    | -                     | P_4.1.34 |

| Current through chip select pin      | I <sub>CSN</sub>  | -10.0  |          | 2.0                  | mA                                    | <i>t</i> ≤ 2 min.     | P_4.1.35 |

| Voltage at serial clock pin          | $V_{\rm SCLK}$    | -0.3   |          | 5.5                  | V                                     |                       | P_4.1.37 |

| Current through serial clock pin     | I <sub>SCLK</sub> | -0.75  |          | 0.75                 | mA                                    | -                     | P_4.1.38 |

| Current through serial clock pin     |                   | -10.0  |          | 2.0                  | mA                                    | <i>t</i> ≤ 2 min.     | P_4.1.39 |

| Voltage at serial input pin          | $V_{\rm SI}$      | -0.3   |          | 5.5                  | V                                     |                       | P_4.1.41 |

| Current through serial input pin     | I <sub>SI</sub>   | -0.75  |          | 0.75                 | mA                                    | -                     | P_4.1.42 |

| Current through serial input pin     | I <sub>SI</sub>   | -10.0  |          | 2.0                  | mA                                    | <i>t</i> ≤ 2 min.     | P_4.1.43 |

| Voltage at serial output pin SO      | $V_{SO}$          | -0.3   |          | V <sub>DD</sub> +0.3 | V                                     |                       | P_4.1.58 |

| Current through serial output pin SO | I <sub>so</sub>   | -0.75  |          | 0.75                 | mA                                    |                       | P_4.1.45 |

| Current through serial output pin SO | I <sub>so</sub>   | -2.0   |          | 10.0                 | mA                                    | <i>t</i> ≤ 2 min.     | P_4.1.46 |

| Temperatures                         | 1                 |        | <b>"</b> | 1                    |                                       |                       | -        |

| Junction Temperature                 | $T_{J}$           | -40    | -        | 150                  | °C                                    | _                     | P_4.1.48 |

| Storage Temperature                  | $T_{\rm stg}$     | -55    | _        | 150                  | °C                                    | _                     | P_4.1.49 |

| ESD Susceptibility                   |                   | *      |          | !                    | 1                                     |                       | <u>'</u> |

| ESD Susceptibility HBM               | $V_{ESD}$         | -4     | -        | 4                    | kV                                    | 5)                    | P_4.1.50 |

| OUT pins vs. V <sub>S</sub> or GND   |                   |        |          |                      |                                       | НВМ                   |          |

| ESD Susceptibility HBM               | $V_{ESD}$         | -2     | -        | 2                    | kV                                    | 5)                    | P_4.1.51 |

| other pins                           |                   |        |          |                      |                                       | HBM                   |          |

| ESD Susceptibility CDM               | $V_{ESD}$         | -750   | _        | 750                  | V                                     | 6)<br>CDM             | P_4.1.52 |

| Pin 1, 12, 13, 24 (corner pins)      | 17                | F00    |          | 500                  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | CDM                   | D 4154   |

| ESD Susceptibility CDM               | $V_{ESD}$         | -500   | _        | 500                  | V                                     | CDM                   | P_4.1.54 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> For a duration of  $t_{\rm on}$  = 400 ms;  $t_{\rm on}/t_{\rm off}$  = 10%; limited to 100 pulses

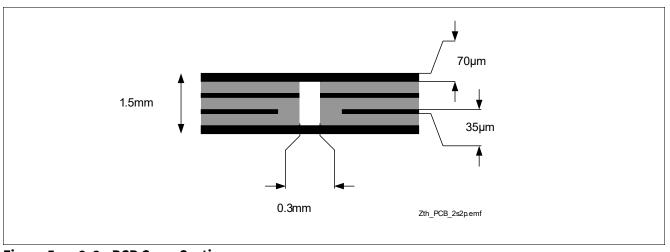

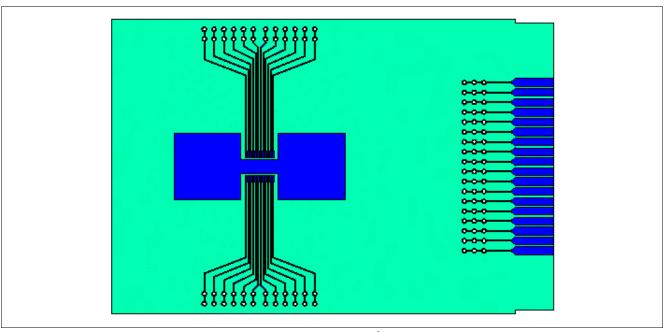

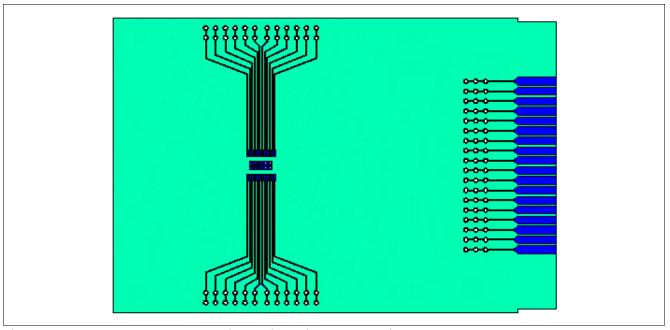

<sup>3)</sup> Device is mounted on a FR4 2s2p board according to Jedec JESD51-2,-5,-7 at natural convection; the Product (Chip+Package) was simulated on a 76.2 \*114.3 \*1.5 mm board with 2 inner copper layers ( $2 * 70 \mu m Cu$ ,  $2 * 35 \mu m Cu$ ). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

#### **General Product Characteristics**

- 4) Pulse shape represents inductive switch off:  $I_L(t) = I_L(0) \times (1 t / t_{pulse})$ ;  $0 < t < t_{pulse}$

- 5) ESD susceptibility, Human Body Model "HBM" according to AEC Q100-002

- 6) ESD susceptibility, Charged Device Mode "CDM" according to AECQ100-011 Rev D

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

## 4.2 Functional Range

Table 3 Functional range

| Parameter                                         | Symbol              | ol Values |      |      | Unit | Note or                      | Number  |

|---------------------------------------------------|---------------------|-----------|------|------|------|------------------------------|---------|

|                                                   |                     | Min.      | Тур. | Max. |      | Test Condition               |         |

| Supply Voltage Range for Normal Operation         | V <sub>S(NOR)</sub> | 7         | -    | 18   | V    | -                            | P_4.2.1 |

| Upper Supply Voltage Range for Extended Operation | $V_{S(EXT,UP)}$     | 18        | -    | 28   | V    | Parameter deviation possible | P_4.2.2 |

| Lower Supply Voltage Range for Extended Operation | $V_{S(EXT,LOW)}$    | 3         | -    | 7    | V    | Parameter deviation possible | P_4.2.3 |

| Junction Temperature                              | T <sub>J</sub>      | -40       | _    | 150  | °C   | _                            | P_4.2.4 |

| Logic supply voltage                              | $V_{ m DD}$         | 3         | _    | 5.5  | V    | _                            | P_4.2.5 |

Note:

Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

#### **General Product Characteristics**

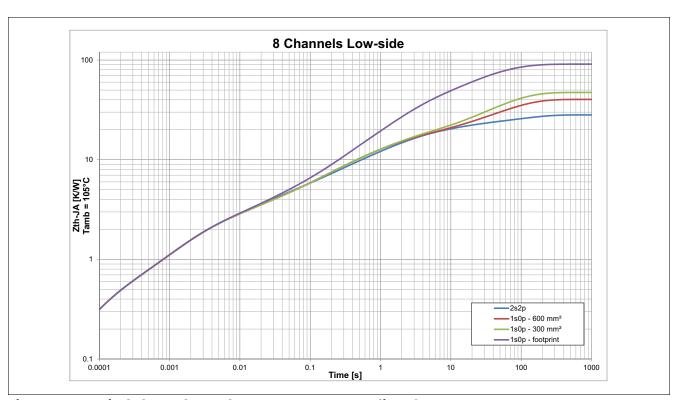

#### **Thermal Resistance** 4.3

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

**Thermal Resistance** Table 4

| Parameter                   | Symbol Values      |      |      | 5    | Unit | Note or                          | Number  |

|-----------------------------|--------------------|------|------|------|------|----------------------------------|---------|

|                             |                    | Min. | Тур. | Max. |      | Test Condition                   |         |

| Junction to Soldering Point | R <sub>thJSP</sub> | -    | 3    | 5    | K/W  | measured to exposed pad (pin 25) | P_4.3.1 |

| Junction to Ambient         | R <sub>thJA</sub>  | -    | 28   | -    | K/W  | 1)2)                             | P_4.3.3 |

<sup>1)</sup> not subject to production test, specified by design

#### 4.3.1 PCB set up

Figure 5 2s2p PCB Cross Section

<sup>2)</sup> Specified  $R_{th,IA}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; the Product (Chip+Package) was simulated on a 76.2 \* 114.3 \* 1.5 mm board with 2 inner copper layers (2 \* 70 μm Cu, 2 \* 35 μm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

# infineon

#### **General Product Characteristics**

PC Board for Thermal Simulation with 600 mm<sup>2</sup> Cooling Area Figure 6

PC Board for Thermal Simulation with 2s2p Cooling Area Figure 7

# infineon

#### **General Product Characteristics**

## 4.3.2 Thermal Impedance

Figure 8 Typical Thermal Impedance. PCB setup according Chapter 4.3.1

Figure 9 Typical Thermal Resistance. PCB setup 1s0p

#### **Control Pins**

#### 5 Control Pins

The device has three pins (INO, IN1 and IDLE) to control directly the device without using SPI.

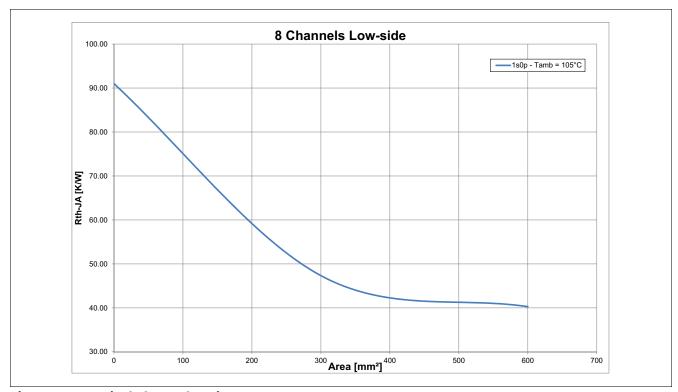

#### 5.1 Input pins

TLE75008-ESD has two input pins available. Each input pin is connected by default to one channel (IN0 to channel 2, IN1 to channel 3). Input Mapping Registers **MAPIN0** and **MAPIN1** can be programmed to connect additional or different channels to each input pin, as shown in **Figure 10**. The signals driving the channels are an OR combination between **OUT** register status, IN0 and IN1 (according to Input Mapping registers status).

Figure 10 Input Mapping

The logic level of the input pins can be monitored via the Input Status Monitor Register (INST). The Input Status Monitor is operative also when TLE75008-ESD is in Limp Home mode. If one of the Input pins is set to "high" and the IDLE pin is set to "low", the device switches into Limp Home mode and activates the channel mapped by default to the input pins. See **Chapter 6.1.5** for further details.

#### 5.2 IDLE pin

The IDLE pin is used to bring the device into Sleep mode operation when is set to "low" and all input pins are set to "low". When IDLE pin is set to "low" while one of the input pins is set to "high" the device enters Limp Home mode.

To ensure a proper mode transition, IDLE pin must be set for at least  $t_{\text{IDLE2SLEEP}}$  (P\_6.3.54, transition from "high" to "low") or  $t_{\text{SLEEP2IDLE}}$  (P\_6.3.53, transition from "low" to "high").

Setting the IDLE pin to "low" has the following consequences:

- All registers in the SPI are reset to default values

- V<sub>DD</sub> and V<sub>S</sub> Undervoltage detection circuits are disabled to decrease current consumption (if both inputs are set to "low")

#### **Control Pins**

• No SPI communication is allowed (SO pin remains in high impedance state also when CSN pin is set to "low") if both input pins are set to "low"

# infineon

#### **Control Pins**

# **5.3** Electrical Characteristics Control Pins

#### **Table 5 Electrical Characteristics: Control Pins**

$V_{\rm DD}$  = 3 V to 5.5 V,  $V_{\rm S}$  = 7 V to 18 V,  $T_{\rm J}$  = -40 °C to +150 °C (unless otherwise specified) Typical values:  $V_{\rm DD}$  = 5 V,  $V_{\rm S}$  = 13.5 V,  $T_{\rm J}$  = 25 °C

| Parameter       | Symbol               |      | Value | S    | Unit | Note or<br>Test Condition | Number   |

|-----------------|----------------------|------|-------|------|------|---------------------------|----------|

|                 |                      | Min. | Тур.  | Max. |      |                           |          |

| IDLE pin        | ,                    |      |       |      |      |                           | <u> </u> |

| L-input level   | $V_{IDLE(L)}$        | 0    |       | 0.8  | V    | _                         | P_5.3.1  |

| H-input level   | $V_{IDLE(H)}$        | 2.0  |       | 5.5  | V    | _                         | P_5.3.2  |

| L-input current | I <sub>IDLE(L)</sub> | 5    | 12    | 20   | μΑ   | V <sub>IDLE</sub> = 0.8 V | P_5.3.3  |

| H-input current | I <sub>IDLE(H)</sub> | 14   | 28    | 45   | μΑ   | V <sub>IDLE</sub> = 2.0 V | P_5.3.4  |

| Input Pins      | ·                    |      |       | ·    |      |                           | ·        |

| L-input level   | $V_{IN(L)}$          | 0    |       | 0.8  | V    | _                         | P_5.3.5  |

| H-input level   | $V_{\text{IN(H)}}$   | 2.0  |       | 5.5  | V    | _                         | P_5.3.6  |

| L-input current | I <sub>IN(L)</sub>   | 5    | 12    | 20   | μΑ   | V <sub>IN</sub> = 0.8 V   | P_5.3.7  |

| H-input current | I <sub>IN(H)</sub>   | 14   | 28    | 45   | μΑ   | V <sub>IN</sub> = 2.0 V   | P_5.3.8  |

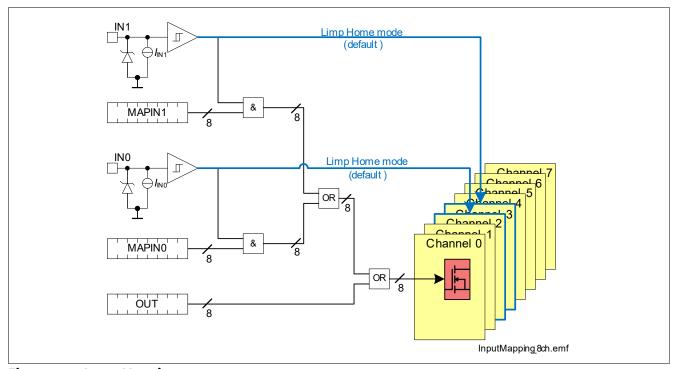

#### **Power Supply**

### 6 Power Supply

The TLE75008-ESD is supplied by two supply voltages:

- V<sub>s</sub> (analog supply voltage used also for the logic)

- *V*<sub>DD</sub> (digital supply voltage)

The  $V_S$  supply line is connected to a battery feed and used, in combination with  $V_{DD}$  supply, for the driving circuitry of the power stages. In situations where  $V_S$  voltage drops below  $V_{DD}$  voltage (for instance during cranking events down to 3.0 V), an increased current consumption may be observed at VDD pin.

$V_{\rm S}$  and  $V_{\rm DD}$  supply voltages have an undervoltage detection circuit, which prevents the activation of the associated function in case the measured voltage is below the undervoltage threshold. More in detail:

- An undervoltage on both  $V_S$  and  $V_{DD}$  supply voltages prevents the activation of the power stages and any SPI communication (the SPI registers are reset)

- An undervoltage on V<sub>DD</sub> supply prevents any SPI communication. SPI read/write registers are reset to default values.

- An undervoltage on  $V_S$  supply forces the TLE75008-ESD to drain all needed current for the low-side switches and for the logic from  $V_{DD}$  supply.

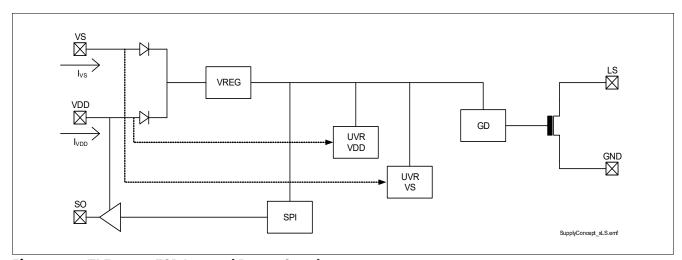

**Figure 11** shows a basic concept drawing of the interaction between supply pins VS and VDD, the output stage drivers and SO supply line.

Figure 11 TLE75008-ESD Internal Power Supply concept

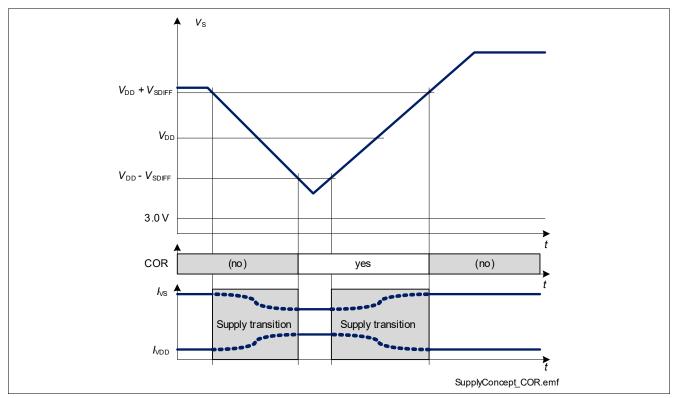

When  $3.0 \text{ V} \le V_{\text{SDIFF}}$  TLE75008-ESD operates in "Cranking Operative Range" (COR). In this condition the current consumption from VDD pin increases while it decreases from VS pin where the total current consumption remains within the specified limits. **Figure 12** shows the voltage levels at VS pin where the device goes in and out of COR. During the transition to and from COR operative region,  $I_{\text{VS}}$  and  $I_{\text{VDD}}$  change between values defined for normal operation and for COR operation. The sum of both current remains within limits specified in "Overall current consumption" section (see **Table 8**).

#### **Power Supply**

Figure 12 "Cranking Operative Range"

Furthermore, when  $V_{S(UV)} \le V_S \le V_{S(OP)}$  it may be not possible to switch ON a channel that was previously OFF. All channels that are already ON keep their state unless they are switched OFF via SPI or via INn pins. An overview of channel behavior according to different  $V_S$  and  $V_{DD}$  supply voltages is shown in **Table 6** (the table is valid after a successful power-up, see **Chapter 6.1.1** for more details).

#### **Power Supply**

Device capability as function of  $V_{\rm S}$  and  $V_{\rm DD}$ Table 6

|                                                                                          | apability as fulletion of v <sub>§</sub> al                                            | TG 7 DD                                                                                                 |                                                                                                         |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

|                                                                                          | $V_{DD} \le V_{DD(UV)}$<br>$(V_{DD(UV)} = P_6.3.25)$                                   | $\begin{vmatrix} V_{DD} = V_{DD(LOP)} \\ (V_{DD(LOP)} = P_{6.3.24} \end{vmatrix}$                       | $V_{\rm DD} > V_{\rm DD(LOP)}$                                                                          |

| $V_{S} \le 3.0 \text{ V}$ $3.0 \text{ V} = V_{S(UV),\text{max}}$                         | channels cannot be controlled                                                          | channels can be switched ON and OFF (SPI control) (R <sub>DS(ON)</sub> deviations possible)             | channels can be switched ON and OFF (SPI control) (R <sub>DS(ON)</sub> deviations possible)             |

| (P_6.3.1)                                                                                | SPI registers reset                                                                    | SPI registers available                                                                                 | SPI registers available                                                                                 |

|                                                                                          | SPI communication not available ( $f_{SCLK} = 0 \text{ MHz}$ )                         | SPI communication possible ( $f_{SCLK} = 1 \text{ MHz}$ ) (P_10.4.34)                                   | SPI communication possible ( $f_{SCLK} = 5 \text{ MHz}$ ) (P_10.4.22)                                   |

|                                                                                          | Limp Home mode not<br>available                                                        | Limp Home mode available (R <sub>DS(ON)</sub> deviations possible)                                      | Limp Home mode available $(R_{DS(ON)}$ deviations possible)                                             |

| $3.0 \text{ V} < V_{\text{S}} \le V_{\text{S(OP)}}$<br>$(V_{\text{S(OP)}} = P_{-}6.3.2)$ | channels cannot be controlled by SPI                                                   | channels can be switched ON and OFF (SPI control) <sup>1)</sup> ( $R_{\rm DS(ON)}$ deviations possible) | channels can be switched ON and OFF (SPI control) <sup>1)</sup> ( $R_{\rm DS(ON)}$ deviations possible) |

|                                                                                          | SPI registers reset                                                                    | SPI registers available                                                                                 | SPI registers available                                                                                 |

|                                                                                          | SPI communication not available ( $f_{SCLK} = 0 \text{ MHz}$ )                         | SPI communication possible ( $f_{SCLK} = 1 \text{ MHz}$ ) (P_10.4.34)                                   | SPI communication possible ( $f_{SCLK} = 5 \text{ MHz}$ ) (P_10.4.22)                                   |

|                                                                                          | Limp Home mode<br>available <sup>1)</sup> (R <sub>DS(ON)</sub><br>deviations possible) | Limp Home mode<br>available <sup>1)</sup> (R <sub>DS(ON)</sub><br>deviations possible)                  | Limp Home mode available $(R_{\rm DS(ON)}$ deviations possible)                                         |

| $V_{\rm S} > V_{\rm S(OP)}$                                                              | channels cannot be controlled by SPI                                                   | channels can be switched ON and OFF                                                                     | channels can be switched ON and OFF                                                                     |

|                                                                                          |                                                                                        | (small $R_{DS(ON)}$ dev. possible when $V_S = V_{S(EXT,LOW)}$ )                                         | (small $R_{DS(ON)}$ dev. possible when $V_S = V_{S(EXT,LOW)}$ )                                         |

|                                                                                          | SPI registers reset                                                                    | SPI registers available                                                                                 | SPI registers available                                                                                 |

|                                                                                          | SPI communication not available ( $f_{SCLK} = 0 \text{ MHz}$ )                         | SPI communication possible ( $f_{SCLK} = 5 \text{ MHz}$ ) (P_10.4.22)                                   | SPI communication possible ( $f_{SCLK} = 5 \text{ MHz}$ ) (P_10.4.22)                                   |

|                                                                                          | Limp Home mode available $(R_{DS(ON)}$ dev. possible when $V_S = V_{S(EXT,LOW)}$ )     | Limp Home mode available $(R_{\rm DS(ON)}$ dev. possible when $V_{\rm S} = V_{\rm S(EXT,LOW)})$         | Limp Home mode available $(R_{DS(ON)}$ dev. possible when $V_S = V_{S(EXT,LOW)}$ )                      |

<sup>1)</sup> undervoltage condition on  $V_S$  must be considered - see **Chapter 6.2.1** for more details

#### **Power Supply**

#### 6.1 Operation Modes

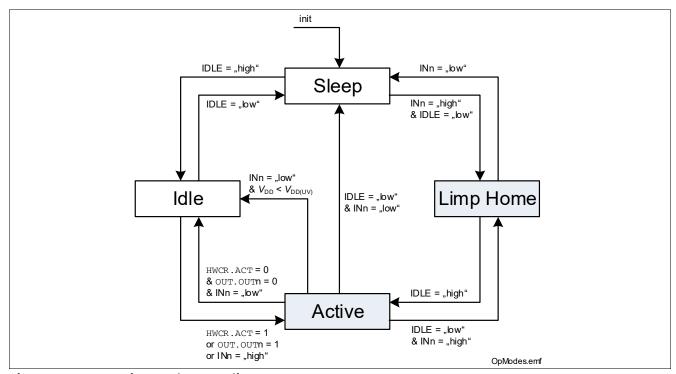

TLE75008-ESD has the following operation modes:

- Sleep mode

- · Idle mode

- Active mode

- Limp Home mode

The transition between operation modes is determined according to following levels and states:

- · logic level at IDLE pin

- · logic level at INn pins

- OUT.OUTn bits state

- HWCR.ACT bit state

The state diagram including the possible transitions is shown in **Figure 13**. The behaviour of TLE75008-ESD as well as some parameters may change in dependence from the operation mode of the device. Furthermore, due to the undervoltage detection circuitry which monitors  $V_S$  and  $V_{DD}$  supply voltages, some changes within the same operation mode can be seen accordingly.

The operation mode of the TLE75008-ESD can be observed by:

- status of output channels

- status of SPI registers

- current consumption at VDD pin (I<sub>VDD</sub>)

- current consumption at VS pin (I<sub>VS</sub>)

The default operation mode to switch ON the loads is Active mode. If the device is not in Active mode and a request to switch ON one or more outputs comes (via SPI or via Input pins), it will switch into Active or Limp Home mode, according to IDLE pin status. Due to the time needed for such transitions, output turn-on time  $t_{\text{ON}}$  will be extended due to the mode transition latency.

Figure 13 Operation Mode state diagram

#### **Power Supply**

**Table 7** shows the correlation between device operation modes,  $V_S$  and  $V_{DD}$  supply voltages, and state of the most important functions (channels operativity, SPI communication and SPI registers).

Table 7 Device function in relation to operation modes,  $V_s$  and  $V_{DD}$  voltages

| Operation<br>Mode | Function      | Undervoltage condition on $V_S^{1}$ $V_{DD} \le V_{DD(UV)}$ | Undervoltage condition on $V_S$ $V_{DD} > V_{DD(UV)}$ | V <sub>S</sub> not in<br>undervoltage<br>V <sub>DD</sub> ≤ V <sub>DD(UV)</sub> | V <sub>S</sub> not in<br>undervoltage<br>V <sub>DD</sub> > V <sub>DD(UV)</sub> |

|-------------------|---------------|-------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Sleep             | Channels      | not available                                               | not available                                         | not available                                                                  | not available                                                                  |

|                   | SPI comm.     | not available                                               | not available                                         | not available                                                                  | not available                                                                  |

|                   | SPI registers | reset                                                       | reset                                                 | reset                                                                          | reset                                                                          |

| Idle              | Channels      | not available                                               | not available                                         | not available                                                                  | not available                                                                  |

|                   | SPI comm.     | not available                                               | ✓                                                     | not available                                                                  | ✓                                                                              |

|                   | SPI registers | reset                                                       | ✓                                                     | reset                                                                          | ✓                                                                              |

| Active            | Channels      | not available                                               | ✓                                                     | √ (IN pins only)                                                               | ✓                                                                              |

|                   | SPI comm.     | not available                                               | ✓                                                     | not available                                                                  | ✓                                                                              |

|                   | SPI registers | reset                                                       | ✓                                                     | reset                                                                          | ✓                                                                              |

| Limp Home         | Channels      | not available                                               | ✓ (IN pins only)                                      | √ (IN pins only)                                                               | √ (IN pins only)                                                               |

|                   | SPI comm.     | not available                                               | √ (read-only)                                         | not available                                                                  | √ (read-only)                                                                  |

|                   | SPI registers | reset                                                       | √ (read-only) <sup>2)</sup>                           | reset                                                                          | √ (read-only) <sup>2)</sup>                                                    |

<sup>1)</sup> see **Chapter 6.2.1** for more details

#### **6.1.1** Power-up

The Power-up condition is satisfied when one of the supply voltages ( $V_S$  or  $V_{DD}$ ) is applied to the device and the INn or IDLE pins are set to "high". If  $V_S$  is above the threshold  $V_{S(OP)}$  or if  $V_{DD}$  is above the threshold  $V_{DD(LOP)}$  the internal power-on signal is set.

#### 6.1.2 Sleep mode

When TLE75008-ESD is in Sleep mode, all outputs are OFF and the SPI registers are reset, independently from the supply voltages. The current consumption is minimum. See parameters  $I_{\text{VDD(SLEEP)}}$  and  $I_{\text{VS(SLEEP)}}$ , or parameter  $I_{\text{SLEEP}}$  for the whole device.

#### 6.1.3 Idle mode

In Idle mode, the current consumption of the device can reach the limits given by parameters  $I_{\text{VDD}(\text{IDLE})}$  and  $I_{\text{VS}(\text{IDLE})}$ , or by parameter  $I_{\text{IDLE}}$  for the whole device. The internal voltage regulator is working. Diagnosis functions are not available. The output channels are switched OFF, independently from the supply voltages. When  $V_{\text{DD}}$  is available, the SPI registers are working and SPI communication is possible. In Idle mode the **ERRn** bits are not cleared for functional safety reasons.

<sup>2)</sup> see Chapter 6.1.5 for a detailed overview

#### **Power Supply**

#### 6.1.4 Active mode

Active mode is the normal operation mode of TLE75008-ESD when no Limp Home condition is set and it is necessary to drive some or all loads. Voltage levels of  $V_{\rm DD}$  and  $V_{\rm S}$  influence the behavior as described at the beginning of **Chapter 6**. Device current consumption is specified with  $I_{\rm VDD(ACTIVE)}$  and  $I_{\rm VS(ACTIVE)}$  ( $I_{\rm ACTIVE}$  for the whole device). The device enters Active mode when IDLE pin is set to "high" and one of the input pins is set to "high" or one **OUT.OUTn** bit is set to "1". If **HWCR.ACT** is set to "0", the device returns to Idle mode as soon as all inputs pins are set to "low" and **OUT.OUTn** bits are set to "0". If **HWCR.ACT** is set to "1", the device remains in Active mode independently of the status of input pins and **OUT.OUTn** bits. An undervoltage condition on  $V_{\rm DD}$  supply brings the device into Idle mode, if all input pins are set to "low". Even if the registers **MAPIN0** and **MAPIN1** are both set to "00<sub>H</sub>" but one of the input pins INn is set to "high", the device goes into Active mode.

#### 6.1.5 Limp Home mode

TLE75008-ESD enters Limp Home mode when IDLE pin is "low" and one of the input pins is set to "high", switching ON the channel connected to it. SPI communication is possible but only in read-only mode (SPI registers can be read but cannot be written). More in detail:

- UVRVS and LOPVDD are set to "1"

- MODE bits are set to "01<sub>R</sub>" (Limp Home mode)

- TER bit is set to "1" on the first SPI command after entering Limp Home mode. Afterwards it works normally

- OLOFF bits is set to "0"

- **ERRn** bits work normally

- DIAG\_OSM.OUTn bits can be read and work normally

- All other registers are set to their default value and cannot be programmed as long as the device is in Limp Home mode

See **Table 6** for a detailed overview of supply voltage conditions required to switch ON channels 2 and 3 during Limp Home. All other channels are OFF.

A transmission of SPI commands during transition from Active to Limp Home mode or Limp Home to Active mode may result in undefined SPI responses.

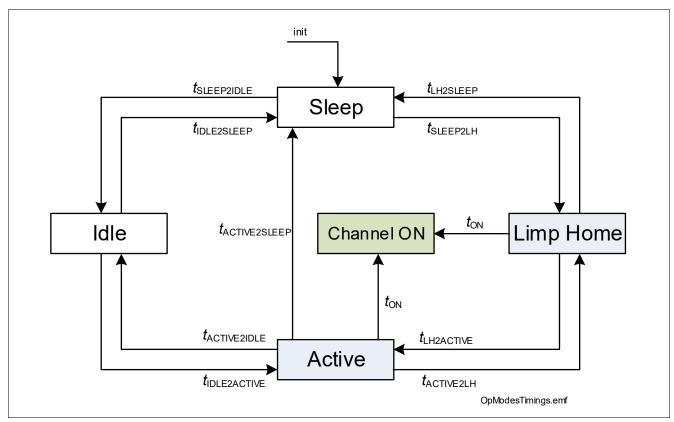

#### 6.1.6 Definition of Power Supply modes transition times

The channel turn-ON time is as defined by parameter  $t_{\rm ON}$  when TLE75008-ESD is in Active mode or in Limp Home mode. In all other cases, it is necessary to add the transition time required to reach one of the two aforementioned Power Supply modes (as shown in **Figure 14**).

# infineon

#### **Power Supply**

Figure 14 Transition Time diagram

#### 6.2 Reset condition

One of the following 3 conditions resets the SPI registers to the default value:

- $V_{\rm DD}$  is not present or below the undervoltage threshold  $V_{\rm DD(UV)}$

- IDLE pin is set to "low"

- a reset command (HWCR.RST set to "1") is executed

- **ERRn** bits are not cleared by a reset command (for functional safety)

- UVRVS and LOPVDD bits are cleared by a reset command

In particular, all channels are switched OFF (if there are no input pin set to "high") and the Input Mapping configuration is reset.

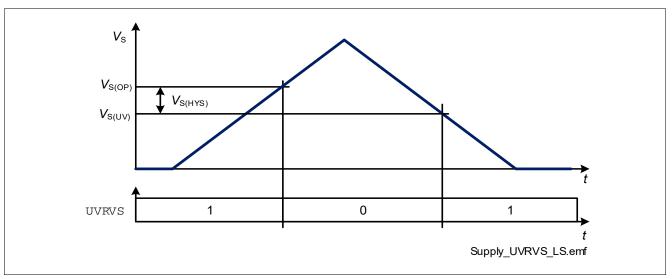

#### 6.2.1 Undervoltage on $V_s$

Between  $V_{S(UV)}$  and  $V_{S(OP)}$  the undervoltage mechanism is triggered. If the device is operative and the supply voltage drops below the undervoltage threshold  $V_{S(UV)}$ , the logic set the bit **UVRVS** to "1". As soon as the supply voltage VS is above the minimum voltage operative threshold  $V_{S(OP)}$ , the bit **UVRVS** is set to "0" after the first Standard Diagnosis readout. Undervoltage condition on VS influences the status of the channels, as described in **Table 6**. **Figure 15** sketches the undervoltage behavior.

#### **Power Supply**

Figure 15 V<sub>s</sub> Undervoltage Behavior

#### Low Operating Power on $V_{\rm DD}$ 6.2.2

When  $V_{\rm DD}$  supply voltage is in the range indicated by  $V_{\rm DD(LOP)}$ , the bit **LOPVDD** is set to "1". As soon as  $V_{\rm DD} > V_{\rm DD(LOP)}$  the bit **LOPVDD** is set to "0" after the first Standard Diagnosis readout.

If  $V_{\rm DD}$  supply voltage is not present, a voltage applied to pins CSN or SO can supply the internal logic (not recommended in normal operation due to internal design limitations).

#### **Power Supply**

#### **Electrical Characteristics Power Supply** 6.3

#### Table 8 **Electrical Characteristics Power Supply**

$V_{\rm DD}$  = 3 V to 5.5 V,  $V_{\rm S}$  = 7 V to 18 V,  $T_{\rm J}$  = -40 °C to +150 °C, all voltages with respect to ground, positive currents flowing as described in **Figure 3** (unless otherwise specified)

Typical values:  $V_{\rm DD}$  = 5 V,  $V_{\rm S}$  = 13.5 V,  $T_{\rm J}$  = 25 °C

| Parameter                                                  | Symbol                 |      | Value | s    | Unit | Note or<br>Test Condition                                                                                                                                                                             | Number   |

|------------------------------------------------------------|------------------------|------|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                            |                        | Min. | Тур.  | Max. |      |                                                                                                                                                                                                       |          |

| VS pin                                                     |                        | '    |       |      | -    |                                                                                                                                                                                                       | *        |

| Analog supply undervoltage shutdown                        | V <sub>S(UV)</sub>     | 1.5  | -     | 3.0  | V    | OUTn = ON<br>from $V_{DS} \le 1 \text{ V}$<br>to <b>UVRVS</b> = $1_{B}$<br>$R_{L} = 50 \Omega$                                                                                                        | P_6.3.1  |

| Analog supply minimum operative voltage                    | $V_{S(OP)}$            | _    | _     | 4.0  | V    | OUT.OUTn = $1_B$<br>from UVRVS = $1_B$<br>to $V_{DS} \le 1 \text{ V}$<br>$R_L = 50 \Omega$                                                                                                            | P_6.3.2  |

| Undervoltage shutdown hysteresis                           | $V_{\rm S(HYS)}$       | _    | 1     | -    | V    | 1)                                                                                                                                                                                                    | P_6.3.3  |

| Analog supply current consumption in Sleep mode with loads | I <sub>VS(SLEEP)</sub> | -    | 0.1   | 3    | μΑ   | $V_{\text{IDLE}}$ floating $V_{\text{INn}}$ floating $V_{\text{CSN}} = V_{\text{DD}}$ $T_{\text{J}} \leq 85 ^{\circ}\text{C}$                                                                         | P_6.3.4  |

| Analog supply current consumption in Sleep mode with loads | I <sub>VS(SLEEP)</sub> | -    | 0.1   | _    | μА   | $V_{\rm IDLE}$ floating $V_{\rm INn}$ floating $V_{\rm CSN} = V_{\rm DD}$ $T_{\rm J} \le 85 ^{\circ}{\rm C}$ VS = 13.5 V                                                                              | P_6.3.63 |

| Analog supply current consumption in Sleep mode with loads | I <sub>VS(SLEEP)</sub> | -    | 0.1   | 20   | μΑ   | $V_{\text{IDLE}}$ floating<br>$V_{\text{INn}}$ floating<br>$V_{\text{CSN}} = V_{\text{DD}}$<br>$T_{\text{J}} = 150 ^{\circ}\text{C}$                                                                  | P_6.3.5  |

| Analog supply current consumption in Idle mode with loads  | I <sub>VS(IDLE)</sub>  | -    | -     | 2.2  | mA   | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $HWCR.ACT = 0_{\text{B}}$ $OUT.OUTn = 0_{\text{B}}$ $DIAG_IOL.OUTn = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$ | P_6.3.6  |

#### **Power Supply**

#### **Electrical Characteristics Power Supply (cont'd)** Table 8

$V_{\rm DD}$  = 3 V to 5.5 V,  $V_{\rm S}$  = 7 V to 18 V,  $T_{\rm J}$  = -40 °C to +150 °C, all voltages with respect to ground, positive currents flowing as described in Figure 3 (unless otherwise specified)

| Parameter                                                                        | Symbol                  |      | Value | Values |    | Note or                                                                                                                                                                                                                                                                    | Number   |

|----------------------------------------------------------------------------------|-------------------------|------|-------|--------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                  |                         | Min. | Тур.  | Max.   |    | <b>Test Condition</b>                                                                                                                                                                                                                                                      |          |

| Analog supply current consumption in Idle mode with loads (COR)                  | I <sub>VS(IDLE)</sub>   | -    | -     | 0.3    | mA | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $\text{HWCR.ACT} = 0_{\text{B}}$ $\text{OUT.OUTn} = 0_{\text{B}}$ $\text{DIAG_IOL.OUTn} = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$ $V_{\text{S}} \leq V_{\text{DD}} - 1 \text{ V}$ | P_6.3.7  |

| Analog supply current consumption in Active mode with loads - channels OFF       | I <sub>VS(ACTIVE)</sub> | -    | -     | 4.2    | mA | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $\text{HWCR.ACT} = 1_{\text{B}}$ $\text{OUT.OUTn} = 0_{\text{B}}$ $\text{DIAG_IOL.OUTn} = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$                                                 | P_6.3.8  |

| Analog supply current consumption in Active mode with loads - channels OFF (COR) | I <sub>VS(ACTIVE)</sub> | -    | 0.1   | 0.3    | mA | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $\text{HWCR.ACT} = 1_{\text{B}}$ $\text{OUT.OUTn} = 0_{\text{B}}$ $\text{DIAG_IOL.OUTn} = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$ $V_{\text{S}} \leq V_{\text{DD}} - 1 \text{ V}$ | P_6.3.12 |

| Analog supply current consumption in Active mode with loads - channels ON        | I <sub>VS(ACTIVE)</sub> | -    | -     | 4.2    | mA | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $HWCR.ACT = 1_{\text{B}}$ $OUT.OUTn = 1_{\text{B}}$ $DIAG_IOL.OUTn = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$                                                                      | P_6.3.15 |

#### **Power Supply**

#### **Table 8** Electrical Characteristics Power Supply (cont'd)

$V_{\rm DD}$  = 3 V to 5.5 V,  $V_{\rm S}$  = 7 V to 18 V,  $T_{\rm J}$  = -40 °C to +150 °C, all voltages with respect to ground, positive currents flowing as described in **Figure 3** (unless otherwise specified)

| Parameter                                                                                | Symbol                  |      | Values |      | Unit | Note or                                                                                                                                                                                                                                              | Number   |

|------------------------------------------------------------------------------------------|-------------------------|------|--------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                          |                         | Min. | Тур.   | Max. |      | <b>Test Condition</b>                                                                                                                                                                                                                                |          |

| Analog supply current<br>consumption in Active mode<br>with loads - channels ON<br>(COR) | I <sub>VS(ACTIVE)</sub> | -    | 0.1    | 0.3  | mA   | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $HWCR.ACT = 1_{\text{B}}$ $OUT.OUTn = 1_{\text{B}}$ $DIAG_IOL.OUTn = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$ $V_{\text{S}} \le V_{\text{DD}} - 1 \text{ V}$ | P_6.3.20 |

| VDD pin                                                                                  |                         |      |        |      |      |                                                                                                                                                                                                                                                      |          |

| Logic Supply Operating<br>voltage                                                        | $V_{\rm DD(OP)}$        | 3.0  | -      | 5.5  | V    | $f_{\text{SCLK}} = 5 \text{ MHz}$                                                                                                                                                                                                                    | P_6.3.23 |

| Logic Supply Lower<br>Operating Voltage                                                  | $V_{\rm DD(LOP)}$       | 3.0  | -      | 4.5  | V    | -                                                                                                                                                                                                                                                    | P_6.3.24 |

| Undervoltage shutdown                                                                    | $V_{\rm DD(UV)}$        | 1    | _      | 3.0  | V    | $V_{SI} = 0 \text{ V}$<br>$V_{SCLK} = 0 \text{ V}$<br>$V_{CSN} = 0 \text{ V}$<br>SO from "low" to high impedance                                                                                                                                     | P_6.3.25 |

| Logic supply current in<br>Sleep mode                                                    | I <sub>VDD(SLEEP)</sub> | _    | 0.1    | 2.5  | μΑ   | $V_{\text{IDLE}}$ floating $V_{\text{INn}}$ floating $V_{\text{CSN}} = V_{\text{DD}}$ $T_{\text{J}} \le 85 ^{\circ}\text{C}$                                                                                                                         | P_6.3.26 |

| Logic supply current in<br>Sleep mode                                                    | I <sub>VDD(SLEEP)</sub> | -    | -      | 10   | μА   | $V_{\text{IDLE}}$ floating $V_{\text{INn}}$ floating $V_{\text{CSN}} = V_{\text{DD}}$ $T_{\text{J}} = 150 ^{\circ}\text{C}$                                                                                                                          | P_6.3.27 |

| Logic supply current in Idle<br>mode                                                     | I <sub>VDD(IDLE)</sub>  | -    | _      | 0.3  | mA   | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $HWCR.ACT = 0_{\text{B}}$ $OUT.OUTn = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$                                                                               | P_6.3.28 |

| Logic supply current in Idle<br>mode (COR)                                               | I <sub>VDD(IDLE)</sub>  | -    | -      | 2.2  | mA   | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $HWCR.ACT = 0_{\text{B}}$ $OUT.OUTn = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$ $V_{\text{S}} \leq V_{\text{DD}} - 1 \text{ V}$                               | P_6.3.29 |

#### **Power Supply**

## Table 8 Electrical Characteristics Power Supply (cont'd)

$V_{\rm DD}$  = 3 V to 5.5 V,  $V_{\rm S}$  = 7 V to 18 V,  $T_{\rm J}$  = -40 °C to +150 °C, all voltages with respect to ground, positive currents flowing as described in **Figure 3** (unless otherwise specified)

| Parameter                                                                  | Symbol                   | Values |      |      | Unit | Note or                                                                                                                                                                                                                | Number   |

|----------------------------------------------------------------------------|--------------------------|--------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                            |                          | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                                                                                                                                                  |          |

| Logic supply current in<br>Active mode - channels OFF                      | I <sub>VDD(ACTIVE)</sub> | -      | _    | 0.3  | mA   | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $HWCR.ACT = 1_{\text{B}}$ $OUT.OUTn = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$                                                 | P_6.3.30 |

| Logic supply current in<br>Active mode - channels OFF<br>(COR)             | I <sub>VDD(ACTIVE)</sub> | -      | -    | 4.2  | mA   | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $HWCR.ACT = 1_{\text{B}}$ $OUT.OUTn = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$ $V_{\text{S}} \leq V_{\text{DD}} - 1 \text{ V}$ | P_6.3.31 |

| Logic supply current in<br>Active mode - channels ON                       | I <sub>VDD(ACTIVE)</sub> | -      | _    | 0.3  | mA   | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $HWCR.ACT = 1_{\text{B}}$ $OUT.OUTn = 1$ $V_{\text{CSN}} = V_{\text{DD}}$                                                            | P_6.3.35 |

| Logic supply current in<br>Active mode - channels ON<br>(COR)              | I <sub>VDD(ACTIVE)</sub> | -      | -    | 4.2  | mA   | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $HWCR.ACT = 1_{\text{B}}$ $OUT.OUTn = 1_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$ $V_{\text{S}} \leq V_{\text{DD}} - 1 \text{ V}$ | P_6.3.36 |

| Overall current consumption                                                | on                       |        |      |      |      |                                                                                                                                                                                                                        |          |

| Overall current consumption in Sleep mode $I_{VS(SLEEP)} + I_{VDD(SLEEP)}$ | I <sub>SLEEP</sub>       | -      | _    | 5    | μΑ   | $V_{\text{IDLE}}$ floating $V_{\text{INn}}$ floating $V_{\text{CSN}} = V_{\text{DD}}$ $T_{\text{J}} \leq 85 ^{\circ}\text{C}$                                                                                          | P_6.3.40 |

| Overall current consumption in Sleep mode $I_{VS(SLEEP)} + I_{VDD(SLEEP)}$ | I <sub>SLEEP</sub>       | -      | -    | 5    | μΑ   | $V_{\text{IDLE}}$ floating $V_{\text{INn}}$ floating $V_{\text{CSN}} = V_{\text{DD}}$ $T_{\text{J}} \le 85 ^{\circ}\text{C}$ $V_{\text{S}} = 13.5 ^{\circ}\text{V}$                                                    | P_6.3.64 |

#### **Power Supply**

#### **Electrical Characteristics Power Supply (cont'd)** Table 8

$V_{\rm DD}$  = 3 V to 5.5 V,  $V_{\rm S}$  = 7 V to 18 V,  $T_{\rm J}$  = -40 °C to +150 °C, all voltages with respect to ground, positive currents flowing as described in Figure 3 (unless otherwise specified)

| Parameter                                                                                    | Symbol                  | Values |      |      | Unit | Note or                                                                                                                                                                                               | Number   |

|----------------------------------------------------------------------------------------------|-------------------------|--------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                              |                         | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                                                                                                                                 |          |

| Overall current consumption in Sleep mode $I_{VS(SLEEP)} + I_{VDD(SLEEP)}$                   | I <sub>SLEEP</sub>      | -      | -    | 30   | μА   | $V_{IDLE}$ floating<br>$V_{INn}$ floating<br>$V_{CSN} = V_{DD}$<br>$T_{J} = 150 ^{\circ}\text{C}$                                                                                                     | P_6.3.41 |

| Overall current consumption in Idle mode $I_{VS(IDLE)} + I_{VDD(IDLE)}$                      | I <sub>IDLE</sub>       | -      | -    | 2.5  | mA   | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $HWCR.ACT = 0_{\text{B}}$ $OUT.OUTn = 0_{\text{B}}$ $DIAG_IOL.OUTn = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$ | P_6.3.42 |

| Overall current consumption in Active mode - channels OFF $I_{VS(ACTIVE)} + I_{VDD(ACTIVE)}$ | I <sub>ACTIVE</sub>     | -      | -    | 4.5  | mA   | IDLE = "high" $V_{\text{INn}} \text{ floating}$ $f_{\text{SCLK}} = 0 \text{ MHz}$ $HWCR.ACT = 1_{\text{B}}$ $OUT.OUTn = 0_{\text{B}}$ $DIAG_IOL.OUTn = 0_{\text{B}}$ $V_{\text{CSN}} = V_{\text{DD}}$ | P_6.3.43 |

| Overall current consumption in Active mode - channels ON $I_{VS(ACTIVE)} + I_{VDD(ACTIVE)}$  | I <sub>ACTIVE</sub>     | -      | -    | 4.5  | mA   | IDLE = "high" $V_{\rm INn} \ {\rm floating}$ $f_{\rm SCLK} = 0 \ {\rm MHz}$ ${\rm HWCR.ACT} = 1_{\rm B}$ ${\rm OUT.OUTn} = 1_{\rm B}$ ${\rm DIAG\_IOL.OUTn} = 0_{\rm B}$ $V_{\rm CSN} = V_{\rm DD}$   | P_6.3.47 |

| Voltage difference between $V_{\rm S}$ and $V_{\rm DD}$ supply lines                         | V <sub>SDIFF</sub>      | -      | 200  | -    | mV   | 1)                                                                                                                                                                                                    | P_6.3.52 |

| Timings                                                                                      |                         |        |      |      |      |                                                                                                                                                                                                       |          |

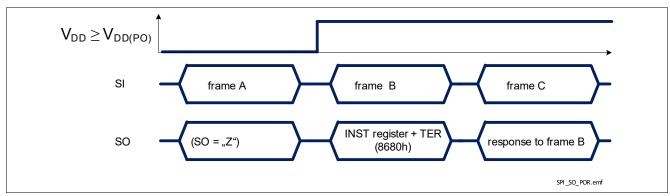

| Sleep to Idle delay                                                                          | t <sub>sleep2IDLE</sub> | -      | 200  | 400  | μs   | from IDLE pin to TER + INST register = 8680 <sub>H</sub> (see Chapter 10.6.1 for details)                                                                                                             | P_6.3.53 |

#### **Power Supply**

#### **Electrical Characteristics Power Supply (cont'd)** Table 8

$V_{\rm DD}$  = 3 V to 5.5 V,  $V_{\rm S}$  = 7 V to 18 V,  $T_{\rm J}$  = -40 °C to +150 °C, all voltages with respect to ground, positive currents flowing as described in Figure 3 (unless otherwise specified)

| Parameter                 | Symbol                   | Values |                          |                          | Unit | Note or                                                                                                                             | Number   |

|---------------------------|--------------------------|--------|--------------------------|--------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------|----------|

|                           |                          | Min.   | Тур.                     | Max.                     |      | <b>Test Condition</b>                                                                                                               |          |

| Idle to Sleep delay       | t <sub>IDLE2SLEEP</sub>  | -      | 100                      | 200                      | μs   | from IDLE pin to Standard Diagnosis = 0000 <sub>H</sub> (see <b>Chapter 10.5</b> for details) external pull-down SO to GND required | P_6.3.54 |

| Idle to Active delay      | t <sub>IDLE2ACTIVE</sub> | -      | 100                      | 200                      | μs   | from INn or CSN pins to MODE = 10 <sub>B</sub>                                                                                      | P_6.3.55 |

| Active to Idle delay      | t <sub>ACTIVE2IDLE</sub> | -      | 100                      | 200                      | μs   | from INn or CSN pins to MODE = 11 <sub>B</sub>                                                                                      | P_6.3.56 |

| Sleep to Limp Home delay  | t <sub>SLEEP2LH</sub>    | -      | 300<br>+t <sub>ON</sub>  | 600<br>+t <sub>ON</sub>  | μs   | from INn pins<br>to $V_{DS} = 10\% V_{S}$                                                                                           | P_6.3.57 |

| Limp Home to Sleep delay  | t <sub>lh2Sleep</sub>    | -      | 200<br>+t <sub>OFF</sub> | 400<br>+t <sub>OFF</sub> | μs   | from INn pins to Standard Diagnosis = 0000 <sub>H</sub> (see Chapter 10.6.1 for details). External pull-down SO to GND required     | P_6.3.58 |

| Limp Home to Active delay | t <sub>LH2ACTIVE</sub>   | -      | 50                       | 100                      | μs   | from IDLE pin to  MODE = $10_B$                                                                                                     | P_6.3.59 |

#### **Power Supply**

#### **Electrical Characteristics Power Supply (cont'd)** Table 8

$V_{\rm DD}$  = 3 V to 5.5 V,  $V_{\rm S}$  = 7 V to 18 V,  $T_{\rm J}$  = -40 °C to +150 °C, all voltages with respect to ground, positive currents flowing as described in Figure 3 (unless otherwise specified)

| Parameter                 | Symbol                    | Values |      |      | Unit | Note or                                                                                                                                                                                                            | Number   |

|---------------------------|---------------------------|--------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                           |                           | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                                                                                                                                              |          |