# TLE9012AQU

# Li-Ion Battery Monitoring and Balancing IC

# Features

- General

- Monitors up to 12 cells connected in series

- Supports communication of up to 20 devices

- Supports hot plugging

- Voltage measurement

- 16 bit high resolution ADC measurement for each cell

- High accuracy measurement for SoC (State-of-Charge) and SoH (State-of-Health) calculation

- Temperature compensated measurements

- Built-in noise filtering

- Selectable measurement bit length

- Temperature measurement

- 5 temperature measurement channels for connection to external NTC

- Internal temperature measurement

- Balancing

- Integrated balancing switch allowing up to 150 mA balancing current

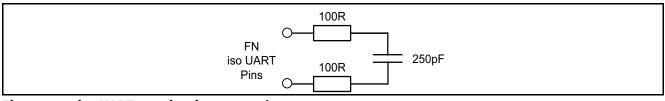

- Communication Bus (iso UART)

- Differential robust serial interface for communication between battery blocks

- High speed communication with 2 Mbps

- Power balanced communication scheme

- Additional 4 GPIO pins to e.g. connect an external EEPROM

- Green product (RoHS-compliant)

- ISO-26262 ready, supporting ASIL-C BMS safety applications<sup>1)</sup>

#### Safety features

- Two independent internal voltage references

- Block voltage measurement based on different ADCs

- Configurable analog OV/UV comparators

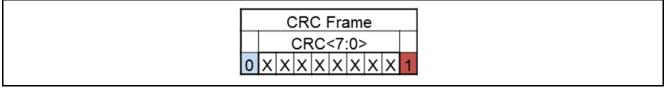

- End-to-end CRC secured communication

- CRC secured configuration registers

- Internal open load detection

<sup>1)</sup> according to ISO 26262-8 clause 13 first edition

1

• Emergency mode signaling using iso UART lines

# **Potential applications**

• Multi-cell battery monitoring and balancing system IC designed for Li-Ion battery packs used in hybrid electric vehicles (HEV), plug-in hybrid electric vehicles (PHEV), battery electric vehicles (BEV) as well as in 12 V Lithium-Ion batteries

# **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

# Description

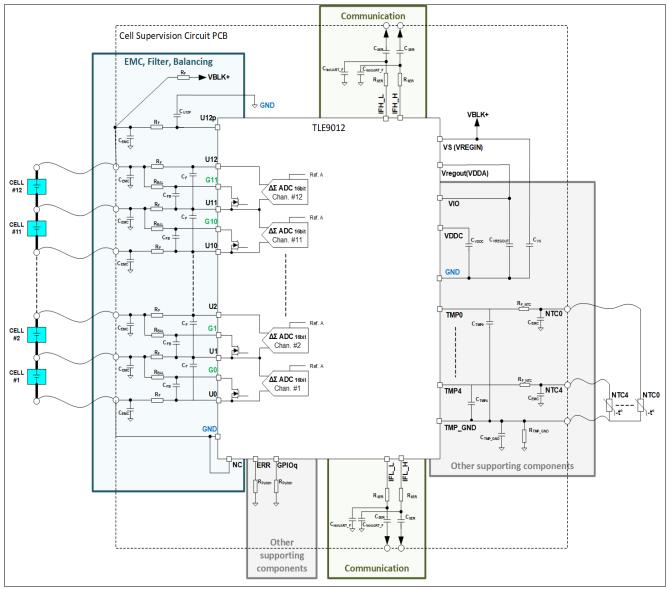

The TLE9012AQU provides the main function of monitoring the temperature of the battery and voltage of each cell as well as the communication to the host controller.

| Туре       | Package    | Marking    |

|------------|------------|------------|

| TLE9012AQU | PG-TQFP-48 | TLE9012AQU |

# **Table of Contents**

| 1                 | Block diagram                                                                                                          | 5 |

|-------------------|------------------------------------------------------------------------------------------------------------------------|---|

| 2                 | Pin configuration                                                                                                      | 6 |

| 2.1               | Pin assignment                                                                                                         |   |

| 2.2               | Pin definitions and functions                                                                                          |   |

| <b>3</b><br>3.1   | General product characteristics                                                                                        |   |

| 3.1<br>3.2        | Functional range                                                                                                       |   |

| 3.3               | Thermal resistance                                                                                                     |   |

| 4                 | Power supply                                                                                                           | 3 |

| 4.1               | Functional description                                                                                                 | 3 |

| 4.2               | Power supply description                                                                                               |   |

| 4.3<br>4.4        | Using an external voltage regulator for the UART/GPIO unit                                                             |   |

| 4.4<br>4.5        | Wake-up and sleep mode       1         Power supply monitoring       1                                                 |   |

| 4.6               | Electrical characteristics power supply                                                                                |   |

| 5                 | Cell management unit                                                                                                   |   |

| 5.1               | Overview                                                                                                               |   |

| 5.2               | Accurate cell voltage measurement 1                                                                                    |   |

| 5.3               | Configurable analog overvoltage/undervoltage (OV/UV) comparators                                                       |   |

| 5.4<br>5.5        | Cell diagnosis                                                                                                         |   |

|                   | Cell diagnosis                                                                                                         |   |

| <b>6</b><br>6.1   | Cell block voltage and auxiliary measurements       3         Cell block voltage measurement (BVM) description       3 |   |

| 6.2               | Auxiliary voltage measurement (AVM) description         3.                                                             |   |

| 6.3               | Electrical characteristics                                                                                             |   |

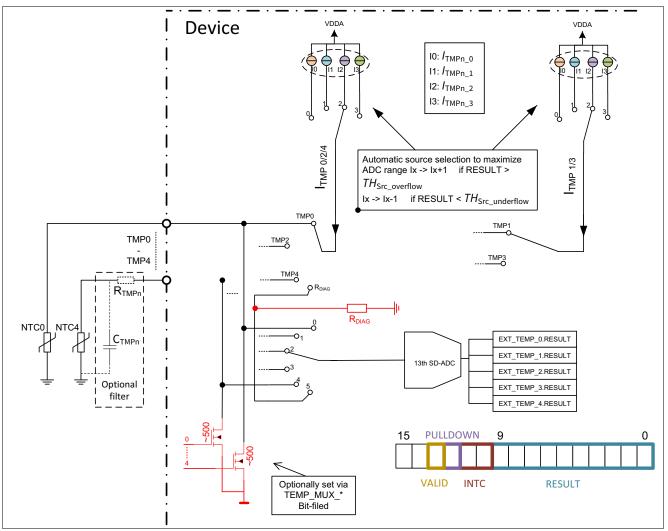

| 7                 | Temperature measurement   3                                                                                            | 5 |

| 7.1               | Electrical characteristics                                                                                             | 6 |

| 8                 | Housekeeping functions                                                                                                 | 8 |

| 8.1               | Functional description 3                                                                                               |   |

| 8.2               | Watchdog and wake-up function    3                                                                                     |   |

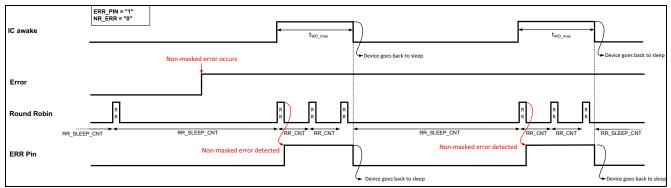

| 8.3<br>8.4        | Round robin       4         Emergency mode (EMM) and ERR pin function       4                                          |   |

| 9.4               |                                                                                                                        |   |

|                   | General Purpose Input / Output (GPIO)                                                                                  |   |

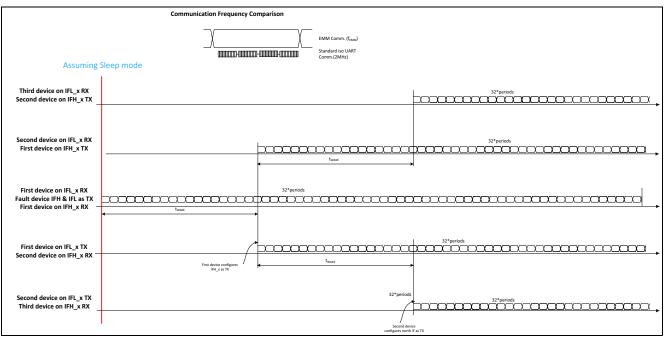

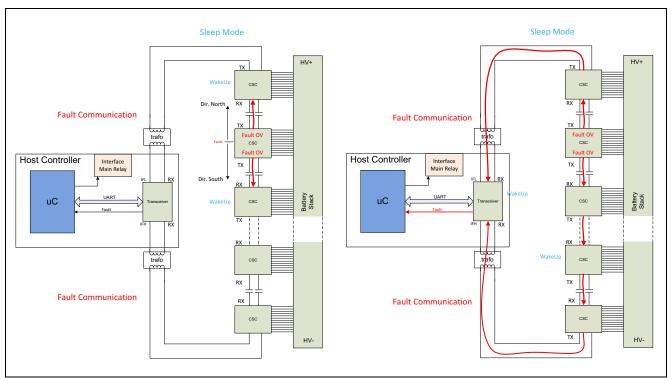

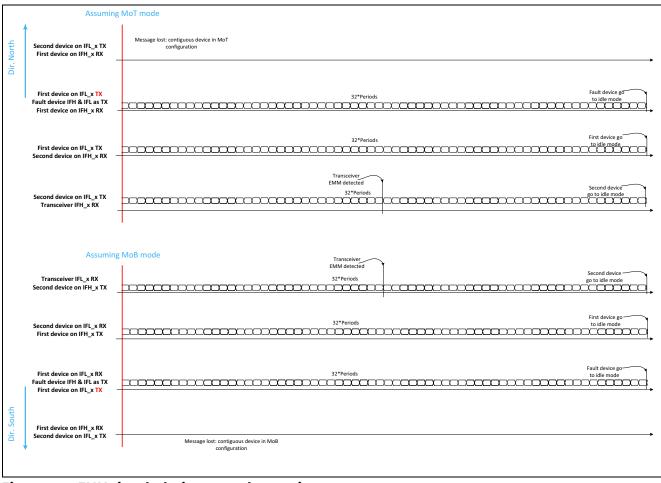

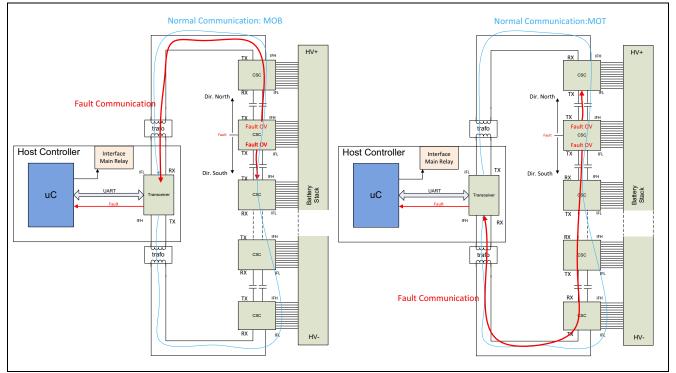

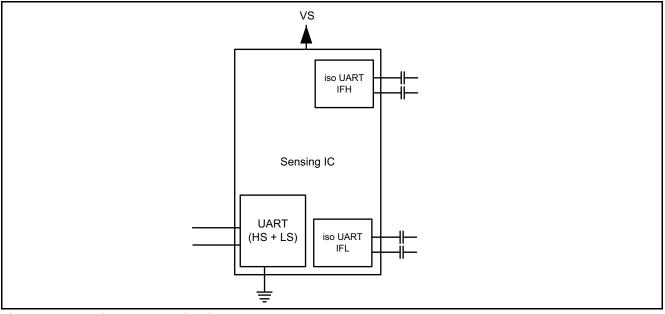

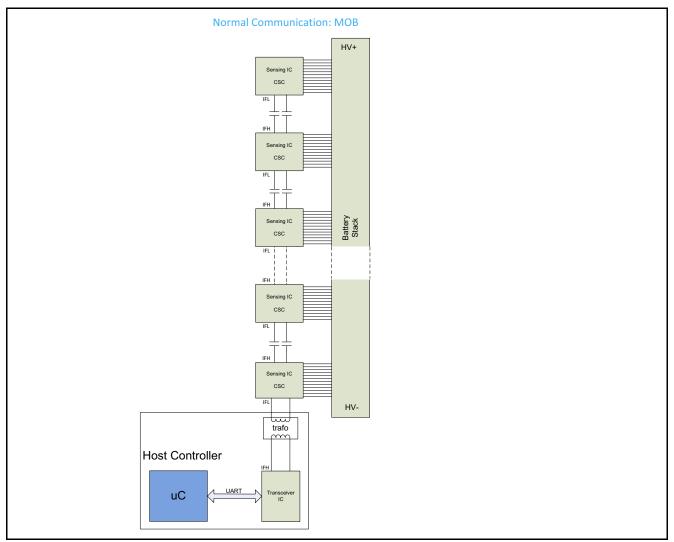

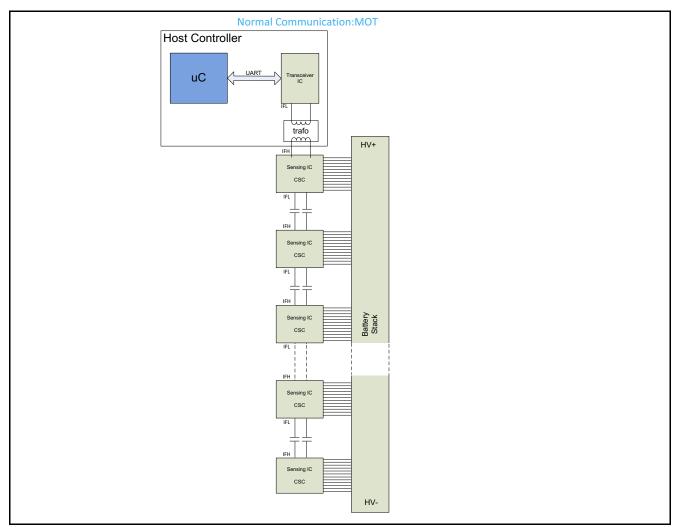

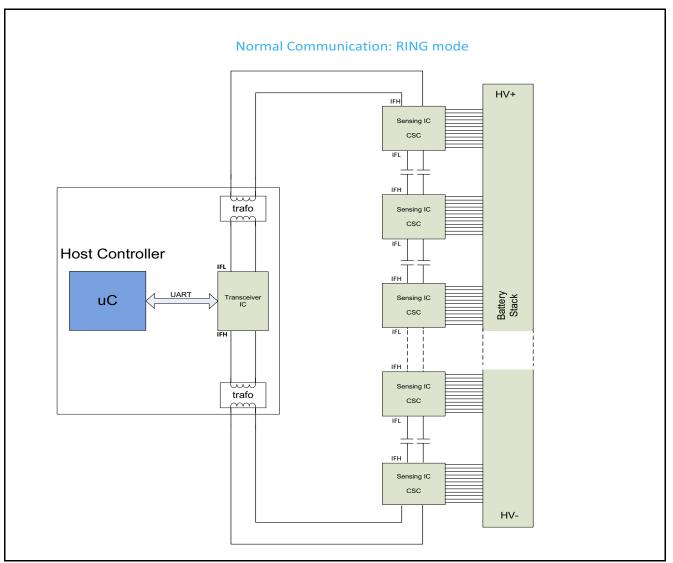

| <b>10</b><br>10.1 | Communication interfaces       5         Physical layer       5                                                        |   |

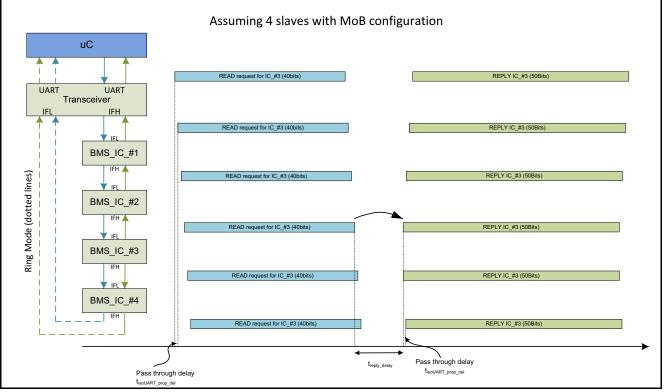

| 10.1              | Bus topology                                                                                                           |   |

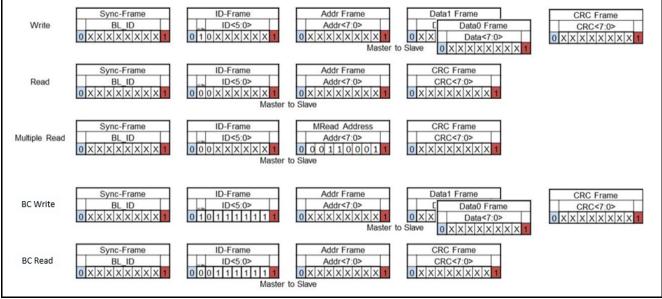

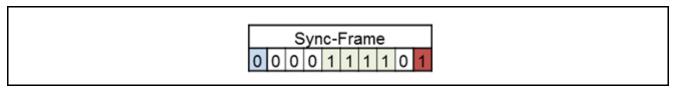

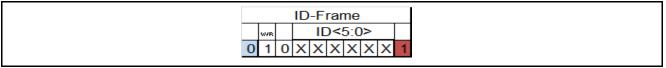

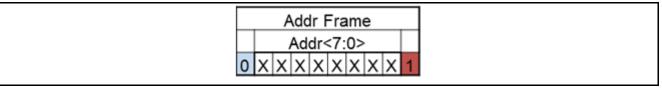

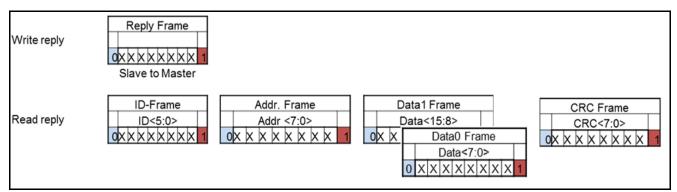

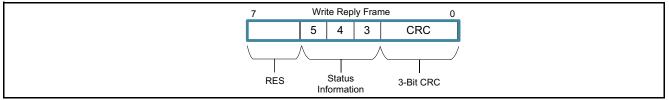

| 10.3              | Frame description                                                                                                      |   |

| 10.4              | Chain timing                                                                                                           | 7 |

| 11                | Built-in diagnosis features                                                                                            | 9 |

| 12                | Registers                                                                                                              | 1 |

| 12.1              | Registers overview                                                                                                     | 1 |

| 13                | Application information                                                                                                | 4 |

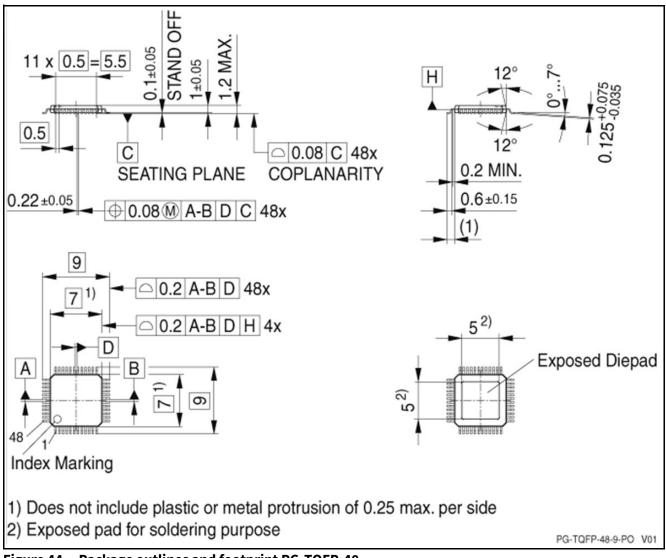

| 14 | Package outlines | 115 |

|----|------------------|-----|

| 15 | Revision history | 116 |

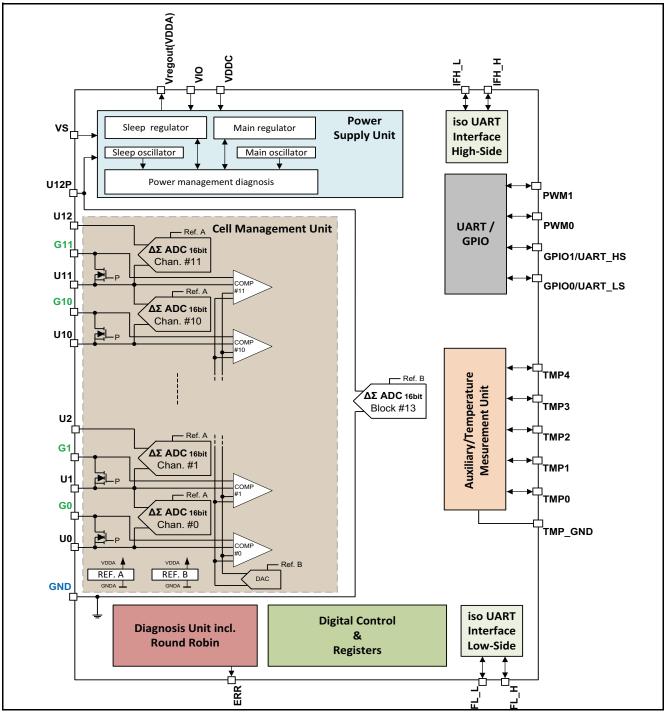

**Block diagram**

# 1 Block diagram

Figure 1 TLE9012AQU block diagram

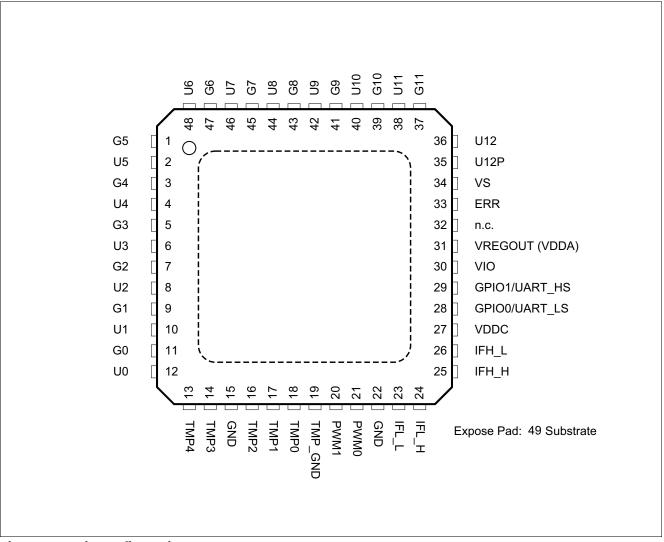

Pin configuration

# 2 Pin configuration

# 2.1 Pin assignment

Figure 2 Pin configuration

# TLE9012AQU

**Pin configuration**

# 2.2 Pin definitions and functions

# Table 1Pin assignment

| Pin | Symbol            | Function                                                                                                                                         |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | G5                | Cell balance control channel 5, input of SCVS                                                                                                    |

| 2   | U5                | Cell voltage measurement channel 5 negative terminal (positive terminal of cell 4)                                                               |

| 3   | G4                | Cell balance control channel 4, input of SCVC                                                                                                    |

| 4   | U4                | Cell voltage measurement channel 4 negative terminal (positive terminal of cell 3)                                                               |

| 5   | G3                | Cell balance control channel 3, input of SCVC                                                                                                    |

| 6   | U3                | Cell voltage measurement channel 3 negative terminal (positive terminal of cell 2)                                                               |

| 7   | G2                | Cell balance control channel 2, input of SCVC                                                                                                    |

| 8   | U2                | Cell voltage measurement channel 2 negative terminal (positive terminal of cell 1)                                                               |

| 9   | G1                | Cell balance control channel 1, input of SCVC                                                                                                    |

| 10  | U1                | Cell voltage measurement channel 1 negative terminal (positive terminal of cell 0)                                                               |

| 11  | G0                | Cell balance control channel 0, input of SCVC                                                                                                    |

| 12  | U0                | Cell voltage measurement channel 0 negative terminal (same potential as local GND)                                                               |

| 13  | TMP4              | Temperature sensor 4; If not used, please connect pin to GND. If TMP4 is disabled, the pin can be used as 0 2 V auxiliary ADC miscellaneous pin. |

| 14  | TMP3              | Temperature sensor 3; If not used, please connect pin to GND. If TMP3 is disabled, the pin can be used as 0 2 V auxiliary ADC miscellaneous pin. |

| 15  | GND               | Local GND of CSC (Cell Supervision Circuit) device                                                                                               |

| 16  | TMP2              | Temperature sensor 2; If not used, please connect pin to GND. If TMP2 is disabled, the pin can be used as 0 2 V auxiliary ADC miscellaneous pin. |

| 17  | TMP1              | Temperature sensor 1; If not used, please connect pin to GND. If TMP1 is disabled, the pin can be used as 0 2 V auxiliary ADC miscellaneous pin. |

| 18  | TMP0              | Temperature sensor 0; If not used, please connect pin to GND. If TMP0 is disabled, the pin can be used as 0 2 V auxiliary ADC miscellaneous pin. |

| 19  | TMP_GND           | Temperature sensor reference. This pin can be connected to local GND.                                                                            |

| 20  | PWM1              | PWM output channel 1; This pin has also a general purpose input/output function; If not used, please connect pin to GND.                         |

| 21  | PWM0              | PWM output channel 0; This pin has also a general purpose input/output function; If not used, please connect pin to GND.                         |

| 22  | GND               | Local GND of CSC device (Cell Supervision Circuit)                                                                                               |

| 23  | IFL_L             | Lower Communication Bus (iso UART) L pin                                                                                                         |

| 24  | IFL_H             | Lower Communication Bus (iso UART) H pin                                                                                                         |

| 25  | IFH_H             | Upper Communication Bus (iso UART) H pin                                                                                                         |

| 26  | IFH_L             | Upper Communication Bus (iso UART) L pin                                                                                                         |

| 27  | VDDC              | Buffer capacitor pin for internal Communication Bus (iso UART) supply                                                                            |

| 28  | GPIO0/<br>UART_LS | General purpose input/output channel 0. This pin has also the function of UART_LS; If not used, please connect pin to GND.                       |

# **Pin configuration**

| Table 1 | Pin assi          | gnment                                                                                                                     |

|---------|-------------------|----------------------------------------------------------------------------------------------------------------------------|

| Pin     | Symbol            | Function                                                                                                                   |

| 29      | GPIO1/<br>UART_HS | General purpose input/output channel 1. This pin has also the function of UART_HS; if not used, please connect pin to GND. |

| 30      | VIO               | Supply for GPIO interface.                                                                                                 |

| 31      | Vregout           | Output pin of the internal regulator.                                                                                      |

| 32      | n.c.              | Not connected; this pin shall be connected to GND.                                                                         |

| 33      | ERR               | Erroroutput to microcontroller; open drain PMOS connected to VS. If not used, please leave pin open.                       |

| 34      | VS                | Supply pin of internal regulator Vregout.                                                                                  |

| 35      | U12P              | Positive supply pin; connect to positive terminal of topmost cell in block; supply of the sleep regulator.                 |

| 36      | U12               | Cell voltage measurement channel 11 positive terminal (most upper cell in the block)                                       |

| 37      | G11               | Cell balance control channel 11, input of SCVC                                                                             |

| 38      | U11               | Cell voltage measurement channel 11 negative terminal (positive terminal of cell 10)                                       |

| 39      | G10               | Cell balance control channel 10, input of SCVC                                                                             |

| 40      | U10               | Cell voltage measurement channel 10 negative terminal (positive terminal of cell 9)                                        |

| 41      | G9                | Cell balance control channel 9, input of SCVC                                                                              |

| 42      | U9                | Cell voltage measurement channel 9 negative terminal (positive terminal of cell 8)                                         |

| 43      | G8                | Cell balance control channel 8, input of SCVC                                                                              |

| 44      | U8                | Cell voltage measurement channel 8 negative terminal (positive terminal of cell 7)                                         |

| 45      | G7                | Cell balance control channel 7, input of SCVC                                                                              |

| 46      | U7                | Cell voltage measurement channel 7 negative terminal (positive terminal of cell 6)                                         |

| 47      | G6                | Cell balance control channel 6, input of SCVC                                                                              |

| 48      | U6                | Cell voltage measurement channel 6 negative terminal (positive terminal of cell 5)                                         |

| 49      | EPAD              | Cooling tab; should be connected to GND externally.                                                                        |

infineon

**General product characteristics**

# 3 General product characteristics

# 3.1 Absolute maximum ratings

# Table 2 Absolute maximum ratings<sup>1)</sup>

$T_j$  = -40°C to +150°C; all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                         | Symbol                                   | Symbol Values             |      |                          |   | Note or                                                                                             | Number |

|---------------------------------------------------|------------------------------------------|---------------------------|------|--------------------------|---|-----------------------------------------------------------------------------------------------------|--------|

|                                                   |                                          | Min.                      | Тур. | Max.                     |   | Test Condition                                                                                      |        |

| Voltages                                          |                                          | <u>+</u>                  | •    | 1                        | - |                                                                                                     |        |

| Supply voltage VS                                 | V <sub>vs</sub>                          | -0.3                      | -    | 75                       | V | -                                                                                                   |        |

| Supply voltage U12P                               | V <sub>U12P</sub>                        | -0.3                      | _    | 75                       | V | -                                                                                                   |        |

| Supply voltage VIO                                | V <sub>VIO</sub>                         | -0.3                      | _    | 5.5                      | V | -                                                                                                   |        |

| Supply voltage VS rel.                            | V <sub>vs</sub>                          | V <sub>regout</sub> - 0.3 | -    | -                        | - | -                                                                                                   |        |

| Regulator output VREGOUT                          | <i>V</i> <sub>regout</sub>               | -0.3                      | _    | 3.6                      | V | -                                                                                                   |        |

| Regulator output VDDC                             | V <sub>VDDC</sub>                        | -0.3                      | _    | 3.6                      | V | -                                                                                                   |        |

| Communication Bus (iso UART) interface IFH_x      | V <sub>IFH_L</sub><br>V <sub>IFH_H</sub> | -3                        | -    | 5.5                      | V | <sup>2)</sup> BCI test max.<br>300 mA                                                               |        |

| Communication Bus (iso UART)<br>interface IFL_x   | V <sub>IFL_L</sub><br>V <sub>IFL_H</sub> | -3                        | _    | 5.5                      | V | injected via<br>twisted pair<br>cable onto iso<br>UART interface<br>(max. pin<br>current<br>150 mA) |        |

| Cell sense input voltage abs. Un                  | V <sub>Un</sub>                          | -0.3                      | -    | 75                       | V | 0 ≤ n ≤ 12                                                                                          |        |

| Cell balancing pin abs. Gn                        | V <sub>Gn</sub>                          | -0.3                      | -    | 75                       | V | $0 \le n \le 11$                                                                                    |        |

| Cell sense input voltages rel. Un                 | V <sub>Un</sub>                          | V <sub>Un-1</sub> - x     | -    | V <sub>Un-1</sub> + 5.5  | V | $1 \le n \le 12;$<br>x= -0.0016*T <sub>j</sub> +<br>0.54; e.g.:<br>x=0.5@T <sub>j</sub> =25°C       |        |

| Cell balancing pins rel. Gn                       | V <sub>Gn</sub>                          | V <sub>Un</sub> - 0.3     | _    | V <sub>Un+1</sub> + 0.3  | V | 0 ≤ n ≤ 11                                                                                          |        |

| Temperature sensor input<br>voltages abs. TMPn    | V <sub>TMPn</sub>                        | -0.3                      | _    | 2.75                     | V | $0 \le n \le 4$                                                                                     |        |

| Temperature sensor input<br>voltages rel. TMPn    | V <sub>TMPn</sub>                        | -0.3                      | -    | V <sub>regout</sub> +0.3 | V |                                                                                                     |        |

| Temperature sensor input<br>voltages abs. TMP_GND | V <sub>TMP_GND</sub>                     | -0.3                      | -    | 2.75                     | V | -                                                                                                   |        |

| Temperature sensor input voltages rel. TMP_GND    | V <sub>TMP_GND</sub>                     | -0.3                      | -    | V <sub>regout</sub> +0.3 | V | -                                                                                                   |        |

#### **General product characteristics**

#### Absolute maximum ratings<sup>1</sup> (cont'd) Table 2

$T_i = -40^{\circ}$ C to +150°C; all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                     | Symbol                  |      | Value | S                      | Unit | Note or<br>Test Condition                                                                                                        | Number |

|-----------------------------------------------|-------------------------|------|-------|------------------------|------|----------------------------------------------------------------------------------------------------------------------------------|--------|

|                                               |                         | Min. | Тур.  | Max.                   |      |                                                                                                                                  |        |

| General purpose I/O voltages<br>abs. GPIOn    | V <sub>GPIOn</sub>      | -0.3 | -     | 5.5                    | V    | $0 \le n \le 1$                                                                                                                  |        |

| General purpose I/O voltages<br>rel. GPIOn    | V <sub>GPIOn</sub>      | -0.3 | -     | V <sub>VIO</sub> + 0.3 | V    | _                                                                                                                                |        |

| Pulse width modulation I/O voltages abs. PWMn | V <sub>PWMn</sub>       | -0.3 | -     | 5.5                    | V    | 0 ≤ n ≤ 1                                                                                                                        |        |

| Pulse width modulation I/O voltages rel. PWMn | V <sub>PWMn</sub>       | -0.3 | -     | V <sub>VIO</sub> + 0.3 | V    | _                                                                                                                                |        |

| Open drain output pin abs. ERR                | V <sub>ERR</sub>        | -0.3 | -     | 75                     | V    | -                                                                                                                                |        |

| Open drain output pin rel. ERR                | V <sub>ERR</sub>        | -0.3 | -     | V <sub>VS</sub> +0.3   | V    | -                                                                                                                                |        |

| Ground pin GND                                | V <sub>GND</sub>        | 0    | -     | 0                      | V    | Absolute GND                                                                                                                     |        |

| Temperatures                                  |                         |      |       |                        |      | 1                                                                                                                                |        |

| Junction temperature Tj                       | T <sub>j</sub>          | -40  | -     | 150                    | °C   | -                                                                                                                                |        |

| Storage temperature Tstg                      | T <sub>stg</sub>        | -55  | -     | 150                    | °C   | -                                                                                                                                |        |

| ESD robustness                                |                         |      |       |                        |      |                                                                                                                                  |        |

| ESD robustness 2 kV                           | V <sub>ESD</sub>        | -2   | -     | 2                      | kV   | HBM <sup>3)</sup> ; all pins                                                                                                     |        |

| ESD robustness 4 kV                           | V <sub>ESD</sub>        | -4   | -     | 4                      | kV   | HBM <sup>3)</sup> ;<br>Robustness vs.<br>GND for pins:<br>VS, U12P, Un,<br>TMPn,<br>TMP_GND,<br>AUX_MISn,<br>IFH_x, IFL_x,<br>Gn |        |

| ESD robustness CDM 500 V                      | V <sub>ESD</sub>        | -500 | -     | 500                    | V    | CDM <sup>4)</sup> ; all pins                                                                                                     |        |

| ESD robustness CDM 750 V                      | V <sub>ESD_Corner</sub> | -750 | -     | 750                    | V    | CDM <sup>4)</sup> ; corner                                                                                                       |        |

1) Not subject to production test, specified by design.

2) Positive and negative transients with a maximum duration of 100ns allowed between +/- 8 V; This should simulate ESD events; however, during normal and steady state condition voltage on these pins must stay inside the maximum ratings specified.

pins

3) ESD robustness, according to Human Body Model "HBM" ANSI/ESDA/JEDEC JS-001 (1.5 kΩ, 100 pF)

4) ESD robustness, according to Charged Device Model "CDM" JESD22-C101

#### Notes

1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **General product characteristics**

2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### **General product characteristics**

#### 3.2 Functional range

Note: Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical characteristics table.

#### Table 3Functional range

| Parameter           | Symbol            |      | Value | S    | Unit | Note or<br>Test Condition         | Number |

|---------------------|-------------------|------|-------|------|------|-----------------------------------|--------|

|                     |                   | Min. | Тур.  | Max. |      |                                   |        |

| Supply voltage VS   | V <sub>VS</sub>   | 4.75 | -     | 60   | V    | when using the internal regulator |        |

| Supply voltage U12P | V <sub>U12P</sub> | 4.75 | -     | 60   | V    | -                                 |        |

| Supply voltage VIO  | V <sub>VIO</sub>  | 3    | -     | 5.5  | V    | -                                 |        |

## 3.3 Thermal resistance

*Note:* This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to **www.jedec.org**.

#### Table 4Thermal resistance

| Parameter                 | Symbol            | Values |      | Values |     | Values         |  | Unit | Note or | Number |

|---------------------------|-------------------|--------|------|--------|-----|----------------|--|------|---------|--------|

|                           |                   | Min.   | Тур. | Max.   |     | Test Condition |  |      |         |        |

| Junction to case RthJC    | R <sub>thJC</sub> | -      | 6    | -      | K/W | 1)             |  |      |         |        |

| Junction to ambient RthJA | R <sub>thJA</sub> | -      | 30   | -      | K/W | 1)2)           |  |      |         |        |

1) Not subject to production test, specified by design.

2) Specified R<sub>thJA</sub> value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The product (chip + package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 2 inner copper layers (2 × 70 mm Cu, 2 × 35 mm Cu). Where applicable, a thermal via array under the exposed pad contacted the first inner copper layer. Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

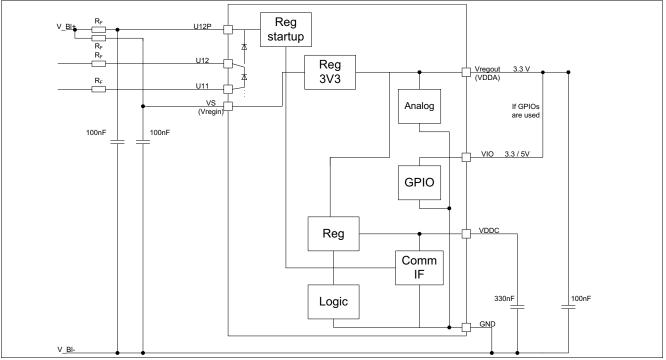

Power supply

# 4 Power supply

# 4.1 Functional description

The TLE9012AQU has an internal power supply to be able to work completely independent by using the power stored in the cells which it monitors.

# 4.2 Power supply description

The following table contains a description of the power supply pins of the TLE9012AQU.

| Pin name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VS             | VS is the main supply pin. This pin is the input for the internal regulator that is intended<br>to supply the device in normal mode. It should be connected to the highest voltage in<br>the module (usually the positive pole of the top cell). Supplying this pin is necessary to<br>function the device.                                                                                                                                                                   |

| U12P           | U12P is the sense pin for the block voltage measurement (BVM); additionally this pin is<br>the input supply pin for the sleep regulator which supplies the wake-up structures. The<br>built-in sleep regulator powers the detection of incoming iso UART and UART wake-up<br>signals in sleep mode which will then trigger the start-up procedure. It should be<br>connected to the highest voltage in the module. Supplying this pin is necessary to<br>function the device. |

| Vregout (VDDA) | This pin is the output of the internal regulator. Usually this voltage can be used to drive the GPIOs for communication with other devices on board. Please connect this pin to a buffer capacitor.                                                                                                                                                                                                                                                                           |

| VIO            | This pin is the supply for the GPIOs. It can be connected either to Vregout or to the output of an external voltage regulator. The voltage available on this pin, will define the GPIO logic output levels as well as the thresholds of the GPIO logic inputs.                                                                                                                                                                                                                |

| VDDC           | VDDC is the output of the internal regulator used for the iso UART communication interface. This pin is used for buffering of the regulator. Please connect this pin to a buffer capacitor to ensure proper and robust communication.                                                                                                                                                                                                                                         |

| GND            | This is the main reference for the TLE9012AQU on the board.                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Table 5Power supply pins

The cell partitioning can be configured in the **PART\_CONFIG** register with the given constraint of starting from the most upper cell (CELL\_11). Please note: Only cells activated in **PART\_CONFIG** are being measured and checked in the round robin scheme (see also **Chapter 8.3.1**).

## Power supply

Figure 3 Typical power supply configuration using the internal voltage regulator

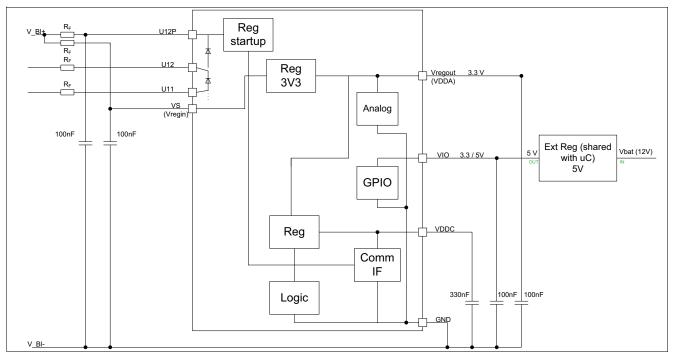

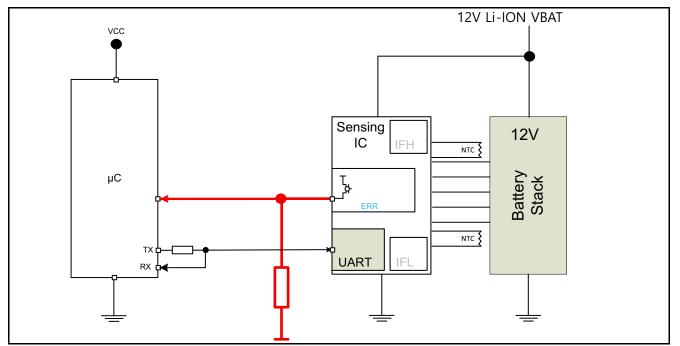

# 4.3 Using an external voltage regulator for the UART/GPIO unit

It is also possible to use an external voltage regulator. This might be desired to have common I/O voltage levels with the host controller in case of systems where no transceiver IC is used and communication is happening directly via UART/GPIO (non-HV application like 12 V/48 V).

Figure 4 System using an external voltage regulator (non-transceiver application)

#### Power supply

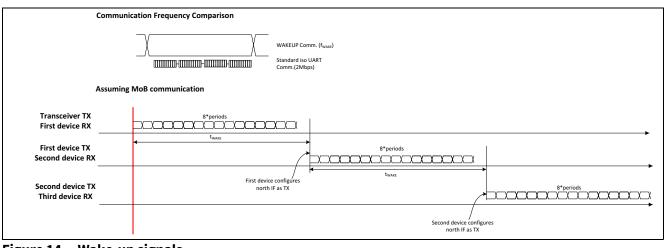

# 4.4 Wake-up and sleep mode

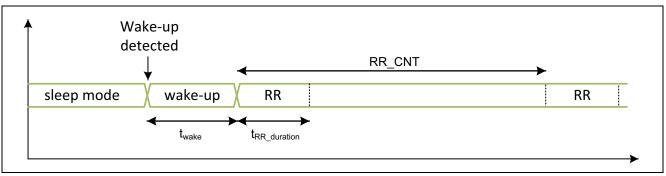

The TLE9012AQU is designed to be continuously connected to a battery. Therefore, the physical connection to the cells which powers the device is expected to happen only once in a lifetime. After receiving power on U12P and VS, the part will go into sleep mode and will be monitoring the communication interfaces for a wake-up sequence.

In order to activate the TLE9012AQU a wake-up sequence as described in **Chapter 8.2.2** has to be sent via either the iso UART port or the UART interface.

A watchdog is implemented that has to be triggered by regular iso UART/UART communication in order to keep the TLE9012AQU in normal mode. The watchdog timer is programmable (register **WDOG\_CNT**). The device will revert to sleep mode automatically as soon as the watchdog has timed out.

Additionally the TLE9012AQU includes the option to send the device directly to sleep mode, this can be performed by setting the PD bit-field in the **OP\_MODE** register.

# 4.5 Power supply monitoring

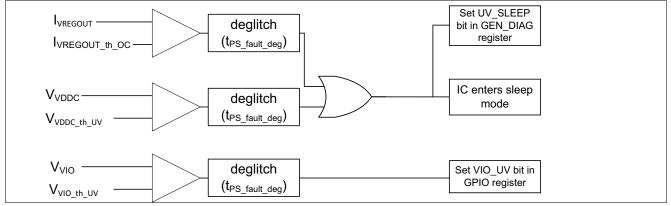

To ensure the correct function of the TLE9012AQU, the device is equipped with an internal monitoring unit for the different internal voltages as well as other supply functions. If important supplies go below levels to ensure correct functionality, the IC will enter sleep mode. The fault bit UV\_SLEEP in the **GEN\_DIAG** register indicates sleep mode due to a supply level outside the limits.

Figure 5 HW monitoring unit

# TLE9012AQU

#### **Power supply**

# 4.6 Electrical characteristics power supply

# Table 6 Electrical characteristics power supply

$V_{VS}$  = 4.75 V to 60 V,  $T_j$  = -40°C to +150°C, all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                            | Symbol                      |      | Values |      | Unit | Note or                                                                                                                                                | Number |

|------------------------------------------------------|-----------------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                      |                             | Min. | Тур.   | Max. |      | <b>Test Condition</b>                                                                                                                                  |        |

| Internal regulators                                  |                             |      |        |      |      |                                                                                                                                                        |        |

| internal regulator output<br>voltage VREGOUT         | V <sub>Vregout</sub>        | 3    | 3.45   | 3.6  | V    | -                                                                                                                                                      |        |

| Overcurrent threshold<br>VREGOUT                     | I <sub>VREGOUT_th_OC</sub>  | 31   | 40     | 60   | mA   | -                                                                                                                                                      |        |

| Undervoltage threshold<br>falling VIO                | $V_{\rm VIO\_th\_UV\_fall}$ | 2.2  | -      | 2.76 | V    | -                                                                                                                                                      |        |

| Undervoltage threshold rising VIO                    | $V_{\rm VIO\_th\_UV\_rise}$ | 2.24 | -      | 2.8  | V    | -                                                                                                                                                      |        |

| VIO undervoltage hysteresis<br>VIO                   | $V_{\rm VIO\_th\_UV\_hys}$  | 40   | 100    | 160  | mV   | -                                                                                                                                                      |        |

| Output voltage VDDC                                  | V <sub>VDDC</sub>           | 2.42 | 2.5    | 2.75 | V    | -                                                                                                                                                      |        |

| Undervoltage threshold VDDC                          | V <sub>VDDC_th_UV</sub>     | 2.15 | -      | 2.42 | V    | -                                                                                                                                                      |        |

| Undervoltage threshold<br>hysteresis VDDC            | V <sub>VDDC_th_UV_hys</sub> | 80   | 100    | 140  | mV   | -                                                                                                                                                      |        |

| Power supply fault deglitch time                     | t <sub>PS_fault_deg</sub>   | 8    | 15     | 24   | μs   | 1)                                                                                                                                                     |        |

| Supply currents                                      | 1                           | 1    |        |      |      | 1                                                                                                                                                      | -1     |

| Sleep mode current U12P                              | I <sub>U12P_sleep</sub>     | 0    | 3      | 4.9  | μΑ   | T <sub>j</sub> = 25°C;                                                                                                                                 |        |

| Sleep mode leakage current<br>VS                     | I <sub>VS_sleep</sub>       | -1   | -      | 1    | μΑ   | $-40^{\circ}\text{C} \le T_{j} \le 85^{\circ}\text{C}$                                                                                                 |        |

| Idle current U12P                                    | I <sub>U12P_idle</sub>      | -    | 2.5    | 10   | μΑ   | IC in idle mode (no                                                                                                                                    |        |

| Idle current VS                                      | / <sub>VS_idle</sub>        | _    | 4.7    | 9.2  | mA   | sleep mode), but no<br>measurement or<br>communication. VIO<br>connected to<br>Vregout                                                                 |        |

| Current consumption during<br>GPIO communication VIO | I <sub>VIO_comm</sub>       | -    | -      | 5    | mA   | depending on load<br>on GPIO                                                                                                                           |        |

| Current consumption during<br>CVM & BVM VS           | I <sub>VS_meas</sub>        | -    | 21     | 25   | mA   | Parallel<br>measurement of all<br>cells + block voltage<br>measurement. VIO<br>connected to<br>Vregout. Incl. idle<br>consumption I <sub>vS_idle</sub> |        |

### Power supply

# Table 6Electrical characteristics power supply (cont'd)

$V_{VS}$  = 4.75 V to 60 V,  $T_j$  = -40°C to +150°C, all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                                                                            | Symbol                   |      | Values |      | Unit | Note or<br>Test Condition                                                                                                                                                          | Number |

|------------------------------------------------------------------------------------------------------|--------------------------|------|--------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                                                      |                          | Min. | Тур.   | Max. |      |                                                                                                                                                                                    |        |

| Current consumption during<br>round robin scheme running<br>VS                                       | I <sub>VS_RR</sub>       | -    | 9      | 26   | mA   | Only during round<br>robin scheme is<br>running. VIO<br>connected to<br>Vregout. Incl. idle<br>consumption I <sub>vS_idle</sub>                                                    |        |

| Current consumption during communication VS                                                          | I <sub>VS_comm</sub>     | -    | 6.5    | 10.8 | mA   | Valid for GPIO or iso<br>UART<br>communication.<br>Current to charge-up<br>external interface<br>components not<br>included. Incl. idle<br>consumption I <sub>vs_idle</sub>        |        |

| Current consumption during<br>communication only for<br>external iso UART interface<br>components VS | I <sub>VS_comm_ext</sub> | -    | -      | 6    | mA   | <sup>1)</sup> $C_{isoUART_ser} = 1 \text{ nF}$<br>$BR_{isoUART} = 2 \text{ MBits}$<br>$R_{isoUART_ser} = 39 \Omega$<br>This consumption<br>needs to be added to<br>$I_{VS_comm}$ . |        |

1) Not subject to production test, specified by design.

# 5 Cell management unit

# 5.1 Overview

The TLE9012AQU provides the tools required for managing up to 12 cells stacked in series. It provides the following functions:

- Accurate voltage measurement

- Configurable OV/UV comparators

- Passive cell balancing

- Cell diagnosis

Additionally, other central functions take care of providing the tools to manage the module as a whole. More information can be found in **Chapter 8**.

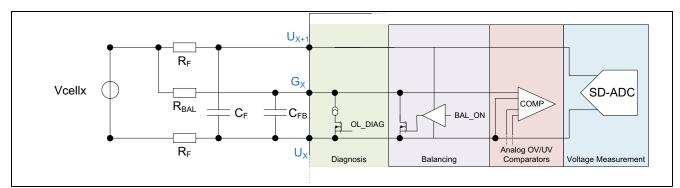

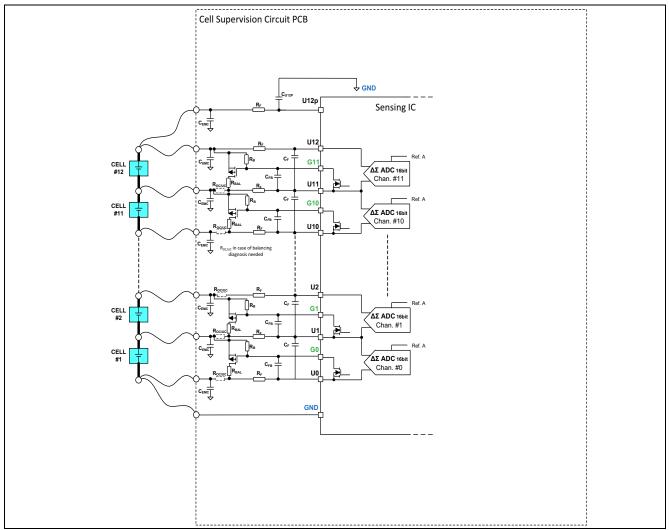

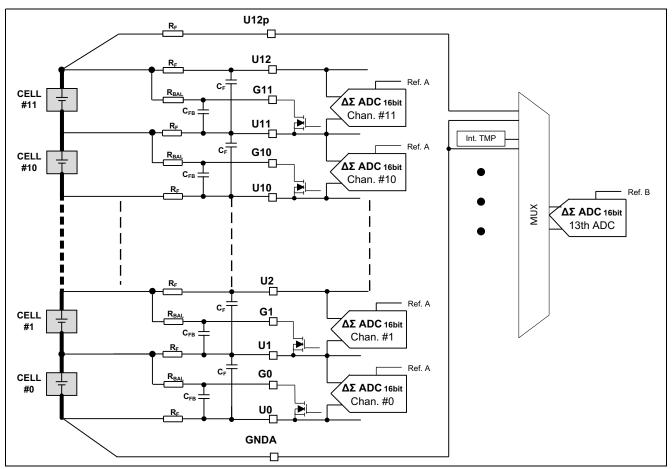

Each cell has the same structure as shown in **Figure 6**. Additionally **Figure 6** shows how the unit is connected to the external structure. The cell voltage measurement unit contains a 16-Bit SD-ADC. It is recommend to use similar filter characteristics for the Ux+1 - Ux and Gx - Ux input filters to support a synchronous OV/UV check with both units (comparator & SD-ADC).

Figure 6 Example of internal structure for 1 cell monitoring hardware

# 5.2 Accurate cell voltage measurement

The exact voltage of each cell is necessary to estimate parameters like state of charge of the battery. The TLE9012AQU provides the necessary ADCs to accurately measure the voltage of each cell.

The voltage measurement path consists of 12 individual 16 bit delta sigma analog to digital converters, one for each cell. The use of separate ADC units enables the conversion of all 12 cell voltages simultaneously. The offset and gain errors of the converters are trimmed individually.

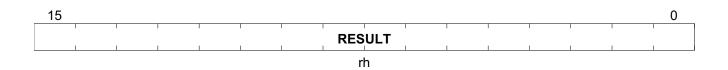

The AD conversion for all cells are initiated by writing the CVM\_START bit-field in the MEAS\_CTRL register. The IC has the option to enable a programmable timer  $t_{\text{CVM}\_del}$ . After receiving a command, which initiates the start of a cell voltage measurement, this timer delays the start of the cell voltage measurement. The IC's cell voltage measurement ADC samples with  $f_s$  and averages the cell voltage measurement result of each cell for the duration of  $t_{\text{CVM}}$ . If CVM is started, during the  $t_{\text{CVM}}$ , the measurement result is reset. At the end of the conversion, the CVM\_START bit-field is automatically cleared and the RESULT is available. This bit-field can be monitored by reading the respective register. The result registers can be accessed by reading the RESULT bit-field in the CVM\_0 – CVM\_11 registers.

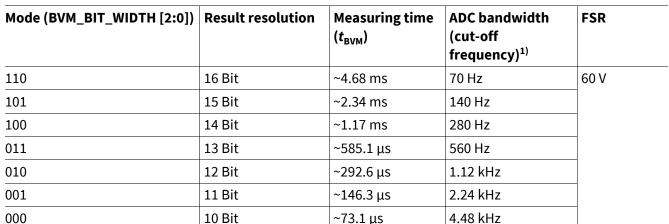

Different measurement modes can be selected (this mode will affect all channels at once):

| Mode (CVM_BIT_WIDTH [2:0]) | Result resolution | Measuring time<br>(t <sub>сvм</sub> ) | ADC bandwidth<br>(cut-off<br>frequency) <sup>1)</sup> | FSR |  |

|----------------------------|-------------------|---------------------------------------|-------------------------------------------------------|-----|--|

| 110                        | 16 Bit            | ~4.68 ms                              | 70 Hz                                                 | 5 V |  |

| 101                        | 15 Bit            | ~2.34 ms                              | 140 Hz                                                |     |  |

| 100                        | 14 Bit            | ~1.17 ms                              | 280 Hz                                                |     |  |

| 011                        | 13 Bit            | ~585.1 µs                             | 560 Hz                                                |     |  |

| 010                        | 12 Bit            | ~292.6 µs                             | 1.12 kHz                                              |     |  |

| 001                        | 11 Bit            | ~146.3 µs                             | 2.24 kHz                                              |     |  |

| 000                        | 10 Bit            | ~73.1 µs                              | 4.48 kHz                                              |     |  |

### Table 7Voltage measurement modes

1) The given cut-off frequencies are only theoretical calculations assuming 1st order averaging filter and should be used only for orientation purposes. They will neither be tested nor guaranteed.

The result is always an unsigned value. In case the result is less than 16 bits, the remaining LSBs will be set to "0". The equation to convert the value read from the RESULT bit-fields in the **CVM\_0** – **CVM\_11** registers to the cell voltage is:

Cell voltage [mV] = (FSR\*1000 [mV] / (2^16)) \* RESULT

The voltage measurement unit averages the signal automatically over the entire measurement time. So the voltage measurement unit of each cell provides a built-in digital filtering for the cell voltage measurement. The reference for the primary cell voltage measurement ADCs is the internal voltage reference A.

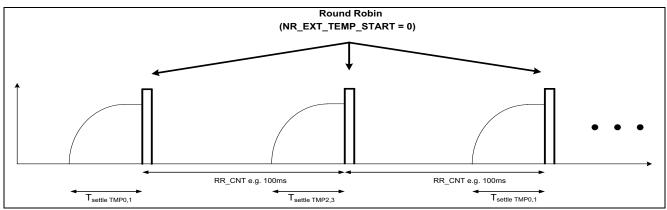

Please note: As soon as a cell voltage measurement start command is received, any ongoing round robin schedule will be cancelled and the measurement will start after  $t_{\text{CVM}\_del}$ . After the measurement is finished, the RR task will be restarted. For more information please refer to **Chapter 8.3**.

(5.1)

# 5.2.1 Electrical characteristics

#### Table 8 Electrical characteristics

$V_{VS}$  = 4.75 V to 60 V,  $T_j$  = -40°C to +150°C, all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                                   | Symbol                   | Values |                                            |       | Unit | Note or                                                                                                                   | Number |

|-------------------------------------------------------------|--------------------------|--------|--------------------------------------------|-------|------|---------------------------------------------------------------------------------------------------------------------------|--------|

|                                                             |                          | Min.   | Тур.                                       | Max.  |      | Test Condition                                                                                                            |        |

| Cell sense inputs                                           |                          | 4      | I                                          | -     |      | 1                                                                                                                         |        |

| CVM differential input<br>current Un                        | / <sub>Un_CVM</sub>      | 18     | 25                                         | 32    | μΑ   | during CVM<br>$V_{CVM}$ =5 V<br>$0 \le n \le 12$<br>typ. value $I_{Un_{CVM}}$ =<br>$V_{CVM}$ / 200 k $\Omega$             |        |

| Input leakage current Un                                    | I <sub>Un_leak</sub>     | -1.0   | 0                                          | 1.0   | μΑ   | 0 ≤ n ≤ 12<br>in sleep mode & in idle<br>mode                                                                             |        |

| Timing                                                      |                          |        |                                            |       |      |                                                                                                                           |        |

| CVM propagation delay<br>within IC                          | t <sub>CVM_prop</sub>    | 0      | -                                          | 10    | μs   | <sup>1)</sup> Propagation delay<br>between complete<br>arrival of CVM start<br>message and the<br>actual start of the CVM |        |

| CVM start delay timer resolution                            | t <sub>CVM_del_LSB</sub> | 35.1   | 36.6                                       | 38.1  | μs   | 1)                                                                                                                        |        |

| CVM start delay timer<br>maximum interval                   | $t_{\rm CVM\_del\_max}$  | 1.09   | 1.13                                       | 1.18  | ms   | 1)                                                                                                                        |        |

| Primary voltage measure                                     | ement                    |        |                                            |       |      |                                                                                                                           |        |

| CVM input range                                             | V <sub>CVM</sub>         | 0      | -                                          | 5     | V    | <sup>1)</sup> Measuring $V_{cell} = V_{Un+1} - V_{Un}; 0 \le n \le 11$                                                    |        |

| CVM resolution                                              | V <sub>CVM_LSB</sub>     | -      | FSR/2 <sup>m</sup>                         | -     | V    | <sup>1)</sup> $10 \le m \le 16$ ; FSR = 5 V                                                                               |        |

| CVM ADC sampling frequency                                  | f <sub>s_CVM_ADC</sub>   | 13.44  | 14                                         | 14.56 | MHz  | 1)                                                                                                                        |        |

| CVM time                                                    | t <sub>cvm</sub>         | -      | 2 <sup>m</sup> /<br>f <sub>s_CVM_ADC</sub> | -     | s    | <sup>1)</sup> $10 \le m \le 16$                                                                                           |        |

| Maximum CVM time<br>deviation between<br>channels within IC | Dev <sub>CVM_IC</sub>    | -0.5   | -                                          | 0.5   | %    | <sup>1)</sup> deviation between<br>CVM time <i>t</i> <sub>CVM</sub> within<br>one IC                                      |        |

| Maximum CVM time<br>deviation across ICs                    | Dev <sub>CVM_chain</sub> | -4     | -                                          | 4     | %    | <sup>1)</sup> deviation between<br>CVM time t <sub>CVM</sub> over all<br>ICs                                              |        |

# Table 8Electrical characteristics (cont'd)

$V_{VS}$  = 4.75 V to 60 V,  $T_j$  = -40°C to +150°C, all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                           | Symbol                           | Values |      |      | Unit | Note or                                                                                                                                                  | Number |

|-----------------------------------------------------|----------------------------------|--------|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                     |                                  | Min.   | Тур. | Max. |      | Test Condition                                                                                                                                           |        |

| CVM relative accuracy -<br>initial <sup>2)4)</sup>  | CVM <sub>ERR_relati</sub><br>ve  | -0.9   | -    | 0.9  | mV   | 16 bit mode<br>V <sub>cell</sub> = 4.3 V<br>T <sub>j</sub> = 25°C<br>±3 sigma distribution<br>within abs. min/max<br>limits                              |        |

| CVM accuracy - initial <sup>2)4)</sup>              | CVM <sub>ERR</sub>               | -2     | -    | 2    | mV   | 14 - 16 bit mode2.7 V $\leq V_{cell} \leq 4.3$ V $T_j = 25^{\circ}$ C±3 sigma distributionwithin abs. min/maxlimitsAccuracy at tester inbackend          |        |

| CVM accuracy EOL <sup>3)4)</sup>                    | CVM <sub>ERR_EOL</sub>           | -5.8   | -    | 5.8  | mV   | 14 -16 bit mode2.7 V $\leq V_{cell} \leq 4.3$ V-40°C $\leq T_j \leq 125°C$ $\pm 3$ sigma distributionwithin abs. min/maxlimits                           |        |

| CVM accuracy EoL - 10 Bit<br>mode <sup>1)3)4)</sup> | CVM <sub>ERR_EOL_</sub><br>10Bit | -25    | -    | 25   | mV   | 10 bit mode<br>$0.05 V \le V_{cell} \le 4.8 V$<br>$-40^{\circ}C \le T_j \le 150^{\circ}C$<br>$\pm 3$ sigma distribution<br>within abs. min/max<br>limits |        |

1) Not subject to production test, specified by design.

- 2) Initial accuracy verified by Infineon backend.

- 3) End-of-Life; according to AEC-Q100 Grade 1 Rev. H automotive qualification.

- 4) Parameters are verified during the following conditions: no NTC measurement; no iso UART communication; no AUX measurement

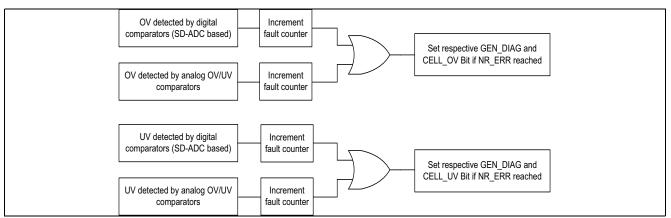

# 5.3 Configurable analog overvoltage/undervoltage (OV/UV) comparators

Additionally to the primary measurement path with the SD-ADC the TLE9012AQU includes also a separate analog OV/UV check (see also **Figure 6**) via comparators and a Digital-Analog-Converter (DAC). The threshold values of the comparators are configurable. Furthermore the comparator logic is averaging its checks over a time period of  $t_{comp}$ . Similar to the digital comparators used in the round robin scheme to check for OV/UV based on the primary measurement, the analog comparators check the voltage at Gx-Ux against the OV/UV thresholds stored in register OL\_OV\_THR and OL\_UV\_THR as secondary redundant OV/UV path.

This analog unit is connected to the Gx pin which also means the external filter structure is different from the primary path. The approach of the different pins avoids having potential faults violating both OV/UV check paths in the same way.

The analog OV/UV check against the thresholds happens synchronously to the digital check in every round robin scheme. Please see also round robin scheme description in **Chapter 8.3.1**.

# 5.3.1 Electrical characteristics

#### Table 9 Electrical characteristics

$V_{VS}$  = 4.75 V to 60 V,  $T_j$  = -40°C to +150°C, all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                   | Symbol                 |         | Values                   |      | Unit | Note or<br>Test Condition                                                                                             | Number |

|---------------------------------------------|------------------------|---------|--------------------------|------|------|-----------------------------------------------------------------------------------------------------------------------|--------|

|                                             |                        | Min.    | Тур.                     | Max. |      |                                                                                                                       |        |

| Cell Gx sense inputs                        |                        |         |                          |      |      |                                                                                                                       |        |

| Comparator differential<br>input current Gn | I <sub>Gn_comp</sub>   | -       | 7                        | 10   | μΑ   | $0 \le n \le 11$<br>during<br>comparator<br>check in round<br>robin <sup>1)</sup>                                     |        |

| Analog overvoltage/unde                     | rvoltage con           | nparate | ors                      |      |      |                                                                                                                       |        |

| Comparator input range                      | V <sub>Comp</sub>      | 0       | -                        | 5    | V    | <sup>1)</sup> Measuring<br>$V_{cell} = V_{Gn} - V_{Un}$<br>$0 \le n \le 11$                                           |        |

| Comparator resolution                       | V <sub>Comp_LSB</sub>  | -       | FSR/2 <sup>10</sup>      | -    | V    | <sup>1)</sup> FSR = 5 V                                                                                               |        |

| Comparator accuracy                         | COMP <sub>ERR</sub>    | -50     | -                        | 50   | mV   | $1 V < V_{cell} < 4.7 V$<br>-40°C $\leq T_j \leq 150$ °C<br>±3 sigma<br>distribution<br>within abs.<br>min/max limits |        |

| Relative comparator<br>accuracy             | COMP <sub>ERR_li</sub> | -30     | _                        | 30   | mV   | $V_{cell} = 3.6 V$<br>-40°C $\leq T_j \leq 25°C$<br>±3 sigma<br>distribution<br>within abs.<br>min/max limits         |        |

| Comparator sampling frequency               | f <sub>comp</sub>      | 1       | -                        | -    | MHz  | 1)                                                                                                                    |        |

| Comparator checking time                    | t <sub>comp</sub>      | -       | $2^{10}/f_{s\_CVM\_ADC}$ | -    | μs   | 1)                                                                                                                    |        |

1) Not subject to production test, specified by design.

# 5.4 Cell balancing

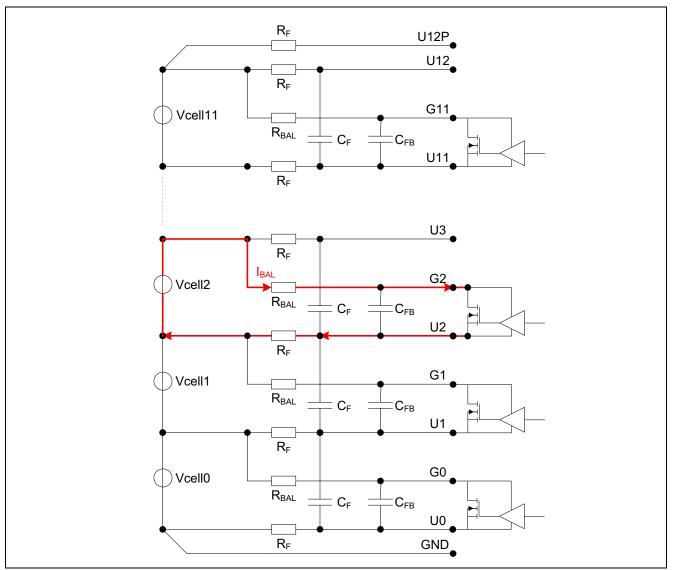

The TLE9012AQU IC supports passive balancing of up to 12 cells connected in series. The device contains 12 built-in MOSFET switches which can be used together with external resistors to dissipate each cell's energy, see **Figure 7**.

Balancing can be activated for each cell independently and in any combination, including all 12 channels simultaneously. The internal switches can support balancing currents of  $I_{BAL}$ . For balancing currents higher than  $I_{BAL}$ , external P channel MOSFET transistors can be used as shown in **Figure 9**.

# Cell management unit

Figure 7 Passive balancing example of Cell2

Passive balancing is initiated by the host microcontroller by writing to the **BAL\_SETTINGS** register via the UART or the iso UART interface. Writing a "1" to the ON\_1 bit-field, for instance, will turn on the passive balancing switch connected to the G1 pin and the current will start flowing. The switch remains on until a "0" is written to the ON\_1 bit-field, the IC enters the sleep state or a failure occurs (see **Chapter 8.4**).

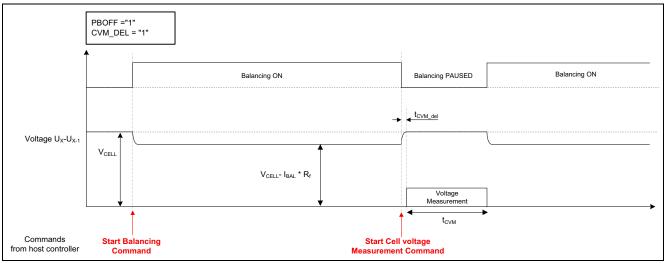

To avoid measurement errors due to passive balancing current, the passive balancing switches can be deactivated automatically during the conversion by setting the PBOFF bit-field in the **MEAS\_CTRL** register.

#### Cell management unit

Figure 8 Timing diagram for balancing & cell voltage measurement with  $t_{CVM del}$  (PBOFF Bit = 1)

A programmable settling time  $t_{\text{CVM}_{del}}$  (bit-field CVM\_DEL) can be programmed in the **MEAS\_CTRL** register; this delays the start of the measurement after the passive balancing transistors are disabled. Please note that for a global synchronization the start of the measurement is always delayed by  $t_{\text{CVM}_{del}}$  no matter whether balancing was happening or not. Please see **Figure 8** for more details.

The TLE9012AQU includes an extended watchdog mode. In this mode, the watchdog LSB step interval changes to  $t_{WD\_EXT\_LSB}$ . With this extended timing, there is a maximum watchdog duration of  $t_{WD\_EXT\_max}$ .

During the round robin (RR) measurements, the passive balancing switches will be deactivated to avoid false detections during the round robin checks. After the RR scheme is done, the balancing will continue automatically (this is true independent of the PBOFF state). If balancing was activated before the RR starts, the RR will perform a balancing over- and undercurrent check. The balancing fault flag (one for OC and one for UC) is set in the **GEN\_DIAG** register if an overcurrent or undercurrent occurs on any cell.

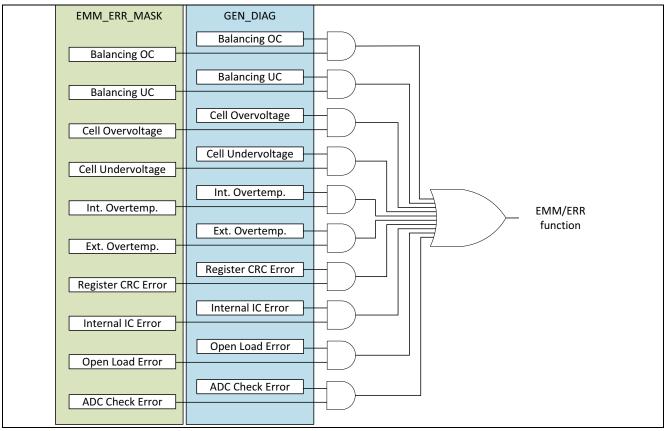

The balancing function will be deactivated if one of the following errors is detected. The errors are indicated in **GEN\_DIAG**.

- Balancing error overcurrent, bit-field: BAL\_ERR\_OC. Balancing only for affected cell(s) deactivated.

- Balancing error undercurrent, bit-field: BAL\_ERR\_UC. Balancing only for affected cell(s) deactivated.

- Overvoltage error, bit-field: CELL\_OV. Balancing only for affected cell(s) deactivated.

- Undervoltage error, bit-field: CELL\_UV. Balancing only for affected cell(s) deactivated.

- Internal temperature sensor over temperature error, bit-field: INT\_OT. Balancing for all cells deactivated.

- External temperature sensor measurement error, bit-field: EXT\_OT. Balancing for all cells deactivated.

- Configuration register CRC error, bit-field: REG\_CRC\_ERR. Balancing for all cells deactivated.

- Internal IC error, bit-field: INT\_IC\_ERR. Balancing for all cells deactivated.

- Open load error, bit-field: OL\_ERR. Balancing for all cells deactivated.

- ADC error, bit-field: ADC\_ERR. Balancing for all cells deactivated.

# 5.4.1 Using external balancing switches

If the necessary current is higher than the maximum allowed internal balancing current, an external P-MOS can be used to increase the balancing current further. Assuming a proper dimensioning of the external components, all the functions remain unchanged. Please see **Figure 9** for more details. The Roc/uc resistor is

# infineon

# TLE9012AQU Datasheet

# Cell management unit

needed to support the balancing overcurrent and undercurrent diagnosis also for the external switch (see also **Chapter 5.5.2**).

Figure 9 Diagram of the cell unit using external balancing switches

# 5.4.2 Electrical characteristics

# Table 10 Electrical characteristics

$V_{VS}$  = 4.75 V to 60 V,  $T_j$  = -40°C to +150°C, all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                | Symbol                |      | Values |      |    | Note or                           | Number |

|------------------------------------------|-----------------------|------|--------|------|----|-----------------------------------|--------|

|                                          |                       | Min. | Тур.   | Max. |    | <b>Test Condition</b>             |        |

| Input leakage current<br>Gn              | I <sub>Gn_leak</sub>  | -1.0 | 0      | 1.0  | μA | 0≤n≤11<br>in sleep & idle<br>mode |        |

| Balancing switch on-<br>state resistance | R <sub>BAL_DSON</sub> | 1.5  | 2.7    | 5.3  | Ω  | $1.5V \le V_{Cell}$               |        |

# Table 10Electrical characteristics (cont'd)

$V_{VS}$  = 4.75 V to 60 V,  $T_j$  = -40°C to +150°C, all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                  | Symbol                  |      | Values |                     |    | Note or                                                                                                                                                                                                                                | Number |

|--------------------------------------------|-------------------------|------|--------|---------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                            |                         | Min. | Тур.   | Max.                |    | <b>Test Condition</b>                                                                                                                                                                                                                  |        |

| Balancing current                          | I <sub>BAL</sub>        | -    | -      | 150                 | mA | $1.5V \le V_{Cell}$                                                                                                                                                                                                                    |        |

| Balancing<br>overcurrent detection<br>time | t <sub>BAL_OC_DET</sub> | -    | _      | t <sub>RR_max</sub> | ms | <sup>1)</sup> Time till a<br>balancing over<br>current must be<br>detected.<br>Equivalent to<br>max. round robin<br>cycle time (when<br>the error counter<br>is disabled which<br>is the default<br>value,<br>M_NR_ERR_BAL_<br>OC = 1) |        |

1) Not subject to production test, specified by design.

# 5.5 Cell diagnosis

The cell diagnosis are part of the round robin (see **Chapter 8.3**). The TLE9012AQU provides the necessary tools to detect a possible open load/wire of the different cell connections.

In order to help the diagnosis, the following hardware is available:

- 12x cell-specific Sigma-Delta ADC (CVM)

- 1x block measurement ADC (BVM)

- 12x diagnosis current sink (1x for each cell)

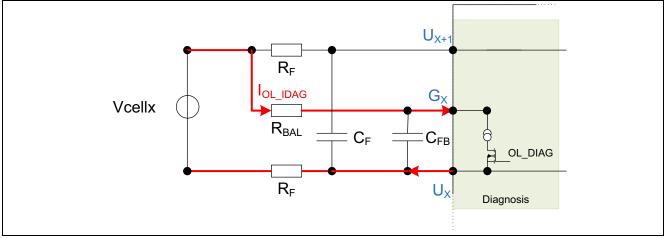

Figure 10 Current path for open load detection

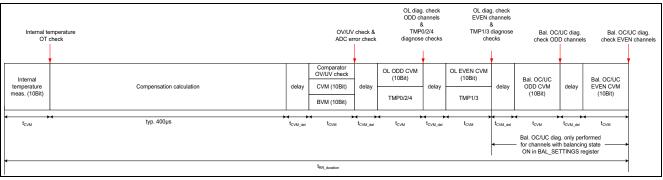

# 5.5.1 Automatic open load detection

The TLE9012AQU offers the possibility to automatically detect open wires in the following pins: Ux, Gx, VS/U12P and GND.

The following steps are executed in the automatic open load detection:

- Turn off diagnosis current sinks and balancing switches (just to be sure that they are off).

- Wait for the duration set in the CVM\_DEL (register **MEAS\_CTRL**).

- Voltage measurement with all CVM in fast acquisition mode (10 bits in 75  $\mu$ s).

- Measure block voltage with BVM. This step is done simultaneously with the previous one.

- Store all 13 intermediate values (12x CVM + 1x BVM) and perform ADC check.

- Turn ON all ODD diagnosis current sinks.

- Wait for the duration set in the CVM\_DEL (register MEAS\_CTRL).

- Voltage measurement with all ODD SD-ADC.

- Turn OFF all ODD diagnosis current sinks.

- Compare ODD results.

- Turn ON all EVEN diagnosis current sinks.

- Wait for the duration set in the CVM\_DEL (register MEAS\_CTRL).

- Voltage measurement with all EVEN SD-ADC.

- Turn OFF all EVEN diagnosis current sinks.

- Store all 12 intermediate values (6x odd cell specific values + 6x even cell specific values).

- Compare EVEN results.

#### Cell management unit

This test will detect an open wire in the path marked in red on **Figure 10**. The sequence above happens automatically within every RR (see also **Chapter 8**). Once the results are available the following conclusions can be derived:

- If the wire is intact, the voltage measurements before turning on the diagnosis current sinks and after turning off again shall have only a small difference (by I<sub>OL\_DIAG</sub>\* R<sub>F</sub>). If the OL thresholds are set properly to the voltage difference, no OL fault will be indicated.

- If the wire is not connected at the cell (so an open connection between cell + / cell and the respective R<sub>F</sub> or the R<sub>F</sub> itself at U<sub>x</sub> is broken as open), the measurement comparison will result in a higher delta voltage and an OL fault will be indicated if the OL\_max threshold exceeded.

- if R<sub>F</sub> at U<sub>x</sub> is broken as a short or R<sub>BAL</sub> is broken open, the result will be a lower delta voltage and an OL fault will be indicated if OL\_min threshold exceeded.

Furthermore in order to detect an open wire on the corner wire connecting pins U12P/U12/VS or GND/U0 (or the lowest Ux if less than 12 cells are connected) with the respective cell, all CVM values retrieved during the first CVM measurement need to be added up and the sum should be compared to the BVM (ADC check). This happens automatically in RR in the CVM vs BVM check:

- If the wire connecting U12P/U12/VS or GND/U0 is open, a CVM vs BVM check fault will occur.

- Further distinction between U12P/U12/VS and GND/U0 happens via a cell voltage check (similar to UV but with hard programmed 50 mV threshold). If the lowest cell voltage result is close to zero, the fault happened at GND/U0, and if the highest cell voltage result is close to zero, the fault happened at U12P/U12/VS.

- If both errors which are described above occur (CVM vs. BVM & V\_cell < 50 mV) at the same time, the TLE9012AQU also increments the respective OL error counter.

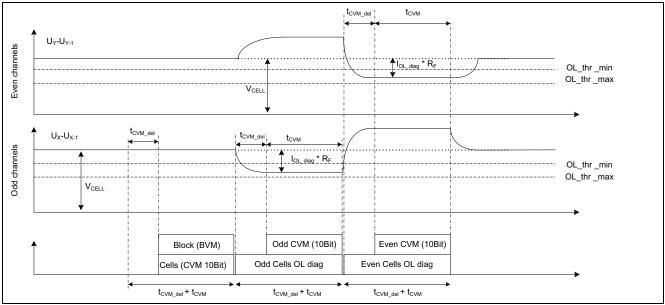

The following diagram shows the full process and the expected voltage variations:

Figure 11 Open load detection timing diagram (no faults)

# 5.5.2 Overcurrent and undercurrent

The TLE9012AQU offers the possibility to detect over- and undercurrent during balancing. This check will be done during the round robin diagnosis for each cell were balancing was active at the start of the round robin. The check principle is similar to the open load check described in the chapter above.

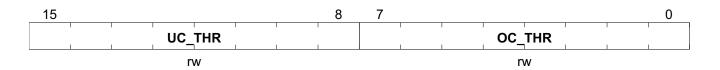

During balancing, the round robin function will read the cell voltage and compare the value to the expected value (voltage difference =  $I_{BAL} * R_F$ ):

- If the difference is lower than the threshold UC\_THR (register **BAL\_CURR\_THR**), the undercurrent error counter will be incremented.

- If the difference is higher than the threshold OC\_THR (register **BAL\_CURR\_THR**), the overcurrent error counter will be incremented.

As soon as a balancing error is set in **GEN\_DIAG**, the balancing function will be disabled for the given channel. If an external PMOS is used see chapter 5.4.1.

# 5.5.3 Electrical characteristics

#### Table 11Electrical characteristics

$V_{\rm VS}$  = 4.75 V to 60 V,  $T_{\rm j}$  = -40°C to +150°C, all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                                  | Symbol                  | Symbol Valu |                     |      | Unit | Note or                                                                                 | Number |

|------------------------------------------------------------|-------------------------|-------------|---------------------|------|------|-----------------------------------------------------------------------------------------|--------|

|                                                            |                         | Min.        | Тур.                | Max. |      | Test Condition                                                                          |        |

| Sink current for open load diagnosis                       | I <sub>OL_DIAG</sub>    | 10          | 15                  | 18.3 | mA   | $0.75 \text{ V} \leq V_{\text{cell}}$                                                   |        |

| Open load                                                  |                         |             |                     |      |      |                                                                                         |        |

| Open load threshold maximum value                          | OL <sub>thr_range</sub> | -           | 307.6               | -    | mV   | <sup>1)</sup> bit-field with<br>6 bits                                                  |        |

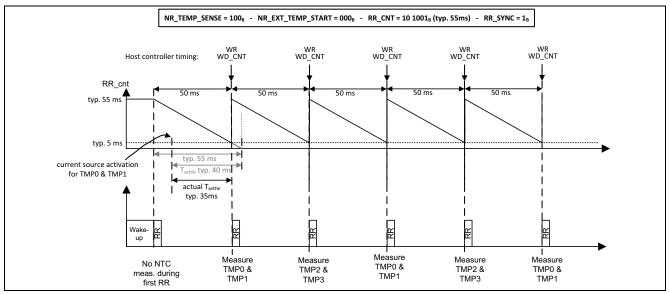

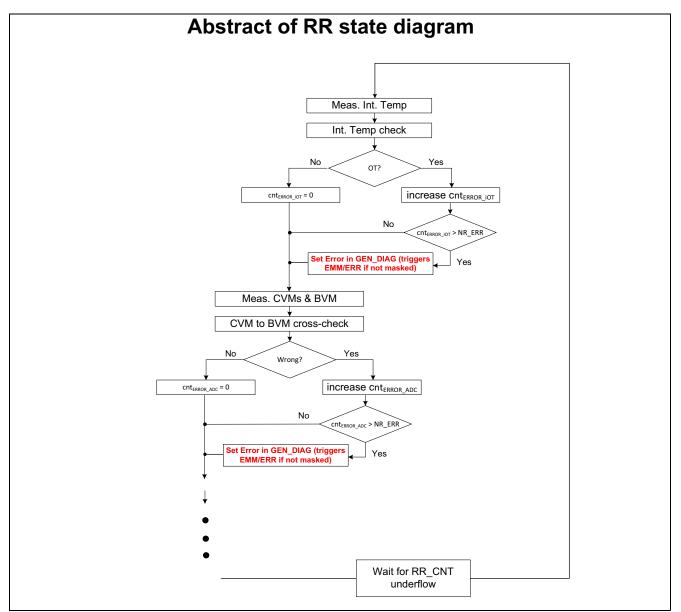

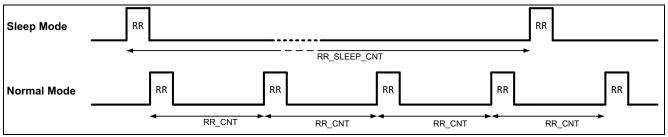

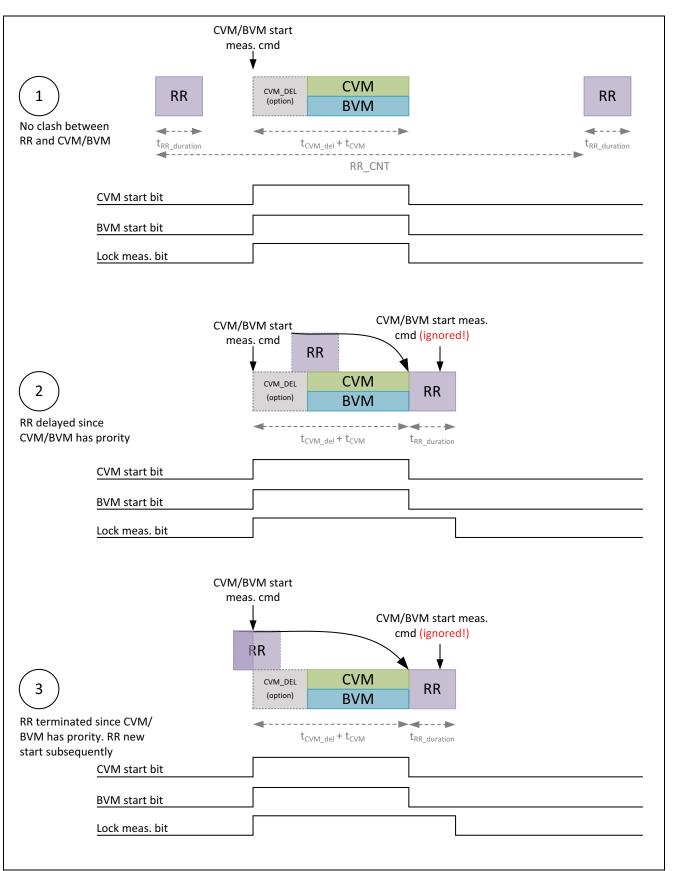

| Open load threshold resolution                             | OL <sub>thr_res</sub>   | -           | FSR/2 <sup>10</sup> | -    | mV   | <sup>1)</sup> FSR = 5 V                                                                 |        |