# Multiple MOSFET Driver IC

# 1 Overview

# **Features**

- Eight half-bridge gate drivers for external N-channel MOSFETs

- Control of reverse battery protection MOSFET

- Adaptive MOSFET gate control

- Improved electromagnetic emission

- Reduced switching losses in PWM mode

- 24-bit Serial Peripheral Interface

- Two current sense amplifiers with configurable gain

- High-side and low-side capable for protection and diagnosis

- Drain-source monitoring for short circuit detection

- · Overtemperature warning and shutdown

- Timeout watchdog

- Detailed off-state diagnostic (open load, short circuit to battery or short circuit to GND) via SPI

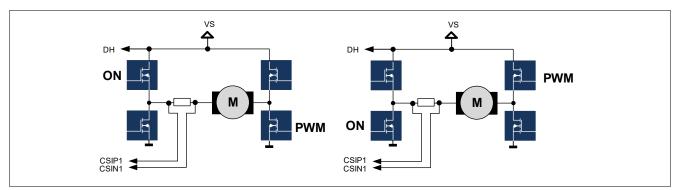

- Three PWM inputs

- High-side and low-side PWM capable

- Active free-wheeling

- Up to 25 kHz PWM frequency

- Low current consumption in sleep mode

- Leadless power package with support of optical lead tip inspection

- Green Product (RoHS compliant)

- AEC Qualified

# **Potential applications**

- Seat control and extended functions (steering column adjustment, gas pedal adjustment)

- Central door lock

- Body control module (cargo cover, washer pump, window lift, rear wiper ...)

# **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

# **Multiple MOSFET Driver IC**

### Overview

# **Description**

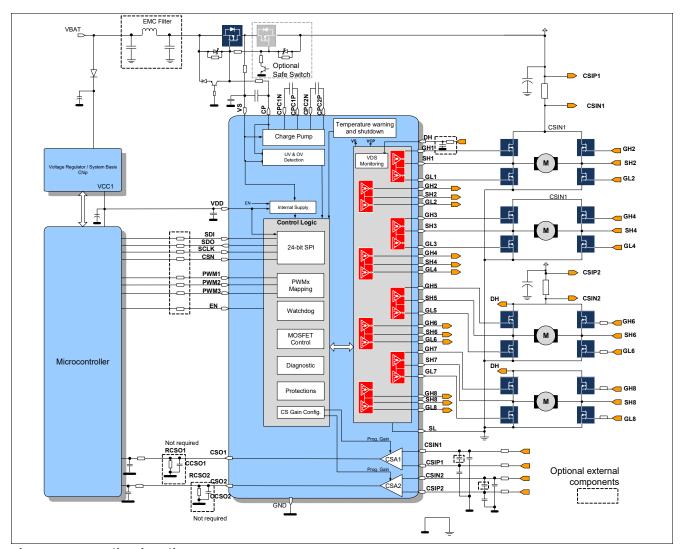

The TLE92108-231QX is a Multi-MOSFET driver IC dedicated to control up to sixteen n-channel MOSFETs. It includes eight half-bridges for DC motor control applications such as automotive power seat control or other applications.

A 24-bit Serial Peripheral Interface (SPI) is used to configure the TLE92108-231QX and to control the halfbridges. It also allows the read out of the status registers for diagnostic purpose.

The TLE92108-231QX offers a wide range of diagnostic features such as the monitoring of the supply voltage, the charge pump voltage, temperature warning and over-temperature shutdown. Each gate driver monitors independently its external MOSFET drain-source voltage for fault conditions.

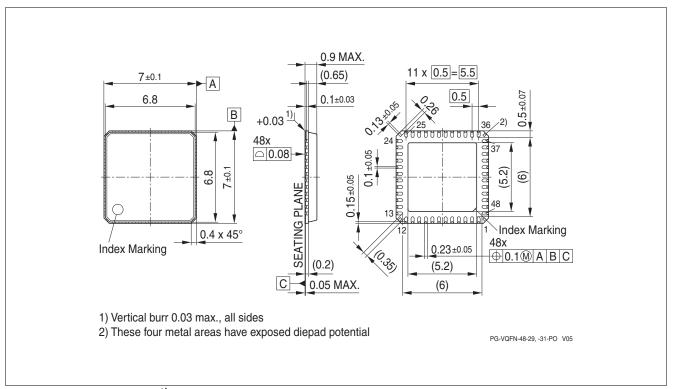

The device is housed in a VQFN-48 with exposed pad supporting lead tip inspection. The package provides a good thermal performance and minimizes the required PCB space.

| Туре           | Package    | Marking        |

|----------------|------------|----------------|

| TLE92108-231QX | PG-VQFN-48 | TLE92108-231QX |

# TLE92108-231QX Multiple MOSFET Driver IC

# **Table of contents**

| L                      | Overview                                                                                         | 1  |

|------------------------|--------------------------------------------------------------------------------------------------|----|

| 2                      | Block diagram                                                                                    | 4  |

| 2.1                    | Voltage and current definition                                                                   | 5  |

| 3                      | Pin configuration                                                                                | 6  |

| 3.1                    | Pin assignment                                                                                   | 6  |

| 3.2                    | Pin definitions and functions                                                                    | 7  |

| 1                      | General product characteristics                                                                  | 9  |

| 1.1                    | Absolute maximum ratings                                                                         |    |

| 1.2                    | Functional range                                                                                 |    |

| 1.3                    | Thermal resistance                                                                               |    |

| 5                      | General description                                                                              |    |

| 5.1                    | Power supply                                                                                     |    |

| 5.2<br>5.2.1           | Operation modes                                                                                  |    |

| 5.2.1                  | Normal mode                                                                                      |    |

| 5.2.3                  | Fail Safe Mode                                                                                   |    |

| 5.3                    | Reset behavior                                                                                   |    |

| 5.4                    | Charge pump                                                                                      | 16 |

| 5.5                    | Frequency modulation                                                                             | 16 |

| 5.6                    | Electrical characteristics                                                                       |    |

| 5.6.1                  | Electrical characteristics: supply                                                               |    |

| 5.6.2<br>5.6.3         | Electrical characteristics: logic inputs PWMx, EN         Electrical characteristics charge pump |    |

| .0.3                   |                                                                                                  |    |

| 5                      | Floating gate drivers                                                                            |    |

| 7                      | Protections and diagnostics                                                                      | 23 |

| 3                      | Serial Peripheral Interface - SPI                                                                |    |

| 3.1                    | SPI protocol with independent slave selection                                                    |    |

| 3.2                    | Global Error Flag (GEF)                                                                          |    |

| 3.3<br>3.4             | Global status byte                                                                               |    |

| 3. <del>4</del><br>3.5 | Daisy chain                                                                                      |    |

| 3.6                    | SPI electrical characteristics: timings                                                          |    |

| )<br>)                 | Register specification                                                                           |    |

| ,                      | Application information                                                                          |    |

| LO                     | • •                                                                                              |    |

| <b>l1</b>              | Package outlines                                                                                 |    |

| <b>L2</b>              | Revision History                                                                                 | 40 |

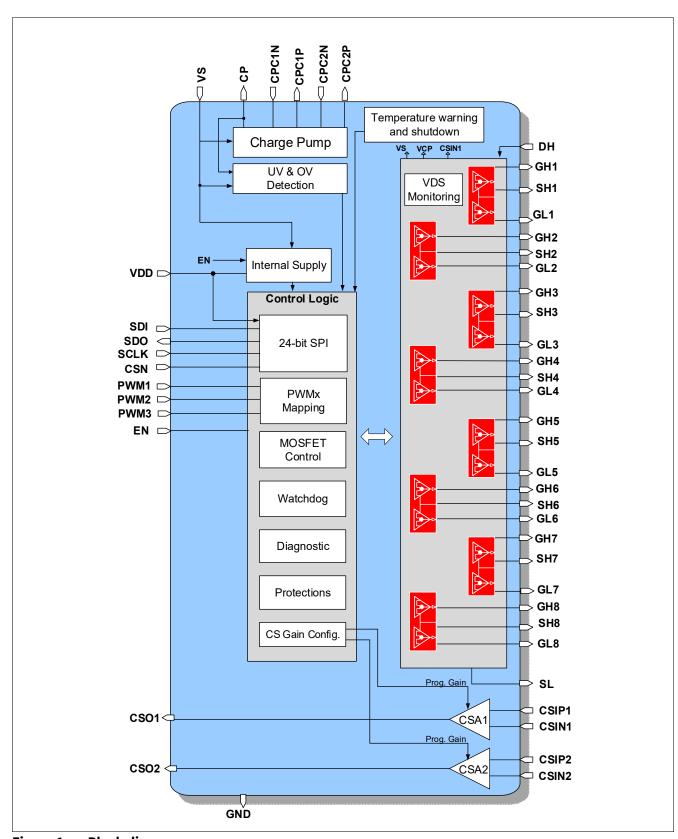

### **Block diagram** 2

Figure 1 **Block diagram**

# **Multiple MOSFET Driver IC**

# **Block diagram**

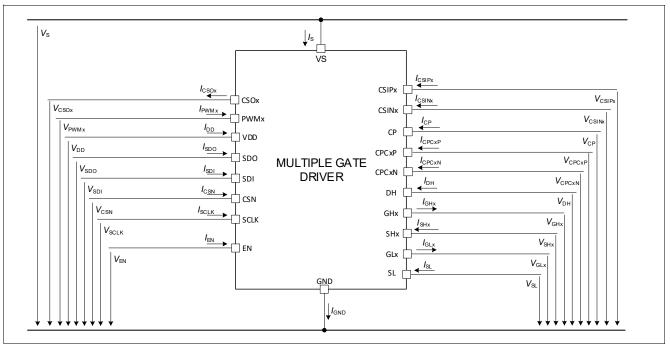

### Voltage and current definition 2.1

Figure 2 shows terms used in this datasheet, with associated convention for positive value.

Voltage and current definition Figure 2

Pin configuration

### **Pin configuration** 3

### Pin assignment 3.1

Figure 3 Pin configuration TLE92108-231QX

# **Multiple MOSFET Driver IC**

Pin configuration

### Pin definitions and functions 3.2

Pin configuration TLE92108-231QX Table 1

| Pin | Symbol | Function                                                                                                                                 |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GH1    | Gate high-side 1 Analog I/O pin to turn on/off high-side MOSFET 1. Connect to the gate of high-side MOSFET 1.                            |

| 2   | SH1    | Source high-side 1                                                                                                                       |

|     |        | Connection to source of high-side MOSFET 1.                                                                                              |

| 3   | PWM3   | PWM input 3                                                                                                                              |

| 4   | СР     | Charge Pump Output                                                                                                                       |

| 5   | VS     | <b>Supply Voltage</b> Device supply voltage. Connect this pin to the supply (battery) voltage with a reverse battery protection circuit. |

| 6   | CPC1N  | Negative connection to Charge Pump Capacitor 1                                                                                           |

| 7   | CPC1P  | Positive connection to Charge Pump Capacitor 1                                                                                           |

| 8   | CPC2P  | Positive connection to Charge Pump Capacitor 2                                                                                           |

| 9   | CPC2N  | Negative connection to Charge Pump Capacitor 2                                                                                           |

| 10  | DH     | <b>Drain input for high-sides</b> Input for the drains of high-side MOSFETs. Refer to <b>Chapter 7.3</b> .                               |

| 11  | GH8    | Gate high-side 8                                                                                                                         |

| 12  | SH8    | Source high-side 8                                                                                                                       |

| 13  | GH7    | Gate high-side 7                                                                                                                         |

| 14  | SH7    | Source high-side 7                                                                                                                       |

| 15  | SL     | Source low-side Common connection to the source of the low-side MOSFETs.                                                                 |

| 16  | GL8    | Gate low-side 8                                                                                                                          |

| 17  | GL7    | Gate low-side 7                                                                                                                          |

| 18  | GL6    | Gate low-side 6                                                                                                                          |

| 19  | GL5    | Gate low-side 5                                                                                                                          |

| 20  | EN     | Enable input with internal pull-down                                                                                                     |

| 21  | SDO    | Serial Data Output                                                                                                                       |

| 22  | CSN    | Chip Select Not with internal pull-up                                                                                                    |

| 23  | GH6    | Gate high-side 6                                                                                                                         |

| 24  | SH6    | Source high-side 6                                                                                                                       |

| 25  | GH5    | Gate high-side 5                                                                                                                         |

| 26  | SH5    | Source high-side 5                                                                                                                       |

| 27  | CSIP2  | Non-Inverting input of the Current Sense Amplifier 2                                                                                     |

| 28  | CSIN2  | Inverting input of the Current Sense Amplifier 2                                                                                         |

| 29  | SCLK   | Serial Clock Input with internal pull-down                                                                                               |

| 30  | CSO2   | Current Sense Amplifier Output 2                                                                                                         |

# **Multiple MOSFET Driver IC**

# Pin configuration

Pin configuration TLE92108-231QX Table 1

| Pin | Symbol | Function                                                                                                                                                                                   |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31  | VDD    | Logic supply                                                                                                                                                                               |

| 32  | GND    | Ground connection                                                                                                                                                                          |

| 33  | CSO1   | Current Sense Amplifier Output1                                                                                                                                                            |

| 34  | SDI    | Serial Data Input with internal pull-down                                                                                                                                                  |

| 35  | GH4    | Gate high-side 4                                                                                                                                                                           |

| 36  | SH4    | Source high-side 4                                                                                                                                                                         |

| 37  | GH3    | Gate high-side 3                                                                                                                                                                           |

| 38  | SH3    | Source high-side 3                                                                                                                                                                         |

| 39  | CSIP1  | Non-inverting input of the Current Sense Amplifier 1                                                                                                                                       |

| 40  | CSIN1  | <b>Inverting input of the Current Sense Amplifier 1</b> . This pin can be used as reference for the high-side MOSFET drain if CSA1 is configured as high-side. Refer to <b>Chapter 7.3</b> |

| 41  | PWM2   | PWM input 2                                                                                                                                                                                |

| 42  | GL4    | Gate low-side 4                                                                                                                                                                            |

| 43  | GL3    | Gate low-side 3                                                                                                                                                                            |

| 44  | GL2    | Gate low-side 2                                                                                                                                                                            |

| 45  | GL1    | Gate low-side 1                                                                                                                                                                            |

| 46  | PWM1   | PWM input 1                                                                                                                                                                                |

| 47  | GH2    | Gate high-side 2                                                                                                                                                                           |

| 48  | SH2    | Source high-side 2                                                                                                                                                                         |

|     | E.P.   | <b>Exposed pad</b> For cooling purpose only, do not use as electrical GND <sup>1)</sup> .                                                                                                  |

<sup>1)</sup> The exposed pad at the bottom of the package allows better power dissipation from TLE92108-231QX via the PCB. The exposed pad must be left floating or connected to GND (recommended) for best EMC and thermal performance.

**General product characteristics**

### **General product characteristics** 4

### **Absolute maximum ratings** 4.1

### Absolute maximum ratings1) Table 2

$T_i = -40$ °C to 150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                          | Symbol                                                 |                      | Value | s                     | Unit | Note or               | Number   |

|--------------------------------------------------------------------|--------------------------------------------------------|----------------------|-------|-----------------------|------|-----------------------|----------|

|                                                                    |                                                        | Min.                 | Тур.  | Max.                  |      | <b>Test Condition</b> |          |

| Voltages                                                           |                                                        | -                    |       |                       |      |                       | -        |

| Supply voltage                                                     | $V_{S}$                                                | -0.3                 | -     | 40                    | V    | _                     | P_4.1.1  |

| PWM input voltages (PWMx)                                          | $V_{PWMx}$                                             | -0.3                 | _     | V <sub>DD</sub> + 0.3 | V    | /  < 10 mA            | P_4.1.2  |

| Logic input voltages (SDI, SCLK, CSN, EN)                          | $V_{\rm SDI}, V_{\rm SCLK}, \ V_{\rm CSN}, V_{\rm EN}$ | -0.3                 | _     | V <sub>DD</sub> + 0.3 | V    | /  < 10 mA            | P_4.1.3  |

| Voltage range and SDO                                              | $V_{SDO}$                                              | -0.3                 | _     | V <sub>DD</sub> + 0.3 | V    | /  < 10 mA            | P_4.1.4  |

| Voltage range at CSIPx and<br>CSINx                                | $V_{\rm CSIP}, V_{\rm CSIN}$                           | -8.0                 | -     | 40                    | V    | -                     | P_4.1.5  |

| Differential input voltage range<br>CSIPx - CSINx                  | V <sub>CSIDiff</sub>                                   | -8.0                 | -     | 8.0                   | V    | -                     | P_4.1.21 |

| Voltage range at DH                                                | $V_{DH}$                                               | -0.3                 | _     | 40                    | V    | -                     | P_4.1.6  |

| Voltage range at SL                                                | $V_{SL}$                                               | -8.0                 | _     | 6.0                   | V    | -                     | P_4.1.7  |

| Voltage range at SHx                                               | $V_{SH}$                                               | -8.0                 | _     | 48                    | V    | _                     | P_4.1.8  |

| Voltage range at GHx                                               | $V_{GH}$                                               | -8.0                 | -     | 48                    | V    | -                     | P_4.1.9  |

| Voltage range at GLx                                               | $V_{GL}$                                               | -8.0                 | -     | 24                    | V    | -                     | P_4.1.10 |

| Voltage difference between GLx and SL                              | $V_{\rm GS\_LS}$                                       | -0.3                 | _     | 16                    | V    | -                     | P_4.1.11 |

| Voltage difference between GHx and SHx                             | V <sub>GS_HS</sub>                                     | -1.0                 | -     | 16                    | V    | 2)                    | P_4.1.23 |

| Voltage range at charge pump<br>pins CP                            | V <sub>CP</sub>                                        | V <sub>S</sub> -0.3  | -     | V <sub>S</sub> +15    | V    | -                     | P_4.1.12 |

| Voltage range at charge pump<br>pins CPC1N, CPC1P, CPC2N,<br>CPC2P | V <sub>CPCx</sub>                                      | V <sub>CP</sub> -0.3 | -     | V <sub>CP</sub> +0.3  | V    | -                     | P_4.1.22 |

| Logic supply voltage                                               | $V_{\mathrm{DD}}$                                      | -0.3                 | -     | 5.5                   | V    | -                     | P_4.1.13 |

| Voltage at CSOx                                                    | V <sub>CSOx</sub>                                      | -0.3                 | _     | V <sub>DD</sub> + 0.3 | V    | -                     | P_4.1.14 |

| Temperatures                                                       | •                                                      | ·                    |       |                       |      |                       | •        |

| Junction temperature                                               | $T_{\rm j}$                                            | -40                  | -     | 150                   | °C   | _                     |          |

| Storage temperature                                                | $T_{\rm stg}$                                          | -55                  | _     | 150                   | °C   | _                     | P_4.1.16 |

# **Multiple MOSFET Driver IC**

**General product characteristics**

# Table 2 Absolute maximum ratings<sup>1)</sup> (cont'd)

$T_{\rm j}$  = -40°C to 150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                       | Symbol               |      | Value | S            | Unit           | Note or               | Number   |  |

|-------------------------------------------------|----------------------|------|-------|--------------|----------------|-----------------------|----------|--|

|                                                 |                      | Min. | Тур.  | Max.         |                | <b>Test Condition</b> |          |  |

| ESD susceptibility                              | -!                   |      |       | <del>!</del> | <del>- '</del> |                       |          |  |

| ESD susceptibility all pins                     | $V_{\rm ESDHBM1}$    | -2   | _     | 2            | kV             | HBM <sup>3)</sup>     | P_4.1.17 |  |

| ESD susceptibility of VS and DH pins versus GND | V <sub>ESDHBM2</sub> | -4   | -     | 4            | kV             | HBM <sup>3)</sup>     | P_4.1.18 |  |

| ESD susceptibility all pins                     | $V_{\rm ESDCDM1}$    | -500 | _     | 500          | V              | CDM <sup>4)</sup>     | P_4.1.19 |  |

| ESD susceptibility pin corner pins              | V <sub>ESDCDM2</sub> | -750 | -     | 750          | V              | CDM <sup>4)</sup>     | P_4.1.20 |  |

- 1) Not subject to production test, specified by design.

- 2)  $V_{\rm GS~GH}$  may be between -1.0 and -0.3V only if the current injected into SHx is below 4 mA

- 3) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS001 (1.5 k $\Omega$ , 100 pF).

- 4) ESD susceptibility, Charged Device Model "CDM" according JEDEC JESD22-C101.

### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

# 4.2 Functional range

Table 3 Functional range

| Parameter                                 | Symbol                                       |      | Value | S                           | Unit | Unit Note or Test Condition                       | Numbe   |

|-------------------------------------------|----------------------------------------------|------|-------|-----------------------------|------|---------------------------------------------------|---------|

|                                           |                                              | Min. | Тур.  | Max.                        |      |                                                   | r       |

| Supply voltage range for normal operation | $V_{S(nor)}$                                 | 6.0  | -     | 28                          | V    | -                                                 | P_4.2.1 |

| Extended supply voltage range             | V <sub>S(ext)</sub>                          | 5.5  | -     | 6                           | V    | <sup>1)</sup> Parameter<br>deviations<br>possible | P_4.2.7 |

| Extended supply voltage range             | V <sub>S(ext)</sub>                          | 28   | -     | V <sub>SOV_OFF2</sub> (max) | V    | <sup>1)</sup> Parameter<br>deviations<br>possible | P_4.2.2 |

| Supply voltage transients slew rate       | $dV_S/dt$                                    | -10  | -     | 10                          | V/µs | 1)                                                | P_4.2.3 |

| Logic supply voltage                      | $V_{DD}$                                     | 3.0  | -     | 5.5                         | ٧    | -                                                 | P_4.2.4 |

| SPI logic input voltage                   | $V_{\rm SDI}, \ V_{\rm SCLK}, \ V_{\rm CSN}$ | 0    | -     | V <sub>DD</sub>             | V    | -                                                 | P_4.2.5 |

| Junction temperature                      | T <sub>i</sub>                               | -40  | -     | 150                         | °C   | _                                                 | P_4.2.6 |

# TLE92108-231QX **Multiple MOSFET Driver IC**

# **General product characteristics**

1) Not subject to production test, specified by design.

Note:

Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

# **Multiple MOSFET Driver IC**

**General product characteristics**

# 4.3 Thermal resistance

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to **www.jedec.org**.

### Table 4 Thermal resistance

| Parameter           | Symbol            |      | Values |      | Unit | nit Note or           | Number |

|---------------------|-------------------|------|--------|------|------|-----------------------|--------|

|                     |                   | Min. | Тур.   | Max. |      | <b>Test Condition</b> |        |

| Junction to case    | R <sub>thJC</sub> | _    | 4.4    | _    | K/W  | 1)                    |        |

| Junction to ambient | $R_{\rm thJA}$    | _    | 27     | _    | K/W  | 1)2)                  |        |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 2 inner copper layers (2 × 70 mm Cu, 2 × 35 mm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

# **General description**

# 5 General description

# 5.1 Power supply

The Multiple MOSFET Driver IC requires two power supplies:  $V_{\rm S}$  and  $V_{\rm DD}$ .

$V_{\rm DD}$  supplies the I/O buffers (including the SPI pins) and the internal voltage regulator for the logic.  $V_{\rm DD}$  allows the flexibility of a 3.3 V or a 5.0 V logic interface.

$V_{\rm S}$  supplies the charge pump for the MOSFET gate drivers. The  $V_{\rm S}$  pin must be connected to the battery through a reverse battery protection.

Both supplies are separated so that the information stored in the logic remains intact in the event of voltage drop on  $V_S$ .  $V_{DD}$  and  $V_S$  should be decoupled with ceramic capacitors connected close to the supply and ground planes.

# 5.2 Operation modes

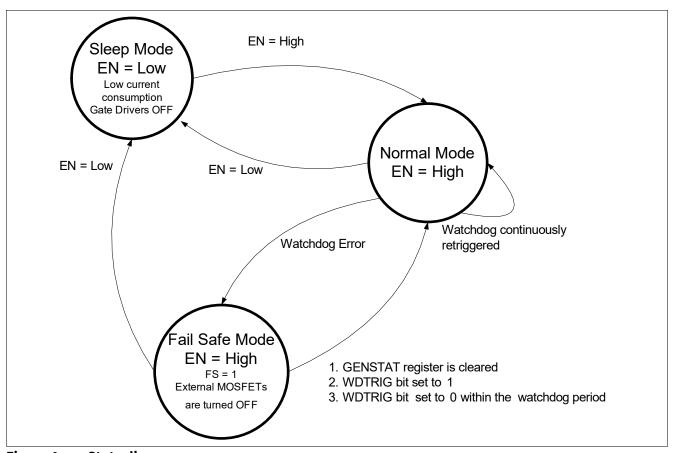

Figure 4 State diagram

Note: The state diagram is valid for  $V_S$  and  $V_{DD}$  within the nominal operating range. For  $V_S$  and  $V_{DD}$  outside of the nominal range, refer to **Chapter 7.7**, respectively **Chapter 5.2.2**.

### 5.2.1 Normal mode

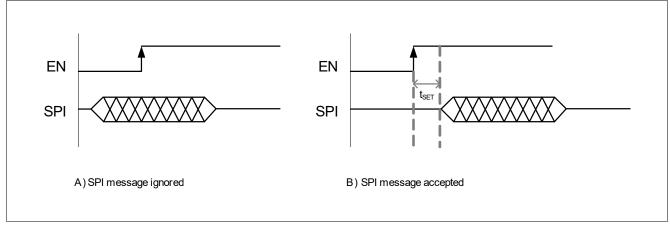

The TLE92108-231QX enters Normal Mode by setting EN pin to High and waiting for the SPI setup time  $t_{\text{SET\_SPI}}$ . In normal mode, the MOSFET gate drivers are enabled and can be configured through the SPI interface,

# TLE92108-231QX Multiple MOSFET Driver IC

# infineon

# **General description**

provided that the voltages applied to  $V_{DD}$  and  $V_{S}$  are within the operating range. The watchdog must be retriggered correctly in order to stay in Normal Mode (see **Chapter 7.9**).

### 5.2.2 Sleep mode

The Multiple MOSFET Driver IC enters Sleep Mode by setting EN pin to Low. The transition to the sleep mode is delayed by  $t_{DSLEEP}^{1)}$  (max tCCP of active half-bridges + 3  $\mu$ s) in order to actively turn-off the external MOSFETs. In this mode, the internal regulator and the internal circuitry are deactivated, and the SPI registers are reset.

The current consumption of  $V_{DD}$  is reduced to  $I_{DD_Q}$ . The current consumption of  $V_S$  is reduced to  $I_{SQ}$  or  $I_{SQ}$  +  $I_{SO}$  BRAKE.

The  $V_S$  current consumption is  $I_{SQ}$  if  $V_S$  never drops below  $V_{SLEEP\_SET}$  after entering sleep mode.

The  $V_S$  current consumption is  $I_{SQ} + I_{SQ\_BRAKE}$  if  $V_S$  has recovered from a voltage below  $V_{SLEEP\_SET}$  (i.e.  $V_S$  has ramped up from a voltage below  $V_{SLEEP\_SET}$ )

The internal resistors  $R_{GGND}$  between GHx/GLx and GND are activated to discharge the gate of the external MOSFETs.

Note:

If EN is set to Low for a duration shorter than ( $t_{\text{ENL\_FILT}}$ , 8  $\mu$ s max.), and EN is set to High again, then device does not go in sleep mode and the registers are not reset. The half-bridges are reactivated according to the settings of the control registers when EN is High.

### 5.2.3 Fail Safe Mode

In case of watchdog error (see **Chapter 7.9**), the device enters Fail Safe Mode, FS bit is set (see **Global status byte**) and the external MOSFETs are actively discharged with the static discharge current (**Chapter 6.2**) during the max. configured tHBxCCP active (**Chapter 7.4.1**). Then the bridge driver is set to passive mode (the passive discharge path is activated, **Chapter 6.4**, all external MOSFETs are latched off, and the charge pump is deactivated). To resume Normal Mode the microcontroller must execute the following sequence<sup>2)</sup>:

- Clear GENSTAT register.

- 2. Write WDTRIG bit to 1 (**GENCTRL1**) within the watchdog period.

- 3. Write WDTRIG bit to 0 within the watchdog period<sup>3)</sup>.

In fail safe mode, the control registers are frozen to their default value, at the exception of **WDTRIG**, **CCSO**, **CSA1L**, **CSA2L**. Any write command (except for WDTRIG bit) or clear command (except for GENSTAT) will be discarded in this mode and sets SPIE bit (**Global status byte**).

A clear command to **GENSTAT** in fail safe mode does not reset any failure flag reported by this status register. The control and status registers can be read in this mode before the start of the exit sequence without SPIE bit being set.

<sup>1)</sup> SPI Frames are ignored during t<sub>DSLEEP</sub>.

<sup>2)</sup> The exit sequence must be strictly followed to leave fail safe mode. If a SPI frame not belonging to the sequence is added, then the device stays in fail safe mode and the microcontroller must restart the complete sequence to enter normal mode.

<sup>3)</sup> During Fail Safe Mode, the charge pump is deactivated and **CPUV** is set. Therefore, recovering from Fail Safe Mode, **GENSTAT** must be cleared again at the end of the Fail Safe exit sequence to re-activate of the gate drivers.

# **Multiple MOSFET Driver IC**

# **General description**

#### 5.3 **Reset behavior**

The following events trigger a Power On Reset:

# **V**<sub>DD</sub> undervoltage reset:

If  $V_{\rm DD} < V_{\rm DD\,PoffR}$  the digital block is deactivated and the outputs are switched off. The digital block is reset once  $V_{\rm DD} > V_{\rm DD\ POR}$ . Then NPOR bit (negated power-on reset bit, see **Global status byte**) is reset to 0 to report the reset condition.

## Reset on EN pin:

If the EN pin is pulled low, the logic content is reset and the device enters sleep mode. Once the device enters Normal Mode (after  $\mathbf{t_{SET\_SPI}}$  with EN = high and  $V_{DD} > V_{DD\ POR}$ ), the NPOR bit is reset to 0 to report the reset condition.

NPOR is set to 1 when **GENSTAT** is cleared.

# **Multiple MOSFET Driver IC**

# **General description**

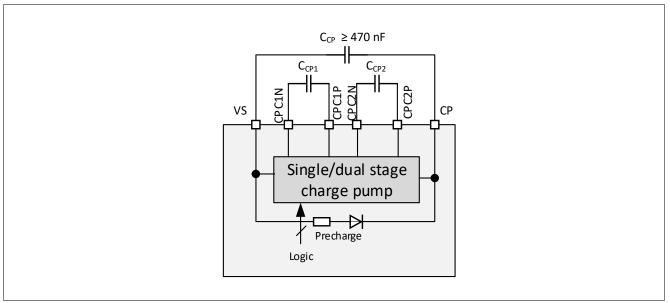

# 5.4 Charge pump

A dual-stage charge pump supplies the gate drivers for the high-side and low-side MOSFETs. It requires three external capacitors connected between CPC1N and CPC1P, CPC2N and CPC2P, VS and CP.

Figure 5 Charge pump

CPSTGA = 0 (default, see **GENCTRL2**), the device operates with the dual-stage charge pump.

If CPSTGA = 1 (**GENCTRL2**), the device switches automatically to single-stage or dual-stage charge pump automatically:

- If  $V_S > V_{CPSO\,DS}$ : the TLE92108-231QX switches from a dual-stage to a single-stage charge pump.

- If  $V_S < V_{CPSO SD}$ : the TLE92108-231QX switches from single-stage to dual-stage charge pump.

The operation with the single-stage charge pump reduces the current consumption from the VS pin.

# 5.5 Frequency modulation

A modulation of the charge pump frequency can be activated to reduce the peak emission. The modulation frequency can be selected based on the resolution bandwidth of the peak detector during EMC testing.

The modulation frequency is set by the control bit FMODE in **GENCTRL1**

- FMODE = 0: No modulation.

- FMODE = 1: Modulation frequency = 15.6 kHz (default).

# **General description**

#### **Electrical characteristics** 5.6

### **Electrical characteristics: supply** 5.6.1

#### Table 5 **Electrical characteristics: supply**

$V_{\rm S}$  = 6.0 V to 18 V if VSOVTH = 0,  $V_{\rm S}$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{\rm DD}$  = 3.0 V to 5.5 V,  $T_{\rm j}$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                          | Symbol                          | Symbol Values |              | Unit                  | Note or | Number                                                                                                                                                                    |          |

|----------------------------------------------------|---------------------------------|---------------|--------------|-----------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                    |                                 | Min.          | Тур.         | Max.                  |         | <b>Test Condition</b>                                                                                                                                                     |          |

| Current consumption, EN =                          | LOW)                            | +             | <del>-</del> | ,                     | •       | •                                                                                                                                                                         | •        |

| Supply quiescent current                           | I <sub>SQ</sub>                 | -             | 2            | 5                     | μΑ      | $T_{\rm j}$ < 85°C, $V_{\rm S}$ = 13.5 V                                                                                                                                  | P_5.5.1  |

| Supply quiescent current                           | I <sub>SQ2</sub>                | -             | 5            | 7                     | μΑ      | $T_{\rm j}$ < 85°C, $V_{\rm S}$ < 25 V                                                                                                                                    | P_5.5.61 |

| Additional supply quiescent current, brake enabled | I <sub>SQ_BRAKE</sub>           | _             | 5            | 7.5                   | μΑ      | $T_{\rm j}$ < 85°C,<br>$V_{\rm S}$ = 13.5 V <sup>1)</sup>                                                                                                                 | P_5.5.60 |

| Logic Supply quiescent<br>current                  | $I_{\mathrm{DD}_{-}\mathrm{Q}}$ | _             | 1            | 3                     | μΑ      | <i>T</i> <sub>j</sub> < 85°C                                                                                                                                              | P_5.5.3  |

| Total quiescent current                            | $I_{DD_Q} + I_{SQ}$             | _             | 3            | 8                     | μΑ      | $T_{\rm j}$ < 85°C, $V_{\rm S}$ = 13.5 V                                                                                                                                  | P_5.5.5  |

| EN Low filter time                                 | t <sub>DSLEEP</sub>             | -             | -            | Max.<br>tCCP+<br>3 μs | μs      | <sup>2)3)</sup> <b>BD_PASS</b> = 0                                                                                                                                        | P_5.5.49 |

| EN Low filter time                                 | t <sub>ENL_FILT</sub>           | 1             | _            | 8                     | μs      | 2)                                                                                                                                                                        | P_5.5.51 |

| VS for LS1-4 setting                               | V <sub>SLEEP_SET</sub>          | _             | _            | 5.5                   | V       |                                                                                                                                                                           | P_5.5.63 |

| Current consumption, EN =                          |                                 | -             |              | -                     |         |                                                                                                                                                                           | ı        |

| Supply current                                     | I <sub>S1</sub>                 | -             | 45           | 55                    | mA      | $HBxVDSTH = 001_B,$ $BD\_PASS = 0,$ $I_{CP} = 0 \text{ mA}$                                                                                                               | P_5.5.6  |

| Supply current                                     | I <sub>52</sub>                 | -             | 83           | 100                   | mA      | $8 \text{ V} < V_S < 28 \text{ V}$<br>$\text{HBxVDSTH} = 001_B$ ,<br>$\text{BD}\_\text{PASS} = 0$ ,<br>$I_{\text{CP}} = -12 \text{ mA}$ ,<br>dual stage CP                | P_5.5.7  |

| Supply current                                     | I <sub>53</sub>                 | -             | 55           | 70                    | mA      | $18 \text{ V} < V_{\text{S}} < 28 \text{ V}$<br>$\text{HBxVDSTH} = 001_{\text{B}},$<br>$\text{BD\_PASS} = 0,$<br>$I_{\text{CP}} = -12 \text{ mA}^{2},$<br>single stage CP | P_5.5.56 |

| Supply current                                     | I <sub>S4</sub>                 | -             | 55           | 70                    | mA      | $V_S = 6 \text{ V},$<br>$HBxVDSTH = 001_B,$<br>$BD\_PASS = 0,$<br>$I_{CP} = -6 \text{ mA}^{2}$                                                                            | P_5.5.57 |

| Supply current                                     | I <sub>S_BD_PASS</sub>          | -             | 10           | 20                    | mA      | HBxMODE=00 <sub>B</sub> , BD_PASS = 1                                                                                                                                     | P_5.5.54 |

# TLE92108-231QX **Multiple MOSFET Driver IC**

# **General description**

#### **Electrical characteristics: supply (cont'd)** Table 5

$V_{\rm S}$  = 6.0 V to 18 V if VSOVTH = 0,  $V_{\rm S}$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{\rm DD}$  = 3.0 V to 5.5 V,  $T_{\rm j}$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                 | Symbol                 |      | Value | S    | Unit | Note or<br>Test Condition                                                                                                     | Number   |

|-------------------------------------------|------------------------|------|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------|----------|

|                                           |                        | Min. | Тур.  | Max. |      |                                                                                                                               |          |

| Logic supply current                      | I <sub>DD1</sub>       | -    | 3     | 4    | mA   | SPI not active,<br>CSA1 and CSA2 off,<br>all I <sub>PDDiag</sub> off,<br>BD_PASS=0                                            | P_5.5.8  |

| Logic supply current                      | I <sub>DD2</sub>       | -    | 3     | 3.8  | mA   | 4) Additional VDD<br>current per CSA on,<br>VCSOx = 4.5 V,<br>LS shunt, CCSO = 1<br>CSAxL = 0,<br>IPDDiag off                 | P_5.5.52 |

| Logic supply current                      | I <sub>DD3</sub>       | -    | 2     | 2.8  | mA   | 4) Additional VDD<br>current per CSA on,<br>CCSO = 0,<br>VCSOx = 4.5 V,<br>LS shunt,<br>CSAxL = 0,<br>I <sub>PDDiag</sub> off | P_5.5.55 |

| Logic supply current                      | I <sub>DD4</sub>       | -    | 6     | 7    | mA   | 5) Additional VDD<br>current per CSA on,<br>VCSOx = 4.5 V,<br>HS shunt,<br>VSOVTH = 1<br>CSAxL = 1,<br>IPDDiag off            | P_5.5.58 |

| Logic supply current                      | I <sub>DD5</sub>       | -    | 4.2   | 5.2  | mA   | 5) Additional VDD<br>current per CSA on,<br>VSOVTH = 0,<br>VCSOx = 4.5 V,<br>HS shunt,<br>CSAxL = 1,<br>IPDDiag off           | P_5.5.59 |

| Additional logic supply current pull-down | I <sub>DD_PDDiag</sub> | -    | 1.5   | 2    | mA   | Additional VDD current when all $I_{\text{PDDiag}}$ are on                                                                    | P_5.5.53 |

| VS with active bridge driv                | ver (BD_PASS           | = 0) |       |      |      |                                                                                                                               |          |

| UV switch ON voltage                      | V <sub>SUV ON</sub>    | _    | _     | 5.5  | V    | $V_{\rm S}$ increasing                                                                                                        | P_5.5.11 |

| UV switch OFF voltage                     | V <sub>SUV OFF</sub>   | 4.0  | 4.5   | 5.0  | V    | $V_{\rm S}$ decreasing                                                                                                        | P_5.5.12 |

| UV ON/OFF hysteresis                      | V <sub>SUV HY</sub>    | _    | 0.5   | -    | V    | V <sub>SUV ON</sub> - V <sub>SUV OFF</sub> 2)                                                                                 | P_5.5.13 |

| OV switch OFF voltage<br>VSOVTH = 0       | V <sub>SOV OFF1</sub>  | 19   | -     | 21   | V    | V <sub>S</sub> increasing                                                                                                     | P_5.5.14 |

# **Multiple MOSFET Driver IC**

# **General description**

#### Table 5 **Electrical characteristics: supply (cont'd)**

$V_S$  = 6.0 V to 18 V if VSOVTH = 0,  $V_S$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_i$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                        | Symbol                 |      | Value | s    | Unit | Note or                                       | Number   |

|--------------------------------------------------|------------------------|------|-------|------|------|-----------------------------------------------|----------|

|                                                  |                        | Min. | Тур.  | Max. |      | <b>Test Condition</b>                         |          |

| OV switch ON voltage<br>VSOVTH = 0               | V <sub>SOV ON1</sub>   | 18   | -     | 20   | V    | $V_{\rm S}$ decreasing                        | P_5.5.15 |

| OV switch OFF voltage<br>VSOVTH = 1              | V <sub>SOV OFF2</sub>  | 29   | -     | 31   | V    | $V_{\rm S}$ increasing                        | P_5.5.16 |

| OV switch ON voltage<br>VSOVTH = 1               | V <sub>SOV ON2</sub>   | 28   | -     | 30   | V    | $V_{\rm S}$ decreasing                        | P_5.5.17 |

| OV ON/OFF hysteresis                             | V <sub>SOV HY</sub>    | _    | 1     | _    | V    | V <sub>SUV ON</sub> - V <sub>SUV OFF</sub> 2) | P_5.5.18 |

| VS undervoltage filter time                      | t <sub>VSUV_FILT</sub> | 7    | 10    | 13   | μs   | 1)                                            | P_5.5.47 |

| VS overvoltage filter time                       | t <sub>VSOV_FILT</sub> | 7    | 10    | 13   | μs   | 2)                                            | P_5.5.48 |

| CP turn-off delay after VS overvoltage detection | $t_{D\_CPVSOV}$        | 12.8 | 16    | 19.2 | μs   | 2)                                            | P_5.5.50 |

| VDD                                              |                        | -    |       | 1    |      |                                               | <u> </u> |

| V <sub>DD</sub> Power-On-Reset                   | $V_{\rm DD\ POR}$      | 2.40 | 2.60  | 2.80 | V    | V <sub>DD</sub> increasing                    | P_5.5.19 |

| V <sub>DD</sub> Power-Off-Reset                  | $V_{\rm DD\ POffR}$    | 2.30 | 2.50  | 2.70 | V    | V <sub>DD</sub> decreasing                    | P_5.5.20 |

| $V_{\rm DD}$ Power-On-Reset<br>Hysteresis        | V <sub>DD POR HY</sub> | -    | 0.1   | -    | V    | $V_{\rm DDPOR}$ - $V_{\rm DDPOffR}^{2)}$      | P_5.5.21 |

- 1) Additional quiescent current if VS drops below V<sub>SLEEP</sub> SET.

- 2) Not subject to production test, specified by design.

- 3) Max. cross-current protection time of the active half-bridges.

- 4) Parameter independent of **VSOVTH**.

- 5) Parameter independent of CCSO.

#### **Electrical characteristics: logic inputs PWMx, EN** 5.6.2

#### Table 6 **Electrical characteristics: PWMx, EN**

$V_S$  = 6.0 V to 18 V if VSOVTH = 0,  $V_S$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_i$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter             | Symbol            |                       | Values                 | ;                     | Unit | Note or<br>Test Condition | Number   |

|-----------------------|-------------------|-----------------------|------------------------|-----------------------|------|---------------------------|----------|

|                       |                   | Min.                  | Тур.                   | Max.                  |      |                           |          |

| EN high voltage       | V <sub>ENH</sub>  | 0.7 × V <sub>DD</sub> | _                      | -                     | V    | -                         | P_5.5.22 |

| EN low voltage        | $V_{ENL}$         | -                     | -                      | 0.3 × V <sub>DD</sub> | V    | _                         | P_5.5.23 |

| EN hysteresis         | V <sub>ENHY</sub> | -                     | 0.12 × V <sub>DD</sub> | -                     | V    | 1)                        | P_5.5.24 |

| EN pull-down resistor | $R_{PD_{EN}}$     | 30                    | 40                     | 50                    | kΩ   | _                         | P_5.5.25 |

| PWMx high voltage     | $V_{\text{PWMH}}$ | 0.7 × V <sub>DD</sub> | -                      | -                     | V    | -                         | P_5.5.26 |

# TLE92108-231QX Multiple MOSFET Driver IC

# Infined

# **General description**

# Table 6 Electrical characteristics: PWMx, EN

$V_S$  = 6.0 V to 18 V if VSOVTH = 0,  $V_S$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter               | Symbol               | Values |                        |                       | Unit | Note or               | Number   |

|-------------------------|----------------------|--------|------------------------|-----------------------|------|-----------------------|----------|

|                         |                      | Min.   | Тур.                   | Max.                  |      | <b>Test Condition</b> |          |

| PWMx low voltage        | $V_{PWML}$           | -      | -                      | 0.3 × V <sub>DD</sub> | V    | -                     | P_5.5.27 |

| PWMx hysteresis         | $V_{\text{PWMHY}}$   | -      | 0.12 × V <sub>DD</sub> | _                     | V    | 1)                    | P_5.5.28 |

| PWMx pull-down resistor | R <sub>PD_PWMx</sub> | 30     | 40                     | 50                    | kΩ   | -                     | P_5.5.29 |

<sup>1)</sup> Not subject to production test, specified by design.

# 5.6.3 Electrical characteristics charge pump

# Table 7 Electrical characteristics: charge pump

$V_S$  = 6.0 V to 18 V if VSOVTH = 0,  $V_S$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                              | Symbol               | Values |      |      | Unit | Note or                                                                        | Number   |

|--------------------------------------------------------|----------------------|--------|------|------|------|--------------------------------------------------------------------------------|----------|

|                                                        |                      | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                          |          |

| Charge Pump Frequency                                  | $f_{\sf CP}$         | _      | 250  | _    | kHz  | 3)                                                                             | P_5.5.30 |

| Output Voltage VCP vs. VS                              | V <sub>CPmin</sub>   | 8.5    | -    | -    | V    | $V_{\rm S} = 6  \rm V$ ,<br>$I_{\rm CP} = -6  \rm mA$                          | P_5.5.31 |

| Regulated output voltage VCP vs. VS, CPSTGA = 0        | V <sub>CP1</sub>     | 11     | 15   | 17   | V    | $8 \text{ V} < V_{\text{S}} < 28 \text{ V},$ $I_{\text{CP}} = -12 \text{ mA}$  | P_5.5.32 |

| Regulated output voltage VCP vs. VS, CPSTGA = 1        | V <sub>CP2</sub>     | 12     | 15   | 17   | V    | $18 \text{ V} < V_{\text{S}} < 28 \text{ V},$ $I_{\text{CP}} = -12 \text{ mA}$ | P_5.5.41 |

| Turn-on time, CPSTGA = 0                               | t <sub>ON_VCP1</sub> | 10     | 40   | 80   | μs   | $8 \text{ V} < V_{\text{S}} < 28 \text{ V}$<br>(25%) <sup>1)2)3)4)</sup>       | P_5.5.34 |

| Rise time, CPSTGA = 0                                  | $t_{RISE\_VCP1}$     | 10     | 60   | 100  | μs   | $8 \text{ V} < V_{\text{S}} < 28 \text{ V}$<br>(25%-75%) <sup>1)2)3)4)</sup>   | P_5.5.35 |

| Turn-on time, CPSTGA = 1                               | t <sub>ON_VCP2</sub> | 10     | 40   | 80   | μs   | $18 \text{ V} < V_{\text{S}} < 28 \text{ V}$ $(25\%)^{1/2/3/5/}$               | P_5.5.36 |

| Rise time, CPSTGA = 1                                  | $t_{RISE\_VCP2}$     | 10     | 60   | 100  | μs   | $18 \text{ V} < V_{\text{S}} < 28 \text{ V}$ $(25\%-75\%)^{1(2)3(5)}$          | P_5.5.37 |

| Charge Pump Undervoltage (referred to VS)              | V <sub>CPUV1</sub>   | 5.5    | 6    | 6.5  | V    | CPUVTH = 0,<br>VCP falling                                                     | P_5.5.38 |

| Charge Pump Undervoltage (referred to VS)              | V <sub>CPUV2</sub>   | 7      | 7.5  | 8    | V    | CPUVTH = 1,<br>VCP falling                                                     | P_5.5.42 |

| Automatic switch over dual to single stage charge pump | V <sub>CPSO DS</sub> | 16     | 17   | 18   | V    | CPSTGA = 1                                                                     | P_5.5.43 |

| Automatic switch over single to dual stage charge pump | V <sub>CPSO SD</sub> | 15.5   | 16.5 | 17.5 | V    | CPSTGA = 1                                                                     | P_5.5.44 |

| Charge pump switch over hysteresis                     | V <sub>CPSO HY</sub> | -      | 0.5  | -    | V    | <sup>3)</sup> <b>CPSTGA</b> = 1, $V_{\text{CPSO DS}} - V_{\text{CPSO SD}}$     | P_5.5.45 |

# **Multiple MOSFET Driver IC**

# **General description**

## Table 7 Electrical characteristics: charge pump

$V_S$  = 6.0 V to 18 V if VSOVTH = 0,  $V_S$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                            | Symbol             | Values |      |      | Unit | Note or                                                | Number   |

|--------------------------------------|--------------------|--------|------|------|------|--------------------------------------------------------|----------|

|                                      |                    | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                  |          |

| Charge Pump Undervoltage Filter Time | t <sub>CPUV</sub>  | 51     | 64   | 77   | μs   | 3)                                                     | P_5.5.39 |

| Charge pump minimum output current   | I <sub>CPOC1</sub> | _      | -    | -12  | mA   | $^{2)3)4)} V_S = 13.5 \text{ V};$<br><b>CPSTGA</b> = 0 |          |

| Charge pump minimum output current   | I <sub>CPOC2</sub> | _      | -    | -12  | mA   | $^{2)3)5)} V_S = 18 \text{ V};$ <b>CPSTGA</b> = 1      |          |

- 1) Parameter dependent on the capacitance  $C_{CP}$ .

- 2)  $C_{CPC1} = C_{CPC2} = 220 \text{ nF}, C_{CP} = 470 \text{ nF}, I_{CP} = 0 \text{ mA}.$

- 3) Not subject to production test, specified by design.

- 4) Dual stage charge pump.

- 5) Single stage charge pump.

# **Multiple MOSFET Driver IC**

Floating gate drivers

### Floating gate drivers 6

The TLE92108-231QX integrates sixteen floating gate drivers capable of controlling a wide range of n-channel MOSFETs. They are configured as eight high-sides and low-sides, building eight half-bridges.

The gate driver are current controlled, allowing a regulation of the MOSFET switching times.

For more information, please contact your sales partner for the datasheet including the complete device description.

# **Multiple MOSFET Driver IC**

**Protections and diagnostics**

### **Protections and diagnostics** 7

The TLE92108-231QX integrates comprehensive diagnostic and protection functions.

For more information, please contact your sales partner for the datasheet including the complete device description.

## **Serial Peripheral Interface - SPI**

#### **Serial Peripheral Interface - SPI** 8

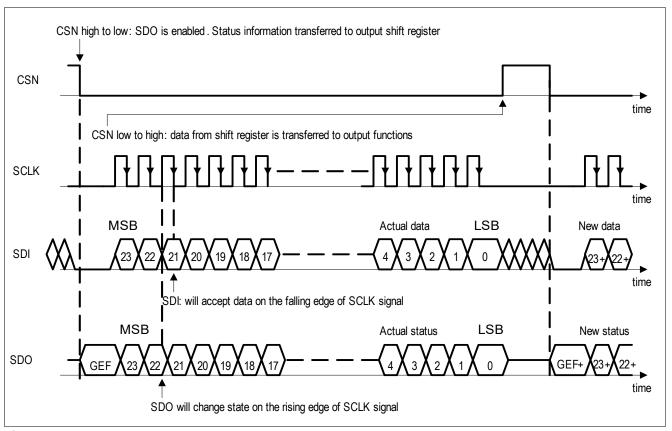

The 24-bit Serial Peripheral Interface (SPI) enables the communication between the microcontroller and the TLE92108-231QX. It allows to configure and control the device, and to read out the status registers for diagnostic purpose. The MOSFET driver IC acts as a SPI-slave while the microcontroller acts as a SPI-master.

The interface has a serial data input pin (SDI) to transfer data to the device, a serial data output pin (SDO) for reading data back from the device, and a serial clock pin (SCLK) for clocking data into and out of the device. A chip select pin (CSN) enables or disables the serial interface.

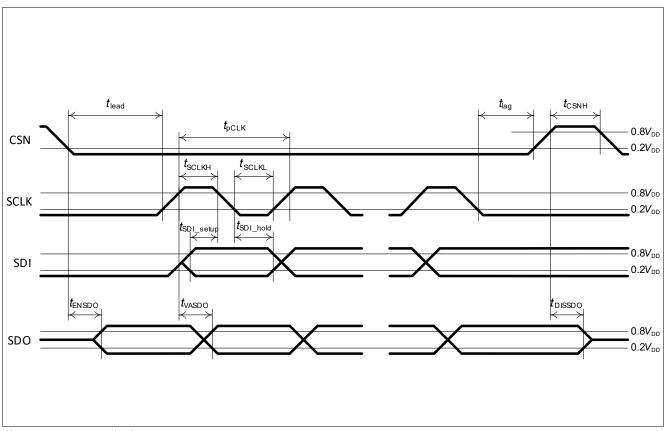

The SPI frame starts with the falling edge of CSN. During the falling edge of CSN, SCLK must be low (Clock Polarity CPOL = 0). Received data on SDI are shifted in on the falling edge of SCLK. Transmitted data by SDO are shifted out on the rising edge of SCLK (Clock Phase CPHA = 1). Refer to Figure 7.

The Most Significant Bit (MSB, bit 23) is shifted in/out first.

Write and clear commands are executed at the rising edge of CSN.

The SPI protocol supports both independent slave selection and daisy chain configurations.

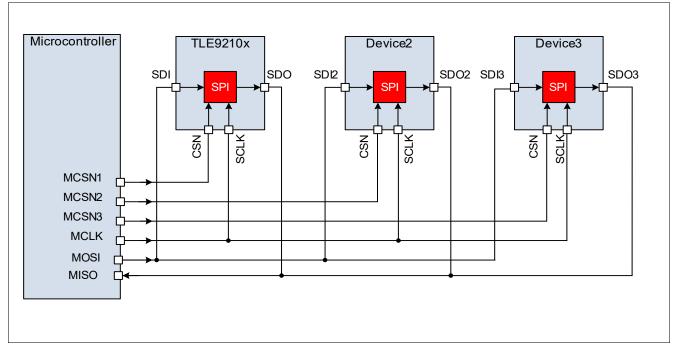

#### 8.1 SPI protocol with independent slave selection

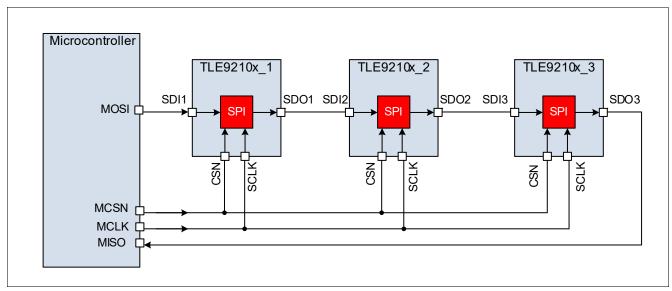

With individual slave selection, the microcontroller controls the CSN pin of each SPI slave individually (Figure 6).

Figure 6 Individual slave selection with three slave devices

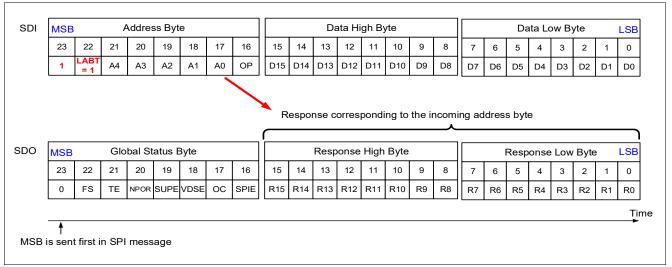

A SPI communication consists of 24-bit frame (Figure 7):

- SDI receives one address byte followed by two data bytes.

- SDO transmits the Global Error Flag and the Global Status Byte followed by two response bytes.

# infineon

## **Serial Peripheral Interface - SPI**

Figure 7 SPI Data Transfer

## The MSB of the address byte must be set to '1'.

The address byte specifies (see Figure 8):

- the target register (A[4:0])

- the type of operation:

- For control registers:

- Read only: OP bit<sup>1)</sup> = '0'

- Read and write: OP bit = '1'

- For status registers:

- Read only: OP bit = '0'

- Read and clear: OP bit = '1'

# With individual slave selection, the Last Address Byte Token (LABT) must be set to '1'.

## In-frame response

The SPI protocol incorporates an in-frame response: The content of the addressed register is shifted out by SDO within the same SPI frame. This feature reduces the SPI bus load during the read out of the control or status registers.

<sup>1)</sup> OP bit is the least significant bit of the address byte, see Figure 8

# **Multiple MOSFET Driver IC**

## **Serial Peripheral Interface - SPI**

In-frame response with individual slave selection Figure 8

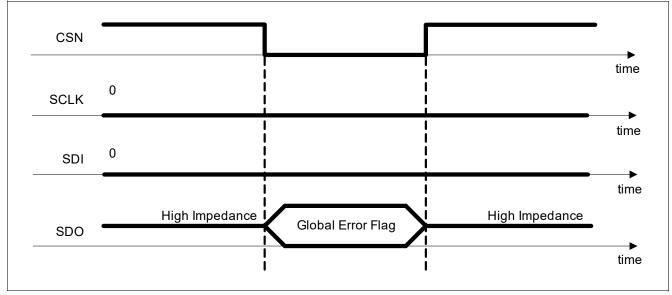

#### 8.2 **Global Error Flag (GEF)**

The Global Error Flag (GEF) is reported on SDO between the CSN falling edge and the first SCLK rising edge. GEF is set if a fault condition is detected or if the device comes from a Power On Reset (POR). It is therefore possible to have a quick device diagnostic without any SPI clock pulse (Figure 9).

Figure 9 GEF - Diagnostic with 0-clock cycle

#### 8.3 Global status byte

The SDO shifts out during the first eight SCLK cycles the Global Status Byte. This register provides an overview of the device status. The following error conditions are reported in this byte:

- Fail Safe (FS bit).

- Temperature error (TE bit): logical OR combination between Thermal Warning (TW) and Thermal shutdown (TSD).

- **Negated** Power ON Reset (NPOR bit, refer to **Chapter 5.3** for reset conditions).

# **Multiple MOSFET Driver IC**

## **Serial Peripheral Interface - SPI**

- Supply Error (SUPE bit): logical OR combination between VS undervoltage shutdown (VSUV), VS overvoltage shutdown (VSOV) and charge pump undervoltage (CPUV).

- VDS monitoring Error (VDSE bit): logical OR combination between the bits of the **DSOV** register.

- Overcurrent (OC bit): logical OR combination between OC1 and OC2 status bits (GENSTAT register).

- SPI protocol Error (SPIE bit).

Note:

The Global Error Flag is a logic OR combination of every bit of the Global Status Byte and of TDREGx: GEF = (FS) OR (TE) OR (NOT(NPOR)) OR (SUPE) OR (VDSE) OR (OC) OR (SPIE) OR (NOT(TDREGX) AND (PWMx\_EN =1) AND (NOT (MSKTDREG))),  $x = 1 \dots 3$ .

The following table shows how failures are reported in the Global Status Byte and the error Flag:

**Table 8** Failure reported in the global status byte and global error flag

| Type of Error                                     | Failure reported in the Global<br>Status Byte                             | Global Error Flag                                  |  |  |

|---------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------|--|--|

| Fail safe                                         | FS = 1                                                                    | 1                                                  |  |  |

| Thermal error                                     | TE = 1                                                                    | 1                                                  |  |  |

| Power ON reset                                    | NPOR = 0                                                                  | 1                                                  |  |  |

| Supply error                                      | SUPE = 1                                                                  | 1                                                  |  |  |

| Drain source voltage monitoring                   | VDSE = 1                                                                  | 1                                                  |  |  |

| Overcurrent                                       | OC = 1                                                                    | 1                                                  |  |  |

| SPI protocol error                                | SPIE = 1                                                                  | 1                                                  |  |  |

| TDREGx, $x = 1 \dots 3^{1}$ (see <b>GENSTAT</b> ) | -                                                                         | 1 if MSKTDREG = $0^{2}$<br>0 if MSKTDREG = $1^{2}$ |  |  |

| No error and no power ON reset                    | SPIE = 0<br>OC = 0<br>VDSE = 0<br>SUPE= 0<br>NPOR = 1<br>TE = 0<br>FS = 0 | 0                                                  |  |  |

|                                                   | TDREGx = 0,                                                               |                                                    |  |  |

<sup>1)</sup> See status register **GENSTAT**.

Note: The default value (after Power ON Reset) of NPOR is 0, therefore the default value of GEF is 1.

In fail safe mode, the control registers are frozen to their default value, with the exception of the WDTRIG bit (refer to Chapter 5.2.3). Any write access (except for WDTRIG bit) in fail safe mode will be discarded and the SPIE bit will set.

<sup>2)</sup> See control register **GENCTRL2**.

# **Multiple MOSFET Driver IC**

**Serial Peripheral Interface - SPI**

### 8.4 SPI error detection

The SPI incorporates an error flag in the Global Status Byte (SPIE) to supervise and preserve the data integrity. If an SPI protocol error is detected during a given frame, the SPIE bit is set in the next SPI communication.

The SPIE bit is set in the following error conditions:

- The number of SCLK clock pulses received when CSN is Low is (protocol error):

- not zero

- or less than 24

- or more than 24 but not a multiple of 8

- The microcontroller sends an SPI command to an unused address (protocol error).

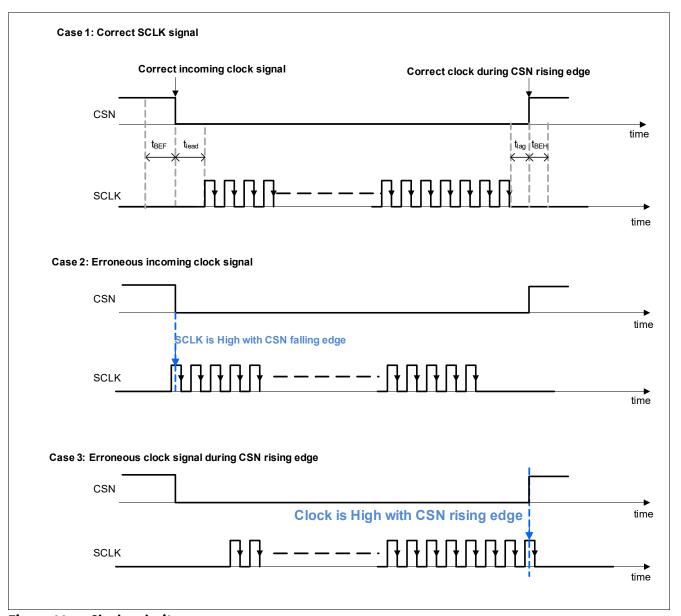

- A clock polarity error is detected (see **Figure 10** Case 2 and Case 3): the incoming clock signal was High during CSN rising or falling edges (protocol error).

- No address byte or no last address byte are detected (protocol error).

- In daisy chain: the microcontroller does not send in sequence the first address byte until the last address byte (i.e. with gaps between two address bytes). In this case, the SDO signal is set to '0' during the remaining part of the SPI frame<sup>1)</sup>, in order to prevent other devices from executing wrong commands (protocol error).

- A clear command to address 0x1F (Device ID register, Offset address = 0x1F).

- The same half-bridge is allocated to several activated PWM channels.

- Any write or clear command received in fail safe mode and not belonging to the exit sequence (refer to **Chapter 5.2.3**).

Note: SPI commands to activate a half-bridge mapped to several PWM channels are ignored.

In fail safe mode, the control registers may not be accessed, except for writing WDTRIG. An invalid write command in this mode sets the SPIE bit.

For a correct SPI communication:

- SCLK must be Low for a minimum t<sub>BEF</sub> before CSN falling edge and t<sub>lead</sub> after CSN falling edge.

- SCLK must be Low for a minimum t<sub>lag</sub> before CSN rising edge and t<sub>BEH</sub> after CSN rising edge.

# infineon

## **Serial Peripheral Interface - SPI**

Figure 10 Clock polarity error

The reset condition of the SPIE bit depends on the cause of error:

- In normal mode:

- The microcontroller must clear HBVOUT\_PWMERR if one half-bridge has been allocated to several PWM channels.

- The microcontroller must send a correct SPI frame for the other errors reported by SPIE.

- If SPIE has been set in fail safe mode, the device must enter normal mode first.

# 8.5 Daisy chain

In daisy chain configuration the master output / slave input (noted MOSI) is connected to a slave SDI. The first slave SDO is connected to the next slave SDI in the chain. The SDO of the final in the chain is connected to the master input / slave output (noted MISO). In daisy chain configuration, the microcontroller MCSN is connected to all the slave CSN inputs (Figure 11).

# **Multiple MOSFET Driver IC**

## **Serial Peripheral Interface - SPI**

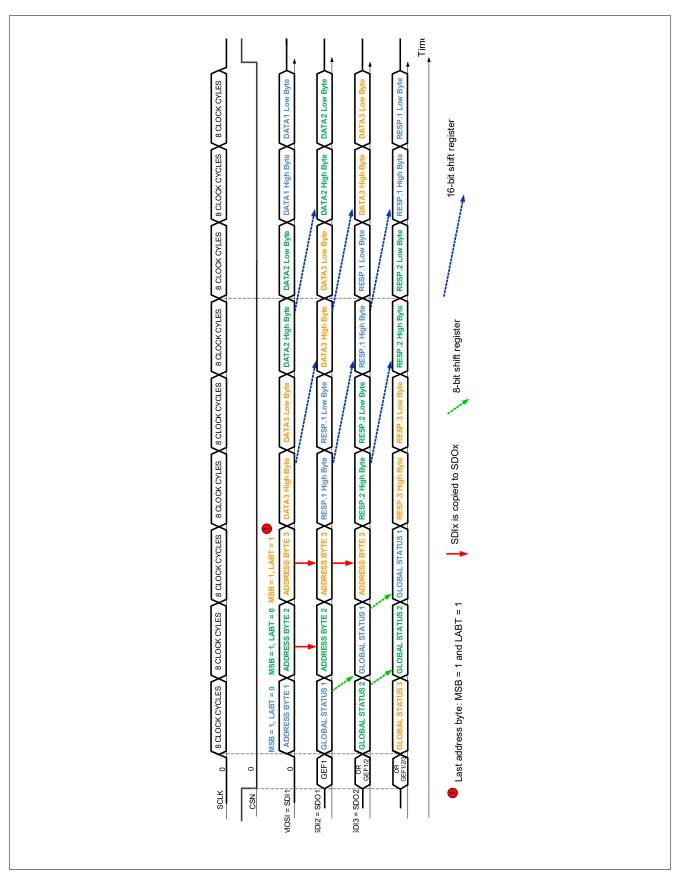

To support daisy chain configurations, the TLE92108-231QX accepts SPI frames with more than 24 bits, provided that the number of bits is a multiple of 8, and the structure of the address byte is respected.

In daisy chain, the TLE92108-231QX works as follows:

- 1. The TLE92108-231QX operates as a 8-bit shift register until it receives the first address byte. This first received address byte is considered by the device as its own address byte.

- 2. The TLE92108-231QX copies directly SDI to SDO until the last address byte is detected.

- 3. The TLE92108-231QX shifts out the response high byte and low byte corresponding to the address byte.

- 4. After the last address byte, the TLE92108-231QX operates as a 16-bit shift register until the end of the SPI frame.

Figure 11 Daisy chain configuration with three TLE9210x devices

In daisy chain configuration (**Figure 11**), the microcontroller must send the address and data bytes in the following order (**Figure 12**):

- 1. The address bytes altogether are sent first:

- Address byte 1 (for TLE9210x\_1) is sent first, followed by address byte 2 (for TLE9210x\_2), followed by address byte 3 (for TLE9210x\_3).

- The LABT bit of the last address byte must be '1', while the LABT bit of all the other address bytes must be '0'.

- 2. The data bytes are sent altogether **in reverse order** once the address bytes are transmitted:

- The data high byte for the TLE9210x\_3 is sent first followed by the data low byte for the TLE9210x\_3.

- Then the data high byte for the TLE9210x\_2 is sent followed by the data low byte for the TLE9210x\_2.

- Then the data high byte for the TLE9210x\_1 is sent followed by the data low byte for the TLE9210x\_1.

The Master Input / Slave Output (MISO), which is connected to SDO of the last device in the daisy chain, receives:

- 1. A logic OR combination of all Global Error Flags (GEF) at the beginning of the SPI frame, between CSN falling edge and the first SCLK rising edge.

- 2. The Global Status Byte of each TLE9210x in reverse order:

# **Multiple MOSFET Driver IC**

**Serial Peripheral Interface - SPI**

- The Global Status Byte 3 (GSB3) corresponding to the TLE9210x\_3 is received first, followed by GSB2 (corresponding to the TLE9210x\_2), and finally the GSB1 (corresponding to the TLE9210x\_1) is received.

- 3. The response of each TLE9210x in reverse order:

- The response high byte of the TLE9210x\_3 is received first followed by the response low byte of the TLE9210x\_3.

- Then the response high byte of the TLE9210x\_2 is received followed by the response low byte of the TLE9210x\_2.

- Then the response high byte of the TLE9210x\_1 is received followed by the response low byte of the TLE9210x\_1.

# infineon

# **Serial Peripheral Interface - SPI**

Figure 12 SPI Frame in daisy chain configuration with three TLE9210x devices

# **Multiple MOSFET Driver IC**

# **Serial Peripheral Interface - SPI**

### **SPI electrical characteristics: timings** 8.6

#### Table 9 **Electrical characteristics: SPI interface**

$V_{\rm S} = 6.0 \text{ V to } 18 \text{ V if VSOVTH} = 0, V_{\rm S} = 6.0 \text{ V to } 28 \text{ V if VSOVTH} = 1; V_{\rm DD} = 3.0 \text{ V to } 5.5 \text{ V}, T_{\rm i} = -40 ^{\circ}\text{C} \text{ to } 150 ^{\circ}\text{C}, \text{ all voltages}$ with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                    | Symbol                                        | Values                   |                        |                                    | Unit | Note or                                                           | Number   |

|----------------------------------------------|-----------------------------------------------|--------------------------|------------------------|------------------------------------|------|-------------------------------------------------------------------|----------|

|                                              |                                               | Min.                     | Тур.                   | Max.                               |      | <b>Test Condition</b>                                             |          |

| SPI frequency                                |                                               |                          | •                      | •                                  |      |                                                                   |          |

| Maximum SPI frequency                        | $f_{\rm SPI,max}$                             | _                        | _                      | 4                                  |      | 1)                                                                | P_8.6.1  |

| Delay from EN rising edge to                 |                                               | rame                     | <u>.</u>               | <u>.</u>                           | *    |                                                                   |          |

| SPI interface setup time <sup>2)</sup>       | t <sub>SET_SPI</sub>                          | _                        | _                      | 150                                | μs   | 1)                                                                | P_8.6.32 |

| SPI interface, logic inputs S                |                                               | SN                       |                        |                                    |      |                                                                   |          |

| High input voltage threshold                 | $V_{IH}$                                      | 0.7 x V <sub>DD</sub>    | -                      | -                                  | V    |                                                                   | P_8.6.2  |

| Low input voltage threshold                  | $V_{IL}$                                      | -                        | -                      | 0.3 x V <sub>DD</sub>              | V    |                                                                   | P_8.6.3  |

| Hysteresis of input voltage                  | $V_{IHY}$                                     | -                        | 0.12 x V <sub>DD</sub> | -                                  | V    | 1)                                                                | P_8.6.4  |

| Pull up resistor at pin CSN                  | R <sub>PU_CSN</sub>                           | 20                       | 40                     | 80                                 | kΩ   | $V_{\rm CSN} = 0.7 \times V_{\rm DD}$                             | P_8.6.5  |

| Pull down resistor at pin SDI,<br>SCLK       | R <sub>PD_SDI</sub> ,<br>R <sub>PD_SCLK</sub> | 20                       | 40                     | 80                                 | kΩ   | $V_{\text{SDI}}, V_{\text{SCLK}} = 0.2 \text{ x}$ $V_{\text{DD}}$ | P_8.6.6  |

| Input capacitance at pin<br>CSN, SDI or SCLK | Cı                                            | -                        | 10                     | -                                  | pF   | $^{1)}$ 0 V < $V_{DD}$ < 5.5 V                                    | P_8.6.7  |

| Input interface, logic outpu                 | ts SDO                                        |                          | 1                      | 1                                  |      |                                                                   | 1        |

| H-output voltage level                       | $V_{SDOH}$                                    | 0.8 x V <sub>DD</sub>    | -                      | -                                  | V    | I <sub>SDOH</sub> = -1.6 mA                                       | P_8.6.8  |

| L-output voltage level                       | V <sub>SDOL</sub>                             | -                        | -                      | 0.2 x V <sub>DD</sub>              | V    | I <sub>SDOL</sub> = 1.6 mA                                        | P_8.6.9  |

| Tri-state Leakage Current                    | I <sub>SDOLK</sub>                            | -10                      | -                      | 10                                 | μΑ   |                                                                   | P_8.6.10 |

| Tri-state input capacitance                  | C <sub>SDO</sub>                              | _                        | 10                     | 15                                 | pF   | 1)                                                                | P_8.6.11 |

| Data input timing. See Figu                  |                                               |                          |                        |                                    |      |                                                                   |          |