## **Transmission IO IC**

#### Features

- Four input interfaces for two-wire Hall Effect position sensors

- Short to supply protection

- Overtemperature protection

- Sensor state status available by SPI

- Four input interfaces for two-wire Hall Effect speed sensors

- Digital output for speed and direction sensing

- Further features set see position sensors above

- Two high-side gate drive channels

- Short circuit protection

- Programmable overcurrent threshold

- Output state status available by SPI

- A high-side gate drive channel for driving n-channel MOSFETs in anti-serial configuration

Reverse polarity protected power switch

- Reverse polarity protected powers

- Integrated charge pump

- 16 bit SPI interface

- Green Product (RoHS-compliant)

## **Potential applications**

- Automatic Transmission Control Modules

- Powertrain Control Modules

## **Product validation**

- Qualified for automotive applications

- Product validation according to AEC-Q100

## Description

The TLE9241QU is an integrated circuit (IC) intended for use in automatic transmission control modules. Two gate drive outputs are included for controlling a reverse polarity protected high-side switch typically used to switch off power to the control module while the module is in a sleep state. Two high-side gate drive channels are also included for controlling two "safety" switches. These switches are typically used to provide power to the transmission solenoids. The device also provides interfaces for eight two-wire Hall Effect sensors, four of which can be used with position sensors and four which can be used with either position or speed sensors.

| Туре      | Package    | Marking   |

|-----------|------------|-----------|

| TLE9241QU | PG-TQFP-48 | TLE9241QU |

## **Table of contents**

| Potential applications                                    |    |

|-----------------------------------------------------------|----|

| Product validation                                        | 1  |

| Description                                               | 1  |

| Table of contents                                         |    |

| 1 Block diagram                                           |    |

| 2 Pin configuration                                       |    |

| 2.1 Pin definitions and functions                         |    |

| 3 General product characteristics                         | 7  |

| 3.1 Absolute maximum ratings                              | 7  |

| 3.2 Functional range                                      |    |

| 3.3 Electrical characteristics                            | 9  |

| 4 Reverse polarity protected high-side switch gate driver | 10 |

| 4.1 Electrical characteristics                            |    |

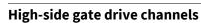

| 5 High-side gate drive channels                           | 11 |

| 5.1 Electrical characteristics                            |    |

| 6 Two wire Hall Effect sensor interfaces                  | 13 |

| 6.1 Electrical characteristics                            | 14 |

| 7 SPI interface                                           | 15 |

| 7.1 SPI frame                                             |    |

| 7.2 Timing diagram                                        | 15 |

| 7.2.1 Electrical characteristics SPI interface            |    |

| 8 Package outlines                                        | 17 |

| Revision history                                          |    |

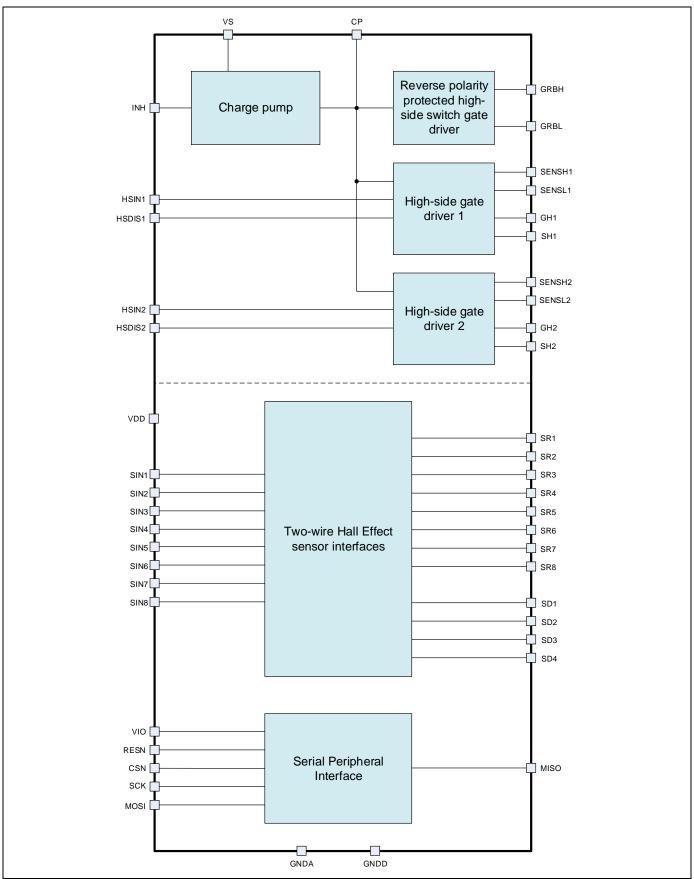

Block diagram

Figure 1 Block diagram

**Transmission IO IC**

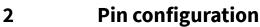

**Pin configuration**

Figure 2 Pin configuration

TLE9241QU Transmission IO IC Pin configuration

## 2.1 Pin definitions and functions

#### Table 1Pin definitions and functions

| <b>P</b> ' | D: N     |                                                                                |

|------------|----------|--------------------------------------------------------------------------------|

|            | Pin Name | Function                                                                       |

| 1          | HSDIS2   | High-side disable pin channel 2                                                |

| 2          | HSDIS1   | High-side disable pin channel 1                                                |

| 3          | HSIN2    | High-side control input channel 2                                              |

| 4          | HSIN1    | High-side control input channel 1                                              |

| 5          | SR8      | Hall effect speed sensor analogue output channel 8                             |

| 6          | SR7      | Hall effect speed sensor analogue output channel 7                             |

| 7          | SR6      | Hall effect speed sensor analogue output channel 6                             |

| 8          | SR5      | Hall effect speed sensor analogue output channel 5                             |

| 9          | SR4      | Hall effect speed sensor analogue output channel 4                             |

| 10         | SR3      | Hall effect speed sensor analogue output channel 3                             |

| 11         | SR2      | Hall effect speed sensor analogue output channel 2                             |

| 12         | SR1      | Hall effect speed sensor analogue output channel 1                             |

| 13         | SD4      | Hall effect speed sensor digital output channel 4                              |

| 14         | SD3      | Hall effect speed sensor digital output channel 3                              |

| 15         | SD2      | Hall effect speed sensor digital output channel 2                              |

| 16         | SD1      | Hall effect speed sensor digital output channel 1                              |

| 17         | RESN     | Reset input (low active)                                                       |

| 18         | MISO     | SPI master in slave out                                                        |

| 19         | MOSI     | SPI master out slave in                                                        |

| 20         | SCK      | SPI serial clock                                                               |

| 21         | CSN      | SPI chip select (low active)                                                   |

| 22         | VIO      | IO supply voltage. External connection to $V_{10}$                             |

| 23         | VDD      | 5 V supply Input. External connection to V_DD                                  |

| 24         | N.C.     | Not connected                                                                  |

| 25         | VS       | Supply input (reverse protected battery connection). External connection to Vs |

| 26         | СР       | Charge pump capacitor connection                                               |

| 27         | GRBH     | Power switch gate high                                                         |

| 28         | GRBL     | Power switch gate low                                                          |

| 29         | SENSH1   | Overcurrent sense resistor connection high channel 1                           |

| 30         | SENSL1   | Overcurrent sense resistor connection low channel 1                            |

| 31         | GH1      | Gate of external high-side FET channel 1                                       |

| 32         | SH1      | Source of external high-side FET channel 1                                     |

| 33         | SENSH2   | Overcurrent sense resistor connection high channel 2                           |

| 34         | SENSL2   | Overcurrent sense resistor connection low channel 2                            |

| 35         | GH2      | Gate of external high-side FET channel 2                                       |

| 36         | SH2      | Source of external high-side FET channel 2                                     |

| 37         | N.C.     | Not connected                                                                  |

| 38         | INH      | Inhibit input (LOW = inhibit, HIGH = device enabled)                           |

| 39         | GNDD     | Digital Ground                                                                 |

| 40         | GNDA     | Analogue Ground                                                                |

| 41         | SIN8     | Hall effect sensor input channel 8                                             |

| 42         | SIN7     | Hall effect sensor input channel 7                                             |

| 43         | SIN6     | Hall effect sensor input channel 6                                             |

| 44         | SIN5     | Hall effect sensor input channel 5                                             |

| 45         | SIN4     | Hall effect sensor input channel 4                                             |

|            |          |                                                                                |

## **Transmission IO IC**

### Pin configuration

| Pin | Pin Name | Function                           |

|-----|----------|------------------------------------|

| 46  | SIN3     | Hall effect sensor input channel 3 |

| 47  | SIN2     | Hall effect sensor input channel 2 |

| 48  | SIN1     | Hall effect sensor input channel 1 |

## **3 General product characteristics**

### 3.1 Absolute maximum ratings

#### Table 2Absolute maximum ratings1)

All voltages with respect to ground (GNDD), positive current flowing into pin (unless otherwise specified)

|                                                         |                                                              |      | Values | 5                     |      | Note or              |          |

|---------------------------------------------------------|--------------------------------------------------------------|------|--------|-----------------------|------|----------------------|----------|

| Parameter                                               | Symbol                                                       | Min. | Тур.   | Max.                  | Unit | Test<br>Condition    | Number   |

| Voltage                                                 |                                                              |      |        |                       |      |                      |          |

| VS supply voltage                                       | Vs                                                           | -0.3 |        | 40                    | V    |                      | P_3.1.1  |

| VDD, VIO supply voltage                                 | $V_{\rm DD}, V_{\rm IO}$                                     | -0.3 |        | 5.5                   | V    |                      | P_3.1.2  |

| Voltage range GRBH pin                                  | V <sub>grbh</sub>                                            | -14  |        | 55                    | V    |                      | P_3.1.3  |

| Voltage range GRBL, CP, GHx pin                         | $V_{\text{grbl}}, V_{\text{CP}}, V_{\text{GHX}}$             | -0.3 |        | 55                    | v    |                      | P_3.1.4  |

| Voltage range INH pin                                   | V <sub>INH</sub>                                             | -0.3 |        | 40                    | V    |                      | P_3.1.5  |

| Voltage range SENSHx, SENSLx, SHx                       | V <sub>SENSHX</sub> , V <sub>SENSLX</sub> , V <sub>SHX</sub> | -5.5 |        | 40                    | V    |                      | P_3.1.6  |

| Difference SENSHx-SENSLx                                | V <sub>SENS_DIFF</sub>                                       | -0.3 |        | 5.5                   | V    |                      | P_3.1.7  |

| Voltage range at HSINx, HSDISx, CSN,<br>SCK, MOSI, RESN | V <sub>dig_in</sub>                                          | -0.3 |        | V <sub>DD</sub> + 0.3 | V    |                      | P_3.1.8  |

| Voltage range MISO pin                                  | V <sub>MISO</sub>                                            | -0.3 |        | V <sub>IO</sub> + 0.3 | V    |                      | P_3.1.9  |

| Voltage range at SINx                                   | V <sub>SINX</sub>                                            | -0.3 |        | 40                    | V    |                      | P_3.1.10 |

| Voltage range at SRx                                    | V <sub>SRX</sub>                                             | -0.3 |        | 5.5                   | V    |                      | P_3.1.11 |

| Voltage range at SDx                                    | V <sub>SDX</sub>                                             | -0.3 |        | V <sub>DD</sub> + 0.3 | V    |                      | P_3.1.12 |

| Ground voltage offset GNDA vs. GNDD                     | V <sub>gnda</sub>                                            | -0.3 |        | 0.3                   | V    |                      | P_3.1.13 |

| Temperature                                             |                                                              |      |        |                       |      |                      |          |

| Junction temperature                                    | Tj                                                           | -40  |        | 150                   | °C   |                      | P_3.1.14 |

| ESD                                                     |                                                              |      |        |                       |      |                      |          |

| ESD susceptibility HBM, pins VS and SINx vs. GND        | Vesd, hbm, vs; Vesd, hbm, sinx                               | -4   |        | 4                     | kV   | HBM <sup>2)</sup>    | P_3.1.15 |

| ESD susceptibility HBM, all pins                        | <i>V</i> <sub>ESD,HBM</sub>                                  | -2   |        | 2                     | kV   | HBM <sup>2) 3)</sup> | P_3.1.16 |

| ESD susceptibility CDM, corner pins                     | V <sub>ESD,CDM,1;12;13;24;25;36;37;48</sub>                  | -750 |        | 750                   | V    | CDM <sup>4)</sup>    | P_3.1.17 |

| ESD susceptibility CDM, all pins                        | V <sub>ESD,CDM</sub>                                         | -500 |        | 500                   | V    | CDM <sup>4)</sup>    | P_3.1.18 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Human Body Model "HBM" AEC Q100-002

<sup>3)</sup> Pin SENSH1: +/- 1.5 kV

<sup>4)</sup> Charged Device Model "CDM" AEC Q100-011

Notes:

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

### Transmission IO IC

**General product characteristics**

## 3.2 Functional range

#### Table 3Functional range

| Parameter                | Symbol          |      | Values | 5    | llmit | Note or        | Number   |

|--------------------------|-----------------|------|--------|------|-------|----------------|----------|

| Palameter                | Symbol          | Min. | Тур.   | Max. | Unit  | Test Condition | Nulliber |

| VS supply voltage range  | Vs              | 5.5  |        | 40   | V     |                | P_3.2.1  |

| VDD supply voltage range | V <sub>DD</sub> | 4.75 | 5      | 5.25 | V     |                | P_3.2.2  |

| VIO supply voltage range | V <sub>IO</sub> | 3.1  |        | 5.25 | V     |                | P_3.2.3  |

Note: Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

### **3.3** Electrical characteristics

#### Table 4Electrical characteristics

$V_{\rm S}$  = 5.5 V to 40 V,  $V_{\rm DD}$  = 4.75 V to 5.25 V,  $V_{\rm IO}$  = 3.1 V to 5.25 V,  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to ground (GNDD), positive current flowing into pin (unless otherwise specified)

| <b>D</b>                                                        |                          |      | Value | S    |      | Note or                                                                             |           |

|-----------------------------------------------------------------|--------------------------|------|-------|------|------|-------------------------------------------------------------------------------------|-----------|

| Parameter                                                       | Symbol                   | Min. | Тур.  | Max. | Unit | <b>Test Condition</b>                                                               | Number    |

| Central functions                                               |                          |      | •     | •    | •    |                                                                                     |           |

| VDD supply current                                              | I <sub>DD</sub>          |      | 7.5   | 10.0 | mA   | 2)                                                                                  | P_3.2.4   |

| VIO supply current                                              | <i>I</i> <sub>10</sub>   |      |       | 0.5  | mA   |                                                                                     | P_3.2.5   |

| VS supply current                                               | Is                       |      | 4     | 6    | mA   | 2)                                                                                  | P_3.2.6   |

| VS quiescent current                                            | <i>I</i> <sub>S1</sub>   |      |       | 10   | μΑ   | INH = LOW,<br>$V_{\rm S} < 13 \text{ V},$<br>$T_{\rm j} < 50^{\circ} \text{C}^{-1}$ | P_3.2.7   |

| VS quiescent current                                            | I <sub>52</sub>          |      |       | 15   | μΑ   | INH = LOW,<br>V <sub>s</sub> < 13 V,<br>T <sub>j</sub> < 150°C                      | P_3.2.7a  |

| VDD undervoltage reset threshold                                | V <sub>DDUV</sub>        | 3.0  |       | 3.5  | V    |                                                                                     | P_3.2.8   |

| Charge pump undervoltage threshold<br>vs. VS                    | $V_{\rm CPUV\_rise}$     | 7.0  |       | 9.0  | v    | V <sub>CP</sub> rising                                                              | P_3.2.9   |

| Charge pump undervoltage threshold<br>vs. VS                    | $V_{\text{CPUV}_{fall}}$ | 5.5  |       | 6.8  | V    | $V_{\rm CP}$ falling                                                                | P_3.2.9a  |

| Charge pump undervoltage hysteresis                             | $V_{CPUV_hyst}$          | 1    |       | 3    | V    |                                                                                     | P_3.2.16  |

| Charge pump output current VCP = 9 V                            | I <sub>CP9_low</sub>     | 40   |       |      | μΑ   | $V_{\rm S}$ = 5.5 V <sup>1)</sup>                                                   | P_3.2.12  |

| Charge pump output current VCP = 10 V                           | I <sub>CP10_nom</sub>    | 40   |       |      | μΑ   | $V_{\rm S}$ = 12.0 V <sup>1)</sup>                                                  | P_3.2.12a |

| Charge pump output current VCP = 0 V                            | I <sub>CP0_low</sub>     | 300  |       |      | μΑ   | $V_{\rm S}$ = 5.5 V <sup>1)</sup>                                                   | P_3.2.12b |

| Charge pump output current VCP = 0 V                            | I <sub>CP0_nom</sub>     | 300  |       |      | μΑ   | $V_{\rm S}$ = 12.0 V <sup>1)</sup>                                                  | P_3.2.12c |

| Charge pump overvoltage clamp vs. VS                            | V <sub>CL_CP</sub>       |      | 11    | 15   | V    | $I_{CP} = 1 \text{ mA}$                                                             | P_3.2.10  |

| Charge pump frequency                                           | f <sub>CP</sub>          |      | 16.0  |      | MHz  | 1)                                                                                  | P_3.2.11  |

| Overtemperature shutdown threshold                              | T <sub>SD</sub>          | 160  | 175   | 190  | °C   |                                                                                     | P_3.2.13  |

| Main oscillator frequency                                       | fosc                     |      | 8.25  |      | MHz  |                                                                                     | P_3.2.14  |

| Digital input pins                                              |                          |      |       |      |      |                                                                                     |           |

| Low level input voltage HSINx, HSDISx,<br>RESN, CSN, MOSI, SCK  | VIL                      |      |       | 0.8  | V    |                                                                                     | P_3.2.17  |

| High level input voltage HSINx, HSDISx,<br>RESN, CSN, MOSI, SCK | V <sub>IH</sub>          | 2.0  |       |      | V    |                                                                                     | P_3.2.18  |

| Hysteresis voltage HSINx, HSDISx,<br>RESN, CSN, MOSI, SCK       | V <sub>HYS</sub>         | 75   | 150   |      | mV   | 1)                                                                                  | P_3.2.19  |

| HSIN1, HSIN2, RESN, MOSI, SCK pull<br>down current              | I <sub>PD</sub>          | 30   | 50    | 70   | μA   |                                                                                     | P_3.2.20  |

| HSDIS1, HSDIS2, CSN pull up current                             | I <sub>PU</sub>          | -70  | -50   | -30  | μA   |                                                                                     | P_3.2.21  |

$^{\rm 1)}$  Not subject to production test, specified by design.

$^{2)}$  During discharge of an inductive load, i.e. SH1/2 < 0 V:  $\mathit{I}_{\text{DD}}$  < 15 mA;  $\mathit{I}_{\text{S}}$  < 20 mA.

#### Reverse polarity protected high-side switch gate driver

## 4 Reverse polarity protected high-side switch gate driver

The device includes two gate drive outputs for controlling external MOSFETs for reverse battery protection and system power supply.

The device includes a charge pump for driving the gates of the external MOSFETs.

The state of the reverse protected power switch gate drive outputs are controlled by the input pin INH.

If the power switch is in the "off" state, the gate drive outputs GRBL is driven to ground potential. The gate drive output GRBH will remain near the battery voltage.

### 4.1 Electrical characteristics

#### Table 5Electrical characteristics

$V_{\rm S}$  = 5.5 V to 40 V,  $V_{\rm DD}$  = 4.75 V to 5.25 V,  $V_{\rm IO}$  = 3.1 V to 5.25 V,  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to ground (GNDD), positive current flowing into pin (unless otherwise specified)

| Devementer                            | Symphol                  |      | Value | S    | Unit | Note or                                                                                       | Number   |

|---------------------------------------|--------------------------|------|-------|------|------|-----------------------------------------------------------------------------------------------|----------|

| Parameter                             | Symbol                   | Min. | Тур.  | Max. | Unit | <b>Test Condition</b>                                                                         | Number   |

| Reverse protected switch              |                          |      |       |      |      |                                                                                               |          |

| Low level input voltage INH           | $V_{\rm IL\_INH}$        |      |       | 1.0  | V    |                                                                                               | P_4.1.1  |

| High level input voltage INH          | V <sub>IH_INH</sub>      | 3.0  |       |      | V    |                                                                                               | P_4.1.2  |

| Input hysteresis INH                  | V <sub>HYS_INH</sub>     | 75   | 150   |      | mV   |                                                                                               | P_4.1.3  |

| INH pull down resistor to GND         | $R_{\rm PD\_INH}$        | 0.5  | 1.25  | 2.0  | MΩ   | <i>V</i> <sub>INH</sub> = 1.0 V                                                               | P_4.1.4  |

| Power switch activation time          | T <sub>on_ps</sub>       |      |       | 15   | ms   | time until ext.<br>MOSFET is<br>switched on<br>after INH signal<br>assertion <sup>1) 2)</sup> | P_4.1.5  |

| Power switch de-activation time       | $T_{\rm OFF_PS}$         |      |       | 15   | ms   | time until ext.<br>MOSFET is<br>switched off<br>after INH signal<br>de-assertion              | P_4.1.6  |

| High level output voltage GRBH vs. VS | $V_{\rm OH\_GRBH1}$      | 6.75 |       | 15   | V    | V <sub>S</sub> = 5.5 V,<br>I <sub>GRBH</sub> < 40 μA                                          | P_4.1.7  |

| High level output voltage GRBH vs. VS | $V_{\rm OH_{GRBH2}}$     | 8    |       | 15   | V    | V <sub>S</sub> > 12 V,<br>I <sub>GRBH</sub> < 40 μA                                           | P_4.1.8  |

| Low level output voltage GRBH vs. VS  | $V_{\rm OL_GRBH}$        | -2   |       | 1    | V    |                                                                                               | P_4.1.9  |

| Low level output voltage GRBL         | $V_{\rm OL_GRBL}$        | -2   |       | 1    | V    |                                                                                               | P_4.1.10 |

| DC output current GRBx                | <i>I</i> <sub>GRBX</sub> |      | 25    |      | μA   |                                                                                               | P_4.1.11 |

| Overvoltage clamp GRBH to VS          | $V_{CL_{GRBH}}$          | -21  | -19   | -17  | V    |                                                                                               | P_4.1.12 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> For more details on activation time please see the User Manual.

## 5 High-side gate drive channels

The device includes two high-side pre-driver channels for driving external normal level n-channel MOSFETs.

The device includes a charge pump for driving the gates of the two external MOSFETs. The state of the gate drive outputs are controlled by a pair of input pins for each channel.

The states of the input pins HSIN1, HSIN2, HSDIS1 and HSDIS2 can be verified by reading the appropriate register.

The status of the high-side driver output is monitored by the device and is accessible in a register.

An external shunt resistor is required in the high-side driver circuit for overcurrent detection. The voltage drop across this resistor is monitored by the device, and the driver is turned off if the overcurrent threshold voltage is exceeded. The overcurrent detection function includes a fixed delay timer.

The value of the overcurrent threshold can be configured by writing to the overcurrent threshold register.

If an overcurrent fault is detected, the channel is turned off and a high-side overcurrent fault flag is set.

The HSINx signals can be controlled by SPI instead of the HSINx pin if configured accordingly.

## 5.1 Electrical characteristics

#### Table 6Electrical characteristics

$V_{\rm S}$  = 5.5 V to 40 V,  $V_{\rm DD}$  = 4.75 V to 5.25 V,  $V_{\rm IO}$  = 3.1 V to 5.25 V,  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to ground (GNDD), positive current flowing into pin (unless otherwise specified)

| <b>-</b>                               |                      |      | Values    | 5    |      | Note or                                                                                                                               |          |

|----------------------------------------|----------------------|------|-----------|------|------|---------------------------------------------------------------------------------------------------------------------------------------|----------|

| Parameter                              | Symbol               | Min. | Тур.      | Max. | Unit | Test Condition                                                                                                                        | Number   |

| High-side driver                       |                      |      |           |      |      |                                                                                                                                       |          |

| High-side blanking time                | $T_{\rm BL_HS}$      | 4    | 8         | 12   | μs   |                                                                                                                                       | P_5.1.6  |

| SHx output state threshold             | V <sub>TH_SHX</sub>  |      | $V_{s}/2$ |      | V    |                                                                                                                                       | P_5.1.7  |

| SHx pull down current                  | I <sub>PD_SHX</sub>  |      | 200       | 300  | μA   |                                                                                                                                       | P_5.1.8  |

| Short to battery filter time           | $T_{\rm FL_STB}$     |      | 64        |      | μs   |                                                                                                                                       | P_5.1.9  |

| High level output GHx vs. SHx          | V <sub>OH_HS1</sub>  | 6.75 |           | 15   | V    | V <sub>s</sub> = 5.5 V,<br>I <sub>GHX</sub> < 25 μA                                                                                   | P_5.1.10 |

| High level output GHx vs. SHx          | V <sub>OH_Hs2</sub>  | 8    |           | 15   | V    | V <sub>S</sub> > 12 V,<br>I <sub>GHX</sub> < 25 μA                                                                                    | P_5.1.11 |

| Low level output GHx vs. SHx           | $V_{\rm OL_{HS}}$    | -2   |           | 1    | V    |                                                                                                                                       | P_5.1.12 |

| Turn on delay time                     | T <sub>ON_HS</sub>   |      |           | 100  | μs   | From command to 80%,<br>$Q_{GHX} = 20 \text{ nC}^{-1}$                                                                                | P_5.1.13 |

| Turn off delay time                    | T <sub>OFF_HS</sub>  |      |           | 100  | μs   | From command to 20%, $Q_{GHX} = 20 \text{ nC}^{1}$                                                                                    | P_5.1.14 |

| Gate driver output current             | I <sub>GHX</sub>     | 2    | 4         | 6    | mA   | $V_{\rm S} = 5 \text{ V},$<br>$V_{\rm CP} - V_{\rm S} = 10 \text{ V},$<br>$V_{\rm SHX} = 0 \text{ V},$<br>$V_{\rm GHX} = 5 \text{ V}$ | P_5.1.15 |

| GHx negative clamp voltage             | $V_{\rm CL_GHX}$     | -1   |           |      | V    |                                                                                                                                       | P_5.1.16 |

| SHx bias current                       | I <sub>OFF_SHX</sub> |      |           | 50   | μA   | Channel off                                                                                                                           | P_5.1.17 |

| Overcurrent filter time                | $T_{\rm FLT_OC}$     |      | 4         |      | μs   |                                                                                                                                       | P_5.1.18 |

| Overcurrent threshold 000b             | I <sub>OC0</sub>     | 15   | 25        | 35   | mV   |                                                                                                                                       | P_5.1.19 |

| Overcurrent threshold 001 <sub>b</sub> | I <sub>OC1</sub>     | 40   | 50        | 60   | mV   |                                                                                                                                       | P_5.1.20 |

| Overcurrent threshold 010 <sub>b</sub> | I <sub>OC2</sub>     | 65   | 75        | 85   | mV   |                                                                                                                                       | P_5.1.21 |

| Overcurrent threshold $011_{ m b}$     | I <sub>OC3</sub>     | 90   | 100       | 110  | mV   |                                                                                                                                       | P_5.1.22 |

| Overcurrent threshold 100 <sub>b</sub> | I <sub>OC4</sub>     | 115  | 125       | 135  | mV   |                                                                                                                                       | P_5.1.23 |

| Overcurrent threshold 101 <sub>b</sub> | I <sub>OC5</sub>     | 140  | 150       | 160  | mV   |                                                                                                                                       | P_5.1.24 |

| Overcurrent threshold 110 <sub>b</sub> | I <sub>OC6</sub>     | 165  | 175       | 185  | mV   |                                                                                                                                       | P_5.1.25 |

| Overcurrent threshold 111 <sub>b</sub> | I <sub>OC7</sub>     | 190  | 200       | 210  | mV   |                                                                                                                                       | P_5.1.26 |

<sup>1)</sup> Not subject to production test, specified by design.

Two wire Hall Effect sensor interfaces

## 6 Two wire Hall Effect sensor interfaces

The device includes eight interface channels for two-wire Hall Effect sensors. Four of the channels include a digital output.

The channels detect the supply current of the two-wire sensor. Each channel provides a path from the ground pin of the sensor to ground.

The analogue output of each channel at the pin SRx is a current sink proportional to the detected sensor current.

An internal register contains the detected state of each sensor channel.

The device includes four digital outputs, SD1-4. The state of the output pin is the same as the value of the respective bit in the sensor state register.

Each channel is short-circuit protected by a current limitation function. In a short circuit condition, the current flowing into the SINx input pin is actively limited. There is no overcurrent shutdown function for the sensor interface channels.

Each sensor interface channel includes overtemperature shutdown.

If the overtemperature fault is active and simultaneously overcurrent is detected, the affected channel is disabled. Also, the SRx pin is driven to a voltage near to ground potential, and the SDx pin is driven HIGH.

Each channel can be individually disabled.

**Transmission IO IC**

Two wire Hall Effect sensor interfaces

## 6.1 Electrical characteristics

#### Table 7 Electrical characteristics

$V_{\rm S}$  = 5.5 V to 40 V,  $V_{\rm DD}$  = 4.75 V to 5.25 V,  $V_{\rm IO}$  = 3.1 V to 5.25 V,  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to ground (GNDD), positive current flowing into pin (unless otherwise specified)

| De versus et e v                                         | Cumb al                  |                     | Values | 5    | Unit | Note or                                                      | Number   |

|----------------------------------------------------------|--------------------------|---------------------|--------|------|------|--------------------------------------------------------------|----------|

| Parameter                                                | Symbol                   | Min.                | Тур.   | Max. | Unit | <b>Test Condition</b>                                        | Number   |

| Hall sensor interface                                    |                          |                     |        |      |      |                                                              |          |

| Ratio of sensor input current vs.                        | k <sub>ilis</sub>        | 19                  | 20     | 21   |      | For 4 mA < I <sub>SINX</sub> <                               | P_6.1.1  |

| SRx pin current                                          |                          |                     |        |      |      | 20 mA                                                        | _        |

| Voltage drop SINx vs. GND                                | V <sub>DO_SINX</sub>     |                     |        | 0.4  | V    | $I_{SINX} = 20 \text{ mA}$                                   | P_6.1.2  |

| Voltage drop SINx vs. GND (open circuit)                 | $V_{\rm DO_OC_SINX}$     |                     |        | 0.2  | V    | $I_{\text{SINX}} = 0 \text{ mA}^{1)}$                        | P_6.1.19 |

| Short to supply threshold current                        | I <sub>CL_SINX</sub>     | 20                  | 30     | 40   | mA   |                                                              | P_6.1.3  |

| SINx current with interface<br>disabled                  | I <sub>DIS_SINX</sub>    |                     |        | 50   | μA   |                                                              | P_6.1.4  |

| SRx current with interface disabled                      | I <sub>DIS_SRX</sub>     |                     |        | 2.5  | μA   |                                                              | P_6.1.5  |

| SDx high threshold                                       | <i>I</i> <sub>тн_н</sub> | 11.5                |        |      | mA   | $R_{SRX} = 3.5 \text{ k}\Omega,$<br>$V_{DD} = 5.0 \text{ V}$ | P_6.1.6  |

| SDx low threshold                                        | I <sub>TH_L</sub>        |                     |        | 8.5  | mA   | $R_{SRX} = 3.5 \text{ k}\Omega,$<br>$V_{DD} = 5.0 \text{ V}$ | P_6.1.7  |

| SDx hysteresis                                           | I <sub>TH_HYS</sub>      | 0.7                 | 0.8    | 0.9  | mA   | $R_{SRX} = 3.5 \text{ k}\Omega,$<br>$V_{DD} = 5.0 \text{ V}$ | P_6.1.8  |

| SDx filter time constant                                 | T <sub>FLT_SDX</sub>     | 1                   |        | 8    | μs   |                                                              | P_6.1.9  |

| SRx pin saturation voltage                               | V <sub>SAT_SRX</sub>     | 0.6                 | 1      | 1.5  | V    |                                                              | P_6.1.10 |

| SRx pin overtemperature<br>shutdown voltage              | V <sub>OTSD_SRX</sub>    |                     |        | 0.5  | v    | I <sub>SRX</sub> = 1.5 mA                                    | P_6.1.11 |

| SRx chopper ripple frequency                             | FOSC_CHOP                |                     | 1      |      | MHz  |                                                              | P_6.1.12 |

| SRx settling time after activation of sensor channel     | T <sub>ACT_SRX</sub>     |                     |        | 75   | μs   | 1)                                                           | P_6.1.13 |

| SRx settling time from sensor high to sensor low current | T <sub>FALL_SRX</sub>    |                     |        | 25   | μs   | 1)                                                           | P_6.1.14 |

| Speed sensor operational<br>frequency                    | F <sub>MAX_SINX</sub>    |                     |        | 15   | kHz  | 1)                                                           | P_6.1.15 |

| Speed sensor pulse-width<br>distortion                   | F <sub>PWDIS</sub>       | -10                 |        | 10   | μs   |                                                              | P_6.1.16 |

| SDx output low voltage                                   | V <sub>OL_SDX</sub>      |                     |        | 0.4  | V    | $I_{SDX} = 1 \text{ mA}$                                     | P_6.1.17 |

| SDx output high voltage                                  | V <sub>он_sdx</sub>      | V <sub>DD</sub> - 1 |        |      | V    | <i>I</i> <sub>SDX</sub> = -1 mA                              | P_6.1.18 |

<sup>1)</sup> Not subject to production test, specified by design.

SPI interface

## 7 SPI interface

### 7.1 SPI frame

#### **MOSI SPI frame**

| 15   | 14     | 13 | 12 | 11 | 10      | 9       | 8       | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|------|--------|----|----|----|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| RN/W | PARITY | 0  | 0  | 0  | ADDR[2] | ADDR[1] | ADDR[0] | DATA[7] | DATA[6] | DATA[5] | DATA[4] | DATA[3] | DATA[2] | DATA[1] | DATA[0] |

#### **MISO SPI frame**

Note:

| 15   | 14     | 13             | 12              | 11 | 10      | 9       | 8       | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|------|--------|----------------|-----------------|----|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| RN/W | PARITY | FAULT<br>comm. | FAULT<br>global | 0  | ADDR[2] | ADDR[1] | ADDR[0] | DATA[7] | DATA[6] | DATA[5] | DATA[4] | DATA[3] | DATA[2] | DATA[1] | DATA[0] |

The parity bit (odd) is calculated over the entire frame (bit 15 + bits 13 - 0)

## 7.2 Timing diagram

Figure 3 SPI signal timing diagram

**SPI interface**

## 7.2.1 Electrical characteristics SPI interface

#### Table 8Electrical characteristics

$V_{\rm S}$  = 5.5 V to 40 V,  $V_{\rm DD}$  = 4.75 V to 5.25 V,  $V_{\rm IO}$  = 3.1 V to 5.25 V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground (GNDD), positive current flowing into pin (unless otherwise specified)

| Parameter                                          | Symbol                | Values |      |      |      | Note or                                  |          |

|----------------------------------------------------|-----------------------|--------|------|------|------|------------------------------------------|----------|

|                                                    |                       | Min.   | Тур. | Max. | Unit | <b>Test Condition</b>                    | Number   |

| Serial clock frequency                             | f <sub>sck</sub>      |        |      | 6    | MHz  | 1) 2)                                    | P_7.2.1  |

| Serial clock high time                             | t <sub>scк_н</sub>    | 65     |      |      | ns   | 1)                                       | P_7.2.2  |

| Serial clock low time                              | t <sub>sck_L</sub>    | 65     |      |      | ns   | 1)                                       | P_7.2.3  |

| Enable lead time (falling CSN to rising SCK)       | $t_{\rm CSN\_LEAD}$   | 150    |      |      | ns   | 1)                                       | P_7.2.4  |

| Enable lag time (falling SCK to rising CSN)        | $t_{\rm CSN\_LAG}$    | 150    |      |      | ns   | 1)                                       | P_7.2.5  |

| Transfer delay time (rising CSN to falling CSN)    | t <sub>csn_td</sub>   | 1      |      |      | μs   | 1)                                       | P_7.2.6  |

| Data setup time (required time SI to falling SCK)  | t <sub>MISO_SU</sub>  | 20     |      |      | ns   | 1)                                       | P_7.2.7  |

| Data hold time (required time falling SCK to MOSI) | t <sub>MOSI_H</sub>   | 20     |      |      | ns   | 1)                                       | P_7.2.8  |

| Output enable time (falling CSN to MISO valid)     | t <sub>miso_en</sub>  |        |      | 200  | ns   | $C_{\rm MISO} = 200 \ \rm pF^{-1}$       | P_7.2.9  |

| Output disable time (rising CSN to MISO tri-state) | t <sub>miso_dis</sub> |        |      | 200  | ns   | $C_{\rm MISO} = 200 \ \rm pF^{-1}$       | P_7.2.10 |

| Output data valid time with capacitive load        | t <sub>MISO_V</sub>   |        |      | 100  | ns   | $C_{\rm MISO} = 200 \ \rm pF^{-1}$       | P_7.2.11 |

| MISO rise time                                     | t <sub>MISO_R</sub>   |        |      | 50   | ns   | C <sub>MISO</sub> = 200 pF <sup>1)</sup> | P_7.2.12 |

| MISO fall time                                     | t <sub>MISO_F</sub>   |        |      | 50   | ns   | $C_{\rm MISO} = 200 \ \rm pF^{-1}$       | P_7.2.13 |

| Input pin capacitance: CSN, SCK,<br>MOSI           | C <sub>IN</sub>       |        |      | 20   | pF   | 1)                                       | P_7.2.14 |

| MISO pin capacitance                               | C <sub>MISO_HIZ</sub> |        |      | 25   | рF   | Tri-state <sup>1)</sup>                  | P_7.2.15 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Output load capacitance on MISO pin is  $\leq$  25 pF.

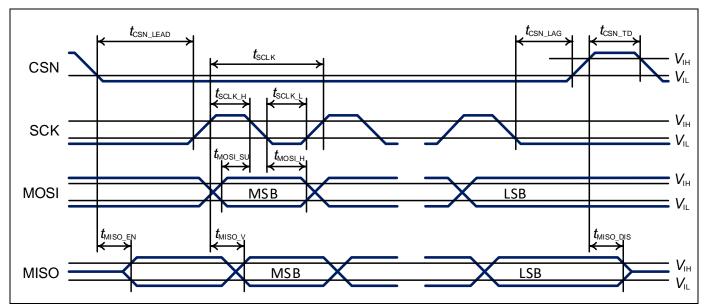

## TLE9241QU Transmission IO IC Package outlines

## 8 Package outlines

Figure 4 Package outline PG-TQFP-48-9

## Green Product (RoHS-compliant)

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-compliant (i.e. Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

For further information on alternative packages, please visit our website: <u>http://www.infineon.com/packages</u>

## **Revision history**

| Document<br>version | Date of release | Description of changes |

|---------------------|-----------------|------------------------|

| 1.0                 | 2019-02-20      | Datasheet created      |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Published by Infineon Technologies AG 81726 München, Germany

Edition 2019-02-20

© 2019 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

Document reference Z8F60158692

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Current & Power Monitors & Regulators category:

Click to view products by Infineon manufacturer:

Other Similar products are found below :

NCP347MTAHTBG NCS37000MNG NCP4353BSNT1G MAX4845DEYT+T ZXCT1080QE5TA NCP4353ASNT1G INA234AIYBJR ZXCT1008QFTA UC3838ADW NCP361SNT1G ZXCT1023DFGTA ADM1294-1AARUZ-RL7 LT3092ETS8#TRPBF LTC4151IMS-1#PBF LM334S8#PBF INA203AIDR ADM1294-1AACPZ ADM1294-1BACPZ ADL5317ACPZ-REEL7 ADM1041ARQZ ADM1192-1ARMZ-R7 ADM1293-1BARUZ ADM1294-1AARUZ LT3092EST#TRPBF LTC1921CMS8#PBF LTC1921IS8#PBF LTC1392CS8#PBF LTC1921CS8#PBF LTC2921CGN#PBF LTC2947IUHF-65#PBF ZXCT1009FTA DM7332G-00364-B1 CS5460A-BSZ LT2940IDD#PBF ZXCT1110W5-7 ZXCT1083E5TA ZXCT1021E5TA ZXCT1022E5TA ZXCT1041E5TA ZXCT1051E5TA ZXCT1080E5TA ZXCT1107SA-7 INA285AQDGKRQ1 INA286AQDGKRQ1 IR3725MTRPBF ISL28023FR12Z-T7A ISL28025FI12Z-T7A IXCY10M45S LTC2970IUFD#PBF LTC2991IMS#TRPBF