# TLE9879 EvalKit V1.2 Users' Manual

# **Contents**

| Abbreviations                            | 3  |

|------------------------------------------|----|

| 1 Concept                                | 4  |

| 2 Interconnects                          | 5  |

| 3 Test Points                            | 6  |

| 4 Jumper Settings                        | 7  |

| 5 Communication Interfaces               | 8  |

| 5.1 LIN (via Banana jack and uIO BSL)    | 8  |

| 5.2 UART (via USB)                       | 8  |

| 5.3 Debugging (via USB or SWD-Interface) | 9  |

| 6 Technical Data                         | 9  |

| 7 Optional Additional Placements         | 10 |

| 8 Schematics and Layout                  | 11 |

| 8.1 Schematic                            | 11 |

| 8.1 Layout                               | 15 |

| 9 Frrata                                 | 17 |

| 9.1 Short of internal layer 2 and Jumper (JP4) | 17 |

|------------------------------------------------|----|

| Related limitations:                           | 17 |

| Workaround:                                    | 17 |

| 9.2 Jumper (JP6) not connected to VDDP.        | 17 |

| Related limitations:                           | 17 |

| Workaround:                                    | 17 |

| 9.3 Workaround Proposal                        | 18 |

# **Abbreviations**

|         | 1                                           |

|---------|---------------------------------------------|

| BLDC    | Brushless Direct Current                    |

| BSL     | Bootstrap Loader                            |

| GH1,2,3 | Gate High side MOSFET for Phases 1, 2, 3    |

| GL1,2,3 | Gate Low side MOSFET for Phase 1, 2, 3      |

| GPIO    | General Port Input / Output                 |

| ISP     | In-system Programmer                        |

| LIN     | Local Interconnect Network                  |

| MON     | Monitor                                     |

| n.c.    | not connected                               |

| n/u     | not used                                    |

| OP1     | Negative operational Amplifier Input        |

| OP2     | Positive operational Amplifier Input        |

| RST     | Reset                                       |

| SL      | Source Low side MOSFET                      |

| SWD     | ARM Serial Wire Debug                       |

| TMS     | Test Mode Select                            |

| UART    | Universal Asynchronous Receiver Transmitter |

| VAREF   | Reference Voltage                           |

| VBAT    | Battery Voltage Supply                      |

| VCOM    | Virtual COM-Port                            |

| VCP     | Voltage Charge Pump                         |

| VDDC    | Core Supply                                 |

| VDDEXT  | External Voltage Supply Output              |

| VDDP    | I/O Port Supply                             |

| VDH     | Voltage Drain High side MOSFET              |

| VS      | Battery Supply Input                        |

| VSD     | Battery Supply Input for MOSFET Driver      |

|         |                                             |

Table 1: Abbreviations

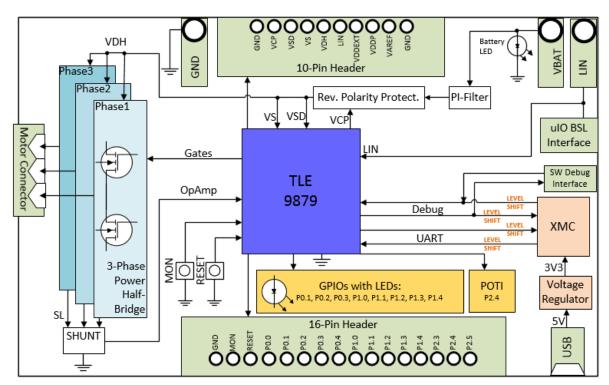

# 1 Concept

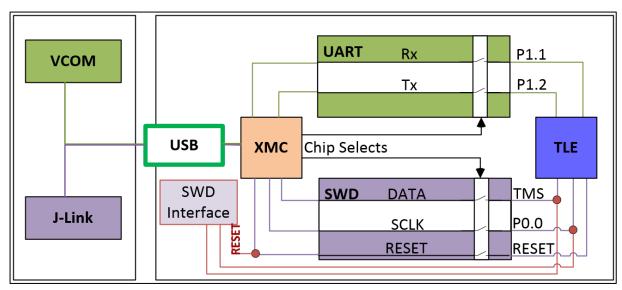

Figure 1: Board Concept

This board is intended to provide a simple, easy-to-use tool for getting familiar with Infineon's embedded power IC TLE9879. It contains the TLE9879 and its typical application circuit including three MOSFET half bridges to instantly drive a BLDC motor. The board is ready to connect with car supply or similar and has an implemented Segger for debugging on board.

All relevant chip pins are connected to pin headers at the edge of the board, where signals can be probed or applied directly (see Table 2, Table 3). By different jumper settings LEDs can be put in parallel to several ports and selected functions can be configured (see Table 6). Push button switches allow easy hardware reset and triggering of the MON input. There are intended test points for all six gate driver pins, for measurements at the shunt, VDDC and several ground points on the evaluation board (see Figure 3). For testing analog signals ADC inputs can be varied by the potentiometer on board. Three phases of motor current can be picked off at a terminal block to connect a DC brushless motor.

The evaluation board can be operated by standard laboratory equipment as power supply and LIN communication are working via banana jacks. Debugging and UART are provided via an USB interface combined with onboard Segger J-Link (XMC4200). Bidirectional level shifters ensure that the respective XMC pins are in tristate as long as UART or debugging is not used.

In case the user wants to use another ISP than the onboard Segger the SWD interface can be used. To program the TLE9879 via LIN there is an additional uIO BSL interface (see Table 4).

There is a battery LED that indicates that the board is connected to supply the right way. Otherwise reverse polarity protection secures the board from damage by cross connection.

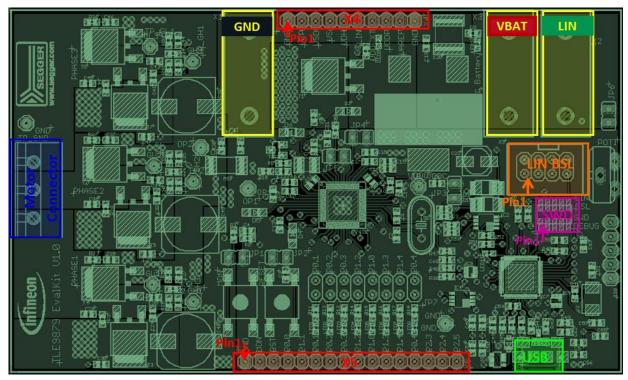

# 2 Interconnects

Figure 2: Interconnects

### Banana jacks (marked yellow)

There are jacks in different colors for ground, supply (max.28V) and LIN communication via banana jack: GND (black), VBAT (red), LIN (green)

# Pin Ports X4 and X5 (marked red)

Soldering pin headers with 2,54mm pitch for X4 (1x10) and X5(1x16) yields test points for the TLE9879 pins. Following signals are connected to the pins:

### X4:

| 1   | 2   | 3   | 4  | 5   | 6   | 7      | 8    | 9     | 10  |

|-----|-----|-----|----|-----|-----|--------|------|-------|-----|

| GND | VCP | VSD | VS | VDH | LIN | VDDEXT | VDDP | VAREF | GND |

Table 2: Pin Configuration Top Line Pin Port (X4)

### X5:

| 1   | 2   | 3   | 4    | 5    | 6    | 7    | 8    | 9    | 10   | 11   | 12   | 13   | 14   | 15   | 16   |

|-----|-----|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|

| GND | MON | RST | P0.0 | P1.1 | P0.1 | P0.2 | P0.3 | P1.2 | P1.0 | P1.3 | P1.4 | P0.4 | P2.3 | P2.4 | P2.5 |

Table 3: Pin Configuration Bottom Line Pin Port (X5)

### Terminal block for connecting the motor (marked blue)

The three pins of the terminal block provide access to the three half bridges and are intended to connect a DC brushless motor.

### **USB for UART and Debugging** (marked green)

With this Micro USB PC and evaluation board can get connected.

#### uIO BSL for LIN (marked orange)

This uIO bootstrap loader is an 8 pin header (2x4) with 2,54mm pitch.

It is intended to connect additional hardware for bootstrap loading. For programming the TLE9879 via LIN this uIO interface can be used (see <a href="www.hitex.com/uio">www.hitex.com/uio</a>).

| n.c.  | 1 | 2 | GND  |

|-------|---|---|------|

| n.c.  | 3 | 4 | n.c. |

| LIN   | 5 | 6 | VS   |

| RESET | 7 | 8 | n.c. |

**Table 4: Pin Configuration uIO BSL**

#### Pin Header for SWD (marked purple)

There is a 10 pin header (2x5) with 1,27mm pitch on the evaluation board. For debugging with another ISP than the onboard Segger this interface can be used.

DBPRE will be implicitly connected to GND by connecting the external ISP. This keeps the XMC in reset state to prevent interference of the SWD communication.

| 5V    | 1 | 2  | SWDIO (TMS)  |

|-------|---|----|--------------|

| GND   | 3 | 4  | SWCLK (P0.0) |

| GND   | 5 | 6  | n.c.         |

| n.c.  | 7 | 8  | n.c.         |

| DBPRE | 9 | 10 | RESET        |

**Table 5: Pin Configuration SWD Interface**

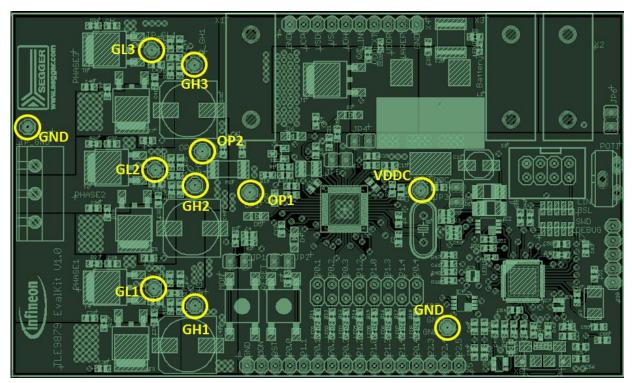

# **3 Test Points**

Figure 3: Test Points

The 3-phase power half-bridge is controlled by six gate driver pins, driving the gates of high side MOSFET and low side MOSFET for each phase. Each gate has an intended test point to measure the respective signals at high side gates and low side gates (GL1, GL2, GL3, GH1, GH2, GH3).

Test points OP1 and OP2 are provided at both sides of the shunt, which is 5mR.

Additionally there is an intended test point for VDDC and various ground points.

All test points marked in the following figure are not populated. In order to use these pins they have to be soldered in the designated solder holes.

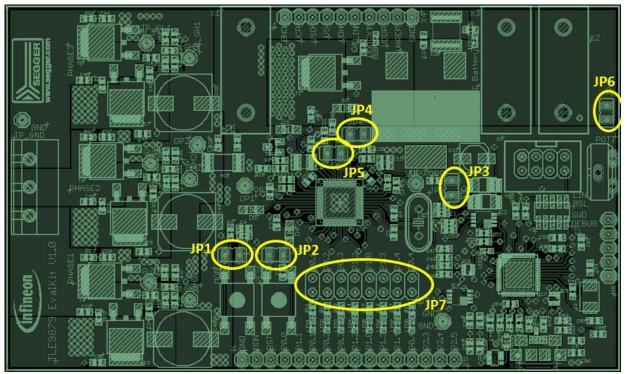

# **4 Jumper Settings**

The following table summarizes the jumpers' options. More detailed information can be found in the text below.

| JP1 | Enable or disable MON button                        |

|-----|-----------------------------------------------------|

| JP2 | Enable or disable RESET button                      |

| JP3 | Select TLE9879 as LIN Master or LIN Slave           |

| JP4 | Connect or disconnect VAREF with VDDEXT             |

| JP5 | Replace by an ampere meter to measure input current |

| JP6 | Enable or disable POTI                              |

| JP7 | Enable or disable LED for respective GPIO           |

**Table 6: Jumpers' functionalities**

Figure 4: Jumpers

**JP1**: Close this jumper to connect MON button to MON input. Open it to disconnect MON button from MON input.

**JP2**: Close this jumper to connect RESET button to RESET input. Open it to disconnect RESET button from RESET input.

**JP3**: Close this jumper to connect an additional 1k pull-up resistor. This is intended for LIN master communication. Open the jumper to use the TLE9879 as slave in a LIN network. Software for LIN low level driver can be found at the homepage of IHR (www.ihr.de).

**JP4**: Close this jumper in order to supply VAREF by VDDEXT. In case VAREF is supplied externally the user has to take care by software that the internal VAREF is disabled. Open the jumper to use the internal VAREF which has to be enabled by software.

**JP5:** This jumper is closed by default. If this jumper is left open the device is not supplied. It is intended to open the VS line in order to measure the current flowing into the TLE9879.

**JP6:** Close this jumper to connect the potentiometer to P2.4. Open this jumper to disconnect the potentiometer.

**JP7:** Jumper 7 provides one individual jumper per LED in order to connect or disconnect the respective LED to the pin port.

| P0.1 | P0.2 | P0.3 | P1.2 | P1.0 | P1.3 | P1.4 | P0.4 |

|------|------|------|------|------|------|------|------|

| LED1 | LED2 | LED3 | LED4 | LED5 | LED6 | LED7 | LED8 |

**Table 7: Combinations of GPIOs and LEDs**

### **5 Communication Interfaces**

### 5.1 LIN (via Banana jack and uIO BSL)

The device integrated LIN transceiver is connected to a banana jack and additionally to the uIO BSL interface. To integrate the device in a LIN network it is sufficient to use the single wire banana interface. The BSL interface is intended to program the device via LIN. For further information about the uIO interface see <a href="https://www.hitex.com/uio.">www.hitex.com/uio.</a>

# 5.2 UART (via USB)

A virtual COM port provided by Segger driver enables a PC – board – communication via UART. The UART2 module of TLE9879 uses the pins P1.1 (transmit) and P1.2 (receive). Those are connected to the XMC4200, which emulates Rx and Tx on PC side with Segger firmware. Though they cannot be disconnected physically, bidirectional level shifters ensure that the XMC pins are hi-Z in case the virtual COM port is not used.

By connecting the evaluation board to the PC a virtual COM port gets emulated by the Segger driver automatically. The port used will show up in the Microsoft® Windows® device manager.

Figure 5: UART and Debugging

Note: Only one of the interfaces USB or SWD can be used at one time. While using the SWD interface the XMC is hold in reset. As long as a debugger is connected with the SWD interface it eliminates therefore debugging or UART via USB.

# **5.3 Debugging (via USB or SWD-Interface)**

For serial wire debug the TLE9879 uses the pins TMS (data) and P0.0 (clock). Level shifters between XMC4200 and TLE9879 allow using P0.0, while it is not used for debugging.

The Segger J-Link module on board allows serial wire debugging via USB. Alternative debugging via SWD interface is possible to debug with another ISP than the onboard Segger e.g. U-Link2. Therefore the signals are routed through the 10 pin header SWD interface between the XMC4200 and the TLE9879. The pin configuration makes sure that the XMC is hold in reset while another debugger is physically connected as DBPRE will be implicitly connected to GND by connecting the external ISP (see Table 5).

Information regarding the software installation for editor, compiler and debugger can be found in the documentation *ePower Tool Chain Setup SDK* on the provided USB flash drive.

#### 6 Technical Data

Platine Size: (110x66) mm Voltage Supply: max. 28V Motor Current: max. 20A

Pin Ports: 5V (GPIOs of TLE9879)

# **7 Optional Additional Placements**

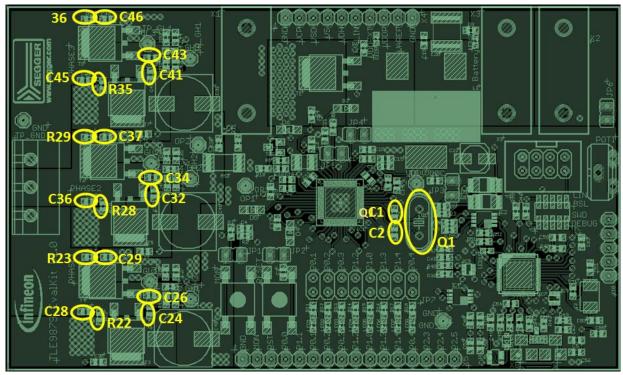

Figure 6: Additional Placements' positions

Values for these optional additional placements have to be determined depending on application.

| Q1  | External Oscillator                          |

|-----|----------------------------------------------|

| C1  | Oscillator Capacity 1                        |

| C2  | Oscillator Capacity 2                        |

| R22 | Resistance Snubber High side MOSFET Phase 1  |

| C28 | Capacity Snubber High side MOSFET Phase 1    |

| C24 | Gate Drain Capacity High side MOSFET Phase 1 |

| R23 | Resistance Snubber Low side MOSFET Phase 1   |

| C29 | Capacity Snubber Low side MOSFET Phase 1     |

| C26 | Gate Drain Capacity Low side MOSFET Phase 1  |

| R28 | Resistance Snubber High side MOSFET Phase 2  |

| C36 | Capacity Snubber High side MOSFET Phase 2    |

| C32 | Gate Drain Capacity High side MOSFET Phase 2 |

| R29 | Resistance Snubber Low side MOSFET Phase 2   |

| C37 | Capacity Snubber Low side MOSFET Phase 2     |

| C34 | Gate Drain Capacity Low side MOSFET Phase2   |

| R35 | Resistance Snubber High side MOSFET Phase 3  |

| C45 | Capacity Snubber High side MOSFET Phase 3    |

| C41 | Gate Drain Capacity High side MOSFET Phase 3 |

| R36 | Resistance Snubber Low side MOSFET Phase 3   |

| C46 | Capacity Snubber Low side MOSFET Phase 3     |

| C43 | Gate Drain Capacity Low side MOSFET Phase 3  |

|     |                                              |

**Table 8: Additional Placements**

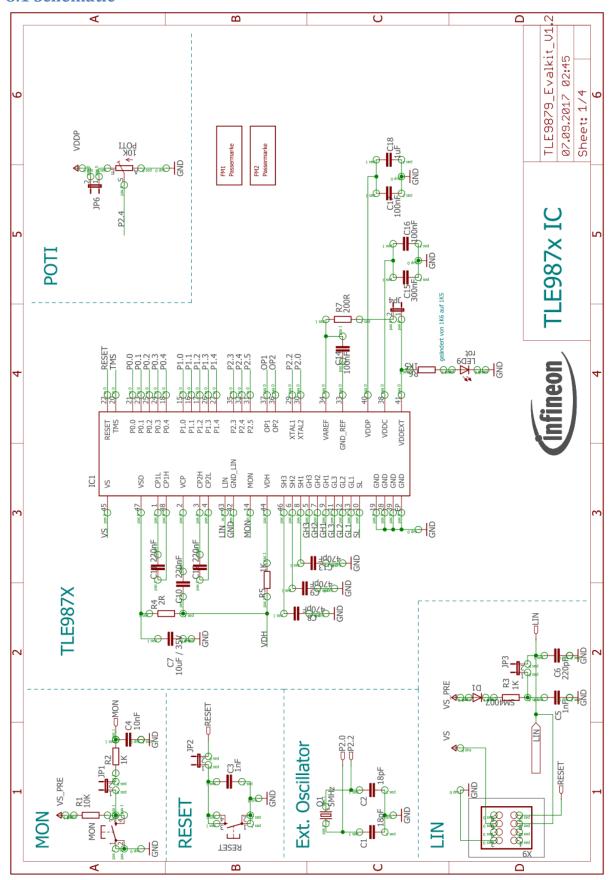

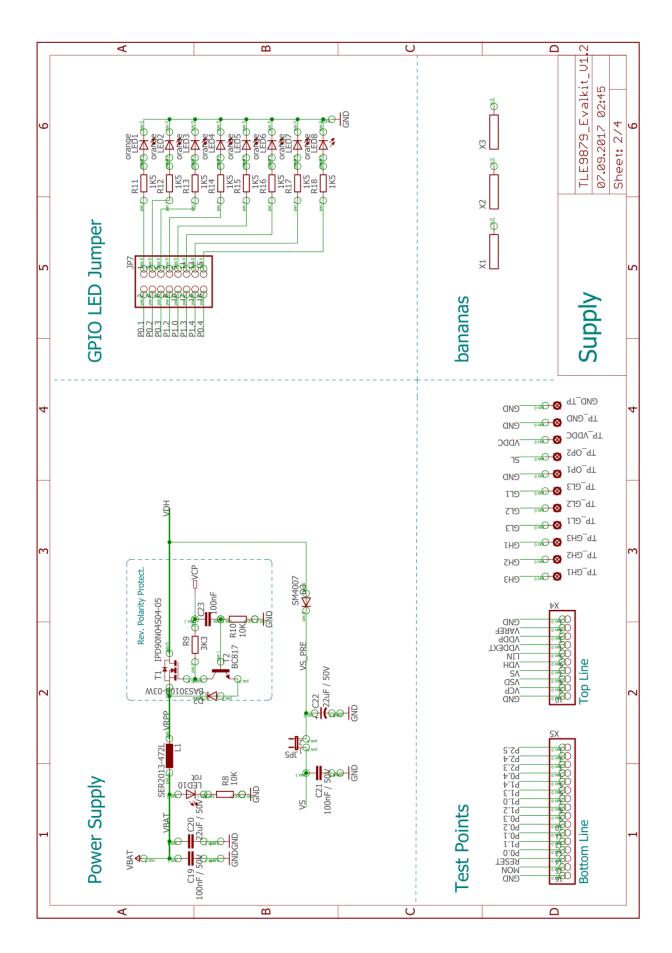

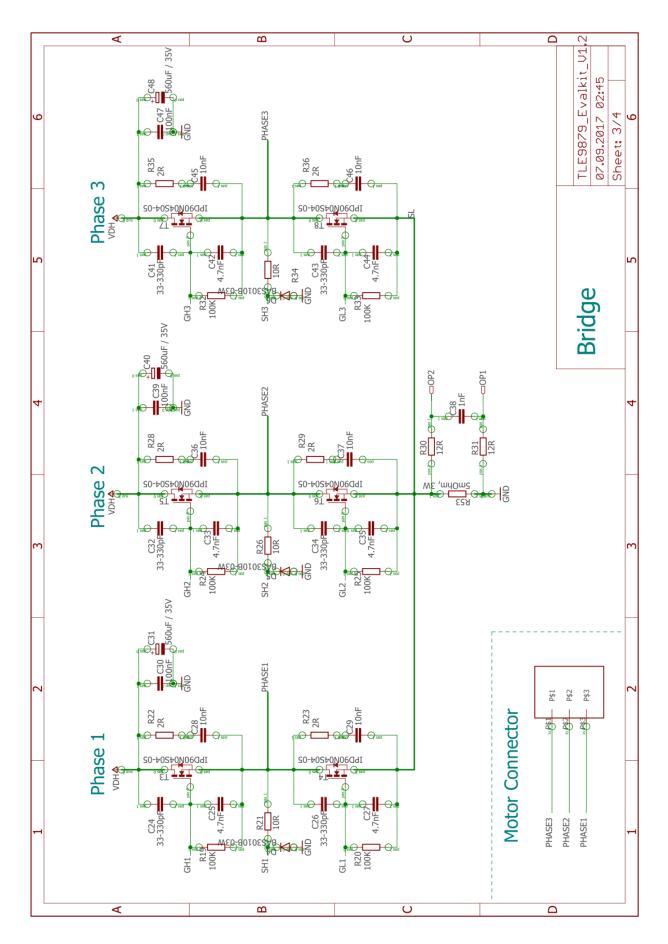

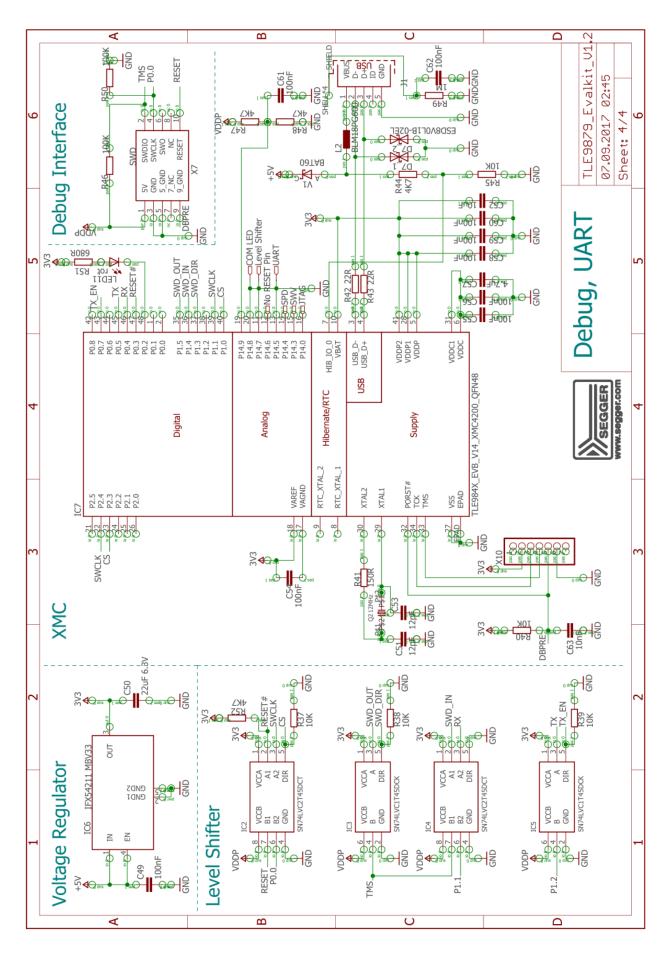

# **8 Schematics and Layout**

# 8.1 Schematic

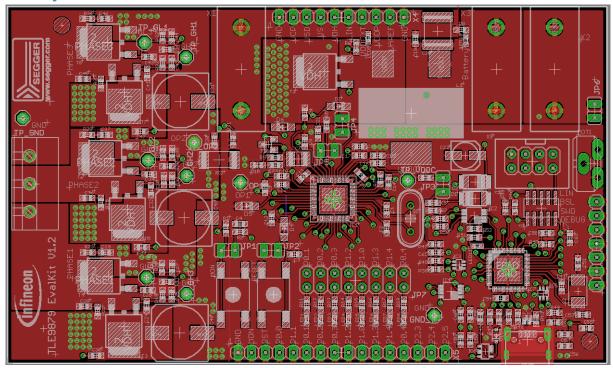

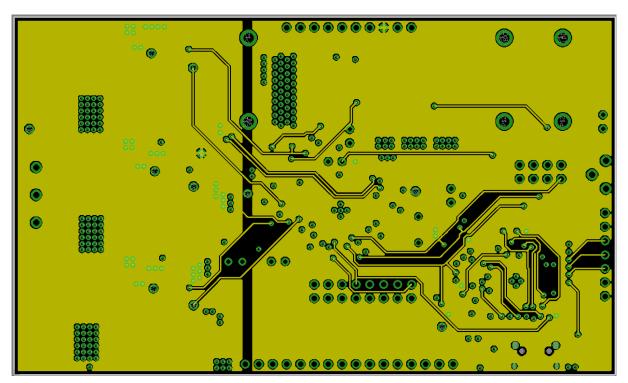

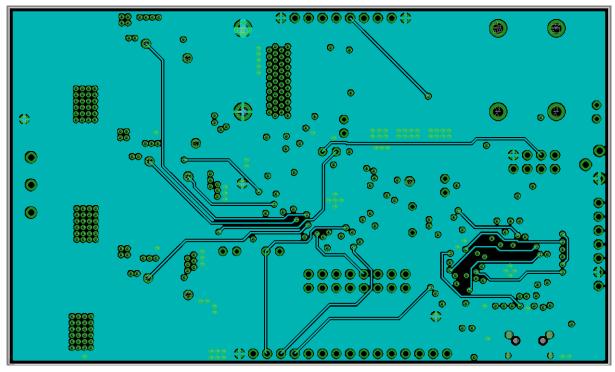

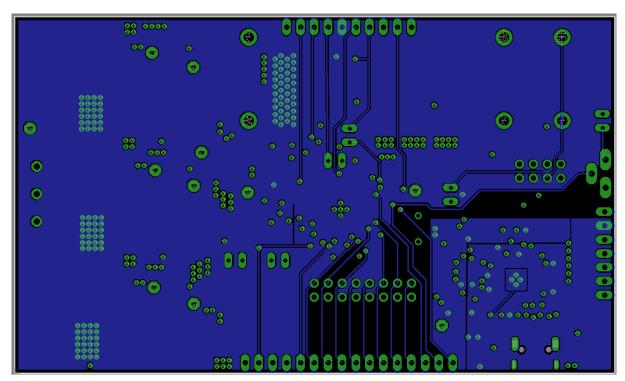

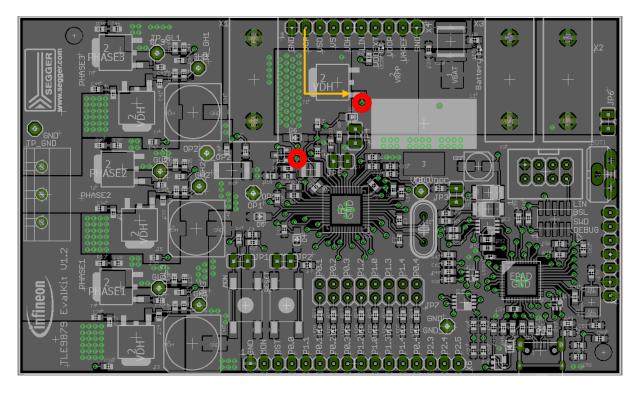

# 8.1 Layout

Top Layer

Layer 2

Layer 3

**Bottom Layer**

# 9 Errata

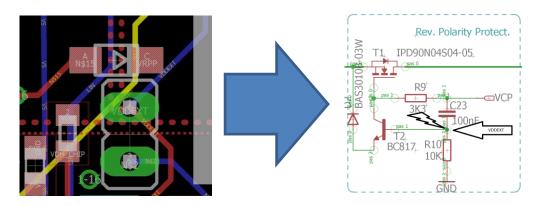

Note: TLE9879 Evalkit Rev 1.2 has some restrictions in functionality, which are described in this chapter.

# 9.1 Short of internal layer 2 and Jumper (JP4)

Redesign activities caused a short between T2 supply line and VDDEXT Jumper.

### Related limitations:

- VDDEXT cannot be used, when charge pump is enabled

- Reverse polarity circuit not functional

#### Workaround:

- Remove Jumper (JP4)

- Use VDDP instead of VDDEXT for evaluation.

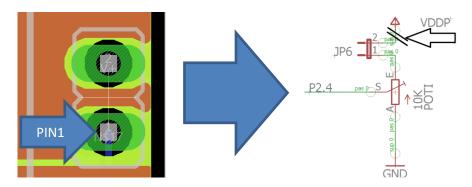

# 9.2 Jumper (JP6) not connected to VDDP.

JP6 is not connected to VDDP voltage.

### Related limitations:

- Change of potentiometer position will not change analog value on port P2.4

- Example Code, using the potentiometer is not functional without workaround

#### Workaround:

- Connect Pin 1 of JP6 with VDDP

- Potentiometer can be used as expected

# 9.3 Workaround Proposal

With this proposal, the VDDEXT PIN can be used again.

Two vias has to be drilled with a 1.1mm drill bit. The vias are marked in red in the picture below. This workaround disconnect the reverse polarity MOSFET from the Charge-Pump voltage VCP. After the fix is applied, the VDDEXT can be used as specified.

Note: The disconnected Transistor T1 can cause a voltage drop from VBAT connection to VDH voltage level. This voltage drop can be avoided by manually connecting the Gate Pin of T1 to the VCP voltage Pin (orange arrow).

If the Evaluation Kit Sample Box is marked with Revision 1.2a, this fix is already applied.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management IC Development Tools category:

Click to view products by Infineon manufacturer:

Other Similar products are found below:

EVALZ ADP130-1.8-EVALZ ADP1740-1.5-EVALZ ADP1870-0.3-EVALZ ADP1874-0.3-EVALZ ADP199CB-EVALZ ADP2102-1.25EVALZ ADP2102-1.875EVALZ ADP2102-1.8-EVALZ ADP2102-2-EVALZ ADP2102-3-EVALZ ADP2102-4-EVALZ AS3606-DB

BQ25010EVM BQ3055EVM ISLUSBI2CKIT1Z LM2734YEVAL LP38512TS-1.8EV EVAL-ADM1186-1MBZ EVAL-ADM1186-2MBZ

ADP122UJZ-REDYKIT ADP166Z-REDYKIT ADP170-1.8-EVALZ ADP2107-1.8-EVALZ ADP171-EVALZ ADP1853-EVALZ ADP1873-0.3-EVALZ

ADP198CP-EVALZ ADP2102-1.0-EVALZ ADP2102-1-EVALZ ADP2107-1.8-EVALZ ADP5020CP-EVALZ CC-ACC-DBMX-51

ATPL230A-EK MIC23250-S4YMT EV MIC26603YJL EV MIC33050-SYHL EV TPS60100EVM-131 TPS65010EVM-230 TPS7193328EVM-213 TPS72728YFFEVM-407 TPS79318YEQEVM UCC28810EVM-002 XILINXPWR-083 LMR22007YMINI-EVM