# Dual-channel low drop out linear voltage regulator

### **Features**

- Integrated current monitor

- Overvoltage, overtemperature and overcurrent detection

- Adjustable output voltage

- Output current up to 300 mA

- Adjustable output current limitation

- Very low current consumption

- Very low dropout voltage

- Stable with ceramic output capacitor of 1 μF

- Wide input voltage range up to 40 V

- · Reverse current protection

- Reverse polarity protection

- · Short circuit protection

- Overtemperature shutdown

- Automotive temperature range  $-40^{\circ}$ C  $\leq T_i \leq 150^{\circ}$ C

- Green Product (RoHS compliant)

# **Potential applications**

- Infotainment active antenna power supply

- Surround view camera power supply

- Automotive applications that are permanently connected to the battery

#### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

# **Description**

The OPTIREG™ linear TLF4477-3LA is a monolithic integrated dual channel low drop out voltage regulator capable of supplying loads up to 300 mA. For an input voltage up to 40 V the TLF4477-3LA provides an adjustable output voltage in the range from 3 V up to 20 V in a thermally enhanced PG-TSON-14 package.

The channel specific current monitors of the TLF4477-3LA provide access to unique diagnostic and protection features. They measures the output currents and translate them to a proportional voltage at the current sense output CSOx. The output current limits for each channel can be manually set by via an external resistor.

1

# Dual-channel low drop out linear voltage regulator

Overtemperature, overcurrent and output overvoltage fault conditions can be detected as an analogue voltage level at the current sense output CSOx above the current sensing range.

Separate digital status pins ST1 and ST2 for each channel can indicate the presence of one or multiple of the aforementioned faults.

The outputs of the device can be disabled independently via the enable signals on EN1 and EN2 to reduce power consumption.

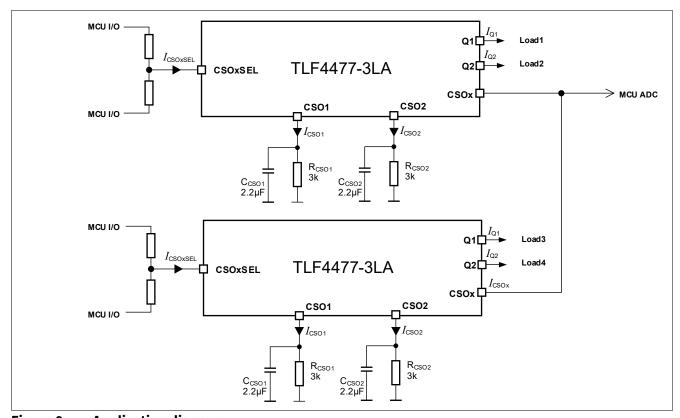

The CSOxSel selects the channel monitored at the CSOx pin. CSOxSel can also set the monitor pin CSOx into a high impedance state. This allows the CSOx signals of multiple devices to be monitored by a single ADC connected.

| Туре        | Package    | Marking |

|-------------|------------|---------|

| TLF4477-3LA | PG-TSON-14 | 44773   |

# Dual-channel low drop out linear voltage regulator

# **Table of contents**

|                          | Features                                                                                              | . 1            |

|--------------------------|-------------------------------------------------------------------------------------------------------|----------------|

|                          | Potential applications                                                                                | . 1            |

|                          | Product validation                                                                                    | . 1            |

|                          | Description                                                                                           | . 1            |

|                          | Table of contents                                                                                     | . :            |

| 1                        | Block diagram                                                                                         | . :            |

| <b>2</b><br>2.1<br>2.2   | Pin configuration                                                                                     | . 6            |

| 3                        | General product characteristics                                                                       | . 8            |

| 3.1<br>3.2<br>3.3        | Absolute maximum ratings                                                                              | . 9            |

| 4                        | Voltage regulator                                                                                     | 11             |

| 4.1<br>4.2<br>4.3<br>4.4 | Description voltage regulator                                                                         | 13<br>13<br>15 |

| 5                        | Current consumption                                                                                   | 17             |

| 5.1<br>5.2               | Electrical characteristics current consumption         Typical performance graphs current consumption |                |

| 6                        | Current and protection monitor functions                                                              |                |

| 6.1<br>6.2               | Linear current monitor                                                                                |                |

| 6.3                      | Overvoltage detection                                                                                 |                |

| 6.4                      | Thermal shutdown detection                                                                            |                |

| 6.5                      | Status output signal                                                                                  |                |

| 6.6<br>6.7               | Electrical characteristics current monitor       Typical performance characteristics current monitor  |                |

| 7                        | Enable                                                                                                |                |

| 7.1<br>7.2               | Functional description enable Electrical characteristics enable                                       | 26             |

| 8                        | Application information                                                                               |                |

| 8.1                      | Application diagram                                                                                   |                |

| 8.2<br>8.2.1             | Selection of external components                                                                      |                |

| 8.2.2                    | Output pin                                                                                            |                |

| 8.3                      | Thermal considerations                                                                                |                |

| 8.4<br>8.5               | Reverse polarity protection                                                                           |                |

| 8.5<br><b>9</b>          | Package information                                                                                   |                |

| J                        | Falkage IIIIVI IIIalivii                                                                              | 3(             |

# **Dual-channel low drop out linear voltage regulator**

| LO | Revision history | ••••• | 3 | 1 |

|----|------------------|-------|---|---|

|----|------------------|-------|---|---|

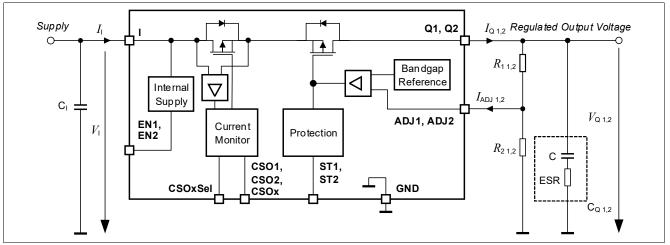

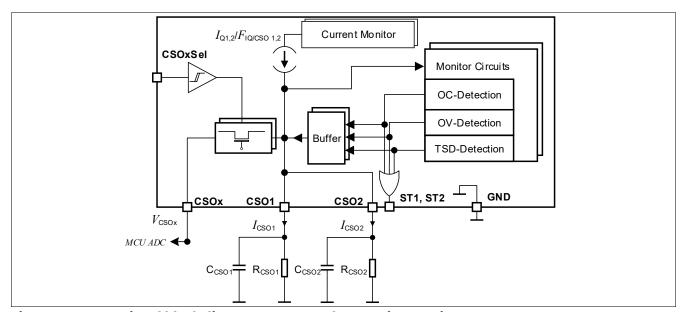

**Block diagram**

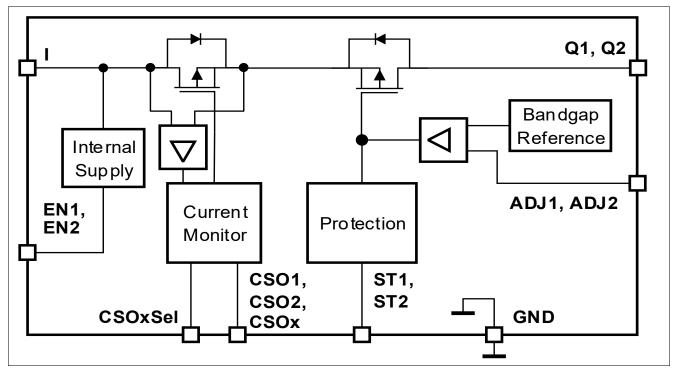

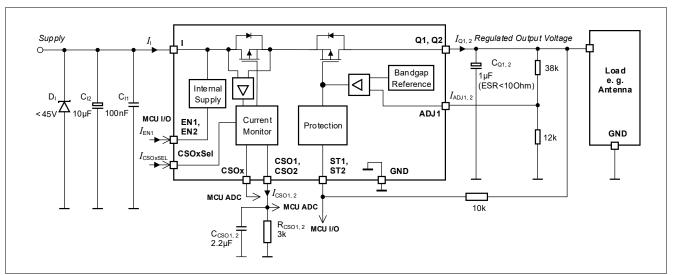

# 1 Block diagram

Figure 1 Block diagram

Pin configuration

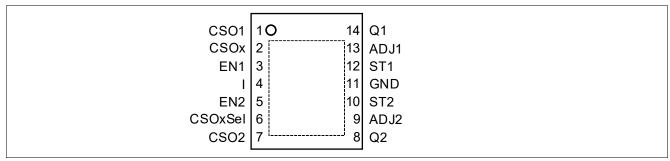

#### **Pin configuration** 2

#### Pin assignment 2.1

Pin configuration (top view) Figure 2

#### Pin definitions and functions 2.2

| Pin | Symbol  | Function                                                                                                 |

|-----|---------|----------------------------------------------------------------------------------------------------------|

| 1   | CSO1    | Current sense output                                                                                     |

|     |         | Current monitor and status output for Q1.                                                                |

|     |         | Connect a capacitor $C_{CSO1}$ and resistor $R_{CSO1}$ between CSO1 and GND close to the IC pins.        |

| 2   | CSOx    | Current sense output                                                                                     |

|     |         | Current monitor and status for Q2, if CSOxSel is "high" ( $V_{\text{CSOxSel}} = V_{\text{CSOxSel},H}$ ). |

|     |         | Current monitor and status for Q1, if CSOxSel is "low" ( $V_{CSOxSel} = V_{CSOxSel,L}$ ).                |

|     |         | High impedance (HZ), if $V_{CSOxSel} = V_{CSOxSel,T}$ or if $V_{EN1} = V_{EN2} = V_{EN1,2,low}$ .        |

| 3   | EN1     | Enable                                                                                                   |

|     |         | "High" signal ( $V_{EN1} = V_{EN1,2,high}$ ) enables regulator output Q1.                                |

|     |         | "Low" signal ( $V_{EN1} = V_{EN1,2,low}$ ) disables regulator output Q1.                                 |

|     |         | Connect to I to permanently enable the output Q1.                                                        |

|     |         | Internal pull-down (R <sub>EN1</sub> ), leave floating when Q1 permanently disabled.                     |

| 4   | 1       | IC supply                                                                                                |

|     |         | It is recommended to place a capacitor from this pin to GND, close to the pins, in order                 |

|     |         | to compensate for line influences.                                                                       |

| 5   | EN2     | Enable                                                                                                   |

|     |         | "High" signal ( $V_{EN2} = V_{EN1,2,high}$ ) enables regulator output Q2.                                |

|     |         | "Low" signal $(V_{EN2} = V_{EN1,2,low})$ disables regulator output Q2.                                   |

|     |         | Connect to I to permanently enable the output Q2.                                                        |

|     |         | Internal pull-down ( $R_{\rm EN2}$ ), leave floating when Q2 permanently disabled.                       |

| 6   | CSOxSel | Current sense output selection                                                                           |

|     |         | "High" signal ( $V_{CSOxSel} = V_{CSOxSel,H}$ ) CSOx is the current monitor and status for Q2.           |

|     |         | "Low" signal $(V_{CSOxSel} = V_{CSOxSel,L})$ CSOx is the current monitor and status for Q1.              |

|     |         | $V_{\text{CSOxSel}} = V_{\text{CSOxSel},T}$ sets CSOx to high impedance (HZ).                            |

| 7   | CSO2    | Current sense output                                                                                     |

|     |         | Current monitor and status output for Q2.                                                                |

|     |         | Connect a capacitor $C_{CSO2}$ and resistor $R_{CSO2}$ between CSO2 and GND close to the IC pins.        |

|     |         | . 6302                                                                                                   |

# **Dual-channel low drop out linear voltage regulator**

# Pin configuration

| Pin | Symbol | Function                                                                                                                                                                           |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | Q2     | <b>Regulator output</b> Connect a capacitor between Q2 and GND close to the IC pins, respecting the values given for its capacitance $C_{Q2}$ and ESR in <b>Functional range</b> . |

| 9   | ADJ2   | Voltage adjust Connect an external voltage divider to configure the nominal output voltage Q2.                                                                                     |

| 10  | ST2    | Status output Digital output signal with open drain output. A "low" signal $(V_{ST2} = V_{ST1,2,low})$ indicates fault conditions at the regulator's output Q2.                    |

| 11  | GND    | Ground                                                                                                                                                                             |

| 12  | ST1    | Status output Digital output signal with open drain output. A "low" signal ( $V_{ST1} = V_{ST1,2,low}$ ) indicates fault conditions at the regulator's output Q1.                  |

| 13  | ADJ1   | Voltage adjust Connect an external voltage divider to configure the nominal output voltage Q1.                                                                                     |

| 14  | Q1     | <b>Regulator output</b> Connect a capacitor between Q1 and GND close to the IC pins, respecting the values given for its capacitance $C_{Q1}$ and ESR in <b>Functional range</b> . |

| Pad | -      | Exposed pad Connect the exposed pad to a heat sink area. Connect the exposed pad to GND.                                                                                           |

# Dual-channel low drop out linear voltage regulator

**General product characteristics**

# 3 General product characteristics

# 3.1 Absolute maximum ratings

# Table 1 Absolute maximum ratings<sup>1)</sup>

$T_{\rm j}$  = -40°C to 150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                               | Symbol                   |      | Value | S    | Unit | Note or                                            | Number   |  |

|---------------------------------------------------------|--------------------------|------|-------|------|------|----------------------------------------------------|----------|--|

|                                                         |                          | Min. | Тур.  | Max. |      | <b>Test Condition</b>                              |          |  |

| Voltages                                                | <del></del>              |      | •     | •    | •    |                                                    | *        |  |

| IC supply I                                             | $V_{I}$                  | -40  | -     | 45   | V    | $ V_{\rm I} - V_{\rm Q1,2}  < 35 \rm V$            | P_4.1.1  |  |

| Enable input EN                                         | V <sub>EN1,2</sub>       | -40  | -     | 45   | V    | $ V_{\text{EN1,2}} - V_{\text{I}}  < 60 \text{ V}$ | P_4.1.2  |  |

| CSOxSel                                                 | $V_{\rm CSOxSel}$        | -0.3 | -     | 5    | V    | -                                                  | P_4.1.3  |  |

| Voltage adjust input ADJ                                | V <sub>ADJ1,2</sub>      | -0.3 | -     | 24   | V    | -                                                  | P_4.1.4  |  |

| Regulator output Q                                      | V <sub>Q1,2</sub>        | -0.3 | -     | 45   | V    | -                                                  | P_4.1.5  |  |

| Current monitor out CSO                                 | V <sub>CSO1,2,x</sub>    | -0.3 | -     | 5    | V    | -                                                  | P_4.1.6  |  |

| Status output                                           | V <sub>ST1,2</sub>       | -0.3 | _     | 45   | V    | <sup>2)</sup> see also <b>"Status</b>              | P_4.1.7  |  |

|                                                         | ·                        |      |       |      |      | output signal ST1,                                 |          |  |

|                                                         |                          |      |       |      |      | ST2"                                               |          |  |

| Temperatures                                            |                          |      |       |      |      |                                                    |          |  |

| Junction temperature                                    | $T_{\rm j}$              | -40  | -     | 150  | °C   | _                                                  | P_4.1.8  |  |

| Storage temperature                                     | $T_{\rm stg}$            | -55  | -     | 150  | °C   | -                                                  | P_4.1.9  |  |

| ESD susceptibility                                      |                          |      |       | •    | •    |                                                    |          |  |

| ESD susceptibility to GND                               | $V_{ESD}$                | -2   | -     | 2    | kV   | <sup>3)</sup> HBM                                  | P_4.1.10 |  |

| ESD susceptibility to GND                               | $V_{ESD}$                | -500 | -     | 500  | V    | <sup>4)</sup> CDM                                  | P_4.1.11 |  |

| ESD susceptibility pin 1, 7, 8, 14 (corner pins) to GND | V <sub>ESD1,7,8,14</sub> | -750 | _     | 750  | V    | <sup>4)</sup> CDM                                  | P_4.1.12 |  |

| / Ismay to our                                          | .6. 11 1 .               |      |       |      |      |                                                    |          |  |

- 1) Not subject to production test, specified by design.

- 2) Special care must be taken to control (for by optical inspection) the proper handling of ST pin with an external resistor and not connecting directly to a higher voltage level, which allows an uncontrolled current flowing into the pin.

- 3) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS001 (1.5 k $\Omega$ , 100 pF).

- 4) ESD susceptibility, Charged Device Model "CDM" according JEDEC JESD22-C101.

#### **Notes**

- 1. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as outside normal operating range. Protection functions are not designed for continuous repetitive operation.

- 2. Stresses above the ones listed her may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Dual-channel low drop out linear voltage regulator

# **General product characteristics**

#### **Functional range** 3.2

**Functional range** Table 2

| Parameter                                   | Symbol                |                                         | Values | 5    | Unit | Note or                                                    | Number  |

|---------------------------------------------|-----------------------|-----------------------------------------|--------|------|------|------------------------------------------------------------|---------|

|                                             |                       | Min.                                    | Тур.   | Max. |      | <b>Test Condition</b>                                      |         |

| Input voltage                               | V <sub>I</sub>        | $V_{\mathrm{Q1,2}}$ + $V_{\mathrm{dr}}$ | -      | 40   | V    | $(V_1 - V_{Q1,2}) < 35 \text{ V}$<br>$V_1 > 5.5 \text{ V}$ | P_4.2.1 |

| Enable voltage                              | V <sub>EN1,2</sub>    | 0                                       |        | 40   | V    | -                                                          | P_4.2.2 |

| Output voltage range                        | V <sub>Q1,2</sub>     | 3                                       | -      | 20   | V    | -                                                          | P_4.2.3 |

| Current sense output resistor               | R <sub>CSO1,2</sub>   | 1.7                                     | -      | 10.2 | kΩ   | _                                                          | P_4.2.4 |

| Current sense output capacitor requirements | C <sub>CSO1,2</sub>   | 1                                       | -      | 4.7  | μF   | 1)                                                         | P_4.2.5 |

| Current sense output capacitor requirements | ESR <sub>CSO1,2</sub> | -                                       | -      | 10   | Ω    | 1)                                                         | P_4.2.6 |

| Junction temperature                        | T <sub>j</sub>        | -40                                     | -      | 150  | °C   | -                                                          | P_4.2.7 |

| Output capacitor requirements               | $C_{Q}$               | 1                                       | -      | _    | μF   | 1)2)                                                       | P_4.2.8 |

| Output capacitor requirements               | ESR <sub>CQ</sub>     | -                                       | -      | 10   | Ω    | 1)3)                                                       | P_4.2.9 |

<sup>1)</sup> Not subject to production test, specified by design.

Note:

Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

<sup>2)</sup> The minimum output capacitance requirement is applicable for a worst case capacitance tolerance of 30%.

<sup>3)</sup> Relevant ESR value at f = 10 kHz.

# Dual-channel low drop out linear voltage regulator

### **General product characteristics**

#### 3.3 Thermal resistance

Table 3 Thermal resistance<sup>1)</sup>

| Parameter               | Symbol     |      | Value | S    | Unit | Note or                                              | Number  |

|-------------------------|------------|------|-------|------|------|------------------------------------------------------|---------|

|                         |            | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                |         |

| Junction to case bottom | $R_{thJC}$ | _    | 9.5   | -    | K/W  | Measured to the exposed pad                          | P_4.3.1 |

| Junction to ambient     | $R_{thJA}$ | -    | 137   | -    | K/W  | <sup>2)</sup> Footprint only                         | P_4.3.2 |

| Junction to ambient     | $R_{thJA}$ | -    | 67    | -    | K/W  | <sup>2)</sup> 300 mm <sup>2</sup> PCB heat sink area | P_4.3.3 |

| Junction to ambient     | $R_{thJA}$ | _    | 57    | -    | K/W  | <sup>2)</sup> 600 mm <sup>2</sup> PCB heat sink area | P_4.3.4 |

| Junction to ambient     | $R_{thJA}$ | _    | 45    | -    | K/W  | <sup>3)</sup> 2s2p PCB                               | P_4.3.5 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Specified  $R_{thJA}$  value is according to Jedec JESD 51-3 at natural convection on FR4 1s0p board; The product (chip and package) was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with 1 copper layer (1 × 70  $\mu$ m Cu).

<sup>3)</sup> Specified  $R_{thJA}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The product (chip and package) was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with 2 inner copper layers (2 × 70  $\mu$ m Cu, 2 × 35  $\mu$ m Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

# Dual-channel low drop out linear voltage regulator

**Voltage regulator**

# 4 Voltage regulator

# 4.1 Description voltage regulator

The output voltage  $(V_{Q1}, V_{Q2})$  is divided by an external resistor network and applied to the ADJ1 and ADJ2 pins as  $(V_{ADJ1}, V_{ADJ2})$ . The device compares the voltage  $V_{ADJ1}, V_{ADJ2}$  with an internal reference voltage and drives the pass transistor of each channel accordingly.

The following factors determine the stability of the control loop:

- · Output capacitor

- Load currents I<sub>Q1</sub>, I<sub>Q1</sub>

- Chip temperature T<sub>i</sub>

- Internal circuit design

#### **Output capacitor**

To ensure stable operation, the capacitance of the output capacitors ( $C_{Q1}$ ,  $C_{Q2}$ ) and its equivalent series resistors ( $ESR_{CQ1}$ ,  $ESR_{CQ2}$ ) requirements must be maintained, see **Functional range**. The output capacitor must be sized according to the requirements of the application.

#### Input capacitor

An input capacitor  $C_1$  is recommended to compensate line influences. Connect the capacitors close to the component's terminals.

#### **Reverse polarity protection**

A secondary PMOS detects and limits potential reverse current flow. An external reverse polarity protection diode is not needed. The reverse current must be taken into consideration for thermal design, since the thermal protection circuit does not operate in reverse polarity condition. For details on the reverse current see **Electrical characteristics: voltage regulator**.

#### **Output current limitation**

In addition to the channel specific and user-configurable current limitation on the CSO1 and CSO2 pins, an internal current limitation protects the device from destruction in case of catastrophic events. The internal current limitation is always active as a secondary protection feature. For details on how to set the user-configurable current limitation see **Adjustable output current limitation**.

#### Overtemperature shutdown

The overtemperature shutdown circuit prevents the device from immediate destruction in case of a fault condition, for example due to a permanent short circuit at the output. In such condition the overtemperature shutdown circuit switches off the power stage. After the device cools down again, the regulator restarts. This leads to an oscillatory behavior of the output voltages  $V_{Q1}$ ,  $V_{Q2}$ . However, any junction temperature above 150°C is outside the maximum ratings and therefore significantly reduces the lifetime of the device.

Since the device allows for negative supply voltages, small currents can flow through the device in reverse direction increasing its junction temperature. This reverse current must be taken into account, since the overtemperature shutdown circuit does not mitigate its heating effects.

# Dual-channel low drop out linear voltage regulator

# **Voltage regulator**

Figure 3 Functional block diagram voltage regulator circuit

# Dual-channel low drop out linear voltage regulator

**Voltage regulator**

#### **Electrical characteristics voltage regulator** 4.2

#### Table 4 **Electrical characteristics: voltage regulator**

$V_1 = 13.5 \text{ V}$ ,  $T_1 = -40 ^{\circ}\text{C}$  to 150  $^{\circ}\text{C}$ , all voltages with respect to ground, direction of currents as shown in Figure 8 "Application diagram" on Page 27 (unless otherwise specified)

| Parameter                                   | Symbol                         |      | Value | s         | Unit | Note or                                                                                                                                                                                                                      | Number   |  |

|---------------------------------------------|--------------------------------|------|-------|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

|                                             |                                | Min. | Тур.  | Тур. Мах. |      | Test Condition                                                                                                                                                                                                               |          |  |

| Reference voltage                           | V <sub>REF,int</sub>           | -    | 1.2   | -         | V    | 1)                                                                                                                                                                                                                           | P_5.2.1  |  |

| Output voltage tolerance                    | V <sub>Q1,2</sub>              | -2   | -     | 2         | %    | $^{2)}$ 1 mA $\leq I_{Q1,2} \leq$ 300 mA;<br>9 V $\leq V_{I} \leq$ 16 V;<br>3 V $\leq V_{Q1,2} \leq$ 14 V with<br>$V_{I} > V_{Q1,2} + V_{dr} + 0.5 V$                                                                        | P_5.2.2  |  |

| Output voltage tolerance                    | $V_{\mathrm{Q1,2}}$            | -2   | _     | 2         | %    | $\begin{array}{l} 1 \text{ mA} \leq I_{Q1,2} \leq 150 \text{ mA}; \\ 6 \text{ V} \leq V_{I} \leq 16 \text{ V}; \\ 5 \text{ V} \leq V_{Q1,2} \leq 15 \text{ V with} \\ V_{I} > V_{Q1,2} + V_{dr} + 0.5 \text{ V} \end{array}$ | P_5.2.3  |  |

| Output voltage tolerance                    | $V_{\mathrm{Q1,2}}$            | -2   | _     | 2         | %    | 1 mA $\leq I_{Q1,2} \leq 100$ mA;<br>16 V $\leq V_{l} \leq 32$ V;<br>3 V $\leq V_{Q1,2} \leq 15$ V                                                                                                                           | P_5.2.4  |  |

| Output voltage tolerance                    | V <sub>Q1,2</sub>              | -2   | _     | 2         | %    | 1 mA $\leq I_{Q1,2} \leq$ 10 mA;<br>32 V $\leq V_{I} \leq$ 40 V;<br>3 V $\leq V_{Q1,2} \leq$ 16 V                                                                                                                            | P_5.2.5  |  |

| Output voltage tolerance                    | $V_{\mathrm{Q1,2}}$            | -1.5 | -     | 1.5       | %    | 100 mA $\leq I_{Q1,2} \leq$ 300 mA;<br>$8 \text{ V} \leq V_{l} \leq$ 16 V;<br>$-40^{\circ}\text{C} \leq T_{j} \leq$ 85°C;<br>$7 \text{ V} \leq V_{Q1,2} \leq$ 9 V;<br>$V_{l} > V_{Q1,2} + V_{dr} + 0.5 \text{ V}$            | P_5.2.6  |  |

| Load regulation steady state                | $\Delta V_{\mathrm{Q1,2load}}$ | -30  | -5    | -         | mV   | $I_{Q1,2} = 1 \text{ mA to } 250 \text{ mA;}$<br>$V_1 = 6 \text{ V; } V_{Q1,2} = 5 \text{ V}$                                                                                                                                | P_5.2.7  |  |

| Line regulation steady state                | $\Delta V_{\rm Q1,2,line}$     | _    | 5     | 20        | mV   | $V_1 = 6 \text{ V to } 32 \text{ V};$<br>$I_{Q1,2} = 5 \text{ mA}; V_{Q1,2} = 5 \text{ V}$                                                                                                                                   | P_5.2.8  |  |

| Power supply ripple rejection               | PSRR                           | 60   | 65    | _         | dB   | $^{1)} f_{\text{ripple}} = 100 \text{ Hz};$ $V_{\text{ripple}} = 1 \text{ V}_{\text{pp}};$ $V_{\text{Q1,2}} = 5 \text{ V};$ $I_{\text{Q1,2}} < 100 \text{ mA}$                                                               | P_5.2.10 |  |

| Dropout voltage $V_{dr} = V_{l} - V_{Q1,2}$ | $V_{ m dr}$                    | _    | 200   | 350       | mV   | $I_{Q1,2} = 100 \text{ mA};$<br>$I_{Q1,2} = 5 \text{ V}$                                                                                                                                                                     | P_5.2.12 |  |

| Dropout voltage $V_{dr} = V_{l} - V_{Q1,2}$ | $V_{ m dr}$                    | _    | 350   | 650       | mV   | $I_{Q1,2} = 200 \text{ mA};$<br>$I_{Q1,2} = 5 \text{ V}$                                                                                                                                                                     | P_5.2.13 |  |

| Output current limitation                   | $I_{\mathrm{Q1,2,lim}}$        | 301  | _     | 500       | mA   | $0 \text{ V} \le V_{Q1,2} \le 0.95 \times V_{Q1,2,\text{nom}}$                                                                                                                                                               | P_5.2.15 |  |

| Reverse current                             | I <sub>Q1,2rev</sub>           | -2   | -1    | _         | mA   | $V_{\rm I} = 0 \text{ V}; V_{\rm Q1,2} = 5 \text{ V}$                                                                                                                                                                        | P_5.2.16 |  |

| Reverse current at negative input voltage   | I <sub>Irev</sub>              | -2.6 | -0.1  | _         | mA   | $V_1 = -16 \text{ V}; V_{Q1,2} = 0 \text{ V}$                                                                                                                                                                                | P_5.2.17 |  |

# Dual-channel low drop out linear voltage regulator

# **Voltage regulator**

#### **Table 4 Electrical characteristics: voltage regulator** (cont'd)

$V_1$  = 13.5 V,  $T_j$  = -40°C to 150°C, all voltages with respect to ground, direction of currents as shown in **Figure 8** "Application diagram" on Page 27 (unless otherwise specified)

| Parameter                                     | Symbol               | Values |      |      | Unit | Note or                                    | Number   |

|-----------------------------------------------|----------------------|--------|------|------|------|--------------------------------------------|----------|

|                                               |                      | Min.   | Тур. | Мах. |      | <b>Test Condition</b>                      |          |

| Reverse current at output short to battery    | I <sub>QtoVbat</sub> | -40    | -    | _    | μΑ   | $V_{\rm I}$ = 5.8 V; $V_{\rm Q1,2}$ = 16 V | P_5.2.18 |

| Overtemperature shutdown threshold            | $T_{\rm j,sd}$       | 151    | 165  | 180  | °C   | <sup>1)</sup> T <sub>j</sub> increasing    | P_5.2.19 |

| Overtemperature shutdown threshold hysteresis | $T_{\rm j,hy}$       | 5      | 10   | 15   | K    | <sup>1)</sup> T <sub>j</sub> decreasing    | P_5.2.20 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Referring to the device tolerance only, the tolerance of the resistor divider can cause additional deviation.

<sup>3)</sup> Measured when the output voltage  $V_{\rm Q1,2}$  has dropped 100 mV from its nominal value.

# Dual-channel low drop out linear voltage regulator

**Voltage regulator**

# 4.3 Application information for setting the variable output voltage

The output voltages of both outputs Q1, Q2 can be adjusted between 3 V and 20 V independently via an external output voltage divider, closing the control loops to their respective voltage adjust pins ADJ1, ADJ2.

The device compares the voltages at ADJ1, ADJ2 pins to the internal reference of typical 1.2 V with channel specific error amplifiers. Each error amplifier drives the channel's pass transistor accordingly to control the output voltage.

Figure 4 Application detail external components at output for variable voltage regulator

The output voltage is calculated according to **Equation (4.1)**:

$$V_{Q1,2} = (R_{11,2} + R_{21,2})/R_{21,2} \times V_{REF,int}$$

, neglecting  $I_{ADJ1,2}$  (4.1)

$V_{\text{REF.int}}$  is typically 1.2 V.

To avoid errors caused by the leakage current  $I_{ADJ1,2}$ , we recommend to choose the resistor value for  $R_{2,1,2} < 27 \text{ k}\Omega$ .

The accuracy of the resistors for the external voltage divider also influence the output voltage tolerance. To achieve a reasonable accuracy resistors with a tolerance of 1% or less are recommended for the feedback divider.

**Voltage regulator**

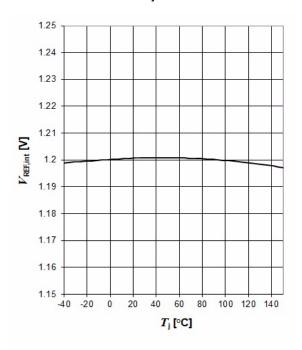

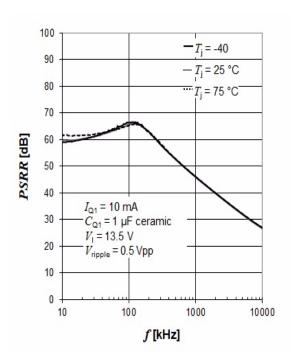

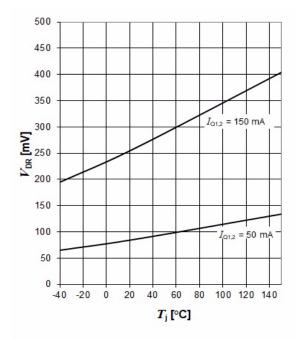

# 4.4 Typical performance characteristics voltage regulator

# Reference voltage $V_{\text{REF,int}}$ versus junction temperature $T_{\text{i}}$

# Power supply ripple rejection PSRR

# Dropout voltage $V_{dr}$ versus junction temperature $T_i$

# Dual-channel low drop out linear voltage regulator

**Current consumption**

#### **Current consumption** 5

#### **Electrical characteristics current consumption** 5.1

#### **Electrical characteristics: current consumption** Table 5

$V_{\rm I}$  = 13.5 V,  $T_{\rm j}$  = -40°C to 150°C, all voltages with respect to ground; direction of currents as shown in **Figure 7** "Application diagram" on Page 27 (unless otherwise specified)

| Parameter           | Symbol                |      | Value | s    | Unit | Note or Test Condition                                                                                                                               | Number   |

|---------------------|-----------------------|------|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                     |                       | Min. | Тур.  | Max. |      |                                                                                                                                                      |          |

| Current consumption | I <sub>q1,on</sub>    | -    | -     | 815  | μА   | $I_{Q1} \le 200 \mu A;$ $T_j \le 25^{\circ}C;$ $V_{EN1} = 5 V;$ $V_{EN2} = 0 V;$ $I_{q1} = I_1 - I_{Q1} - I_{CSO1}$                                  | P_6.1.1  |

| Current consumption | I <sub>q1,on</sub>    | -    | -     | 835  | μА   | $I_{Q1} \le 200 \mu\text{A};$ $T_j \le 85^{\circ}\text{C};$ $V_{EN1} = 5 \text{V};$ $V_{EN2} = 0 \text{V};$ $I_{q1} = I_1 - I_{Q1} - I_{CSO1}$       | P_6.1.2  |

| Current consumption | I <sub>q1,on</sub>    | _    | _     | 1    | mA   | $I_{Q1} = 200 \text{ mA};$ $V_{EN1} = 5 \text{ V};$ $V_{EN2} = 0 \text{ V};$ $I_{q1} = I_1 - I_{Q1} - I_{CSO1}$                                      | P_6.1.3  |

| Current consumption | I <sub>q2,on</sub>    | -    | -     | 815  | μА   | $I_{Q2} \le 200 \mu\text{A};$ $T_{j} \le 25^{\circ}\text{C};$ $V_{EN2} = 5 \text{V};$ $V_{EN1} = 0 \text{V};$ $I_{Q2} = I_{1} - I_{Q2} - I_{CSO2}$   | P_6.1.6  |

| Current consumption | I <sub>q2,on</sub>    | -    | _     | 835  | μΑ   | $I_{Q2} \le 200  \mu\text{A}; T_j \le 85^{\circ}\text{C};$<br>$V_{EN2} = 5  V; V_{EN1} = 0V;$<br>$I_{q2} = I_1 - I_{Q2} - I_{CSO2}$                  | P_6.1.7  |

| Current consumption | I <sub>q2,on</sub>    | _    | _     | 1    | mA   | $I_{Q2} = 200 \text{ mA};$<br>$V_{EN2} = 5 \text{ V}; V_{EN1} = 0 \text{ V};$<br>$I_{q2} = I_1 - I_{Q2} - I_{CSO1}$                                  | P_6.1.8  |

| Current consumption | I <sub>q1,2,on</sub>  | _    | _     | 1.5  | mA   | $I_{Q1} = I_{Q2} = 50 \text{ mA};$<br>$V_{EN1} = 5 \text{ V}; V_{EN2} = 5 \text{ V};$<br>$I_{q1,20n} = I_1 - I_{Q2} - I_{Q1} - I_{CSO1} - I_{CSO2}$  | P_6.1.9  |

| Current consumption | I <sub>q1,2,on</sub>  | _    | _     | 1.6  | mA   | $I_{Q1} = I_{Q2} = 200 \text{ mA};$<br>$V_{EN1} = 5 \text{ V}; V_{EN2} = 5 \text{ V};$<br>$I_{q1,2on} = I_1 - I_{Q2} - I_{Q1} - I_{CSO1} - I_{CSO2}$ | P_6.1.10 |

| Current consumption | I <sub>q1,2,off</sub> | _    | -     | 3    | μΑ   | $T_{\rm j} \le 25^{\circ}\text{C};$<br>$V_{\rm EN1} = 0 \text{ V}; V_{\rm EN2} = 0 \text{ V}$                                                        | P_6.1.11 |

| Current consumption | I <sub>q1,2,off</sub> | _    | _     | 5    | μΑ   | $T_{\rm j} \le 85^{\circ}\text{C}$<br>$V_{\rm EN1} = 0 \text{ V}; V_{\rm EN2} = 0 \text{ V}$                                                         | P_6.1.12 |

# Dual-channel low drop out linear voltage regulator

# **Current consumption**

#### Table 5 **Electrical characteristics: current consumption** (cont'd)

$V_1$  = 13.5 V,  $T_1$  = -40°C to 150°C, all voltages with respect to ground; direction of currents as shown in **Figure 7** "Application diagram" on Page 27 (unless otherwise specified)

| Parameter           | Symbol                | Values |      | Unit | Note or Test Condition | Number                                                                                            |          |

|---------------------|-----------------------|--------|------|------|------------------------|---------------------------------------------------------------------------------------------------|----------|

|                     |                       | Min.   | Тур. | Max. |                        |                                                                                                   |          |

| Current consumption | I <sub>q1,2,off</sub> | _      | _    | 15   | μΑ                     | $T_{\rm j} \le 85^{\circ}\text{C};$<br>$V_{\rm EN1} = 0.8 \text{ V}; V_{\rm EN2} = 0.8 \text{ V}$ | P_6.1.13 |

| Current consumption | $I_{q1,2,off}$        | _      | _    | 15   | μΑ                     | $T_{\rm j} \le 85$ °C;<br>$V_{\rm EN1} = 0.8$ V; $V_{\rm EN2} = 0$ V                              | P_6.1.14 |

| Current consumption | I <sub>q1,2,off</sub> | -      | -    | 15   | μΑ                     | $V_{\text{EN1}} = 0 \text{ V}; V_{\text{EN2}} = 0 \text{ V}$                                      | P_6.1.15 |

**Current consumption**

#### Typical performance graphs current consumption **5.2**

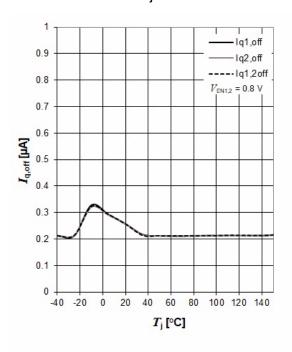

# Current consumption $I_{\rm q1,off}$ , $I_{\rm q2,off}$ , $I_{\rm q1,2,off}$ versus junction temperature $T_i$

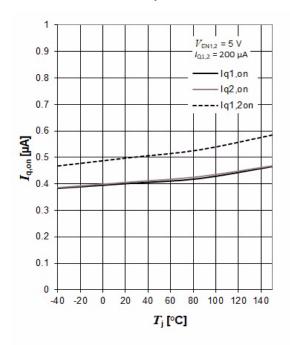

# Current consumption $I_{\rm q1,on}, I_{\rm q2,on}, I_{\rm q1,2,on}$ versus junction temperature $T_i$

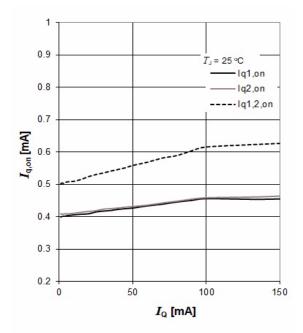

# Current consumption $I_{\rm q1,on}, I_{\rm q2,on}, I_{\rm q1,2,on}$ versus output current $I_{Q1,2}$

# Dual-channel low drop out linear voltage regulator

**Current and protection monitor functions**

# 6 Current and protection monitor functions

The device provides a set of advanced monitoring functions to support system analysis and failure identification.

#### **Current and failure monitor**

The output currents of the power stages ( $I_{Q1}$ ,  $I_{Q2}$ ) are scaled down by the current monitor factor  $F_{IQ/ICSO1,2,x}$  and flow out of the respective pins CSO1 and CSO2, causing a voltage drop at the external resistors  $R_{CSO1}$ ,  $R_{CSO2}$ . By choosing the size of ( $R_{CSO1}$ ,  $R_{CSO2}$ ) the current limit can be programmed, see **Adjustable output current limitation**. The voltage on the CSO1 and CSO2 pin can be sampled by an ADC to measure the respective power stage currents  $I_{Q1}$ ,  $I_{Q2}$ . Hereby the ratios between  $R_{CSO1}$ ,  $R_{CSO2}$  and  $F_{IQ/ICSO1,2,x}$  must be taken into account accordingly. The capacitors  $C_{CSO1}$ ,  $C_{CSO2}$  are required for loop stability and must be sized as given in **Functional range**.

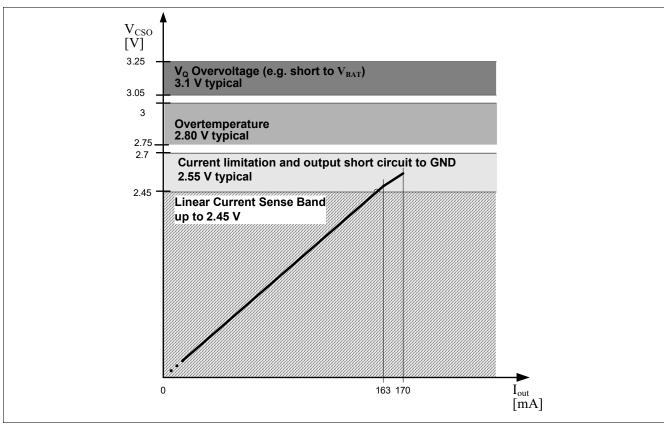

Voltage levels on the CSO1 and CSO2 pin above the linear current sensing range indicate fault conditions, see **Figure 6**. This includes an active current limit, overtemperature and overvoltage.

In addition the presence of either of the three fault conditions can also be detected on the channel specific digital pins ST1 and ST2, see **Status output signal**.

By applying  $V_{\text{CSOxSel,L}}$  from **Electrical characteristics: current monitor** to the CSOxSel pin, CSOx can be internally connected to CSO1. When applying  $V_{\text{CSOxSel,H}}$  to CSOxSel it is internally connected to CSO2. The voltage  $V_{\text{CSOxSel,T}}$  on CSOxSel puts CSOx into a high impedance state. This feature allows the CSOx signal to be shared between multiple channels and devices that are connected to a single ADC for monitoring, see **Application information**. Any additional current drawn from CSOx influences the voltage levels on the CSO1 and CSO2 pins due to the internal current sources driving  $I_{\text{CSO1}}$  and  $I_{\text{CSO2}}$  respectively.

Figure 5 Functional block diagram current and protection monitor

To reduce possible effects from the supply voltage  $V_1$  additional filtering of the supply voltage is recommended. Place a 100 nF capacitor as close a possible to the IC terminal, which is connected to  $V_1$ .

# Dual-channel low drop out linear voltage regulator

### **Current and protection monitor functions**

**Figure 6** shows the output voltage level at the CSO output (CSO1, CSO2, CSOx pin) versus the operation or fault condition. The graph is valid for the following set up of external components:

$$C_{\text{CSO1,2}} = 2.2 \,\mu\text{F}$$

$$R_{\rm CSO1,2} = 3 \text{ k}\Omega$$

Note:

In case of high junction temperature ( $T_j > 151$ °C) and with any of the CSO pins (CSO1, CSO2) directly connected to GND, the return to normal operation from the thermal shutdown mode cannot be ensured.

Figure 6 Output levels and functionality of the CSO output

Note: The graph is just an example and only valid for a certain configuration of the external components.

#### 6.1 Linear current monitor

Inside the linear current monitor area of **Figure 6** the current driven out of the CSO1 or CSO2 pin is directly proportional to the corresponding output load  $I_{Q1}$ ,  $I_{Q2}$ .

The level of the current  $I_{CSO~1.2}$  can be calculated according to **Equation (6.1)**:

(6.1)

$$I_{\text{CSO 1,2}} = \frac{I_{\text{Q1,2}}}{F_{\text{IQ/ICSO 1,2}}}$$

# Dual-channel low drop out linear voltage regulator

### **Current and protection monitor functions**

# 6.2 Adjustable output current limitation

The device has a channel specific and adjustable current limitation for the current flowing out of the respective power stage. If the level of the output current exceeds its defined current limit threshold  $I_{Q,lim}$ , then the device limits the output current.

Setting the adjustable current limitation:

(6.2)

$$I_{\text{Q 1,2,lim}} = \frac{2.55\text{V} \cdot F_{\text{IQ/ICSO 1,2}}}{R_{\text{CSO 1,2}}}$$

A voltage level as defined in **CSO voltage level Overvoltage detected** is applied at the CSO output pins. In addition the ST1, ST2 pins are set to "low."

Note:

During power up of the device, the regulator current limit is according to **CSO current at no load condition**. If an adjustable current limit is set, the status output pin ST is set to "low" as long as the adjustable current limitation is active during the power up sequence.

For example, use the following configuration to set the current limitation at 170 mA:

$$I_{\text{Q 1,2,lim}} = \frac{2.55\text{V} \cdot 200}{3\text{k}\Omega}$$

$$FIQ/ICSO = 200$$

$R_{CSO} = 3 \text{ k}\Omega$

# 6.3 Overvoltage detection

To detect a possible short circuit of the output to a higher supply rail the device has an overvoltage detection. If the voltage level at the ADJ1 pin is 20% higher than the internal reference voltage  $V_{\text{REF,int}}$  defined in **Reference voltage**, then the device detects overvoltage.

If the device detects an overvoltage event at one of the outputs Q1, Q2, then it sets the respective CSO output CSO1, CSO2 to a voltage level defined in **CSO voltage level Overvoltage detected**. In addition, the device sets the corresponding digital status output ST1, ST2 to "low".

#### 6.4 Thermal shutdown detection

If the junction temperature exceeds the limits defined in the **Overtemperature shutdown threshold**, then the device disables the output. In this case the device applies a voltage level defined in **CSO voltage level Current limitation** at the respective pins CSO1 and CSO2. In addition, the device sets the corresponding pins ST1 and ST2 to "low".

# 6.5 Status output signal

The status condition pins ST1, ST2 are open drain outputs. An external pull-up resistor must be applied for functionality. The current into the pin must be limited by sizing the resistor according to **Status output digital signal sink current**. Do not connect the ST1 pin nor the ST2 pin directly to a supply voltage, as this can damage the device.

# Dual-channel low drop out linear voltage regulator

### **Current and protection monitor functions**

If one or more of the monitored protection functions (overcurrent, overvoltage and temperature shutdown) are active for Q1, then the device sets the digital status output pin ST1 to "low".

If one or more of the monitored protection functions (overcurrent, overvoltage and temperature shutdown) are active for Q2, then the device sets the digital status output pin ST2 to "low".

#### **Electrical characteristics current monitor** 6.6

#### Table 6 **Electrical characteristics: current monitor**

$V_1 = 13.5 \text{ V}$ ,  $T_1 = -40 ^{\circ}\text{C}$  to 150  $^{\circ}\text{C}$ , all voltages with respect to ground, direction of currents as shown in Figure 7 "Application diagram" on Page 27 (unless otherwise specified)

| Parameter                                      | Symbol                   |      | Value    | S    | Unit | Note or<br>Test Condition                                                                                                                                                                              | Number  |

|------------------------------------------------|--------------------------|------|----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                |                          | Min. | Тур.     | Max. |      |                                                                                                                                                                                                        |         |

| Linear current monitor C                       | SO1, CSO2                |      | <u>'</u> | 1    |      |                                                                                                                                                                                                        |         |

| Current monitor factor $I_{\rm Q}/I_{\rm CSO}$ | F <sub>IQ/ICSO 1,2</sub> | 194  | 200      | 206  | -    | $^{1)}$ $T_{\rm j}$ = -40°C to 125°C;<br>5.5 V $\leq$ $V_{\rm l} \leq$ 16 V; 3 V $\leq$ $V_{\rm Q1,2} \leq$ 15 V;<br>$V_{\rm l} > V_{\rm Q1,2} + 0.5$ V;<br>100 mA $\leq$ $I_{\rm Q1,2} \leq$ 300 mA   | P_7.1.1 |

| Current monitor factor $I_{\rm Q}/I_{\rm CSO}$ | F <sub>IQ/ICSO 1,2</sub> | 190  | 200      | 210  | _    | $T_{\rm j}$ = -40°C to 125°C;<br>5.5 V $\leq$ $V_{\rm l}$ $\leq$ 16 V;<br>3 V $\leq$ $V_{\rm Q1,2}$ $\leq$ 15 V;<br>$V_{\rm l}$ > $V_{\rm Q1,2}$ + 0.5 V;<br>40 mA $\leq$ $I_{\rm Q1,2}$ $\leq$ 100 mA | P_7.1.2 |

| Current monitor factor $I_{\rm Q}/I_{\rm CSO}$ | F <sub>IQ/ICSO 1,2</sub> | 190  | 200      | 210  | _    | $T_{\rm j}$ = -40°C to 125°C;<br>5.5 V ≤ $V_{\rm l}$ ≤ 16 V;<br>3 V ≤ $V_{\rm Q1,2}$ ≤ 15 V;<br>$V_{\rm l}$ > $V_{\rm Q1,2}$ + 0.5 V;<br>5 mA ≤ $I_{\rm Q1,2}$ ≤ 40 mA                                 | P_7.1.3 |

| Current monitor factor $I_{\rm Q}/I_{\rm CSO}$ | F <sub>IQ/ICSO 1,2</sub> | 176  | 200      | 224  | -    | $T_{j}$ = -40°C to 125°C;<br>5.5 V ≤ $V_{l}$ ≤ 16 V;<br>3 V ≤ $V_{Q1,2}$ ≤ 15 V;<br>$V_{l}$ > $V_{Q1,2}$ + 0.5 V;<br>2 mA ≤ $I_{Q1,2}$ ≤ 5 mA                                                          | P_7.1.4 |

| Current monitor factor $I_{\rm Q}/I_{\rm CSO}$ | F <sub>IQ/ICSO 1,2</sub> | 160  | 200      | 240  | _    | $T_{\rm j}$ = -40°C to 125°C;<br>5.5 V $\leq V_{\rm l} \leq$ 16 V;<br>3 V $\leq V_{\rm Q1,2} \leq$ 15 V;<br>$V_{\rm l} < V_{\rm Q1,2} + 0.5$ V;<br>1 mA $\leq I_{\rm Q1,2} \leq$ 300 mA                | P_7.1.6 |

| CSO current at no load condition               | I <sub>CSO1,2,off</sub>  | -    | -        | 550  | nA   | No load connected at Q1, Q2; $R_{21} = 27 \text{ k}\Omega$ , $R_{22} = 27 \text{ k}\Omega$ ; $V_{Q1,2} = 5 \text{ V}$                                                                                  | P_7.1.7 |

# Dual-channel low drop out linear voltage regulator

# **Current and protection monitor functions**

#### **Table 6 Electrical characteristics: current monitor** (cont'd)

$V_1$  = 13.5 V,  $T_j$  = -40°C to 150°C, all voltages with respect to ground, direction of currents as shown in **Figure 7** "Application diagram" on Page 27 (unless otherwise specified)

| Parameter                                  | Symbol                  |                                         | Value  | ·s                                      | Unit | Note or<br>Test Condition                                                                                                                                                                                                    | Number   |

|--------------------------------------------|-------------------------|-----------------------------------------|--------|-----------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                            |                         | Min.                                    | Тур.   | Max.                                    |      |                                                                                                                                                                                                                              |          |

| Linear current monitor CSO                 | x                       | -                                       | +      |                                         |      |                                                                                                                                                                                                                              | +        |

| CSOx current                               | I <sub>CSOx,off</sub>   | -50                                     | _      | 50                                      | nA   | CSOx set to high impedance                                                                                                                                                                                                   | P_7.1.8  |

| Adjustable current limitation              | on                      |                                         |        | ·                                       |      |                                                                                                                                                                                                                              |          |

| Adjustable current limit                   | I <sub>Qlim1,2</sub>    | 50                                      | _      | 300                                     | mA   | 1) 1.7 kΩ < $R_{CSO1,2}$ < 10.2 kΩ;                                                                                                                                                                                          | P_7.1.9  |

| Adjustable current limit<br>Tolerance      | I <sub>QlimTOL1,2</sub> | -10                                     | -      | 10                                      | %    | $V_{\rm Q1,2} < 0.95 \times V_{\rm Q,nom}$<br>$50 \text{ mA} \le I_{\rm Qlim1,2} \le 300 \text{ mA}$<br>$T_{\rm j} = -40^{\circ}\text{C to } 125^{\circ}\text{C};$<br>$0.95 \times V_{\rm Q,nom} > V_{\rm Q1,2} >$<br>3.0  V | P_7.1.10 |

| Adjustable current limit<br>Tolerance      | I <sub>QlimTOL1,2</sub> | -10                                     | -      | 25                                      | %    | 50 mA $\leq I_{\text{Qlim1,2}} \leq$ 300 mA<br>$T_{\text{j}} = -40^{\circ}\text{C to } 125^{\circ}\text{C};$<br>$0.95 \times V_{\text{Q,nom}} > V_{\text{Q1,2}} > 0 \text{ V}$                                               | P_7.1.11 |

| CSO voltage level<br>Current limitation    | V <sub>CSOlim1,2</sub>  | 2.45                                    | 2.55   | 2.7                                     | V    | $V_{Q1,2} \le 0.95 \times V_{Q,nom}$                                                                                                                                                                                         | P_7.1.12 |

| Output level overvoltage de                | etected CS              | 01, CSO                                 | 2, CSO | (                                       |      |                                                                                                                                                                                                                              |          |

| CSO voltage level<br>Overvoltage detected  | V <sub>CSO,OV1,2</sub>  | 3.05                                    | 3.1    | 3.25                                    | V    | $^{1)}V_{ADJ} > 1.2 \times V_{REF,nom}$                                                                                                                                                                                      | P_7.1.13 |

| Over voltage threshold level               | V <sub>ADJ,OV1,2</sub>  | 1.44 -<br>0.04<br>V <sub>Q1,2,nom</sub> | 1.44   | 1.44 +<br>0.04<br>V <sub>Q1,2,nom</sub> | V    | 1)                                                                                                                                                                                                                           | P_7.1.14 |

| Output level overtemperate                 | ure detect              | ed CSO1                                 | CSO2,  |                                         | -    |                                                                                                                                                                                                                              |          |

| CSO voltage level overtemperature detected | $V_{\rm CSO,TSD}$       | 2.75                                    | 2.8    | 3                                       | V    | <sup>2)</sup> 151°C < T <sub>j</sub> < 180°C                                                                                                                                                                                 | P_7.1.15 |

| Status output signal ST1, S                | Т2                      | 1                                       |        |                                         | -    |                                                                                                                                                                                                                              | II.      |

| Status output digital signal "low" voltage | V <sub>ST1,2,low</sub>  | _                                       | 0.2    | 0.4                                     | V    | I <sub>ST1,2</sub> ≤ 1.8 mA                                                                                                                                                                                                  | P_7.1.16 |

| Status output digital signal sink current  | I <sub>ST1,2</sub>      | -                                       | -      | 1.8                                     | mA   | -                                                                                                                                                                                                                            | P_7.1.17 |

| CSOxSel                                    |                         |                                         |        |                                         |      |                                                                                                                                                                                                                              |          |

| CSOxSel digital signal "low" voltage       | $V_{CSOxSel,L}$         | _                                       | -      | 0.8                                     | V    | Sets CSOx to CSO1                                                                                                                                                                                                            | P_7.1.18 |

| CSOxSel digital signal third state         | $V_{CSOxSel,T}$         | 1.1                                     | -      | 1.7                                     | V    | Sets CSOx to high impedance                                                                                                                                                                                                  | P_7.1.19 |

| CSOxSel digital signal "high" voltage      | $V_{\rm CSOxSel,H}$     | 2                                       | -      | -                                       | V    | Sets CSOx to CSO2                                                                                                                                                                                                            | P_7.1.20 |

- 1) Referring to the device tolerance only, the tolerance of the external components can cause additional deviation.

- 2) Not subject to production test, specified by design.

# Dual-channel low drop out linear voltage regulator

**Current and protection monitor functions**

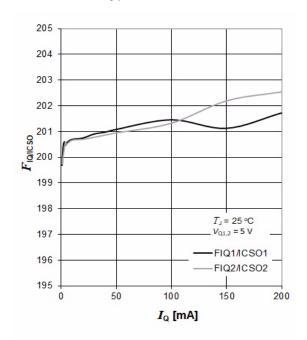

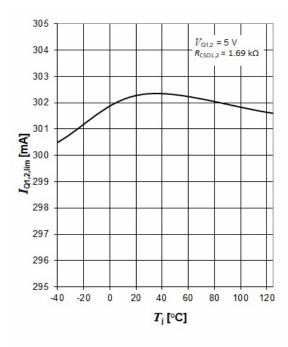

# 6.7 Typical performance characteristics current monitor

# Current monitor factor $F_{\rm IQ/ICSO~1,2,x}$ versus output current $I_{\rm Q1,2}$

# External current limitation $I_{Q, lim1, 2}$ versus junction temperature $T_i$

# Dual-channel low drop out linear voltage regulator

**Enable**

#### 7 **Enable**

#### 7.1 **Functional description enable**

Each outputs of the device Q1, Q2 can be switched on or switched off individually via EN1, EN2 input respectively. By applying voltage levels within  $V_{\rm EN1,2,high}$  applied to the EN1 and EN2 inputs the device switches on completely. A voltage level of  $V_{\rm EN1,2,low}$  applied to the EN1 and EN2 inputs sets the device to low quiescent current mode. In this state the device is switched off and is not functional. The enable input has a hysteresis to avoid toggling between on-state and off-state due to signals with slow slope at the input. The enable input pins EN1 and EN2 provide separate internal pull-down resistors.

#### **Electrical characteristics enable** 7.2

#### Table 7 **Electrical characteristics: enable**

$V_1 = 13.5 \text{ V}$ ,  $T_1 = -40 ^{\circ}\text{C}$  to 150  $^{\circ}\text{C}$ , all voltages with respect to ground, direction of currents as shown in Figure 7 "Application diagram" on Page 27 (unless otherwise specified)

| Parameter                          | Symbol                  | Values |      |      | Unit | Note or Test Condition                                                                                                                                                                                                              | Number  |

|------------------------------------|-------------------------|--------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                    |                         | Min.   | Тур. | Max. |      |                                                                                                                                                                                                                                     |         |

| Enable "low" signal valid          | V <sub>EN1,2,low</sub>  | -      | _    | 0.8  | ٧    | -                                                                                                                                                                                                                                   | P_8.2.1 |

| Enable "high" signal valid         | V <sub>EN1,2,high</sub> | 2      | _    | _    | V    | See also startup time P_8.2.7                                                                                                                                                                                                       | P_8.2.2 |

| Enable threshold<br>hysteresis     | V <sub>EN1,2,hyst</sub> |        | -    | _    | mV   | -                                                                                                                                                                                                                                   | P_8.2.3 |

| Enable input current               | I <sub>EN1,2,high</sub> | _      | _    | 5.3  | μΑ   | V <sub>EN1,2</sub> = 5 V                                                                                                                                                                                                            | P_8.2.4 |

| Enable input current               | I <sub>EN1,2,high</sub> | -      | _    | 20   | μΑ   | V <sub>EN1,2</sub> < 18 V                                                                                                                                                                                                           | P_8.2.5 |

| Enable internal pull-down resistor | R <sub>EN1,2</sub>      | 0.94   | 1.5  | 9    | МΩ   | V <sub>EN1,2</sub> < 5 V                                                                                                                                                                                                            | P_8.2.6 |

| Startup time                       | t <sub>EN1,2</sub>      | -      | 1    | -    | ms   | $C_{\rm Q1,2}$ = 1 µF; $V_{\rm Q1,2,nom}$ = 5 V;<br>$I_{\rm Q1,2,load}$ = 150 mA;<br>$R_{\rm CSO1,2}$ = 2.83 k $\Omega$ ;<br>time from $V_{\rm EN}$ > 2 V;<br>(0 V to 5 V transition) until $V_{\rm Q}$ = 90%<br>of $V_{\rm Q,nom}$ | P_8.2.7 |

**Application information**

# 8 Application information

Note:

The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

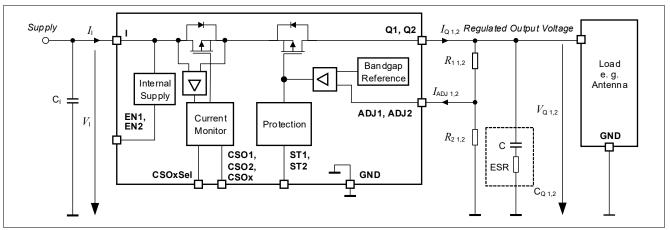

# 8.1 Application diagram

Figure 7 Application diagram

Figure 8 Application diagram

# Dual-channel low drop out linear voltage regulator

**Application information**

### 8.2 Selection of external components

# 8.2.1 Input pin

**Figure 7** shows the typical input circuitry for a linear voltage regulator.

A ceramic capacitor at the input, in the range of 100 nF to 470 nF, is recommended to filter out the high frequency disturbances imposed by the line for example ISO pulses 3a/b. This capacitor must be placed very close to the input pin of the linear voltage regulator on the PCB.

An aluminum electrolytic capacitor in the range of  $10\,\mu\text{F}$  to  $470\,\mu\text{F}$  is recommended as an input buffer to smooth out high energy pulses, such as ISO pulse 2a. This capacitor should be placed close to the input pin of the linear voltage regulator on the PCB.

An overvoltage suppressor diode can be used to further suppress any high voltage beyond the maximum rating of the linear voltage regulator and protect the device against damage due to overvoltage above 45 V.

The external components at the input are not mandatory for the operation of the voltage regulator, but they are recommended in order to protect the voltage regulator against external disturbances and damages.

### 8.2.2 Output pin

An output capacitor is mandatory for the stability of linear voltage regulators.

For the requirements for the output capacitor see Functional range.

The device is designed to be stable with extremely low ESR capacitors. According to the automotive requirements, ceramic capacitors with X5R or X7R dielectrics are recommended.

The output capacitor should be placed as close as possible to the regulator output and GND pins and on the same side of the PCB as the regulator.

In case of rapid transients of input voltage or load current, the capacitance should be dimensioned in accordance and verified in the real application in order to fulfill the output stability requirements.

### 8.3 Thermal considerations

From the input voltage, the output voltage and the load profile of the application, the total power dissipation can be calculated:

$$P_{\rm D} = (V_{\rm I} - V_{\rm O1}) \times I_{\rm O1} + (V_{\rm I} - V_{\rm O2}) \times I_{\rm O2} + V_{\rm I} \times (I_{\rm o1} + I_{\rm o2}) \tag{8.1}$$

with

- P<sub>D</sub>: continuous power dissipation

- V<sub>I</sub>: input voltage

- $V_{01}$ ,  $V_{02}$ : output voltage

- I<sub>O1</sub>, I<sub>O2</sub>:output current

- I<sub>a1</sub>, I<sub>a2</sub>: quiescent current

# Dual-channel low drop out linear voltage regulator

### **Application information**

The maximum acceptable thermal resistance  $R_{th,IA}$  can then be calculated:

$$R_{\text{thJA,max}} = \left(T_{\text{j,max}} - T_{\text{a}}\right) / P_{\text{D}} \tag{8.2}$$

with

- T<sub>i,max</sub>: maximum allowed junction temperature

- T<sub>a</sub>: ambient temperature

Based on the above calculation the proper PCB type and the necessary heat sink area can be determined with reference to the specification in **Thermal resistance**.

### **Example**

Application conditions:

$$V_{\rm I}$$

= 13.5 V

$$V_{01} = 5 \text{ V}$$

$I_{01} = 50 \text{ mA}$

$$V_{02} = 5 \text{ V}$$

$$I_{02} = 50 \text{ mA}$$

$$T_a = 85^{\circ} \text{C}$$

Calculation of  $R_{thJA,max}$ :

$$\begin{split} P_{\rm D} &= (V_{\rm I} - V_{\rm Q1}) \times I_{\rm Q1} + (V_{\rm I} - V_{\rm Q2}) \times I_{\rm Q2} + V_{\rm I} \times (I_{\rm q1} + I_{\rm q2}) \\ &= (13.5 \, {\rm V} - 5 \, {\rm V}) \times 50 \, {\rm mA} + (13.5 \, {\rm V} - 5 \, {\rm V}) \times 50 \, {\rm mA} + 13.5 \, {\rm V} \times (1.5 \, {\rm mA}) \\ &= 0.850 \, {\rm W} + 0.021 \, {\rm W} \\ &= 0.871 \, {\rm W} \\ R_{\rm thJA,max} &= (T_{\rm j,max} - T_{\rm a}) \, / \, P_{\rm D} \\ &= (150^{\circ}{\rm C} - 85^{\circ}{\rm C}) \, / \, 0.871 \, {\rm W} = 74.62 \, {\rm K/W} \end{split}$$

As a result, the PCB design must ensure a thermal resistance  $R_{\rm thJA}$  lower than 74.62 K/W. According to **Thermal resistance**, at least 300 mm<sup>2</sup> heatsink area is necessary on the FR4 1s0p PCB, or the FR4 2s2p board can be used.

#### 8.4 Reverse polarity protection

The device is self protected against reverse polarity faults and allows negative supply voltage. An external reverse polarity diode is not needed. However, the **Absolute maximum ratings** of the device must be maintained.

Reverse voltage causes several small currents to flow into the IC the increase its junction temperature.

Application design must consider that the thermal shut down circuitry does not work in reverse polarity condition.

# 8.5 Further application information

For further information you may contact <a href="http://www.infineon.com/">http://www.infineon.com/</a>

**Package information**

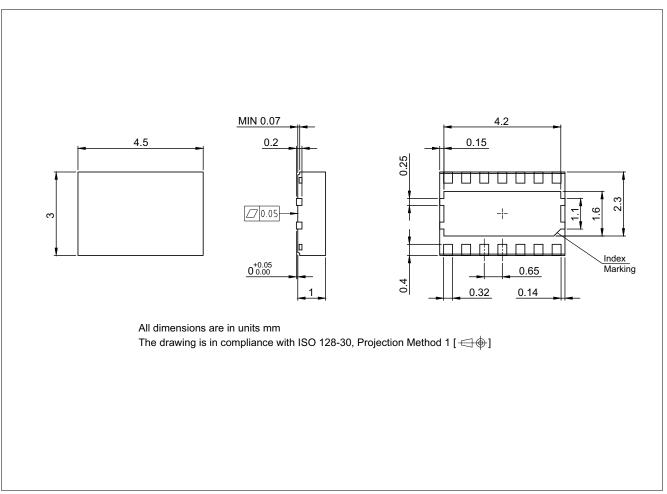

# 9 Package information

Figure 9 PG-TSON-14

# **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

# Dual-channel low drop out linear voltage regulator

**Revision history**

# 10 Revision history

| Revision | Date       | Changes           |  |  |

|----------|------------|-------------------|--|--|

| 1.0      | 2020-11-11 | Datasheet created |  |  |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2020-11-11 Published by Infineon Technologies AG 81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com

Document reference Z8F66321558

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LDO Voltage Regulators category:

Click to view products by Infineon manufacturer:

Other Similar products are found below:

AP7363-SP-13 NCV8664CST33T3G L79M05TL-E AP7362-HA-7 PT7M8202B12TA5EX TCR3DF185,LM(CT TLF4949EJ

NCP4687DH15T1G NCV8703MX30TCG LP2951CN NCV4269CPD50R2G AP7315-25W5-7 NCV47411PAAJR2G AP2111H-1.2TRG1

ZLDO1117QK50TC AZ1117ID-ADJTRG1 NCV4263-2CPD50R2G NCP706ABMX300TAG NCP114BMX075TCG MC33269T-3.5G

TLE4471GXT AP7315-33SA-7 NCV4266-2CST33T3G NCP715SQ15T2G NCV8623MN-50R2G NCV563SQ18T1G NCV8664CDT33RKG

NCV4299CD250R2G NCP715MX30TBG NCV8702MX25TCG TLE7270-2E NCV562SQ25T1G AP2213D-3.3TRG1 AP2202K-2.6TRE1

NCV8170BMX300TCG NCV8152MX300180TCG NCP700CMT45TBG AP7315-33W5-7 NCP154MX180300TAG AP2113AMTR-G1

NJW4104U2-33A-TE1 MP2013AGG-5-P NCV8775CDT50RKG NJM2878F3-45-TE1 S-19214B00A-V5T2U7 S-19214B50A-V5T2U7 S

19213B50A-V5T2U7 S-19214BC0A-E8T1U7\*1 S-19213B00A-V5T2U7 S-19213B33A-V5T2U7