# **OPTIREG<sup>™</sup> switcher TLS4125D0EPV50**

# 2.8 MHz synchronous step down regulator

# Features

- 2.5 A step down regulator

- Input voltage from 3.7 V to 35 V

- 5 V output voltage

- ±1.5% feedback voltage accuracy in PWM mode

- Ultra low current consumption 31 μA

- Integrated high side and low side power MOSFETs

- Peak current mode PWM regulation

- Light load PFM mode with improved efficiency

- Switching frequency range: 320 kHz to 560 kHz or 1.6 MHz to 2.8 MHz

- 100% duty cycle operation

- Synchronization input

- Spread spectrum frequency modulation for improved EMI performance

- Soft-start function

- Integrated compensation network

- Output discharge function in disabled state

- Ultra low current consumption in disabled state (typically 1 μA)

- Undervoltage monitoring

- Overvoltage monitoring

- Overcurrent protection and overload protection

- Input undervoltage shutdown

- Wide temperature range T<sub>i</sub> = -40°C to 150°C

- Green Product (RoHS compliant)

# **Potential applications**

- Body

- ADAS

- Infotainment, telematics

- Navigation

# **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

### Description

# Description

The OPTIREG<sup>™</sup> switcher TLS4125D0EPV50 is a 2.8 MHz synchronous step down regulator especially designed for automotive applications. The device has a current capability of 2.5 A, fixed 5 V output voltage and a feedback voltage accuracy of ±1.5% in PWM mode. The integrated power stages, soft-start feature and integrated compensation network reduce the required amount of external components and thus system costs and board space. The wide input voltage range and a 100% duty cycle operation mode make the device suitable for battery cranking scenarios in automotive applications. The wide switching frequency range allows the selection of appropriate coils and capacitors. The switching frequency can be synchronized to an external clock signal. Spread spectrum frequency modulation can be activated to improve the EMI performance in PWM operation. The device offers low current consumption in PFM mode at light loads to optimize efficiency. The TLS4125D0EPV50 can detect undervoltage and overvoltage conditions of the output voltage and indicates this with the reset output signal. Overcurrent and overload protections avoid excessive current to protect the device during short circuit conditions at the buck converter output. The integrated thermal shutdown feature protects the device from overheating. The enhanced PG-TSDSO-14 exposed pad package offers advantageous thermal performance in the application.

| Туре           | Package     | Marking  |

|----------------|-------------|----------|

| TLS4125D0EPV50 | PG-TSDSO-14 | 4125D0V5 |

# Table of contents

# Table of contents

|         | Features                                                     |

|---------|--------------------------------------------------------------|

|         | Potential applications                                       |

|         | Product validation                                           |

|         | <b>Description</b>                                           |

|         | Table of contents    3                                       |

| 1       | Block diagram                                                |

| 2       | Pin configuration                                            |

| 2.1     | Pin assignment                                               |

| 2.2     | Pin definitions and functions                                |

| 3       | General product characteristics                              |

| 3.1     | Absolute maximum ratings                                     |

| 3.2     | Functional range                                             |

| 3.3     | Thermal resistance                                           |

| 4       | Buck regulator                                               |

| 4.1     | Functional description buck regulator                        |

| 4.1.1   | Regulation loop and operation modes                          |

| 4.1.1.1 | PWM (Pulse Width Modulation) mode 11                         |

| 4.1.1.2 | PFM (Pulse Frequency Modulation) mode12                      |

| 4.1.1.3 | Continuous conduction mode and discontinuous conduction mode |

| 4.1.1.4 | High duty cycle operation                                    |

| 4.1.2   | Power-up and power-down control14                            |

| 4.1.2.1 | Startup procedure with soft-start 14                         |

| 4.1.2.2 | Active output discharge                                      |

| 4.1.3   | Protection features                                          |

| 4.1.3.1 | Overcurrent protection and overload protection15             |

| 4.1.3.2 | Input undervoltage shutdown 15                               |

| 4.1.3.3 | Overtemperature protection15                                 |

| 4.2     | Electrical characteristics buck regulator    16              |

| 4.3     | Typical performance characteristics buck regulator    18     |

| 5       | <b>Oscillator</b>                                            |

| 5.1     | Functional description oscillator23                          |

| 5.1.1   | Synchronization input                                        |

| 5.1.2   | Spread spectrum                                              |

| 5.2     | Electrical characteristics oscillator    24                  |

| 5.3     | Typical performance characteristics oscillator    26         |

| 6       | Current consumption and enable                               |

# Table of contents

| 6.1<br>6.2<br>6.3             | Functional description current consumption and enable       27         Electrical characteristics current consumption and enable       27         Typical performance characteristics current consumption and enable       28 |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>7</b><br>7.1<br>7.2<br>7.3 | Reset29Functional description reset29Electrical characteristics reset31Typical performance characteristics reset33                                                                                                            |

| <b>8</b><br>8.1<br>8.2        | Application information34Layout recommendations36Additional information36                                                                                                                                                     |

| 9                             | Package information    37      Revision history    38      Disclaimer    39                                                                                                                                                   |

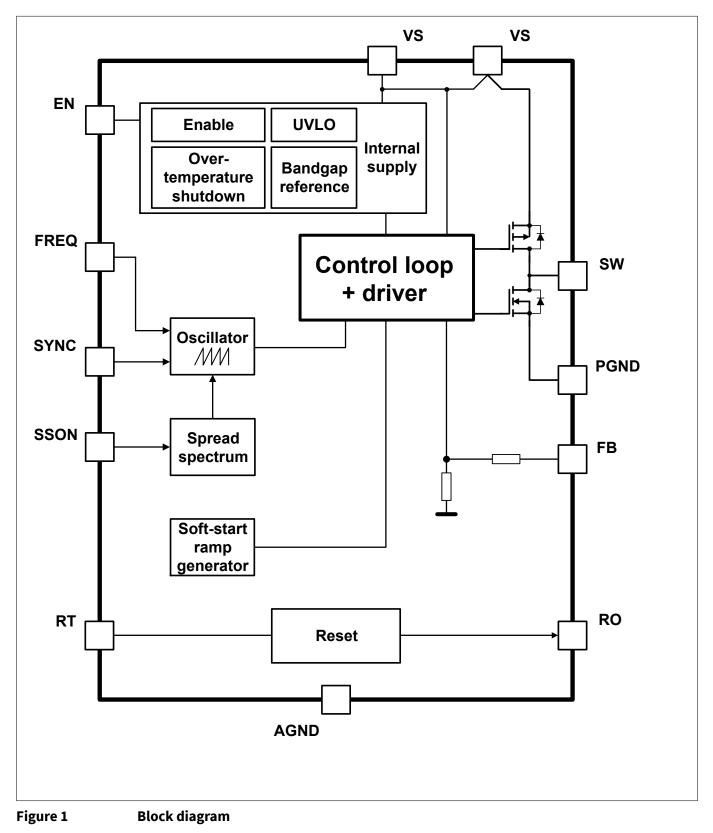

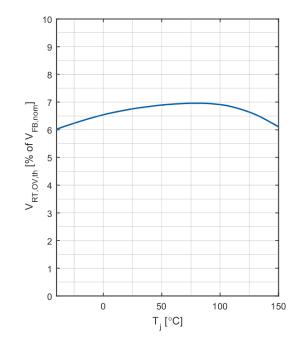

### Block diagram

Pin configuration

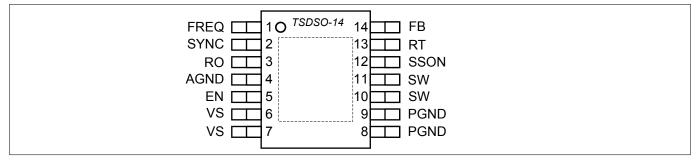

# 2 Pin configuration

# 2.1 Pin assignment

### Figure 2 Pin configuration

# 2.2 Pin definitions and functions

| Pin    | Symbol | Function                                                                                                |

|--------|--------|---------------------------------------------------------------------------------------------------------|

| 1      | FREQ   | Frequency selection input:                                                                              |

|        |        | Connect this pin to GND via resistor for frequency selection.                                           |

|        |        | Leave this pin open to set the default high switching frequency.                                        |

|        |        | Connect this pin to GND to set the default low switching frequency.                                     |

| 2      | SYNC   | Synchronization input:                                                                                  |

|        |        | Connect this pin to external clock to synchronize the switching frequency.                              |

|        |        | If this pin is not used, then connect it to GND.                                                        |

| 3      | RO     | Reset output:                                                                                           |

|        |        | Open drain reset output. Provides the reset output signal.                                              |

|        |        | If the reset feature is used, then connect this pin via external resistor to $V_{CC}$ or to an external |

|        |        | pull-up voltage.                                                                                        |

|        |        | If the reset feature is not used, then leave this pin open.                                             |

| 4      | AGND   | Analog ground:                                                                                          |

|        |        | Connect this pin to GND using a low inductive, broad PCB trace.                                         |

| 5      | EN     | Enable input:                                                                                           |

|        |        | This pin has an integrated pull-down resistor.                                                          |

|        |        | "High" enables the device.                                                                              |

|        |        | "Low" disables the device.                                                                              |

| 6,7    | VS     | Supply voltage input:                                                                                   |

|        |        | Connect this pin to supply voltage.                                                                     |

|        |        | Short pins 6 and 7 at the PCB.                                                                          |

| 8,9    | PGND   | Power ground:                                                                                           |

|        |        | Connect this pin directly to GND using a low inductive, broad PCB trace.                                |

|        |        | Short pins 8 and 9 at the PCB.                                                                          |

| 10, 11 | SW     | Regulator switch node:                                                                                  |

# Pin configuration

| Pin | Symbol         | Function                                                                                                                                            |

|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                | Connect this pin to the buck converter power inductor.                                                                                              |

|     |                | Short pins 10 and 11 at the PCB.                                                                                                                    |

| 12  | SSON           | Spread spectrum enable input:                                                                                                                       |

|     |                | This pin has an integrated pull-down resistor.                                                                                                      |

|     |                | "High" enables spread spectrum.                                                                                                                     |

|     |                | "Low" disables spread spectrum.                                                                                                                     |

| 13  | RT             | Reset configuration input:                                                                                                                          |

|     |                | Connect this pin via a resistor to GND to adjust the reset delay time and the reset undervoltage threshold.                                         |

|     |                | Connect this pin to GND, if the reset function is not needed or to configure the default reset delay time and default undervoltage reset threshold. |

| 14  | FB             | Feedback input:                                                                                                                                     |

|     |                | Feedback input to the regulator. Connect this pin directly to the output capacitor of the buck converter.                                           |

| -   | Exposed<br>pad | Connect the exposed pad to a heatsink area and to GND with low inductive and broad PCB trace.                                                       |

**General product characteristics**

# 3 General product characteristics

### 3.1 Absolute maximum ratings

### Table 1Absolute maximum ratings1)

$T_i = -40^{\circ}$ C to 150°C; all voltages with respect to ground (unless otherwise specified)

| Parameter                    | Symbol                            |                | Valu                  | es  | Unit                                                                  | Note or                                            | Number   |

|------------------------------|-----------------------------------|----------------|-----------------------|-----|-----------------------------------------------------------------------|----------------------------------------------------|----------|

|                              |                                   | Min. Typ. Max. |                       |     | condition                                                             |                                                    |          |

| Voltages                     |                                   |                | 1                     |     |                                                                       |                                                    |          |

| Enable input                 | V <sub>EN</sub>                   | -20            | -                     | 35  | V                                                                     | -                                                  | P_3.1.1  |

| Enable input                 | V <sub>EN,dyn</sub>               | -20            | -                     | 42  | V                                                                     | <sup>2)</sup> Transients<br>present on this<br>pin | P_3.1.2  |

| Synchronization input        | V <sub>SYNC</sub>                 | -0.3           | -                     | 6   | V                                                                     | -                                                  | P_3.1.3  |

| Spread spectrum enable input | V <sub>SSON</sub>                 | -0.3           | -                     | 6   | V                                                                     | -                                                  | P_3.1.4  |

| Frequency selection          | V <sub>FREQ</sub>                 | -0.3           | -                     | 6   | V                                                                     | -                                                  | P_3.1.5  |

| Reset output                 | V <sub>RO</sub>                   | -0.3           | -                     | 6   | V                                                                     | -                                                  | P_3.1.6  |

| Reset configuration          | V <sub>RT</sub>                   | -0.3           | -                     | 6   | V                                                                     | -                                                  | P_3.1.7  |

| Feedback input               | V <sub>FB</sub>                   | -0.3           | -                     | 7   | V                                                                     | -                                                  | P_3.1.8  |

| Buck switch output           | tch output V <sub>SW</sub> -0.3 – |                | V <sub>VS</sub> + 0.3 | V   | Minimum -2.0 V<br>in transient<br>condition (single<br>event < 15 ns) | P_3.1.9                                            |          |

| Supply voltage input         | V <sub>VS</sub>                   | -0.3           | -                     | 35  | V                                                                     | -                                                  | P_3.1.10 |

| Supply voltage input         | V <sub>VS,dyn</sub>               | -0.3           | -                     | 42  | V                                                                     | <sup>2)</sup> Transients<br>present on this<br>pin | P_3.1.11 |

| Power GND                    | V <sub>PGND</sub>                 | -0.3           | -                     | 0.3 | V                                                                     | -                                                  | P_3.1.12 |

| Analog GND                   | V <sub>AGND</sub>                 | -0.3           | -                     | 0.3 | V                                                                     | -                                                  | P_3.1.13 |

| Temperatures                 |                                   |                |                       |     |                                                                       |                                                    |          |

| Junction temperature         | Tj                                | -40            | -                     | 150 | °C                                                                    | -                                                  | P_3.1.14 |

| Storage temperature          | T <sub>stg</sub>                  | -55            | -                     | 150 | °C                                                                    | -                                                  | P_3.1.15 |

| ESD susceptibility           |                                   |                |                       |     |                                                                       |                                                    |          |

| ESD susceptibility to GND    | V <sub>ESD,HBM</sub>              | -2             | -                     | 2   | kV                                                                    | <sup>3)</sup> HBM                                  | P_3.1.16 |

| ESD susceptibility to GND    | V <sub>ESD,CDM</sub>              | -500           | -                     | 500 | V                                                                     | <sup>4)</sup> CDM                                  | P_3.1.17 |

<sup>&</sup>lt;sup>1</sup> Not subject to production test, specified by design.

<sup>&</sup>lt;sup>2</sup> Transients between 35 V and 42 V can be tolerated for a total lifetime duration shorter than 48 s.

<sup>&</sup>lt;sup>3</sup> ESD susceptibility, Human Body Model (HBM) according to ANSI/ESDA/JEDEC JS-001 (1.5 kΩ, 100 pF).

<sup>&</sup>lt;sup>4</sup> ESD susceptibility, Charged Device Model (CDM) according to JEDEC JESD22-C101.

### **General product characteristics**

### Table 1 Absolute maximum ratings<sup>1)</sup> (continued)

$T_i = -40^{\circ}$ C to 150°C; all voltages with respect to ground (unless otherwise specified)

| Parameter                                            | Symbol                 |      | Valu | es   | Unit |                   | Number   |  |

|------------------------------------------------------|------------------------|------|------|------|------|-------------------|----------|--|

|                                                      |                        | Min. | Тур. | Max. |      | condition         |          |  |

| ESD susceptibility corner pins 1, 7, 8,<br>14 to GND | V <sub>ESD,CDM,C</sub> | -750 | -    | 750  | V    | <sup>4)</sup> CDM | P_3.1.18 |  |

Notes:

**1.** Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

**2.** Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as outside the normal operating range. Protection functions are not designed for continuous repetitive operation.

### 3.2 Functional range

### Table 2Functional range

$T_i = -40^{\circ}$ C to 150°C; all voltages with respect to ground (unless otherwise specified)

| Parameter                 | Symbol              | ol Values |      | Unit | Note or condition | Number                                                                                   |          |  |

|---------------------------|---------------------|-----------|------|------|-------------------|------------------------------------------------------------------------------------------|----------|--|

|                           |                     | Min.      | Тур. | Max. |                   |                                                                                          |          |  |

| Supply voltage decreasing | V <sub>VS,dec</sub> | 3.7       | -    | 35   | V                 | <sup>5)</sup> Minimum value<br>represents low<br>battery voltage<br>condition (cranking) | P_3.2.1  |  |

| Supply voltage increasing | V <sub>VS,inc</sub> | 6.0       | -    | 35   | V                 | Minimum value<br>represents startup<br>condition                                         | P_3.2.2  |  |

| Enable input              | V <sub>EN</sub>     | 0         | -    | 35   | V                 | -                                                                                        | P_3.2.3  |  |

| Output voltage            | V <sub>CC</sub>     | -         | 5.0  | -    | V                 | -                                                                                        | P_3.2.5  |  |

| SYNC input voltage        | V <sub>SYNC</sub>   | 0         | -    | 5.2  | V                 | -                                                                                        | P_3.2.8  |  |

| Reset output voltage      | V <sub>RO,hi</sub>  | 0         | -    | 5.2  | V                 | 6)                                                                                       | P_3.2.11 |  |

| Output current            | I <sub>CC</sub>     | 0         | -    | 2.5  | A                 | -                                                                                        | P_3.2.13 |  |

| Junction temperature      | Tj                  | -40       | -    | 150  | °C                | -                                                                                        | P_3.2.15 |  |

<sup>&</sup>lt;sup>1</sup> Not subject to production test, specified by design.

<sup>&</sup>lt;sup>4</sup> ESD susceptibility, Charged Device Model (CDM) according to JEDEC JESD22-C101.

<sup>&</sup>lt;sup>5</sup> With 3.7 V <  $V_{VS}$  < 6 V, a reduced performance of parameter settings applies to feedback voltage accuracy, synchronization and the reset function.

<sup>&</sup>lt;sup>6</sup> Allowed external pull-up voltage applied via pull-up resistance to pin RO.

### **General product characteristics**

*Note:* Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the electrical characteristics table.

### 3.3 Thermal resistance

### Table 3Thermal resistance<sup>7)</sup>

| Parameter           | Symbol              | Values |      |      | Unit | Note or condition                        | Number  |

|---------------------|---------------------|--------|------|------|------|------------------------------------------|---------|

|                     |                     | Min.   | Тур. | Max. |      |                                          |         |

| Junction to case    | R <sub>thJC</sub>   | -      | 8.6  | -    | K/W  | -                                        | P_3.3.1 |

| Junction to ambient | R <sub>thJA,1</sub> | -      | 34   | _    | K/W  | <sup>8)</sup> 2s2p                       | P_3.3.2 |

| Junction to ambient | R <sub>thJA,2</sub> | -      | 45   | -    | K/W  | <sup>9)</sup> 1s0p + 600 mm <sup>2</sup> | P_3.3.3 |

| Junction to ambient | R <sub>thJA,3</sub> | -      | 54   | -    | K/W  | <sup>9)</sup> 1s0p + 300 mm <sup>2</sup> | P_3.3.4 |

| Junction to ambient | R <sub>thJA,4</sub> | -      | 116  | -    | K/W  | <sup>9)</sup> 1s0p footprint             | P_3.3.5 |

*Note:* This thermal data was generated in accordance with JEDEC JESD51 standards. For more information visit **www.jedec.org**.

<sup>&</sup>lt;sup>7</sup> Not subject to production test, specified by design.

<sup>&</sup>lt;sup>8</sup> Specified R<sub>thJA</sub> value is according to JEDEC JESD51-2,-5,-7 at natural convection on FR4 2s2p board; the product (chip and package) was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with two inner copper layers (2 × 70 µm Cu, 2 × 35 µm Cu). Where applicable, a thermal via array next to the package contacted the first inner copper layer.

<sup>&</sup>lt;sup>9</sup> Specified  $R_{thJA}$  value is according to JEDEC JESD 51-3 at natural convection on FR4 1s0p board; the product (IC and package) was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with 1 copper layer (1 × 70  $\mu$ m Cu).

# 4 Buck regulator

# 4.1 Functional description buck regulator

The TLS4125D0EPV50 is a synchronous current mode step down (buck) regulator with selectable switching frequency  $f_{OSC}$ . The device regulates the output voltage in pulse width modulation (PWM) or in pulse frequency modulation (PFM) mode and automatically moves between both modes on load change or input voltage change. At low input voltage conditions, for example during battery cranking, the device can operate at a duty cycle of 100%.

# 4.1.1 Regulation loop and operation modes

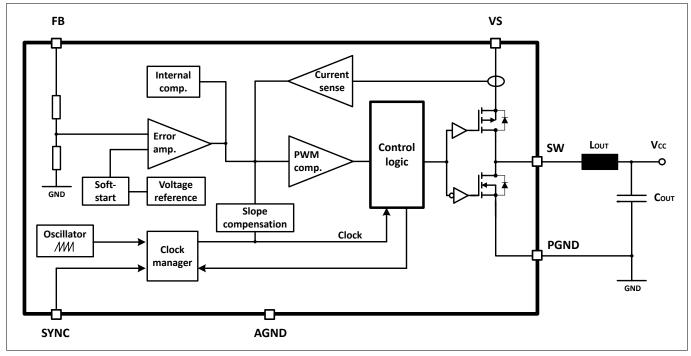

*Figure 3* shows the regulation loop. An internal resistor divider is connected between pin FB and pin AGND to reduce the magnitude of the output voltage signal, which is connected to pin FB. The error amplifier processes the difference between scaled output feedback voltage and internal reference voltage to provide a reference current to the PWM comparator. The PWM comparator compares that reference current to a scaled version of the inductor current to determine the PWM duty cycle that is required for stable output voltage regulation. In PFM mode the error amplifier output signal also serves to modulate the switching frequency.

The control logic supervises the handover between operation modes and triggers the drivers of high side PMOS power stage and the low side NMOS power stage accordingly. For the modes of PWM, PFM and 100% duty cycle operation see *PWM (Pulse Width Modulation) mode, PFM (Pulse Frequency Modulation) mode, Continuous conduction mode* and *High duty cycle operation* respectively.

Functional block diagram buck regulator

# 4.1.1.1 PWM (Pulse Width Modulation) mode

At high load the TLS4125D0EPV50 operates with the configured switching frequency  $f_{OSC}$  in PWM mode. In PWM mode the device modulates the duty cycle to achieve a regulated output voltage. The nominal switching frequency can be set using one of the following methods, see *Oscillator*:

- by an external resistor connected at pin FREQ

- from a synchronization signal applied at the SYNC pin

The pulse width modulation is based on peak current mode detection to achieve a fast reaction time and an optimized feedback accuracy. The PWM comparator processes the current signal detected at the high side power stage as well as the current signals of the slope compensation and the error amplifier to adjust the switching duty cycle to regulate the output voltage accordingly. With a duty cycle above 50% the slope compensation ensures system stability. This is achieved by avoidance of subharmonic oscillations of the output inductor current.

Due to a current sense signal inaccuracy at the beginning of each high side switch conduction phase, a short blanking time is required to mask the output of the current sense before processing it. The blanking time defines the minimum allowed on-time  $t_{on,min}$  of the high side PMOS power stage and therefore the point of transition from PWM to PFM operation.

# 4.1.1.2 PFM (Pulse Frequency Modulation) mode

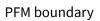

The device can operate at constant on-time  $t_{on,min}$  of the high side PMOS power stage to achieve a stable output voltage at light load or high input voltage conditions. In PFM mode the device operates at a constant on-time and modulates the switching frequency to regulate the output voltage. The switching frequency is lower than in PWM mode. For further information about the PFM boundary condition and the frequency modulation depending on load and on input voltage, see **Typical performance characteristics buck regulator**.

In PFM mode with light load the device offers optimized efficiency with reduced current consumption.

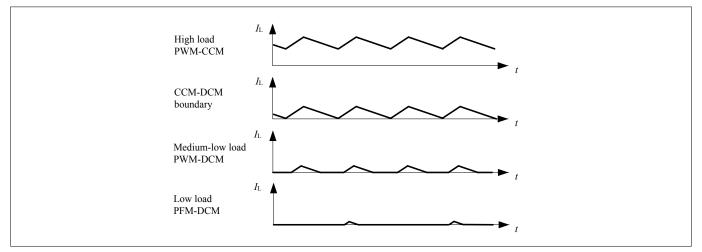

# 4.1.1.3 Continuous conduction mode and discontinuous conduction mode

### Continuous conduction mode (CCM)

The device operates at a continuously rising or falling triangular positive inductor current. The on-time and the switching duty cycle mainly depend on the ratio of output voltage to input voltage.

### Boundary condition for CCM $\rightarrow$ DCM transition

With a decrease of the load current during continuous conduction mode, the minimum valley inductor current can obtain approximately zero, which is the boundary condition for the discontinuous conduction mode. Further reduction of the load current leads to discontinuous conduction mode.

### **Discontinuous conduction mode (DCM)**

The device turns off the low side power stage to avoid a negative inductor current. Further reduction of the load current reduces the on-time and leads to transition from PWM into PFM when obtaining the minimum on-time.

Typical example inductor current waveforms for CCM and DCM

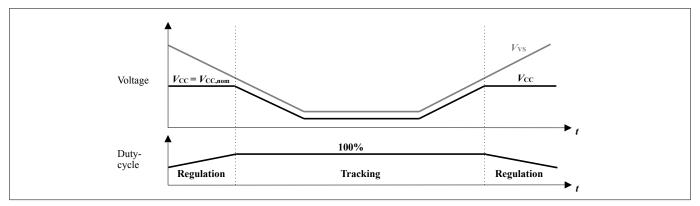

# 4.1.1.4 High duty cycle operation

In 100% duty cycle mode the high side PMOS power stage constantly conducts current. If the input voltage is close to the nominal output voltage or lower, then the device enters this operation mode, see *Figure 5*.

If the input voltage is decreased (for example during a battery cranking scenario) and the device moves from regulation to the 100% duty cycle mode, then the output voltage tracks the input voltage as accurate as possible down to an input voltage  $V_{VS}$  of 3.7 V. During steady state operation, the difference of the output voltage and the tracked input voltage as well as the entry point into 100% duty cycle mainly depend on the voltage drop at the resistance  $R_{on,hs}$  of the high side PMOS power stage, which in turn depends on the load current  $I_{CC}$ . Parasitic elements of external application circuitry and components, such as the output inductor series resistance, increase the voltage drop.

At high duty cycles close to 100%, the loop might not propagate very short off-times and compensates this by skipping switching cycles to ensure a smooth transition to 100% duty cycle with a stable output voltage.

Typical 100% duty cycle mode tracking behavior

### 4.1.2 Power-up and power-down control

The following features of the device control power up and power down, see *Table 4* for electrical characteristics:

- Startup with soft-start

- Active output discharge

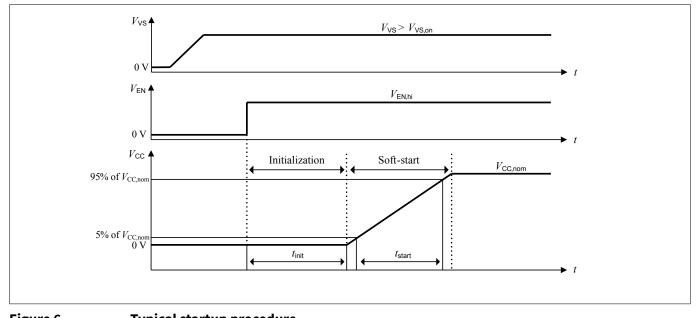

### 4.1.2.1 Startup procedure with soft-start

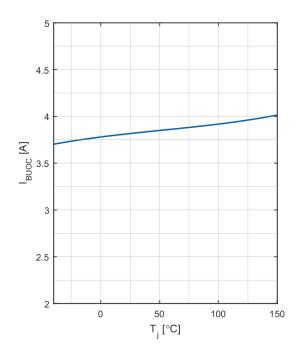

The soft-start function of the TLS4125D0EPV50 controls the ramp-up of the output voltage with defined timing  $t_{\text{start}}$  during startup, see *Figure 6*. If  $V_{\text{VS}} > V_{\text{VS,on}}$ , then a "high" signal  $V_{\text{EN,hi}}$  at pin EN triggers the startup procedure. During startup the internal supply establishes a stable state and the device initializes the switching frequency and the reset function according to the configuration. The regulator then increases the output voltage  $V_{\text{cc}}$  by ramping up the internal voltage reference connected to the error amplifier.

# Figure 6 Typical startup procedure

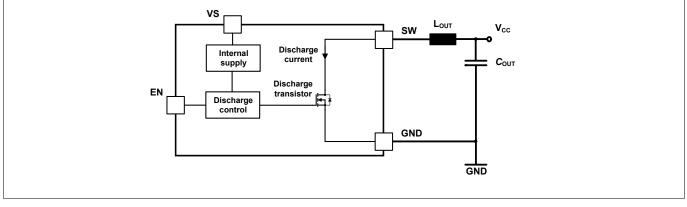

### 4.1.2.2 Active output discharge

The active output discharge function of the TLS4125D0EPV50 controls the ramp-down of the output voltage during power down, see *Figure 7*. If the device detects a "low" signal  $V_{EN,lo}$  at the EN pin, then it switches on the integrated discharge transistor connected to the SW pin in order to discharge the output capacitor  $C_{OUT}$  via the output inductor  $L_{OUT}$ . The typical on-resistance  $R_{dc}$  of the discharge transistor is 55  $\Omega$ .

Figure 7

Active output discharge block diagram

# 4.1.3 Protection features

The device offers features that are designed to protect it from fault events such as overcurrent, overload, input undervoltage and overtemperature, see *Table 4*.

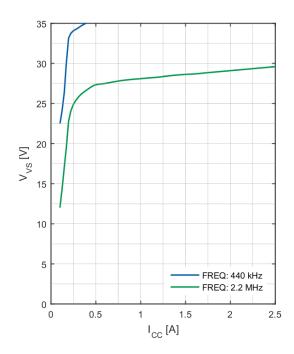

### 4.1.3.1 Overcurrent protection and overload protection

If the sensed current through the high side PMOS power stage exceeds the buck peak overcurrent limit *I*<sub>BUOC</sub> after the blanking time of the current sense, then the device switches off the high side power stage for the remaining time of the current cycle. Active current limitation can decrease the output voltage level.

If the sensed freewheeling current through the low side NMOS power stage exceeds the overload limit  $I_{BUOL}$ , then the device prevents the high side PMOS power stage from switching on in the subsequent clock cycles to avoid overheating. The overload threshold level is set to a higher value than the overcurrent threshold level.

If an overload condition and an undervoltage condition occur for longer than 3 ms typically, then the device detects a short circuit at the output voltage node and shuts down. After a waiting time of typically 1 s, the device restarts with a soft-start.

# 4.1.3.2 Input undervoltage shutdown

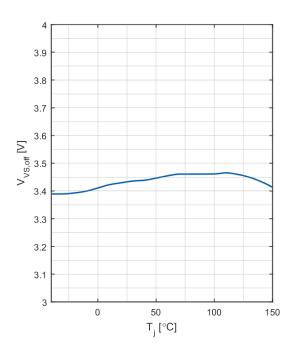

The device incorporates an undervoltage shutdown function. If the input voltage  $V_{VS}$  drops below the input undervoltage shutdown threshold  $V_{VS,off}$ , then the device shuts down.

# 4.1.3.3 Overtemperature protection

The integrated overtemperature protection turns off the device in case of a too high junction temperature. The typical junction thermal shutdown temperature is 175°C. After the device has cooled down by the amount of the typical junction temperature hysteresis 10 K and a subsequent waiting time of typically 1 s, the device restarts with a soft-start to resume normal operation. The thermal shutdown is an integrated protection function to prevent the immediate destruction of the device during fault conditions. However, a junction temperature above 150°C is outside of the maximum ratings and reduces the lifetime of the device.

# 4.2 Electrical characteristics buck regulator

### Table 4 Electrical characteristics buck regulator

$V_{VS}$  = 6 V to 35 V;  $T_i$  = -40°C to 150°C; all voltages with respect to ground (unless otherwise specified)

| Parameter                          | Symbol                 |      | Values | ;    | Unit | Note or condition                                                                                    | Number   |  |

|------------------------------------|------------------------|------|--------|------|------|------------------------------------------------------------------------------------------------------|----------|--|

|                                    |                        | Min. | Тур.   | Max. | -    |                                                                                                      |          |  |

| Feedback voltage accuracy          |                        | 1    | 1      |      | 1    |                                                                                                      | 1        |  |

| Feedback voltage accuracy          | V <sub>FB,PWM</sub>    | -1.5 | -      | +1.5 | %    | 6 V ≤ V <sub>VS</sub> ≤ 35 V;<br>PWM mode                                                            | P_4.2.1  |  |

| Feedback voltage accuracy          | V <sub>FB,PFM,1</sub>  | -2   | -      | +3.5 | %    | 6 V ≤ V <sub>VS</sub> ≤ 35 V;<br>PFM mode                                                            | P_4.2.2  |  |

| Feedback voltage V <sub>FB</sub>   | V <sub>FB</sub>        | -    | 5      | -    | V    | -                                                                                                    | P_4.2.3  |  |

| MOSFETs                            |                        |      |        |      |      |                                                                                                      |          |  |

| High side MOSFET on-<br>resistance | R <sub>on,hs</sub>     | -    | 120    | 240  | mΩ   | / <sub>CC</sub> = 100 mA                                                                             | P_4.2.7  |  |

| Low side MOSFET on-<br>resistance  | R <sub>on,ls</sub>     | -    | 70     | 150  | mΩ   | / <sub>CC</sub> = 100 mA                                                                             | P_4.2.9  |  |

| Regulation loop                    |                        |      |        |      |      |                                                                                                      | _        |  |

| Maximum duty cycle                 | D <sub>max</sub>       | -    | -      | 100  | %    | 10)                                                                                                  | P_4.2.11 |  |

| Minimum on-time,<br>high frequency | t <sub>on,min,hf</sub> | _    | 78     | -    | ns   | <ul> <li><i>I</i><sub>CC</sub> = 1.5 A;</li> <li>valid for high frequency operation range</li> </ul> | P_4.2.12 |  |

| Minimum on-time,<br>low frequency  | t <sub>on,min,lf</sub> | -    | 308    | -    | ns   | <ul> <li><i>I</i><sub>CC</sub> = 1.5 A;</li> <li>valid for low frequency operation range</li> </ul>  | P_4.2.13 |  |

| Startup and active discharge       | 12)                    | 1    | 1      | 1    | 1    |                                                                                                      | I        |  |

| Soft-start time                    | t <sub>start</sub>     | 0.8  | 1      | 1.2  | ms   | V <sub>CC</sub> rising from 5% to 95% of nominal V <sub>CC</sub> level                               | P_4.2.14 |  |

| Startup initialization time        | t <sub>init</sub>      | -    | -      | 2.6  | ms   | time from rising edge of V <sub>EN</sub><br>(0 V to V <sub>EN,hi</sub> ) until soft-start            | P_4.2.15 |  |

| Input voltage startup<br>threshold | V <sub>VS,on</sub>     | 2.6  | -      | 6.0  | V    | V <sub>VS</sub> increasing;<br>V <sub>EN</sub> ≥ 2 V                                                 | P_4.2.16 |  |

| Output discharge resistance        | R <sub>dc</sub>        | -    | 55     | -    | Ω    | $V_{EN} = 0 V;$<br>$V_{VS} = 13.5 V;$<br>$V_{SW} = 100 \text{ mV}$                                   | P_4.2.17 |  |

| Current limitation                 |                        |      |        |      |      |                                                                                                      |          |  |

| Buck peak overcurrent limit        | I <sub>BUOC</sub>      | 3.3  | 3.9    | 4.5  | А    | -                                                                                                    | P_4.2.19 |  |

<sup>&</sup>lt;sup>10</sup> See *Functional range* and *High duty cycle operation*.

<sup>&</sup>lt;sup>11</sup> Specified by design, not subject to production test.

<sup>&</sup>lt;sup>12</sup> See *Power-up and power-down control*

### Table 4 Electrical characteristics buck regulator (continued)

$V_{VS}$  = 6 V to 35 V;  $T_i$  = -40°C to 150°C; all voltages with respect to ground (unless otherwise specified)

| Parameter                                 | Symbol                | Values |      |      | Unit | Note or condition                                                                 | Number   |

|-------------------------------------------|-----------------------|--------|------|------|------|-----------------------------------------------------------------------------------|----------|

|                                           |                       | Min.   | Тур. | Max. | -    |                                                                                   |          |

| Overload current limit                    | I <sub>BUOL</sub>     | 3.9    | 4.4  | 5.1  | А    | -                                                                                 | P_4.2.21 |

| Overload overcurrent gap                  | I <sub>BUOL,gap</sub> | 0.05   | 0.5  | -    | A    | Overload current limit is<br>typically 0.5 A above buck<br>peak overcurrent limit | P_4.2.22 |

| Undervoltage shutdown                     |                       |        |      |      |      |                                                                                   |          |

| Input undervoltage shutdown threshold     | V <sub>VS,off</sub>   | 3.3    | -    | 3.55 | V    | V <sub>VS</sub> decreasing                                                        | P_4.2.23 |

| Input undervoltage shutdown<br>hysteresis | V <sub>VS,hys</sub>   | 180    | 280  | 420  | mV   | -                                                                                 | P_4.2.24 |

# 4.3 Typical performance characteristics buck regulator

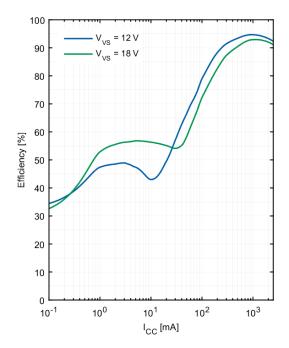

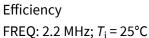

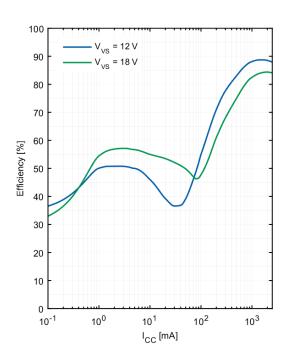

FREQ: 2.2 MHz;  $V_{VS}$  = 13.5 V;  $T_j$  = 25°C (if not otherwise specified). The shown performance characteristics was measured on a 4 layer FR4 printed circuit board with external components as recommended in *Application information*.

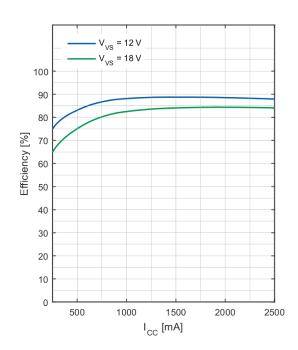

### Efficiency

FREQ: 440 kHz; *T*<sub>i</sub> = 25°C

Efficiency FREQ: 440 kHz; *T*<sub>j</sub> = 25°C

Efficiency FREQ: 2.2 MHz; *T*<sub>i</sub> = 25°C

$I_{CC} = 1 \text{ A}$

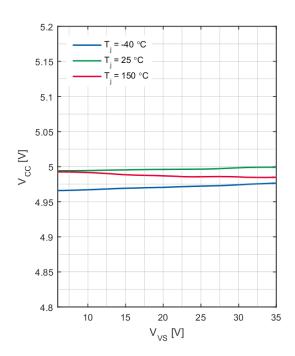

Output voltage precision

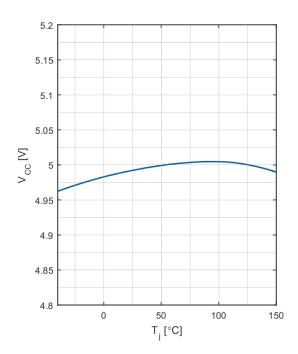

*I*<sub>CC</sub> = 200 mA

Load regulation

*V*<sub>VS</sub> = 13.5 V

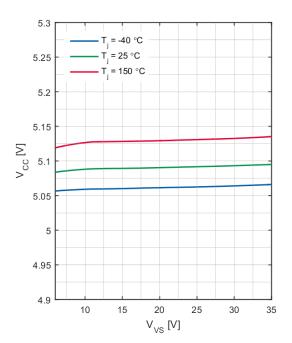

Line regulation (low load)  $I_{CC} = 100 \,\mu\text{A}$

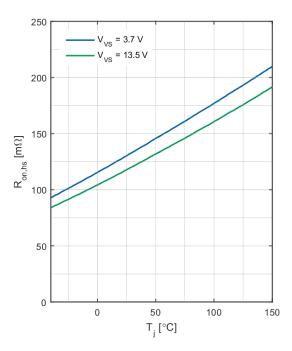

High side MOSFET on-resistance  $I_{CC} = 100 \text{ mA}$

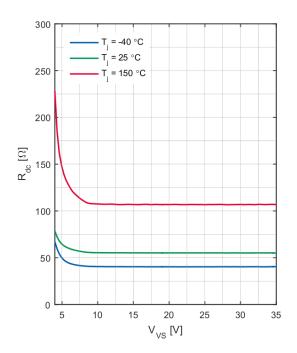

Output discharge resistance  $V_{\text{EN}} = 0 \text{ V}; V_{\text{SW}} = 100 \text{ mV}$

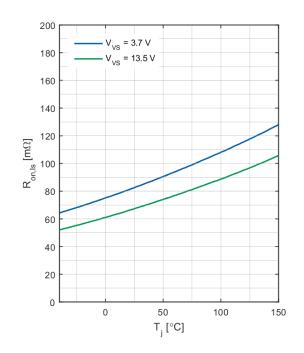

Low side MOSFET on-resistance  $I_{CC} = 100 \text{ mA}$

Input undervoltage shutdown threshold *V*<sub>VS</sub> decreasing

PFM frequency modulation (CCM) FREQ: 440 kHz;  $I_{CC}$  = 1.5 A

PFM frequency modulation (DCM) FREQ: 440 kHz;  $T_i = 25^{\circ}C$

PFM frequency modulation (CCM) FREQ: 2.2 MHz;  $I_{CC}$  = 1.5 A

PFM frequency modulation (DCM) FREQ: 2.2 MHz;  $T_i = 25^{\circ}C$

*T*<sub>j</sub> = 25°C

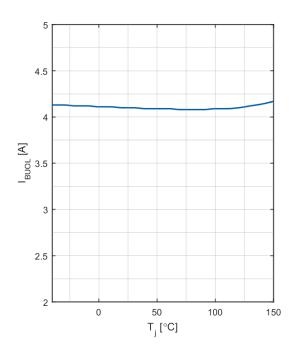

Buck peak overcurrent limit  $V_{VS} = 13.5 V$

Load step response  $I_{CC}$ : 0.6 A to 2 A to 0.6 A

Overload current limit V<sub>VS</sub> = 13.5 V

# 5 Oscillator

# 5.1 Functional description oscillator

The integrated clock provides a constant frequency to the regulation loop. In PWM mode the device switches on and off the high side and low side power stages at the oscillator frequency  $f_{OSC}$ .

The oscillator frequency can be set by connecting a resistor  $R_{FREQ}$  between the FREQ pin and ground, see **Table 5**, **Table 6** and **Table 7**. The device sets the selected switching frequency during startup.

### Table 5 FREQ configuration for typical oscillator frequencies in the low frequency range

| R <sub>FREQ</sub> [kΩ] <sup>13)</sup>       | f <sub>osc</sub> [kHz] |

|---------------------------------------------|------------------------|

| 2.2                                         | 320                    |

| 3.3                                         | 360                    |

| 4.7                                         | 400                    |

| ≤ 1.0 (or connect FREQ pin directly to GND) | 440 <sup>14)</sup>     |

| 6.8                                         | 480                    |

| 10                                          | 520                    |

| 15                                          | 560                    |

Table 6

FREQ configuration for typical oscillator frequencies in the high frequency range

| $R_{FREQ} [k\Omega]^{15}$      | f <sub>OSC</sub> [MHz] |

|--------------------------------|------------------------|

| 22                             | 1.6                    |

| 33                             | 1.8                    |

| 47                             | 2.0                    |

| ≥ 200 (or leave FREQ pin open) | 2.2 <sup>16)</sup>     |

| 68                             | 2.4                    |

| 100                            | 2.6                    |

| 150                            | 2.8                    |

# 5.1.1 Synchronization input

In PWM mode the device can synchronize the switching frequency to an external oscillator connected to the SYNC pin. The internal clock manager triggers at the falling edge of the external signal. The phase shift towards the switching frequency can be adjusted with the duty cycle of the external oscillator. 50% duty cycle of the external oscillator corresponds to a phase shift of approximately zero. A suitable setting of  $R_{FREQ}$  is required so that the internal operation frequency is equal to the corresponding external synchronization frequency or above it. This is a prerequisite for the automatic transitions between PWM mode and PFM mode.

As soon as the startup is completed and the device accepts the external signal at the SYNC pin, the synchronization turns active.

<sup>&</sup>lt;sup>13</sup> Resistor tolerance  $\leq 5\%$ .

<sup>&</sup>lt;sup>14</sup> Default oscillator low frequency.

<sup>&</sup>lt;sup>15</sup> Resistor tolerance  $\leq 5\%$ .

<sup>&</sup>lt;sup>16</sup> Default oscillator high frequency.

### 5.1.2 Spread spectrum

In PWM mode, when used without an external clock at the SYNC pin, the TLS4125D0EPV50 can apply spread spectrum to optimize EMI performance. The device modulates the switching frequency up and down by a triangle waveform with a typical frequency of 8.3 kHz within a range of typically ±7.5% of the selected oscillator frequency. The logical signal on the SSON pin switches spread spectrum on or off.

# 5.2 Electrical characteristics oscillator

### Table 7 Electrical characteristics oscillator

$V_{VS}$  = 6 V to 35 V;  $T_i$  = -40°C to 150°C; all voltages with respect to ground (unless otherwise specified)

| Parameter                                    | Symbol               |      | Values |      | Unit | Note or condition                                                    | Number   |  |

|----------------------------------------------|----------------------|------|--------|------|------|----------------------------------------------------------------------|----------|--|

|                                              |                      | Min. | Тур.   | Max. |      |                                                                      |          |  |

| Frequency setting                            |                      | -    | -      | 1    | -    |                                                                      |          |  |

| Default oscillator low frequency             | f <sub>osc,1</sub>   | 396  | 440    | 484  | kHz  | R <sub>FREQ</sub> ≤ 1.0 kΩ or<br>connect FREQ pin<br>directly to GND | P_5.2.1  |  |

| Default oscillator high frequency            | f <sub>osc,2</sub>   | 1.98 | 2.2    | 2.42 | MHz  | R <sub>FREQ</sub> ≥200 kΩ or<br>leave FREQ pin<br>open               | P_5.2.2  |  |

| Oscillator frequency                         | f <sub>osc,3</sub>   | 288  | 320    | 352  | kHz  | $R_{\rm FREQ} = 2.2  \rm k\Omega$                                    | P_5.2.3  |  |

| Oscillator frequency                         | f <sub>osc,4</sub>   | 324  | 360    | 396  | kHz  | $R_{\rm FREQ} = 3.3  \rm k\Omega$                                    | P_5.2.4  |  |

| Oscillator frequency                         | f <sub>osc,5</sub>   | 360  | 400    | 440  | kHz  | $R_{\rm FREQ} = 4.7  \rm k\Omega$                                    | P_5.2.5  |  |

| Oscillator frequency                         | f <sub>osc,6</sub>   | 432  | 480    | 528  | kHz  | $R_{\rm FREQ} = 6.8  \rm k\Omega$                                    | P_5.2.6  |  |

| Oscillator frequency                         | f <sub>osc,7</sub>   | 468  | 520    | 572  | kHz  | $R_{\rm FREQ} = 10 \ \rm k\Omega$                                    | P_5.2.7  |  |

| Oscillator frequency                         | f <sub>osc,8</sub>   | 504  | 560    | 616  | kHz  | $R_{\rm FREQ} = 15  \rm k\Omega$                                     | P_5.2.8  |  |

| Oscillator frequency                         | f <sub>osc,9</sub>   | 1.44 | 1.6    | 1.76 | MHz  | $R_{\rm FREQ} = 22 \ \rm k\Omega$                                    | P_5.2.9  |  |

| Oscillator frequency                         | f <sub>osc,10</sub>  | 1.62 | 1.8    | 1.98 | MHz  | $R_{\rm FREQ} = 33  \rm k\Omega$                                     | P_5.2.10 |  |

| Oscillator frequency                         | f <sub>osc,11</sub>  | 1.8  | 2.0    | 2.2  | MHz  | $R_{\rm FREQ} = 47 \ \rm k\Omega$                                    | P_5.2.11 |  |

| Oscillator frequency                         | f <sub>osc,12</sub>  | 2.16 | 2.4    | 2.64 | MHz  | $R_{\rm FREQ} = 68 \ \rm k\Omega$                                    | P_5.2.12 |  |

| Oscillator frequency                         | f <sub>osc,13</sub>  | 2.34 | 2.6    | 2.86 | MHz  | $R_{\rm FREQ}$ = 100 k $\Omega$                                      | P_5.2.13 |  |

| Oscillator frequency                         | f <sub>osc,14</sub>  | 2.52 | 2.8    | 3.08 | MHz  | $R_{\rm FREQ}$ = 150 k $\Omega$                                      | P_5.2.14 |  |

| Synchronization input                        |                      |      |        |      |      |                                                                      |          |  |

| Synchronization low frequency capture range  | f <sub>sync,lf</sub> | 320  | -      | 560  | kHz  | <sup>17)</sup> valid for<br>oscillator low<br>frequency range        | P_5.2.15 |  |

| Synchronization high frequency capture range | f <sub>sync,hf</sub> | 1.6  | -      | 2.8  | MHz  | <sup>17)</sup> valid for<br>oscillator high<br>frequency range       | P_5.2.16 |  |

| SYNC "high" signal                           | V <sub>SYNC,hi</sub> | 3.3  | _      | -    | V    | $(17) V_{CC} = 5 V$                                                  | P_5.2.20 |  |

<sup>&</sup>lt;sup>17</sup> Synchronization of PWM to the falling edge.

### Table 7 Electrical characteristics oscillator (continued)

$V_{VS}$  = 6 V to 35 V;  $T_i$  = -40°C to 150°C; all voltages with respect to ground (unless otherwise specified)

| Parameter                                      | Symbol                | Values |      |      | Unit | Note or condition         | Number   |

|------------------------------------------------|-----------------------|--------|------|------|------|---------------------------|----------|

|                                                |                       | Min.   | Тур. | Max. |      |                           |          |

| SYNC "low" signal                              | V <sub>SYNC,lo</sub>  | -      | -    | 0.8  | V    | 17)                       | P_5.2.21 |

| SYNC signal hysteresis                         | V <sub>SYNC,hys</sub> | 45     | 255  | 600  | mV   | 17)                       | P_5.2.22 |

| SYNC "high" input current                      | I <sub>SYNC,hi</sub>  | -      | 0.1  | 1    | μA   | $V_{\rm SYNC} = 5  \rm V$ | P_5.2.23 |

| SYNC "low" input current                       | I <sub>SYNC,lo</sub>  | -      | 0.1  | 1    | μA   | $V_{\rm SYNC} = 0  \rm V$ | P_5.2.26 |

| SYNC signal duty cycle                         | D <sub>SYNC</sub>     | 10     | -    | 90   | %    | -                         | P_5.2.28 |

| Spread spectrum                                |                       | ·      |      | ·    |      | ·                         |          |

| Spread spectrum "high" signal                  | V <sub>SSON,hi</sub>  | 2.0    | -    | -    | V    | Enables spread spectrum   | P_5.2.29 |

| Spread spectrum "low" signal                   | V <sub>SSON,lo</sub>  | -      | -    | 0.8  | V    | Disables spread spectrum  | P_5.2.30 |

| Spread spectrum enable hysteresis              | V <sub>SSON,hys</sub> | 100    | 250  | 1000 | mV   | -                         | P_5.2.31 |

| Spread spectrum enable "high"<br>input current | I <sub>SSON,hi</sub>  | 0.7    | 1    | 1.25 | μA   | V <sub>SSON</sub> = 5.0 V | P_5.2.32 |

| Spread spectrum modulation frequency           | f <sub>SS,mod</sub>   | 7.5    | 8.3  | 9.3  | kHz  | Spread spectrum enabled   | P_5.2.33 |

| Spread spectrum modulation range               | f <sub>SS,range</sub> | -      | ±7.5 | -    | %    | Spread spectrum enabled   | P_5.2.34 |

<sup>&</sup>lt;sup>17</sup> Synchronization of PWM to the falling edge.

# 5.3 Typical performance characteristics oscillator

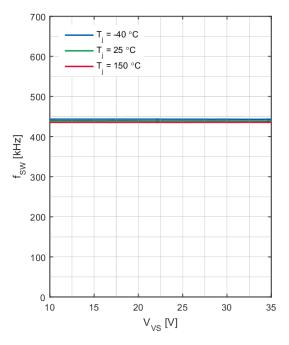

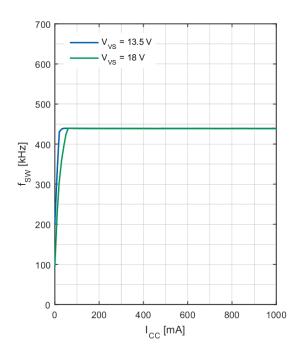

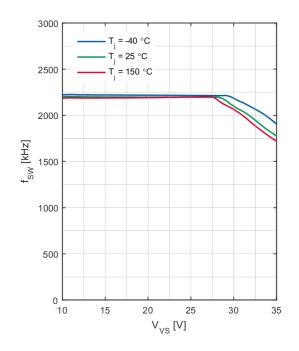

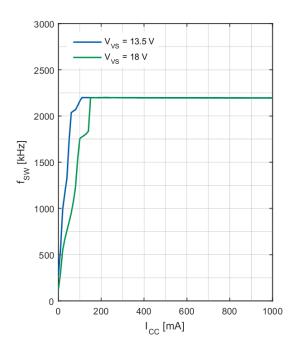

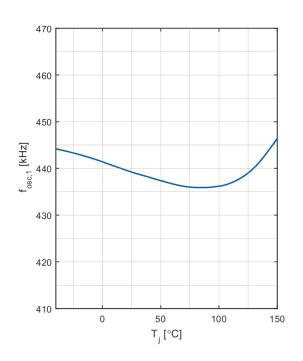

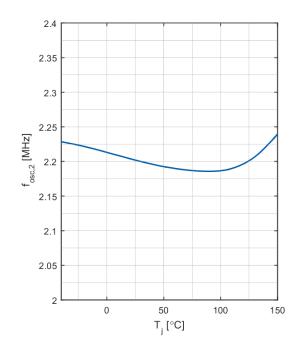

Oscillator (low frequency) V<sub>VS</sub> = 13.5 V; FREQ: 440 kHz Oscillator (high frequency) V<sub>VS</sub> = 13.5 V; FREQ: 2.2 MHz

**Current consumption and enable**

# 6 Current consumption and enable

## 6.1 Functional description current consumption and enable

A "high" signal  $V_{\text{EN,hi}}$  at the EN pin switches on the regulator. In on-state the device can operate at very low current consumption  $I_{\text{VS,on}}$  to improve the efficiency with low load in PFM mode.

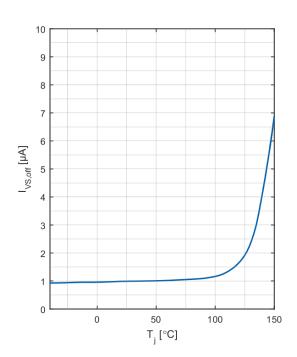

A "low" signal  $V_{\text{EN,lo}}$  at the EN pin switches the regulator off. In turned off-state, the current consumption  $I_{\text{VS,off}}$  of the device is 1  $\mu$ A typically. If the EN pin is left open, then an internal pull-down resistor  $R_{\text{EN,int}}$  ensures that the device remains switched off.

# 6.2 Electrical characteristics current consumption and enable

### Table 8 Electrical characteristics current consumption and enable

$V_{VS}$  = 6 V to 35 V;  $T_i$  = -40°C to 150°C; all voltages with respect to ground (unless otherwise specified)

| Parameter                            | Symbol               |      | Values | i    | Unit | Note or condition                                                                                                                    | Number  |

|--------------------------------------|----------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                      |                      | Min. | Тур.   | Max. |      |                                                                                                                                      |         |

| Current consumption                  |                      |      |        |      |      |                                                                                                                                      |         |

| Current consumption in off-<br>state | I <sub>VS,off</sub>  | -    | 1      | 2    | μΑ   | V <sub>EN</sub> = 0 V;<br>V <sub>VS</sub> = 13.5 V;<br>T <sub>j</sub> < 85°C                                                         | P_6.2.1 |

| Current consumption in on-<br>state  | I <sub>VS,on</sub>   | -    | 31     | 65   | μA   | $V_{\rm EN} = 5.0 \text{ V};$<br>$V_{\rm VS} = 13.5 \text{ V};$<br>$T_{\rm j} < 85^{\circ}\text{C};$<br>not switching <sup>18)</sup> | P_6.2.2 |

| Enable                               |                      |      |        |      |      |                                                                                                                                      | i       |

| Enable "high" signal                 | V <sub>EN,hi</sub>   | 2.0  | -      | -    | V    | -                                                                                                                                    | P_6.2.3 |

| Enable "low" signal                  | V <sub>EN,lo</sub>   | -    | -      | 0.8  | V    | -                                                                                                                                    | P_6.2.4 |

| Enable hysteresis                    | V <sub>EN,hys</sub>  | 100  | 400    | 1000 | mV   | -                                                                                                                                    | P_6.2.5 |

| Enable "high" input current          | I <sub>EN,hi,1</sub> | -    | 0.6    | 1    | μA   | V <sub>EN</sub> = 5.0 V                                                                                                              | P_6.2.6 |

| Enable "high" input current          | I <sub>EN,hi,2</sub> | -    | 2.5    | 3.5  | μA   | V <sub>EN</sub> = 13.5 V                                                                                                             | P_6.2.7 |

| Enable, internal resistor to<br>GND  | R <sub>EN,int</sub>  | 5.6  | 8      | 10.4 | MΩ   | V <sub>EN</sub> = 2.0 V                                                                                                              | P_6.2.8 |

<sup>&</sup>lt;sup>18</sup> The current consumption is tested while the output voltage is forced to a slightly higher value than the nominal output voltage to prevent switching activities of the regulator.

Current consumption and enable

# 6.3 Typical performance characteristics current consumption and enable

Current consumption in off-state  $V_{VS} = 13.5 \text{ V}; V_{EN} = 0 \text{ V}$

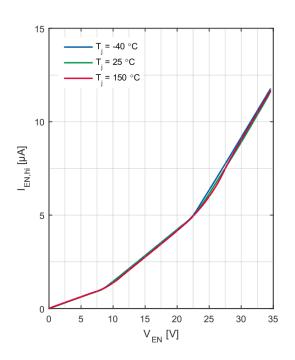

Enable "high" input current V<sub>VS</sub> = 13.5 V

Current consumption in on-state

$V_{\rm VS}$  = 13.5 V;  $V_{\rm EN}$  = 5 V; no switching

# 7 Reset

# 7.1 Functional description reset

The reset function supervises the regulator output voltage  $V_{CC}$  by monitoring the feedback voltage  $V_{FB}$ . The device indicates the reset status at the RO pin. RO "high" indicates, that the output voltage is within the desired reset thresholds. RO "low" indicates that the output voltage is outside the desired reset thresholds. As long as the device operates within the specified range, the reset function is active, see *Table 10* and *Functional range*.

### **Reset output RO**

The reset output pin RO is an open drain structure and needs to be pulled up to  $V_{CC}$  or to a voltage rail via an external pull-up resistor  $R_{RO}$ , which must be chosen according to the maximum pull-up current  $I_{RO,lo}$ . During battery cranking conditions of the input voltage  $V_{VS}$ , the reset feature is active down to an input voltage  $V_{VS}$  of 2.8 V.

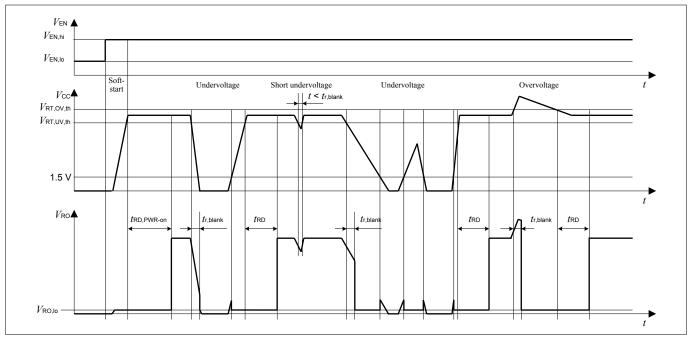

### Power-on reset delay time

Power-on reset delay time  $t_{\text{RD,PWR-on}}$  is the time period from completion of the soft-start until the device releases the reset by switching the reset output RO from "low" to "high", see *Figure 8*. An external resistor  $R_{\text{RT}}$  connected to the RT pin determines the value of power-on reset delay time  $t_{\text{RD,PWR-on}}$ , see *Table 9*.

### Reset undervoltage, overvoltage and delay time

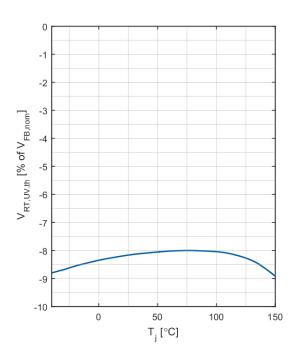

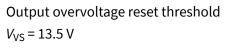

In contrast to the power-on reset delay time  $t_{RD,PWR-on}$ , the reset delay time  $t_{RD}$  refers to an output undervoltage or output overvoltage event during operation, see *Figure 8*. If  $V_{FB}$  drops below the undervoltage reset threshold  $V_{RT,UV,th}$ , then the device sets the reset signal at the RO to "low". When the output voltage recovers and  $V_{FB}$ exceeds the undervoltage reset threshold plus the hysteresis ( $V_{RT,UV,th} + V_{RT,UV,hys}$ ), then the device sets the RO pin to "high" after the reset delay time  $t_{RD}$ . In accordance with the undervoltage reset delay time, the overvoltage reset delay time  $t_{RD}$  considers an output overvoltage event. If case  $V_{FB}$  exceeds the overvoltage reset threshold  $V_{RT,OV,th}$ , then the device sets the RO pin to "low". When the output voltage recovers and  $V_{FB}$ drops below the overvoltage reset threshold minus the hysteresis ( $V_{RT,OV,th} - V_{RT,OV,hys}$ ), then the device sets the RO pin to "high" after the reset delay time  $t_{RD}$ . An external resistor  $R_{RT}$  connected to the RT pin determines the value of the reset delay time  $t_{RD}$  along with the reset undervoltage threshold  $V_{RT,UV,th}$ , see *Table 9*. The device sets the selected reset delay time and reset threshold during initialization phase. The value of the overvoltage reset threshold  $V_{RT,OV,th}$  is fixed.

### **Reset reaction time**

If the output voltage of the regulator drops below the output undervoltage reset threshold  $V_{\text{RT,UV,th}}$  or rises above the output overvoltage reset threshold  $V_{\text{RT,OV,th}}$ , then this triggers the internal output voltage monitoring circuit. If that condition lasts longer than the blanking time  $t_{r,blank}$  (see *Table 10*), then the device sets the reset signal at the RO pin to "low". If the output overvoltage or undervoltage condition lasts shorter than  $t_{r,blank}$ , then the device keeps the reset signal "high". This prevents a microcontroller reset due to very short distortions of the output voltage, see *Figure 8*.

# Table 9RT configuration for typical values of power-on, undervoltage, overvoltage reset delay<br/>time and undervoltage reset threshold

| R <sub>RT</sub> [kΩ] <sup>19)</sup> | t <sub>RD,PWR-on</sub> [ms] | t <sub>RD</sub> [ms] | <i>V</i> <sub>RT,UV,th</sub> [% of <i>V</i> <sub>FB</sub> ] <sup>20)</sup> |

|-------------------------------------|-----------------------------|----------------------|----------------------------------------------------------------------------|

| ≤ 1.0 (or connect to GND)           | 0.06                        | 0.03                 | -8                                                                         |

| 2.2                                 | 0.06                        | 0.03                 | -14                                                                        |

| 3.3                                 | 0.06                        | 0.03                 | -25                                                                        |

| 4.7                                 | 0.06                        | 0.03                 | -40                                                                        |

| 6.8                                 | 1.9                         | 1.3                  | -8                                                                         |

| 10                                  | 1.9                         | 1.3                  | -14                                                                        |

| 15                                  | 1.9                         | 1.3                  | -25                                                                        |

| 22                                  | 1.9                         | 1.3                  | -40                                                                        |

| 33                                  | 7.7                         | 5.1                  | -14                                                                        |

| 47                                  | 7.7                         | 5.1                  | -25                                                                        |

| 68                                  | 7.7                         | 5.1                  | -40                                                                        |

| 100                                 | 15.4                        | 10.2                 | -8                                                                         |

| 150                                 | 15.4                        | 10.2                 | -14                                                                        |

| ≥200 (or leave open)                | 7.7                         | 5.1                  | -8                                                                         |

#### Figure 8

Reset timing diagram<sup>21)</sup>

<sup>&</sup>lt;sup>19</sup> Resistor tolerance  $\leq 5\%$ .

<sup>&</sup>lt;sup>20</sup> In relation to the typical feedback voltage level 5 V.

<sup>&</sup>lt;sup>21</sup> The diagram neglects the reset undervoltage hysteresis and reset overvoltage hysteresis to improve the overview.  $V_{RO}$  is connected to the output voltage  $V_{CC}$  via an external pull-up resistor. The input voltage  $V_{VS}$  is set to a level higher than  $V_{VS,on}$ .

# 7.2 Electrical characteristics reset

### Table 10Electrical characteristics reset

$V_{VS}$  = 6 V to 35 V;  $T_i$  = -40°C to 150°C; all voltages with respect to ground (unless otherwise specified)

| Parameter                                              | Symbol                   | Values |      |      | Unit | Note or condition                                                                             | Number   |

|--------------------------------------------------------|--------------------------|--------|------|------|------|-----------------------------------------------------------------------------------------------|----------|

|                                                        |                          | Min.   | Тур. | Max. |      |                                                                                               |          |

| Reset output RO                                        |                          |        |      |      |      |                                                                                               | i.       |

| Reset output "low" voltage                             | V <sub>RO,lo</sub>       | -      | -    | 0.4  | V    | $V_{\rm CC} \ge 1.5 \text{ V};$ $V_{\rm EN} \ge 2 \text{ V};$ $I_{\rm RO} \le 1.5 \text{ mA}$ | P_7.2.1  |

| Reset output "low" pull-up<br>current                  | I <sub>RO,lo</sub>       | -      | -    | 1.5  | mA   | $V_{\rm EN} \ge 2 \text{ V};$<br>$V_{\rm RO} = 0.4 \text{ V}$                                 | P_7.2.2  |

| Reset output "high"<br>leakage current                 | I <sub>RO,hi</sub>       | -      | -    | 1    | μA   | V <sub>RO</sub> = 5 V                                                                         | P_7.2.3  |

| Output overvoltage reset t                             | hreshold                 |        |      |      |      |                                                                                               |          |

| Output overvoltage reset threshold increasing          | V <sub>RT,OV,th</sub>    | 5      | 7    | 9    | %    | percentage of V <sub>FB</sub>                                                                 | P_7.2.4  |

| Output overvoltage reset<br>hysteresis                 | V <sub>RT,OV,hys</sub>   | -      | 1    | 2    | %    | percentage of V <sub>FB</sub>                                                                 | P_7.2.5  |

| Output undervoltage reset                              | threshold <sup>22</sup>  | )      |      | -    |      |                                                                                               | i        |

| Output undervoltage reset<br>threshold decreasing -8%  | V <sub>RT,UV,th,1</sub>  | -10    | -8   | -6   | %    | percentage of V <sub>FB</sub>                                                                 | P_7.2.6  |

| Output undervoltage reset threshold decreasing -14%    | V <sub>RT,UV,th,2</sub>  | -16    | -14  | -12  | %    | percentage of V <sub>FB</sub>                                                                 | P_7.2.7  |

| Output undervoltage reset<br>threshold decreasing -25% | V <sub>RT,UV,th,3</sub>  | -27    | -25  | -23  | %    | percentage of V <sub>FB</sub>                                                                 | P_7.2.8  |

| Output undervoltage reset<br>threshold decreasing -40% | V <sub>RT,UV,th,4</sub>  | -42    | -40  | -38  | %    | percentage of V <sub>FB</sub>                                                                 | P_7.2.9  |

| Output undervoltage reset<br>hysteresis                | V <sub>RT,UV,hys</sub>   | -      | 1    | 2    | %    | percentage of V <sub>FB</sub>                                                                 | P_7.2.10 |

| Reset delay timing <sup>22)</sup>                      |                          | 1      | 1    | 1    | 1    |                                                                                               |          |

| Power-on reset delay time<br>60 μs                     | t <sub>RD,PWR-on,1</sub> | 15     | 60   | 90   | μs   | -                                                                                             | P_7.2.11 |

| Power-on reset delay time<br>1.9 ms                    | t <sub>RD,PWR-on,2</sub> | 1.7    | 1.9  | 2.2  | ms   | -                                                                                             | P_7.2.12 |

| Power-on reset delay time<br>7.7 ms                    | t <sub>RD,PWR-on,3</sub> | 6.9    | 7.7  | 8.6  | ms   | -                                                                                             | P_7.2.13 |

| Power-on reset delay time<br>15.4 ms                   | t <sub>RD,PWR-on,4</sub> | 13.9   | 15.4 | 17.1 | ms   | -                                                                                             | P_7.2.14 |

<sup>&</sup>lt;sup>22</sup> For RT configuration see *Table 9*

### Table 10 Electrical characteristics reset (continued)

$V_{VS}$  = 6 V to 35 V;  $T_i$  = -40°C to 150°C; all voltages with respect to ground (unless otherwise specified)

| Parameter                | Symbol               |      | Values |      |    | Note or condition | Number   |

|--------------------------|----------------------|------|--------|------|----|-------------------|----------|

|                          |                      | Min. | Тур.   | Max. |    |                   |          |

| Reset delay time 30 µs   | t <sub>RD,1</sub>    | 15   | 30     | 95   | μs | -                 | P_7.2.15 |

| Reset delay time 1.3 ms  | t <sub>RD,2</sub>    | 1.1  | 1.3    | 1.5  | ms | -                 | P_7.2.16 |

| Reset delay time 5.1 ms  | t <sub>RD,3</sub>    | 4.6  | 5.1    | 5.7  | ms | -                 | P_7.2.17 |

| Reset delay time 10.2 ms | t <sub>RD,4</sub>    | 9.3  | 10.2   | 11.4 | ms | -                 | P_7.2.18 |

| Reset blanking time      | t <sub>r,blank</sub> | 2    | 5      | 10   | μs | -                 | P_7.2.19 |

# 7.3 Typical performance characteristics reset

### **Application information**

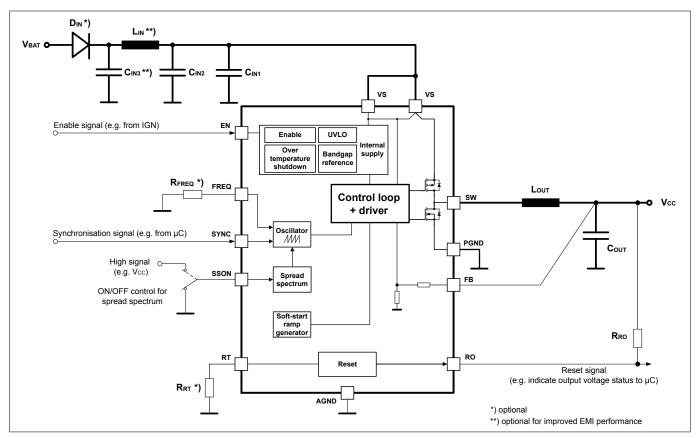

# 8 Application information

*Note:* The following information is given as an example for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

### Figure 9 Application diagram

*Note:* This figure is a simplified example of an application circuit. The function must be verified in the application.

### Application information

| Table 11         | Recomm               | Recommended values for components in the application diagram |                                                                      |  |  |  |  |  |  |  |  |

|------------------|----------------------|--------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Name             | Value <sup>23)</sup> | Switching frequency                                          | Component type                                                       |  |  |  |  |  |  |  |  |

| C <sub>IN1</sub> | 100 nF               | -                                                            | Ceramic X7R capacitor; 50 V                                          |  |  |  |  |  |  |  |  |

| C <sub>IN2</sub> | 10 µF                | -                                                            | Ceramic X7R capacitor; 50 V                                          |  |  |  |  |  |  |  |  |

| L <sub>OUT</sub> | 22 μH                | 320 kHz to 560 kHz                                           | Shielded power inductor; $I_{SAT} > I_{BUOC}$<br>DCR < 70 m $\Omega$ |  |  |  |  |  |  |  |  |

| C <sub>OUT</sub> | 88 μF <sup>24)</sup> | 320 kHz to 560 kHz                                           | 22 μF (x4) ceramic X7R capacitor; 16 V                               |  |  |  |  |  |  |  |  |

| L <sub>OUT</sub> | 2.2 μΗ               | 1.6 MHz to 2.8 MHz                                           | Shielded power inductor; $I_{SAT} > I_{BUOC}$<br>DCR < 70 m $\Omega$ |  |  |  |  |  |  |  |  |

| C <sub>OUT</sub> | 44 μF <sup>24)</sup> | 1.6 MHz to 2.8 MHz                                           | 22 μF (x2) ceramic X7R capacitor; 16 V                               |  |  |  |  |  |  |  |  |

<sup>&</sup>lt;sup>23</sup> Typical condition

<sup>&</sup>lt;sup>24</sup> For maintenance of loop stability it is recommended to use capacitors with a limited voltage derating at the typical output voltage level. A capacitor in parallel can be added to match the recommended typical capacitance value as close as possible.

### **Application information**

### 8.1 Layout recommendations

### Introduction

A switch mode power supply is a potential source of electromagnetic disturbance, which may affect the application environment as well as the device itself. This can lead to sporadic malfunction including regulator instability or irreversible damage depending on the amount of generated disturbance.

Main types of electromagnetic disturbance:

- Radiated emission

- Conducted emission

#### **Radiated emission**

Radiated emission is caused by circulating currents and voltage oscillations. Alternating currents appear in so called current windows, which are defined by the area of the circulating current within the corresponding filter stage at the input or the output of the regulator. Voltage oscillations are mainly caused by resonant circuits induced by parasitic inductance and capacitance of the PCB layout.

The following PCB layout design recommendations help to minimize radiated emission:

- Place external components close to the device to reduce parasitic elements of the PCB layout and to keep the area of circulating currents small. At the same time some distance should be kept between the components to avoid coupling.

- Reduce the switching area at pin SW to minimize the inductance and especially the parasitic capacitance. The parasitic capacitance can be further reduced by removing inner GND layers below the switching area. Routing of other signal traces below the switching area should be avoided generally.

- Use GND layers to shield areas with alternating currents or voltage oscillations.

### **Conducted emission**

Conducted emission consists of voltage oscillations, which occur permanently or by occasion at the regulator input or output connection. Their frequency range can exceed 100 MHz and they are superimposed to the input voltage  $V_{VS}$  and to the output voltage  $V_{CC}$ . This might disturb other components of the application.

Countermeasures against conducted disturbances are the same as against radiated emission. The following recommendations can further reduce the conducted emission:

- Reduce high frequency conducted emission by placing well connected small ceramic filter capacitors (1 nF to 220 nF) with low ESR and low ESL in parallel to the input capacitors as close as possible to the input pin VS and in parallel to the output capacitor C<sub>OUT</sub> close to the output inductor L<sub>OUT</sub>.

- Reduce noise injected into the battery supply line by using a  $\pi$ -filter, for example consisting of  $C_{IN1}$ ,  $C_{IN2}$ ,  $C_{IN3}$  and  $L_{IN}$ . This requires additional capacitors and an inductor. The filter must be designed according to the requirements of the application.

# 8.2 Additional information

Please contact Infineon:

- for information regarding the pin behavioral assessment

- for application notes with more detailed information about this device

- for any further information visit https://www.infineon.com/

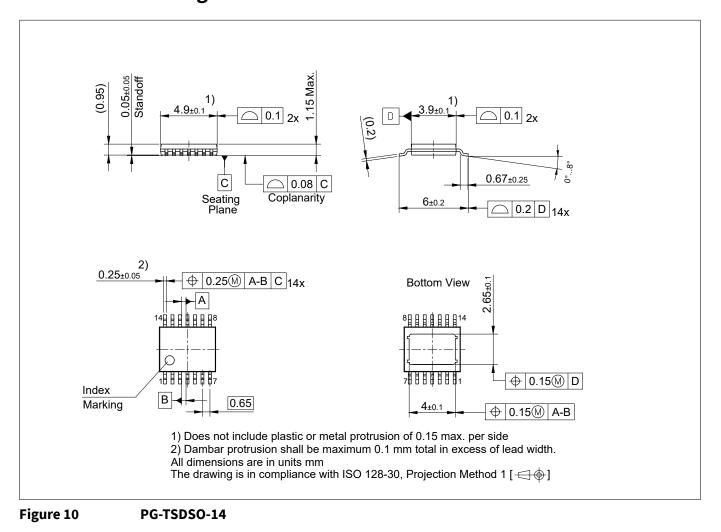

### Package information

9

**Package information**

### Green Product (RoHS compliant)

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a Green Product. Green Products are RoHS compliant (Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

### Information on alternative packages

Please visit www.infineon.com/packages.

**Revision history**

# **Revision history**

| Version   | Date       | Changes           |