# **XDP<sup>™</sup> Digital Power**

Datasheet Revision 1.1

## **Features**

- Single stage flyback controller with Power Factor Correction (PFC)

- Primary side regulated Constant Current (CC) output with high precision

- Supports universal AC input (90 V<sub>rms</sub> to 305 V<sub>rms</sub>)

- Supports wide LED load voltage range (up to 4 times of the minimum LED load voltage)

- Excellent line and load regulation (typical within +/- 2%)

- High power quality (Typical *Power Factor (PF)* up to 0.99 and *Total Harmonic Distortion (THD)* < 10%)

- High efficiency with Quasi-Resonant Mode, switching in first valley (QRM1) at high output power and frequency controlled Discontinuous Conduction Mode (DCM) at medium output power

- Dim-to-off operation (with typical standby power as low as 60 mW)

- Dedicated PWM input pin for dimming control by either a micro-controller or a transformer-less IEC60929compliant isolated 0 - 10 V dimming circuit (based on CDM10VD)

- Dimming down to 1%

- Limited Power (LP) mode

- Input overvoltage and undervoltage (Brown-in/Brown-out) protection with configurable threshold for output on/off

- Brown-out maximum power reduction, to better protect primary components from overheating and saturation

- Adaptive output overvoltage protection to meet UL1310 standard (Class 2) for the 54 V LED driver design.

- Output and VCC undervoltage protection

- Configurable dimming parameters, e.g. dimming curve (linear/quadratic), minimum current, dim-to-off option (enabled/disabled)

# **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

# **Potential applications**

Electronic control gear for LED luminaires

# **Potential applications**

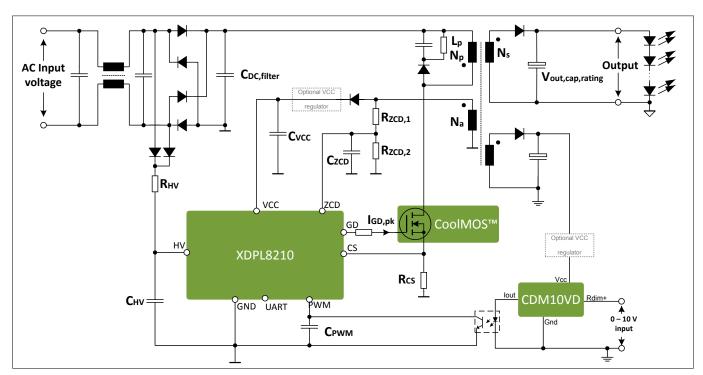

Figure 1 Potential application 1 for XDPL8210

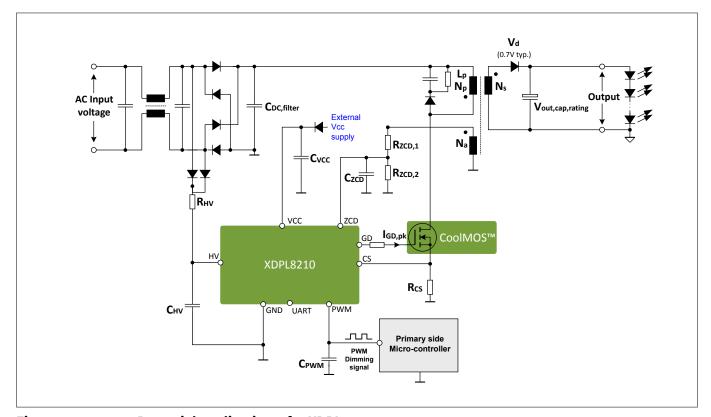

Figure 2 Potential application 2 for XDPL8210

| Product type | Package  | Marking  | Firmware version | Ordering code |

|--------------|----------|----------|------------------|---------------|

| XDPL8210     | PG-DSO-8 | XDPL8210 | 4.2.0.0          | SP001643692   |

XDP™ Digital Power

**Description**

# **Description**

The XDPL8210 is a high performance configurable single-stage flyback controller with high power factor, primary side regulated constant current output and **LP** mode.

The primary side control saves external components especially an opto coupler, thus reducing cost and effort and increasing reliability. With its integrated functionality, XDPL8210 enables an increase set of features without external parts.

The digital core of the XDPL8210 and its advanced control algorithms provide multiple operation modes such as QRM1, DCM or Active Burst Mode (ABM). In addition, XDPL8210 includes an enhanced PFC function which can partially compensate the effect of the input capacitance on power factor and harmonic distortion. With this functionality and smooth transition between the operation modes, the controller delivers high efficiency, high power factor and low harmonic distortion over wide load range. The active burst mode control scheme significantly extends the dimming range and is synchronized with the line frequency avoiding effects like flicker while reducing audible noise.

Operation parameters such as the output current, dimming curve and the protection features are digitally configurable. Infineon offers a user friendly **Graphic User Interface** for **Personal Computers**, allowing rapid engineering changes without the need for complex component design iterations. Functionality can be defined at the end of the production line. Multiple different Light Emitting Diode (LED) drivers can be built with the same hardware using different XDPL8210 parameter sets.

For instance, the dimming curve shape is configurable to linear or quadratic (eye-adaptive) and can optionally be inverted. Additionally, dim-to-off can be enabled or disabled.

Note: By default, the configurable parameters of a new XDPL8210 chip from Infineon are empty, so it is necessary to configure them before any application testing.

The system performance and efficiency can be optimized using Infineon CoolMOS P7 power MOSFETs.

# **Table of contents**

# **Table of contents**

|        | Features                                                              | 1  |

|--------|-----------------------------------------------------------------------|----|

|        | Product validation                                                    | 1  |

|        | Potential applications                                                | 1  |

|        | Description                                                           | 3  |

|        | Table of contents                                                     | 4  |

| 1      | Pin configuration                                                     | 6  |

| 2      | Functional block diagram                                              | 7  |

| 3      | Functional description                                                | 8  |

| 3.1    | Regulated mode                                                        | 8  |

| 3.1.1  | Constant current and limited power set-point                          | 8  |

| 3.1.2  | Multimode operation                                                   |    |

| 3.1.3  | Control loop initialization                                           |    |

| 3.2    | Configurable gate voltage rising slope at GD pin                      | 12 |

| 3.3    | Startup                                                               | 12 |

| 3.4    | Line synchronization                                                  |    |

| 3.5    | Input voltage, output voltage and output current estimation           | 14 |

| 3.5.1  | Input voltage estimation                                              | 15 |

| 3.5.2  | Output voltage estimation                                             | 15 |

| 3.5.3  | Output current estimation                                             | 16 |

| 3.6    | Power factor correction                                               | 18 |

| 3.7    | Dimming control                                                       | 18 |

| 3.8    | Protection features                                                   | 19 |

| 3.8.1  | Primary MOSFET overcurrent protection                                 | 20 |

| 3.8.2  | Output undervoltage protection                                        | 20 |

| 3.8.3  | Output overvoltage protection                                         | 21 |

| 3.8.4  | Transformer demagnetization time shortage protection                  | 23 |

| 3.8.5  | Regulated mode peak output overcurrent protection                     |    |

| 3.8.6  | Minimum input voltage startup check and input undervoltage protection | 24 |

| 3.8.7  | Maximum input voltage startup check and input overvoltage protection  | 24 |

| 3.8.8  | VCC undervoltage lockout                                              | 24 |

| 3.8.9  | VCC overvoltage protection                                            | 25 |

| 3.8.10 | IC overtemperature protection                                         | 25 |

| 3.8.11 | Other protections                                                     | 25 |

| 3.8.12 | Protection reactions                                                  | 26 |

| 4      | Debug mode                                                            | 26 |

| 5      | List of Parameters                                                    | 28 |

|        |                                                                       |    |

# Table of contents

| 6   | Electrical Characteristics and Parameters | 34 |

|-----|-------------------------------------------|----|

| 6.1 | Package Characteristics                   | 34 |

| 6.2 | Absolute Maximum Ratings                  |    |

| 6.3 | Operating conditions                      | 35 |

| 6.4 | DC Electrical characteristics             |    |

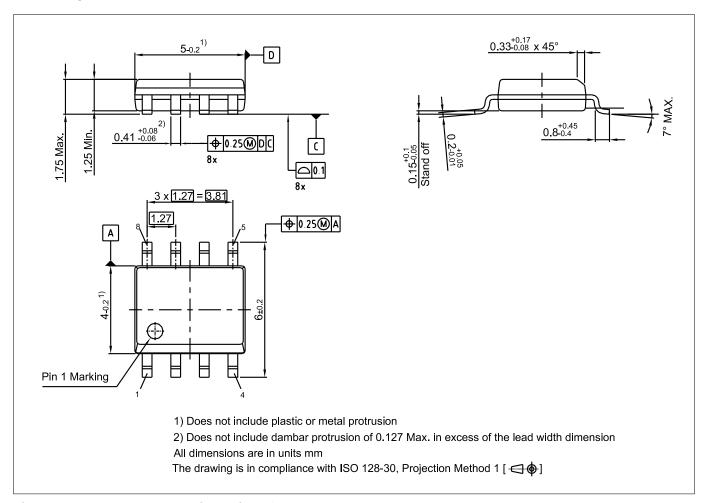

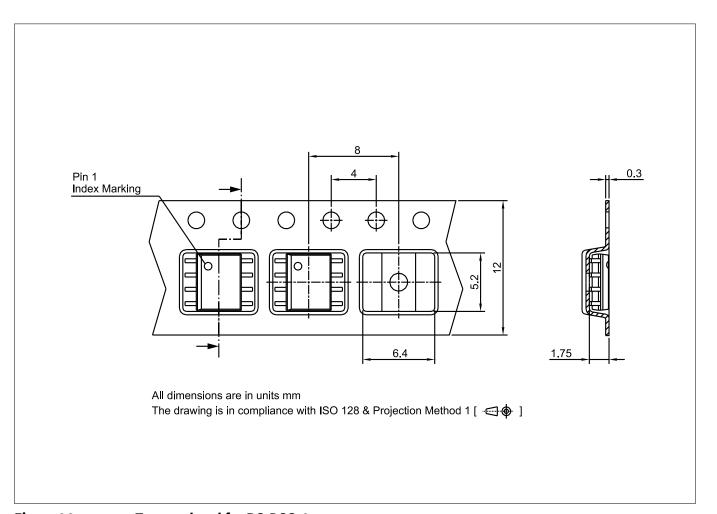

| 7   | Package dimensions                        | 46 |

| 8   | References                                | 48 |

|     | Revision History                          | 48 |

|     | Glossary                                  | 48 |

|     | Disclaimer                                | 51 |

**Pin configuration**

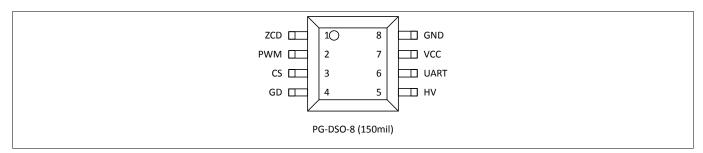

### **Pin configuration** 1

Pin assignments and basic pin description information are shown below.

Figure 3 **Pinning of XDPL8210**

Pin definitions and functions Table 1

| Name | Pin | Туре | Function                                                                                                                                                                                                                                                    |

|------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZCD  | 1   | I    | Zero-crossing detection:                                                                                                                                                                                                                                    |

|      |     |      | The ZCD pin is connected to the auxiliary winding via external resistors divider. It is used for zero-crossing detection, primary-side output voltage sensing and input voltage sensing.                                                                    |

| PWM  | 2   | I    | Pulse Width Modulation (PWM) dimming:                                                                                                                                                                                                                       |

|      |     |      | The <i>PWM</i> pin is used as a dimming input. The PWM frequency should be fixed in the range from 500 Hz to 2 kHz.                                                                                                                                         |

| CS   | 3   | I    | Current sensing:                                                                                                                                                                                                                                            |

|      |     |      | The CS pin is used for Flyback MOSFET current sensing via external shunt resistor.                                                                                                                                                                          |

| GD   | 4   | 0    | Gate driver:                                                                                                                                                                                                                                                |

|      |     |      | The <i>GD</i> pin is used for Flyback MOSFET gate drive control via external series resistor.                                                                                                                                                               |

| HV   | 5   | I    | High voltage:                                                                                                                                                                                                                                               |

|      |     |      | The HV pin is connected to the rectified input voltage via external series resistor. The HV pin is used to charge VCC pin voltage during startup and protection, via an internal 600 V startup cell. In addition, it is also used for line synchronization. |

| UART | 6   | I/O  | Universal Asynchronous Receiver Transmitter configuration:                                                                                                                                                                                                  |

|      |     |      | The UART pin is used as the digital interface for parameter configuration.                                                                                                                                                                                  |

| VCC  | 7   | 1    | Operating voltage supply and sensing                                                                                                                                                                                                                        |

| GND  | 8   | -    | Integrated Circuit (IC) grounding                                                                                                                                                                                                                           |

**Functional block diagram**

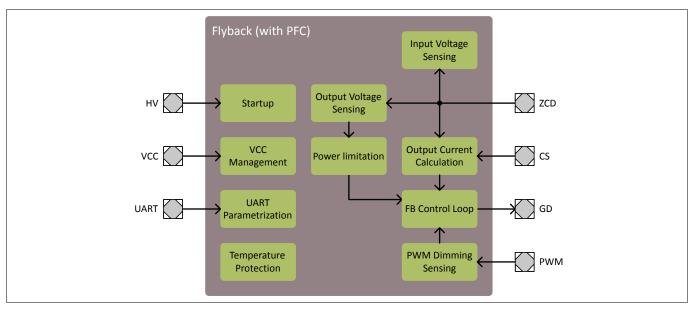

#### Functional block diagram 2

The functional block diagram shows the basic data flow from input pins via signal processing to the output pins.

Figure 4 XDPL8210 functional block diagram

XDP™ Digital Power

**Functional description**

#### **Functional description** 3

The functional description provides an overview about the integrated functions and features as well as their relationship. The mentioned parameters and equations are based on typical values at  $T_A = 25$ °C. The corresponding min. and max. values are shown in the electrical characteristics.

#### 3.1 **Regulated mode**

The XDPL8210 regulated mode provides a primary side control of the output current. The secondary side feedback components are not necessary for the output current control as the primary side regulation control loop is fully integrated.

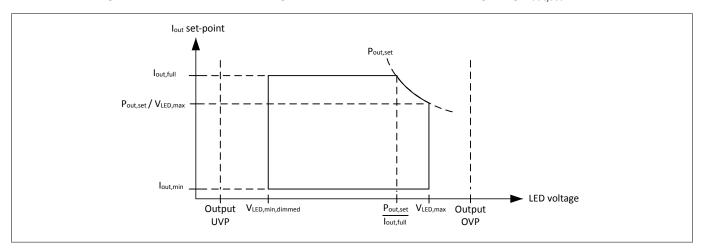

#### Constant current and limited power set-point 3.1.1

Under non-dimming condition, the regulated mode CC output current set-point is based on the maximum output current set-point I<sub>out.full</sub>. Under dimming condition, the regulated mode CC output current set-point is selected between  $I_{\text{out,full}}$  and minimum output current set-point  $\bar{I_{\text{out,min}}}$ , depending on the dimming level. Both *I*<sub>out,min</sub> and *I*<sub>out,full</sub> parameters are configurable.

If the output power produced by the regulated mode CC output current set-point and the connected LED voltage  $V_{\text{LED}}$  exceeds the configurable maximum output power limit set-point  $P_{\text{out.set}}$ , the regulated mode LP set point based on  $P_{\text{out,set}}$  parameter would take over and reduce the output current set-point to  $P_{\text{out,set}}$  /  $V_{\text{LED}}$ .

To achieve a full CC output dimming range between  $I_{\text{out,min}}$  and  $I_{\text{out,full}}$ , the connected LED voltage  $V_{\text{LED}}$  should not exceed  $P_{\text{out,set}} / I_{\text{out,full}}$ , as shown in *Figure 5*.

If only the CC regulation is desired, the LP regulation can be disabled by configuring  $P_{\text{out,set}} = 0$ .

Figure 5 Operating window with constant current and limited power regulation

V<sub>LED.max</sub> refers to the desired maximum operating LED voltage when output current is I<sub>out,full</sub>. V<sub>LED.max</sub> Note: should be designed well below the output overvoltage protection level.

$V_{\text{LED.min.dimmed}}$  refers to the desired minimum operating LED voltage when output current is  $I_{\text{out.min.}}$ Note:  $V_{\mathsf{LED},\mathsf{min},\mathsf{dimmed}}$  should be designed well above the output undervoltage protection level.

# **XDP<sup>™</sup> Digital Power**

**Functional description**

3.1.2

# **Multimode operation**

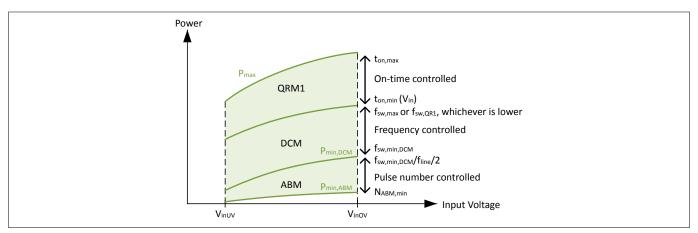

In regulated mode, there are three different switching modes (QRM1, DCM and ABM). The integrated primary side control loop selects the switching mode depending on the operating condition.

Figure 6 **Multimode operation scheme**

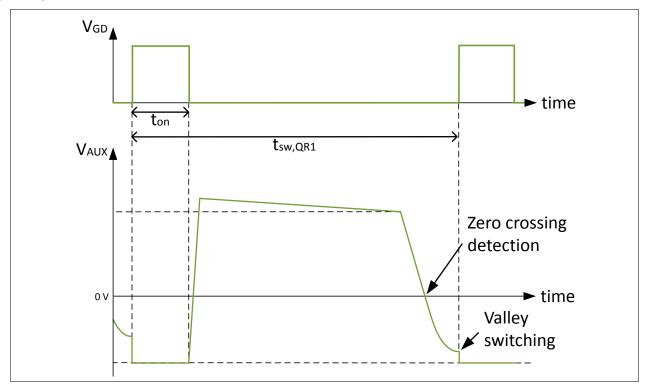

QRM1: This mode minimizes the switching loss by switching on the MOSFET at the quasi-resonant 1st valley of the primary auxiliary winding voltage V<sub>AUX</sub> signal, to maximize the efficiency. The power is controlled by regulating the on-time of the MOSFET.

Figure 7 **Switching waveforms in QRM1**

If the quasi-resonant 1st valley switching period  $t_{\rm sw,QR1}$  is lower than the minimum switching Note: period of  $1/f_{\text{sw.max}}$ , the MOSFET can only be switched on after the quasi-resonant 1<sup>st</sup> valley.

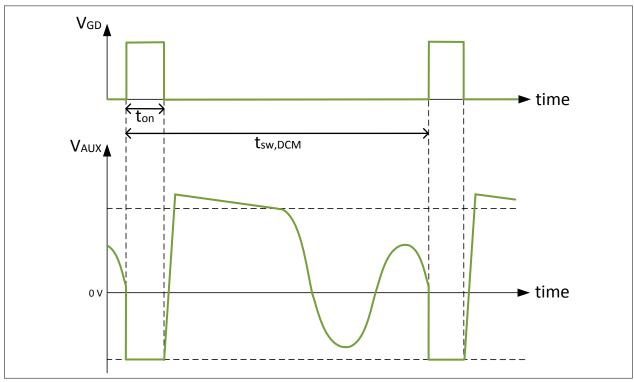

DCM: This mode minimizes the switching loss by reducing the switching frequency when the output power is reduced. The on-time is kept at the minimum value, while the power is controlled by regulating the switching frequency. The minimum power transfer in DCM P<sub>min,DCM</sub> happens when the minimum switching frequency  $f_{sw,min}$  is reached.

# **XDP<sup>™</sup> Digital Power**

## **Functional description**

Figure 8 Switching waveforms in DCM

ABM: This mode can be enabled with  $EN_{ABM}$  parameter to deliver a lower output power than in **DCM**, for a lower minimum output current. The on-time and switching frequency are kept at the minimum value, while the power is controlled by regulating the switching pulse number of each burst period. The burst frequency in this mode is synchronized to the rectified AC input frequency, to ensure good light quality and low audible noise. The minimum power transfer in ABM P<sub>min,ABM</sub> happens when the minimum switching pulse number N<sub>ABM.min</sub> is reached.

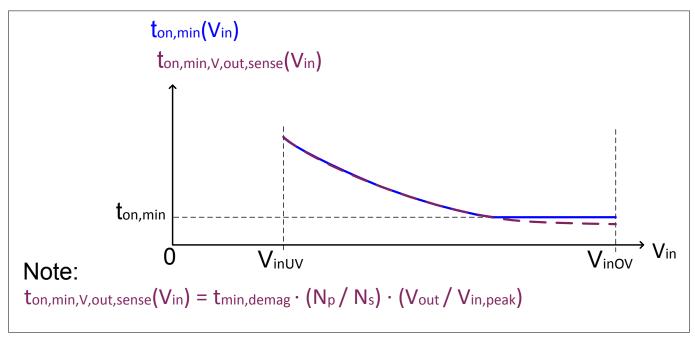

## Minimum on-time adaptation based on estimated input voltage

In all switching modes,  $t_{\text{on,min,V,out,sense}}(V_{\text{in}})$  variable is scaled to allow a desired minimum transformer demagnetization time based on  $t_{min,demag}$  parameter at the peak of input voltage  $V_{in,peak}$ , for output voltage sensing.

$$t_{\text{on, min, }V, \text{out, sense}}(V_{\text{in}}) = t_{\text{min, demag}} \cdot \frac{N_p}{N_s} \cdot \frac{V_{\text{out}}}{V_{\text{in, peak}}}$$

### **Equation 1**

The minimum on-time of  $t_{\text{on,min}}(V_{\text{in}})$  is based on  $t_{\text{on,min}}$  parameter or  $t_{\text{on,min,V,out,sense}}(V_{\text{in}})$  variable, whichever is higher.

$$t_{\text{on}} > t_{\text{on, min}}(V_{\text{in}}) = \max [t_{\text{on, min, }V, \text{ out, sense}}(V_{\text{in}}), t_{\text{on, min}}]$$

# **Equation 2**

# XDP™ Digital Power

## **Functional description**

Figure 9 Minimum on-time depending on the estimated input voltage

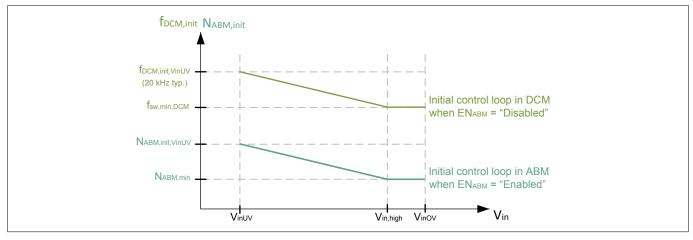

#### 3.1.3 **Control loop initialization**

When the regulated mode is entered initially after the startup phase, the control loop initialization is necessary. To ensure a fast and smooth startup with minimal output current overshoot, XDPL8210 features an adaptive control loop switching parameter initialization depending on the EN<sub>ABM</sub> parameter and estimated input voltage  $V_{\rm in}$ :

- If *ABM* is enabled with *EN*<sub>ABM</sub> parameter, ABM is selected as the initial switching mode for the control loop. The initial controlled ABM switching pulse number  $N_{ABM,init}$  is scaled between  $N_{ABM,min}$  and  $N_{ABM,init,VinUV}$ parameters, depending on  $V_{\rm in}$ .

- If ABM is disabled with *EN*<sub>ABM</sub> parameter, *DCM* is selected as the initial switching mode for the control loop. The initial controlled DCM switching frequency number  $f_{\text{DCM,init}}$  is scaled between  $f_{\text{sw,min,DCM}}$  parameter and  $f_{DCM.init.VinUV}$  (20 kHz typ.), depending on  $V_{in}$ .

Figure 10 Adaptive control loop parameter initialization

$V_{\text{inUV}}$  and  $V_{\text{inOV}}$  refer to the input undervoltage protection level and input overvoltage level parameter Note: respectively.

## **Functional description**

Note:

$V_{\rm in,high}$  refers to the high input voltage parameter. If the estimated input voltage  $V_{\rm in}$  is  $V_{\rm in,high}$  or more,  $N_{ABM,init} = N_{ABM,min}$  or  $f_{DCM,init} = f_{sw,min,DCM}$  is applied.

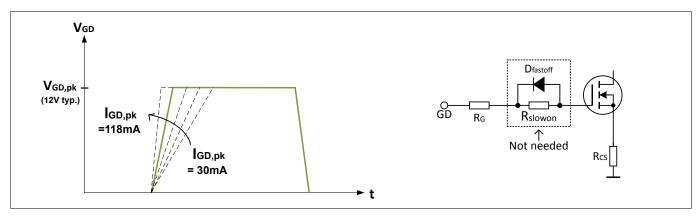

#### 3.2 Configurable gate voltage rising slope at GD pin

The gate drive peak voltage  $V_{\mathrm{GD,pk}}$  is 12 V with sufficient Vcc voltage supply. To achieve a good balance of switching loss and *Electro-Magnetic Interference (EMI)*, the gate voltage rising slope which determines the MOSFET switching on speed can be controlled, by configuring the gate driver peak source current I<sub>GD.pk</sub> parameter (Configurable range: 30 mA to 118 mA). This saves two components (see  $D_{fastoff}$ ,  $R_{slowon}$  in *Figure 11*), which are conventionally added for the same purpose.

Figure 11 Configurable gate voltage rising slope and component saving

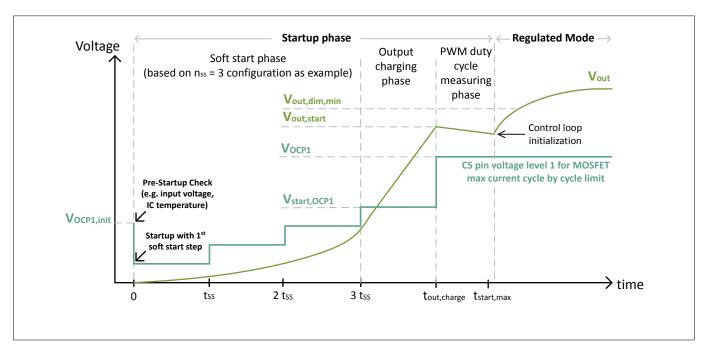

#### 3.3 **Startup**

The startup phase is entered upon checking the startup conditions (e.g. input voltage, IC temperature) are within limits.

To estimate the input voltage level before startup, ZCD pin signal is measured during a single pulse generated on GD pin. This single pulse has an on-time based on the pre-start CS pin maximum voltage limit of  $V_{\rm OCP1,init}$  or 8 times of the leading edge blanking time  $t_{CS,LEB}$  (e.g. 8 \* 480 ns = 3.84  $\mu$ s typ.). If the estimated input voltage or any other startup conditions are not within limits, startup phase is not entered and this single pulse will be generated again after an auto-restart duration.

The startup phase consists of soft start phase, output charging phase and **PWM** duty cycle measuring phase. The soft start phase is to minimize the component stress during startup. The output charging phase is to fast charge the output voltage for fast VCC voltage self supply takeover from the primary auxiliary winding, while the PWM duty cycle measuring phase is to determine the regulated mode output current set-point.

# XDP™ Digital Power

## **Functional description**

Figure 12 Start up phase with soft start step n<sub>ss</sub>=3

During soft start phase, the switching frequency is fixed at 20 kHz. The MOSFET current is limited in the first soft start step based on CS pin maximum voltage limit of  $V_{\text{start},OCP1}/(n_{\text{ss}}+1)$ , where  $V_{\text{start},OCP1}$  is the parameter for the output charging phase CS pin maximum voltage limit and  $n_{ss}$  is the parameter for the number of soft start steps. The soft start phase CS pin maximum voltage limit is increased by  $V_{\text{start,OCP1}}/(n_{\text{ss}}+1)$  after each soft start step until  $V_{\text{start},OCP1}$  is reached, and the typical duration of each soft start step  $t_{\text{ss}}$  is  $3.2/n_{\text{ss}}$  ms or 0.5 ms, whichever is lower.

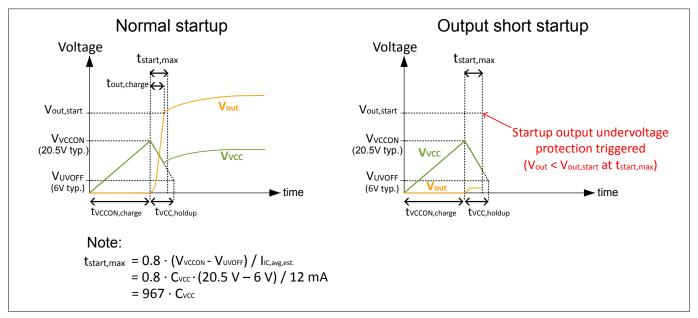

During output charging phase, the output voltage is fast charged with MOSFET switching pulses based on either the output charging phase CS pin maximum voltage limit of  $V_{\text{start}, OCP1}$  or the maximum on time of  $t_{\text{on,max}}$  in **QRM1**. To exit the startup phase and enter the regulated mode without triggering the startup output undervoltage protection, the ZCD pin estimated output voltage  $V_{\mathrm{out}}$  has to reach the output charging voltage set-point of  $V_{\text{out,start}}$  before the maximum allowable startup phase duration of  $t_{\text{start,max}}$  is reached (see example in *Figure 12*). To avoid output overshoot, *V*<sub>out.start</sub> should be designed below the fully dimmed minimum output LED voltage V<sub>out,dim,min</sub>.

$t_{\text{start.max}}$  parameter can be indirectly configured with VCC capacitance parameter  $C_{\text{VCC}}$ , based on:

$$t_{\text{start, max}} = 967 \cdot C_{\text{VCC}}$$

## **Equation 3**

Note:

A typical leading edge blanking time  $t_{CS,LEB}$  of 480 ns applies on  $V_{OCP1,init}$ ,  $V_{start,OCP1}$  and the CS pin maximum voltage limit for every soft start step starting from  $V_{\text{start.OCP1}}/(n_{\text{ss}} + 1)$ .

During the PWM duty cycle measurement phase, the MOSFET switching pulses are based on very short on-time and switching frequency of  $f_{\text{SW,DIM,DCM}}$  (1 kHz typically).

After the startup phase is ended with neither protection triggering nor dim-to-off entering, the control loop is initialized for output current regulation in the regulated mode.

#### Line synchronization 3.4

The XDPL8210 synchronizes most of its operation to the AC input half sine wave period or the rectified AC input frequency, via the HV pin. For instance, based on AC input frequency of 50 Hz, the line synchronization

## **Functional description**

should be based on the rectified AC input frequency of 100 Hz or AC input half sine wave period of 10 ms. Such line synchronization is used for the enhanced **PFC** in compensating the input current displacement caused by the line filter and DC link filter capacitor. If the line synchronization is not established, for example during startup, the controller would synchronize its operation based on an internally preset half sine wave period of approximately 9.823 ms.

# 3.5 Input voltage, output voltage and output current estimation

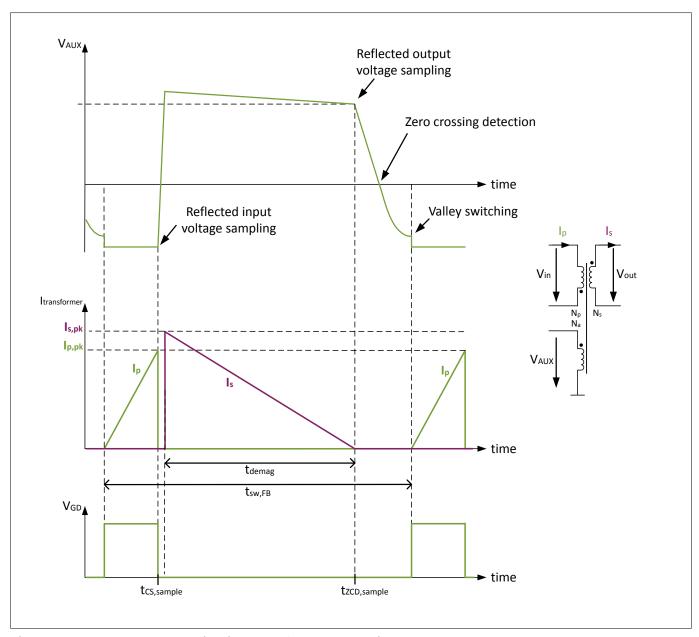

As shown in **Figure 13**, the auxiliary winding voltage signal  $V_{AUX}$  sensed via ZCD pin contains information of the transformer demagnetization time  $t_{demag}$ , reflected output voltage and reflected input voltage, while the primary peak current signal  $I_{p,pk}$  sensed via CS pin contains the secondary peak current  $I_{s,pk}$  information. To estimate the output current, the  $t_{demag}$  and  $t_{s,pk}$  information are necessary.

Figure 13 Flyback switching waveform example in QRM1

# **XDP<sup>™</sup> Digital Power**

# **Functional description**

#### 3.5.1 Input voltage estimation

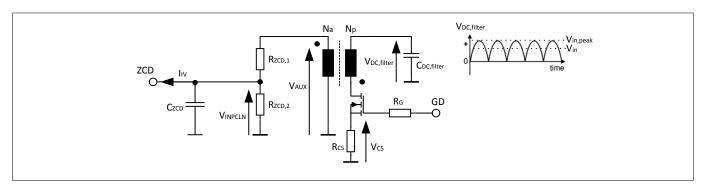

The input voltage is estimated by sensing the reflected input voltage signal from the transformer primary auxiliary winding voltage  $V_{AUX}$ , when the MOSFET is switched on. As the reflected input voltage signal is a negative voltage which cannot be sensed directly, the voltage at ZCD pin is clamped to a negative voltage of  $V_{\text{INPCLN}}$ . A resistor divider with  $R_{\text{ZCD},1}$  and  $R_{\text{ZCD},2}$  adapts  $-I_{\text{IV}}$  which is the clamping current flowing out of ZCD pin, based on its operational range, while a ZCD pin filter capacitor  $C_{7CD}$  is needed for noise filtering, as shown in Figure 14.

Based on the sampled clamping current - $I_{IV}$  at the timing of  $t_{CS,sample}$  shown in **Figure 13**, which is at the end of on-time, the reflected input voltage signal from  $V_{AUX}$  is sensed. The interval of each  $-I_{IV}$  sample is approximately 1/64 of the half sine wave period.

The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on Note: the operating conditions, as explained in **Line synchronization**.

The estimated peak input voltage  $V_{\text{in,peak}}$  over a half sine wave period is based on:

$$V_{\text{in, peak}} = \max \left\{ \frac{N_p}{N_a} \cdot \left[ \left( -I_{\text{IV}} - \frac{V_{\text{INPCLN}}}{R_{\text{ZCD, 2}}} \right) \cdot R_{\text{ZCD, 1}} - V_{\text{INPCLN}} \right] + \frac{R_{\text{in}}}{R_{\text{CS}}} \cdot V_{\text{CS, peak}} \right\}$$

### **Equation 4**

Where  $N_p$  is the primary main winding turns,  $N_a$  is the primary auxiliary winding turns,  $R_{CS}$  is the CS pin shunt resistor value,  $V_{CS,peak}$  is the peak CS pin voltage, and  $R_{in}$  is the fine-tuning parameter for input voltage sensing accuracy improvement by compensating the switching frequency voltage ripple on  $C_{DC,filter}$ .

The estimated input voltage  $V_{in}$  in rms value is assumed by the controller as 0.707 of  $V_{in,peak}$  based on a filtered value over a few half sine wave periods. The update rate of  $V_{in}$  is once per half sine wave period.

$$V_{\rm in} = 0.707 \cdot V_{\rm in, peak}$$

## **Equation 5**

Figure 14 Input voltage estimation based on -IIV

The estimated input voltage  $V_{in}$  is used for input voltage protections and the enhanced **PFC** (EPFC). Therefore, it is important to ensure that **IC** parameters  $R_{ZCD,1}$ ,  $R_{ZCD,2}$ ,  $N_p$ ,  $N_a$  and  $R_{CS}$  are configured as per the actual system hardware dimensioning.

#### **Output voltage estimation** 3.5.2

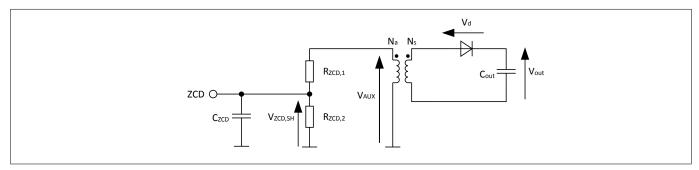

The output voltage is estimated by sensing the reflected output voltage signal from the transformer primary auxiliary winding voltage  $V_{AUX}$ , when the MOSFET is switched off and near the end of transformer demagnetization. A resistor divider with  $R_{ZCD,1}$  and  $R_{ZCD,2}$  adapts the voltage at ZCD pin based on its operational range, while a ZCD pin filter capacitor C<sub>ZCD</sub> is needed for noise filtering, as shown in Figure 15.

Based on the sampled ZCD pin voltage  $V_{ZCD,SH}$  at the timing of  $t_{ZCD,sample}$  shown in *Figure 13*, which is approximately a quarter of oscillation period ( $T_{\rm osc}/4$ ) before the 1<sup>st</sup> zero crossing of  $V_{\rm AUX}$ , a ratio of the reflected

# **XDP<sup>™</sup> Digital Power**

## **Functional description**

output voltage signal from  $V_{\text{AUX}}$  is sensed. The interval of each  $V_{\text{ZCD,SH}}$  sampling is approximately 1/64 of the half sine wave period, while the oscillation period  $T_{\text{osc}}$  is measured once before startup and updated every 7<sup>th</sup> half sine wave period after entering the regulated mode.

Note: The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on

the operating conditions, as explained in **Line synchronization**.

Note: As  $V_{AUX}$  zero crossing can only be detected by the IC via ZCD pin upon its internal analog delay plus

external delay caused by  $C_{\sf ZCD}$ ,  $t_{\sf ZCDPD}$  parameter fine-tuning is needed to compensate such delays, to

have the proper timing of  $t_{ZCD,sample}$  for output voltage estimation.

Attention: Please note that the transformer demagnetization time  $t_{demag}$  has to be longer than 2.0  $\mu$ s to ensure that the reflected output voltage can be sensed properly at the ZCD pin.

The estimated output voltage  $V_{\text{out}}$  is based on:

$$V_{\text{out}} = V_{\text{ZCD, SH}} \cdot \frac{R_{\text{ZCD, 1}} + R_{\text{ZCD, 2}}}{R_{\text{ZCD, 2}}} \cdot \frac{N_s}{N_a} - V_d$$

### **Equation 6**

Where  $N_s$  is the transformer secondary main winding turns,  $N_a$  is the transformer primary auxiliary winding turns and  $V_d$  is the secondary main output diode forward voltage (assumed by the controller as 0.7 V).

Figure 15 Output voltage estimation based on  $V_{ZCD,SH}$

The estimated output voltage  $V_{\text{out}}$  is used for output voltage protections and the enhanced **PFC** (EPFC). Therefore, it is important to ensure that IC parameters  $R_{\text{ZCD},1}$ ,  $R_{\text{ZCD},2}$ ,  $N_{\text{s}}$  and  $N_{\text{a}}$  are configured as per the actual system hardware dimensioning.

# 3.5.3 Output current estimation

Based on the sampled CS pin voltage  $V_{\text{CS,SH}}$  at the timing of  $t_{\text{CS,sample}}$  shown in **Figure 13**, which is at the end of on-time, the primary peak current signal  $I_{\text{p,pk}}$  is sensed. The interval of each  $V_{\text{CS,SH}}$  sample is approximately 1/64 of the half sine wave period.

Note: The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on the operating conditions, as explained in **Line synchronization**.

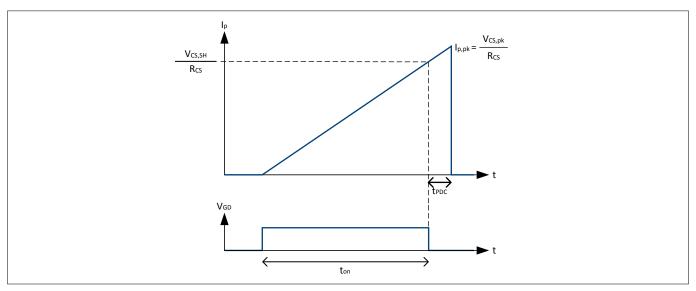

To compensate the propagation delay between the falling edges of *GD* pin voltage and  $I_{p,pk}$ , as shown in *Figure 16*, a more accurate primary peak current  $I_{p,pk}$  can be estimated by optimizing the propagation delay compensation parameter  $t_{pDC}$  value:

$$I_{p, \, \text{pk}} = \frac{V_{\text{CS, SH}}}{R_{\text{CS}}} \cdot \frac{t_{\text{on}} + t_{\text{PDC}}}{t_{\text{on}}}$$

#### **Equation 7**

# **XDP<sup>™</sup> Digital Power**

## **Functional description**

Figure 16 Propagation delay compensation for more accurate primary peak current estimation

The secondary peak current  $I_{s,pk}$  can be estimated based on  $I_{p,pk}$ , transformer turns ratio  $N_p/N_s$ , transformer coupling coefficient  $K_{coupling}$ , primary main winding inductance  $L_p$  and primary leakage inductance  $L_{p,lk}$ :

$$I_{s, pk} = I_{p, pk} \cdot \frac{N_p}{N_s} \cdot K_{\text{coupling}} \cdot \frac{L_p}{L_p + L_{p, lk}}$$

# **Equation 8**

Note:  $L_{p,lk}$  is 1% of  $L_p$  by default.

The average output current per switching cycle  $I_{\text{out}}(n)$  can be estimated based on  $I_{\text{s,pk}}$ , transformer demagnetization time  $t_{\text{demag}}$ , switching period  $t_{\text{sw}}$ , ABM pulse number  $N_{\text{ABM}}$ , line frequency  $f_{\text{line}}$ , DCM minimum switching frequency parameter  $f_{\text{sw,min,DCM}}$ , the estimated output voltage  $V_{\text{out}}$ , output undervoltage protection level  $V_{\text{outUV}}$  and the auxiliary loss compensation parameter  $G_{\text{loss}}$  which is to achieve better load regulation at low output current.

•  $I_{\text{out}}(n)$  in **QRM1** and **DCM**:

$$I_{\text{out, QRM1, DCM}}(n) = \frac{1}{2} \cdot I_{s, \text{pk}} \cdot \frac{t_{\text{demag}}}{t_{\text{sw}}} - G_{\text{out, loss}} \cdot (V_{\text{out}} - V_{\text{outUV}})$$

### **Equation 9**

•  $I_{\text{out}}(n)$  in **ABM**:

$$I_{\text{out,ABM}}(n) = \frac{1}{2} \cdot I_{\text{s,pk}} \cdot \frac{t_{\text{demag}}}{t_{\text{sw}}} \cdot N_{\text{ABM}} \cdot \frac{2 \cdot f_{\text{line}}}{f_{\text{sw,min,DCM}}} - G_{\text{out,loss}} \cdot (V_{\text{out}} - V_{\text{outUV}})$$

## **Equation 10**

The interval of each  $I_{\text{out}}(n)$  sample is approximately 1/64 of the half sine wave period. The average output current per half sine wave period for output regulation is obtained from the moving average filter based on 64  $I_{\text{out}}(n)$  samples.

# XDP™ Digital Power

**Functional description**

Note:

The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on the operating conditions, as explained in **Line synchronization**.

#### **Power factor correction** 3.6

For better **PFC**, the patented enhanced PFC (EPFC) feature can be enabled by configuring  $C_{\text{EMI}}$  parameter value above zero and fine-tuning the value, to compensate the input current displacement effect which is mainly caused by the DC link filter capacitor  $C_{DC,filter}$ . With this feature enabled, in **QRM1**, the regulated on-time is not constant, but modulated with a function based on the estimated input voltage  $V_{\rm in}$ , estimated output voltage  $V_{\text{out}}$ , estimated output current, phase angle and modulation gain of  $C_{\text{EMI}}$  parameter value.

The enhanced PFC (EPFC) feature can also be disabled by configuring  $C_{\text{FMI}}$  parameter as zero.

#### 3.7 **Dimming control**

The XDPL8210 senses the duty cycle of the PWM pin voltage signal, to determine the output current set-point based on the configured dimming curve and maximum power limit setting. In regulated mode, the output current is analogue (except for ABM) and the output ripple frequency is synchronized to the double line frequency, to achieve flicker-free operation.

## PWM pin internal pull up resistor

The PWM pin internal pull up resistor can be optionally enabled by configuring PWM<sub>R,pull,up</sub> parameter between 2.25 kohm and 30 kohm. The internal pull up voltage is 3.2 V typically.

## PWM pin duty cycle sensing and frequency range

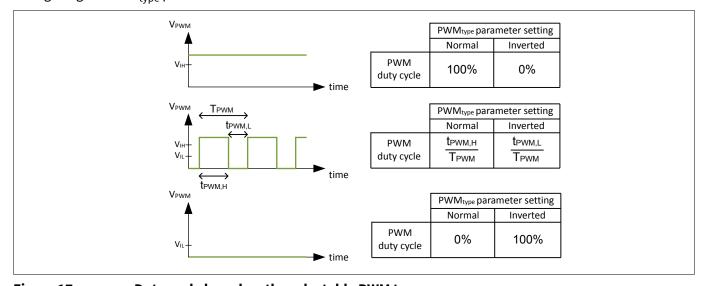

The XDPL8210 can sense the duty cycle based on either a normal *PWM* signal or an inverted PWM signal, by configuring the *PWM*<sub>type</sub> parameter.

Figure 17 Duty cycle based on the selectable PWM type

To sense a stable PWM duty cycle level for the regulation based on a stable output current set-point, a hysteresis level for PWM duty cycle jittering suppression is configurable based on PWM<sub>Dutv,hvst</sub> parameter. Any change of the PWM duty cycle within the hysteresis will not affect the output current.

The PWM frequency should be fixed in the range of 500 Hz and 2 kHz.

# **XDP<sup>™</sup> Digital Power**

# **Functional description**

## **Dimming curve**

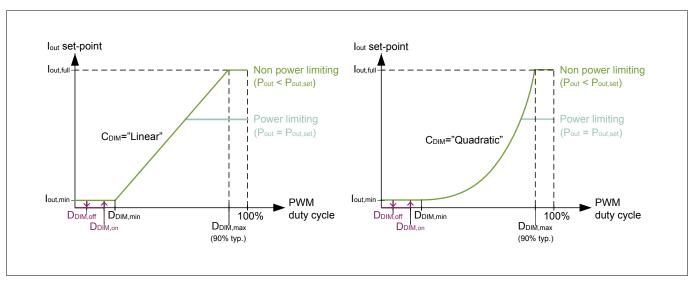

The XDPL8210 can be configured based on  $C_{\rm DIM}$  parameter, to use either a linear or a quadratic dimming curve for the mapping of the PWM duty cycle to the output current set-point, as shown in *Figure 18*. The PWM duty cycle levels of  $D_{\rm DIM,min}$  and  $D_{\rm DIM,max}$  ensure that the minimum current  $I_{\rm out,min}$  and maximum current  $I_{\rm out,full}$  can always be achieved, thereby making the application robust against component tolerances.

Figure 18 Selectable Dimming Curves

If the  $DIM_{\rm type}$  parameter is configured as "Dim (to off)", dim-to-off is entered to turn off the light output when the measured PWM duty cycle gets below  $D_{\rm DIM,off}$  (see purple line in *Figure 18*). During dim-to-off, if the measured PWM duty cycle gets above  $D_{\rm DIM,on}$ , the regulated mode is entered to turn on the light output. After hardware reset, if the first measured PWM duty cycle is above  $D_{\rm DIM,off}$ , the regulated mode is entered to turn on the light output.

During dim-to-off, the output voltage is recharged (based on  $V_{\text{out,start}}$  parameter) to measure the PWM duty cycle, every fast auto-restart period  $t_{\text{auto,restart,fast}}$  of 400 ms approximately. While the PWM duty cycle measurement is ongoing, the controller GD pin switching frequency is based on  $f_{\text{sw,DIM,DCM}}$  of 1 kHz typically. To achieve low standby power during dim-to-off, the sleep mode is entered if the measured PWM duty cycle gets below  $D_{\text{DIM,off}}$ .

Note: A weak passive bleeder on the output is required for proper dim-to-off operation.

If the  $DIM_{\rm type}$  parameter is configured as "Dim (without off)", the light output is not turned off and the output current set-point is based on  $I_{\rm out,min}$  when the measured PWM duty cycle gets below either  $D_{\rm DIM,min}$  or  $D_{\rm DIM,off}$  (see green line in *Figure 18*).

If the output power is limited by  $P_{\text{out,set}}$ , the output current set-point follows the cyan line in *Figure 18* which would result to extended dead travel below  $D_{\text{DIM,max}}$ . As soon as the product of output current and output voltage drops below  $P_{\text{out,set}}$ , the output current will follow the green line, as shown in *Figure 18*)).

## 3.8 Protection features

Protections ensure the operation of the controller under restricted conditions. The protection monitoring signal(s) sampling rate, protection triggering condition(s) and protection reaction are described in this section.

Attention: The sampled protection monitoring signal accuracy is subjective to the digital quantization, tolerances of components (including IC) and estimations with indirect sensing (e.g. input and output voltage estimations based on ZCD, CS pin signals), while the protection level triggering accuracy is subjective to the sampled signal accuracy, sampling delay, indirect sensing delay (e.g. reflected output voltage signal cannot be sensed by ZCD pin near AC input phase angle of 0° and 180°) and blanking time.

XDP™ Digital Power

**Functional description**

#### 3.8.1 **Primary MOSFET overcurrent protection**

$V_{\rm OCP2}$  denotes the CS pin voltage level 2 for primary MOSFET overcurrent protection. Under the single fault condition of shorted primary main winding, the primary MOSFET overcurrent protection is triggered when the CS pin voltage exceeds  $V_{OCP2}$  for longer than a blanking time based on  $t_{CSOCP2}$  parameter.

$t_{CSOCP2}$  parameter is 240 ns by default. Note:

The level of  $V_{OCP2}$  is automatically selected based on #unique 39/unique 39 Connect 42 table dxh gzl jhb.

Table 2 V<sub>OCP2</sub> level selection depending on V<sub>OCP1</sub> parameter value

| V <sub>OCP1</sub> (V) | V <sub>OCP2</sub> (V) |

|-----------------------|-----------------------|

| 0.40 to 0.54          | 0.8                   |

| 0.55 to 0.72          | 1.2                   |

| 0.73 to 1.08          | 1.6                   |

The reaction of primary MOSFET overcurrent protection is fixed as auto-restart.

#### 3.8.2 **Output undervoltage protection**

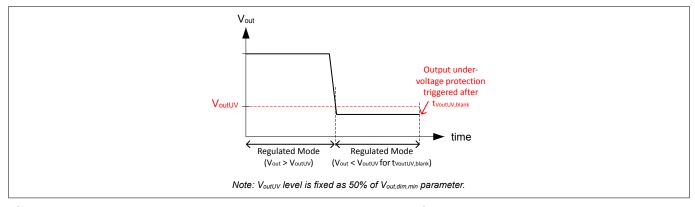

In case of a short or too low LED load voltage, the output voltage would drop to a low level. The output undervoltage protection can be triggered, if the condition is met by monitoring the estimated output voltage V<sub>out</sub> based on the ZCD pin switching signal (see **Output voltage estimation** for details).

In regulated mode, if the estimated output voltage  $V_{\text{out}}$  is lower than the  $V_{\text{outUV}}$  parameter for longer than a blanking time of  $t_{VoutUV,blank}$  parameter, the regulated mode output undervoltage protection is triggered.

The reaction of the regulated mode output undervoltage protection is fixed as auto-restart.

By default,  $V_{\text{outUV}}$  is fixed as 50% of the configurable  $V_{\text{out,dim,min}}$  parameter.  $V_{\text{out,dim,min}}$  denotes the Note: fully dimmed minimum output LED voltage.

Figure 19 Regulated mode output undervoltage protection

In startup phase, if the estimated output voltage  $V_{\text{out}}$  is lower than  $V_{\text{out,start}}$  parameter over a timeout period of  $t_{\text{start,max}}$  parameter, the startup output undervoltage protection is triggered.  $t_{\text{start,max}}$  parameter refers to the maximum allowable duration of the soft-start phase and output charging phase. It can be indirectly configured with *VCC* capacitance parameter  $C_{VCC}$ .

The reaction of startup output undervoltage protection is fixed as auto-restart.

# **XDP<sup>™</sup> Digital Power**

## **Functional description**

Figure 20 Normal startup and startup output undervoltage (short) protection waveforms

#### 3.8.3 **Output overvoltage protection**

In case of output open, the output voltage may rise to a high level. The output overvoltage protection can be triggered, if the condition is met by monitoring the estimated output voltage  $V_{\text{out}}$  based on the ZCD pin switching signal (see **Output voltage estimation** for details).

If the estimated output voltage  $V_{\text{out}}$  is higher than  $V_{\text{outOV}}$  for longer than a blanking time, the output overvoltage protection is triggered.

In **QRM1** and **DCM**, the blanking time is typically a quarter of the half sine wave period. In **ABM**, the Note: blanking time is configurable based on  $t_{VoutOV, blank, ABM}$  parameter.

The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on Note: the operating conditions, as explained in **Line synchronization**.

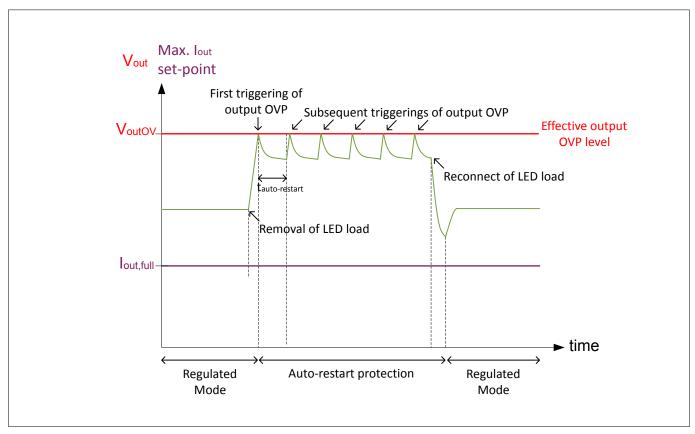

The reaction of the output overvoltage protection is configurable to auto-restart or latch-mode based on Reaction<sub>OVP,Vout</sub> parameter. Figure 21 shows an example of the output overvoltage protection and recovery waveform, based on the auto-restart reaction.

# XDP™ Digital Power

## **Functional description**

Figure 21 Output overvoltage protection and recovery waveform

Attention:

It is mandatory to ensure that V<sub>outOV</sub> is configured well below the actual output capacitor voltage rating Vout, cap, rating , while the Vout, cap, rating is not exceeded in actual testing with all the necessary test conditions. The protection level triggering accuracy is subjective to the sampled signal accuracy, sampling delay, indirect sensing delay (e.g. reflected output voltage signal cannot be sensed by ZCD pin near AC input phase angle of 0° and 180°) and blanking time.

Attention: If the minimum ABM switching pulses number parameter N<sub>ABM,min</sub> and minimum output current parameter I<sub>out,min</sub> configured values are both very low, the output overvoltage protection actual triggering level might drift up when output current set-point is Iout.min.

### Adaptive output overvoltage protection level

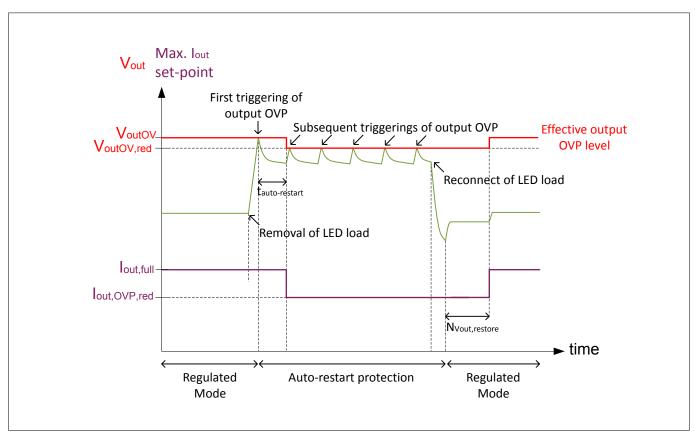

To have lower output open load voltage during auto-restart, the adaptive output overvoltage protection can be enabled with the *EN*<sub>adaptive,OVP,Vout</sub> parameter, as shown in *Figure 22*.

Upon triggering the enabled adaptive output overvoltage protection for the first time, the protection level is reduced from  $V_{\text{out,OV,red}}$  and the output current set-point maximum limit is reduced from  $I_{\text{out,full}}$  to I<sub>out,OVP,red</sub>.

For a successful output recovery, the estimated output voltage  $V_{\rm out}$  upon auto-restart has to be lower than  $V_{\text{out,OV,red}}$  for a number of half sine wave periods based on  $N_{\text{Vout,restore}}$  parameter, in order to restore the protection level and the output current set-point maximum limit to  $V_{\text{out,OV}}$  and  $I_{\text{out,full}}$ , respectively.

# XDP™ Digital Power

### **Functional description**

Figure 22 Adaptive output overvoltage protection and recovery waveform

Note:

The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on the operating conditions, as explained in **Line synchronization**.

#### 3.8.4 Transformer demagnetization time shortage protection

In case of insufficient transformer demagnetization time, the reflected output voltage signal cannot be properly sensed via the ZCD pin. If such condition presents for longer than 50% of a half sine wave period, the protection will be triggered. The reaction of this protection is fixed as auto-restart.

Note:

The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on the operating conditions, as explained in **Line synchronization**.

#### 3.8.5 Regulated mode peak output overcurrent protection

By monitoring the estimated average output current per switching cycle based on the switching signals (see **Output current estimation** for details), the regulated mode peak output overcurrent protection can be triggered if the condition is met.

EN<sub>lout,max,peak</sub> parameter refers to the enable switch for the regulated mode peak output overcurrent protection. Upon startup and in the regulated mode, if EN<sub>lout,max,peak</sub> parameter is enabled and the average output current per switching cycle is higher than  $I_{\text{out,max,peak}}$  for longer than a blanking time, the regulated mode peak output current protection will be triggered. The blanking time is based on  $I_{\text{out,max,peak,blank}}$  parameter.

The reaction of the regulated mode peak output overcurrent protection is fixed as auto-restart. The auto-restart speed is configurable based on Speed<sub>OCP,lout</sub> parameter:

- If Speed<sub>OCP.lout</sub> is configured as "fast", the auto-restart time is approximately 0.4 second.

- If Speed<sub>OCP,lout</sub> is configured as "slow", the auto-restart time is based on the configurable  $t_{auto,restart}$ parameter.

**Functional description**

# 3.8.6 Minimum input voltage startup check and input undervoltage protection

By monitoring the estimated input voltage  $V_{in}$  based on the ZCD pin and CS pin switching signals (see *Input voltage estimation* for details), the minimum input voltage startup check can be performed, and the input undervoltage protection can be triggered if the condition is met.

$EN_{\text{UVP,In}}$  parameter refers to the enable switch for the minimum input voltage startup check (based on  $V_{\text{in,start,min}}$ ) and input undervoltage protection (based on  $V_{\text{inUV}}$ ).

Note:

$V_{\text{in,start,min}}$  parameter refers to the minimum input voltage level for startup, while  $V_{\text{inUV}}$  parameter refers to the input undervoltage protection level.

During pre-startup check, if  $EN_{UVP,In}$  parameter is enabled and the estimated input voltage  $V_{in}$  is lower than  $V_{in,start,min}$ , the startup phase will not be entered and the protection reaction of auto-restart will be performed.

Upon startup and in the regulated mode, if  $EN_{\text{UVP},\text{In}}$  parameter is enabled and the estimated input voltage  $V_{\text{in}}$  is lower than  $V_{\text{inUV}}$  for longer than a blanking time, the input undervoltage protection will be triggered. The blanking time of the input undervoltage protection is typically 10 half sine wave periods.

Note:

The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on the operating conditions, as explained in **Line synchronization**.

The reaction of the input undervoltage protection is fixed as auto-restart.

# 3.8.7 Maximum input voltage startup check and input overvoltage protection

By monitoring the estimated input voltage  $V_{in}$  based on the ZCD pin and CS pin switching signals (see *Input voltage estimation* for details), the maximum input voltage startup check can be performed, and the input overvoltage protection can be triggered if the condition is met.

$EN_{\text{OVP,In}}$  parameter refers to the enable switch for the maximum input voltage startup check (based on  $V_{\text{in,start,max}}$ ) and input overvoltage protection (based on  $V_{\text{inOV}}$ ).

Note:

$V_{\rm in,start,max}$  parameter refers to the maximum input voltage level for startup, while  $V_{\rm inOV}$  parameter refers to the input overvoltage protection level.

During pre-startup check, if  $EN_{OVP,In}$  parameter is enabled and the estimated input voltage  $V_{in}$  is higher than  $V_{in,start,max}$ , the startup phase will not be entered and the protection reaction of auto-restart will be performed.

Upon startup and in the regulated mode, if  $EN_{\text{OVP,In}}$  parameter is enabled and the estimated input voltage  $V_{\text{in}}$  is higher than  $V_{\text{inOV}}$  for longer than a blanking time, the input overvoltage protection will be triggered. The blanking time of the input overvoltage protection is typically 1 half sine wave period.

Note:

The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on the operating conditions, as explained in **Line synchronization**.

The reaction of the input overvoltage protection is fixed as auto-restart.

# 3.8.8 VCC undervoltage lockout

The *Undervoltage Lockout (UVLO)* is implemented in the hardware. It ensures the enabling and disabling of the *IC* operation based on the defined thresholds of the operating supply voltage  $V_{VCC}$  at the *VCC* pin.

The UVLO contains a hysteresis with the voltage thresholds  $V_{VCCon}$  for enabling the controller and  $V_{UVOFF}$  for disabling the controller. Once the mains input voltage is applied, current flows through an external resistor into the HV pin via the integrated depletion cell and diode to the VCC pin. The controller is enabled once  $V_{VCC}$  exceeds the  $V_{VCCon}$  threshold and  $V_{VCC}$  will then start to drop. For normal startup,  $V_{VCC}$  supply should be taken over by either external supply or the self-supply via the auxiliary winding before  $V_{VCC}$  drops to  $V_{UVOFF}$ .

# XDP™ Digital Power

**Functional description**

#### 3.8.9 VCC overvoltage protection

If the sampled VCC voltage is higher than the VCC overvoltage protection level  $V_{VCC,max}$ , the VCC overvoltage protection will be triggered. The VCC overvoltage protection reaction is fixed as auto-restart.

The VCC voltage is sampled once per 7 half sine wave periods.

Note:

The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on the operating conditions, as explained in **Line synchronization**.

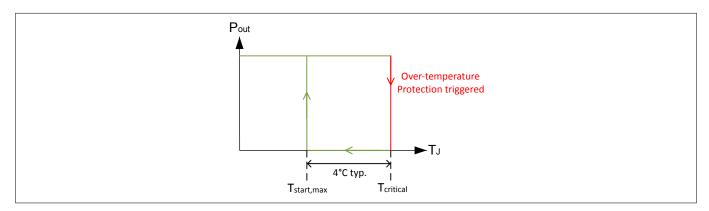

#### 3.8.10 IC overtemperature protection

If the sampled IC junction temperature  $T_i$  is higher than  $T_{critical}$  parameter, the IC overtemperature protection will be triggered. The protection reaction is fixed as auto-restart, while the maximum junction temperature for startup and restart  $T_{\text{start,max}}$  is fixed as 4°C below  $T_{\text{critical}}$ .

The IC junction temperature  $T_i$  is sampled once per 7 half sine wave periods.

Note:

The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on the operating conditions, as explained in **Line synchronization**.

IC lifetime is not guaranteed when operating junction temperature is above 125°C, which is Attention: possible if  $T_{critical}$  is configured above 119°C, with temperature sensing tolerance of  $\pm$  6°C.

Figure 23 IC overtemperature protection

#### 3.8.11 Other protections

- A hardware weak pull-up protects against an open CS pin. The reaction of this protection reaction is

- A firmware watchdog triggers a protection if the ADC hardware cannot provide all necessary information within a defined time period. This may occur if timing requirements for the ADC are exceeded. The reaction of this protection is fast auto-restart.

- A hardware watchdog checks correct execution of firmware. A protection is triggered in the event that the firmware does not service the watchdog within a defined period. The reaction of this protection is auto-restart.

- A hardware parity check triggers a protection if a bit in the memory changes unintentionally. The reaction of this protection is auto-restart.

- A firmware Cyclic Redundancy Check at each startup verifies the integrity of firmware and parameters. The reaction of this protection is stop mode.

- A firmware task execution watchdog triggers a protection if the firmware tasks are not executed as expected. The reaction of this protection is auto-restart.

# **XDP<sup>™</sup> Digital Power**

### **Debug mode**

- A protection is triggered if the configurable parameter values are empty at startup. The reaction of this protection is stop mode.

- A protection is triggered if no reflected input voltage signal sensed from the ZCD pin at startup. The reaction of this protection is stop mode.

#### **Protection reactions** 3.8.12

The sequence of a protection reaction (not including hardware restart reaction) is as follows:

Upon triggering a protection, the gate driver is disabled within a maximum time, which is 1/512 of the half sine wave period.

Note: The half sine wave period is either 9.823 ms or the inverse of the rectified AC input frequency, based on the operating conditions, as explained in **Line synchronization**.

- The reaction depends on the triggered protection: 2.

- In case of latch mode, the application will enter latch mode at this time. No further sequence is done until VCC voltage drops below V<sub>UVOFF</sub>.

- In case of auto-restart reaction, the controller will enter power saving mode PSMD2 with the auto-restart time based on  $t_{\text{auto,restart}}$  parameter.

- In case of fast auto-restart reaction, the controller will enter power saving mode PSMD2 with the fast auto-restart time of 0.4 sec.

Note:

For latch mode, auto-restart and fast auto-restart reactions, the internal HV startup cell is automatically enabled and disabled during this sequence, in order to keep the VCC voltage between the  $V_{UVLO}$  and  $V_{OVLO}$  thresholds.

Note: For stop mode, if there is no external voltage supply for the VCC, the VCC voltage will drain to *V*<sub>UVOFF</sub> and a hardware restart will be performed.

- 3. After the (fast) auto-restart time is expired, the controller executes a single discharge pulse of duration  $t_{\rm pw}$ . This pulse partially discharges the capacitance after the bridge rectifier to improve accuracy of the next pre-startup input voltage check.

- Any auto restart may include a new VCC charging cycle. The recharging time of VCC via HV pin current 4. depends on the input voltage level and VCC level at the time when the (fast) auto-restart time is expired.

- 5. The power stage will enable its gate driver for pre-startup check. If the conditions for pre-startup check are within limits, the startup phase is entered and followed by the regulated mode. During this time, if any protection is triggered, the sequence of a protection reaction (not including hardware restart reaction) starts again from step number 1 above.

#### **Debug mode** 4

If an unexpected system protection was triggered during testing, the *Debug*<sub>Mode</sub> parameter can be enabled to enter stop mode reaction upon the protection triggering (except for VCC undervoltage lockout), to read out the firmware status code. For example in Figure 24, the firmware status code readout in the GUI shows a number of 0040<sub>H</sub> (in red color), which indicates that the input undervoltage protection has been triggered.

If there is no protection being triggered, the firmware status code should be 0000<sub>H</sub> (in black color). Note:

Debug<sub>Mode</sub> parameter should only be enabled for debugging purpose. For actual application running, Note: it has to be disabled.

# **XDP<sup>™</sup> Digital Power**

# **Debug mode**

Figure 24 Firmware status code readout for debugging

Please refer to the design guide for the recommended setup & procedures to read out the firmware status code in debug mode.

# **XDP<sup>™</sup> Digital Power**

**List of Parameters**

#### **List of Parameters** 5

This list provides information about the configurable and fixed parameters.

This document uses symbols to ease the readability of formulas. As some tools do not support this format, the symbols are translated into plain text using underscores. For example, the parameter  $f_{\text{sw.max}}$  translates to f\_sw\_max.

All parameter values are typical settings. The accuracy might vary due to digital quantization and tolerances.

Note:

By default, the configurable parameters of a new XDPL8210 chip from Infineon are empty, so it is necessary to configure them digitally via UART pin before any application testing.

# List of configurable parameters

#### Table 3 Configurable parameters for output set-points

| Symbol                | Basic description                                     | Example | Minimum<br>value | Maximum<br>value |

|-----------------------|-------------------------------------------------------|---------|------------------|------------------|

| I <sub>out,full</sub> | Steady-state maximum output current set-point         | 830 mA  | Refer GUI        | Refer GUI        |

| P <sub>out,set</sub>  | Steady-state maximum output power limit set-<br>point | 34.5 W  | Refer GUI        | Refer GUI        |

#### Table 4 Configurable parameters for dimming

| Symbol                   | Basic description                                                | Example      | Minimum<br>value                                               | Maximum<br>value      |

|--------------------------|------------------------------------------------------------------|--------------|----------------------------------------------------------------|-----------------------|

| DIM <sub>type</sub>      | Dimming type via <i>PWM</i> pin                                  | Dim (to off) | <ul><li>Non-dim</li><li>Dim (with</li><li>Dim (to of</li></ul> | •                     |

| I <sub>out,min</sub>     | Minimum output current set-point                                 | 41.5 mA      | Refer GUI                                                      | I <sub>out,full</sub> |

| C <sub>DIM</sub>         | Shape of the dimming curve                                       | Linear       | <ul><li>Linear</li><li>Quadratic</li></ul>                     |                       |

| PWM <sub>type</sub>      | PWM type                                                         | Inverted     | <ul><li>Normal</li><li>Inverted</li></ul>                      |                       |

| f <sub>PWM,max</sub>     | Maximum switching frequency of PWM dimming signal                | 1050 Hz      | f <sub>PWM,min</sub>                                           | 2000 Hz               |

| $f_{PWM,min}$            | Minimum switching frequency of PWM dimming signal                | 950 Hz       | 500 Hz                                                         | f <sub>PWM,max</sub>  |

| D <sub>DIM,max</sub>     | PWM duty cycle level for maximum output current                  | 90%          | $D_{DIM,min}$                                                  | Refer GUI             |

| D <sub>DIM,min</sub>     | PWM duty cycle level for minimum output current                  | 15%          | $D_{DIM,off}$                                                  | D <sub>DIM,max</sub>  |

| D <sub>DIM,on</sub>      | PWM duty cycle level for exiting dim-to-off                      | 11%          | $D_{DIM,off}$                                                  | D <sub>DIM,min</sub>  |

| $D_{DIM,off}$            | PWM duty cycle level for entering dim-to-off                     | 10%          | Refer GUI                                                      | D <sub>DIM,min</sub>  |

| PWM <sub>Duty,hyst</sub> | Hysteresis level for <i>PWM</i> duty cycle jittering suppression | 0.1%         | 0%                                                             | 2%                    |

# **List of Parameters**

# Table 5 Configurable parameters for hardware configuration

| Symbol                      | Basic description                           | Example  | Minimum<br>value                                       | Maximum<br>value |  |

|-----------------------------|---------------------------------------------|----------|--------------------------------------------------------|------------------|--|

| $\overline{N_{p}}$          | Transformer primary main winding turns      | 58       | 1                                                      | 300              |  |

| N <sub>s</sub>              | Transformer secondary main winding turns    | 17       | 1                                                      | 300              |  |

| N <sub>a</sub>              | Transformer primary auxiliary winding turns | 15       | 1                                                      | 300              |  |

| $L_{p}$                     | Transformer primary main winding inductance | 0.566 mH | Refer GUI                                              | 3 mH             |  |

| R <sub>CS</sub>             | Current sense resistor value                | 0.22 Ω   | 0.1 Ω                                                  | 3 Ω              |  |

| $R_{\rm ZCD,1}$             | ZCD series resistor                         | 56.2 kΩ  | Refer GUI                                              | 255 kΩ           |  |

| $R_{ZCD,2}$                 | ZCD shunt resistor                          | 2.7 kΩ   | Refer GUI                                              | Refer GUI        |  |

| VCC <sub>supply</sub>       | VCC voltage supply                          | Wide     | <ul><li>Wide</li><li>Narrow</li><li>External</li></ul> |                  |  |

| C <sub>VCC</sub>            | VCC capacitor value                         | 15 μF    | Refer GUI                                              | 100 μF           |  |

| V <sub>out,cap,rating</sub> | Output capacitor voltage rating             | 80 V     | 10 V                                                   | 450 V            |  |

| $R_{HV}$                    | HV series resistor                          | 100 kΩ   | Refer GUI                                              | 255 kΩ           |  |

| $I_{\rm GD,pk}$             | Gate driver peak source current             | 30 mA    | 30 mA                                                  | 118 mA           |  |

| PWM <sub>R,pull,up</sub>    | PWM pin internal pull up resistor           | 2.25 kΩ  | 2.25 kΩ to 30 kΩ, or Disable                           |                  |  |

# Table 6Configurable parameters for startup

| Symbol                   | Basic description                                                                                                  | Example | Minimum<br>value                | Maximum value            |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|---------|---------------------------------|--------------------------|

| $n_{\rm ss}$             | Number of soft start steps                                                                                         | 20      | 1                               | 20                       |

| $V_{\text{out,dim,min}}$ | Minimum output voltage when fully dimmed                                                                           | 12 V    | V <sub>out,start</sub>          | $V_{\text{outOV}}$       |

| V <sub>out,start</sub>   | Output charging phase output voltage set-point                                                                     | 10.5 V  | 50% of V <sub>out,dim,min</sub> | V <sub>out,dim,min</sub> |

| V <sub>start,OCP1</sub>  | Output charging phase CS pin voltage level 1 for MOSFET max. current cycle by cycle limit                          | 0.5 V   | Refer GUI                       | V <sub>OCP1</sub>        |

| V <sub>OCP1,init</sub>   | Initial CS pin voltage level 1 for MOSFET max. current limit on the input voltage measurement pulse before startup | 0.3 V   | Refer GUI                       | V <sub>OCP1</sub>        |

# Table 7 Configurable parameters for protections

| Symbol                       | Basic description                                                                         | Example          | Minimum<br>value         | Maximum<br>value |

|------------------------------|-------------------------------------------------------------------------------------------|------------------|--------------------------|------------------|

| t <sub>auto,restart</sub>    | Auto-restart time                                                                         | 1.6 s            | 0.4 s                    | 4.0 s            |

| $\overline{V_{\text{OCP1}}}$ | Regulated mode <i>CS</i> pin voltage level 1 for MOSFET max. current cycle by cycle limit | 0.5 V            | Refer GUI                | 1.08 V           |

| Reaction <sub>OVP,Vou</sub>  | Output overvoltage protection reaction                                                    | Auto-<br>restart | Auto-restart             | Latch-Mode       |

| $V_{\text{outOV}}$           | Output overvoltage protection level                                                       | 56.9 V           | V <sub>out,dim,min</sub> | Refer GUI        |

(table continues...)

# **List of Parameters**

# Table 7 (continued) Configurable parameters for protections

| Symbol                               | Basic description                                                                                                                                                                        | Example              | Minimum<br>value          | Maximum<br>value          |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------|---------------------------|

| t <sub>VoutOV,blank,</sub> ABM       | Output overvoltage protection blanking time in <b>ABM</b>                                                                                                                                | 0.5 ms               | 0.2 ms                    | 5.0 ms                    |

| EN <sub>adaptive</sub> ,OVP,Vo<br>ut | Enable switch for adaptive output overvoltage protection level                                                                                                                           | Enabled              | Enabled                   | Disabled                  |

| V <sub>outOV,red</sub>               | Output overvoltage protection level applied during auto-restart when the last triggered protection is output overvoltage protection with <i>EN</i> <sub>adaptive,OVP,Vout</sub> enabled. | 51.3 V               | V <sub>out,dim,min</sub>  | V <sub>outOV</sub>        |

| I <sub>out,OVP,red</sub>             | Output current set point max. limit applied during auto-restart when the last triggered protection is output overvoltage protection with <i>EN</i> <sub>adaptive,OVP,Vout</sub> enabled. | 41.5 mA              | $I_{ m out,min}$          | I <sub>out,full</sub>     |

| N <sub>Vout,</sub> restore           | Blanking time for output voltage below $V_{\text{outOV,red}}$ to exit output overvoltage protection with $EN_{\text{adaptive,OVP,Vout}}$ enabled.                                        | 500                  | 0                         | 5000                      |

| t <sub>VoutUV</sub> ,blank           | Blanking time for regulated mode output undervoltage protection                                                                                                                          | 40 ms                | 40 ms                     | 1000 ms                   |

| EN <sub>lout,max,peak</sub>          | Enable switch for peak output overcurrent protection                                                                                                                                     | Enabled              | Enabled                   | Disabled                  |

| I <sub>out,max,peak</sub>            | Peak output overcurrent protection level                                                                                                                                                 | 2100 mA              | Refer GUI                 | Refer GUI                 |

| t <sub>lout,max,peak,bla</sub><br>nk | Blanking time for peak output overcurrent protection                                                                                                                                     | 1 ms                 | 0 ms                      | 5 ms                      |

| Speed <sub>OCP,lout</sub>            | Auto-restart speed for peak output overcurrent protection                                                                                                                                | Fast                 | Slow                      | Fast                      |

| EN <sub>OVP,In</sub>                 | Enable switch for maximum input voltage startup check and input overvoltage protection                                                                                                   | Enabled              | Enabled                   | Disabled                  |

| EN <sub>UVP,In</sub>                 | Enable switch for minimum input voltage startup check and input undervoltage protection                                                                                                  | Enabled              | Enabled                   | Disabled                  |

| $V_{inOV}$                           | Input overvoltage protection level (rms in case of AC input)                                                                                                                             | 352 V <sub>rms</sub> | V <sub>in,start,max</sub> | Refer GUI                 |

| V <sub>in,start,max</sub>            | Maximum input voltage level at startup (rms in case of AC input)                                                                                                                         | 326 V <sub>rms</sub> | V <sub>in,start,min</sub> | V <sub>inOV</sub>         |

| V <sub>in,start,min</sub>            | Minimum input voltage level at startup (rms in case of AC input)                                                                                                                         | 80 V <sub>rms</sub>  | V <sub>inUV</sub>         | Refer GUI                 |

| $V_{inUV}$                           | Input undervoltage protection level (rms in case of AC input)                                                                                                                            | 63 V <sub>rms</sub>  | Refer GUI                 | V <sub>in,start,min</sub> |

| $T_{ m critical}$                    | Temperature threshold for IC overtemperature protection                                                                                                                                  | 119°C                | Refer GUI                 | 143°C                     |

| Debug <sub>Mode</sub>                | Enable switch for debug mode                                                                                                                                                             | Disabled             | Enabled                   | Disabled                  |

# infineon

# **List of Parameters**

# Table 8 Configurable parameters for multimode

| Symbol                         | Basic description                                                                                                                                | Example              | Minimum<br>value          | Maximum<br>value    |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------|---------------------|

| $\overline{f_{\text{sw,max}}}$ | Maximum switching frequency for <b>QRM1</b> and <b>DCM</b>                                                                                       | 70 kHz               | 20 kHz                    | Refer GUI           |

| $N_{DCM,mod,gain}$             | Switching period modulation attenuation                                                                                                          | 16                   | 0 (disabled),             | 4, 8, 16, 32        |

| t <sub>on,min</sub>            | Minimum on-time $t_{\text{on,min}}(V_{\text{in}})$ value when $t_{\text{on,min,V,out,sense}}(V_{\text{in}})$ is lower than $t_{\text{on,min}}$   | 2 μs                 | Refer GUI                 | t <sub>on,max</sub> |

| $t_{ m min,demag}$             | Minimum transformer demagnetizing time value used for $t_{\rm on,min,V,out,sense}(V_{\rm in})$ variable calculation internally                   | 3 μs                 | 3 μs                      | Refer GUI           |

| t <sub>on,max</sub>            | Maximum on-time                                                                                                                                  | 11.5 μs              | Refer GUI                 | 30 μs               |

| $f_{\text{sw,min,DCM}}$        | Minimum switching frequency in DCM                                                                                                               | 20 kHz               | Refer GUI                 | 20 kHz              |

| EN <sub>ABM</sub>              | Enable switch for ABM                                                                                                                            | Enabled              | Enabled                   | Disabled            |

| $N_{ABM,min}$                  | Minimum number of pulses per burst                                                                                                               | 11                   | 4                         | Refer GUI           |

| N <sub>ABM,init,VinUV</sub>    | Initial number of pulses per burst when $EN_{ABM}$ is enabled and $V_{in}$ is near to input undervoltage protection level $V_{inUV}$             | 132                  | N <sub>ABM,min</sub>      | Refer GUI           |

| V <sub>in,high</sub>           | Input voltage level which when exceeded, the initial number of pulses per burst is fixed as $N_{\text{ABM,min}}$ if $EN_{\text{ABM}}$ is enabled | 277 V <sub>rms</sub> | V <sub>in,start,min</sub> | $V_{\rm inOV}$      |

# Table 9 Configurable parameters for control loop response

| Symbol                        | Basic description                                                                     |      | Minimum<br>value | Maximum<br>value |

|-------------------------------|---------------------------------------------------------------------------------------|------|------------------|------------------|

| $K_{P,QRM}$                   | Proportional gain of control loop in QRM1                                             | 512  | 10               | 3000             |

| $K_{I,QRM}$                   | Integral gain of control loop in QRM1                                                 | 32   | 1                | 1000             |

| $K_{P,DCM}$                   | Proportional gain of control loop in DCM                                              | 2048 | 100              | 30000            |

| $K_{I,DCM}$                   | Integral gain of control loop in DCM                                                  | 512  | 10               | 10000            |

| $K_{P,ABM}$                   | Proportional gain of control loop in ABM                                              | 128  | 1                | 600              |

| K <sub>I,ABM</sub>            | Integral gain of control loop in ABM                                                  | 32   | 1                | 200              |

| ABM <sub>thrs,multiplie</sub> | Minimum set-point error threshold multiplier to activate control loop response in ABM | 3    | 0                | 10               |

# Table 10 Parameters for power factor correction

| Symbol           | Basic description                                                       | Example | Minimum<br>value | Maximum<br>value |