# Intel<sup>®</sup> NUC Board/Kit NUC7i3DN Technical Product Specification

October 2019

Intel<sup>®</sup> NUC Board NUC7i3DN may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata, if any, are documented in Intel NUC Board NUC7i3DN Specification Update.

# **Revision History**

| Revision | Revision History                                                                  | Date           |

|----------|-----------------------------------------------------------------------------------|----------------|

| 100      | First release of the Intel NUC Board/Kit NUC7i3DN Technical Product Specification | September 2017 |

| 101      | Additional Specifications                                                         | September 2017 |

| 102      | Clarifying Specifications                                                         | October 2017   |

| 103      | Additional Explanations                                                           | January 2018   |

| 104      | Added Clarifications                                                              | February 2018  |

| 105      | Added clarifications for supported technologies                                   | June 2018      |

| 106      | Added additional Intel NUC Kit information                                        | June 2018      |

| 107      | Added clarification to Wireless information in Feature Summary section            | September 2018 |

| 108      | Specification Clarification                                                       | October 2018   |

| 109      | Specification Clarification                                                       | November 2018  |

| 110      | Specification Clarification                                                       | November 2018  |

| 111      | Added section 2.5.2 - Weights                                                     | February 2019  |

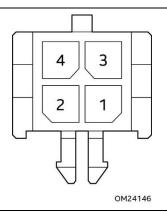

| 112      | Updated image for section 2.2.4 to show correct pin 1 position                    | October 2019   |

| 113      | Specification Clarification                                                       | October 2019   |

### Disclaimer

This product specification applies to only the standard Intel NUC Board with BIOS identifier DNKBLi30.86A. INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>\*</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

All Intel NUC Boards are evaluated as Information Technology Equipment (I.T.E.) for use in personal computers (PC) for installation in homes, offices, schools, computer rooms, and similar locations. The suitability of this product for other PC or embedded non-PC applications or other environments, such as medical, industrial, alarm systems, test equipment, etc. may not be supported without further evaluation by Intel.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families: Go to: Learn About Intel<sup>®</sup> Processor Numbers

Intel NUC may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Intel, the Intel logo, Intel NUC and Intel Core are trademarks of Intel Corporation in the U.S. and/or other countries. \* Other names and brands may be claimed as the property of others.

Copyright © 2019 Intel Corporation. All rights reserved.

## **Board Identification Information**

#### Basic Intel® NUC Board NUC7i3DNBE Identification Information

| AA Revision | BIOS Revision     | Notes |

|-------------|-------------------|-------|

| J57625-506  | DNKBLi30.86A.0056 | 1,2   |

Notes:

1. The AA number is found on a small label on the component side of the board.

2. The Intel<sup>®</sup> Core<sup>™</sup> i3-7100U processor is used on this AA revision consisting of the following component:

| Device        | Stepping | S-Spec Numbers |

|---------------|----------|----------------|

| Intel Core i3 | ВО       | SR343          |

## **Production Identification Information**

#### Intel® NUC Products NUC7i3DN{x} Identification Information

| Product Name | Intel <sup>®</sup> NUC Board | Differentiating Features                                                             |

|--------------|------------------------------|--------------------------------------------------------------------------------------|

| NUC7i3DNKE   |                              | Kit with power adapter                                                               |

| NUC7i3DNHE   |                              | HDD kit with power adapter                                                           |

| NUC7i3DNBE   |                              | Board                                                                                |

| NUC7i3DNKTC  | NUC7i3DNB                    | Kit with power adapter, Intel 128GB M.2 NVMe SSD,<br>4GB DDR4 SDRAM, Windows* 10 Pro |

| NUC7i3DNHNC  |                              | HDD kit with power adapter, 1TB HDD, 4GB DDR4<br>SDRAM, Windows* 10 Pro              |

Complete information on the Intel NUC Kits based upon this board are available on https://ark.intel.com.

# **Specification Changes or Clarifications**

The table below indicates the Specification Changes or Specification Clarifications that apply to the Intel NUC Board/Kit NUC7i3DN.

| Date       | Type of Change | Description of Changes or Clarifications                                                                                                                                                                                                |

|------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2/2/2018   | Clarification  | Pin 1 designator on board silkscreen is incorrect for the following headers and connectors: USB 2.0, HDMI CEC, Serial Port, SATA Power, and eDP. The pinout information and pin 1 designators in the TPS are correct for these headers. |

| 09/07/2018 | Clarification  | Added text to Wireless row of table in Feature Summary section:                                                                                                                                                                         |

|            |                | "Pre-installed M.2 module"                                                                                                                                                                                                              |

| 11/12/2018 | Clarification  | Updated "Headless display emulation" and "Persistent display emulation" information in "EDID Emulation Modes" section.                                                                                                                  |

| 11/29/2018 | Clarification  | In the "Integrated Audio Provided by the HDMI interfaces" section, changed "192kHz/16-bit" to "192kHz/24-bit"                                                                                                                           |

| 10/21/2019 | Clarification  | Clarified Board vs Kit environmental specifications.                                                                                                                                                                                    |

#### **Specification Changes or Clarifications**

## Errata

Current characterized errata, if any, are documented in a separate Specification Update. See <u>https://www.intel.com/content/www/us/en/nuc/overview.html</u> for the latest documentation.

# Preface

This Technical Product Specification (TPS) specifies the board layout, components, connectors, power and environmental requirements, and the BIOS for Intel® NUC Board/Kits NUC7i3DN. Some features are only available on Kit SKUs.

## **Intended Audience**

The TPS is intended to provide detailed, technical information about Intel® NUC Board/Kit NUC7i3DN and its components to the vendors, system integrators, and other engineers and technicians who need this level of information. It is specifically not intended for general audiences.

# What This Document Contains

| Chapter | Description                                                          |

|---------|----------------------------------------------------------------------|

| 1       | A description of the hardware used on Intel® NUC Board NUC7i3DNBE    |

| 2       | A map of the resources of the Intel® NUC Board                       |

| 3       | The features supported by the BIOS Setup program                     |

| 4       | A description of the BIOS error messages, beep codes, and POST codes |

# **Typographical Conventions**

This section contains information about the conventions used in this specification. Not all of these symbols and abbreviations appear in all specifications of this type.

### Notes, Cautions, and Warnings

# NOTE

Notes call attention to important information.

#

Cautions are included to help you avoid damaging hardware or losing data.

| #     | Used after a signal name to identify an active-low signal (such as USBPO#)                                     |

|-------|----------------------------------------------------------------------------------------------------------------|

| GB    | Gigabyte (1,073,741,824 bytes)                                                                                 |

| GB/s  | Gigabytes per second                                                                                           |

| Gb/s  | Gigabits per second                                                                                            |

| КВ    | Kilobyte (1024 bytes)                                                                                          |

| Kb    | Kilobit (1024 bits)                                                                                            |

| kb/s  | 1000 bits per second                                                                                           |

| MB    | Megabyte (1,048,576 bytes)                                                                                     |

| MB/s  | Megabytes per second                                                                                           |

| Mb    | Megabit (1,048,576 bits)                                                                                       |

| Mb/s  | Megabits per second                                                                                            |

| TDP   | Thermal Design Power                                                                                           |

| xxh   | An address or data value ending with a lowercase h indicates a hexadecimal value.                              |

| x.x V | Volts. Voltages are DC unless otherwise specified.                                                             |

| x.x A | Amperes.                                                                                                       |

| *     | This symbol is used to indicate third-party brands and names that are the property of their respective owners. |

## **Other Common Notation**

# Contents

| Re | evisio            | on Hist  | ory                                         | ii |

|----|-------------------|----------|---------------------------------------------|----|

|    |                   |          |                                             |    |

|    |                   |          | fication Information                        |    |

|    |                   |          |                                             |    |

|    |                   |          |                                             |    |

| Pr | efac              | е        |                                             | vi |

|    | Inter             | nded Au  | dience                                      | vi |

|    | Wha               | t This D | ocument Contains                            | vi |

|    | Туро              | ographic | cal Conventions                             | vi |

| Co | onter             | nts      |                                             | ix |

| 1  | Pro               | duct D   | escription                                  |    |

|    | 1.1               | Overvie  | ew                                          |    |

|    |                   | 1.1.1    | Feature Summary                             |    |

|    |                   | 1.1.2    | Board Layout (Top)                          | 15 |

|    |                   | 1.1.3    | Board Layout (Bottom)                       |    |

|    |                   | 1.1.4    | Block Diagram                               |    |

|    | 1.2               | Online   | Support                                     | 19 |

|    | 1.3               | Proces   | sor                                         | 19 |

|    | 1.4 System Memory |          | 19                                          |    |

|    | 1.5               | Proces   | sor Graphics Subsystem                      | 22 |

|    |                   | 1.5.1    | Integrated Graphics                         | 22 |

|    | 1.6               | USB      |                                             | 26 |

|    | 1.7               | SATA I   | nterface                                    | 26 |

|    |                   | 1.7.1    | AHCI Mode                                   | 26 |

|    |                   | 1.7.2    | NVMe                                        | 27 |

|    |                   | 1.7.3    | Intel® Rapid Storage Technology / SATA RAID | 27 |

|    |                   | 1.7.4    | Intel® Next Generation Storage Acceleration | 27 |

|    | Real              |          | lock Subsystem                              |    |

|    | 1.8               |          | Subsystem Software                          |    |

|    |                   | 1.8.1    | NUC7i3DNHNC Audio Priority                  |    |

|    |                   | 1.8.2    | Audio Subsystem Software                    |    |

|    | 1.9               |          | ıbsystem                                    |    |

|    |                   | 1.9.1    | Intel® I219LM Gigabit Ethernet Controller   |    |

|    |                   | 1.9.2    | RJ-45 LAN Connector with Integrated LEDs    |    |

|    |                   | 1.9.3    | Wireless Network Module                     |    |

|    | 1.10              |          | are Management Subsystem                    |    |

|    |                   | 1.10.1   | Hardware Monitoring                         |    |

|    |                   | 1.10.2   | Fan Monitoring                              |    |

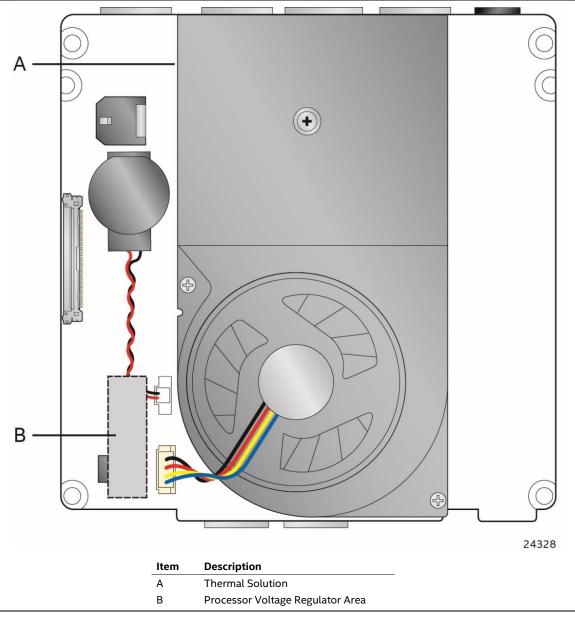

|    |                   | 1.10.3   | Thermal Solution                            |    |

|   | 1.11                                                                                                                                                | Power Management                                                                                                                                                                                                                                                                                        | 32                                   |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|   |                                                                                                                                                     | 1.11.1 ACPI                                                                                                                                                                                                                                                                                             |                                      |

|   |                                                                                                                                                     | 1.11.2 Hardware Support                                                                                                                                                                                                                                                                                 |                                      |

|   | 1.12                                                                                                                                                | Intel® Platform Security Technologies                                                                                                                                                                                                                                                                   | 36                                   |

| 2 | Тес                                                                                                                                                 | hnical Reference                                                                                                                                                                                                                                                                                        | 39                                   |

|   | 2.1                                                                                                                                                 | Memory Resources                                                                                                                                                                                                                                                                                        |                                      |

|   |                                                                                                                                                     | 2.1.1 Addressable Memory                                                                                                                                                                                                                                                                                |                                      |

|   | 2.2                                                                                                                                                 | Connectors and Headers                                                                                                                                                                                                                                                                                  | 39                                   |

|   |                                                                                                                                                     | 2.2.1 Front Panel Connectors                                                                                                                                                                                                                                                                            | 40                                   |

|   |                                                                                                                                                     | 2.2.2 Back Panel Connectors                                                                                                                                                                                                                                                                             |                                      |

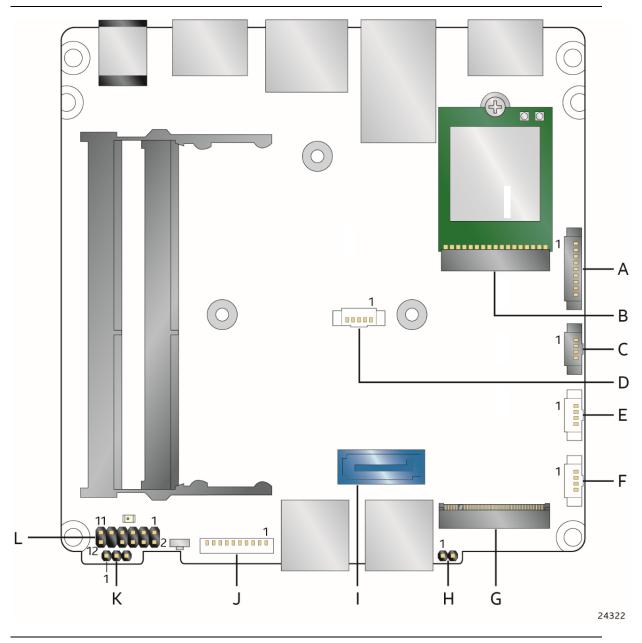

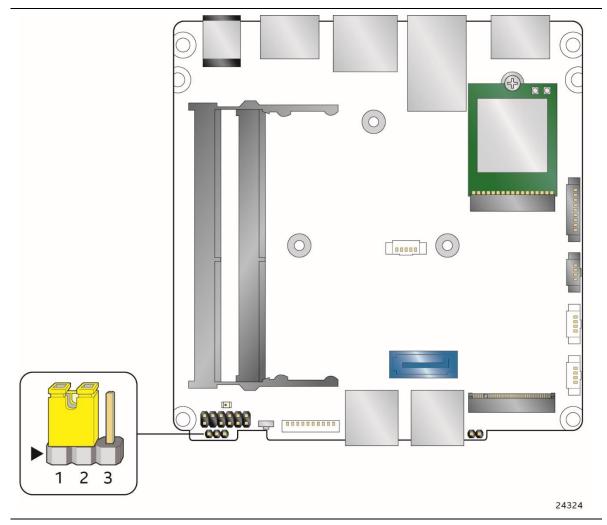

|   |                                                                                                                                                     | 2.2.3 Connectors and Headers (Top)                                                                                                                                                                                                                                                                      | 41                                   |

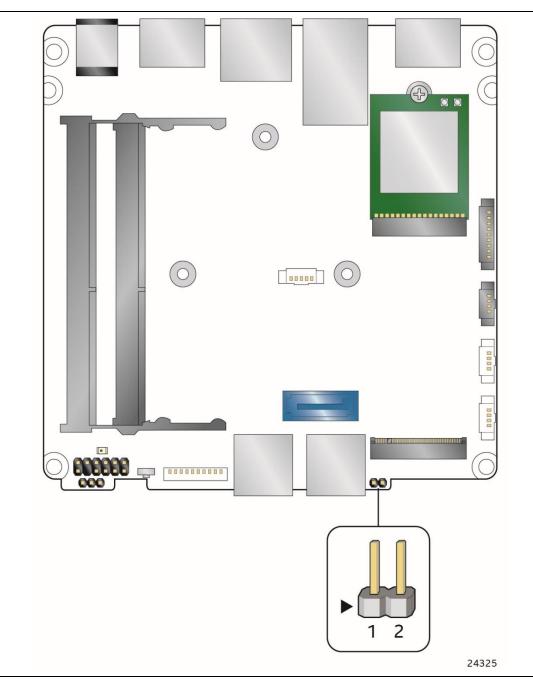

|   |                                                                                                                                                     | 2.2.4 Connectors and Headers (Bottom)                                                                                                                                                                                                                                                                   |                                      |

|   | 2.3                                                                                                                                                 | BIOS Security Jumper                                                                                                                                                                                                                                                                                    |                                      |

|   | 2.4                                                                                                                                                 | Intel® Management Engine BIOS Extension (Intel® MEBX) Reset Header                                                                                                                                                                                                                                      |                                      |

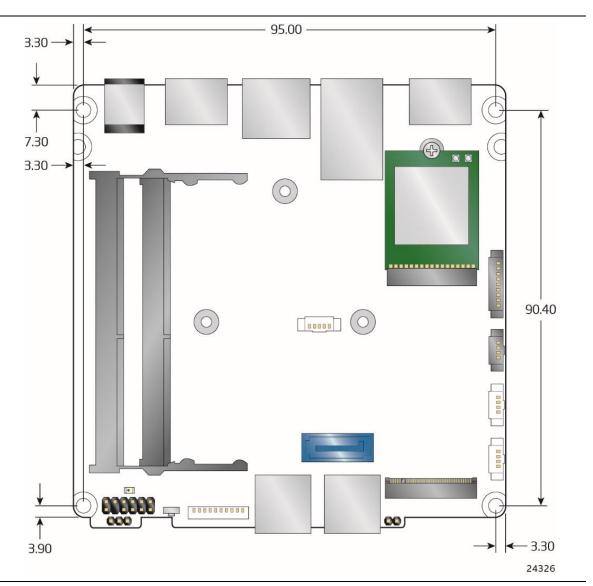

|   | 2.5                                                                                                                                                 | Mechanical Considerations                                                                                                                                                                                                                                                                               |                                      |

|   |                                                                                                                                                     | 2.5.1 Form Factor                                                                                                                                                                                                                                                                                       |                                      |

|   |                                                                                                                                                     | 2.5.2 Weights                                                                                                                                                                                                                                                                                           |                                      |

|   | 2.6                                                                                                                                                 | Electrical Considerations                                                                                                                                                                                                                                                                               |                                      |

|   |                                                                                                                                                     | 2.6.1 Power Supply Considerations                                                                                                                                                                                                                                                                       |                                      |

|   |                                                                                                                                                     | 2.6.2 Fan Header Current Capability                                                                                                                                                                                                                                                                     |                                      |

|   | 2.7                                                                                                                                                 | Thermal Considerations                                                                                                                                                                                                                                                                                  |                                      |

|   | 2.8                                                                                                                                                 | Reliability                                                                                                                                                                                                                                                                                             | 65                                   |

|   |                                                                                                                                                     | _ · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                 |                                      |

|   | 2.9                                                                                                                                                 | Environmental                                                                                                                                                                                                                                                                                           |                                      |

| 3 | 2.9                                                                                                                                                 | Environmental                                                                                                                                                                                                                                                                                           | 65                                   |

| 3 | 2.9                                                                                                                                                 |                                                                                                                                                                                                                                                                                                         | 65<br><b> 67</b>                     |

| 3 | 2.9<br><b>Ove</b>                                                                                                                                   | erview of BIOS Features                                                                                                                                                                                                                                                                                 | 65<br><b>67</b><br>67                |

| 3 | 2.9<br><b>Ove</b><br>3.1                                                                                                                            | erview of BIOS Features<br>Introduction<br>BIOS Flash Memory Organization<br>System Management BIOS (SMBIOS)                                                                                                                                                                                            | 65<br>67<br>67<br>67<br>67           |

| 3 | 2.9<br><b>Ove</b><br>3.1<br>3.2                                                                                                                     | erview of BIOS Features<br>Introduction<br>BIOS Flash Memory Organization<br>System Management BIOS (SMBIOS)<br>Legacy USB Support                                                                                                                                                                      | 65<br>67<br>67<br>67<br>67<br>68     |

| 3 | 2.9<br><b>Ove</b><br>3.1<br>3.2<br>3.3                                                                                                              | erview of BIOS Features<br>Introduction<br>BIOS Flash Memory Organization<br>System Management BIOS (SMBIOS)<br>Legacy USB Support<br>BIOS Updates                                                                                                                                                      |                                      |

| 3 | 2.9<br><b>Ove</b><br>3.1<br>3.2<br>3.3<br>3.4                                                                                                       | erview of BIOS Features<br>Introduction<br>BIOS Flash Memory Organization<br>System Management BIOS (SMBIOS)<br>Legacy USB Support<br>BIOS Updates<br>3.5.1 Language Support                                                                                                                            |                                      |

| 3 | 2.9<br><b>Ove</b><br>3.1<br>3.2<br>3.3<br>3.4                                                                                                       | Prview of BIOS Features<br>Introduction<br>BIOS Flash Memory Organization<br>System Management BIOS (SMBIOS)<br>Legacy USB Support<br>BIOS Updates<br>3.5.1 Language Support<br>3.5.2 BIOS Recovery.                                                                                                    |                                      |

| 3 | 2.9<br><b>Ove</b><br>3.1<br>3.2<br>3.3<br>3.4                                                                                                       | Prview of BIOS Features<br>Introduction<br>BIOS Flash Memory Organization<br>System Management BIOS (SMBIOS)<br>Legacy USB Support<br>BIOS Updates<br>3.5.1 Language Support<br>3.5.2 BIOS Recovery<br>Boot Options                                                                                     |                                      |

| 3 | 2.9<br><b>Ove</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                                                                | erview of BIOS Features<br>Introduction<br>BIOS Flash Memory Organization<br>System Management BIOS (SMBIOS)<br>Legacy USB Support<br>BIOS Updates<br>3.5.1 Language Support<br>3.5.2 BIOS Recovery<br>Boot Options<br>3.6.1 Network Boot                                                               |                                      |

| 3 | 2.9<br><b>Ove</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                                                                | Introduction<br>BIOS Flash Memory Organization<br>System Management BIOS (SMBIOS)<br>Legacy USB Support<br>BIOS Updates<br>3.5.1 Language Support<br>3.5.2 BIOS Recovery<br>Boot Options<br>3.6.1 Network Boot<br>3.6.2 Booting Without Attached Devices                                                |                                      |

| 3 | 2.9<br><b>Ove</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                                                                | Prview of BIOS Features<br>Introduction<br>BIOS Flash Memory Organization<br>System Management BIOS (SMBIOS)<br>Legacy USB Support<br>BIOS Updates<br>3.5.1 Language Support<br>3.5.2 BIOS Recovery<br>Boot Options<br>3.6.1 Network Boot<br>3.6.2 Booting Without Attached Devices<br>3.6.3 iSCSI Boot |                                      |

| 3 | 2.9<br><b>Ove</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                                                                | Prview of BIOS Features<br>Introduction                                                                                                                                                                                                                                                                 |                                      |

| 3 | 2.9<br>Ove<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                                                | erview of BIOS Features<br>Introduction                                                                                                                                                                                                                                                                 |                                      |

| 3 | <ul> <li>2.9</li> <li><b>Ove</b></li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ul>                           | Introduction<br>BIOS Flash Memory Organization                                                                                                                                                                                                                                                          |                                      |

| 3 | 2.9<br>Ove<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                                                | erview of BIOS Features<br>Introduction                                                                                                                                                                                                                                                                 |                                      |

| 3 | <ul> <li>2.9</li> <li><b>Ove</b></li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> </ul> | Introduction<br>BIOS Flash Memory Organization                                                                                                                                                                                                                                                          | 656767676768686969707070707071727375 |

|   | <ul> <li>2.9</li> <li><b>Ove</b></li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> </ul> | Introduction<br>BIOS Flash Memory Organization                                                                                                                                                                                                                                                          |                                      |

## Figures

| Figure 1. Major Board Components (Top)                                | 15 |

|-----------------------------------------------------------------------|----|

| Figure 2. Major Board Components (Bottom)                             | 16 |

| Figure 3. Block Diagram                                               | 18 |

| Figure 4. Memory Channel and SO-DIMM Configuration                    | 21 |

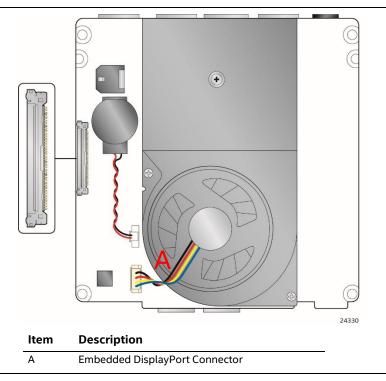

| Figure 5. eDP Connector on Bottom-side of the Board                   |    |

| Figure 6. LAN Connector LED Locations                                 | 30 |

| Figure 7. Thermal Solution and Fan Header                             | 31 |

| Figure 8. Location of the Standby Power LED                           | 35 |

| Figure 9. Front Panel Connectors                                      |    |

| Figure 10. Back Panel Connectors                                      |    |

| Figure 11. Connectors and Headers (Top)                               | 41 |

| Figure 12. Connectors and Headers (Bottom)                            | 42 |

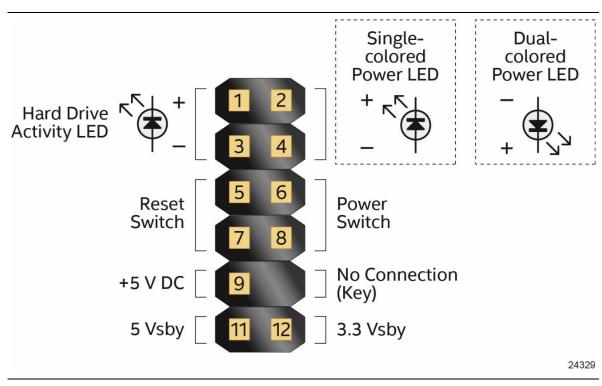

| Figure 13. Connection Diagram for Front Panel Header (2.0 mm Pitch)   | 50 |

| Figure 14. Connection Diagram for the Internal Power Supply Connector | 52 |

| Figure 15. Location of the BIOS Security Jumper                       | 53 |

| Figure 16. Intel MEBX Reset Header                                    | 56 |

| Figure 17. Board Dimensions                                           | 57 |

| Figure 18. Board Height Dimensions                                    |    |

| Figure 19. Localized High Temperature Zones                           |    |

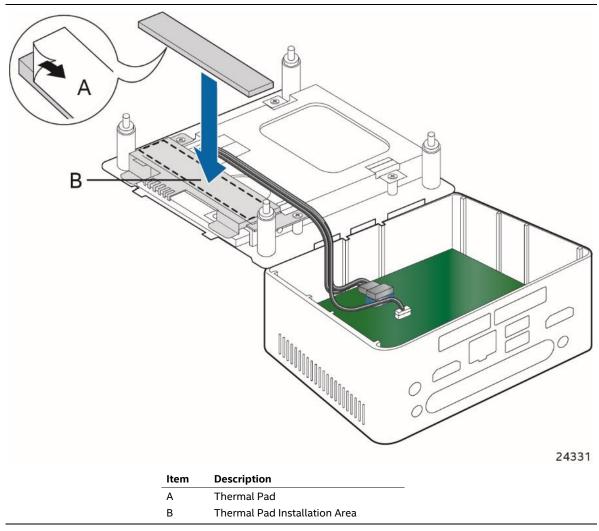

| Figure 20. Installation Area of the Thermal Pad                       | 63 |

### Tables

| Table 1. Feature Summary                                                              | 13 |

|---------------------------------------------------------------------------------------|----|

| Table 2. Components Shown in Figure 2                                                 | 17 |

| Table 3. Supported Memory Configurations                                              | 20 |

| Table 4. Unsupported Memory Configurations                                            | 20 |

| Table 5. LAN Connector LED States                                                     |    |

| Table 6. Effects of Pressing the Power Switch                                         |    |

| Table 7. Power States and Targeted System Power                                       |    |

| Table 8. Wake-up Devices and Events                                                   |    |

| Table 9. Connectors and Headers Shown in Figure 11                                    | 41 |

| Table 10. Connectors and Headers Shown in Figure 12                                   |    |

| Table 11. SATA Power Header (1.25 mm pitch)                                           | 44 |

| Table 12. Internal USB 2.0 Header (1.25 mm pitch)                                     |    |

| Table 13. Internal USB 3.0 Header (1.25 mm pitch)                                     |    |

| Table 14. Serial Port Header (1.25 mm pitch)                                          |    |

| Table 15. HDMI CEC Header (1.25 mm pitch)                                             | 46 |

| Table 16. M.2 2280 Module (Mechanical Key M) Connector                                | 46 |

| Table 17. M.2 2230 Module (Mechanical Key E) Connector                                | 47 |

| Table 18. 40-Pin eDP Connector                                                        | 49 |

| Table 19. Front Panel Header (2.0 mm Pitch)                                           |    |

| Table 20. States for a One-Color Power LED                                            | 51 |

| Table 21. States for a Dual-Color Power LED                                           |    |

| Table 22. 12-24 V Internal Power Supply Connector                                     | 52 |

| Table 23. BIOS Security Jumper Settings                                               | 54 |

| Table 24. Intel MEBX Reset Header Signals                                             | 56 |

| Table 25. Select Weights                                                              | 58 |

| Table 26. Power Budget for Assessing the DC-to-DC Circuit's Power Rating (worst case: |    |

| Embedded board in 3 <sup>rd</sup> party chassis)                                      |    |

| Table 27. Fan Header Current Capability                                               |    |

| Table 28. Thermal Considerations for Components                                       |    |

| Table 29. Tcontrol Values for Components                                              |    |

| Table 30. Environmental Specifications                                                |    |

| Table 31. Acceptable Drives/Media Types for BIOS Recovery                             |    |

| Table 32. Boot Device Menu Options                                                    |    |

| Table 33. Master Key and User Hard Drive Password Functions                           |    |

| Table 34. Supervisor and User Password Functions                                      |    |

| Table 35. Front-panel Power LED Blink Codes                                           |    |

| Table 36. BIOS Error Messages                                                         | 75 |

# 1.1 Overview

### 1.1.1 Feature Summary

Table 1 summarizes the major features of Intel® NUC Board NUC7i3DNBE.

| Table 1  | Feature | Summary |

|----------|---------|---------|

| Table I. | reature | Summary |

| Form Factor           | 4.0 inches by 4.0 inches (101.60 millimeters by 101.60 millimeters)                                                                      |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Processor             | Intel® NUC Board NUC7i3DNBE has a soldered-down 7 <sup>th</sup> generation Intel® Core™ i3-7100U dual-core processor with up to 15 W TDP |

|                       | — Intel® HD Graphics 620                                                                                                                 |

|                       | <ul> <li>Integrated memory controller</li> </ul>                                                                                         |

|                       | — Integrated PCH                                                                                                                         |

| Memory                | Two 260-pin 1.2 V DDR4 SDRAM Small Outline Dual Inline Memory Module (SO-DIMM) sockets                                                   |

|                       | <ul> <li>— Support for DDR4 1866/2133 MHz SO-DIMMs</li> </ul>                                                                            |

|                       | <ul> <li>Support for 4 Gb and 8 Gb memory technology</li> </ul>                                                                          |

|                       | <ul> <li>Support for up to 32 GB of system memory with two SO-DIMMs using 8 Gb memory<br/>technology</li> </ul>                          |

|                       | <ul> <li>— Support for non-ECC memory</li> </ul>                                                                                         |

|                       | <ul> <li>— Support for 1.2 V low voltage JEDEC memory only</li> </ul>                                                                    |

|                       | Note: 2 Gb memory technology (SDRAM Density) is not compatible                                                                           |

| Graphics              | Integrated graphics support for processors with Intel® Graphics Technology:                                                              |

|                       | <ul> <li>— Two High Definition Multimedia Interface* 2.0a (HDMI*) back panel connectors</li> </ul>                                       |

|                       | — Flat panel displays via the internal Embedded DisplayPort* 1.4 (eDP) connector                                                         |

| Audio                 | Intel® High Definition (Intel® HD) Audio via the HDMI v2.0a interface through the processor                                              |

| Storage               | SATA ports:                                                                                                                              |

|                       | — One SATA 6.0 Gb/s port (blue)                                                                                                          |

|                       | <ul> <li>— One SATA 6.0 Gb/s port is reserved for an M.2 2280 module</li> </ul>                                                          |

|                       | Note: Intel $^{\circ}$ NUC Board NUC7i3DNBE supports key type M (PCI Express* x1/x2/x4 and SATA)                                         |

| Peripheral Interfaces | USB 3.0 ports:                                                                                                                           |

|                       | <ul> <li>Two ports are implemented with external front panel connectors (blue)</li> </ul>                                                |

|                       | <ul> <li>Two ports are implemented with external back panel connectors (blue)</li> </ul>                                                 |

|                       | <ul> <li>One port is implemented with an internal 1x10 1.25mm pitch header (white)</li> </ul>                                            |

|                       | USB 2.0 ports:                                                                                                                           |

|                       | <ul> <li>Two ports via two single-port internal 1x4 1.25 mm pitch headers (white)</li> </ul>                                             |

|                       | <ul> <li>— One port is reserved for an M.2 2230 Module (key type E)</li> </ul>                                                           |

|                       | Serial Port 1x9 1.25mm pitch header(black)                                                                                               |

|                       | HDMI CEC 1x4 1.25 mm pitch header (black)                                                                                                |

continued

| One M.2 Module supporting M.2 2280 (key type M)                                                                   |  |  |

|-------------------------------------------------------------------------------------------------------------------|--|--|

| One M.2 Module supporting M.2 2230 (key type E)                                                                   |  |  |

| Intel <sup>®</sup> BIOS resident in the Serial Peripheral Interface (SPI) Flash device                            |  |  |

| Support for Advanced Configuration and Power Interface (ACPI), Plug and Play, and System Management BIOS (SMBIOS) |  |  |

| Gigabit (10/100/1000 Mb/s) LAN subsystem using the Intel® I219LM Gigabit Ethernet Controller                      |  |  |

| Hardware monitoring subsystem, based on ITE Tech. ITE8987E-VG embedded controller, including:                     |  |  |

| Voltage sense to detect out of range power supply voltages                                                        |  |  |

| Thermal sense to detect out of range thermal values                                                               |  |  |

| One processor fan header                                                                                          |  |  |

| Fan sense input used to monitor fan activity                                                                      |  |  |

| Fan speed control                                                                                                 |  |  |

| Intel® Dual Band Wireless-AC 8265                                                                                 |  |  |

| — 802.11ac, Dual Band, 2x2 Wi-Fi + Bluetooth v4.2                                                                 |  |  |

| <ul> <li>Maximum Transfer speed up to 867 Mbps</li> </ul>                                                         |  |  |

| Supports Intel <sup>®</sup> Smart Connect Technology                                                              |  |  |

| Pre-installed M.2 module                                                                                          |  |  |

| Intel® Platform Trust Technology                                                                                  |  |  |

|                                                                                                                   |  |  |

Table 1. Feature Summary (continued)

# 1.1.2 Board Layout (Top)

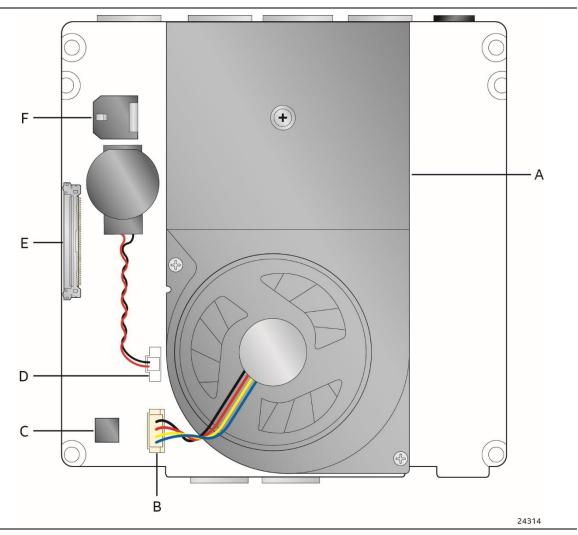

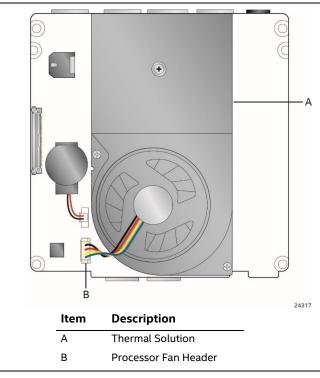

Figure 1 shows the location of the major components on the top-side of Intel NUC Board NUC7i3DNBE.

| Table 2. Components | Shown | in | Figure 1 |

|---------------------|-------|----|----------|

|---------------------|-------|----|----------|

| Item from Figure 1 | Description                 |

|--------------------|-----------------------------|

| A                  | Thermal Solution            |

| В                  | Processor Fan Header        |

| С                  | SPI                         |

| D                  | Battery Header              |

| E                  | eDP Connector               |

| F                  | DC Internal Power Connector |

### 1.1.3 Board Layout (Bottom)

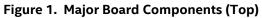

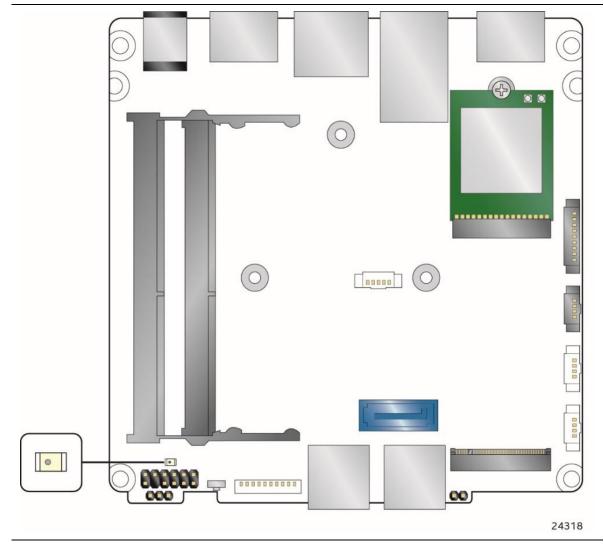

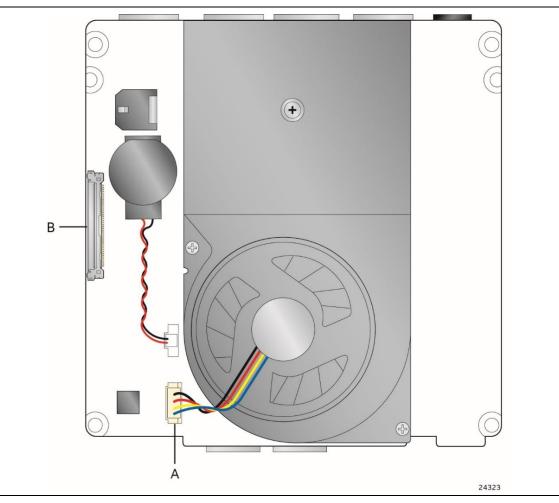

Figure 2 shows the location of the major components on the bottom-side of Intel NUC Board NUC7i3DNBE.

Figure 2. Major Board Components (Bottom)

| Item from Figure 2 | Description                                                        |

|--------------------|--------------------------------------------------------------------|

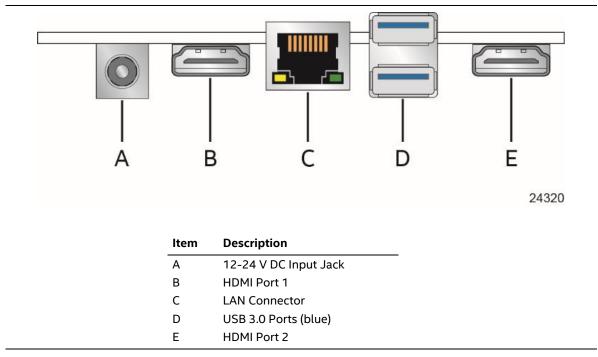

| A                  | 12-24 V DC Input Jack                                              |

| В                  | HDMI 2.0a Port 1 with HDCP 2.2 Support and Built-In CEC Support    |

| С                  | LAN Connector                                                      |

| D                  | Back Panel USB 3.0                                                 |

| E                  | HDMI 2.0a Port 2                                                   |

| F                  | Serial Port Header                                                 |

| G                  | M.2 2230 Module Connector (Key Type E) (Wireless card on Kit only) |

| Н                  | HDMI CEC                                                           |

| I                  | SATA Power Header                                                  |

| J                  | USB 2.0 Header                                                     |

| К                  | USB 2.0 Header                                                     |

| L                  | M.2 2280 Module Connector (Key Type M)                             |

| М                  | Intel® Management Engine BIOS Extension (Intel® MEBX) Reset Header |

| Ν                  | Front Panel USB 3.0                                                |

| 0                  | SATA 6.0 Gb/s Connector                                            |

| Р                  | Front Panel USB 3.0                                                |

| Q                  | USB 3.0 Header                                                     |

| R                  | Front Panel Power Button                                           |

| S                  | BIOS Security Header                                               |

| Т                  | Front Panel Header                                                 |

| U                  | Standby Power LED                                                  |

| V                  | DDR4 SO-DIMM 2 Socket                                              |

| W                  | DDR4 SO-DIMM 1 Socket                                              |

Table 2. Components Shown in Figure 2

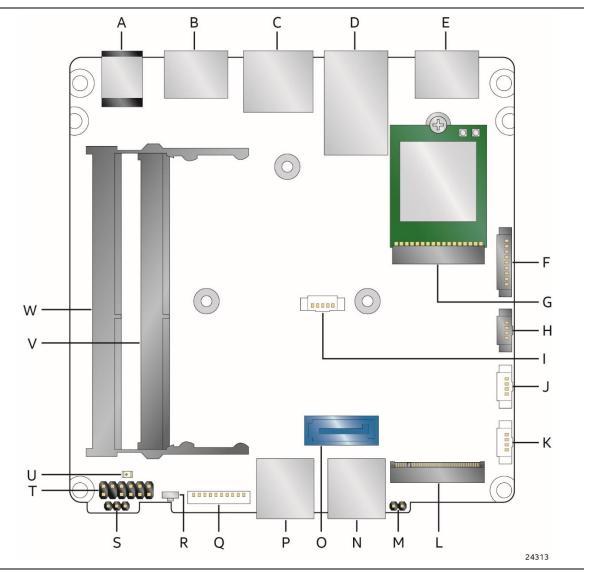

### 1.1.4 Block Diagram

Figure 3 is a block diagram of the major functional areas of the board.

Figure 3. Block Diagram

# 1.2 Online Support

#### To find information about...

Intel NUC Board/Kit NUC7i3DN Intel NUC Board/Kit Support High level details for Intel NUC Board/Kit NUC7i3DN

BIOS and driver updates Tested memory Integration information Processor datasheet

#### Visit this World Wide Web site:

http://www.intel.com/NUC http://www.intel.com/NUCSupport http://ark.intel.com

http://downloadcenter.intel.com http://www.intel.com/NUCSupport http://www.intel.com/NUCSupport http://ark.intel.com

# 1.3 Processor

Intel NUC Board NUC7i3DNBE has a soldered-down 7<sup>th</sup> generation Intel Core i3-7100U dual-core processor with up to 15 W TDP:

- Intel<sup>®</sup> HD Graphics 620

- Integrated memory controller

- Integrated PCH

# NOTE

There are specific requirements for providing power to the processor. Refer to Section 2.6.1 on page 59 for information on power supply requirements.

# 1.4 System Memory

The board has two 260-pin SO-DIMM sockets and supports the following memory features:

- 1.2 V DDR4 SDRAM SO-DIMMs with gold plated contacts

- Two independent memory channels with interleaved mode support

- Unbuffered, single-sided or double-sided SO-DIMMs

- 32 GB maximum total system memory (with 8 Gb memory technology). Refer to Section 2.1.1 on page 39 for information on the total amount of addressable memory.

- Minimum recommended total system memory: 2048 MB

- Non-ECC SO-DIMMs

- Serial Presence Detect

- DDR4 1866/2133 MHz SDRAM SO-DIMMs

- Supports 4 Gb and 8 Gb memory technology (SDRAM Density)

####

To be fully compliant with all applicable DDR SDRAM memory specifications, the board should be populated with SO-DIMMs that support the Serial Presence Detect (SPD) data structure. This allows the BIOS to read the SPD data and program the chipset to accurately configure memory settings for optimum performance. If non-SPD memory is installed, the BIOS will attempt to correctly configure the memory settings, but performance and reliability may be impacted or the SO-DIMMs may not function under the determined frequency.

# NOTE

NOTE:

Intel NUC Board NUC7i3DNBE supports only 4 Gb and 8 Gb memory technologies (also referred to as "SDRAM density"). Table 3 lists the supported SO-DIMM configurations. Table 4 lists the SO-DIMM configurations that are **not** supported.

| SO-DIMM  |                      | SDRAM   | SDRAM Organization   | Number of SDRAM |

|----------|----------------------|---------|----------------------|-----------------|

| Capacity | Configuration (Note) | Density | Front-side/Back-side | Devices         |

| 2048 MB  | SS                   | 4 Gbit  | 512 M x4/empty       | 4               |

| 4096 MB  | DS                   | 4 Gbit  | 512 M x4/512 M x4    | 8               |

| 4096 MB  | SS                   | 8 Gbit  | 1024 M x4/empty      | 4               |

| 8192 MB  | DS                   | 4 Gbit  | 512 M x8/512 M x8    | 16              |

| 8192 MB  | DS                   | 8 Gbit  | 1024 M x4/1024 M x4  | 8               |

| 16384 MB | DS                   | 8 Gbit  | 1024 M X8/1024 M x8  | 16              |

#### Table 3. Supported Memory Configurations

Note: "DS" refers to double-sided memory modules and "SS" refers to single-sided memory modules.

| SO-DIMM  |                      | SDRAM   | SDRAM Organization   | Number of SDRAM |

|----------|----------------------|---------|----------------------|-----------------|

| Capacity | Configuration (Note) | Density | Front-side/Back-side | Devices         |

| 1024 MB  | SS                   | 1 Gbit  | 128 M x8/empty       | 8               |

| 2048 MB  | DS                   | 1 Gbit  | 128 M x8/128 M x8    | 16              |

| 2048 MB  | SS                   | 2 Gbit  | 256 M x8/empty       | 8               |

| 4096 MB  | DS                   | 2 Gbit  | 256 M x8/256 M x8    | 16              |

#### Table 4. Unsupported Memory Configurations

Note: "DS" refers to double-sided memory modules and "SS" refers to single-sided memory modules.

#### For information about... Refer to:

|               |                                 | _ |

|---------------|---------------------------------|---|

| Tested Memory | http://www.intel.com/NUCSupport |   |

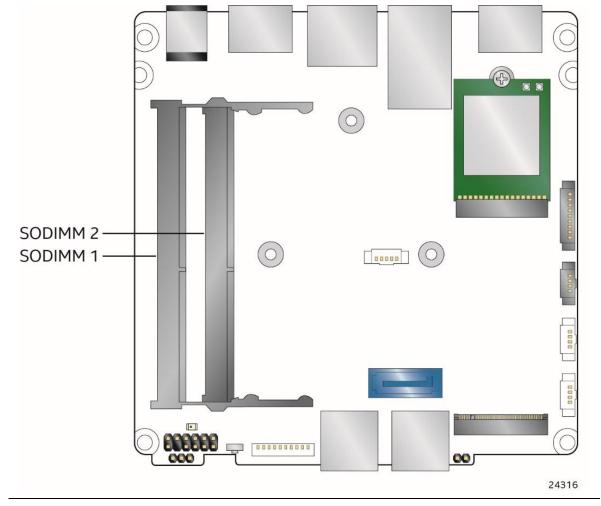

Figure 4 illustrates the memory channel and SO-DIMM configuration.

Figure 4. Memory Channel and SO-DIMM Configuration

# 1.5 Processor Graphics Subsystem

The board supports graphics through Intel® HD Graphics 620.

### 1.5.1 Integrated Graphics

The board supports integrated graphics via the processor.

#### 1.5.1.1 Intel<sup>®</sup> High Definition (Intel<sup>®</sup> HD) Graphics

The Intel® HD Graphics 620 controller features the following:

- 3D Features

- DirectX\* 12 support

- OpenGL\* 4.4 support

- Display

- Supports eDP flat panel displays up to 3840 x 2160 at 60 Hz

- Supports HDMI displays up to 4096 x 2160 at 60 Hz

- Next Generation Intel<sup>®</sup> Clear Video Technology HD support is a collection of video playback and enhancement features that improve the end user's viewing experience

- Encode/transcode HD content

- Playback of high definition content including Blu-ray\* disc

- Superior image quality with sharper, more colorful images

- DirectX\* Video Acceleration (DXVA) support for accelerating video processing

- Full AVC/VC1/MPEG2/HEVC/VP8/JPEG HW Decode

- Intel HD Graphics with Advanced Hardware Video Transcoding (Intel® Quick Sync Video)

- HDR 10 (High Dynamic Range 10 bit)

- HDCP (High-bandwidth Digital Content Protection) 2.2

#

Intel Quick Sync Video is enabled by an appropriate software application.

HDMI 2.0a enabled by a LSPCON (DisplayPort 1.2 to HDMI 2.0a controller). Stereo 3D (S3D) technology is not supported.

#### 1.5.1.2 High Definition Multimedia Interface\* (HDMI\*)

The HDMI ports are HDMI 2.0a specification compliant and support standard, enhanced, or high definition video, plus multi-channel digital audio on a single cable. The port is compatible with all ATSC and DVB HDTV standards and supports eight full range channels of lossless audio formats. The system can support up to two displays at the maximum supported resolution of 4096 x 2160 @ 60 Hz, 24bpp.

| For information about | Refer to            |

|-----------------------|---------------------|

| HDMI technology       | http://www.hdmi.org |

#### 1.5.1.2.1 Integrated Audio Provided by the HDMI Interfaces

The following audio technologies are supported by the HDMI 2.0a interface:

- AC3 Dolby\* Digital

- Dolby Digital Plus

- DTS-HD\*

- 192kHz/24-bit or 176.4 kHz/24-bit, 32 Channel

- Dolby True HD, DTS-HD Master Audio\* (Lossless Blu-ray Disc\* Audio Format)

#### 1.5.1.3 High-bandwidth Digital Content Protection (HDCP)

HDMI Port 1 supports HDCP 2.2. HDCP is the technology for protecting high definition content against unauthorized copy or interception between a source (computer, digital set top boxes, etc.) and the sink (panels, monitor, and TVs). The PCH supports HDCP 2.2 for content protection over wired displays.

#### 1.5.1.4 HDMI Consumer Electronics Control (CEC)

The system provides built-in HDMI CEC support on port 1 (refer to Figure 2), as well as a header for 3<sup>rd</sup> party HDMI CEC daughtercard support on HDMI port 2. The built-in HDMI CEC feature is OS agnostic and supports bi-directional power on/off control between the system and the attached display, as well as automatic HDMI input port detection from the display. This feature can be enabled and configured in BIOS Setup (Advanced  $\rightarrow$  Display tab). Additional HDMI CEC capabilities can be implemented on HDMI port 2 using a 3<sup>rd</sup> party daughtercard, which allows bidirectional power on/off control and other capabilities as supported by the daughtercard, such as the use of the media buttons on the display's remote controller.

| For information about   | Refer to                                             |

|-------------------------|------------------------------------------------------|

| HDMI CEC feature on NUC | https://www.intel.com/content/www/us/en/support/arti |

|                         | <u>cles/000023500/mini-pcs/intel-nuc-kits.html</u>   |

#### 1.5.1.5 Flat Panel Display Interfaces

The board supports flat panel displays via the Embedded DisplayPort interface. Figure 5 shows the flat panel connector on the bottom-side of the board.

#### 1.5.1.5.1 Embedded DisplayPort (eDP) Interface

The Embedded DisplayPort 1.4 (eDP) flat panel display interface supports the following:

- Maximum resolution of 3840 x 2160 at 60 Hz

- 4-lane bandwidth at 5.4 GT/s

- Multiple EDID data source capability (panel, predefined, and custom payloads)

- 3.3V flat panel display voltage

- 0.6A of maximum backlight current capability

- Backlight power voltage same as NUC board DC power source

- Board connector used is I-PEX-20455-040E-12, or compatible.

- Mating plug is I-PEX 20453-040T, or compatible.

#### 1.5.1.5.2 Configuration Modes

Video mode configuration for eDP displays is supported as follows:

- Panel: automatic panel identification via Extended Display Identification Data (EDID) for panels with onboard EDID support

- Predefined: panel selection from common predefined panel types

- Custom payloads: custom EDID payload installation for ultimate parameter flexibility, allowing custom definition of EDID data on panels without onboard EDID

In addition, BIOS setup provides the following configuration parameters for internal flat panel displays when a display is connected prior to booting:

- Color Depth: allows the system integrator to select whether the panel is 24 bpp with VESA or JEIDA color mapping, or 18 bpp.

- eDP Interface Type: allows the system integrator to select whether the eDP panel is a singlelane, dual-lane, or quad-lane display.

- eDP Data Rate: allows the system integrator to select whether the eDP panel runs at 1.62 Gb/s, 2.7 Gb/s, or 5.4 Gb/s.

- Inverter Frequency and Polarity: allows the system integrator to set the operating frequency and polarity of the panel inverter board.

- Maximum and Minimum Inverter Current Limit (%): allows the system integrator to set maximum PWM%, as appropriate, according to the power requirements of the internal flat panel display and the selected inverter board.

#

Support for flat panel display configuration complies with the following:

- 1. Internal flat panel display settings will be preserved across BIOS updates.

- 2. Backlight inverter voltage option "Vin" refers to board input voltage as provided to board power input connector.

#### 1.5.1.6 EDID Emulation Modes

The board supports emulation of displays so that the system may be remotely accessed in a headless configuration, or be capable of tolerating display connectivity interruptions without the operating system redetecting and rearranging the overall display layout. The display emulation feature may be enabled in BIOS Setup (Advanced  $\rightarrow$  Video  $\rightarrow$  "Display Emulation" drop down menu), with the following options:

- "No display emulation" (default selection): the system operates normally.

- "Headless display emulation": provides a virtual display when no displays are connected to the HDMI ports. The system creates a virtual 1280x1024 display when it boots with no displays connected.

- "Persistent display emulation": The purpose of Persistent Display Mode is to "emulate" that both displays are always connected. Persistent Display Mode prevents the GFX engine from automatically reassigning the content of a temporarily disconnected display to the remaining display. When Persistent Display Mode is selected the EC asserts that both HDMI ports are always connected to a display no matter their actual connection status. The EDID information from each display will remain programmed through S3, S4, and S5 power states, until the feature is disabled or a power cycle event (G3 global state) occurs.

Mill Toron (Million) Million (Million) A. Darly that for Int. A. Darly that for Int. In

#### NOTE

"Persistent display emulation" is not compatible with HDCP 2.2 displays.

When using "Persistent display emulation" it would be expected behavior for the system not to properly drive displays different than those connected when the feature was enabled, as the EDID parameters of the initially connected displays are still being driven by the system. In

order to retrain "Persistent display emulation" with a different display configuration a power cycle (AC power loss) is required.

# 1.6 USB

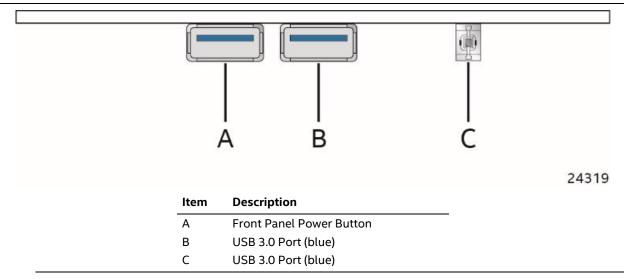

The board supports eight USB ports. All eight ports are high-speed, full-speed, and low-speed capable. The port arrangement is as follows:

- USB 3.0 ports:

- Two ports are implemented with external front panel connectors (blue)

- Two ports are implemented with external back panel connectors (blue)

- One port is implemented with a 1x10 1.25mm internal header (white)

- USB 2.0 ports:

- Two ports via two single-port internal 1x4 1.25 mm pitch headers (white)

- One port is reserved for the M.2 2230 Module Connector (Key Type E) (Wireless card on Kit only)

# NOTE

Computer systems that have an unshielded cable attached to a USB port may not meet FCC Class B requirements, even if no device is attached to the cable. Use a shielded cable that meets the requirements for full-speed devices.

| For information about                                | Refer to           |

|------------------------------------------------------|--------------------|

| The location of the USB connectors on the back panel | Figure 10, page 40 |

| The location of the front panel USB headers          | Figure 9, page 40  |

| The location of the internal connectors              | Figure 12, page 42 |

# 1.7 SATA Interface

The board provides the following SATA interfaces:

- One internal M.2 SATA port supporting M.2 2280 (key type M) modules

- One SATA 6.0 Gb/s port (blue)

The PCH provides independent SATA ports with a theoretical maximum transfer rate of 6 Gb/s. A point-to-point interface is used for host to device connections.

### 1.7.1 AHCI Mode

The board supports AHCI storage mode.

#

In order to use AHCI mode, AHCI must be enabled in the BIOS. Microsoft\* Windows\* 10 includes the necessary AHCI drivers without the need to install separate AHCI drivers during the operating

system installation process; however, it is always good practice to update the AHCI drivers to the latest available by Intel.

#### 1.7.2 NVMe

The board supports M.2 NVM Express\* (NVMe) drives. NVMe is an optimized, high-performance scalable host controller interface designed to utilize PCIe-based solid-state storage. NVMe is designed to provide efficient access to storage devices built with non-volatile memory, from current NAND flash technology to future, higher performing persistent memory technologies like Optane. NVMe is designed to meet serial bandwidth requirements and very high IOPs. It is based on PCIe Gen 3 and can deliver up to 4GB/s bandwidth. Current NVMe is based on version 1.3 of the specification.

### 1.7.3 Intel<sup>®</sup> Rapid Storage Technology / SATA RAID

The PCH supports Intel® Rapid Storage Technology, providing both AHCI and integrated RAID functionality. The RAID capability provides high-performance RAID 0 and 1 functionality on all SATA ports. Other RAID features include hot spare support, SMART alerting, and RAID 0 auto replace. Software components include an Option ROM for pre-boot configuration and boot functionality, a Microsoft Windows compatible driver, and a user interface for configuration and management of the RAID capability of the PCH.

#

Intel Rapid Storage Technology / SATA RAID is only supported if an M.2 SATA SSD module is used with the onboard SATA interface. RAID is not available with an M.2 NVMe SSD module and onboard SATA interface. Supported on chassis with 2.5 inch SATA HDD capability.

### 1.7.4 Intel<sup>®</sup> Next Generation Storage Acceleration

Intel® Next Generation Storage Acceleration with Intel® Optane<sup>™</sup> Technology is a disk caching solution that can provide improved computer system performance with improved power savings. It allows configuration of a computer system with the advantage of having HDDs for maximum storage capacity and with Intel® Optane<sup>™</sup> Technology for improved system performance. Supported on chassis with 2.5 inch SATA HDD capability.

For more information on Intel® Optane™ Technology, go to <u>http://www.intel.com/content/www/us/en/architecture-and-technology/non-volatile-memory.html</u>

# **Real-Time Clock Subsystem**

A coin-cell battery (CR2032) powers the real-time clock and CMOS memory. When the computer is not plugged into a wall socket, the battery has an estimated life of three years. When the computer is plugged in, the standby current from the power supply extends the life of the battery. The clock is accurate to  $\pm$  13 minutes/year at 25 °C with 3.3 VSB applied via the power supply 5 V STBY rail.

#

If the battery and AC power fail, date and time values will be reset and the user will be notified during the POST.

When the voltage drops below a certain level, the BIOS Setup program settings stored in CMOS RAM (for example, the date and time) might not be accurate. Replace the battery with an equivalent one. Figure 1 on page 15 shows the location of the battery.

#

Risk of explosion if the battery is replaced with an incorrect type. Batteries should be recycled where possible. Disposal of used batteries must be in accordance with local environmental regulations.

# 1.8 Audio Subsystem Software

Audio is supported through the HDMI 2.0a ports interface through the processor and supports eight full range channels of lossless audio formats per port. When using an encoded format (such as DTS-HD MA or Dolby True HD) the board supports a single 7.1 stream. When using an unencoded format the board supports 8 discrete, un-encoded channels per HDMI port simultaneously, for a total of 16 discrete/un-encoded channels.

### 1.8.1 NUC7i3DNHNC Audio Priority

The default audio priority for Dawson Canyon is the front panel 3.5mm headset jack  $\rightarrow$  USB connected headset/speakers  $\rightarrow$  HDMI connected audio. The default audio priority can be changed inside the OS. In Windows it can be changed under the default playback menu.

### 1.8.2 Audio Subsystem Software

Audio drivers are built into the Graphics driver and are available from Intel's website.

| For information about              | Refer to                        |

|------------------------------------|---------------------------------|

| Obtaining NUC software and drivers | http://downloadcenter.intel.com |

# 1.9 LAN Subsystem

The LAN subsystem consists of the following:

- Intel I219LM Gigabit Ethernet Controller (10/100/1000 Mb/s)

- RJ-45 LAN connector with integrated status LEDs

Additional features of the LAN subsystem include:

- CSMA/CD protocol engine

- LAN connect interface between the Processor and the LAN controller

- Power management capabilities

- ACPI technology support

- LAN wake capabilities

- LAN subsystem software

| For information about    | Refer to                        |

|--------------------------|---------------------------------|

| LAN software and drivers | http://downloadcenter.intel.com |

### 1.9.1 Intel<sup>®</sup> I219LM Gigabit Ethernet Controller

The Intel I219LM Gigabit Ethernet Controller supports the following features:

- Compliant with the 1 Gb/s Ethernet 802.3, 802.3u, 802.3z, 802.3ab specifications

- Multi-speed operation: 10/100/1000 Mb/s

- Full-duplex operation at 10/100/1000 Mb/s; Half-duplex operation at 10/100 Mb/s

- Flow control support compliant with the 802.3X specification as well as the specific operation of asymmetrical flow control defined by 802.3z

- VLAN support compliant with the 802.3q specification

- Supports Jumbo Frames (up to 9 kB)

- IEEE 1588 supports (Precision Time protocol)

- MAC address filters: perfect match unicast filters, multicast hash filtering, broadcast filter, and promiscuous mode

### 1.9.2 RJ-45 LAN Connector with Integrated LEDs

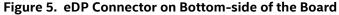

Two LEDs are built into the RJ-45 LAN connector (shown in Figure 6).

#### Figure 6. LAN Connector LED Locations

Table 5 describes the LED states when the board is powered up and the LAN subsystem is operating.

Table 5. LAN Connector LED States

| LED                    | LED Color | LED State                        | Condition                      |

|------------------------|-----------|----------------------------------|--------------------------------|

|                        | Off       | LAN link is not established.     |                                |

| Link                   | Green     | On                               | LAN link is established.       |

|                        | Blinking  | LAN activity is occurring.       |                                |

|                        |           | Off                              | 10 Mb/s data rate is selected. |

| Data Rate Green/Yellow | Green     | 100 Mb/s data rate is selected.  |                                |

|                        | Yellow    | 1000 Mb/s data rate is selected. |                                |

#### 1.9.3 Wireless Network Module

The Intel Dual Band Wireless-AC 8265 module provides hi-speed wireless connectivity provided with the following capabilities. The wireless module is included with Kit SKUs only:

- Compliant IEEE 802.11a/b/g/n/ac, 802.11d, 802.11e, 802.11i, 802.11w, 802.11r, 802.11k, 802.11v (pending OS support) specifications

- Maximum bandwidth of 867 Mbps

- Dual Mode Bluetooth\* 4.2

- Wi-Fi Direct\* for peer to peer device connections

- Wi-Fi Miracast\* as Source

- Authentication: WPA and WPA2, 802.1X (EAP-TLS, TTLS, PEAP, LEAP, EAP-FAST), EAP-SIM, EAP-AKA

- Encryption: 64-bit and 128-bit WEP, 128-bit AES-CCMP

| For information about               | Refer to                        |

|-------------------------------------|---------------------------------|

| Obtaining WLAN software and drivers | http://downloadcenter.intel.com |

| Full Specifications                 | http://intel.com/wireless       |

# 1.10 Hardware Management Subsystem

The board has several hardware management features, including thermal and voltage monitoring.

#### 1.10.1 Hardware Monitoring

The hardware monitoring and fan control subsystem is based on an ITE Tech. ITE8987E-VG embedded controller, which supports the following:

- Processor and system ambient temperature monitoring

- Fan speed monitoring

- Voltage monitoring of CPU IO Vcc (+Vccio), Memory Vcc (V\_SM), CPU IN Vcc (+Vccp)

- SMBus communication with internal components

### 1.10.2 Fan Monitoring

Fan monitoring can be implemented using third-party software.

### 1.10.3 Thermal Solution