# Intel® FM2112 24-Port 10G/1G Ethernet Switch Chip

**Data Sheet**

April, 2008 (Revision 2.2)

# Legal

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

The Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2011. Intel Corporation. All Rights Reserved.

# **Table of Contents**

| Document Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Over | view    |          |                                         | . 4        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------|-----------------------------------------|------------|

| Other Related Documents and Tools         5           1.0 Introduction         6           1.1 Product Overview         6           1.1.1 Applications         6           1.1.2 Features         6           1.1.3 Ethernet Interface Flexibility         7           1.1.4 Control and Test Interfaces         8           1.2 Application Examples         8           1.2.1 Advanced TCA Chassis Base Fabric Switch         9           1.2.2 Stackable Switch         9           1.2.3 2.5 Gigabit Backplane Upgrade         10           1.2.4 Applications Summary         11           1.3 Supported Standards and Specifications         11           1.4 Definitions         12           2.0 Architectural Overview         13           2.1 Principles of Operation         13           2.1 Principles of Operation         13           3.0 Functional Description         16           3.1.1 Port and Lane Configuration         16           3.1.2 SerDes         17           3.1.3 SerDes - Testing with BIST         21           3.1.4 PCS         22           3.1.5 IFG Stretch (IFGS)         24           3.1.4 PCS         22           3.1.5 IFG Stretch (IFGS)         24                 | Docu | ment l  | Revisio  | n History                               | . 4        |

| 1.0       Introduct Overview       6         1.1       Product Overview       6         1.1.1       Applications       6         1.1.2       Features       6         1.1.3       Ethernet Interface Flexibility       7         1.1.4       Control and Test Interfaces       8         1.2       Application Examples       8         1.2.1       Advanced TCA Chassis Base Fabric Switch       9         1.2.2       Stackable Switch       9         1.2.3       2.5 Gigabit Backplane Upgrade       10         1.2.4       Applications Summary       11         1.3       Supported Standards and Specifications       11         1.4       Definitions       12         2.0       Architectural Overview       13         2.1       Principles of Operation       13         2.2       Architectural Partitioning       13         3.0       Functional Description       16         3.1       Ethernet Port Logic (EPL)       16         3.1.1       Port and Lane Configuration       16         3.1.2       SerDes       17         3.1.3       SerDes - Testing with BIST       21         3.1.4       PCS                                                                                                 | Prod | uct Ap  | plicabil | ity                                     | . 4        |

| 1.1       Product Overview       6         1.1.1       Applications       6         1.1.2       Features       6         1.1.3       Ethernet Interface Flexibility       7         1.1.4       Control and Test Interfaces       8         1.2       Application Examples       8         1.2.1       Advanced TCA Chassis Base Fabric Switch       9         1.2.2       Stackable Switch       9         1.2.3       2.5 Gigabit Backplane Upgrade       10         1.2.4       Applications Summary       11         1.3       Supported Standards and Specifications       11         1.4       Definitions       12         2.0       Architectural Overview       13         2.1       Principles of Operation       13         2.2       Architectural Partitioning       13         3.1       Ethernet Port Logic (EPL)       16         3.1       Principles of Operation       16         3.1       Port and Lane Configuration       16         3.1       Port and Lane Configuration       16         3.1.1       Port and Lane Configuration       16         3.1.2       SerDes       17         3.1.3 <t< td=""><td>Othe</td><td>r Relat</td><td>ed Doc</td><td>uments and Tools</td><td>.5</td></t<> | Othe | r Relat | ed Doc   | uments and Tools                        | .5         |

| 1.1.1       Applications       6         1.1.2       Features       6         1.1.3       Ethernet Interface Flexibility       7         1.1.4       Control and Test Interfaces       8         1.2       Application Examples       8         1.2.1       Advanced TCA Chassis Base Fabric Switch       9         1.2.2       Stackable Switch       9         1.2.3       Supported Standards and Specifications       11         1.4       Definitions       12         2.0       Architectural Overview       13         2.1       Principles of Operation       13         2.2       Architectural Overview       13         2.1       Principles of Operation       13         3.2       Principles of Operation       13         3.1       Ethernet Port Logic (EPL)       13<                                                                                                     | 1.0  |         | duction  |                                         | . 6        |

| 1.1.2       Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | 1.1     |          |                                         |            |

| 1.1.3       Ethernet Interface Flexibility       .7         1.1.4       Control and Test Interfaces       .8         1.2       Application Examples       .8         1.2.1       Advanced TCA Chassis Base Fabric Switch       .9         1.2.2       Stackable Switch       .9         1.2.3       2.5 Gigabit Backplane Upgrade       .10         1.2.4       Applications Summary       .11         1.3       Supported Standards and Specifications       .11         1.4       Definitions       .11         2.0       Architectural Overview       .13         2.1       Principles of Operation       .13         2.2       Architectural Portion       .13         2.2       Architectural Portion       .13         3.0       Functional Description       .16         3.1       Ethernet Port Logic (EPL)       .16         3.1.1       Port and Lane Configuration       .16         3.1.2       SerDes       .17         3.1.3       SerDes - Testing with BIST       .21         3.1.4       PCS       .22         3.1.5       IFG Stretch (IFGS)       .24         3.1.6       MAC       .26         3.2       <                                                                                        |      |         |          |                                         |            |

| 1.1.4 Control and Test Interfaces.       8         1.2 Application Examples       8         1.2.1 Advanced TCA Chassis Base Fabric Switch       9         1.2.2 Stackable Switch       9         1.2.3 2.5 Gigabit Backplane Upgrade       10         1.2.4 Applications Summary       11         1.3 Supported Standards and Specifications       11         1.4 Definitions       12         2.0 Architectural Overview       13         2.1 Principles of Operation       13         2.2 Architectural Partitioning       13         3.0 Functional Description       16         3.1 Ethernet Port Logic (EPL)       16         3.1.1 Port and Lane Configuration       16         3.1.2 SerDes       17         3.1.3 SerDes - Testing with BIST       21         3.1.4 PCS       22         3.1.5 IFG Stretch (IFGS)       24         3.1.6 MAC       26         3.2 Frame Control       29         3.2.1 MAC Address Security       29         3.2.2 IEEE 802.1x - Port Access Control       30         3.2.3 VLAN       30         3.2.4 Network Topology and Spanning Tree Protocol (STP)       32         3.2.5 Multicast and Protocol Traps       33         3.2.6 MAC Add                                  |      |         |          |                                         |            |

| 1.2 Application Examples       8         1.2.1 Advanced TCA Chassis Base Fabric Switch       9         1.2.2 Stackable Switch       9         1.2.3 2.5 Gigabit Backplane Upgrade       10         1.2.4 Applications Summary       11         1.3 Supported Standards and Specifications       11         1.4 Definitions       12         2.0 Architectural Overview       13         2.1 Principles of Operation       13         2.2 Architectural Partitioning       13         3.0 Functional Description       16         3.1 Ethernet Port Logic (EPL)       16         3.1.1 Port and Lane Configuration       16         3.1.2 SerDes       17         3.1.3 SerDes - Testing with BIST       21         3.1.4 PCS       21         3.1.5 IFG Stretch (IFGS)       24         3.1.6 MAC       26         3.2 Frame Control       26         3.2.1 MAC Address Security       29         3.2.2 IEEE 802.1x - Port Access Control       30         3.2.3 VLAN       30         3.2.4 Network Topology and Spanning Tree Protocol (STP)       32         3.2.5 Multicast and Protocol Traps       33         3.2.6 MAC Address Table and VLAN Table       34         3.2.1 Li                                  |      |         | _        |                                         |            |

| 1.2.1       Advanced TCA Chassis Base Fabric Switch       9         1.2.2       Stackable Switch       9         1.2.3       2.5 Gigabit Backplane Upgrade       10         1.2.4       Applications Summary       11         1.3       Supported Standards and Specifications       11         1.4       Definitions       12         2.0       Architectural Overview       13         2.1       Principles of Operation       13         2.2       Architectural Partitioning       13         3.0       Functional Description       16         3.1       Ethernet Port Logic (EPL)       16         3.1.1       Port and Lane Configuration       16         3.1.2       SerDes       17         3.1.3       SerDes - Testing with BIST       21         3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       22         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree                                                                                            |      | 1.0     |          |                                         |            |

| 1.2.2       Stackable Switch       9         1.2.3       2.5 Gigabit Backplane Upgrade       10         1.2.4       Applications Summary       11         1.3       Supported Standards and Specifications       11         1.4       Definitions       12         2.0       Architectural Overview       13         2.1       Principles of Operation       13         2.2       Architectural Partitioning       13         3.0       Functional Description       16         3.1       Ethernet Port Logic (EPL)       16         3.1.1       Port and Lane Configuration       16         3.1.2       SerDes       17         3.1.3       SerDes - Testing with BIST       21         3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol                                                                                             |      | 1.2     |          | Advanced TCA Charles Base Falsis Cuitel | 8          |

| 1.2.3       2.5 Gigabit Backplane Upgrade                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |         |          |                                         |            |

| 1.2.4 Applications Summary       11         1.3 Supported Standards and Specifications       11         1.4 Definitions       12         2.0 Architectural Overview       13         2.1 Principles of Operation       13         2.2 Architectural Partitioning       13         3.0 Functional Description       16         3.1 Ethernet Port Logic (EPL)       16         3.1.1 Port and Lane Configuration       16         3.1.2 SerDes       17         3.1.3 SerDes - Testing with BIST       21         3.1.4 PCS       22         3.1.5 IFG Stretch (IFGS)       24         3.1.6 MAC       26         3.2 Frame Control       29         3.2.1 MAC Address Security       29         3.2.2 IEEE 802.1x - Port Access Control       30         3.2.3 VLAN       30         3.2.4 Network Topology and Spanning Tree Protocol (STP)       32         3.2.5 Multicast and Protocol Traps       33         3.2.6 MAC Address Table and VLAN Table       34         3.2.9 Discard and Monitoring: User-defined Triggers       36         3.2.10 Link-Aggregation       36         3.2.12 Memory Integrity       41         3.3.1 Priority Mapping       42         3.3.2 Shared                                  |      |         |          |                                         |            |

| 1.3       Supported Standards and Specifications       11         1.4       Definitions       12         2.0       Architectural Overview       13         2.1       Principles of Operation       13         2.2       Architectural Partitioning       13         3.0       Functional Description       16         3.1       Ethernet Port Logic (EPL)       16         3.1.1       Port and Lane Configuration       16         3.1.2       SerDes       17         3.1.3       SerDes       17         3.1.3       SerDes       17         3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.9       Discard and Monitoring: User-defined Trig                                                                                            |      |         |          |                                         |            |

| 1.4     Definitions     12       2.0     Architectural Overview     13       2.1     Principles of Operation     13       3.2.2     Architectural Partitioning     13       3.0     Functional Description     16       3.1.1     Port and Lane Configuration     16       3.1.2     SerDes     17       3.1.3     SerDes - Testing with BIST     21       3.1.4     PCS     22       3.1.5     IFG Stretch (IFGS)     24       3.1.6     MAC     26       3.2     Frame Control     29       3.2.1     MAC Address Security     29       3.2.2     IEEE 802.1x - Port Access Control     30       3.2.3     VLAN     30       3.2.4     Network Topology and Spanning Tree Protocol (STP)     32       3.2.5     Multicast and Protocol Traps     33       3.2.6     MAC Address Table and VLAN Table     34       3.2.7     Lookups and Forwarding     35       3.2.8     Forwarding     36       3.2.9     Discard and Monitoring: User-defined Triggers     36       3.2.10     Link-Aggregation     38       3.2.11     Table Modification     40       3.2.12     Memory Integrity     41       3.3.1 </td <td></td> <td>1 2</td> <td></td> <td></td> <td></td>                                                 |      | 1 2     |          |                                         |            |

| 2.0       Architectural Overview       13         2.1       Principles of Operation       13         2.2       Architectural Partitioning       13         3.0       Functional Description       16         3.1       Ethernet Port Logic (EPL)       16         3.1.1       Port and Lane Configuration       16         3.1.2       SerDes       17         3.1.3       SerDes - Testing with BIST       21         3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10                                                                                             |      |         |          |                                         |            |

| 2.1       Principles of Operation       13         2.2       Architectural Partitioning       13         3.0       Functional Description       16         3.1       Ethernet Port Logic (EPL)       16         3.1.1       Port and Lane Configuration       16         3.1.2       SerDes       17         3.1.3       SerDes - Testing with BIST       21         3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       30         3.2.12       <                                                                                        |      |         |          |                                         |            |

| 2.2       Architectural Partitioning       13         3.0       Functional Description       16         3.1       Ethernet Port Logic (EPL)       16         3.1.1       Port and Lane Configuration       16         3.1.2       SerDes       17         3.1.3       SerDes - Testing with BIST       21         3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12 <td< td=""><td>2.0</td><td></td><td></td><td></td><td></td></td<>                                | 2.0  |         |          |                                         |            |

| 3.0       Functional Description       16         3.1       Ethernet Port Logic (EPL)       16         3.1.1       Port and Lane Configuration       16         3.1.2       SerDes       17         3.1.3       SerDes - Testing with BIST       21         3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestio                                                                                            |      |         |          |                                         |            |

| 3.1       Ethernet Port Logic (EPL)       16         3.1.1       Port and Lane Configuration       16         3.1.2       SerDes       17         3.1.3       SerDes - Testing with BIST       21         3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memo                                                                                            |      |         |          |                                         |            |

| 3.1.1       Port and Lane Configuration       16         3.1.2       SerDes       17         3.1.3       SerDes - Testing with BIST       21         3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Shared Memory Queues       43         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Qu                                                                                            | 3.0  | Funct   | ional D  | escription                              | 16         |

| 3.1.2       SerDes       17         3.1.3       SerDes - Testing with BIST       21         3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       35         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted                                                                                            |      | 3.1     |          |                                         |            |

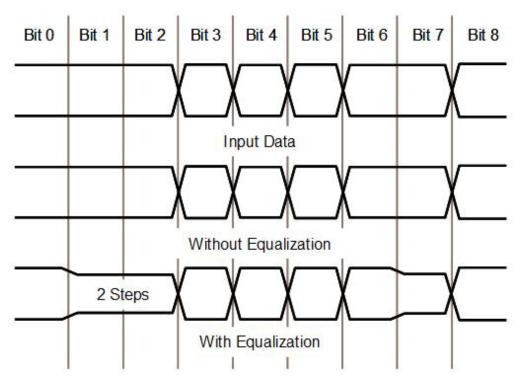

| 3.1.3       SerDes - Testing with BIST       21         3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       30         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.4       Pause Flow Control       46         3.3.5       Egress Sch                                                                                            |      |         | _        |                                         |            |

| 3.1.4       PCS       22         3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       35         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.5       Managem                                                                                            |      |         |          | SerDes Tocting with PICT                | 1/         |

| 3.1.5       IFG Stretch (IFGS)       24         3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       35         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management                                                                                                  |      |         | _        |                                         |            |

| 3.1.6       MAC       26         3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Man                                                                                            |      |         |          |                                         |            |

| 3.2       Frame Control       29         3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                             |      |         |          |                                         |            |

| 3.2.1       MAC Address Security       29         3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                                   |      | 2.2     |          |                                         |            |

| 3.2.2       IEEE 802.1x - Port Access Control       30         3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                        |      | 3.2     |          |                                         |            |

| 3.2.3       VLAN       30         3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                                                                                       |      |         | _        | TEEE 802 1v - Port Access Control       | 3U<br>23   |

| 3.2.4       Network Topology and Spanning Tree Protocol (STP)       32         3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                                                                                                                         |      |         | _        |                                         |            |

| 3.2.5       Multicast and Protocol Traps       33         3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                                                                                                                                                                                                        |      |         |          |                                         |            |

| 3.2.6       MAC Address Table and VLAN Table       34         3.2.7       Lookups and Forwarding       35         3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |         |          |                                         |            |

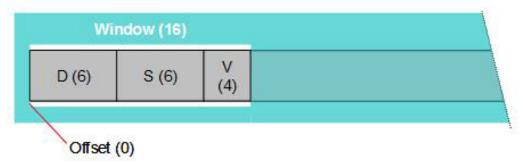

| 3.2.7       Lookups and Forwarding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |         |          |                                         |            |

| 3.2.8       Forwarding       36         3.2.9       Discard and Monitoring: User-defined Triggers       36         3.2.10       Link-Aggregation       38         3.2.11       Table Modification       40         3.2.12       Memory Integrity       41         3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |         |          |                                         |            |

| 3.2.9 Discard and Monitoring: User-defined Triggers       36         3.2.10 Link-Aggregation       38         3.2.11 Table Modification       40         3.2.12 Memory Integrity       41         3.3 Congestion Management       41         3.3.1 Priority Mapping       42         3.3.2 Shared Memory Queues       43         3.3.3 PWD (Priority Weighted Discard)       44         3.3.4 Pause Flow Control       46         3.3.5 Egress Scheduling       48         3.4 Statistics       49         3.5 Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |         |          |                                         |            |

| 3.2.10 Link-Aggregation       38         3.2.11 Table Modification       40         3.2.12 Memory Integrity       41         3.3 Congestion Management       41         3.3.1 Priority Mapping       42         3.3.2 Shared Memory Queues       43         3.3.3 PWD (Priority Weighted Discard)       44         3.3.4 Pause Flow Control       46         3.3.5 Egress Scheduling       48         3.4 Statistics       49         3.5 Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |         | _        |                                         |            |

| 3.2.11 Table Modification       40         3.2.12 Memory Integrity       41         3.3 Congestion Management       41         3.3.1 Priority Mapping       42         3.3.2 Shared Memory Queues       43         3.3.3 PWD (Priority Weighted Discard)       44         3.3.4 Pause Flow Control       46         3.3.5 Egress Scheduling       48         3.4 Statistics       49         3.5 Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |         |          |                                         |            |

| 3.2.12 Memory Integrity       41         3.3 Congestion Management       41         3.3.1 Priority Mapping       42         3.3.2 Shared Memory Queues       43         3.3.3 PWD (Priority Weighted Discard)       44         3.3.4 Pause Flow Control       46         3.3.5 Egress Scheduling       48         3.4 Statistics       49         3.5 Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |         | 3 2 11   | Table Modification                      | <u>ع</u> 0 |

| 3.3       Congestion Management       41         3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |         |          |                                         |            |

| 3.3.1       Priority Mapping       42         3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 3 3     |          |                                         |            |

| 3.3.2       Shared Memory Queues       43         3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 5.5     | -        |                                         |            |

| 3.3.3       PWD (Priority Weighted Discard)       44         3.3.4       Pause Flow Control       46         3.3.5       Egress Scheduling       48         3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |         |          |                                         |            |

| 3.3.4 Pause Flow Control       46         3.3.5 Egress Scheduling       48         3.4 Statistics       49         3.5 Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |         |          |                                         |            |

| 3.3.5       Egress Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |         |          |                                         |            |

| 3.4       Statistics       49         3.5       Management       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |         |          |                                         |            |

| 3.5 Management50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | 3.4     |          |                                         |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | _       |          |                                         |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |         | _        |                                         |            |

|     |       | 3.5.2     | Bootstrap Finite State Machine             |     |

|-----|-------|-----------|--------------------------------------------|-----|

|     |       | 3.5.3     | CPU Interface                              | 61  |

|     |       | 3.5.4     | SPI Interface (EEPROM)                     | 64  |

|     |       | 3.5.5     | LED Interface                              | 65  |

|     |       | 3.5.6     | JTAG                                       |     |

|     | 3.6   |           |                                            |     |

|     | 5.0   | 3.6.1     | SerDes Clocks, RCK[A:B][1:4]P/N            |     |

|     |       |           |                                            |     |

|     |       | 3.6.2     | CPU Interface Clock                        | 65  |

|     |       | 3.6.3     | JTAG Clock                                 |     |

|     |       | 3.6.4     | Frame Handler Clock                        | 70  |

| 4.0 | Elect | rical Spe | ecifications                               | 71  |

|     | 4.1   | Absolut   | e Maximum Ratings                          | 71  |

|     | 4.2   | Recomr    | mended Operating Conditions                | 71  |

|     | 4.3   |           | ing Specifications                         |     |

|     |       | 4.3.1     | CPU Interface, General Timing Requirements |     |

|     |       | 4.3.2     | JTAG Interface                             |     |

|     |       |           |                                            |     |

| 5.0 |       | ter Def   | initions                                   | 77  |

|     | 5.1   |           | r Conventions                              |     |

|     | 5.2   | Registe   | r Map                                      | 77  |

|     | 5.3   | Global F  | Registers                                  |     |

|     |       | 5.3.1     | Global Register Tables                     |     |

|     | 5.4   | Switch    | Configuration                              | 87  |

|     |       | 5.4.1     | Critical Events                            | 87  |

|     |       | 5.4.2     | System Configuration                       |     |

|     |       | 5.4.3     | Per port Configuration                     |     |

|     |       | 5.4.4     | Non-IEEE 802.3 Header Info                 |     |

|     |       | 5.4.5     | Logical CPU Interface Registers            |     |

|     |       |           |                                            |     |

|     | 5.5   |           | Registers                                  |     |

|     |       | 5.5.1     | Switch Control Tables                      |     |

|     |       | 5.5.2     | Port Trunk Registers (Link-Aggregation)    |     |

|     |       | 5.5.3     | Filtering and Monitoring                   |     |

|     | 5.6   | Conges    | tion Management                            |     |

|     |       | 5.6.1     | Priority Mapping                           | 107 |

|     |       | 5.6.2     | Queue Management - PWD                     | 109 |

|     |       | 5.6.3     | Switch Latency                             |     |

|     | 5.7   |           | CS                                         |     |

|     | 0.7   | 5.7.1     | Statistics Registers                       |     |

|     |       | 5.7.2     | Counter Groups                             | 115 |

|     | 5.8   |           | gisters                                    |     |

|     | 5.6   |           |                                            |     |

|     |       | 5.8.1     | SERDES Registers                           |     |

|     |       | 5.8.2     | PCS Registers                              | 126 |

|     |       |           | MAC Registers                              |     |

|     |       | 5.8.4     | Scan Registers                             | 136 |

| 6.0 | Signa | al. Ball. | and Package Descriptions                   | 138 |

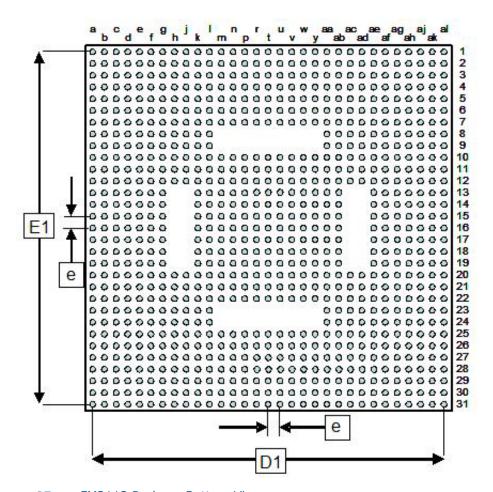

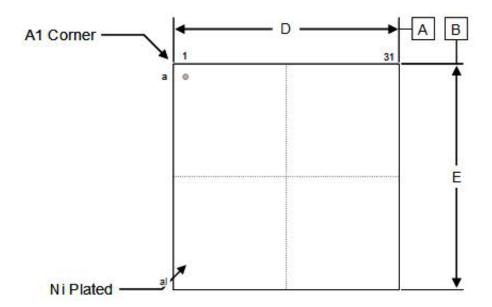

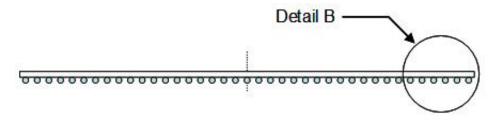

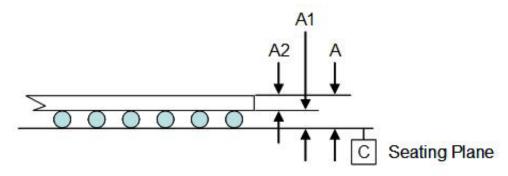

|     | 6.1   | Package   | e Overview                                 | 138 |

|     | 6.2   |           | Mapping                                    |     |

|     | 6.3   |           | ce Mapping                                 |     |

|     | 6.4   |           | Descriptions                               |     |

|     | 0.7   | 6.4.1     | FM2112 Signals                             |     |

|     |       | 6.4.2     |                                            |     |

|     |       | ~··-      | Recommended Connections                    |     |

|     |       | 6.4.3     | Ball Assignment                            |     |

|     | 6.5   |           | e Dimensions                               |     |

|     | 6.6   | Power [   | Dissipation and Heat Sinking               |     |

|     |       | 661       | Power Dissination                          | 161 |

|     | 6.     | .6.2 Heat Sinking                 | 162 |

|-----|--------|-----------------------------------|-----|

|     | 6.     | .6.3 Temperature Sensor Operation | 163 |

| 7.0 | Docume | ent Revision Information          | 165 |

|     | 7.1 No | omenclature                       | 165 |

|     | 7.2 Re | ev 1.0 to 1.1 Changes             | 165 |

|     | 7.3 Re | ev 2.0 to 2.1 Changes             | 166 |

|     | 7.4 Re | ev 2.1 to 2.2 Changes             | 166 |

# **Overview**

Intel<sup>®</sup> intends to offer multiple market- and customer-specific product variants based on the platform. This preliminary data sheet documents the features and functionality of the variant of the Intel<sup>®</sup>Ethernet Switch Family platform that features eight 10G (quad SerDes) interfaces and sixteen 1G (single SerDes) interfaces, which will be referred to in this document as the FM2112.

Note:

This document provides information about the FM2112. All specifications are based on pre-production release test data and are subject to change. Rev 2.0 of this datasheet, when released, will contain complete and final specifications and will be available concurrently with the product's production release.

# **Document Revision History**

| Revision | Date           | Notes                                    |

|----------|----------------|------------------------------------------|

| 1.0      | Oct 25, 2006   | Initial version of Preliminary Datasheet |

| 2.0      | July 30, 2007  | Updates per section 7.2                  |

| 2.1      | Oct 1, 2007    | Updates per section 7.3                  |

| 2.2      | April 17, 2008 | Updates per section 7.4                  |

# **Product Applicability**

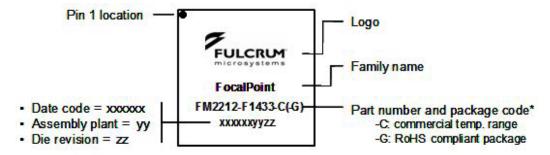

This preliminary data sheet documents the features and functionality of the FM2112, the second member of the FM2000 product family. The Intel<sup>®</sup> Ethernet Switch Family FM2112 part number is structured as follows:

\*Note: Pre-Production part numbering may differ slightly

#### Key:

- Product Family: "2" represents the Ethernet L2 switch product family, of which the Intel®Ethernet Switch Family is a member.

- Port Configuration: Provides guidance on the composition of the ports in the device, as follows:

- 1: More than 50% of the interfaces are single-SerDes interfaces

- 2: More than 50% of the interfaces are quad-SerDes interfaces

- Aggregate Bandwidth: "12" represents an aggregate bandwidth of 120Gbps

- Temperature: "C" represents Commercial temperature grade. The grades indicate case temperatures as follows:

| Grade      | Designator | Tcase(min) (°C) | Tcase(max) (°C) |

|------------|------------|-----------------|-----------------|

| Commercial | -C         | 0               | +85             |

| Extended   | -E         | 0               | +105            |

| Industrial | -I         | -40             | +115            |

• RoHS Compliance: The presence of a "-G" means that the device is compliant with the RoHS requirements for restrictions on the use of hazardous substances. Compliance is via exemption #15 in the RoHS Directive Annex, which allows for the use of Pb (lead) in the solder bumps used for die attaché in flip-chip packages. -G parts have lead-free solder balls on the exterior of the package for PC board die attach.

Note:

The non-RoHS compliant package meets the RoHS limits for the other five substances, but contains Pb in the external solder balls, which is not allowed by the RoHS directive, and in the solder bumps for die attach.

# Other Related Documents and Tools

Other documents that may be useful for evaluating and using the FM2112 include:

- FM2112 Software API Specification

- FM2112 Specification Update, which contains errata and other specification and documentation changes

- FM2112 Design and Layout Guide

- FM2112 Reference Design Data Sheet

- FM2112 Design Support Package on CD

# 1.0 Introduction

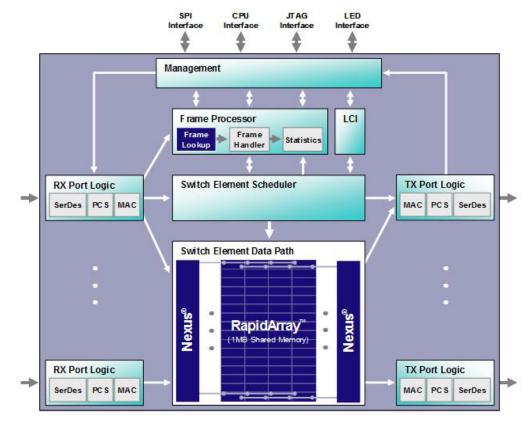

# 1.1 Product Overview

The FM2112 is a fully-integrated, single-chip 24-port 10G/2.5G/1G Ethernet layer-2 switch chip that offers wire-speed performance, extremely low-latency characteristics, and leading power efficiency. With its robust layer-2 switching capabilities and the ubiquity of Ethernet, the FM2112 fits comfortably in a number of existing and emerging applications. And, with the unprecedented level of integration, the FM2112 removes the cost, area, and power barrier for rapid and far-reaching high-performance Ethernet deployment.

# 1.1.1 Applications

With unprecedented integration, performance, power efficiency, and latency characteristics, the FM2112 can be used for a variety of infrastructure and interconnect applications, some of which include:

- Blade computer and IP storage platform internal fabric

- Data center cluster interconnect (clustered computers and storage resources)

- Enterprise stackable switch (performance workgroups and workgroup aggregation)

- AdvancedTCA backplane fabric (star or mesh architecture)

- AdvancedTCA carrier card switch (interconnecting mezzanine cards)

- AdvancedTCA base fabric

- Proprietary system backplane fabric

# 1.1.2 Features

# The following are the general features of the device:

#### Interface Features

- 8 Quad-SerDes Ethernet interfaces (802.3ae), configurable as follows:

- XAUI (10GBase-CX4 compliant)

- XAUI overspeed up to 12.5Gbps

- 2.5G Ethernet

- 1G Ethernet (SGMII, 1000BASE-X)

- 10/100M Ethernet

- 16 Single-SerDes Ethernet interfaces, configurable as follows:

- 2.5G Ethernet

- 1G Ethernet (SGMII, 1000B-CX)

- 10/100M Ethernet

- Link Aggregation (802.3ad)

## **Chip Performance**

- 120 Gbps bandwidth

- 180M FPS

- >180M segments per second (segments of 64 bytes)

- Low-latency cut-through switching: 200 ns @ 10G, 650 ns @ 1G.

- · Store and Forward mode

#### **Switch Element Features**

- Centrally-buffered, fully provisioned, nonblocking, shared memory switch with ideal transfer characteristics

- 2x internal fabric overspeed

- ¾ TB of shared memory bandwidth

- 600 MHz memory event rate

- Full speed multicast

- Multi-point Link-Ag extensions

- PAUSE flow control (802.3x)

- Inter-frame gap stretch (Rate Control)

- Intel<sup>®</sup> extensions to support complex topologies and large-scale applications

#### Security

- · MAC address security

- Port access control (802.1x)

#### **Bridge Features**

- 16K entry MAC address table

- Spanning Tree (802.1D, s, w)

- VLAN, priority (802.1Q, P)

- 4K VLAN table

- Link Aggregation (802.3ad)

- Duplex Flow Control (802.3x)

- All IEEE protocol traps

- · User-defined monitoring and filtering rules

- RMON, and Intel<sup>®</sup> statisticsChip Performance

#### **Test Features**

- · JTAG and boundary scan support

- · Per-interface field loopback and BIST

#### **Congestion Management**

- · Egress scheduling of 4 traffic classes

- · Shared and private watermarks

- · PWD (Priority Weighted Discard) on 16 priorities

- Priority regeneration

#### **Control Features**

- 32-bit standard CPU interface

- SPI EEPROM interface

- · Standard LED interface

#### Physical

- 1.0W/0.5W (typ) per active 10G/2.5G interface

- Power scales linearly on activity

- 130 nm CMOS process technology

- 897-ball BGA package

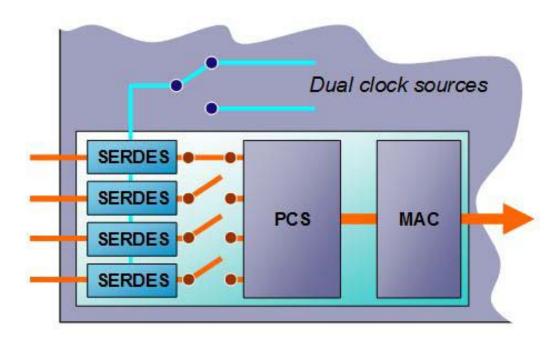

# 1.1.3 Ethernet Interface Flexibility

The FM2112 contains 24 interfaces, 8 of which are quad SerDes interfaces and can be independently configured to support one of the following modes:

- 10G Ethernet: XAUI interface, with 10GBase-CX4 compliance (accomplished with four SerDes pairs operating at 3.125 GHz, with 8b/10b encoding)

- 2.5G Ethernet: Pre-standard implementation (accomplished with a single SerDes pair operating at 3.125 GHz, with 8b/10b encoding)

- 1G Ethernet: SGMII and 1000BASE-X compliance (accomplished with a single SerDes pair operating at 1.25 GHz, with 8b/10b encoding)

- User-configurable mode: The FM2112 can support two input reference clocks, each operating up to 400 MHz. Each of the device's 8 quad SerDes interfaces can independently select one of the two reference clocks. Additionally, each interface can be configured to have one or four SerDes pair(s) active. So, as an example, given two input clocks of 312.5 MHz and 400 MHz, each interface can be independently configured to support data rates of , 2.5 Gbps, 3.2 Gbps, 10 Gbps, and 12.8 Gbps.

And 16 of which are single SerDes interfaces and can be independently configured to support one of the following modes:

- 2.5G Ethernet: Pre-standard implementation (accomplished with a single SerDes pair operating at 3.125 GHz, with 8b/10b encoding)

- 1G Ethernet: SGMII and 1000Base-CX compliance (accomplished with a single SerDes pair operating at 1.25 GHz, with 8b/10b encoding)

- User-configurable mode: The FM2112 can support two input interface clocks, each

operating up to 4 GHz. Each of the device's 16 interfaces can independently select

one of the two reference clocks. Additionally, each interface can be configured to

have one or four SerDes pair(s) active. So, as an example, given two input clocks

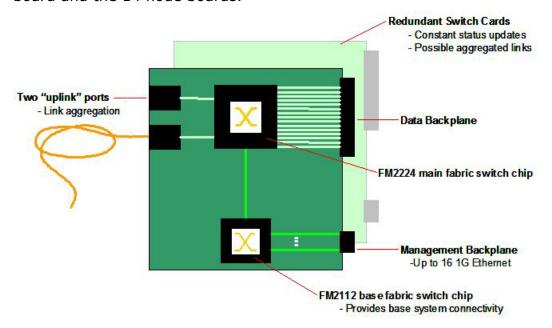

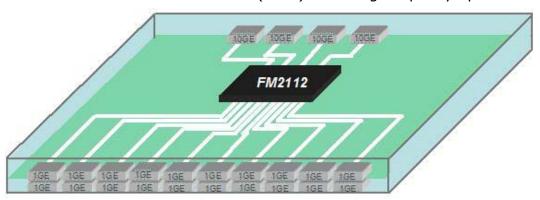

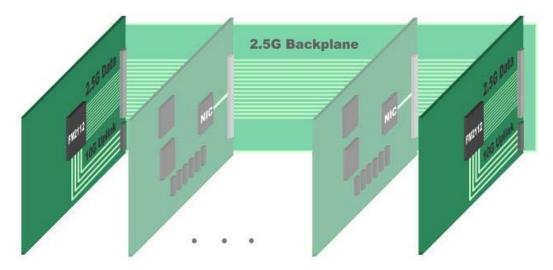

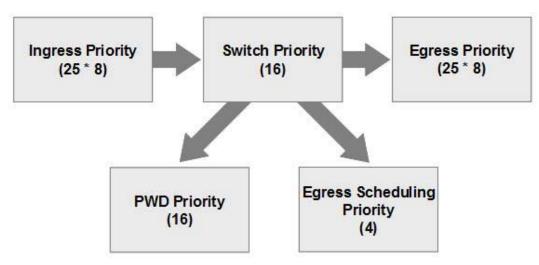

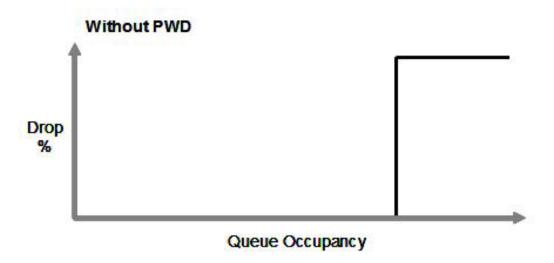

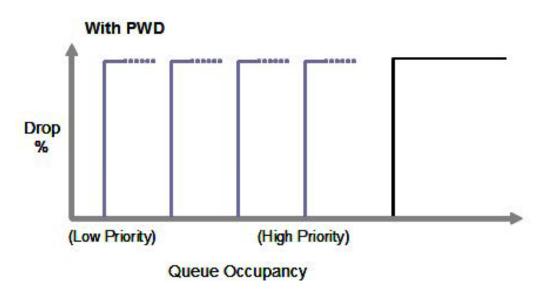

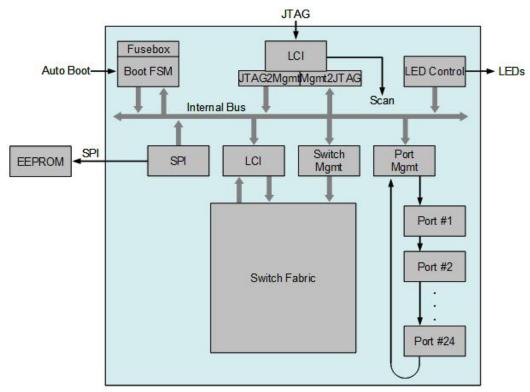

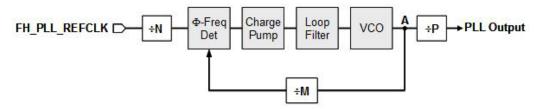

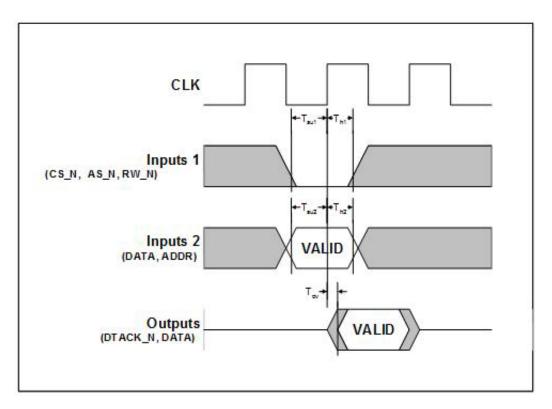

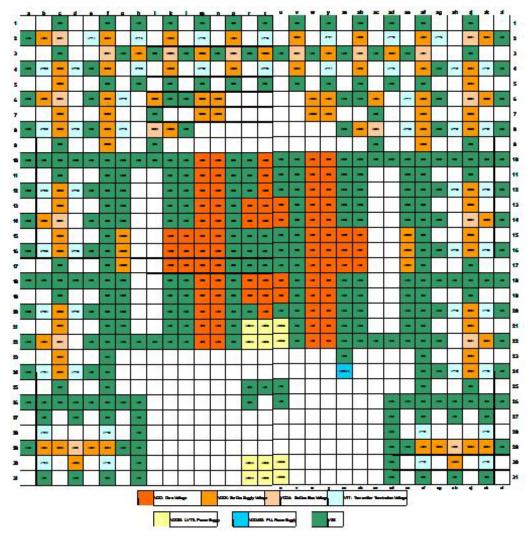

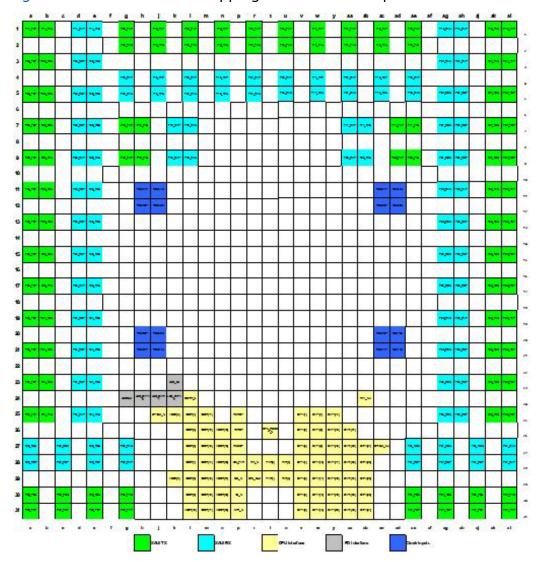

of 3.125 GHz and 4 GHz, each interface can be independently configured to support data rates of 10 Mbps, 100Mbps, 1 Gbps, or 2.5 Gbps.