# N-series Intel<sup>®</sup> Pentium<sup>®</sup> Processors and Intel<sup>®</sup> Celeron<sup>®</sup> Processors

**Datasheet - Volume 1 of 3**

February 2016

Document Number: 332092-002

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at Intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit www.intel.com/design/literature.htm.

I2C is a two-wire communications bus/protocol developed by NXP. SMBus is a subset of the I2C bus/protocol and was developed by Intel. Implementations of the I2C bus/protocol may require licenses from various entities, including NXP Semiconductors N.V.

Intel® 64 architecture requires a system with a 64-bit enabled processor, chipset, BIOS and software. Performance will vary depending on the specifichardware and software you use. Consult your PC manufacturer for more information. For more information, visit http://www.intel.com/content/www/us/en/architecture-and-technology/microarchitecture/intel-64-architecture-general.html.

Intel® Virtualization Technology (Intel® VT) requires a computer system with an enabled Intel® processor, BIOS, and virtual machine monitor (VMM). Functionality, performance or other benefits will vary depending on hardware and software configurations. Software applications may not becompatible with all operating systems. Consult your PC manufacturer. For more information, visit <a href="https://www.intel.com/go/virtualization">https://www.intel.com/go/virtualization</a>.

The original equipment manufacturer must provide TPM functionality, which requires a TPM-supported BIOS. TPM functionality must be initialized andmay not be available in all countries.

For Enhanced Intel SpeedStep® Technology, see the Processor Spec Finder at http://ark.intel.com/ or contact your Intel representative for moreinformation.

Intel® AES-NI requires a computer system with an AES-NI enabled processor, as well as non-Intel software to execute the instructions in the correctsequence. AES-NI is available on select Intel® processors. For availability, consult your reseller or system manufacturer. For more information, see http://software.intel.com/en-us/articles/intel-advanced-encryption-standard-instructions-aes-ni/.

Intel, Celeron, Pentium, Intel® Seamless Display Refresh Rate Switching Technology (Intel® SDRRS Technology), Intel® Display Power Saving Technology (Intel® DPST), Intel® Trusted Execution Engine (Intel® TXE), Intel® Virtualization Technology (Intel® VT), Intel® Acchitecture (Intel® VT-x), Enhanced Intel SpeedStep® Technology, Intel® Display Power Saving Technology (Intel® DPST), Intel® Automatic Display Brightness, Intel® High Definition Audio (Intel® HD Audio), Intel® Performance Primitives, Intel® Advanced Vector Extensions (Intel® AVX), Intel® Rapid Memory Power Management (Intel® RMPM), and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2015-2016, Intel Corporation

# **Contents**

| 1 | Intro | duction                                                                              | 17       |

|---|-------|--------------------------------------------------------------------------------------|----------|

|   | 1.1   | Document Structure and Scope                                                         | 19       |

|   | 1.2   | Terminology                                                                          |          |

|   | 1.3   | Feature Overview                                                                     |          |

|   | 1.4   | Related Documents                                                                    |          |

| 2 | Dhyci | cal Interfaces                                                                       | 27       |

| _ | 2.1   | Platform Power Rails                                                                 |          |

|   | 2.1   | SoC Physical Signal Per Interface                                                    |          |

|   | ۷.۷   | 2.2.1 System Memory Controller Interface Signals (DDR3L)                             |          |

|   |       | 2.2.2 USB 2.0 Controller Interface Signals                                           |          |

|   |       | 2.2.3 USB 3.0 Interface Signals                                                      |          |

|   |       | 2.2.4 Integrated Clock Interface Signals                                             |          |

|   |       | 2.2.5 Display—Digital Display Interface (DDI) Signals                                |          |

|   |       | 2.2.6 MIPI*-CSI (Camera Serial Interface) and ISP Interface Signals                  | 32       |

|   |       | 2.2.7 Storage Controller Interface Signals                                           | 33<br>33 |

|   |       | 2.2.8 High Speed UART Interface Signals                                              |          |

|   |       | 2.2.9 I <sup>2</sup> C Interface Signals                                             |          |

|   | 2.3   | SIO—Serial Peripheral Interface (SPI) Signals                                        |          |

|   | 2.5   | 2.3.1 PCU—Fast Serial Peripheral Interface (SPI) Signals                             |          |

|   |       | 2.3.2 PCU—Real Time Clock (RTC) Interface Signals                                    |          |

|   |       | 2.3.3 PCU—Low Pin Count (LPC) Bridge Interface Signals                               |          |

|   |       | 2.3.4 JTAG Interface Signals                                                         |          |

|   |       | 2.3.5 PCI Express* (PCIe*) Signals                                                   |          |

|   |       | 2.3.6 SATA Signals                                                                   |          |

|   |       | 2.3.7 SMBus Signals                                                                  |          |

|   |       | 2.3.8 Intel <sup>®</sup> High Definition Audio (Intel <sup>®</sup> HD Audio) Signals | 30<br>38 |

|   |       | 2.3.9 Power Management Unit (PMU) Signals                                            |          |

|   |       | 2.3.10 Speaker Signals                                                               |          |

|   |       | 2.3.11 Miscellaneous Signals                                                         |          |

|   | 2.4   | Hardware Straps                                                                      |          |

|   | 2.5   | GPIO Multiplexing                                                                    |          |

| _ |       | essor Core                                                                           |          |

| 3 |       |                                                                                      |          |

|   | 3.1   | SoC Transaction Router                                                               | 49       |

|   | 3.2   | Intel <sup>®</sup> Virtualization Technology (Intel <sup>®</sup> VT)                 | 49       |

|   |       | 3.2.1 Intel® VT-x Objectives                                                         | 49       |

|   | 2.2   | 3.2.2 Intel® VT-x Features                                                           |          |

|   | 3.3   | Security and Cryptography Technologies                                               |          |

|   |       | 3.3.1 PCLMULQDQ Instruction                                                          |          |

|   |       | 3.3.2 Digital Random Number Generator                                                |          |

|   | 2.4   | 3.3.3 Power Aware Interrupt Routing                                                  |          |

|   | 3.4   | Platform Identification and CPUID                                                    |          |

|   | 3.5   | References                                                                           |          |

| 4 | Integ | rated Clock                                                                          | 53       |

| 5 | Ther  | mal Management                                                                       | 55       |

| • | 5.1   | Overview                                                                             |          |

|   | 5.2   | Digital Thermal Sensors                                                              |          |

|   | ٥.۷   | 5.2.1 DTS Timing                                                                     |          |

|   | 5.3   | Hardware Trips                                                                       |          |

|   | ٠.٠   |                                                                                      | /        |

|   |            | 5.3.1 Catastrophic Trip (THERMTRIP)                                                |     |

|---|------------|------------------------------------------------------------------------------------|-----|

|   | 5.4        | SoC Programmable Trips 5                                                           |     |

|   |            | 5.4.1 Aux3 Trip                                                                    | 36  |

|   |            | 5.4.2 Aux2, Aux1, Aux0 Trip 5                                                      | 36  |

|   | 5.5        | Platform Trips 5                                                                   | 36  |

|   |            | 5.5.1 PROCHOT# 5                                                                   |     |

|   |            | 5.5.2 EXTTS                                                                        | 36  |

|   |            | 5.5.3 SVID                                                                         |     |

|   | 5.6        | Dynamic Platform Thermal Framework (DPTF)                                          |     |

|   | 5.7        | Thermal Status                                                                     |     |

| _ | _          |                                                                                    |     |

| 6 |            | r Management 5                                                                     |     |

|   | 6.1        | Power Management Features 5                                                        |     |

|   | 6.2        | Power Management States Supported 5                                                |     |

|   |            | 6.2.1 System States 5                                                              |     |

|   |            | 6.2.2 Integrated Memory Controller States                                          |     |

|   | 6.3        | Processor Core Power Management                                                    |     |

|   |            | 6.3.1 Enhanced Intel <sup>®</sup> SpeedStep <sup>®</sup> Technology 6              | 2   |

|   |            | 6.3.2 Dynamic Cache Sizing 6                                                       |     |

|   |            | 6.3.3 Low-Power Idle States                                                        | 3   |

|   |            | 6.3.3.1 Clock Control and Low-Power States                                         | 3   |

|   |            | 6.3.4 Processor Core C-States Description                                          | 54  |

|   |            | 6.3.4.1 Core C0 State 6                                                            | 4   |

|   |            | 6.3.4.2 Core C1/C1E State 6                                                        |     |

|   |            | 6.3.4.3 Core C6 State 6                                                            |     |

|   |            | 6.3.4.4 Core C7 State 6                                                            |     |

|   |            | 6.3.4.5 C-State Auto-Demotion 6                                                    |     |

|   |            | 6.3.5 Package C-States 6                                                           |     |

|   |            | 6.3.5.1 Package C0 State                                                           |     |

|   |            | 6.3.5.2 Package C1/C1E State                                                       |     |

|   |            | 6.3.5.3 Package C6 State                                                           |     |

|   |            | 6.3.5.4 Package C7 State                                                           |     |

|   |            | 6.3.6 Graphics and Video Decoder C-State                                           |     |

|   |            | 6.3.7 Intel <sup>®</sup> Display Power Saving Technology (Intel <sup>®</sup> DPST) |     |

|   |            | 6.3.8 Intel® Automatic Display Brightness                                          | )/  |

|   |            | 6.3.9 Intel® Seamless Display Refresh Rate Switching Technology (Intel®            |     |

|   | <i>c</i> 1 | SDRRS Technology)                                                                  |     |

|   | 6.4        | Memory Power Management                                                            |     |

|   |            | 6.4.1 Disabling Unused System Memory Outputs                                       |     |

|   |            | 6.4.2 DRAM Power Management and Initialization                                     | 75  |

|   |            | 6.4.2.1 Initialization Role of CKE                                                 |     |

|   |            | 6.4.2.2 Conditional Self-Refresh                                                   |     |

|   |            | 6.4.2.3 Dynamic Power-Down Operation                                               |     |

|   |            | _                                                                                  |     |

| 7 | Syste      | m Memory Controller 7                                                              | 1   |

|   | 7.1        | DDR3L Interface Signals 7                                                          | 1   |

|   | 7.2        | System Memory Technology Supported                                                 | 2   |

| 8 | Grank      | nics, Video, and Display 7                                                         | , , |

| 0 |            |                                                                                    |     |

|   | 8.1        | SoC Graphics Display                                                               |     |

|   |            | 8.1.1 Primary Display Planes A, B, and C                                           | , 3 |

|   |            | 8.1.1.1 Video Sprite Planes A, B, C, D, E, and F                                   | , , |

|   |            | 8.1.1.2 Cursors A, B, and C                                                        |     |

|   |            | 8.1.2 Display Pipes                                                                |     |

|   | 0.0        | 8.1.3 Display Physical Interfaces                                                  |     |

|   | 8.2        | Digital Display Interfaces                                                         | 4   |

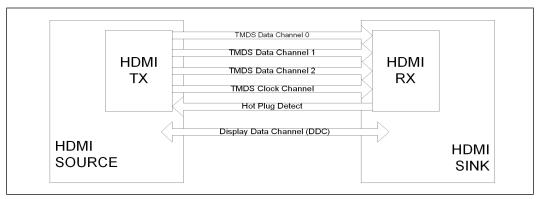

|    |       | 8.2.1 High Definition Multi-media Interface (HDMI)       |           |

|----|-------|----------------------------------------------------------|-----------|

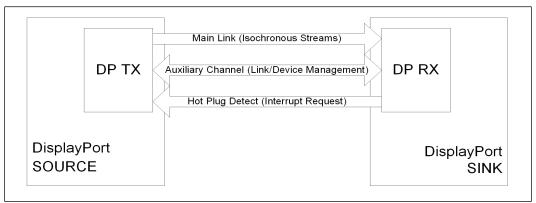

|    |       | 8.2.1.1 DisplayPort*                                     | 76        |

|    |       | 8.2.1.2 embedded DisplayPort* (eDP*)                     | / /<br>77 |

|    |       | 8.2.1.4 Hot-Plug Detect (HPD)                            | / /<br>77 |

|    |       | 8.2.1.5 Integrated Audio Over HDMI and DisplayPort*      | 77<br>77  |

|    |       | 8.2.1.6 High-Bandwidth Digital Content Protection (HDCP) | 77        |

|    | 8.3   | 3-D Graphics and Video                                   |           |

|    |       | 8.3.1 Features                                           |           |

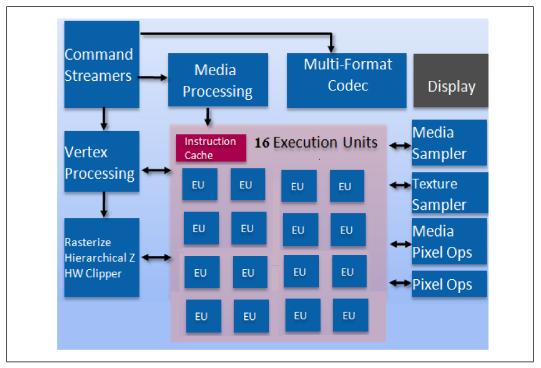

|    |       | 8.3.2 3-D Engine Execution Units                         |           |

|    |       | 8.3.3 3-D Pipeline                                       |           |

|    |       | 8.3.3.1 Vertex Fetch (VF) Stage                          |           |

|    |       | 8.3.3.3 Geometry Shader (GS) Stage                       |           |

|    |       | 8.3.3.4 Clip Stage                                       | 79        |

|    |       | 8.3.3.5 Strips and Fans (SF) Stage                       | 79        |

|    |       | 8.3.3.6 Windower/IZ (WIZ) Stage                          |           |

|    | 8.4   | VED (Video Encode/Decode)                                |           |

|    |       | 8.4.1 Features                                           |           |

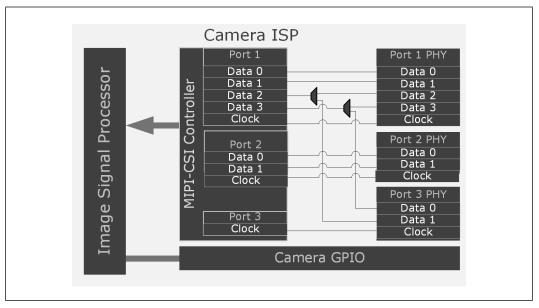

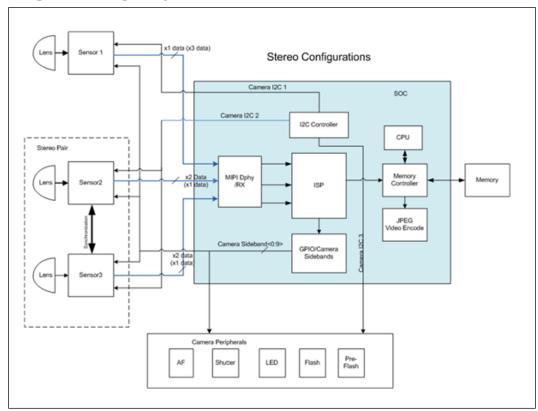

| 9  | MIPI* | *-CSI (Camera Serial Interface) and ISP                  |           |

|    | 9.1   | Signal Descriptions                                      |           |

|    |       | 9.1.1 Imaging Capabilities                               |           |

|    |       | 9.1.2 Simultaneous Acquisition                           |           |

|    |       | 9.1.3 Primary Camera Still Image Resolution              |           |

|    |       | 9.1.4 Burst Mode Support                                 |           |

|    |       | 9.1.6 Secondary Camera Still Image Resolution            |           |

|    |       | 9.1.7 Primary Camera Video Resolution                    |           |

|    |       | 9.1.8 Secondary Camera Video Resolution                  |           |

|    |       | 9.1.9 Bit Depth                                          |           |

|    | 9.2   | Imaging Subsystem Integration                            |           |

|    |       | 9.2.1 Processor Core                                     |           |

|    |       | 9.2.2 Imaging Signal Processor (ISP)                     |           |

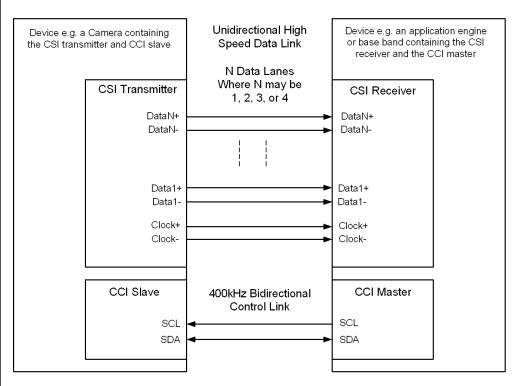

|    |       | 9.2.2.1 MIPI*-CSI-2 Ports                                |           |

|    |       | 9.2.2.2 I <sup>2</sup> C for Camera Interface            |           |

|    | 9.3   | Functional Description                                   |           |

|    | 5.5   | 9.3.1 Preview Mode                                       |           |

|    |       | 9.3.2 Image Capture                                      |           |

|    |       | 9.3.3 Video Capture                                      |           |

|    |       | 9.3.4 ISP Overview                                       |           |

|    | 9.4   | MIPI*-CSI-2 Receiver                                     |           |

|    |       | 9.4.1 MIPI*-CSI-2 Receiver Features                      | 90        |

| 10 | SoC S | Storage                                                  | 93        |

|    | 10.1  | SoC Storage Overview                                     | 93        |

|    |       | 10.1.1 Storage Control Cluster (e-MMC*, SDIO, SD)        | 93        |

|    | 10.2  | Signal Descriptions                                      |           |

|    | 10.3  | References                                               | 94        |

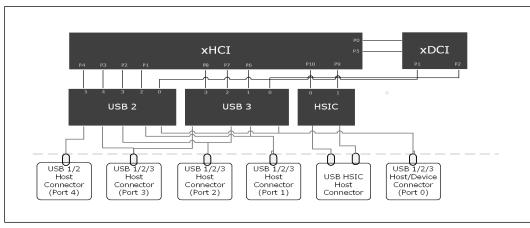

| 11 | USB C | Controller Interfaces                                    | 95        |

|    | 11.1  | SoC Supports                                             |           |

|    | 11.2  | Signal Descriptions                                      |           |

|    | 11.3  | USB 3.0 xHCI (Extensible Host Controller Interface)      |           |

|    |       | 11.3.1 Features of USB 3.0 Host                          |           |

|    |       | 11.3.1.1 USB 3.0 Features                                | 97        |

|    |        | 11.3.2  | Features of USB HSIC                           | 97  |

|----|--------|---------|------------------------------------------------|-----|

|    | 11.4   | Refere  | nces                                           | 97  |

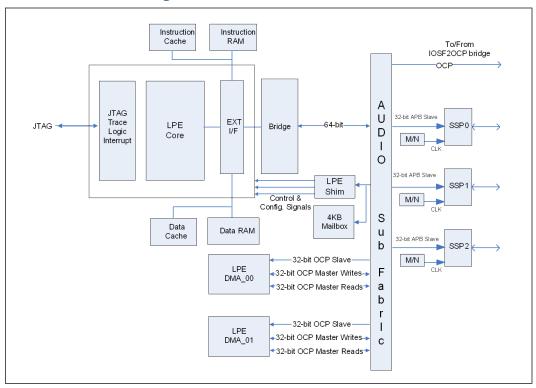

| 12 | Low D  |         | ngine (LPE) for Audio (I <sup>2</sup> S)       |     |

| 12 | 12.1   |         | Descriptions                                   |     |

|    | 12.1   |         | es                                             |     |

|    | 12.2   |         |                                                |     |

|    |        | 12.2.1  | Audio Capabilities                             |     |

|    |        |         | 12.2.1.1 Audio Decode                          |     |

|    | 12.3   |         | 12.2.1.2 Audio Encode                          |     |

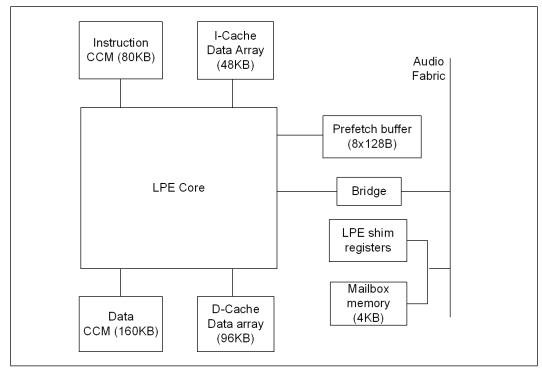

|    | 12.3   | 12.3.1  | ed Block Level Description                     |     |

|    |        | 12.3.1  | LPE Core Memory Architecture                   |     |

|    |        | 12.3.2  | Instruction Closely Coupled Memory (CCM)       |     |

|    |        |         |                                                |     |

|    |        | 12.3.4  | Data Closely Coupled Memory (CCM)              |     |

|    | 12.4   | 12.3.5  | Mailbox Memory and Data Exchange               |     |

|    | 12.4   |         | are Implementation Considerations              |     |

|    |        | 12.4.1  | SoC Processor Core Cache Coherence             |     |

|    |        | 12.4.2  | Interrupts                                     |     |

|    |        |         | 12.4.2.1 LPE Peripheral Interrupts             | 103 |

|    |        |         | 12.4.2.3 Interrupts Between PMC and LPE        |     |

|    |        | 12.4.3  | Power Management Options for the LPE Core      |     |

|    |        | 12.4.3  | External Timer                                 |     |

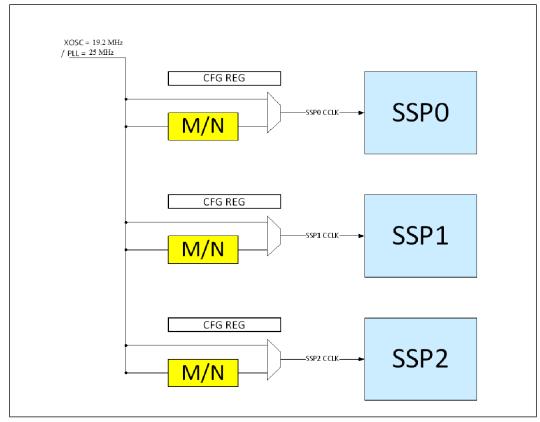

|    | 12.5   | Clocks  |                                                |     |

|    | 12.3   | 12.5.1  | Clock Frequencies                              |     |

|    |        | 12.5.1  | 38.4 MHz Clock for LPE                         |     |

|    |        | 12.5.2  | Calibrated Ring Osc (50/100 MHz) Clock for LPE |     |

|    |        | 12.5.3  | Cache and CCM Clocking                         |     |

|    |        | 12.5.4  | SSP Clocking                                   |     |

|    |        | 12.5.6  | M/N Divider                                    |     |

|    |        |         | 12.5.6.1 Example                               |     |

|    |        |         | 12.5.6.2 Accuracy and Jitter                   |     |

|    |        |         | 12.5.6.3 Configuration                         |     |

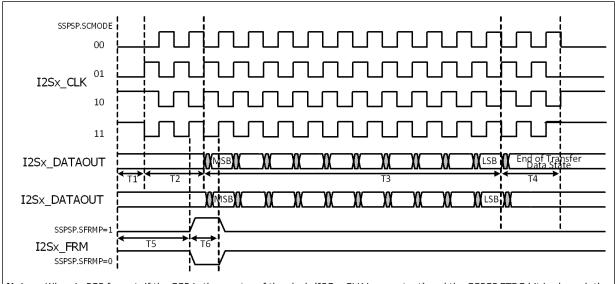

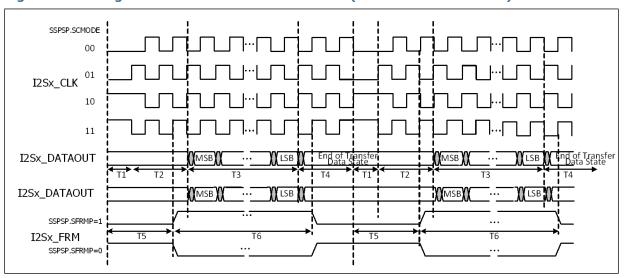

|    | 12.6   |         | <sup>2</sup> S)                                |     |

|    | 12.0   | 12.6.1  | Introduction                                   |     |

|    |        | 12.6.2  | SSP Features                                   |     |

|    |        | 12.6.3  | Operation                                      |     |

|    |        | 12.6.4  | LPE and DMA FIFO Access                        |     |

|    |        | 12.6.5  | Supported Formats                              |     |

|    |        |         | 12.6.5.1 Programmable Serial Protocol (PSP)    |     |

|    | -6     |         | •                                              |     |

| 13 |        |         | d Execution Engine (Intel $^{	ext{@}}$ TXE)    |     |

|    | 13.1   | Featur  | es                                             |     |

|    |        | 13.1.1  | Security Feature                               |     |

|    |        |         | 13.1.1.1 Hardware Accelerators                 | 113 |

| 14 | Intel® | High D  | efinition Audio (Intel <sup>®</sup> HD Audio)  | 115 |

|    | 14.1   |         | Descriptions                                   |     |

|    | 14.1   |         | es                                             |     |

|    | 14.2   |         | nces                                           |     |

|    |        |         |                                                |     |

| 15 | Serial |         | O) Overview                                    |     |

|    | 15.1   | Registe | er Map                                         | 117 |

|    | 15.2   | SIO-S   | Serial Peripheral Interface (SPI)              | 117 |

|    |        | 15.2.1  | Signal Descriptions                            |     |

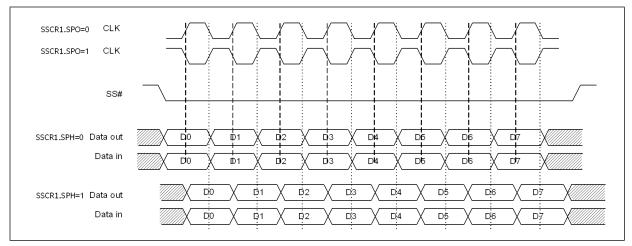

|    |        |         | 15.2.1.1 Clock Phase and Polarity              | 117 |

|    |        |         | SIO—I <sup>2</sup> C Interface                 |     |

|    |        | 15.2.3 Signal Descriptions                             |     |

|----|--------|--------------------------------------------------------|-----|

|    |        | 15.2.4 Features                                        | 119 |

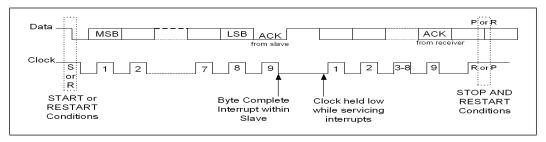

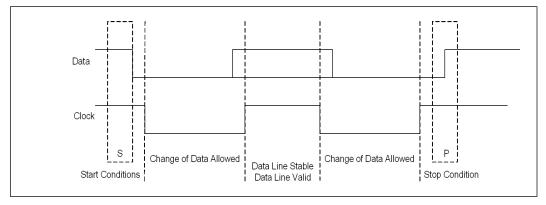

|    |        | 15.2.4.1 I <sup>2</sup> C Protocol                     | 119 |

|    |        | 15.2.4.2 I <sup>2</sup> C Modes of Operation           | 119 |

|    |        | 15.2.4.3 Functional Description                        |     |

|    |        | 15.2.5 References                                      |     |

|    |        | 15.2.6 Register Map                                    |     |

|    | 15.3   | SIO—High Speed UART                                    |     |

|    |        | 15.3.1 Signal Descriptions                             |     |

|    |        | 15.3.2 Features                                        |     |

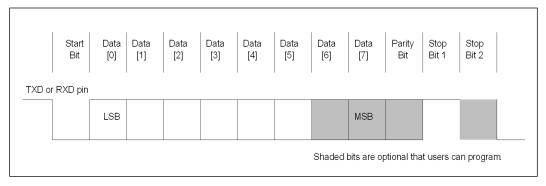

|    |        | 15.3.2.1 UART Function                                 |     |

|    |        | 15.3.2.2 Clock and Reset                               | 122 |

|    |        | 15.3.2.3 Baud Rate Generator                           |     |

|    |        | 15.3.3 Use                                             |     |

|    |        | 15.3.3.1 DMA Mode Operation                            |     |

|    |        | 15.3.3.2 FIFO Polled-Mode Operation                    | 124 |

| 16 | Platfo | orm Controller Unit (PCU) Overview                     | 127 |

|    | 16.1   | PCU Configuration Features for BIOS/EFI Boot Overview  |     |

|    | 10.1   | 16.1.1 BIOS/EFI Top Swap                               |     |

|    |        | 16.1.1.1 BIOS/EFI Controlled                           |     |

|    |        | 16.1.1.2 Hardware Controlled                           |     |

|    |        | 16.1.2 BIOS/EFI Boot Strap                             |     |

|    | 16.2   | PMU—Power Management Controller (PMC)                  |     |

|    |        | 16.2.1 Signal Descriptions                             |     |

|    |        | 16.2.2 Features                                        |     |

|    |        | 16.2.2.1 Sx-G3-Sx—Handling Power Failures              |     |

|    |        | 16.2.2.2 Event Input Signals and Their Usage           |     |

|    |        | 16.2.2.3 System Power Planes                           | 131 |

|    |        | 16.2.2.4 SMI#/SCI Generation                           | 133 |

|    |        | 16.2.2.5 Platform Clock Support                        | 135 |

|    |        | 16.2.2.6 INIT# (Initialization) Generation             |     |

|    | 46.5   | 16.2.3 References                                      |     |

|    | 16.3   | PCU—Serial Peripheral Interface (SPI)                  |     |

|    |        | 16.3.1 Signal Descriptions                             |     |

|    | 46.4   | 16.3.2 Features                                        | 13/ |

|    | 16.4   | PCU—Universal Asynchronous Receiver/Transmitter (UART) |     |

|    |        | 16.4.1 Signal Descriptions                             |     |

|    |        | 16.4.2 Features                                        |     |

|    |        | 16.4.2.1 FIFO Operation                                |     |

|    |        | 16.4.3 Use                                             |     |

|    |        | 16.4.3.1 Base I/O Address                              |     |

|    |        | 16.4.4 UART Enable/Disable                             |     |

|    |        | 16.4.5 I/O Mapped Registers                            |     |

|    | 16.5   | Register Map                                           |     |

|    | 16.5   | PCU—System Management Bus (SMBus)                      |     |

|    | 10.0   | 16.6.1 Signal Descriptions                             |     |

|    |        | 16.6.2 Features                                        |     |

|    |        | 16.6.2.1 Host Controller                               |     |

|    |        | 16.6.2.2 Bus Arbitration                               |     |

|    |        | 16.6.2.3 Bus Timing                                    |     |

|    |        | 16.6.2.4 Interrupts/SMI#                               |     |

|    |        | 16.6.2.5 PCU_SMB_ALERT#                                |     |

|    |        | 16.6.2.6 SMBus CRC Generation and Checking             | 152 |

|    |        | 16.6.2.7 SMBus Slave Interface                         | 152 |

|    |        | 16 6 2 8 Function Disable                              | 153 |

|       | 16.6.3 References                                   |     |

|-------|-----------------------------------------------------|-----|

| 16.7  | PCU—Intel <sup>®</sup> Legacy Block (iLB) Overview  | 154 |

|       | 16.7.1 Signal Descriptions                          | 154 |

|       | 16.7.2 Features                                     |     |

|       | 16.7.2.1 Key Features                               |     |

|       | 16.7.2.2 Non-Maskable Interrupt                     | 155 |

| 16.8  | PCU—iLB Low Pin Count (LPC) Bridge                  |     |

| 10.0  | 16.8.1 Signal Descriptions                          | 156 |

|       | 16.8.2 Features                                     |     |

|       | 16.0.2 Teatures                                     | 150 |

|       | 16.8.2.1 Memory Cycle Notes                         | 157 |

|       | 16.8.2.2 Trusted Flatform Produce (TFM) 1.2 Support | 157 |

|       | 16.8.2.3 FWH Cycle Notes                            | 150 |

|       | 16.8.2.5 POST Code Redirection                      | 158 |

|       | 16.8.2.6 Power Management                           |     |

|       | 16.8.2.7 Serialized IRQ (SERIRQ)                    | 158 |

|       | 16.8.3 Use                                          | 161 |

|       | 16.8.3.1 LPC Clock Delay Compensation               |     |

|       | 16.8.3.2 LPC Power Management                       | 162 |

|       | 16.8.3.3 SERIRQ Disable                             | 162 |

|       | 16.8.4 References                                   | 162 |

| 16.9  | PCU—iLB Real Time Clock (RTC)                       |     |

| 10.5  | 16.9.1 Signal Descriptions                          |     |

|       | 16.9.1 Signal Descriptions                          | 102 |

|       | 16.9.2 Features                                     |     |

|       | 16.9.2.1 Update Cycles                              |     |

|       | 16.9.3 Interrupts                                   |     |

|       | 16.9.3.1 Lockable RAM Ranges                        | 164 |

|       | 16.9.3.2 Clearing Battery-Backed RTC RAM            | 164 |

|       | 16.9.3.3 Using a GPI to Clear CMOS                  | 100 |

|       | 16.9.4 References                                   | 100 |

|       | 16.9.5 I/O Mapped Registers                         |     |

|       | 16.9.6 Indexed Registers                            |     |

| 16.10 | PCU—iLB 8254 Timers                                 |     |

|       | 16.10.1 Signal Descriptions                         |     |

|       | 16.10.2 Features                                    |     |

|       | 16.10.2.1Counter 0—System Timer                     | 167 |

|       | 16.10.2.2Counter 1—Refresh Request Signal           | 167 |

|       | 16.10.2.3Counter 2—Speaker Tone                     |     |

|       | 16.10.3 Use                                         |     |

|       | 16.10.3.1Timer Programming                          | 167 |

|       | 16.10.3.2Reading From the Interval Timer            |     |

| 16.11 | L PCU—iLB High Precision Event Timer (HPET)         | 170 |

|       | 16.11.1 Features                                    |     |

|       | 16.11.1.1Non-Periodic Mode—All Timers               |     |

|       | 16.11.1.2Periodic Mode—Timer 0 Only                 |     |

|       | 16.11.2 References                                  |     |

|       | 16.11.3 Memory Mapped Registers                     |     |

| 16.12 | PCU—iLB GPIO                                        |     |

|       | 16.12.1 Signal Description                          | 174 |

|       | 16.12.2 GPIO Controller                             | 174 |

|       | 16.12.3 Use                                         |     |

|       | 16.12.4 GPIO Registers                              | 175 |

|       | 16.12.4.1Memory Space Address Mapping               |     |

|       | 16.12.5 Register Address Mapping                    |     |

|       | 16.12.6 Hard Strap Logic                            |     |

| 16.13 | PCU—iLB Interrupt Decoding and Routing              |     |

|     |        | 16.13.1 Features                                             | 177  |

|-----|--------|--------------------------------------------------------------|------|

|     |        | 16.13.1.1Interrupt Decoder                                   | 177  |

|     |        | 16.13.1.2Interrupt Router                                    |      |

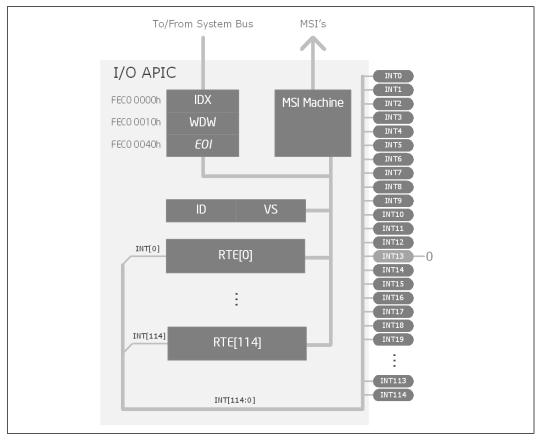

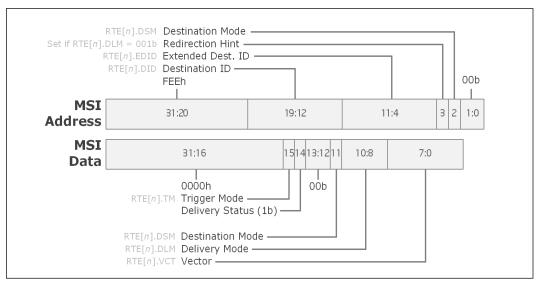

|     | 16.14  | PCU—iLB I/O APIC                                             |      |

|     |        | 16.14.1 Features                                             |      |

|     |        | 16.14.2 Use                                                  |      |

|     | 16.15  | 16.14.3 Indirect I/O APIC Registers(NIC)                     |      |

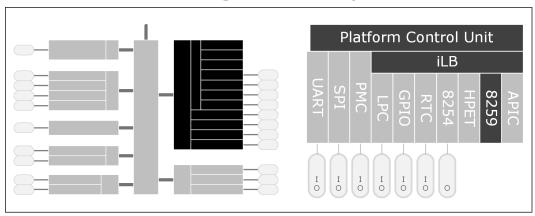

|     | 16.15  | PCU—iLB 8259 Programmable Interrupt Controllers (PIC)        |      |

|     |        | 16.15.1 Features                                             |      |

|     |        | 16.15.1.1Interrupt Handling                                  | 182  |

|     |        | 16.15.1.3Operation Command Words (ICWX)                      |      |

|     |        | 16.15.1.4Modes of Operation                                  | 185  |

|     |        | 16.15.1.5End-of-Interrupt (EOI) Operations                   | 186  |

|     |        | 16.15.1.6Masking Interrupts                                  | 187  |

|     |        | 16.15.2 I/O Mapped Registers                                 | 187  |

| 17  | Serial | ATA (SATA)                                                   | 189  |

| _,  | 17.1   | Functional Feature Descriptions                              |      |

|     | 17.1   | Signal Descriptions                                          |      |

|     | 17.3   | Features                                                     |      |

|     | 17.13  | 17.3.1 Supported Features                                    |      |

|     |        | 17.3.2 Features Not Supported                                |      |

|     | 17.4   | References                                                   |      |

| 4.0 | DCT E  | xpress* 2.0                                                  |      |

| 18  |        | •                                                            |      |

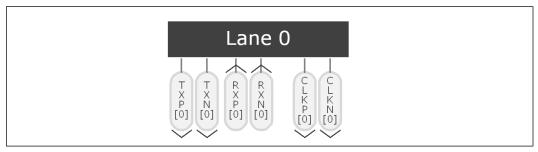

|     | 18.1   | Signal Descriptions                                          |      |

|     | 18.2   | Features                                                     |      |

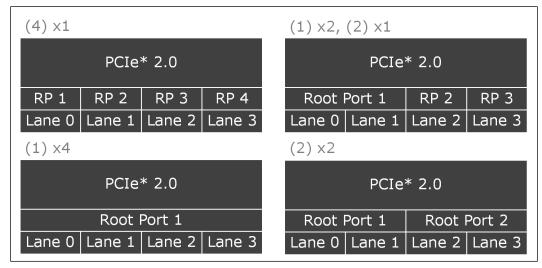

|     |        | 18.2.1 Root Port Configurations                              |      |

|     |        | 18.2.2.1 Express Card Hot-Plug Events                        |      |

|     |        | 18.2.2.2 System Error (SERR)                                 | 193  |

|     |        | 18.2.3 Power Management                                      |      |

|     | 18.3   | References                                                   |      |

|     |        |                                                              |      |

| 19  |        | ap, Ball Out, and SoC Pin Locations                          |      |

|     | 19.1   | SoC Pin List Locations                                       | 201  |

| 20  | Packa  | ge Information                                               | 213  |

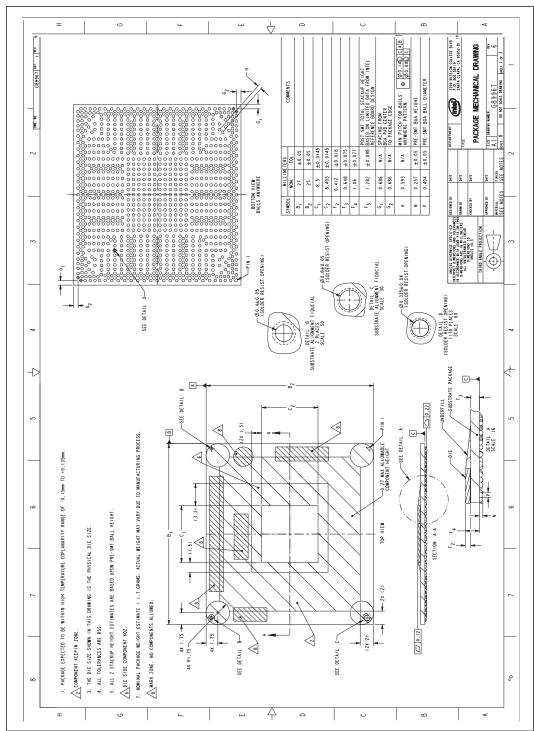

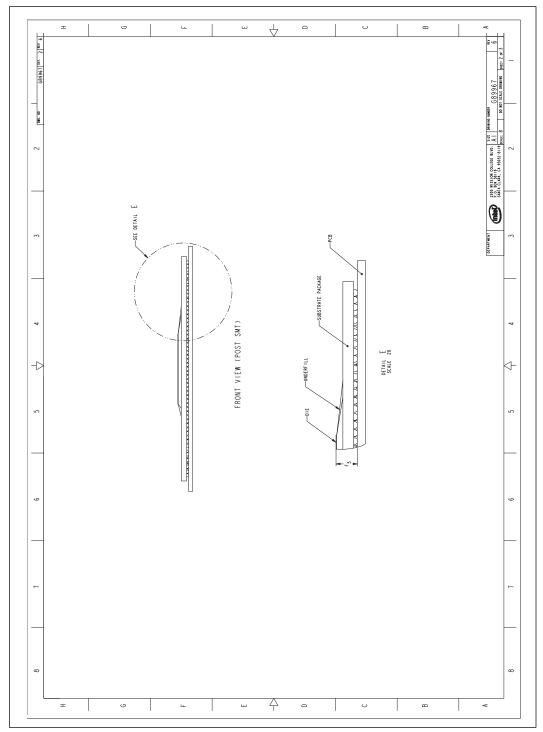

|     | 20.1   | SoC Attributes                                               | 213  |

|     | 20.2   | Package Diagrams                                             | 214  |

| 21  | Flactr | ical Specifications                                          | 217  |

|     | 21.1   | Absolute Maximum and Minimum Specifications                  |      |

|     | 21.2   | Thermal Specifications                                       |      |

|     | 21.3   | Storage Conditions                                           |      |

|     | 21.5   | 21.3.1 Post Board Attach                                     |      |

|     | 21.4   | Voltage and Current Specifications                           |      |

|     |        | 21.4.1 VCC, VGG, and VNN Voltage Specifications              |      |

|     |        | 21.4.2 Voltage Identification (VID)                          |      |

|     | 21.5   | Crystal Specifications                                       |      |

|     | 21.6   | DC Specifications                                            |      |

|     |        | 21.6.1 Display DC Specification                              |      |

|     |        | 21.6.1.1 DisplayPort* DC Specification                       | 230  |

|     |        | 21.6.1.2 HDMI DC Specification                               | 231  |

|     |        | 21.6.1.3 embedded DisplayPort* DC Specification              |      |

|     |        | 21.6.1.4 DisplayPort* AUX Channel DC Specification           | 232  |

|     |        | ZI.D.I.S embedded Display Port" AUX Channel DC Specification | 1.31 |

| 2       | 21.6.1.6 DDC Signal DC Specification                    | 233 |

|---------|---------------------------------------------------------|-----|

| 21.6.2  | MIPI*-Camera Serial Interface (CSI) DC Specification    |     |

| 21.6.3  | SCC—SDIO DC Specification                               |     |

| 21.6.4  | SCC—SD Card DC Specification                            |     |

| 21.6.5  | eMMC* 4.51 DC Electrical Specification                  |     |

| 21.6.6  | JTAG DC Specification                                   | 237 |

| 21.6.7  | DDR3L Memory Controller DC Specification                | 238 |

| 21.6.8  | USB 2.0 Host DC Specification                           |     |

| 21.6.9  | USB HSIC DC Specification                               |     |

| 21.6.10 | USB 3.0 DC Specification                                | 241 |

| 21.6.11 | LPC DC Specification                                    | 241 |

| 21.6.12 | PCU SPI DC Specification                                |     |

| 21.6.13 | Power Management/Thermal (PMC) and RTC DC Specification | 242 |

| 21.6.14 | SVID DC Specification                                   | 244 |

| 21.6.15 | GPIO DC Specification                                   | 245 |

| 21.6.16 | SIO-SPI DC Specifications                               | 245 |

| 21.6.17 | SIO—I <sup>2</sup> C DC Specification                   | 245 |

| 21.6.18 | SIO—UART DC Specification                               |     |

| 21.6.19 | I <sup>2</sup> S Audio DC Specification                 | 246 |

| 21.6.20 | High Definition Audio DC Specifications                 | 246 |

| 21.6.21 | SMBus (System Management) DC Specification              | 247 |

| 21.6.22 | PCI Express* DC Specification                           | 247 |

| 21.6.23 | Serial ATA (SATA) DC Specification                      | 247 |

| Figures                                                                      |       |

|------------------------------------------------------------------------------|-------|

| 1-1 SoC Block Diagram (Netbook)                                              | 18    |

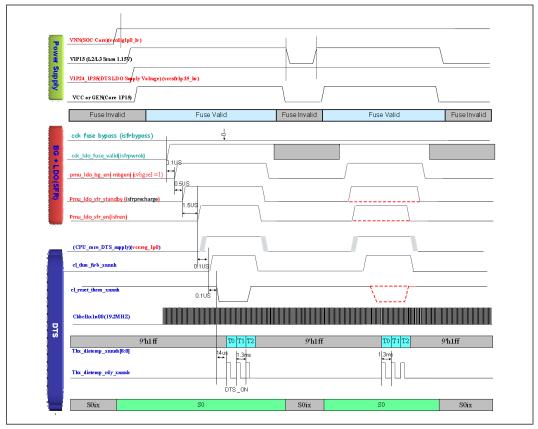

| 5-1 DTS Mode of Operation                                                    |       |

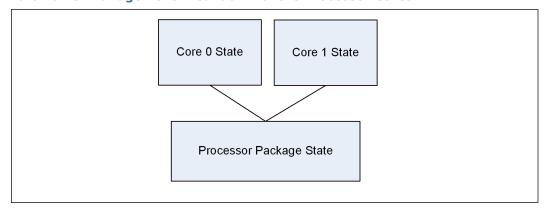

| 6-1 Idle Power Management Breakdown of the Processor Cores                   | 63    |

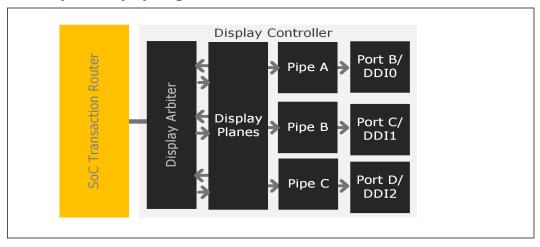

| 8-1 SoC Graphics Display Diagram                                             |       |

| 8-2 HDMI Overview                                                            |       |

| 8-3 DisplayPort* Overview                                                    | 76    |

| 8-4 3-D Graphics Block Diagram                                               | 78    |

| 9-1 Camera Connectivity                                                      |       |

| 9-2 Image Processing Components                                              | 86    |

| 9-3 MIPI*-CSI Bus Block Diagram                                              |       |

| 11-1xHCI Port Mapping                                                        |       |

| 12-1Audio Cluster Block Diagram                                              |       |

| 12-2Memory Connections for LPE                                               |       |

| 12-3SSP CCLK Structure                                                       |       |

| 12-4Programmable Serial Protocol Format                                      |       |

| 12-5Programmable Serial Protocol Format (Consecutive Transfers)              |       |

| 15-1Clock Phase and Polarity                                                 |       |

| 15-2Data Transfer on the I <sup>2</sup> C Bus                                | . 120 |

| 15-3START and STOP Conditions                                                |       |

| 15-4UART Data Transfer                                                       |       |

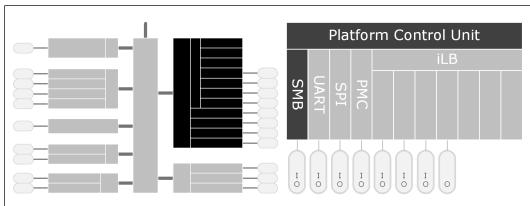

| 16-1Platform Control Unit—System Management Bus                              |       |

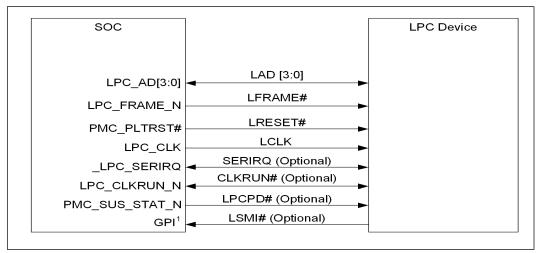

| 16-2LPC Interface Diagram                                                    |       |

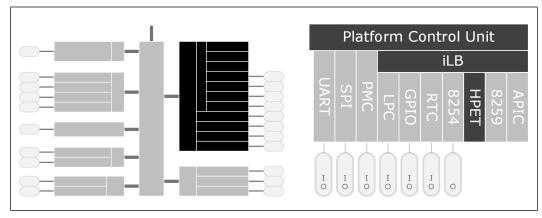

| 16-3Platform Control Unit—High Precision Event Timer (HPET)                  | 170   |

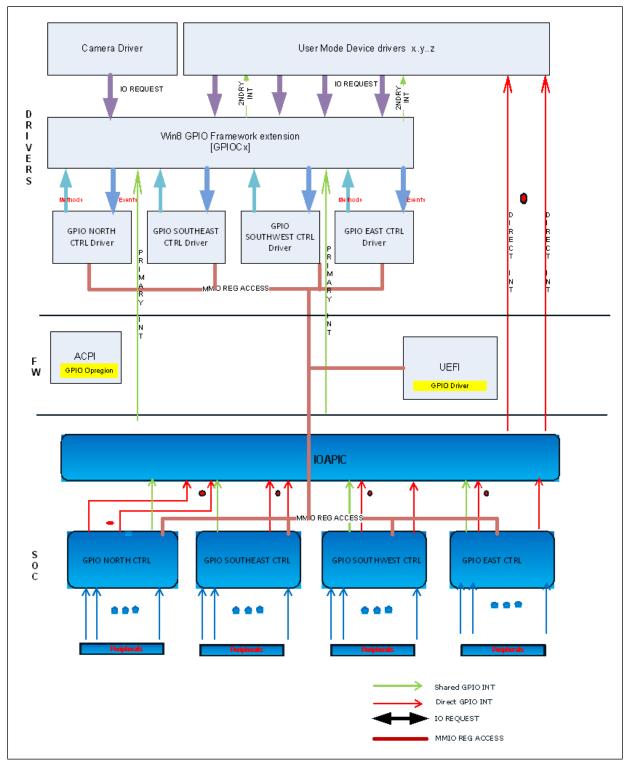

| 16-4GPIO Stack Block Diagram                                                 |       |

| 16-5Platform Control Unit—APIC                                               |       |

| 16-6Detailed Block Diagram                                                   |       |

| 16-7MSI Address and Data                                                     |       |

| 16-8Platform Control Unit—8259 Programmable Interrupt Controllers            |       |

| 18-1PCI Express* 2.0 Lane 0 Signal Example                                   |       |

| 18-2Root Port Configuration Options                                          |       |

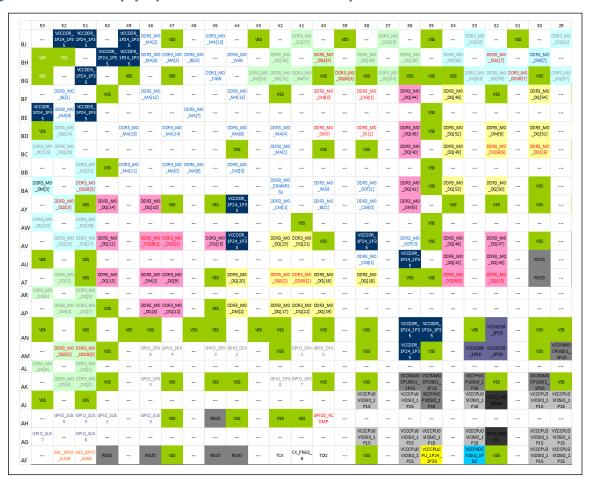

| 19-1Ball Map (Top Left View—Columns 53–29)                                   |       |

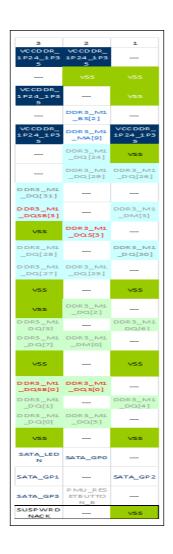

| 19-2Ball Map—DDR3L (Top Right View—Columns 28 – 4)                           |       |

| 19-3Ball Map—DDR3L (Top Right View Columns 3-1)                              |       |

| 19-4Ball Map—DDR3L (Bottom Left View—Columns 53–29)                          |       |

| 19-5Ball Map—DDR3L (Bottom Right View—Columns 28 – 4)                        | 100   |

| 19-6Ball Map—DDR3L (Bottom Right View Columns 3–1)                           | 200   |

| 20-1Package Mechanical Drawing—Part 1 of 3                                   |       |

| 20-2Package Mechanical Drawing—Part 2 of 3                                   |       |

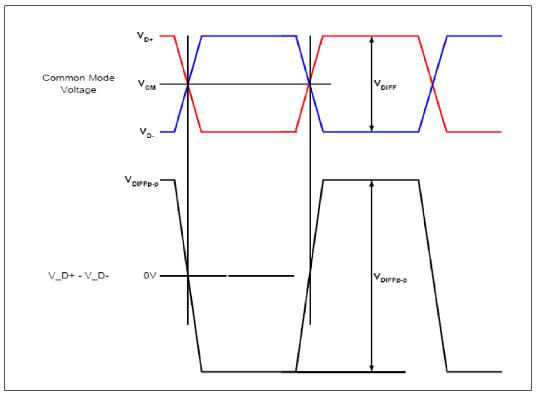

| 21-1Definition of Differential Voltage and Differential Voltage Peak-to-Peak |       |

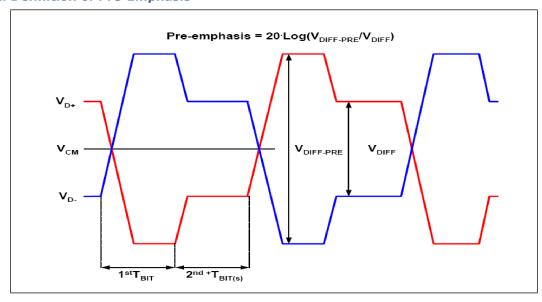

| 21-2Definition of Pre-Emphasis                                               |       |

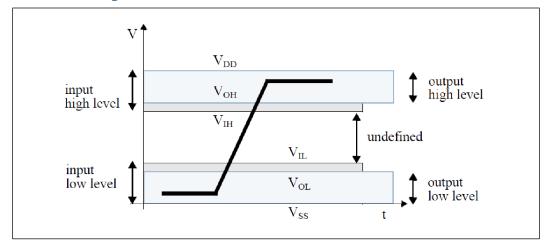

| 21-34.51 DC Bus Signal Level                                                 | 234   |

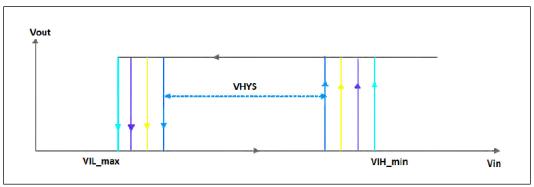

| 21-4Definition of VHYS in the DDR#L Interface Timing Specification           |       |

| 21-4Definition of Vitts in the DDR#L Interface finding Specification         | . 244 |

|                                                                              |       |

|                                                                              |       |

| Tables                                                                       |       |

| 1-1 Structure of the Processor Datasheet                                     | 19    |

| 1-2 Related Documents                                                        |       |

| 2-1 Platform Power Well Definitions                                          |       |

| 2-2 Buffer Type Definitions                                                  |       |

| 2-3 Default Memory Controller Interface Signals                              |       |

| 2-4 DDR3L System Memory Signals                                              |       |

| 2-5 USB 2.0 Interface Signals                                                |       |

| 2-6 USB 2.0 HSIC Interface Signals                                           | 31    |

|                                                                              |       |

| 2-7 USB 3.0 Interface Signals                                                |      |

|------------------------------------------------------------------------------|------|

| 2-8 Integrated Clock Interface Signals                                       | . 31 |

| 2-9 Digital Display Interface Signals                                        |      |

| 2-10MIPI*-CSI Interface Signals                                              |      |

| 2-11Storage Controller (e-MMC*, SDIO, SD) Interface Signals                  |      |

| 2-12High Speed UART Interface Signals                                        |      |

| 2-13I <sup>2</sup> C Interface Signals                                       |      |

| 2-14SIO—Serial Peripheral Interface (SPI) Signals                            | . JJ |

|                                                                              |      |

| 2-15PCU—Fast Serial Peripheral Interface (SPI) Signals                       |      |

| 2-16PCU—Real Time Clock (RTC) Interface Signals                              |      |

| 2-17PCU—LPC Bridge Interface Signals                                         |      |

| 2-18JTAG Interface Signals                                                   | . 37 |

| 2-19PCI Express* (PCIe*) Signals and Clocks                                  | . 37 |

| 2-20SATA Signals and Clocks                                                  | . 38 |

| 2-21SMBus Signals and Clocks                                                 | . 38 |

| 2-22Intel® High Definition Audio (Intel® HD Audio) Signals and Clocks        | . 38 |

| 2-23Power Management Unit (PMU) Signals and Clocks                           |      |

| 2-24SPEAKER Signals and Clocks                                               |      |

| 2-25Miscellaneous Signals and Clocks                                         |      |

| 2-26Hard Strap Description and Functionality                                 |      |

| 2-20 Grad Strap Description and Functionality                                | . 40 |

|                                                                              |      |

| 4-1 SoC Clock Inputs                                                         |      |

| 4-2 SoC Clock Outputs                                                        | . 53 |

| 5-1 Temperature Reading Based on DTS                                         |      |

| 6-1 General Power States for System                                          |      |

| 6-2 Platform Voltage Rails and Power Modes                                   | . 61 |

| 6-3 ACPI PM State Transition Rules                                           | . 61 |

| 6-4 Main Memory States                                                       | . 62 |

| 6-5 Processor Core/States Support                                            |      |

| 6-6 Coordination of Core/Module Power States at the Package Level            |      |

| 7-1 Memory Channel 0 DDR3L Signals                                           |      |

| 7-3 Supported DDR3L DRAM Devices                                             |      |

| 7-4 Supported DDR3L Memory Size Per Rank                                     |      |

| 7-4 Supported DDR3L Memory Size Fer Rank                                     | . /∠ |

|                                                                              |      |

| 8-1 Display Technologies Support                                             |      |

| 8-2 SoC Display Configuration                                                | . 74 |

| 8-3 SoC Display supported Resolutions                                        |      |

| 8-4 Hardware Accelerated Video Decode/Encode Codec Support                   |      |

| 8-5 Resolution Details on Supported HW Accelerated Video Decode/Encode Codec |      |

| 9-1 CSI Signals                                                              | . 83 |

| 9-2 GPIO Signals                                                             | . 83 |

| 9-3 Imaging Capabilities                                                     |      |

| 10-1e-MMC* Signals                                                           |      |

| 10-2SDIO Signals                                                             |      |

| 10-3SD Signals                                                               |      |

|                                                                              |      |

| 11-1USB Signals                                                              |      |

| 11-2HSIC Signals                                                             |      |

| 12-1LPE Signals                                                              |      |

| 12-2Clock Frequencies                                                        |      |

| 12-3M/N Values—Examples                                                      |      |

| 12-4M/N Configurable Fields                                                  |      |

| 12-5Programmable Protocol Parameters                                         |      |

| 14-1Signals Description                                                      | 116  |

| 15-1SPI Interface Signals                                                    |      |

| 15-2I2C [6:0] Signals                                                        |      |

|                                                                              |      |

| 15-3UART 1 Interrace Signals                                    |     |

|-----------------------------------------------------------------|-----|

| 15-4UART 2 Interface Signals                                    | 122 |

| 15-5Baud Rates Achievable with Different DLAB Settings          |     |

| 16-1BBS Configurations                                          |     |

| 16-2PMC Signals                                                 | 128 |

| 16-3Transitions Due to Power Failure                            |     |

| 16-4Transitions Due to Power Button                             |     |

| 16-5System Power Planes                                         |     |

| 16-6Causes of SMI and SCI                                       |     |

| 16-7INIT# Assertion Causes                                      |     |

| 16-8SPI Signals                                                 |     |

| 16-9UART Signals                                                |     |

| 16-10Baud Rate Examples                                         | 141 |

| 16-11Register Access List                                       |     |

| 16-12SMBus Signal Names                                         |     |

| 16-13I <sup>2</sup> C Block Read                                |     |

| 16-14Enable for PCU_SMB_ALERT#                                  | 151 |

| 16-15Enables for SMBus Host Events                              | 151 |

| 16-16Enables for the Host Notify Command                        | 151 |

| 16-17Host Notify Format                                         |     |

| 16-18iLB Signals                                                | 154 |

| 16-19NMI Sources                                                | 155 |

| 16-20LPC Signals                                                | 156 |

| 16-21SERIRQ—Stop Frame Width to Operation Mode Mapping          | 160 |

| 16-22SERIRQ Interrupt Mapping                                   | 160 |

| 16-23RTC Signals                                                | 162 |

| 16-24Register Bits Reset by RTC_RST# Assertion                  | 165 |

| 16-25I/O Registers Alias Locations                              | 166 |

| 16-26RTC Indexed Registers                                      |     |

| 16-278254 Signals                                               |     |

| 16-28Counter Operating Modes                                    |     |

| 16-298254 Interrupt Mapping                                     |     |

| 16-30Generic Community Address Ranges                           |     |

| 16-31Register Address Mapping                                   |     |

| 16-32Interrupt Controller Connections                           | 181 |

| 16-33Interrupt Status Registers                                 |     |

| 16-34Content of Interrupt Vector Byte                           |     |

| 16-35I/O Registers Alias Locations                              |     |

| 17-1Signals Description                                         | 189 |

| 17-2SATA/AHCI Feature Matrix                                    |     |

| 18-1Supported Interrupts Generated From Events/Packets          | 192 |

| 18-2Interrupt Generated for INT[A-D] Interrupts                 | 193 |

| 19-1SoC Pin List Locations                                      | 201 |

| 21-1SoC Base Frequencies and Thermal Specifications             | 218 |

| 21-2Storage Conditions Prior to Board Attach                    |     |

| 21-3C-Step SoC Power Rail DC Specifications and Maximum Current |     |

| 21-4D-Step SoC Power Rail DC Specifications and Maximum Current |     |

| 21-5VCC, VGG, and VNN DC Voltage Specifications                 |     |

| 21-6VSDIO Voltage Setting                                       |     |

| 21-7IMVP7.0 Voltage Identification Reference                    |     |

| 21-8ILB RTC Crystal Specification                               |     |

| 21-9Integrated Clock Crystal Specification                      |     |

| 21-10DisplayPort* DC specification                              |     |

| 21-11HDMI DC Specification                                      |     |

| 21-12embedded Display Port* DC Specification                    | 231 |

| 21-13DDI AUX Channel DC Specification                                               | . 232 |

|-------------------------------------------------------------------------------------|-------|

| 21-14embedded Display Port* AUX Channel DC Specification                            | .232  |

| 21-15DDC Signal DC Specification (DCC_DATA, DDC_CLK)                                | .233  |

| 21-16DDC Miscellaneous Signal DC Specification (HPD, BKLTCTL, VDDEN, BKLTEN)        | .233  |

| 21-17MIPI*-HS-RX/MIPI*-LP-RX Minimum, Nominal, and Maximum Voltage Parameters       | .235  |

| 21-18SDIO DC Specification                                                          | .235  |

| 21-19SD Card DC Specification                                                       |       |

| 21-20eMMC* 4.51 DC Electrical Specifications                                        |       |

| 21-21JTAG Signal Group DC Specification (JTAG_TCK, JTAG_TMS, JTAG_TDI, JTAG_TRST_N) | .237  |

| 21-22JTAG Signal Group DC Specification (JTAG_TDO)                                  | .237  |

| 21-23JTAG Signal Group DC Specification (JTAG_PRDY#, JTAG_PREQ#)                    | .237  |

| 21-24DDR3L Signal Group DC Specifications                                           |       |

| 21-25USB 2.0 Host DC Specification                                                  | .238  |

| 21-26USB HSIC DC Electrical Specification                                           |       |

| 21-27USB 3.0 DC Specification                                                       |       |

| 21-28LPC 1.8V Signal Group DC Specification                                         |       |

| 21-29LPC 3.3V Signal Group DC Specification                                         |       |

| 21-30 PCU SPI DC Specification                                                      |       |

| 21-31Power Management 1.8V Suspend Well Signal Group DC Specification               |       |

| 21-32PMC_RSTBTN# 1.8V Core Well Signal Group DC Specification                       |       |

| 21-33Power Management and RTC Well Signal Group DC Specification                    |       |

| 21-34RTC Well DC Specification                                                      |       |

| 21-35PROCHOT# Signal Group DC Specification                                         |       |

| 21-36SVID Signal Group DC Specification (SVID_DATA, SVID_CLK, SVID_ALERT_N)         |       |

| 21-37GPIO 1.8V Core Well Signal Group DC Specification                              |       |

| 21-38SIO SPI DC Specifications                                                      |       |

| 21-39I <sup>2</sup> C Signal Electrical Specifications                              |       |

| 21-40HD Audio DC Specifications for 1.5V                                            |       |

| 21-41HD Audio DC Specification for 1.8V                                             |       |

| 21-42SMBus DC Specification                                                         |       |

| 21-43 PCI Express DC Receiver Signal Characteristics                                |       |

| 21-44 PCI Express DC Transmit Signal Characteristics                                |       |

| 21-45 PCI Express DC Clock Request Input Signal Characteristics                     | .247  |

# **Revision History**

| Revision<br>Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Revision Date |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 001                | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | April 2015    |

| 002                | Minor updates throughout for clarity Chapter 1: Introduction Added information on J-series Intel® Pentium® Processors and Intel® Celeron® Processors Updated Section 1.3. Removed support for HS400 in the Storage Interface section of the table Chapter 5: Power Sequence Added information on SUSPWRDNACK usage Chapter 6, Thermal Management Updated Section 5.3. Added note. Chapter 21: Electrical Specifications Table 21-3. Updated table title to reflect stepping (C-step). Updated S3, S4 and S5 Imax values for VNN Table 21-3. Updated Notes section Table 21-4. Added SoC power rail and max current specifications for D-step | February 2016 |

# 1 Introduction

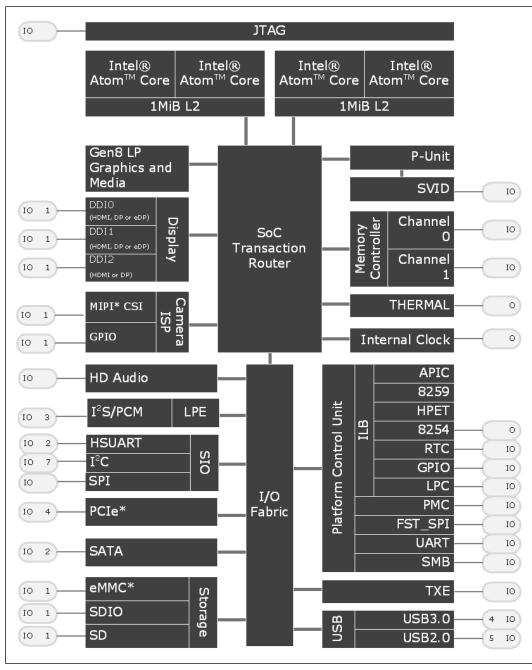

The N-series Intel<sup>®</sup> Pentium<sup>®</sup> processor and Intel<sup>®</sup> Celeron<sup>®</sup> processor families are the Intel Architecture (IA) SoC that integrates the next generation Intel<sup>®</sup> processor core, Graphics, Memory Controller, and I/O interfaces into a single system-on-chip solution.

The following figure shows the system-level block diagram of the SoC. Refer to the subsequent chapters for detailed information on the functionality of the different interface blocks.

This document is distributed as a part of the complete Datasheet document consisting of three volumes. Refer to Section 1.1, "Document Structure and Scope" on page 19 for high-level content listings of each volume.

Throughout this document, the N-series  $Intel^{\circledR}$  Pentium $^{\circledR}$  processor and  $Intel^{\circledR}$  Celeron $^{\circledR}$  processor families may be referred to simply as "processor".

Throughout this document, the N-series Intel<sup>®</sup> Pentium<sup>®</sup> processor and Intel<sup>®</sup> Celeron<sup>®</sup> processor families refers to the Intel<sup>®</sup> Pentium<sup>®</sup> processor N3710, N3700 and Intel<sup>®</sup> Celeron<sup>®</sup> processors N3160, N3150, N3060, N3050, N3010, and N3000. The J-series Intel<sup>®</sup> Pentium<sup>®</sup> processor and Intel<sup>®</sup> Celeron<sup>®</sup> processor families refers to the Intel<sup>®</sup> Pentium<sup>®</sup> processor J3710 and Intel<sup>®</sup> Celeron<sup>®</sup> processors J3160 and J3060.

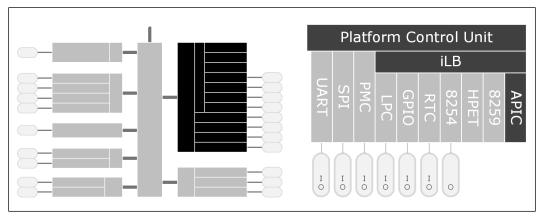

Figure 1-1. SoC Block Diagram (Netbook)

# 1.1 Document Structure and Scope

The following table summarizes the structure and scope of each volume of the processor Datasheet. Refer to the "Related Documents" section for order information.

#### **Table 1-1.** Structure of the Processor Datasheet (Sheet 1 of 2)

| Description                                                                      |  |  |  |  |

|----------------------------------------------------------------------------------|--|--|--|--|

| Volume 1: Architecture, Ballout, Package, and Electrical Specifications          |  |  |  |  |

| Introduction                                                                     |  |  |  |  |

| Physical Interfaces                                                              |  |  |  |  |

| Processor Core                                                                   |  |  |  |  |

| Integrated Clock                                                                 |  |  |  |  |

| Thermal Management                                                               |  |  |  |  |

| Power Management                                                                 |  |  |  |  |

| System Memory Controller                                                         |  |  |  |  |

| Graphics, Video, and Display                                                     |  |  |  |  |

| MIPI*-CSI (Camera Serial Interface) and ISP                                      |  |  |  |  |

| SoC Storage                                                                      |  |  |  |  |

| USB Controller Interfaces                                                        |  |  |  |  |

| Low Power Engine (LPE) for Audio (I <sup>2</sup> S)                              |  |  |  |  |

| Intel <sup>®</sup> Trusted Execution Engine (Intel <sup>®</sup> TXE)             |  |  |  |  |

| Intel <sup>®</sup> High Definition Audio (Intel <sup>®</sup> HD Audio)           |  |  |  |  |

| Serial I/O (SIO) Overview                                                        |  |  |  |  |

| Platform Controller Unit (PCU) Overview                                          |  |  |  |  |

| Serial ATA (SATA)                                                                |  |  |  |  |

| PCI Express* 2.0                                                                 |  |  |  |  |

| Ball Map, Ball Out, and SoC Pin Locations                                        |  |  |  |  |

| Package Information                                                              |  |  |  |  |

| Electrical Specifications                                                        |  |  |  |  |

| Volume 2: Registers                                                              |  |  |  |  |

| Register Access Method Registers                                                 |  |  |  |  |

| Mapping Address Space Registers                                                  |  |  |  |  |

| System Memory Controller Registers                                               |  |  |  |  |

| SoC Transaction Router Registers                                                 |  |  |  |  |

| Graphics, Video, and Display Registers                                           |  |  |  |  |

| MIPI*-CSI (Camera Serial Interface) and ISP Registers                            |  |  |  |  |

| SoC Storage Registers                                                            |  |  |  |  |

| USB xHCI PCI Configuration Registers                                             |  |  |  |  |

| Volume 3: Registers                                                              |  |  |  |  |

| Low Power Engine (LPE) for Audio (I2S) Registers                                 |  |  |  |  |

| Intel <sup>®</sup> High Definition Audio (Intel <sup>®</sup> HD Audio) Registers |  |  |  |  |

• Serial I/O (SIO) Registers

## Table 1-1. Structure of the Processor Datasheet (Sheet 2 of 2)

|                                          | Description |

|------------------------------------------|-------------|

| Platform Controller Unit (PCU) Registers |             |

| Serial ATA (SATA) Registers              |             |

| PCI Express* 2.0 Registers               |             |

# 1.2 Terminology

| Term                   | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AHCI                   | Advanced Host Controller Interface                                                                                                                                                                                                                                                                                                                                                                  |

| ACPI                   | Advanced Configuration and Power Interface                                                                                                                                                                                                                                                                                                                                                          |

| CCm                    | Closely Coupled Memory                                                                                                                                                                                                                                                                                                                                                                              |

| CCI                    | Camera Control Interface                                                                                                                                                                                                                                                                                                                                                                            |

| Cold Reset             | Full reset is when PWROK is de-asserted and all system rails except VCCRTC are powered down                                                                                                                                                                                                                                                                                                         |

| CRU                    | Clock Reset Unit                                                                                                                                                                                                                                                                                                                                                                                    |

| CSI                    | Camera Serial Interface                                                                                                                                                                                                                                                                                                                                                                             |

| DP                     | DisplayPort*                                                                                                                                                                                                                                                                                                                                                                                        |

| DTS                    | Digital Thermal Sensor                                                                                                                                                                                                                                                                                                                                                                              |

| EIOB                   | Electronic In/Out Board                                                                                                                                                                                                                                                                                                                                                                             |

| EMI                    | Electro Magnetic Interference                                                                                                                                                                                                                                                                                                                                                                       |

| eDP                    | embedded DisplayPort*                                                                                                                                                                                                                                                                                                                                                                               |

| GPIO                   | General Purpose IO                                                                                                                                                                                                                                                                                                                                                                                  |

| HDCP                   | High-Bandwidth Digital Content Protection                                                                                                                                                                                                                                                                                                                                                           |

| НДМІ                   | High Definition Multimedia Interface. HDMI supports standard, enhanced, or high-definition video, plus multi-channel digital audio on a single cable. HDMI transmits all Advanced Television Systems Committee (ATSC) HDTV standards and supports 8-channel digital audio, with bandwidth to spare for future requirements and enhancements (additional details available at http://www.hdmi.org/). |

| HPET                   | High Precision Event Timer                                                                                                                                                                                                                                                                                                                                                                          |

| IGD                    | Internal Graphics Unit                                                                                                                                                                                                                                                                                                                                                                              |

| Intel <sup>®</sup> TXE | Intel® Trusted Execution Engine (Intel® TXE)                                                                                                                                                                                                                                                                                                                                                        |

| IPC                    | Inter-Processor Communication                                                                                                                                                                                                                                                                                                                                                                       |