# **5G LDPC Intel® FPGA IP User Guide**

Updated for Intel® Quartus® Prime Design Suite: **21.1**

IP Version: 21.1.0

Version: **2021.03.29**

ID: 683107

UG-20057

# **Contents**

| 1. About the 5G LDPC Intel® FPGA IP                                       | 3  |

|---------------------------------------------------------------------------|----|

| 1.1. 5G LDPC Intel FPGA IP Features                                       |    |

| 1.2. 5G LDPC Intel FPGA IP Device Family Support                          |    |

| 1.3. 5G LDPC IP Release Information                                       |    |

|                                                                           |    |

| 2. Getting Started with the 5G LDPC Intel FPGA IP                         |    |

| 2.1. Installing and Licensing Intel FPGA IP Cores                         |    |

| 2.1.1. Intel FPGA IP Evaluation Mode                                      |    |

| 2.1.2. 5G LDPC IP IP Timeout Behavior                                     |    |

| 3. Designing with the 5G LDPC Intel FPGA IP                               |    |

| 3.1. Generating a 5G LDPC Intel FPGA IP                                   |    |

| 3.2. Simulating the 5G LDPC IP RTL                                        |    |

| 3.3. 5G LDPC Simulation Results                                           |    |

| 4. 5G LDPC Intel FPGA IP Functional Description                           |    |

| 4.1. 5G LDPC Decoder                                                      |    |

| 4.1.1. 5G LDPC Decoder Signals                                            |    |

| 4.1.2. 5G LDPC Decoder Data Formats                                       |    |

| 4.2. 5G LDPC Ir Decoder Parameters                                        |    |

| 4.2.1. 5G LDPC Encoder Signals                                            |    |

| 4.2.2. 5G LDPC Encoder Data Formats                                       | 29 |

| 4.3. Avalon Streaming Interfaces in DSP Intel FPGA IP                     | 31 |

| 5. Parameter Optimization for the 5G LDPC IP                              | 33 |

| 5.1. C++ and MATLAB Software Models                                       |    |

| 5.1.1. Running the 5G LDPC IP C++ Models                                  | 36 |

| 5.1.2. Running the 5G LDPC Decoder and Encoder MATLAB Model in the Design |    |

| Example                                                                   | 37 |

| 6. 5G LDPC IP User Guide Document Archive                                 | 38 |

| 7 Document Revision History for the 5G I DPC Intel FDGA ID User Guide     | 30 |

# 1. About the 5G LDPC Intel® FPGA IP

Low-density parity-check (LDPC) codes are linear error correcting codes that help you to transmit and receive messages over noisy channels. The 5G LDPC Intel® FPGA IP implements LDPC codes compliant with the 3rd Generation Partnership Project (3GPP) 5G specification for integration in your wireless design.

LDPC codes replace Turbo codes, popular in 3G and 4G wireless cellular communications. LDPC codes offer better spectral efficiency and support the high throughput for 5G new radio (NR).

#### **Related Information**

- Introduction to Intel FPGA IP Cores

- Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Qsys Simulation Scripts Create simulation scripts that do not require manual updates for software or IP version upgrades.

- **Project Management Best Practices** Guidelines for efficient management and portability of your project and IP files.

- 3GPP New Radio Specification

The final equivalents are Release 15, 3GPP Technical Specification Group RAN 1, NR:

- (1) Multiplexing and channel coding, 3GPP TS 38.212 (v15.3.0)

- (2) Physical layer procedures for data, 3GPP TS 38.214 (v15.3.0)

## 1.1. 5G LDPC Intel FPGA IP Features

The 5G LDPC IP offers the following features:

- 3GPP 5G LDPC specification compliant

- For the decoder:

- Improved block error rate (BLER) performance

- Improved power efficiency of IP

- Per-block modifiable code block length, code rate, base graph, and maximum number of iterations

- Configurable input precision

- Layered decoder scheduling architecture to double the speed of convergence compared to non-layered architecture

- Early termination based on syndrome check on each iteration

- Single or dual decoders

- For the encoder: per-block modifiable code block length and code rate

- No external memory requirement

- MATLAB and C++ models for performance simulation and RTL test vector generation

- Verilog HDL testbench option

- Avalon®streaming input and output interfaces

#### **Related Information**

- 3GPP New Radio LDPC Specification

- Avalon Streaming Interface Specifications

# 1.2. 5G LDPC Intel FPGA IP Device Family Support

Intel offers the following device support levels for Intel FPGA IP:

- Advance support—the IP is available for simulation and compilation for this device family. FPGA programming file (.pof) support is not available for Quartus Prime Pro Stratix 10 Edition Beta software and as such IP timing closure cannot be guaranteed. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP core for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O standards tradeoffs).

- Preliminary support—Intel verifies the IP core with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. You can use it in production designs with caution.

- Final support—Intel verifies the IP with final timing models for this device family. The IP meets all functional and timing requirements for the device family. You can use it in production designs.

Table 1. 5G LDPC IP Device Family Support

| Device Family                 | Support    |

|-------------------------------|------------|

| Intel Agilex <sup>™</sup>     | Advance    |

| Intel Arria® 10               | Final      |

| Intel Stratix <sup>®</sup> 10 | Final      |

| Other device families         | No support |

# 1.3. 5G LDPC IP Release Information

#### **Table 2.** Release Information

| Item          | Description |

|---------------|-------------|

| Version       | 21.1.0      |

| Release Date  | 2021.05.04  |

| Ordering Code | IP-5G-LDPC  |

Intel verifies that the current version of the Intel Quartus<sup>®</sup> Prime software compiles the previous public version of each IP. Intel does not verify that the Intel Quartus Prime software compiles IP versions older than the previous version. The *Intel FPGA IP Release Notes* lists any exceptions.

#### **Related Information**

Intel FPGA IP Release Notes

## 1.4. 5G LDPC IP Performance and Resource Utilization

Intel generated the resource utilization and performance for the encoder and the decoder by compiling the designs with Intel Quartus Prime software v21.1. Only use these approximate results for early estimation of FPGA resources (e.g. adaptive logic modules (ALMs)) that a project requires.

#### **Decoder**

## Table 3. Resource Utilization and Maximum Frequency for Intel Agilex Devices

Targeting AGFB014R24B2I2V device. The  $f_{MAX}$  is the five-seeds average  $f_{MAX}$  reduced 15% for margins.

| IN_WIDTH | NUM_DECODER | MAX_LF_DECODER0 | MAX_LF_DECODER1 | ALMs   | M20K Memory<br>Blocks | f <sub>MAX</sub> (MHz) |

|----------|-------------|-----------------|-----------------|--------|-----------------------|------------------------|

| 6        | 1           | 384             | -               | 58,720 | 762                   | 548                    |

| 6        | 1           | 192             | -               | 30,082 | 402                   | 572                    |

| 6        | 1           | 128             | -               | 19,898 | 281                   | 574                    |

| 6        | 1           | 96              | -               | 15,604 | 221                   | 574                    |

| 6        | 2           | -               | 192             | 88,696 | 1165                  | 556                    |

| 6        | 2           | -               | 128             | 78,828 | 1044                  | 549                    |

| 6        | 2           | -               | 96              | 74,520 | 984                   | 550                    |

| 5        | 1           | 384             | -               | 53,588 | 677                   | 561                    |

|          |             |                 |                 |        | C                     | ontinued               |

| IN_WIDTH | NUM_DECODER | MAX_LF_DECODER0 | MAX_LF_DECODER1 | ALMs   | M20K Memory<br>Blocks | f <sub>MAX</sub> (MHz) |

|----------|-------------|-----------------|-----------------|--------|-----------------------|------------------------|

| 5        | 1           | 192             | -               | 27,420 | 367                   | 572                    |

| 5        | 1           | 128             | -               | 18,314 | 258                   | 577                    |

| 5        | 1           | 96              | -               | 14,134 | 203                   | 576                    |

| 5        | 2           | -               | 192             | 80,494 | 1045                  | 555                    |

| 5        | 2           | -               | 128             | 71,751 | 936                   | 541                    |

| 5        | 2           | -               | 96              | 67,565 | 881                   | 547                    |

Table 4. Resource Utilization and Maximum Frequency for Intel Arria 10 Devices Targeting 10AT115S1F45E1SG device. The  $f_{MAX}$  is the five-seeds average  $f_{MAX}$  reduced 15% for margins.

| NUM_DECODER | MAX_LF_DECODER0           | MAX_LF_DECODER1                                                                                                                                                                                                                                                                     | ALMs                                                                                                                                                                                                                                                                                                                                                             | M20K Memory<br>Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | f <sub>MAX</sub> (MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | 384                       | -                                                                                                                                                                                                                                                                                   | 47,261                                                                                                                                                                                                                                                                                                                                                           | 762                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 306                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1           | 192                       | -                                                                                                                                                                                                                                                                                   | 24,698                                                                                                                                                                                                                                                                                                                                                           | 402                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1           | 128                       | -                                                                                                                                                                                                                                                                                   | 17,015                                                                                                                                                                                                                                                                                                                                                           | 281                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 348                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1           | 96                        | -                                                                                                                                                                                                                                                                                   | 13,381                                                                                                                                                                                                                                                                                                                                                           | 221                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 360                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2           | -                         | 192                                                                                                                                                                                                                                                                                 | 72,690                                                                                                                                                                                                                                                                                                                                                           | 1165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 290                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2           | -                         | 128                                                                                                                                                                                                                                                                                 | 64,925                                                                                                                                                                                                                                                                                                                                                           | 1044                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 294                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2           | -                         | 96                                                                                                                                                                                                                                                                                  | 61,238                                                                                                                                                                                                                                                                                                                                                           | 984                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 296                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1           | 384                       | -                                                                                                                                                                                                                                                                                   | 41,906                                                                                                                                                                                                                                                                                                                                                           | 677                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 312                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1           | 192                       | -                                                                                                                                                                                                                                                                                   | 21,654                                                                                                                                                                                                                                                                                                                                                           | 367                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 339                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1           | 128                       | -                                                                                                                                                                                                                                                                                   | 15,036                                                                                                                                                                                                                                                                                                                                                           | 258                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 353                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1           | 96                        | -                                                                                                                                                                                                                                                                                   | 11,842                                                                                                                                                                                                                                                                                                                                                           | 203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 353                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2           | -                         | 192                                                                                                                                                                                                                                                                                 | 63,292                                                                                                                                                                                                                                                                                                                                                           | 1045                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 305                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2           | -                         | 128                                                                                                                                                                                                                                                                                 | 56,714                                                                                                                                                                                                                                                                                                                                                           | 936                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 313                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2           | -                         | 96                                                                                                                                                                                                                                                                                  | 53,658                                                                                                                                                                                                                                                                                                                                                           | 881                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 318                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 1 1 1 1 2 2 2 1 1 1 1 2 2 | 1       384         1       192         1       128         1       96         2       -         2       -         1       384         1       192         1       128         1       96         2       -         2       -         2       -         2       -         2       - | 1       384       -         1       192       -         1       128       -         1       96       -         2       -       192         2       -       128         2       -       96         1       192       -         1       128       -         1       96       -         2       -       192         2       -       192         2       -       128 | 1       384       -       47,261         1       192       -       24,698         1       128       -       17,015         1       96       -       13,381         2       -       192       72,690         2       -       128       64,925         2       -       96       61,238         1       384       -       41,906         1       192       -       21,654         1       128       -       15,036         1       96       -       11,842         2       -       192       63,292         2       -       128       56,714 | Blocks         1       384       -       47,261       762         1       192       -       24,698       402         1       128       -       17,015       281         1       96       -       13,381       221         2       -       192       72,690       1165         2       -       128       64,925       1044         2       -       96       61,238       984         1       384       -       41,906       677         1       192       -       21,654       367         1       128       -       15,036       258         1       96       -       11,842       203         2       -       192       63,292       1045         2       -       128       56,714       936 |

Table 5. Resource Utilization and Maximum Frequency for Intel Stratix 10 Devices

Targeting 1SG280HU2F50E2VG device. The f<sub>MAX</sub> is the five-seeds average f<sub>MAX</sub> reduced 15% for margins.

| IN_WIDTH | NUM_DECODER | MAX_LF_DECODER0 | MAX_LF_DECODER1 | ALMs   | M20K Memory<br>Blocks | f <sub>MAX</sub> (MHz) |  |

|----------|-------------|-----------------|-----------------|--------|-----------------------|------------------------|--|

| 6        | 1           | 384             | -               | 62,090 | 762                   | 384                    |  |

| 6        | 1           | 192             | -               | 31,889 | 402                   | 413                    |  |

| 6        | 1           | 128             | -               | 21,772 | 281                   | 409                    |  |

| 6        | 1           | 96              | -               | 16,838 | 221                   | 419                    |  |

| 6        | 2           | -               | 192             | 93,439 | 1165                  | 365                    |  |

| 6        | 2           | -               | 128             | 83,526 | 1044                  | 365                    |  |

| 6        | 2           | -               | 96              | 79,157 | 984                   | 374                    |  |

| 5        | 1           | 384             | -               | 56,806 | 677                   | 369                    |  |

|          | continued   |                 |                 |        |                       |                        |  |

| IN_WIDTH | NUM_DECODER | MAX_LF_DECODER0 | MAX_LF_DECODER1 | ALMs   | M20K Memory<br>Blocks | f <sub>MAX</sub> (MHz) |

|----------|-------------|-----------------|-----------------|--------|-----------------------|------------------------|

| 5        | 1           | 192             | -               | 29,469 | 367                   | 412                    |

| 5        | 1           | 128             | -               | 20,063 | 258                   | 411                    |

| 5        | 1           | 96              | -               | 15,690 | 203                   | 433                    |

| 5        | 2           | -               | 192             | 84,685 | 1045                  | 378                    |

| 5        | 2           | -               | 128             | 75,905 | 936                   | 383                    |

| 5        | 2           | -               | 96              | 71,549 | 881                   | 373                    |

Table 6.

Resource Utilization and Maximum Frequency for Intel Stratix 10-L Devices

Targeting 1SG280HU2F50E2LG device. The  $f_{\text{MAX}}$  is the five-seeds average  $f_{\text{MAX}}$  reduced 15% for margins.

| IN_WIDTH | NUM_DECODER | MAX_LF_DECODER0 | MAX_LF_DECODER1 | ALMs   | M20K Memory<br>Blocks | f <sub>MAX</sub> (MHz) |

|----------|-------------|-----------------|-----------------|--------|-----------------------|------------------------|

| 6        | 1           | 384             | -               | 62,297 | 762                   | 379                    |

| 6        | 1           | 192             | -               | 31,849 | 402                   | 394                    |

| 6        | 1           | 128             | -               | 21,715 | 281                   | 403                    |

| 6        | 1           | 96              | -               | 16,812 | 221                   | 405                    |

| 6        | 2           | -               | 192             | 93,144 | 1165                  | 359                    |

| 6        | 2           | -               | 128             | 83,298 | 1044                  | 360                    |

| 6        | 2           | -               | 96              | 78,968 | 984                   | 368                    |

| 5        | 1           | 384             | -               | 56,768 | 677                   | 378                    |

| 5        | 1           | 192             | -               | 28,754 | 367                   | 403                    |

| 5        | 1           | 128             | -               | 20,038 | 258                   | 401                    |

| 5        | 1           | 96              | -               | 15,684 | 203                   | 399                    |

| 5        | 2           | -               | 192             | 85,326 | 1045                  | 367                    |

| 5        | 2           | -               | 128             | 76,386 | 936                   | 381                    |

| 5        | 2           | -               | 96              | 71,937 | 881                   | 367                    |

# **Encoder**

Intel generated the data for the following devices:

- Intel Agilex AGFA014R24A2E2VR0

- Intel Arria 10 10AT115S1F45E1SG

- Intel Stratix 10 1SG280HU2F50E2VG

- Intel Stratix 10-L 1SG280HU2F50E2LG

# **Table 7.** Resource Utilization and Maximum Frequency

The  $f_{\text{MAX}}$  is the five-seeds average  $f_{\text{MAX}}$  reduced 15% for margins.

| Device           | ALMs   | M20K Memory Blocks | f <sub>MAX</sub> (MHz) |

|------------------|--------|--------------------|------------------------|

| AGFB014R24B2I2V  | 17,629 | 23                 | 554                    |

| 10AT115S1F45E1SG | 16,876 | 23                 | 323                    |

| 1SG280HU2F50E2VG | 17,617 | 23                 | 442                    |

| 1SG280HU2F50E2LG | 17,585 | 23                 | 382                    |

# 2. Getting Started with the 5G LDPC Intel FPGA IP

#### **Related Information**

- Introduction to Intel FPGA IP

- IP Catalog and Parameter Editor

The IP Catalog displays the IP available for your project.

- Generating Intel FPGA IP

Quickly configure Intel FPGA IP cores in the Intel Quartus Prime parameter editor. Double-click any component in the IP Catalog to launch the parameter editor. The parameter editor allows you to define a custom variation of the IP core. The parameter editor generates the IP variation synthesis and optional simulation files, and adds the .ip file representing the variation to your project automatically.

# 2.1. Installing and Licensing Intel FPGA IP Cores

The Intel Quartus Prime software installation includes the Intel FPGA IP library. This library provides many useful IP cores for your production use without the need for an additional license. Some Intel FPGA IP cores require purchase of a separate license for production use. The Intel FPGA IP Evaluation Mode allows you to evaluate these licensed Intel FPGA IP cores in simulation and hardware, before deciding to purchase a full production IP core license. You only need to purchase a full production license for licensed Intel IP cores after you complete hardware testing and are ready to use the IP in production.

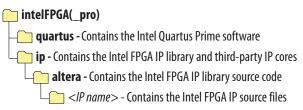

The Intel Quartus Prime software installs IP cores in the following locations by default:

## Figure 1. IP Core Installation Path

| Table 8. | IP Core I | installation I | ocations |

|----------|-----------|----------------|----------|

|          |           |                |          |

| Location                                                               | Software                                | Platform |

|------------------------------------------------------------------------|-----------------------------------------|----------|

| <pre><drive>:\intelFPGA_pro\quartus\ip\altera</drive></pre>            | Intel Quartus Prime Pro Edition         | Windows* |

| <pre><drive>:\intelFPGA\quartus\ip\altera</drive></pre>                | Intel Quartus Prime Standard<br>Edition | Windows  |

| <pre><home directory="">:/intelFPGA_pro/quartus/ip/altera</home></pre> | Intel Quartus Prime Pro Edition         | Linux*   |

| <pre><home directory="">:/intelFPGA/quartus/ip/altera</home></pre>     | Intel Quartus Prime Standard<br>Edition | Linux    |

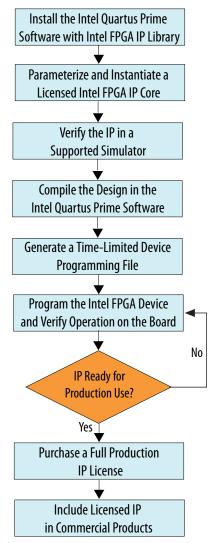

#### 2.1.1. Intel FPGA IP Evaluation Mode

The free Intel FPGA IP Evaluation Mode allows you to evaluate licensed Intel FPGA IP cores in simulation and hardware before purchase. Intel FPGA IP Evaluation Mode supports the following evaluations without additional license:

- Simulate the behavior of a licensed Intel FPGA IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

Intel FPGA IP Evaluation Mode supports the following operation modes:

- **Tethered**—Allows running the design containing the licensed Intel FPGA IP indefinitely with a connection between your board and the host computer. Tethered mode requires a serial joint test action group (JTAG) cable connected between the JTAG port on your board and the host computer, which is running the Intel Quartus Prime Programmer for the duration of the hardware evaluation period. The Programmer only requires a minimum installation of the Intel Quartus Prime software, and requires no Intel Quartus Prime license. The host computer controls the evaluation time by sending a periodic signal to the device via the JTAG port. If all licensed IP cores in the design support tethered mode, the evaluation time runs until any IP core evaluation expires. If all of the IP cores support unlimited evaluation time, the device does not time-out.

- **Untethered**—Allows running the design containing the licensed IP for a limited time. The IP core reverts to untethered mode if the device disconnects from the host computer running the Intel Quartus Prime software. The IP core also reverts to untethered mode if any other licensed IP core in the design does not support tethered mode.

When the evaluation time expires for any licensed Intel FPGA IP in the design, the design stops functioning. All IP cores that use the Intel FPGA IP Evaluation Mode time out simultaneously when any IP core in the design times out. When the evaluation time expires, you must reprogram the FPGA device before continuing hardware verification. To extend use of the IP core for production, purchase a full production license for the IP core.

You must purchase the license and generate a full production license key before you can generate an unrestricted device programming file. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (croject name> time limited.sof) that expires at the time limit.

Figure 2. Intel FPGA IP Evaluation Mode Flow

Note: Refer to each IP core's user guide for parameterization steps and implementation details.

Intel licenses IP cores on a per-seat, perpetual basis. The license fee includes first-year maintenance and support. You must renew the maintenance contract to receive updates, bug fixes, and technical support beyond the first year. You must purchase a full production license for Intel FPGA IP cores that require a production license, before generating programming files that you may use for an unlimited time. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (project name>\_time\_limited.sof) that expires at the time limit. To obtain your production license keys, visit the Self-Service Licensing Center.

The Intel FPGA Software License Agreements govern the installation and use of licensed IP cores, the Intel Quartus Prime design software, and all unlicensed IP cores.

#### **Related Information**

- Intel FPGA Licensing Support Center

- Introduction to Intel FPGA Software Installation and Licensing

### 2.1.2. 5G LDPC IP IP Timeout Behavior

All IP in a device time out simultaneously when the most restrictive evaluation time is reached. If a design has more than one IP, the time-out behavior of the other IP may mask the time-out behavior of a specific IP .

For IP, the untethered time-out is 1 hour; the tethered time-out value is indefinite. Your design stops working after the hardware evaluation time expires. The Quartus Prime software uses Intel FPGA IP Evaluation Mode Files (.ocp) in your project directory to identify your use of the Intel FPGA IP Evaluation Mode evaluation program. After you activate the feature, do not delete these files.

When the evaluation time expires, for the encoders cw goes low and rst\_n goes low; for decoders source\_data goes low, reset\_n goes low.

#### **Related Information**

AN 320: OpenCore Plus Evaluation of Megafunctions

# 3. Designing with the 5G LDPC Intel FPGA IP

# 3.1. Generating a 5G LDPC Intel FPGA IP

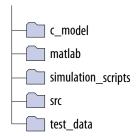

To include the IP in a design, generate the IP in the Intel Quartus Prime software. Or optionally, you can generate a design example that includes the generated 5G LDPC IP, a C++ model, a MATLAB model, simulation scripts, and test data.

- 1. Create a New Intel Quartus Prime project

- 2. Open IP Catalog.

- Select DSP ➤ Error Detection and Correction ➤ 5G LDPC Intel FPGA IP and click Add

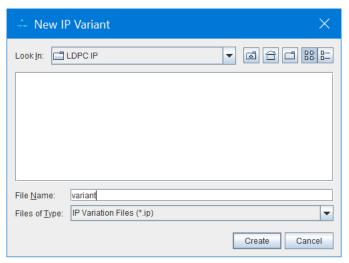

- 4. Enter a name for your IP variant and click **Create**.

Figure 3. IP Variant File Name

The name is for both the top-level RTL module and the corresponding .ip file. The parameter editor for this IP appears.

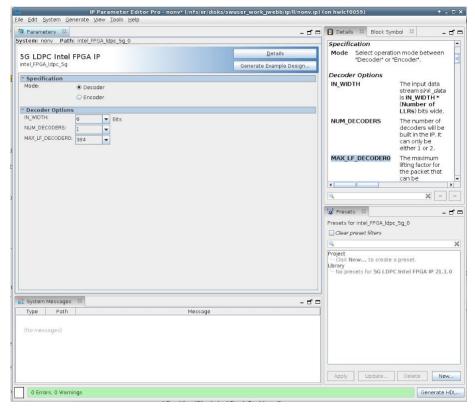

5. Choose your parameters.

You can choose **Encoder** or **Decoder** and select decoder parameters.

Figure 4. 5G LDPC Parameter Editor

6. For an optional design example, click **Generate Example Design**. The software creates files for MATLAB, C, or RTL simulations in the target directory. The software does not generate a hardware example.

Figure 5. Design Example Directory Structure

### 7. Click Generate HDL.

Intel Quartus Prime generates the RTL and the files necessary to instantiate the IP in your design and synthesize it.

## **Related Information**

5G LDPC IP Decoder Parameters on page 27

# 3.2. Simulating the 5G LDPC IP RTL

Verify that the RTL behaves the same as these models.

Before simulating, generate a 5G LDPC design example.

- 1. For Synopsys VCS, in the directory /simulation scripts/synopsys/vcsmx:

- a. Execute source vcsmx\_setup.sh.

After the compilation finishes, it will run the simulation and finish in 100 ps as the default set in the vcsmx\_setup.sh.

- b. Execute ./simv VCS starts to simulate. At the end of the simulation, a script compares the decoder output with the expected output (decoder only) and you see Simulation passed.

- 2. For Mentor ModelSim, in the directory /simulation\_scripts/mentor:

- a. Execute vsim.

- b. In the GUI, execute source msim\_setup.tcl.

- c. Execute 1d to compile the Intel Quartus Prime simulation library, IP design, and testbench files

- d. Execute run -all to start the simulation.

At the end of the simulation, a script compares the decoder output with the expected output (decoder only) and you see Simulation passed.

.

3. For Cadence NCSim, in the directory /simulation\_scripts/cadence, execute source ncsim\_setup.sh.

At the end of the simulation, a script compares the decoder output with the expected output (decoder only) and you see Simulation passed.

#### **Related Information**

- Running the 5G LDPC IP C++ Models on page 36

- Running the 5G LDPC Decoder and Encoder MATLAB Model in the Design Example on page 37

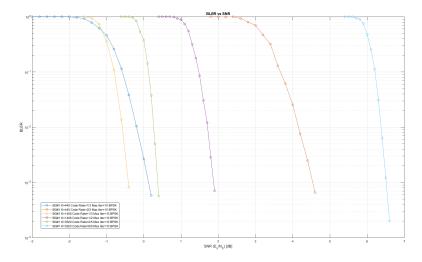

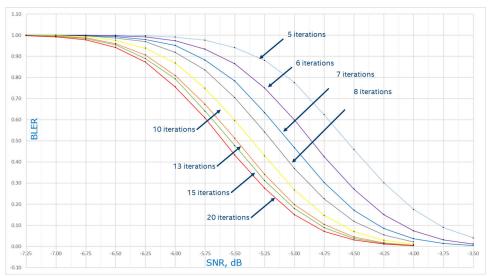

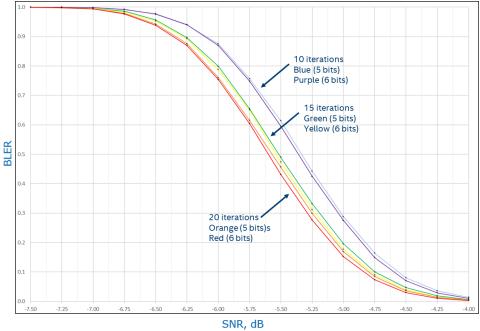

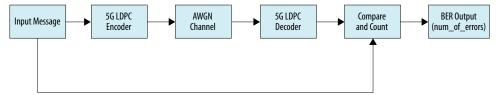

# 3.3. 5G LDPC Simulation Results

#### **Encoder Simulation Results**

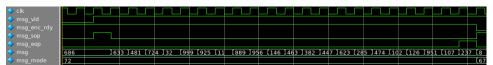

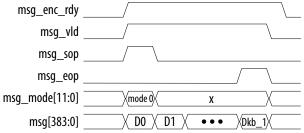

#### Figure 6. Input Message to the Encoder

Table 9. Decimal Interpretations of the Bit Groups in the Input Message to the Encoder

686 is the first word and 237 is the last word in the input message.

| msg_mode | msg_vld | msg | msg_sop | msg_eop |

|----------|---------|-----|---------|---------|

| 72       | HIGH    | 686 | HIGH    | LOW     |

| 72       | HIGH    | 633 | LOW     | LOW     |

| 72       | HIGH    | 481 | LOW     | LOW     |

| 72       | HIGH    | 724 | LOW     | LOW     |

| 72       | HIGH    | 32  | LOW     | LOW     |

| 72       | HIGH    | 999 | LOW     | LOW     |

| 72       | HIGH    | 925 | LOW     | LOW     |

| 72       | HIGH    | 11  | LOW     | LOW     |

| 72       | HIGH    | 899 | LOW     | LOW     |

| 72       | HIGH    | 956 | LOW     | LOW     |

| 72       | HIGH    | 146 | LOW     | LOW     |

| 72       | HIGH    | 463 | LOW     | LOW     |

| 72       | HIGH    | 382 | LOW     | LOW     |

| 72       | HIGH    | 447 | LOW     | LOW     |

| 72       | HIGH    | 623 | LOW     | LOW     |

| 72       | HIGH    | 285 | LOW     | LOW     |

| 72       | HIGH    | 474 | LOW     | LOW     |

| 72       | HIGH    | 102 | LOW     | LOW     |

| 72       | HIGH    | 126 | LOW     | LOW     |

| 72       | HIGH    | 951 | LOW     | LOW     |

| 72       | HIGH    | 107 | LOW     | LOW     |

| 72       | HIGH    | 237 | LOW     | HIGH    |

| 67       | LOW     |     |         | LOW     |

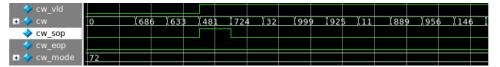

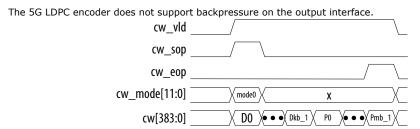

Figure 7. Data and Control Signals at the Start of the Encoder Codeword Output

## Table 10. Data and Control Signals at the Start of the Encoder Codeword Output

The codeword consists of the initial message with 2\*Z starting bits punctured out, and of a block of parity bits appended after the message. The table shows that the first two data words 686 and 633 are punctured out, by deasserting  $cw_vld$  and also by asserting the SOP signal. 481 is the first data word in the codeword.

| cw_vld | cw_mode | cw  | parity bits | cw_sop | cw_eop |

|--------|---------|-----|-------------|--------|--------|

| LOW    | 72      | 686 |             | LOW    | LOW    |

| LOW    | 72      | 633 |             | LOW    | LOW    |

| HIGH   | 72      | 481 |             | HIGH   | LOW    |

| HIGH   | 72      | 724 |             | LOW    | LOW    |

| HIGH   | 72      | 32  |             | LOW    | LOW    |

| HIGH   | 72      | 999 |             | LOW    | LOW    |

| HIGH   | 72      | 925 |             | LOW    | LOW    |

| HIGH   | 72      | 11  |             | LOW    | LOW    |

| HIGH   | 72      | 899 |             | LOW    | LOW    |

| HIGH   | 72      | 956 |             | LOW    | LOW    |

| HIGH   | 72      | 146 |             | LOW    | LOW    |

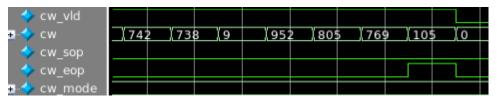

Figure 8. End of the Encoder Codeword Output

Table 11. Data and Control Signals at the End of the Encoder Codeword

| cw_vld | cw_mode    | cw         | parity bits | cw_sop | cw_eop |

|--------|------------|------------|-------------|--------|--------|

| HIGH   | 72         | 742        | parity      | LOW    | LOW    |

| HIGH   | 72         | 738        | Parity      | LOW    | LOW    |

| HIGH   | 72         | 9          | parity      | LOW    | LOW    |

| HIGH   | 72         | 952        | parity      | LOW    | LOW    |

| HIGH   | 72         | 805        | parity      | LOW    | LOW    |

| HIGH   | 72         | 769        | parity      | LOW    | LOW    |

| HIGH   | 72         | 105        | parity      | LOW    | HIGH   |

| LOW    | Don't care | Don't care | Don't care  | LOW    | LOW    |

#### **Decoder Simulation Results**

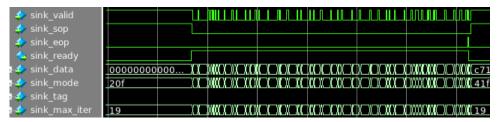

## Figure 9. Codeword LLR Array Input to the Decoder

- sink\_valid remains asserted for the duration of the LLR codeword while input data is valid. The upstream component can deassert it as needed.

- sink\_sop is asserted only for the first data block in. It gets stretched for more than one clock cycle by the backpressure from the decoder, because the decoder deasserts sink\_ready

- sink\_eop pulses high for one clock cycle on the last valid input data block. It also can be stretched by the backpressure from the decoder's sink.

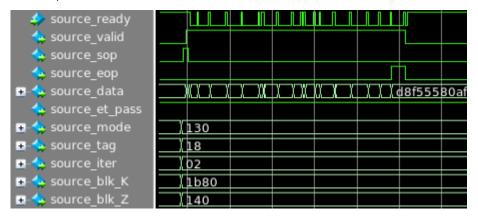

# Figure 10. Decoded Message Output from the Decoder

- source\_valid and source\_sop are asserted about the same time. source\_sop is asserted only for

the first message block out

- The decoder may assert source\_sop earlier and keep it high for a number of clock cycles only the data block output during the last clock cycle just before source\_sop is deasserted (and with source\_valid asserted) is the actual beginning of the message

- source\_valid remains asserted for the duration of the output message

- source\_sop may get stretched for more than one clock cycle by the backpressure from the testbench,

i.e. because the testbench deasserts source\_ready downstream

- sink\_eop is asserted for the last valid message block output. It also can be stretched by the backpressure from the sink downstream.

#### **Related Information**

C++ and MATLAB Software Models on page 35

# 4. 5G LDPC Intel FPGA IP Functional Description

The 5G LDPC Intel FPGA IP comprises an encoder and a decoder.

5G LDPC Decoder on page 19 5G LDPC Encoder on page 27 Avalon Streaming Interfaces in DSP Intel FPGA IP on page 31

# 4.1. 5G LDPC Decoder

The 5G LDPC Decoder supports all modes specified in the 3GPP New Radio specification. The decoder can be either a single decoder or dual decoders.

Input packets arbitration for dual decoders:

- If the incoming packet has small Z, the IP sends it to the second decoder, if it is available. If the second decoder is full and not available to process the small packet, the IP sends the small packet to the first decoder, if it is available. If none of the two decoders are available for the small packet, the IP back pressures to the upstream

- If the incoming packet has large Z, the IP sends it to the first decoder, if it is available. If the first decoder is full and not available to process this packet, the IP back pressures to the upstream. Even if the upstream has the subsequent packet that has small Z and the second decoder is available to process it, the packet doesn't arrive at the IP until the first decoder becomes available to process the previous big packet

The order of output decoded packets is in the order that the IP receives the packets, although the IP processes the packets out of order.

# 4.1.1. 5G LDPC Decoder Signals

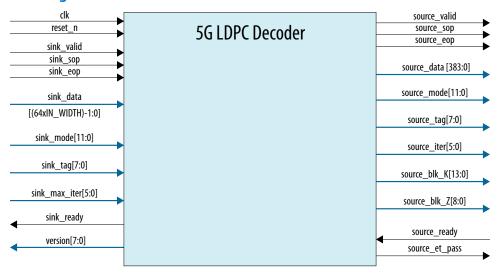

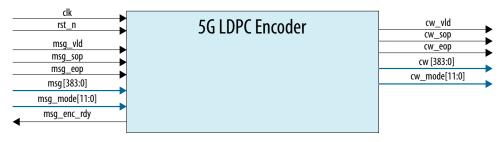

# Figure 11. Decoder Signals

# **Table 12.** Decoder Interface Signals

Signal names beginning with sink are in the input interface to the decoder IP; signal names beginning with source are in the output interface from the decoder IP (except for sink\_ready and source\_ready). Both interfaces comply with the Avalon-ST specification with readyLatency=0.

| Name         | Direction | Description                                                                                                                                              |

|--------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk          | Input     | Clocks the 5G LDPC decoder IP signals and internal transitions.                                                                                          |

| reset_n      | Input     | Active low, synchronous reset signal for 5G LDPC decoder. Asserting this signal for one clock cycle is sufficient to ensure the reset process initiates. |

| version[7:0] | Output    | Version number.For IP version 21.1.0, version = 0x0C).                                                                                                   |

| Name       | Direction | Description                                                                                                                                                                                                                                          |

|------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sink_valid | Input     | Qualifies the sink_data signal. When sink_valid is not asserted, the IP stops processing input until you reassert the sink_valid signal.                                                                                                             |

| sink_sop   | Input     | Marks the start of an incoming packet.                                                                                                                                                                                                               |

| sink_eop   | Input     | Marks the end of an incoming packet.                                                                                                                                                                                                                 |

| sink_ready | Output    | Indicates that the decoder is ready to receive data on the current clock cycle. The IP can backpressure incoming data by deasserting this signal.                                                                                                    |

|            |           | The readyLatency for this signal is 0: the IP can read valid input data in the same clock cycle in which it raises this signal. Refer to the <i>Avalon Interface Specifications</i> for the description of this Avalon streaming interface property. |

|            | 1         | continued                                                                                                                                                                                                                                            |

| Name                         | Direction | Description                                                                                                                                                                                                                                                                                        |

|------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sink_data[(64*IN_WIDTH)-1:0] | Input     | Data input. The IP processes this input only while it asserts sink_ready and you assert the sink_valid signal. The default value of <b>IN_WIDTH</b> is 6.                                                                                                                                          |

| sink_mode[11:0]              | Input     | Input block mode. The value specifies the lifting size, base graph, and code rate. Refer to Input and Output Block Mode Meaning in 5G LDPC Decoder Data Formats on page 23.  This signal must be valid for the current information block when the upstream source asserts sink_sop and sink_valid. |

| sink_tag[7:0]                | Input     | Block tag. An optional tag that accompanies the block from input to output. You can use this tag to identify the correspondence of the input and output block. This signal must be valid for the current information block when the upstream source asserts sink_sop and sink_valid.               |

| sink_max_iter[5:0]           | Input     | Specifies the maximum number of decoding iterations. The maximum value is 63.  This signal must be valid for the current information block when the upstream source asserts sink_sop and sink_valid.                                                                                               |

| Name               | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| source_valid       | Output    | The IP asserts this signal when <code>source_data</code> holds valid data.                                                                                                                                                                                                                                                                                                                                                                                          |

| source_sop         | Output    | The IP asserts this signal to mark the start of a packet.                                                                                                                                                                                                                                                                                                                                                                                                           |

| source_eop         | Output    | The IP asserts this signal to mark the end of a packet.                                                                                                                                                                                                                                                                                                                                                                                                             |

| source_ready       | Input     | Indicates that the design downstream of the IP is ready to receive data. The design can backpressure the IP by deasserting this signal.  The readyLatency for this signal is 0: the downstream design receives data the IP core drives on source_data in the same clock cycle in which the design asserts this signal. Refer to the Avalon Interface Specifications for the description of this Avalon- streaming interface property.                               |

| source_data[383:0] | Output    | Data output. When the IP sends valid data on this bus, it asserts the source_valid signal. If source_ready is deasserted, the decoder holds the data constant until source_ready is asserted.  If NUM_DECODERS = 1, and MAX_LF_DECODER0 is not 384,  • source_data[383:192] is 0 if MAX_LF_DECODER0 is 192,  • source_data[383:128] is 0 if MAX_LF_DECODER0 is 128  • source_data[383:96] is 0 if MAX_LF_DECODER0 is 96  Otherwise, the IP uses the full bus width. |

| source_mode[11:0]  | Output    | The value specifies the lifting size, base graph, and code rate. Refer to Input and Output Block Mode Meaning in 5G LDPC Decoder Data Formats on page 23.  This signal is valid when source_sop and source_valid are both asserted.                                                                                                                                                                                                                                 |

|                    | •         | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Name               | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| source_tag[7:0]    | Output    | Block tag. An optional tag that goes with the block from input to output. You can use this tag to establish the correspondence of the input and output block.  This signal is valid when source_sop and source_valid are both asserted.                                                                                                                                                                                                                       |

| source_blk_K[13:0] | Output    | Transmission block size K, in bits. K is the size of the output block from the decoder IP.  This signal is valid when source_sop and source_valid are both asserted.                                                                                                                                                                                                                                                                                          |

| source_blk_Z[8:0]  | Output    | The lifting size of the output block. For the output block, only the source_blk_Z least significant bits of source_data[383:0] are valid.  This signal is valid when source_sop and source_valid are both asserted.                                                                                                                                                                                                                                           |

| source_iter[5:0]   | Output    | Actual number of decode iterations by the IP to process the current output block. The count starts at 0 and might not be an accurate count of full iterations, because the decoding process might stop at any point if the decoder meets early termination criteria. The count cannot exceed the value communicated for the current transmission block via sink_max_iter minus one.  This signal is valid when source_sop and source_valid are both asserted. |

| source_et_pass     | Output    | Indicates whether the current information block meets early termination criteria. 0 indicates that the block does not meet early termination criteria; 1 indicates that the block meets early termination criteria.  The decoder can also assert the signal on the last iteration.  This signal is valid when source_sop and source_valid are both asserted.                                                                                                  |

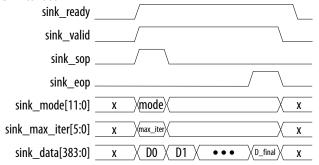

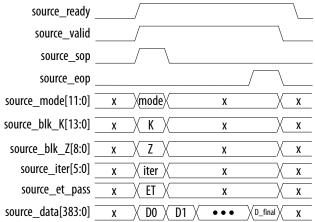

Figure 12. Example 5G LDPC Decoder Input Timing Diagram

This timing diagram illustrates an example transaction on the decoder input interface. Refer to the *Avalon Interface Specifications* for information about the required behavior of the ready, valid, sop, eop, and data signals on this Avalon-ST interface.

## Figure 13. Example 5G LDPC Decoder Output Timing Diagram

This timing diagram illustrates an example transaction on the decoder output interface. Refer to the *Avalon Interface Specifications* for information about the required behavior of the ready, valid, sop, eop, and data signals on this Avalon-ST interface.

#### **Related Information**

## **Avalon Interface Specifications**

Detailed information about Avalon-ST interfaces and their signal behavior requirements, including the definition of readyLatency.

# 4.1.2. 5G LDPC Decoder Data Formats

#### **Input Data Format**