# Interlaken (2nd Generation) Intel<sup>®</sup> FPGA IP User Guide

Updated for Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Suite: **20.2**

IP Version: 19.3.0

## Contents

| 1. Introduction                                               | 4    |

|---------------------------------------------------------------|------|

| 1.1. Features                                                 | 5    |

| 1.2. Device Family Support                                    | 8    |

| 1.3. Performance and Resource Utilization                     | 8    |

| 1.4. Flexible Lanes Support                                   |      |

| 1.5. Round-trip Latency                                       |      |

| 1.6. Release Information                                      |      |

|                                                               |      |

| 2. Getting Started                                            |      |

| 2.1. Installing and Licensing Intel FPGA IP Cores             |      |

| 2.1.1. Intel FPGA IP Evaluation Mode                          |      |

| 2.2. Generated File Structure                                 |      |

| 2.3. Specifying the IP Core Parameters and Options            |      |

| 2.4. Simulating the IP Core                                   |      |

| 2.5. Compiling the Full Design and Programming the FPGA       |      |

| 2.6. Integrating Your IP Core in Your Design                  |      |

| 2.6.1. Pin Assignment                                         |      |

| 2.6.2. Adding the External PLL                                |      |

| 2.6.3. PMA Adaptation Flow                                    | 22   |

| 3. Parameter Settings                                         | . 24 |

| 3.1. Main Parameters                                          |      |

| 3.2. PMA Adaptation Parameters                                |      |

|                                                               |      |

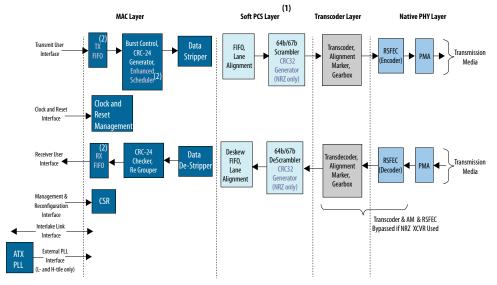

| 4. Functional Description                                     | 31   |

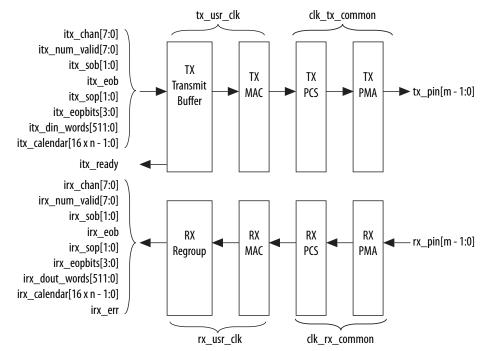

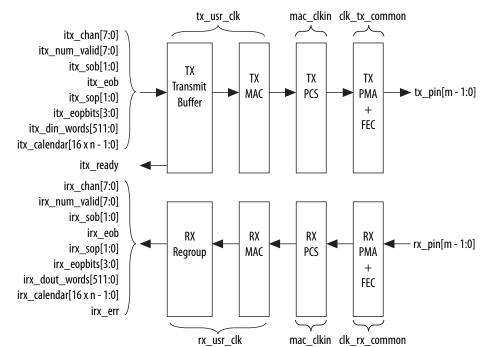

| 4.1. Interfaces                                               | 31   |

| 4.2. IP Clocks                                                | 33   |

| 4.3. High Level Data Path Flow for Interlaken Mode            | 34   |

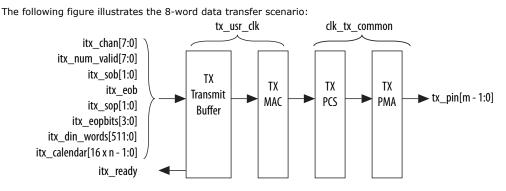

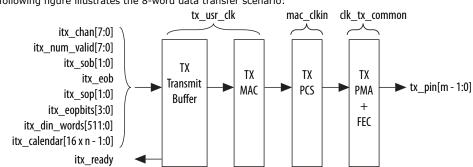

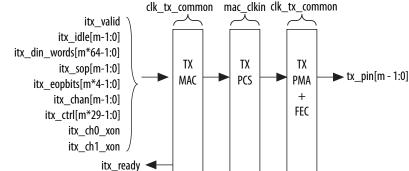

| 4.3.1. Interlaken TX Path                                     | 35   |

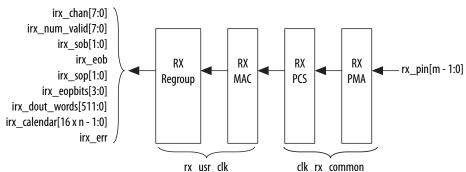

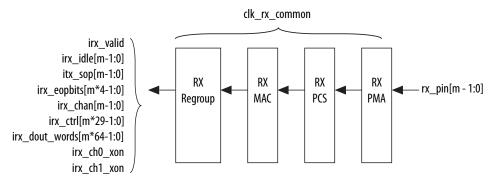

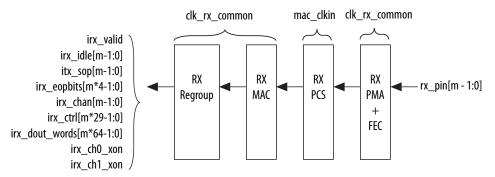

| 4.3.2. Interlaken RX Path                                     | 39   |

| 4.3.3. Unused Transceiver Channels                            | 44   |

| 4.4. High Level Data Path Flow for Interlaken Look-aside Mode | 44   |

| 4.4.1. Interlaken Look-aside TX Path                          |      |

| 4.4.2. Interlaken Look-aside RX Path                          |      |

| 4.5. Modes of Operation                                       | 50   |

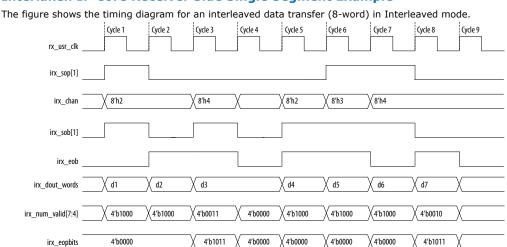

| 4.5.1. Interleaved and Packet Modes                           |      |

| 4.5.2. Interlaken Mode                                        | 51   |

| 4.5.3. Interlaken Look-aside Mode                             |      |

| 4.5.4. Multi-Segment Mode                                     | 59   |

| 4.6. Performance                                              | 63   |

| 4.7. IP Core Reset                                            |      |

| 4.8. M20K ECC Support                                         | 66   |

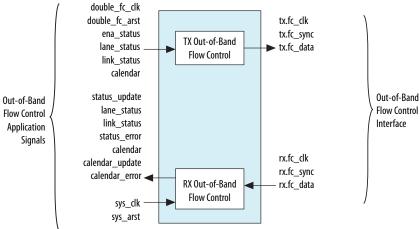

| 4.9. Out-of-Band Flow Control                                 |      |

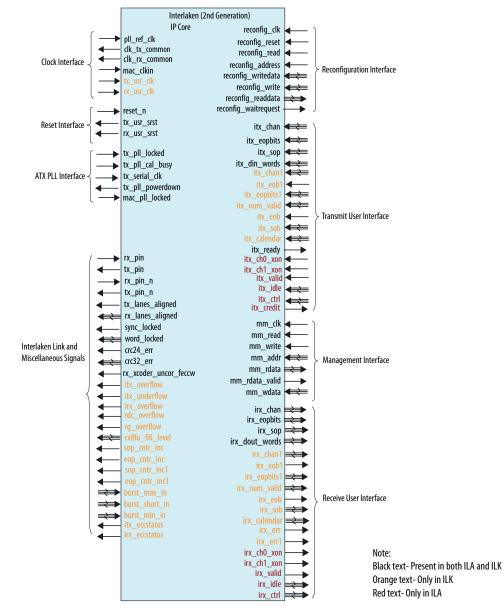

| 5. Interface Signals                                          |      |

| -                                                             |      |

| 5.1. Clock and Reset Interface Signals                        |      |

| 5.2. Transmit User Interface Signals                          |      |

| 5.3. Receive User Interface Signals                           | 79   |

Send Feedback

Interlaken (2nd Generation) Intel® FPGA IP User Guide

Contents

| 5.4. Management Interface Signals                                                        | 85 |

|------------------------------------------------------------------------------------------|----|

| 5.5. Reconfiguration Interface Signals                                                   | 86 |

| 5.6. Interlaken Link and Miscellaneous Signals                                           | 87 |

| 5.7. External PLL Interface Signals                                                      | 90 |

| 6. Register Map                                                                          | 91 |

| 7. Test Features                                                                         | 94 |

| 7.1. Internal Serial Loopback Mode                                                       | 94 |

| 7.2. External Loopback Mode                                                              |    |

| 8. Interlaken (2nd Generation) Intel FPGA IP User Guide Archives                         | 97 |

| 9. Document Revision History for Interlaken (2nd Generation) Intel FPGA IP User<br>Guide | 98 |

## **1. Introduction**

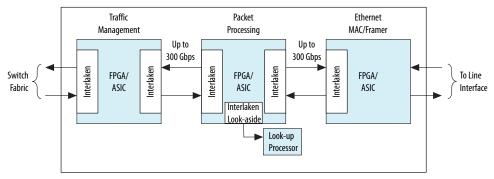

Interlaken is a high-speed serial communication protocol for chip-to-chip packet transfers. The Interlaken (2nd Generation) Intel<sup>®</sup> FPGA IP implements the *Interlaken Protocol Specification, v1.2*. This IP also implements Interlaken Look-aside protocol compliant to *Interlaken Look-Aside Protocol Definition, v1.1*. Interlaken supports multiple combinations of number of lanes (4 to 12) and lane rates from 6.25 gigabits per second (Gbps) to 53.125 Gbps, on Intel Stratix<sup>®</sup> 10 and Intel Agilex<sup>™</sup> devices, providing raw bandwidth up to 300 Gbps.

Interlaken provides low I/O count compared to earlier protocols, supporting scalability in both number of lanes and lane speed. Other key features include flow control, low overhead framing, and extensive integrity checking. The Interlaken IP incorporates a physical coding sublayer (PCS), a physical media attachment (PMA), and a media access control (MAC) block.

Interlaken Look-aside is a scalable protocol that allows interoperability between a datapath device and a Look-aside co-processor with packet transfer rates up to 300 Gbps.

## Figure 1. Typical Interlaken Application

## **Related Information**

- Interlaken (2nd Generation) Intel Stratix 10 FPGA IP Design Example User Guide Describes a simulating testbench and a hardware example design that supports compilation and hardware testing.

- Interlaken Protocol Specification, v1.2

- Interlaken (2nd Generation) Intel FPGA IP User Guide Archives on page 97

- Interlaken (2nd Generation) Intel Agilex FPGA IP Design Example User Guide

- Interlaken Look-Aside Protocol Definition, v1.1

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

## 1.1. Features

The Interlaken (2nd Generation) Intel FPGA IP has the following features:

- General features:

- Compliant with the Interlaken Protocol Specification, Revision 1.2.

- Supports 4, 6, 8, 10, and 12 serial lanes in configurations that provide up to 318.75 Gbps raw bandwidth.

- Supports per-lane data rates of 6.25, 10.3125, 12.5, 25.3, 25.8, and 53.125

Gbps using Intel FPGA on-chip high-speed transceivers.

- User interface features:

- Supports dynamically configurable BurstMax and BurstMin values.

- Supports Packet mode and Interleaved mode for user data transfer.

- Supports up to 256 logical channels in out-of-the-box configuration.

- Supports multi-segment user interface.

- Flow-control features:

- Supports optional out-of-band flow control blocks.

- Supports optional user-controlled in-band flow control with 1, 2, 4, 8, or 16 16-bit calendar pages.

- Supports error correction code (ECC) for memory block implementation with the IP.

- Line-side features:

- Supports per-lane data rate of 53.125 Gbps using pulse amplitude modulation (PAM4) mode in E-tile variations.

- Supports per lane data rates of 6.25, 10.3125, 12.5, 25.3, and 25.8 Gbps using non-return-to-zero (NRZ) mode in E-tile variations.

- PHY features:

- Supports PMA adaptation.

- Interlaken Look-aside mode:

- Supports per lane data rates of 6.25, 10.3125, 12.5, 25.3, and 25.8 Gbps using NRZ and 53.125 Gbps using PAM4 mode in E-tile variations.

- Supports packet mode for user data transfer.

- Available only in Intel Stratix 10 and Intel Agilex E-tile device variations.

## Table 1. IP Supported Combinations of Number of Lanes and Data Rates

The following combinations are supported in the current version of the Intel  ${\rm Quartus}^{\circledast}$  Prime Pro Edition software:

| Paula        | IP Supported Combinations |                                 |  |  |

|--------------|---------------------------|---------------------------------|--|--|

| Device       | Number of Lanes           | Lane Rate (Gbps) <sup>(1)</sup> |  |  |

|              |                           | 6.25                            |  |  |

|              |                           | 12.5                            |  |  |

|              | 4                         | 25.3                            |  |  |

| L-tile       |                           | 25.8                            |  |  |

|              | 8                         | 12.5                            |  |  |

|              | 12                        | 10.3125                         |  |  |

|              | 12                        | 12.5                            |  |  |

|              |                           | 6.25                            |  |  |

| H-tile       | 4                         | 12.5                            |  |  |

|              | +                         | 25.3                            |  |  |

|              |                           | 25.8                            |  |  |

|              | 6                         | 25.3                            |  |  |

|              | 0                         | 25.8                            |  |  |

|              |                           | 12.5                            |  |  |

|              | 8                         | 25.3                            |  |  |

| True         |                           | 25.8                            |  |  |

|              |                           | 12.5                            |  |  |

|              | 10                        | 25.3                            |  |  |

|              |                           | 25.8                            |  |  |

|              |                           | 10.3125                         |  |  |

|              | 12                        | 12.5                            |  |  |

|              | 12                        | 25.3                            |  |  |

|              |                           | 25.8                            |  |  |

|              |                           | 6.25                            |  |  |

|              | 1                         | 12.5                            |  |  |

|              | 4                         | 25.3                            |  |  |

| E-tile (NRZ) |                           | 25.8                            |  |  |

|              | 6                         | 25.3                            |  |  |

|              | 0                         | 25.8                            |  |  |

|              | 8                         | 12.5                            |  |  |

|              |                           | continued                       |  |  |

$<sup>^{(1)}\,</sup>$  You can customize the data rates depending on the tiles. Refer to the KDB for information on how to customize the data rate.

| Device        | IP Supported    | Combinations                    |

|---------------|-----------------|---------------------------------|

| Device        | Number of Lanes | Lane Rate (Gbps) <sup>(1)</sup> |

|               |                 | 25.3                            |

|               |                 | 25.8                            |

|               |                 | 12.5                            |

|               | 10              | 25.3                            |

|               |                 | 25.8                            |

|               |                 | 10.3125                         |

|               | 12              | 12.5                            |

|               | 12              | 25.3                            |

|               |                 | 25.8                            |

| E-tile (PAM4) | 12              | 26.5625 <sup>(2)</sup>          |

## Table 2. IP Theoretical Raw Aggregate Bandwidth

The following combinations are supported in the current version of the Intel Quartus Prime Pro Edition software:

| Number of | Lane Rate (Gbps) |         |      |       |       |         |

|-----------|------------------|---------|------|-------|-------|---------|

| Lanes     | 6.25             | 10.3125 | 12.5 | 25.3  | 25.8  | 26.5625 |

| 4         | 25               | -       | 50   | 101.2 | 103.2 | -       |

| 6         | -                | -       | -    | 151.8 | 154.8 | -       |

| 8         | -                | -       | 100  | 202.4 | 206.4 | -       |

| 10        | -                | -       | 125  | 253   | 258   | -       |

| 12        | -                | 123.75  | 150  | 303.6 | 309.6 | 318.75  |

## **Related Information**

Interlaken Protocol Specification, v1.2

<sup>&</sup>lt;sup>(2)</sup> To obtain 6x53.125 Gbps speed in PAM4 mode, select 12x26.5625 Gbps.

<sup>&</sup>lt;sup>(1)</sup> You can customize the data rates depending on the tiles. Refer to the KDB for information on how to customize the data rate.

## **1.2. Device Family Support**

The following lists the device support level definitions for Intel FPGA IPs:

- Advance support The IP is available for simulation and compilation for this device family. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O standards tradeoffs).

- **Preliminary support** The IP is verified with preliminary timing models for this device family. The IP meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.

- **Final support** The IP is verified with final timing models for this device family. The IP meets all functional and timing requirements for the device family and can be used in production designs.

## Table 3.Device Family Support

| Device Family    | Support |

|------------------|---------|

| Intel Stratix 10 | Final   |

| Intel Agilex     | Advance |

## **1.3. Performance and Resource Utilization**

This section covers the resources and expected performance numbers for selected variations of the Interlaken IP core using the Intel Quartus Prime Pro Edition software. The number of ALMs and logic registers are rounded up to the nearest 100.

For a comprehensive list of supported configurations, refer to *Table 1. IP Supported Combinations of Number of Lanes and Data Rates*

## Table 4. Intel Stratix 10 FPGA Resource Utilization in Interlaken Mode

The following numbers were obtained using the Intel Quartus Prime Pro Edition software version 19.3:

| Parame                     |                  | neters      | Resource Utilization |                 |           |             |

|----------------------------|------------------|-------------|----------------------|-----------------|-----------|-------------|

| Device                     | Device Number of |             | ALMs needed          | Logic Registers |           | M20K Blocks |

|                            | Lanes            | Rate (Gbps) | ALMS needed          | Primary         | Secondary | MZUK BIOCKS |

|                            | 4                | 6.25        | 9500                 | 19500           | 3500      | 30          |

|                            | 4                | 12.5        | 10200                | 22000           | 3600      | 30          |

|                            | 4                | 25.3        | 10200                | 22000           | 3400      | 30          |

| Intel Stratix 10<br>L-tile | 4                | 25.8        | 11300                | 24000           | 4100      | 30          |

|                            | 8                | 12.5        | 21300                | 47400           | 7300      | 45          |

|                            | 12               | 10.3125     | 21000                | 45000           | 6600      | 54          |

|                            | 12               | 12.5        | 24000                | 50000           | 7800      | 54          |

|                            |                  | •           | •                    |                 |           | continued   |

1. Introduction UG-20035 | 2020.06.22

|                                   | Paran     | neters      | Resource Utilization |         |           |               |

|-----------------------------------|-----------|-------------|----------------------|---------|-----------|---------------|

| Device                            | Number of | Data/Lane   |                      | Logic R | egisters  |               |

|                                   | Lanes     | Rate (Gbps) | ALMs needed          | Primary | Secondary | - M20K Blocks |

|                                   | 4         | 6.25        | 9500                 | 19600   | 3300      | 30            |

|                                   | 4         | 12.5        | 10700                | 22400   | 3600      | 30            |

|                                   | 4         | 25.3        | 10500                | 22000   | 3400      | 30            |

| -                                 | 4         | 25.8        | 11600                | 24500   | 3800      | 30            |

|                                   | 6         | 25.3        | 20000                | 44600   | 7200      | 52            |

| -                                 | 6         | 25.8        | 20000                | 44900   | 7300      | 52            |

|                                   | 8         | 12.5        | 22000                | 48600   | 7200      | 45            |

| Intel Stratix 10                  | 8         | 25.3        | 21000                | 45900   | 6200      | 54            |

| H-tile                            | 8         | 25.8        | 21000                | 45900   | 6000      | 54            |

|                                   | 10        | 12.5        | 22000                | 53000   | 6700      | 51            |

| -                                 | 10        | 25.3        | 31100                | 75000   | 8000      | 100           |

| -                                 | 10        | 25.8        | 30100                | 72800   | 8600      | 100           |

| -                                 | 12        | 10.3125     | 22100                | 46600   | 6400      | 54            |

| -                                 | 12        | 12.5        | 24000                | 50300   | 7700      | 54            |

|                                   | 12        | 25.3        | 34400                | 78900   | 8460      | 102           |

| -                                 | 12        | 25.8        | 37100                | 85100   | 9400      | 102           |

|                                   | 4         | 6.25        | 15300                | 30000   | 4700      | 30            |

| -                                 | 4         | 12.5        | 15500                | 30200   | 5000      | 30            |

| -                                 | 4         | 25.8        | 16600                | 32000   | 5300      | 30            |

| -                                 | 6         | 25.8        | 28000                | 58700   | 8800      | 52            |

| -                                 | 8         | 12.5        | 31800                | 64800   | 9500      | 45            |

| Intel Stratix 10<br>E-tile (NRZ)  | 8         | 25.8        | 29000                | 59200   | 8500      | 52            |

| . ,                               | 10        | 12.5        | 38900                | 79200   | 10800     | 53            |

|                                   | 10        | 25.8        | 43700                | 94000   | 12500     | 100           |

|                                   | 12        | 10.3125     | 44900                | 93200   | 11100     | 73            |

|                                   | 12        | 12.5        | 48900                | 100100  | 13300     | 87            |

| -                                 | 12        | 25.8        | 50000                | 108000  | 13200     | 100           |

| Intel Stratix 10<br>E-tile (PAM4) | 6         | 53.125      | 65500                | 134900  | 18000     | 102           |

## Table 5. Intel Agilex FPGA Resource Utilization in Interlaken Mode

|                                | Parameters |             | Resource Utilization |                 |           |             |

|--------------------------------|------------|-------------|----------------------|-----------------|-----------|-------------|

| Device                         | Number of  | Data/Lane   |                      | Logic Registers |           |             |

|                                | Lanes      | Rate (Gbps) | ALMs needed          | Primary         | Secondary | M20K Blocks |

|                                | 4          | 6.25        | 15200                | 28800           | 6700      | 30          |

|                                | 4          | 12.5        | 15600                | 29300           | 6800      | 30          |

|                                | 4          | 25.8        | 16500                | 31300           | 7700      | 30          |

|                                | 6          | 25.8        | 28000                | 57600           | 13100     | 52          |

|                                | 8          | 12.5        | 31800                | 63400           | 13200     | 45          |

| Intel Agilex E-<br>tile (NRZ)  | 8          | 25.8        | 29200                | 59400           | 12500     | 52          |

|                                | 10         | 12.5        | 45700                | 94000           | 16200     | 73          |

|                                | 10         | 25.8        | 43500                | 94300           | 18000     | 100         |

|                                | 12         | 10.3125     | 44900                | 91600           | 16100     | 73          |

|                                | 12         | 12.5        | 48800                | 99200           | 17800     | 87          |

|                                | 12         | 25.8        | 49900                | 106800          | 20000     | 100         |

| Intel Agilex E-<br>tile (PAM4) | 6          | 53.125      | 64900                | 132600          | 26300     | 102         |

The following numbers were obtained using the Intel Quartus Prime Pro Edition software version 19.3:

# Table 6. Intel Stratix 10 E-tile Resource Utilization Numbers in Interlaken Look-aside Mode

The following numbers were obtained using the Intel Quartus Prime Pro Edition software version 20.2:

| Device                            | Parameters |             |       | Resource        | Utilization |            |

|-----------------------------------|------------|-------------|-------|-----------------|-------------|------------|

|                                   | Number of  | Data/Lane   | ALMs  | Logic Registers |             | M20 Blocks |

|                                   | Lanes      | Rate (Gbps) |       | Primary         | Secondary   |            |

|                                   |            | 6           | 11700 | 19400           | 3200        | 2          |

|                                   | 4          | 12          | 11900 | 19700           | 3200        | 2          |

|                                   |            | 25.8        | 10800 | 18200           | 3000        | 0          |

|                                   | 6          | 25.8        | 17200 | 28600           | 4800        | 2          |

|                                   | 8          | 12          | 23200 | 39500           | 6200        | 2          |

| Intel Stratix 10<br>E-tile (NRZ)  |            | 25.8        | 21800 | 37000           | 6100        | 0          |

|                                   | 10         | 12          | 29400 | 50600           | 7900        | 2          |

|                                   |            | 25.8        | 29300 | 49800           | 7500        | 2          |

|                                   | 12         | 10          | 35700 | 62100           | 9200        | 2          |

|                                   |            | 12          | 35800 | 62400           | 9000        | 2          |

|                                   |            | 25.8        | 34000 | 59300           | 8500        | 0          |

| Intel Stratix 10<br>E-tile (PAM4) | 6          | 53.125      | 49600 | 86700           | 12600       | 2          |

Interlaken (2nd Generation) Intel® FPGA IP User Guide

# Table 7. Intel Agilex E-tile Resource Utilization Numbers in Interlaken Look-aside Mode

| Device                          | Parameters |             | Resource Utilization |         |           |            |

|---------------------------------|------------|-------------|----------------------|---------|-----------|------------|

|                                 | Number of  | Data/Lane   | ALMs                 | Logic R | egisters  | M20 Blocks |

|                                 | Lanes      | Rate (Gbps) |                      | Primary | Secondary |            |

|                                 |            | 6           | 11800                | 19300   | 4500      | 2          |

|                                 | 4          | 12          | 11900                | 19600   | 4400      | 2          |

|                                 |            | 25.8        | 10700                | 17700   | 4540      | 0          |

|                                 | 6          | 25.8        | 17500                | 28800   | 6900      | 2          |

|                                 | 8          | 12          | 23400                | 39100   | 8400      | 2          |

| Intel Agilex E-<br>tile (NRZ)   |            | 25.8        | 21900                | 37300   | 8820      | 0          |

|                                 | 10         | 12          | 29600                | 50300   | 10800     | 2          |

|                                 |            | 25.8        | 29600                | 49800   | 11200     | 2          |

|                                 | 12         | 10          | 35700                | 61100   | 12800     | 2          |

|                                 |            | 12          | 35900                | 61300   | 12500     | 2          |

|                                 |            | 25.8        | 33700                | 58600   | 13400     | 0          |

| Intel Agilex E-<br>tile ( PAM4) | 6          | 53.125      | 49100                | 85400   | 17600     | 2          |

The following numbers were obtained using the Intel Quartus Prime Pro Edition software version 20.2:

#### **Related Information**

Features on page 5

## **1.4. Flexible Lanes Support**

In the current version of the Intel Quartus Prime Pro Edition software, the IP parameter editor prompts you to the recommended user clock frequency for the combination of number of lanes and data rates. The software derives the user clock frequency based on the configuration you select. The user clock frequency maps to the tx\_usr\_clk and rx\_usr\_clk signals.

## Table 8.Recommended User Clock Frequency

| Number of Lanes | Data/Lane Rate | Number of Segments | User Clock Frequency (MHz) |        |  |  |  |

|-----------------|----------------|--------------------|----------------------------|--------|--|--|--|

| Number of Lanes | (Gbps)         | Number of Segments | H-tile                     | E-tile |  |  |  |

|                 | 6.25           |                    | 200                        | 100    |  |  |  |

|                 | 12.5           | 1 -                | 20                         | 0      |  |  |  |

| 4               | 25.3           |                    | 400                        |        |  |  |  |

|                 | 25.8           |                    | 400                        |        |  |  |  |

| 6               | 25.3           | 1.2                | 30                         | 0      |  |  |  |

| 0               | 25.8           | 1, 2               | 30                         | 0      |  |  |  |

| 8               | 12.5           | 1, 2               | 200                        |        |  |  |  |

|                 | continued      |                    |                            |        |  |  |  |

| Number of Lanes | Data/Lane Rate                                          | Number of Comments | User Clock Frequency (MHz) |        |

|-----------------|---------------------------------------------------------|--------------------|----------------------------|--------|

| Number of Lanes | (Gbps) Number of Segments                               |                    | H-tile                     | E-tile |

|                 | 25.3                                                    |                    | 4                          | 00     |

|                 | 25.8                                                    |                    | 4                          | 00     |

|                 | 12.5                                                    | 1, 2               | 2                          | 50     |

| 10              | 25.3                                                    | 1, 2, 4            | 2                          | 50     |

|                 | 25.8                                                    | 1, 2, 4            | 300                        |        |

|                 | 10.3125                                                 | 1                  | 300                        | 250    |

|                 |                                                         | 2                  | 250                        | 250    |

| 12.5            |                                                         | 1, 2               | 300                        |        |

| 12              | 25.3                                                    | 1                  | 350                        |        |

| 12              | 25.5                                                    | 2, 4               | 300                        |        |

|                 | 25.8                                                    | 1, 2, 4            | 3                          | 50     |

|                 | 25.5625 (Only in E-<br>tile PAM4 mode IP<br>variations) | 1, 2, 4            | N/A                        | 350    |

## **1.5. Round-trip Latency**

The followingtable includes the round-trip latency numbers for specific variants. The latency numbers were measured for the longest logical datapath for two highest lane rate and number of lanes variants, with FIFO level at 50 for the first packet.

|               |                    |                     | Interlaken            |                                                | Interlaken Look-aside |                                                |

|---------------|--------------------|---------------------|-----------------------|------------------------------------------------|-----------------------|------------------------------------------------|

| Device        | Number of<br>Lanes | Lane Rate<br>(Gbps) | Number of<br>Segments | Latency<br>(Number of<br>tx_usr_clk<br>cycles) | Number of<br>Segments | Latency<br>(Number of<br>tx_usr_clk<br>cycles) |

| E-tile (NRZ)  | 12                 | 25.8                | 4                     | 260                                            | 1                     | 104                                            |

| E-tile (PAM4) | 12                 | 26.5625             | 4                     | 368                                            | 1                     | 228                                            |

## **1.6. Release Information**

IP versions are the same as the Intel Quartus Prime Design Suite software versions up to v19.1. From Intel Quartus Prime Design Suite software version 19.2 or later, IP cores have a new IP versioning scheme.

The IP version (X.Y.Z) number may change from one Intel Quartus Prime software version to another. A change in:

- X indicates a major revision of the IP. If you update your Intel Quartus Prime software, you must regenerate the IP.

- Y indicates the IP includes new features. Regenerate your IP to include these new features.

- Z indicates the IP includes minor changes. Regenerate your IP to include these changes.

## Table 9. Interlaken (2nd Generation) Intel FPGA IP Core Release Information

| Item                        | Value               |                                                          |            |  |  |  |

|-----------------------------|---------------------|----------------------------------------------------------|------------|--|--|--|

| IP Version                  |                     | 19.3.0                                                   |            |  |  |  |

| Intel Quartus Prime Version | 20.2                |                                                          | 20.2       |  |  |  |

| Release Date                | 2020.06.22          |                                                          |            |  |  |  |

|                             | Aggregate Bandwidth | Ordering Code                                            | Product ID |  |  |  |

|                             | 20G to <100G        | IP-ILKN/50G                                              |            |  |  |  |

| Ordering Code               | 100G to <200G       | IP-ILKN/100G                                             | 010E       |  |  |  |

| j                           | 200G to <400G       | 200G to <400G IP-ILKN/200G                               |            |  |  |  |

|                             |                     | or Interlaken Look-aside II<br>aken (2nd Generation) Int |            |  |  |  |

## **Related Information**

Interlaken (2nd Generation) Intel FPGA IP Release Notes Describes changes to the IP in a particular release.

## **2. Getting Started**

The following sections explain how to install, parameterize, simulate, and initialize the Interlaken (2nd Generation) Intel FPGA IP.

#### **Related Information**

- Introduction to Intel FPGA IP Cores

- Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Generating a Combined Simulator Setup Script (Intel Quartus Prime Pro Edition) Create simulation scripts that do not require manual updates for software or IP version upgrades.

- Project File Best Practices Guidelines for efficient management and portability of your project and IP files.

## 2.1. Installing and Licensing Intel FPGA IP Cores

The Intel Quartus Prime software installation includes the Intel FPGA IP library. This library provides many useful IP cores for your production use without the need for an additional license. Some Intel FPGA IP cores require purchase of a separate license for production use. The Intel FPGA IP Evaluation Mode allows you to evaluate these licensed Intel FPGA IP cores in simulation and hardware, before deciding to purchase a full production IP core license. You only need to purchase a full production license for licensed Intel IP cores after you complete hardware testing and are ready to use the IP in production.

The Intel Quartus Prime software installs IP cores in the following locations by default:

## Figure 2. IP Core Installation Path

## 📄 intelFPGA(\_pro)

- quartus - Contains the Intel Quartus Prime software

**ip** - Contains the Intel FPGA IP library and third-party IP cores

altera - Contains the Intel FPGA IP library source code

- - <IP name > - Contains the Intel FPGA IP source files

## Table 10. IP Core Installation Locations

| Location                                                               | Software                        | Platform |

|------------------------------------------------------------------------|---------------------------------|----------|

| <pre><drive>:\intelFPGA_pro\quartus\ip\altera</drive></pre>            | Intel Quartus Prime Pro Edition | Windows* |

| <pre><home directory="">:/intelFPGA_pro/quartus/ip/altera</home></pre> | Intel Quartus Prime Pro Edition | Linux*   |

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

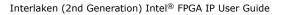

## 2.1.1. Intel FPGA IP Evaluation Mode

The free Intel FPGA IP Evaluation Mode allows you to evaluate licensed Intel FPGA IP cores in simulation and hardware before purchase. Intel FPGA IP Evaluation Mode supports the following evaluations without additional license:

- Simulate the behavior of a licensed Intel FPGA IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

Intel FPGA IP Evaluation Mode supports the following operation modes:

- **Tethered**—Allows running the design containing the licensed Intel FPGA IP indefinitely with a connection between your board and the host computer. Tethered mode requires a serial joint test action group (JTAG) cable connected between the JTAG port on your board and the host computer, which is running the Intel Quartus Prime Programmer for the duration of the hardware evaluation period. The Programmer only requires a minimum installation of the Intel Quartus Prime software, and requires no Intel Quartus Prime license. The host computer controls the evaluation time by sending a periodic signal to the device via the JTAG port. If all licensed IP cores in the design support tethered mode, the evaluation time runs until any IP core evaluation expires. If all of the IP cores support unlimited evaluation time, the device does not time-out.

- **Untethered**—Allows running the design containing the licensed IP for a limited time. The IP core reverts to untethered mode if the device disconnects from the host computer running the Intel Quartus Prime software. The IP core also reverts to untethered mode if any other licensed IP core in the design does not support tethered mode.

When the evaluation time expires for any licensed Intel FPGA IP in the design, the design stops functioning. All IP cores that use the Intel FPGA IP Evaluation Mode time out simultaneously when any IP core in the design times out. When the evaluation time expires, you must reprogram the FPGA device before continuing hardware verification. To extend use of the IP core for production, purchase a full production license for the IP core.

## Figure 3. Intel FPGA IP Evaluation Mode Flow

*Note:* Refer to each IP core's user guide for parameterization steps and implementation details.

Intel licenses IP cores on a per-seat, perpetual basis. The license fee includes firstyear maintenance and support. You must renew the maintenance contract to receive updates, bug fixes, and technical support beyond the first year. You must purchase a full production license for Intel FPGA IP cores that require a production license, before generating programming files that you may use for an unlimited time. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (*<project name>\_time\_limited.sof*) that expires at the time limit. To obtain your production license keys, visit the Self-Service Licensing Center.

The Intel FPGA Software License Agreements govern the installation and use of licensed IP cores, the Intel Quartus Prime design software, and all unlicensed IP cores.

### **Related Information**

- Intel FPGA Licensing Support Center

- Introduction to Intel FPGA Software Installation and Licensing

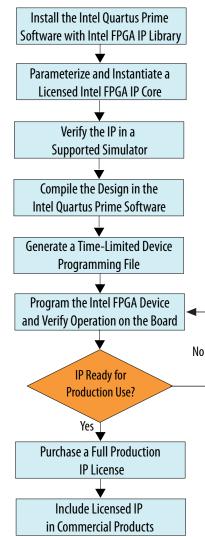

## 2.2. Generated File Structure

The Intel Quartus Prime Pro Edition software generates the following IP output file structure.

For more information about the file structure of the design example, refer to the device-specific *Interlaken IP (2nd Generation) Design Example User Guide*.

#### Figure 4. IP Generated Files

## Table 11.IP Generated Files

| File Name                               | Description                                                                                                                                                                                                                               |  |  |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <your_ip>.ip</your_ip>                  | The top-level IP variation file. < your_ip> is the name that you give your IP variation.                                                                                                                                                  |  |  |  |

| <your_ip>.cmp</your_ip>                 | The VHDL Component Declaration ( <b>.cmp</b> ) file is a text file that contains local generic and port definitions that you can use in VHDL design files.                                                                                |  |  |  |

|                                         | This IP does not support VHDL. However, the Intel Quartus Prime Pro Edition software generates this file.                                                                                                                                 |  |  |  |

| <your_ip>.html</your_ip>                | A report that contains connection information, a memory map showing the address of each slave with respect to each master to which it is connected, and parameter assignments.                                                            |  |  |  |

| <your_ip>_generation.rpt</your_ip>      | IP or Platform Designer generation log file. A summary of the messages during IP generation.                                                                                                                                              |  |  |  |

| <your_ip>.qgsimc</your_ip>              | Lists simulation parameters to support incremental regeneration.                                                                                                                                                                          |  |  |  |

| <your_ip>.qgsynthc</your_ip>            | Lists synthesis parameters to support incremental regeneration.                                                                                                                                                                           |  |  |  |

| <your_ip>.qip</your_ip>                 | Contains all the required information about the IP component to integrate and compile the IP component in the Intel Quartus Prime software.                                                                                               |  |  |  |

| <your_ip>.sopcinfo</your_ip>            | Describes the connections and IP component parameterizations in your<br>Platform Designer system. You can parse its contents to get requirements<br>when you develop software drivers for IP components.                                  |  |  |  |

| <your_ip>.csv</your_ip>                 | Contains information about the upgrade status of the IP component.                                                                                                                                                                        |  |  |  |

| <your_ip>.bsf</your_ip>                 | A Block Symbol File (. <b>bsf</b> ) representation of the IP variation for use in Intel Quartus Prime Block Diagram Files ( <b>.bdf</b> ).                                                                                                |  |  |  |

| <your_ip>.spd</your_ip>                 | Required input file for ip-make-simscript to generate simulation scripts for supported simulators. The <b>.spd</b> file contains a list of files generated for simulation, along with information about memories that you can initialize. |  |  |  |

| <your_ip>.ppf</your_ip>                 | The Pin Planner File ( <b>.ppf</b> ) stores the port and node assignments for IP components created for use with the Pin Planner.                                                                                                         |  |  |  |

| <your_ip>_bb.v</your_ip>                | You can use the Verilog black-box ( <b>_bb.v</b> ) file as an empty module declaration for use as a black box.                                                                                                                            |  |  |  |

| <your_ip>_inst.v or _inst.vhd</your_ip> | HDL example instantiation template. You can copy and paste the contents of this file into your HDL file to instantiate the IP variation.                                                                                                  |  |  |  |

|                                         | This IP does not support VHDL. However, the Intel Quartus Prime Pro Edition software generates the _inst.vhd file.                                                                                                                        |  |  |  |

| <your_ip>.v</your_ip>                   | HDL files that instantiates each submodule or child IP for synthesis or simulation.                                                                                                                                                       |  |  |  |

| mentor/                                 | Contains a ModelSim* script msim_setup.tcl to set up and run a simulation.                                                                                                                                                                |  |  |  |

| synopsys/vcs/                           | Contains a shell script ${\tt vcs\_setup.sh}$ to set up and run a VCS* simulation.                                                                                                                                                        |  |  |  |

| synopsys/vcsmx/                         | Contains a shell script vcsmx_setup.sh and synopsys_ sim.setup file to set up and run a VCS MX* simulation.                                                                                                                               |  |  |  |

| cadence/                                | Contains a shell script $\tt ncsim\_setup.sh$ and other setup files to set up and run an NCSim* simulation.                                                                                                                               |  |  |  |

| xcelium/                                | Contains a shell script xcelium_setup.sh to set up and run a Xcelium* simulation.                                                                                                                                                         |  |  |  |

| submodules/                             | Contains HDL files for the IP core submodules.                                                                                                                                                                                            |  |  |  |

| <child cores="" ip="">/</child>         | For each generated child IP directory, Platform Designer generates $\mathtt{synth}/$ and $\mathtt{sim}/$ sub-directories.                                                                                                                 |  |  |  |

#### **Related Information**

- Interlaken (2nd Generation) Intel Stratix 10 FPGA IP Design Example User Guide

- Interlaken (2nd Generation) Intel Agilex FPGA IP Design Example User Guide

## **2.3. Specifying the IP Core Parameters and Options**

The IP parameter editor allows you to quickly configure your custom IP variation. Perform the following steps to specify IP core options and parameters in the Intel Quartus Prime Pro Edition software.

The Interlaken IP is not supported in Platform Designer. You must use the IP Catalog accessible from the Intel Quartus Prime Pro Edition **Tools** menu. The Interlaken IP does not support VHDL simulation models. You must specify the Verilog HDL for both synthesis and simulation models.

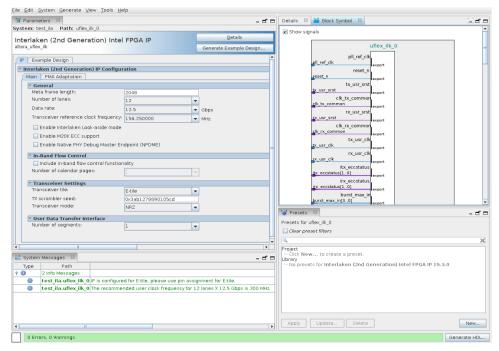

#### Figure 5. IP Parameter Editor

- In the Intel Quartus Prime Pro Edition software, click File ➤ New Project Wizard to create a new Intel Quartus Prime project, or File ➤ Open Project to open an existing Intel Quartus Prime project. The wizard prompts you to specify a device.

- Select the device family either Stratix 10 (GX/SX/MX/TX) or Agilex (FB/FA) as your target device.

- 3. In the IP Catalog (Tools ➤ IP Catalog), locate and double-click Interlaken (2nd Generation) Intel FPGA IP. The New IP Variant window appears.

- 4. Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named <*your\_ip*>.ip.

- 5. Click Create. The parameter editor appears.

- 6. On the **IP** tab, specify the parameters and options for your IP variation, including one or more of the following. Refer to *Parameter Settings* for information about specific IP core parameters.

- Specify parameters defining the IP core functionality, port configurations, and device-specific features.

- Specify options for processing the IP core files in other EDA tools.

- 7. Click Generate HDL. The Generation dialog box appears.

- 8. Specify output file generation options, and then click **Generate**. The IP variation files generate according to your specifications.

- Optionally, click Generate Example Design tab in the parameter editor to generate a demonstration testbench and example design for your IP core variation.

*Note:* To generate the demonstration testbench and example design, you must specify Verilog HDL for both synthesis and simulation models.

- Click Finish. The parameter editor adds the top-level .ip file to the project automatically. If you are prompted to manually add the .ip file to the project, click Project ➤ Add/Remove Files in Project to add the file.

- 11. After generating and instantiating your IP variation, make appropriate pin assignments to connect ports.

#### **Related Information**

- Interlaken (2nd Generation) Intel Stratix 10 FPGA IP Design Example User Guide Describes a simulating testbench and a hardware example design that supports compilation and hardware testing.

- Main Parameters on page 24

- Interlaken (2nd Generation) Intel Agilex FPGA IP Design Example User Guide

## 2.4. Simulating the IP Core

You can simulate your Interlaken IP variation using any of the vendor-specific IEEE encrypted functional simulation models which are available in the new <instance name>/sim/<simulator> subdirectory of your project directory.

The Interlaken IP supports the Synopsys VCS, Mentor Graphics Modelsim-SE\*, and Cadence NCSim and Xcelium Parallel simulators. The Interlaken IP generates a Verilog HDL and VHDL simulation model and testbench. The IP core parameter editor offers you the option of generating a Verilog HDL or VHDL simulation model for the IP core, but the IP core design example does not support a VHDL simulation model or testbench.

For more information about functional simulation models for Intel FPGA IP cores, refer to the *Simulating Intel FPGA Designs* chapter in *Intel Quartus Prime Pro Edition User Guide: Third-party Simulation*.

## **Related Information**

Simulating Intel FPGA Designs

## 2.5. Compiling the Full Design and Programming the FPGA

You can use the **Start Compilation** command on the **Processing** menu in the Intel Quartus Prime software to compile your design. After successfully compiling your design, program the targeted Intel device with the Programmer and verify the design in hardware.

#### **Related Information**

- Programming Intel FPGA Devices

- Design Compilation

## 2.6. Integrating Your IP Core in Your Design

## 2.6.1. Pin Assignment

When you integrate your Interlaken IP instance in your design, you must make appropriate pin assignments.

You do not need to specify pin assignments for simulation. However, you should make the pin assignments before you compile. Pin assignments provide direction to the Fitter and specify the signals that should be assigned to device pins. While compiling only the IP core, you can create virtual pins to avoid making specific pin assignments for top-level signals. When you are ready to map the design to hardware, you can change to the correct pin assignments.

## **Related Information**

GX and GXT Channel Placement Guidelines

## 2.6.2. Adding the External PLL

The Interlaken (2nd Generation) IP core variations that target an L-Tile or H-Tile device require an external TX transceiver PLL to drive the TX transceiver clock, in order to compile and to function correctly in hardware. In many cases, the same PLL can be shared with other transceivers in your design.

You can create an external transceiver PLL from the IP Catalog:

- Select the L-Tile/H-Tile Transceiver ATX PLL Intel Stratix 10 FPGA IP.

- In the parameter editor, set the following parameter values:

- Set **PLL output frequency** to one half the per-lane data rate of the IP core variation.

- Set PLL auto mode reference clock frequency (integer) to the value you select for the transceiver reference clock frequency (pll\_ref\_clk) parameter in the Interlaken (2nd Generation) IP parameter editor.

- Set VCCR\_GXB and VCCT\_GXB Supply Voltage for the transceiver to the same value you specify in the Interlaken (2nd Generation) IP parameter editor.

You must connect tx\_serial\_clock output from the ATX PLL to tx\_serial\_clk input of your Interlaken (2nd Generation) IP core.

For more information about ATX PLL connection and how to instantiate the ATX PLL, refer to the *Instantiating the ATX PLL IP Core* in the *Intel Stratix 10 L- and H-Tile Transceiver PHY User Guide*.

To use fPLL as an external transceiver PLL, select **L-Tile/H-Tile fPLL Intel Stratix 10 FPGA IP** from the IP Catalog and set the parameters using the instructions in the *Instantiating the fPLL IP Core* in the *Intel Stratix 10 L- and H-Tile Transceiver PHY User Guide.*

The Interlaken (2nd Generation) IP core variations that target an E-tile device contains transceiver PLLs and do not require an external PLL for the transceivers. These transceiver PLLs require a reference clock (pll\_ref\_clk). Refer to the *E-Tile Transceiver PHY User Guide* and *Interlaken (2nd Generation) Design Example User Guide* for the reference clock connections.

The E-tile PAM4 mode variations require an additional mac\_clkin input clock generated by a PLL. This PLL must use the same reference clock source that drives the pll\_ref\_clk. Refer to *Figure: Interlaken (2nd Generation) Hardware Design Example High Level Block Diagram for E-tile PAM4 Mode Variations* in *Interlaken (2nd Generation) Intel FPGA IP Design Example User Guide* for more information about mac\_clkin connections.

## **Related Information**

- Intel Stratix 10 L- and H-Tile Transceiver PHY User Guide

- Interlaken (2nd Generation) Intel Stratix 10 FPGA IP Design Example User Guide

- E-Tile Transceiver PHY User Guide

- Interlaken (2nd Generation) Intel Agilex FPGA IP Design Example User Guide

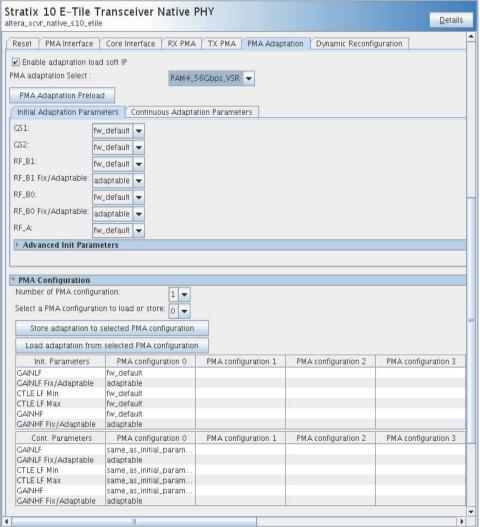

## 2.6.3. PMA Adaptation Flow

The Interlaken (2nd Generation) Intel FPGA IP does not start PMA adaptation in L- and H-tile device variations. If you want to enable PMA adaptation, you must start through transceiver PHY reconfiguration interface. Refer to *Adaptation Control- Start* section of the *Intel Stratix 10 L- and H-tile Transceiver PHY User Guide* for information on how to start PMA adaptation through transceiver PHY reconfiguration interface.

For your E-tile Interlaken IP core variations, perform the following steps to start PMA adaptation:

- 1. Set the operation mode:

- Write 0x200 = 0x1F.

- Write 0x201 = 0x00.

- Write 0x202 = 0x00

- Write 0x203 = 0x93. This picks the opcode for SET\_OPERATION\_MODE.

*Note:* Values set for 0x200 and 0x201 are just examples. Refer to *Figure: Loading PMA Configuration Register SET\_OPERATION\_MODE* in *E-tile Transceiver PHY User Guide* for 32-bits decoding and set it according to your design intent.

2. Load recipe<sup>(3)</sup>:

<sup>&</sup>lt;sup>(3)</sup> If load recipe is required.

- Write 0x40143 = 0x80. Loads the PMA configuration to all channels (0x40143 and 0x40144 can only be accessed from channel 0).

- Read 0x40144[0] until it reports 0x1. This ensures the process is not timed out.

- 3. Start adaptation:

- Write 0x200 = 0xF2.

- Write 0x201 = 0x03.

- Write 0x202 = 0x01.

- Write 0x203 = 0x96.

- *Note:* Values set for 0x200, 0x201, and 0x202 are just examples. Refer to *Figure: Loading PMA Configuration Register START\_ADAPTATION* in *E-tile Transceiver PHY User Guide* for 32-bits decoding and set it according to your design intent.

- *Note:* PRBS will not be disabled automatically after calibration if you have already enabled it in SET\_OPERATION\_MODE and START\_ADAPTATION. You need to turn it off manually.

- 4. Check ical status:

$\tt check\_stat\_cal$  command can be run after  $\tt start\_cal$  command to return the calibration status:

- Write 0x200 = 0x01.

- Write 0x201 = 0x00.

- Write 0x202 = 0x00.

- Write 0x203 = 0x97.

Refer to Figure: Loading PMA Configuration Register CHECK\_CAL\_STAT in E-tile Transceiver PHY User Guide.

- 5. Poll on 0x204 and process the following status:

- If 0x204 = 0x91, PMA adaptation in progress

- If 0x204 = 0x80, PMA adaptation done

- If 0x204 = 0xe2, Continuous adaptation is running

- If 0x204 = 0xa2, One time adaptation in progress

#### **Related Information**

- Adaptation Control- Start

- E-tile Transceiver PHY User Guide

## **3. Parameter Settings**

## **3.1. Main Parameters**

You customize the Interlaken IP by specifying parameters in the IP parameter editor.

#### Table 12. General

| Parameter                                | Supported Values                                                         | Default Setting | Description                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------|--------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Meta fame length                         | 128-8192                                                                 | 2048            | Specifies the meta frame length in<br>64-bit (8-byte) words. Must be a<br>power of two.<br>Smaller values shorten the time to<br>achieve lock. Larger values reduce<br>the overhead while transferring<br>data, after the clock data recover<br>(CDR) circuit achieves lock.                                                                                                   |

| Number of lanes                          | 4, 6, 8, 10, 12                                                          | 12              | This parameter specifies the<br>number of lanes available for<br>Interlaken communication.<br>The Interlaken IP supports various<br>combinations of number of lanes<br>and lane rates. Ensure that your<br>parameter settings specify a<br>supported combination. Refer to<br><i>Table: IP Supported Combinations</i><br>of Number of Lanes and Data Rate<br>in this document. |

| Data rate                                | 6.25, 10.3125,<br>12.5, 25.3, 25.8<br>and 26.5625 <sup>(4)</sup><br>Gbps | 10.3125 Gbps    | This parameter specifies the data<br>rate on each lane.<br>The Interlaken IP supports various<br>combinations of number of lanes<br>and lane rates. Ensure that your<br>parameter settings specify a<br>supported combination. Refer to<br><i>Table: IP Supported Combinations</i><br>of Number of Lanes and Data Rate<br>in this document.                                    |

| Transceiver reference clock<br>frequency | Multiple                                                                 | 412.5 MHz       | This parameter specifies the<br>expected frequency of the<br>pll_ref_clk input clock.<br>If the actual frequency of the<br>pll_ref_clk input clock does not<br>match the value you specify for<br>this parameter, the design fails in<br>both simulation and hardware.                                                                                                         |

|                                          | 1                                                                        |                 | continued                                                                                                                                                                                                                                                                                                                                                                      |

## <sup>(4)</sup> This data rate is only available when you select PAM4 option for **Transceiver Mode** parameter in E-tile variations.

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

3. Parameter Settings UG-20035 | 2020.06.22

| Parameter                            | Supported Values | Default Setting | Descr                                                                                              | iption                                                                                                                                       |

|--------------------------------------|------------------|-----------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                  |                 | Per-Lane Data<br>Rate (Gbps)                                                                       | Valid<br>Frequencies<br>(MHz)                                                                                                                |

|                                      |                  |                 | 6.25                                                                                               | 156.25,<br>195.3125, 250,<br>312.5, 390.625,<br>480.76923 <sup>(6)</sup> ,<br>500 <sup>(5)</sup> , 625 <sup>(5)</sup>                        |

|                                      |                  |                 | 10.3125                                                                                            | 156.25, 206.25,<br>257.8125,<br>322.265625,<br>412.5,<br>491.071428 <sup>(6)</sup> ,<br>515.625 <sup>(5)</sup> ,<br>644.53125 <sup>(5)</sup> |

|                                      |                  |                 | 12.5                                                                                               | 156.25,<br>195.3125, 250,<br>312.5, 390.625,<br>500, 625 <sup>(5)</sup>                                                                      |

|                                      |                  |                 | 25.3                                                                                               | 126.4 <sup>(5)</sup> , 158.0,<br>197.5, 252.8,<br>320.0 <sup>(5)</sup> , 395.0,<br>486.153846 <sup>(6)</sup> ,<br>505.6 <sup>(5)</sup>       |

|                                      |                  |                 | 25.8                                                                                               | 159.135802,<br>201.40625,<br>250.291262 <sup>(5)</sup> ,<br>322.25,<br>402.8125,<br>495.769231 <sup>(6)</sup> ,<br>500.582524 <sup>(5)</sup> |

|                                      |                  |                 | 26.5625 <sup>(7)</sup>                                                                             | 156.25,<br>210.813492,<br>312.5, 390.625,<br>491.898148                                                                                      |

| Enable Interlaken Look-aside<br>mode | On/Off           | Off             | IP core in Interlal<br>mode. This option<br>in E-tile device va                                    | n is only available<br>ariations.                                                                                                            |

|                                      |                  |                 | Note: This mode<br>in non-strip                                                                    | is only supported<br>per mode.                                                                                                               |

| Enable M20K ECC support              | On/Off           | Off             | This parameter sp<br>your Interlaken II<br>supports the ECC<br>M20K memory bl<br>configured as par | P variation<br>feature in the<br>ocks that are<br>t of the IP.                                                                               |

|                                      |                  |                 | You can turn this<br>enable single-erro<br>adjacent-error co<br>adjacent-error de                  | or correct, double-<br>rrect, and triple-<br>tect ECC                                                                                        |

|                                      |                  |                 |                                                                                                    | continued                                                                                                                                    |

- <sup>(5)</sup> Only available in H-tile device variations.

- <sup>(6)</sup> Only available in NRZ E-tile device variations.

- <sup>(7)</sup> Only available in PAM4 E-tile device variations.

| Parameter                                          | Supported Values | Default Setting | Description                                                                                                                                                                                                                                                                             |

|----------------------------------------------------|------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    |                  |                 | functionality in the M20K memory<br>blocks configured in your IP. This<br>feature enhances data reliability<br>but increases latency and resource<br>utilization.<br>The IP does not include M20K ECC<br>support when you turn on <b>Enable</b><br><b>Interlaken Look-aside</b> option. |

| Enable Native PHY Debug<br>Master Endpoint (NPDME) | On/Off           | Off             | This parameter specifies whether<br>your Interlaken IP variation<br>supports the NPDME feature.<br>This parameter exposes debugging<br>features of the Intel Stratix 10<br>Native PHY IP that specifies the<br>transceiver settings in the<br>Interlaken IP.                            |

## Table 13.In-Band Flow Control

The parameters in table below are not available when you turn on **Enable Interlaken Look-aside mode** parameter.

| Parameter                                  | Supported Values | Default Setting | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Include in-band flow control functionality | On/Off           | Off             | This parameter specifies whether<br>your Interlaken IP includes an in-<br>band flow control block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Number of calender pages                   | 1, 2, 4, 8, 16   | 1               | This parameter specifies the<br>number of 16-bit pages of in-band<br>flow control data that your<br>Interlaken IP supports. This<br>parameter is available if you turn<br>on <b>Include in-band flow control</b><br>functionality.<br>Each 16-bit calendar page includes<br>16 in-band flow control bits. The<br>application determines the<br>interpretation of the in-band flow<br>control bits. The IP supports a<br>maximum of 256 channels with in-<br>band flow control.<br>If your design requires a different<br>number of pages, select the lowest<br>supported number of pages which<br>is larger than the number required,<br>and ignore any unused pages. For<br>example, if your configuration<br>requires three in-band flow control<br>calendar pages, you can set this<br>parameter to 4 and use pages 3, 2,<br>and 1 while ignoring page 0. |

## Table 14.Transceiver Settings

| Transceiver Settings Parameter | Supported Values       | Default Setting | Description                                                                                                                                                                                                                          |

|--------------------------------|------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transceiver tile               | L-tile, H-tile, E-tile | H-tile          | Specifies the transceiver tile on<br>your target Intel Stratix 10 device.<br>The <b>Device</b> setting of the Intel<br>Quartus Prime Pro Edition project<br>in which you generate the IP<br>determines the transceiver tile<br>type. |

|                                |                        |                 | continued                                                                                                                                                                                                                            |

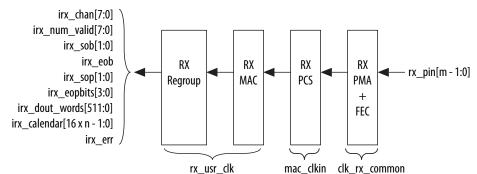

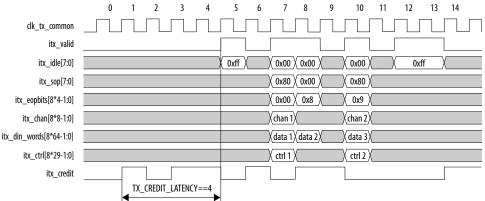

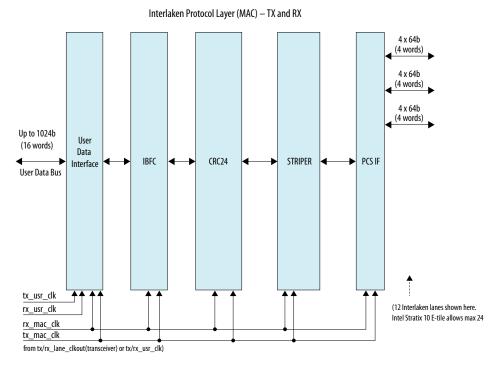

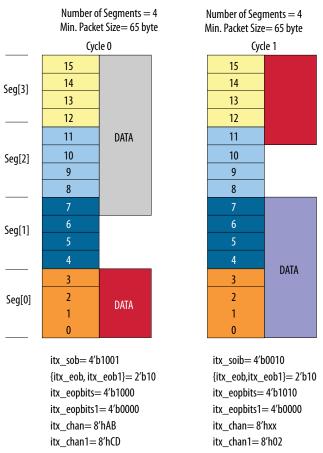

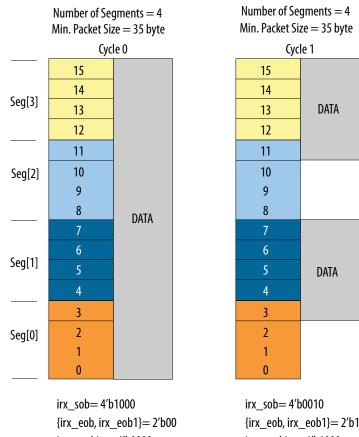

| Transceiver Settings Parameter                                  | Supported Values | Default Setting   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |