# Hybrid Memory Cube Controller IP Core User Guide

Last updated for Quartus Prime Design Suite: 16.0 **UG-01152** 2016.05.02

101 Innovation Drive San Jose, CA 95134 www.altera.com

# Contents

| About the Altera Hybrid Memory Cube Controller IP Core | 1-1 |

|--------------------------------------------------------|-----|

| HMC Controller IP Core Supported Features              |     |

| HMC Controller IP Core Supported HMC Transaction Types |     |

| Device Family Support                                  |     |

| IP Core Verification                                   | 1-5 |

| Simulation                                             |     |

| Hardware Testing                                       |     |

| Performance and Resource Utilization                   |     |

| Device Speed Grade Support                             | 1-7 |

| Release Information                                    | 1-7 |

|                                                        |     |

| Getting Started with the HMC Controller IP Core |      |

|-------------------------------------------------|------|

| Licensing IP Cores                              |      |

| OpenCore Plus IP Evaluation                     |      |

| Specifying IP Core Parameters and Options       | 2-2  |

| HMC Controller IP Core Parameters               |      |

| RX Mapping and TX Mapping Parameters            | 2-7  |

| Files Generated for Altera IP Cores             | 2-10 |

| Integrating Your IP Core in Your Design         |      |

| Pin Constraints                                 | 2-11 |

| Required External Blocks                        | 2-12 |

| Simulating Altera IP Cores                      | 2-17 |

|                                                 |      |

| Functional Description                        |  |

|-----------------------------------------------|--|

| High Level Block Diagram                      |  |

| Interfaces Overview                           |  |

| Application Interfaces                        |  |

| HMC Interface                                 |  |

| Interface to External I <sup>2</sup> C Master |  |

| Control and Status Register Interface         |  |

| Status and Debug Interface                    |  |

| Transceiver Control Interfaces                |  |

| Clocking and Reset Structure                  |  |

| Initialization and Reset                      |  |

| M20K ECC Support                              |  |

| Flow Control                                  |  |

| Error Detection and Management                |  |

| Testing Features                              |  |

| HMC Controller IP Core Signals4- | - 1 | 1 |

|----------------------------------|-----|---|

|----------------------------------|-----|---|

TOC-2

About the Altera Hybrid Memory Cube Controller IP Core

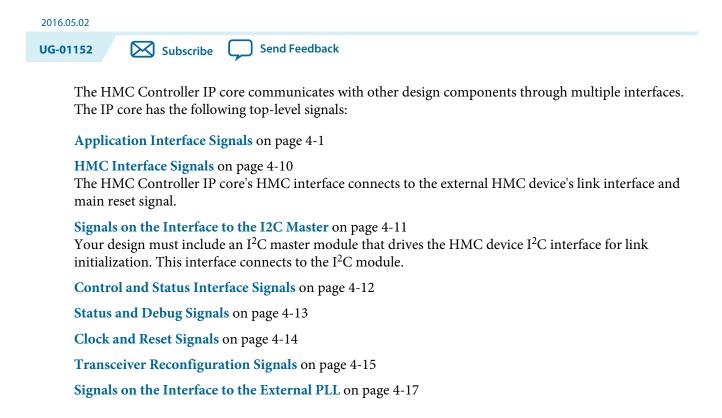

| Application Interface Signals                           | 4-1 |

|---------------------------------------------------------|-----|

| Application Request Interface                           |     |

| Application Response Interface                          |     |

| HMC Controller IP Core Data Path Example                |     |

| HMC Interface Signals                                   |     |

| Signals on the Interface to the I <sup>2</sup> C Master |     |

| Control and Status Interface Signals                    |     |

| Status and Debug Signals                                |     |

| Clock and Reset Signals                                 |     |

| Transceiver Reconfiguration Signals                     |     |

| Signals on the Interface to the External PLL            |     |

## HMC Controller IP Core Register Map......5-1

| CONTROL Register                     | .5-2  |

|--------------------------------------|-------|

| XCVR_STATUS Register                 | .5-3  |

| LANE_STATUS Register                 | .5-4  |

| LINK_STATUS Register                 |       |

| ERROR_RESPONSE Register              | . 5-5 |

| LIMIT_OUTSTANDING_PACKET Register    |       |

| Interrupt Related Registers          |       |

| Error and Retry Statistics Registers |       |

|                                      |       |

##

##

| Additional Information                             | B-1 |

|----------------------------------------------------|-----|

| HMC Controller IP Core User Guide Revision History | B-1 |

| How to Contact Altera                              | B-3 |

| Typographic Conventions                            | B-3 |

Altera Corporation

TOC-3

# About the Altera Hybrid Memory Cube Controller IP Core

## 2016.05.02

UG-01152 Subscribe Send Feedback

The Hybrid Memory Cube (HMC) specification defines a new type of memory device that provides a significant increase in bandwidth and power efficiency over existing memory architectures. The HMC specification targets high performance computers and next-generation networking equipment and provides scalability for a wide range of applications.

The Altera<sup>®</sup> HMC Controller MegaCore<sup>®</sup> IP core enables easy access to external HMC devices. HMC devices provide high bandwidth, reliable access to large amounts of memory with a small form factor, and provide significant system cost savings in high performance, memory intensive applications. The HMC Controller IP core provides a simple user interface through which you can communicate with an external HMC device to incorporate these bandwidth and performance gains in your design.

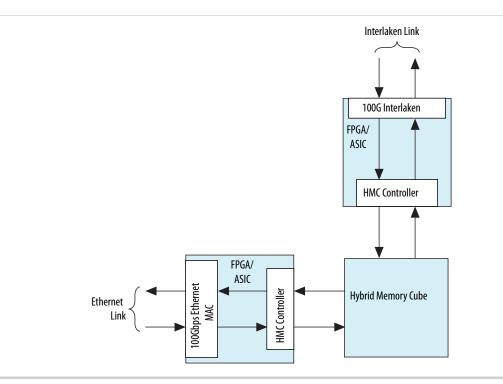

## Figure 1-1: Typical HMC Controller Application

### **Related Information**

HMC Controller IP Core User Guide Archives on page 7-1

<sup>© 2016</sup> Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

1-2

**HMC Controller IP Core Supported Features**

- Hybrid Memory Cube Controller Design Example User Guide

- Introduction to Altera IP Cores Provides general information about all Altera IP cores, including parameterizing, generating, upgrading, and simulating IP.

- Creating Version-Independent IP and Qsys Simulation Scripts Create simulation scripts that do not require manual updates for software or IP version upgrades.

- **Project Management Best Practices** Guidelines for efficient management and portability of your project and IP files.

- HMC Specification 1.1 The HMC specification is available for download from the Hybrid Memory Cube Consortium web page.

# **HMC Controller IP Core Supported Features**

The Altera HMC Controller IP core offers the following features:

- Communicates through Altera high-speed transceivers with an external HMC device compliant with the *HMC Specification 1.1*.

- Communicates with the HMC device at per-lane rates of 10 Gbps or 12.5 Gbps.

- Features Avalon<sup>®</sup> Memory-Mapped (Avalon-MM) interface to access control and status registers.

- Supports selection of a full-width variation that connects to 16 lanes of an HMC device, or a half-width variation that connects to 8 lanes of an HMC device.

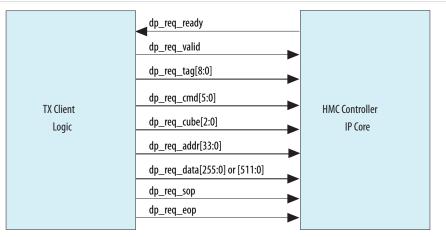

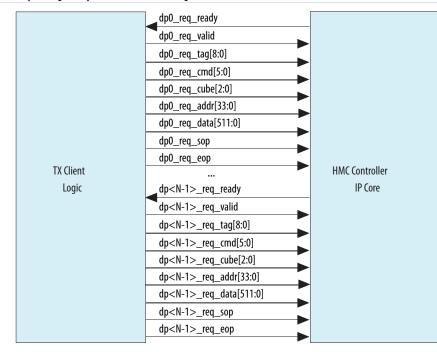

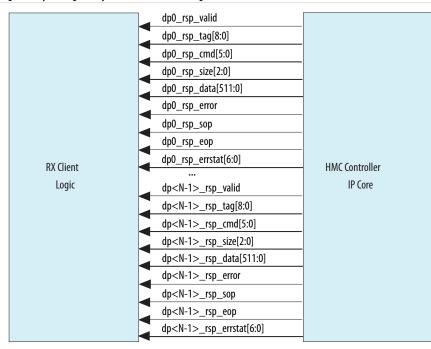

- Full-width IP core variations feature one to four simple 512-bit client data interfaces. Multiple data interfaces provide increased utilization of the HMC link.

- Half-width IP core variations feature a single simple 256-bit client data interface.

- Supports memory READ and WRITE transactions with all valid payload sizes.

- Supports posted and non-posted versions of ATOMIC transactions, BIT WRITE transactions, and WRITE transactions.

- Supports MODE READ and MODE WRITE transactions.

- Supports optional response reordering in full-width variations, to ensure the IP core sends responses on each application response interface in the order it received the requests. When you select this option, the IP core manages the tags, which are not visible on the client interfaces.

- Supports Response Open Loop Mode for receive (RX) flow control to decrease device resource requirements.

- Supports token-based transmit (TX) flow control.

- Supports poisoned packets.

- Supports reordering of transceiver lanes for board-design flexibility.

- Supports link training sequence and provides word alignment, lane alignment, and transceiver status information in real time.

- Provides fast simulation support.

- Provides real-time error statistics.

- Provides hardware and software reset control.

- Optionally supports ADME direct access to transceiver registers through the Altera System Console, for debugging or monitoring PHY signal integrity.

- Provides option to include ECC support in all M20K memory blocks configured in the IP core.

To support multi-link connection to the HMC device in your design, you can configure multiple HMC Controllers to communicate with the same HMC device through separate HMC links.

For the detailed HMC specification refer to the HMC Specification 1.1.

#### **Related Information**

#### **HMC Specification 1.1**

The HMC specification is available for download from the Hybrid Memory Cube Consortium web page.

## HMC Controller IP Core Supported HMC Transaction Types

The Altera HMC Controller IP core supports all HMC transactions.

## HMC Controller To HMC Device Packet Types

The HMC Controller IP core generates the following packet types on the link to the HMC device:

- NULL FLIT

- PRET (single FLIT packet)

- IRTRY (single FLIT packet)

- READ request (single FLIT packet)

- 16-byte WRITE or Posted WRITE request (2-FLIT packet)

- 32-byte WRITE or Posted WRITE request (3-FLIT packet)

- 48-byte WRITE or Posted WRITE request (4-FLIT packet)

- 64-byte WRITE or Posted WRITE request (5-FLIT packet)

- 80-byte WRITE or Posted WRITE request (6-FLIT packet)

- 96-byte WRITE or Posted WRITE request (7-FLIT packet)

- 112-byte WRITE or Posted WRITE request (8-FLIT packet)

- 128-byte WRITE or Posted WRITE request (9-FLIT packet)

- BIT WRITE or Posted BIT WRITE request (2-FLIT packet)

- MODE READ request (single FLIT packet)

- MODE WRITE request (2-FLIT packet)

- Dual 8-byte ADD IMMEDIATE or Posted Dual 8-byte ADD IMMEDIATE request (2-FLIT packet)

- Single 16-byte ADD IMMEDIATE or Posted Single 16-byte ADD IMMEDIATE request (2-FLIT packet)

The HMC Controller IP core operates in the Response Open Loop Mode and therefore does not generate TRET packets.

## HMC Device to HMC Controller Packet Types

The HMC Controller IP core can process the following packet types generated by the HMC device:

- NULL FLIT

- PRET (single FLIT packet)

- TRET (single FLIT packet)

- IRTRY (single FLIT packet)

- ERROR response (single FLIT packet)

- WRITE response (single FLIT packet)

- 16-byte READ response (2-FLIT packet)

- 32-byte READ response (3-FLIT packet)

- 48-byte READ response (4-FLIT packet)

- 64-byte READ response (5-FLIT packet)

- 80-byte READ response (6-FLIT packet)

- 96-byte READ response (7-FLIT packet)

- 112-byte READ response (8-FLIT packet)

- 128-byte READ response (9-FLIT packet)

- MODE READ response (2-FLIT packet)

- MODE WRITE response (single FLIT packet)

The HMC Controller IP core does not define or support any vendor specific packet types.

## **Device Family Support**

The following table lists the device support level definitions for Altera IP cores.

## Table 1-1: Altera IP Core Device Support Levels

## **FPGA Device Families**

**Preliminary support** — The core is verified with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.

**Final support** — The IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.

The following table shows the level of support offered by the HMC Controller IP core for each Altera device family.

## Table 1-2: HMC Controller IP Core Device Family Support

| Device Family             | Support     |

|---------------------------|-------------|

| Arria 10                  | Preliminary |

| All other device families | No support  |

1-5

# **IP Core Verification**

Before releasing a version of the HMC Controller IP core, Altera runs comprehensive regression tests in the current version of the Quartus<sup>®</sup> Prime software. The HMC Controller IP core is tested in simulation and hardware to confirm functionality.

## **Related Information**

- Knowledge Base Errata for HMC Controller IP core Exceptions to functional correctness are documented in the HMC Controller IP core errata.

- Altera IP Release Notes Changes to the HMC Controller IP core are noted in the Altera IP Release Notes starting from the Quartus II software v15.0.

## Simulation

Altera performs the following tests on the HMC Controller IP core in simulation, using the Micron HMC BFM:

- · Constrained random tests that cover randomized legal payload sizes and contents

- Assertion based tests to confirm proper behavior of the IP core with respect to the specification

- Extensive coverage of packet retry functionality

Constrained random techniques generate appropriate stimulus for the functional verification of the IP core. Altera monitors line, expression, and assertion coverage metrics to ensure that all important features are verified.

## **Hardware Testing**

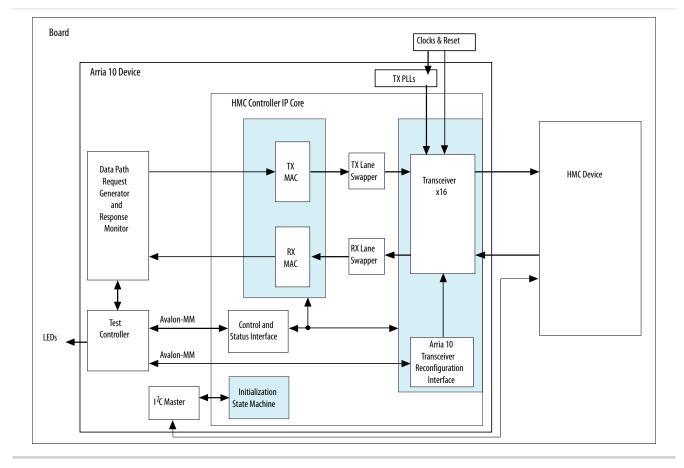

Altera performs hardware testing of the key functions of the HMC Controller IP core. The Altera hardware tests of the HMC Controller IP core also ensure reliable solution coverage for hardware related areas such as performance, link initialization, and reset recovery.

Altera performs hardware testing on the Arria 10 GX FPGA Development Kit with an HMC daughter card. A Micron HMC 15G-SR device on the daughter card is connected to the development board through FMC connectors.

About the Altera Hybrid Memory Cube Controller IP Core

# **Performance and Resource Utilization**

## Table 1-3: HMC Controller IP Core FPGA Resource Utilization

Typical resource utilization for an HMC Controller IP core configured with a data rate of 10 Gbps, using the Quartus Prime software v16.0, with the following IP core features turned off:

- ADME support

- M20K ECC support

The numbers of ALMs and logic registers are rounded up to the nearest 100. The numbers of ALMs, before rounding, are the **ALMs needed** numbers from the Quartus Fitter Report.

|            | IP Core Variation      |                    | Resource Utilization |                              |             |

|------------|------------------------|--------------------|----------------------|------------------------------|-------------|

| Link Width | Response<br>Reordering | Number of<br>Ports | ALMs Needed          | Dedicated Logic<br>Registers | M20K Blocks |

|            | Off                    | 1                  | 24400                | 48200                        | 51          |

|            |                        | 2                  | 29200                | 58400                        | 87          |

|            |                        | 3                  | 34100                | 68600                        | 123         |

| Full-width |                        | 4                  | 38900                | 78800                        | 158         |

| r'un-widun | On                     | 1                  | 29900                | 59400                        | 55          |

|            |                        | 2                  | 37000                | 76200                        | 93          |

|            |                        | 3                  | 44200                | 93100                        | 132         |

|            |                        | 4                  | 51300                | 109900                       | 170         |

| Half-width |                        |                    | 13400                | 24000                        | 37          |

### **Related Information**

- Fitter Resources Reports in the Quartus Prime Help Information about Quartus Prime resource utilization reporting, including ALMs needed.

- Quartus Prime Standard Edition Handbook, Volume 1: Design and Synthesis

# **Device Speed Grade Support**

## Table 1-4: Minimum Recommended Device Family Speed Grades

Altera recommends that you configure the HMC Controller IP core only in the device speed grades listed in the table, or any faster (lower numbered) device speed grades that are available.

Altera does not support configuration of this IP core in slower (higher numbered) device speed grades.

|               | IP Core Variation: Lane Rate |           |  |

|---------------|------------------------------|-----------|--|

| Device Family | 10 Gbps                      | 12.5 Gbps |  |

| Arria 10      | E1, I1, E2, I2               | E1, I1    |  |

## **Release Information**

## Table 1-5: HMC Controller IP Core Current Release Information

| Item          | Value                                                |

|---------------|------------------------------------------------------|

| Version       | 16.0                                                 |

| Release Date  | May 2016                                             |

| Ordering Code | Full-width: IP-HMCSR15FW<br>Half-width: IP-HMCSR15HW |

| Vendor ID     | 6AF7                                                 |

# Getting Started with the HMC Controller IP Core 2

2016.05.02

UG-01152

Subscribe Send Feedback

The following information explains how to install, parameterize, and simulate the Altera Hybrid Memory Cube Controller IP core.

## Licensing IP Cores on page 2-2

The HMC Controller IP core is available with the Quartus Prime software in the Altera IP Library.

## Specifying IP Core Parameters and Options on page 2-2

The HMC Controller IP core supports the standard customization and generation process. This IP core is not supported in Qsys.

## HMC Controller IP Core Parameters on page 2-3

The HMC Controller parameter editor provides the parameters you can set to configure the HMC Controller IP core and simulation testbenches.

## Files Generated for Altera IP Cores on page 2-10

The Quartus Prime software generates multiple files during generation of your IP core variation.

## Integrating Your IP Core in Your Design on page 2-11

To ensure the HMC Controller IP core functions correctly in hardware, you must connect additional blocks to your IP core and assign device pins in order.

## Simulating Altera IP Cores on page 2-17

The Quartus Prime software supports RTL and gate-level design simulation of Altera IP cores in supported EDA simulators. Simulation involves setting up your simulator working environment, compiling simulation model libraries, and running your simulation.

## **Related Information**

- HMC Controller IP Core Design Example on page 6-1 The HMC Controller design example provides an example of how to connect your IP core with an external I<sup>2</sup>C master module and an external TX PLL.

- Introduction to Altera IP Cores Provides general information about all Altera IP cores, including parameterizing, generating, upgrading, and simulating IP.

- Creating Version-Independent IP and Qsys Simulation Scripts Create simulation scripts that do not require manual updates for software or IP version upgrades.

- **Project Management Best Practices** Guidelines for efficient management and portability of your project and IP files.

ow part of Intel

<sup>© 2016</sup> Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Licensing IP Cores**

The Altera IP Library provides many useful IP core functions for your production use without purchasing an additional license. Some Altera MegaCore IP functions require that you purchase a separate license for production use. However, the OpenCore<sup>®</sup> feature allows evaluation of any Altera IP core in simulation and compilation in the Quartus Prime software. After you are satisfied with functionality and performance, visit the Self Service Licensing Center to obtain a license number for any Altera product.

Figure 2-1: IP Core Installation Path

| acds                                                                |  |

|---------------------------------------------------------------------|--|

|                                                                     |  |

| <b>ip</b> - Contains the Altera IP Library and third-party IP cores |  |

| altera - Contains the Altera IP Library source code                 |  |

| IP core name> - Contains the IP core source files                   |  |

**Note:** The default IP installation directory on Windows is *drive*:*lalteraiversion number*; on Linux the IP installation directory is *<i>chome directoryjalteraiversion number*.

## **OpenCore Plus IP Evaluation**

Altera's free OpenCore Plus feature allows you to evaluate licensed MegaCore IP cores in simulation and hardware before purchase. You only need to purchase a license for MegaCore IP cores if you decide to take your design to production. OpenCore Plus supports the following evaluations:

- Simulate the behavior of a licensed IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

OpenCore Plus evaluation supports the following two operation modes:

- Untethered—run the design containing the licensed IP for a limited time.

- Tethered—run the design containing the licensed IP for a longer time or indefinitely. This requires a connection between your board and the host computer.

**Note:** All IP cores that use OpenCore Plus time out simultaneously when any IP core in the design times out.

## **Related Information**

- Altera Licensing Site

- Altera Software Installation and Licensing Manual

# **Specifying IP Core Parameters and Options**

The HMC Controller parameter editor allows you to quickly configure your custom IP variation. Use the following steps to specify IP core options and parameters in the Quartus Prime software.

- In the IP Catalog (Tools > IP Catalog), under Memory Interfaces and Controllers, locate and double-click the name of the IP core to customize. The parameter editor appears.

- 2. Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named *<your\_ip>.qsys*. Click **OK**.

- **3.** Specify the parameters and options for your IP variation in the parameter editor. Refer to the Parameters section for information about specific IP core parameters.

- 4. Click Generate HDL, the Generation dialog box appears.

- **5.** To generate a simulation model of the HMC Controller IP core, under **Simulation** > **Create Simulation Model**, select **Verilog** HDL.

- **6.** Specify other output file generation options, and then click **Generate**. The IP variation files generate according to your specifications.

- 7. Click Finish. The parameter editor adds the top-level .qsys file to the current project automatically. If you are prompted to manually add the .qsys file to the project, click Project > Add/Remove Files in Project to add the file.

- **8.** After generating and instantiating your IP variation, make appropriate pin assignments to connect ports.

## **HMC Controller IP Core Parameters**

The HMC Controller parameter editor provides the parameters you can set to configure the HMC Controller IP core and simulation testbenches.

The HMC Controller parameter editor includes an **Example Design** tab. For information about that tab, refer to the **Hybrid Memory Controller Design Example User Guide**.

## Table 2-1: HMC Controller IP Core Parameters

Parameters for customizing the HMC Controller IP core in the IP tab of the HMC Controller parameter editor.

| Parameter | Туре    | Range                                         | Default Setting | Parameter Description                                                        |

|-----------|---------|-----------------------------------------------|-----------------|------------------------------------------------------------------------------|

| Lanes     | Integer | • 8<br>• 16                                   | 16              | Selects half-width (8 lanes) or<br>full-width (16 lanes) function-<br>ality. |

| Data rate | String  | <ul><li> 10 Gbps</li><li> 12.5 Gbps</li></ul> | 10 Gbps         | Selects the data rate on each lane.                                          |

| Parameter                 | Туре    | Range                                                                                                                                                                                                                          | Default Setting | Parameter Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDR<br>reference<br>clock | String  | <ul> <li>125 MHz</li> <li>156.25 MHz</li> </ul>                                                                                                                                                                                | 125 MHz         | Selects the frequency of the<br>input reference clock for the RX<br>CDR PLL. You must drive the<br>rx_cdr_refclk0 input signal at<br>the frequency you specify for<br>this parameter.<br>In addition, your design must<br>derive this clock, the external<br>transceiver TX PLL reference<br>clock, and the REFCLKP and<br>REFCLKN input signals of the<br>external HMC device from the<br>same clock source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Ports                     | Integer | <ul> <li>1</li> <li>2 (available<br/>only for full-<br/>width<br/>variations)</li> <li>3 (available<br/>only for full-<br/>width<br/>variations)</li> <li>4 (available<br/>only for full-<br/>width<br/>variations)</li> </ul> | 1               | <ul> <li>Number of ports (data path<br/>interfaces). This parameter is<br/>useful only for full-width<br/>variations. Half-width variations<br/>have a single port.</li> <li>Increasing the number of ports<br/>increases utilization of the<br/>Hybrid Memory Cube,<br/>increasing efficiency.</li> <li>If you specify more than one<br/>port, each port is assigned a<br/>range of tags.</li> <li>If you specify 2 ports, port 0<br/>must use tags in the range 0<br/>to 255, and port 1 must use<br/>tags in the range 256 to 511.</li> <li>If you specify 3 ports, port 0<br/>must use tags in the range 0<br/>to 175, port 1 must use tags<br/>in the range 176 to 351, and<br/>port 2 must use tags in the<br/>range 352 to 511.</li> <li>If you specify 4 ports, port 0<br/>must use tags in the range 0<br/>to 127, port 1 must use tags<br/>in the range 128 to 255, port<br/>2 must use tags in the range<br/>256 to 383, and port 3 must<br/>use tags in the range 384 to<br/>511.</li> </ul> |

Getting Started with the HMC Controller IP Core

2-5

| Parameter                | Туре            | Range                                   | Default Setting    | Parameter Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|-----------------|-----------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Response re-<br>ordering | Boolean         | <ul> <li>True</li> <li>False</li> </ul> | False              | Specifies whether the IP core<br>ensures that responses appear<br>on each data response interface<br>in the order the original<br>requests arrived on the<br>corresponding request interface.<br>If you turn on this feature, the<br>IP core manages tags internally.<br>In that case tags are not<br>available on the data interfaces.<br>Turning on this feature can<br>increase round-trip latency.<br>This parameter is available only<br>for full-width variations. |

| RX mapping               | 64-bit<br>value |                                         | 0xFEDCBA9876543210 | Selects the RX lane mapping.<br>Use caution in modifying this<br>parameter. Refer to <b>RX</b><br><b>Mapping and TX Mapping</b><br><b>Parameters</b> on page 2-7.                                                                                                                                                                                                                                                                                                        |

| TX mapping               | 64-bit<br>value |                                         | 0xFEDCBA9876543210 | Selects the TX lane mapping.<br>Use caution in modifying this<br>parameter. Refer to <b>RX</b><br><b>Mapping and TX Mapping</b><br><b>Parameters</b> on page 2-7.                                                                                                                                                                                                                                                                                                        |

| Parameter                                                    | Туре    | Range                                   | Default Setting | Parameter Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------|---------|-----------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable<br>ADME and<br>Optional<br>Reconfigura-<br>tion Logic | Boolean | <ul> <li>True</li> <li>False</li> </ul> | False           | <ul> <li>Specifies whether the IP core turns on the ADME feature in the embedded Arria 10 Native PHY IP core that configures the transceivers. Turning on this parameter turns on the following Arria 10 PHY features:</li> <li>Enable Altera Debug Master Endpoint (ADME)</li> <li>Enable capability registers</li> <li>Enable control and status registers</li> <li>Enable PRBS soft accumulators</li> <li>Note: The Share reconfiguration interface PHY parameter is always turned on for this IP core.</li> <li>The ADME feature enables Native PHY register programming with the Altera System Console, and optional reconfiguration logic. For more information, refer to the Arria 10 Transceiver PHY User Guide.</li> </ul> |

| Enable<br>M20K ECC<br>support                                | Boolean | • True<br>• False                       | False           | Specifies whether the IP core<br>supports the ECC feature in the<br>Arria 10 M20K memory blocks<br>that are configured as part of the<br>IP core.<br>You can turn on this parameter<br>to enhance data reliability by<br>enabling single-error correction,<br>double-adjacent-error<br>correction, and triple-adjacent-<br>error detection ECC function-<br>ality in the M20K memory<br>blocks configured in your IP<br>core. Turn off this parameter to<br>decrease latency and resource<br>utilization.                                                                                                                                                                                                                           |

Getting Started with the HMC Controller IP Core

#### **Related Information**

- Arria 10 Transceiver PHY User Guide Provides information about the Arria 10 ADME feature.

- Embedded Memory Blocks in Arria 10 Devices Provides information about the Arria 10 M20K block ECC feature.

## **RX Mapping and TX Mapping Parameters**

The HMC Controller IP core provides the **RX mapping** and **TX mapping** parameters for flexibility in board design.

The default values of these parameters specify the correct IP core behavior when the HMC device LxTX[<i>] output signal connects to the HMC Controller IP core hmc\_lxrx[<i>] input port, and the LxRX[<i>] input signal connects to the HMC Controller IP core hmc\_lxtx[<i>] output port, for each <i>.

However, if your design constraints prevent you from connecting these signals as expected, you can instead modify one or both HMC Controller IP core mapping parameters to accommodate the non-standard connection.

**Note:** The Quartus Prime Fitter prevents you from mapping the HMC Controller IP core lanes to Arria 10 device transceiver channels out of order. Therefore, these two parameters only compensate for out-of-order connections on the board between the Arria 10 transceiver pins and the HMC device ports.

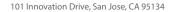

## Figure 2-2: Default RX and TX Mapping Parameter Values

FPG A Hybrid Memory Cube **HMC** Controller hmc\_lxrx[F] LxTX[F] hmc\_lxtx[F] LxRX[F] hmc\_lxrx[E] LxTX[E] hmc\_lxtx[E] LxRX[E] hmc\_lxrx[D] LxTX[D] hmc\_lxtx[D] LxRX[D] hmc\_lxrx[C] LxTX[C] hmc\_lxtx[C] LxRX[C] . . . . . . . . . hmc\_lxrx[3] LxTX[3] LxRX[3] hmc\_lxtx[3] hmc\_lxrx[2] LxTX[2] hmc\_lxtx[2] LxRX[2] hmc\_lxrx[1] LxTX[1] hmc\_lxtx[1] LxRX[1] hmc\_lxrx[0] LxTX[0] hmc\_lxtx[0] LxRX[0]

**RX mapping** value 0xFEDCBA9876543210 **TX mapping** value 0xFEDCBA9876543210

#### 2-8 RX Mapping and TX Mapping Parameters

If the HMC device LxTX[<i>] output signal connects to the HMC Controller IP core hmc\_lxrx[<k>] input port, you must set the value in bits [(4<i>+3):(4<i>)] (nibble <i>) of the **RX mapping** parameter to 4'h<k>. Therefore, the default value of the **RX mapping** parameter is 0xFEDCBA9876543210, indicating that LxTX[F] connects to hmc\_lxrx[F], LxTX[E] connects to hmc\_lxrx[E], and so on.

If the HMC device LxRX[<i>] input signal connects to the HMC Controller IP core hmc\_lxtx[<k>] input port, you must set the value in bits [(4<i>+3):(4<i>)] (nibble <i>) of the **TX mapping** parameter to 4'h<k>. Therefore, the default value of the **TX mapping** parameter is 0xFEDCBA9876543210, indicating that LxRX[F] connects to hmc\_lxtx[F], LxRX[E] connects to hmc\_lxtx[E], and so on.

## Example: Non-Default RX Mapping Parameter Value

## Table 2-2: Non-Default RX Connections

| HMC Device Output Signal | IP Core Input Signal |

|--------------------------|----------------------|

| LxTX[2]                  | hmc_lxrx[0]          |

| LxTX[1]                  | hmc_lxrx[2]          |

| LxTX[0]                  | hmc_lxrx[1]          |

Getting Started with the HMC Controller IP Core

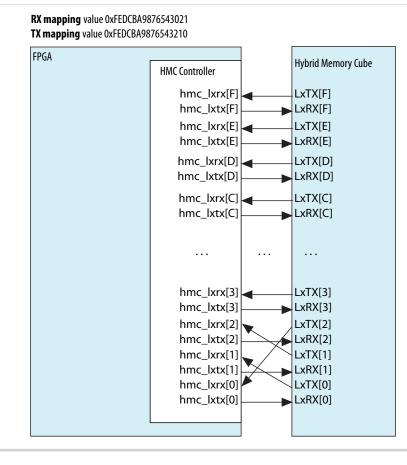

### Figure 2-3: Non-Default RX Mapping Parameter Value Example

If you connect the IP core hmc\_lxrx[2:0] input signals according to the table, and connect all other IP core hmc\_lxrx[<i>] input ports to the corresponding HMC device LxTX[<i>] output ports, you would set the value of the **RX mapping** parameter to 0xFEDCBA9876543**021** to compensate for the non-standard connection.

**Note:** The **RX mapping** parameter specifies the HMC device lane by position and the IP core lane by value. The figure illustrates a mapping parameter value of 0xFED......43021 and not a value of 0xFED.....43102.

## **Example: Non-Default TX Mapping Parameter Value**

## Table 2-3: Non-Default TX Connections

| HMC Device Input Signal | IP Core Output Signal |  |

|-------------------------|-----------------------|--|

| LxRX[2]                 | hmc_lxtx[0]           |  |

| LxRX[1]                 | hmc_lxtx[2]           |  |

| LxRX[0]                 | hmc_lxtx[1]           |  |

2-9

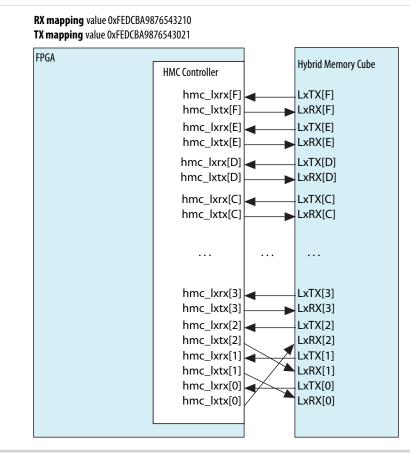

### Figure 2-4: Non-Default TX Mapping Parameter Value Example

If you connect the HMC Controller IP core hmc\_lxtx[2:0] output signals according to the table, and connect all other IP core hmc\_lxtx[<i>] output ports to the corresponding HMC device LxRX[<i>] input ports, you would set the value of the **TX mapping** parameter to 0xFEDCBA9876543**021** to compensate for the non-standard connection.

**Note:** The **TX mapping** parameter specifies the HMC device lane by position and the IP core lane by value. The figure illustrates a mapping parameter value of 0xFED.....43021 and not a value of 0xFED.....43102.

Use caution in modifying these parameters. In loopback configurations, you must ensure the **RX mapping** and **TX mapping** parameters specify reversed mappings. Otherwise, the IP core downstream of the RX lane swapper appears to receive data on the wrong lanes.

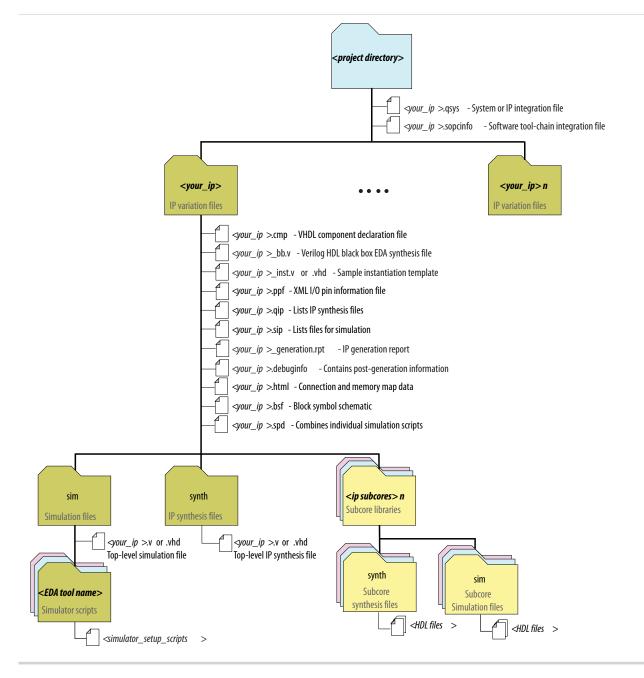

## **Files Generated for Altera IP Cores**

The Quartus Prime software generates multiple files during generation of your IP core variation.

Getting Started with the HMC Controller IP Core

### Figure 2-5: IP Core Generated Files

## Integrating Your IP Core in Your Design

To ensure the HMC Controller IP core functions correctly in hardware, you must connect additional blocks to your IP core and assign device pins in order.

## **Pin Constraints**

Getting Started with the HMC Controller IP Core

**Altera Corporation**

#### 2-12 Required External Blocks

When you integrate your HMC Controller IP core instance in your design, you must make appropriate pin assignments. You can create a virtual pin to avoid making specific pin assignments for top-level signals while you are simulating and not ready to map the design to hardware.

When you are ready to map the design to hardware, you must enforce the following constraints:

- Adjacent HMC Controller lanes must map to adjacent Altera device pins. You cannot swap the lane order by mapping lanes to other Altera device pins. Instead, use the **RX mapping** and **TX mapping** parameters to compensate for board design issues.

- The lanes of an HMC Controller IP core must be configured in no more than three transceiver blocks. To enforce this constraint, you must configure IP core lanes in transceiver channels with the following restrictions:

- Lane 0 of a full-width HMC Controller IP core must map to channel 0, 1, or 2 of a transceiver block.

- If Lane 0 maps to channel 0, then HMC Controller Lane 1 must map to channel 1 of the same transceiver block (transceiver block N), and Lane 15 maps to channel 3 of the transceiver block N+2.

- If Lane 0 maps to channel 1, then HMC Controller Lane 1 must map to channel 2 of the same transceiver block (transceiver block N), and Lane 15 maps to channel 4 of the transceiver block N+2.

- If Lane 0 maps to channel 2, then HMC Controller Lane 1 must map to channel 3 of the same transceiver block (transceiver block N), and Lane 15 maps to channel 5 of the transceiver block N+2.

- Lane 0 of a half-width HMC Controller IP core can map to any channel. If it maps to any of channels 0, 1, 2, 3, or 4, the IP core lanes are configured in two transceiver blocks.

## **Required External Blocks**

To ensure the HMC Controller IP core functions correctly in hardware, you must connect additional blocks to your IP core.

The HMC Controller IP core requires that you define and instantiate the following additional modules:

- External PLL IP core to configure transceiver TX PLL for all of the HMC lanes. Although the hardware these IP cores configure might physically be part of the device transceiver, you must instantiate them in software separately from the HMC Controller IP core. This requirement supports the configuration of multiple Altera IP cores using the same transceiver block in the device.

- An external I<sup>2</sup>C master module in your design. Your design must include this module to initialize the HMC device to which your IP core connects.

Getting Started with the HMC Controller IP Core

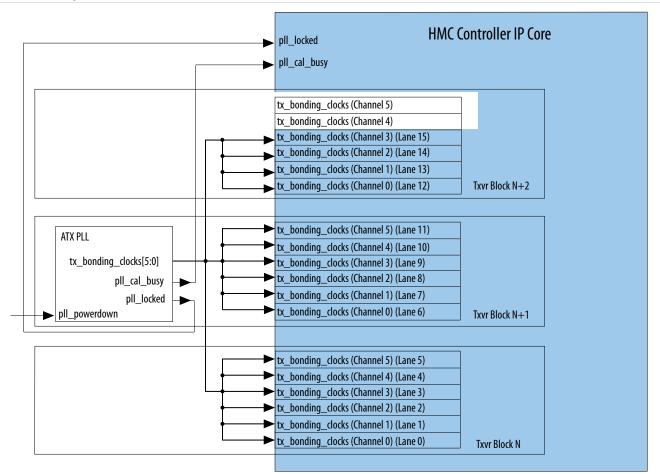

## **Figure 2-6: Required External Blocks**

The required external blocks appear darker than the other blocks in the figure. The external TX PLL IP core configures an ATX PLL in the device transceiver or an fPLL in Transceiver mode.

## Adding the External PLL

The HMC Controller IP core requires that you generate and connect an external transceiver PLL IP core. You must generate the PLL IP core required to clock the transceiver channels that are configured as HMC Controller IP core lanes. The ATX PLL IP core configures the transceiver PLL in the transceiver in hardware, but you must generate the transceiver PLL IP core separately from the HMC Controller IP core in software. You can also configure an fPLL in transceiver mode. If you do not generate and connect the transceiver PLL IP core, the HMC Controller IP core does not function correctly in hardware.

You can use the IP Catalog to generate the external PLL IP core that configures a transceiver PLL on the device. In the IP Catalog, select Arria 10 Transceiver ATX PLL or Arria 10 fPLL.

#### 2-14 Adding the External PLL

In the transceiver PLL parameter editor, you must follow the instructions in the *Arria 10 Transceiver PHY User Guide* to configure the PLL IP core in the xN bonding configuration. In addition, you must set the following parameter values:

- **PLL output frequency** to one half of the per-lane data rate of the IP core variation. The transceiver performs dual edge clocking, using both the rising and falling edges of the input clock from the PLL. Therefore, this PLL output frequency setting drives the transceiver with the correct clock for the lanes that connect to the HMC device.

- PMA interface width to 32.

- PLL integer reference clock frequency (ATX PLL) or Desired reference clock frequency (fPLL).

Note: The HMC Controller IP core does not support PLL feedback compensation bonding.

Altera recommends that you specify 125 MHz, 156.25 MHz, or 166.67 MHz. You can theoretically specify any reference clock frequency from which the PLL can generate the required output clock frequency. However, you must drive this TX PLL and the RX CDR PLL (rx\_cdr\_refclk0 input signal to the HMC Controller IP core) and the HMC device reference clock input signals (REFCLKP and REFCLKN) from the same clock source.

**Note:** You must drive the external PLL reference clock input signal at the frequency you specify for this parameter.

In xN bonding mode, a single PLL is sufficient to drive the channels in the configured transceiver blocks. Recall that your HMC link TX serial lanes must be configured in order in adjacent physical transceiver channels so that these lanes configure a maximum of three transceiver blocks. You can view I/O constraints that enforce these requirements in the design example Quartus Settings File **hmcc\_ example.qsf** provided with the HMC Controller IP core.

The PLL output connects directly to the x6 network for its transceiver block and drives additional transceiver blocks through the xN clock network.

Getting Started with the HMC Controller IP Core

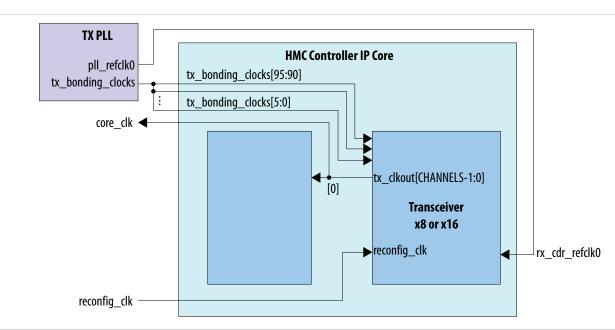

## Figure 2-7: Transceiver PLL Connections Example with xN Bonding Scheme

Example connections between a full-width HMC Controller IP core and a single ATX PLL IP core in xN bonding mode.

You must connect the external PLL signals and the HMC Controller IP core transceiver TX PLL interface signals according to the following rules:

| HMC Controller Signal                              | Connects to TX PLL Signal                                                                                                                                                                                                              |  |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| tx_bonding_clocks[5:0] input signal for HMC lane N | tx_bonding_clocks[5:0] output vector of PLL IP core for the transceiver block in which lane N is configured.                                                                                                                           |  |

|                                                    | In the case of xN bonding, a single PLL connects to the xN clock network and the tx_bonding_clocks[5:0] input pins for HMC lanes in a different transceiver block from the configured PLL receive the clock from the xN clock network. |  |

| pll_locked input signal                            | pll_locked output signal of the external PLL for all of the HMC lanes.                                                                                                                                                                 |  |

| pll_cal_busy input signal                          | pll_cal_busy output signal of the external PLL for all of the HMC lanes.                                                                                                                                                               |  |

Getting Started with the HMC Controller IP Core

**Altera Corporation**

#### 2-16 Adding the External I2C Master Module

User logic must provide the AND and OR functions and connections.

#### **Related Information**

- External PLL Interface on page 3-4

- Signals on the Interface to the External PLL on page 4-17

- HMC Controller IP Core Design Example on page 6-1 The HMC Controller design example provides an example of how to connect an external PLL to your HMC Controller IP core.

- **Pin Constraints** on page 2-11 Describes the requirement that your IP core lanes configure a maximum of three transceiver blocks.

- Arria 10 Transceiver PHY User Guide

Information about the bonding configurations and the correspondence between PLLs and transceiver channels, and information about how to configure an external PLL for your own design. You specify the bonding mode in the PLL parameter editor.

## Adding the External I<sup>2</sup>C Master Module

The HMC Controller IP core requires that you instantiate an external I<sup>2</sup>C master module in your design. Your design must include this module to initialize the HMC device to which your IP core connects.

The I<sup>2</sup>C master module in your system must load the HMC device configuration registers according to the initialization requirements of the specific HMC device in your system.

The HMC specification requires that you set the HMC device REGISTER REQUEST commands register to the value of Init Continue after sending the commands to initialize the HMC. Therefore, the I<sup>2</sup>C master module must set this register to indicate successful completion of the HMC device configuration register load sequence.

In addition, the I<sup>2</sup>C master module must provide the following two signals to connect to the HMC Controller IP core:

- An input signal that accepts requests to load the configuration registers of the HMC device. You must connect this signal to the HMC Controller IP core i2c\_load\_registers output signal. If multiple HMC Controller IP cores connect to the same HMC device, you must connect this input signal to the AND of the individual HMC Controller IP core i2c\_load\_registers output signals. You must provide the AND function.

- An output signal that indicates successful completion of the configuration register load sequence. The I<sup>2</sup>C master must implement this signal with the following behavior:

- 1. Deassert this signal when coming out of reset.

- 2. Assert this signal after writing Init Continue to the HMC device REGISTER REQUEST commands register.

- 3. Deassert this signal in response to the falling edge of the input signal described above.

You must connect this signal to the HMC Controller IP core i2c\_registers\_loaded input signal. If multiple HMC Controller IP cores connect to the same HMC device, you must connect this signal to the i2c\_registers\_loaded signals of all of the HMC Controller IP cores.

For information about the required register configuration sequence, you must refer to the data sheet of the HMC device that is connected to your HMC Controller IP core. Recall that the HMC Controller IP core operates in Response Open Loop Mode, and you must configure the HMC device to communicate correctly with the IP core in this mode. In addition, because the IP core does not support the TGA field,

you must configure the HMC device to respond to every non-posted Write request with a Write response packet.

#### **Related Information**

- HMC Controller IP Core Design Example on page 6-1 The HMC Controller design example provides an example I<sup>2</sup>C master module and demonstrates how to connect it to your HMC Controller IP core.

- Interface to External I2C Master on page 3-3

- Signals on the Interface to the I2C Master on page 4-11

Describes the signals on this interface and the four-way handshaking protocol that the HMC Controller IP core implements and that the I<sup>2</sup>C master must implement for correct IP core functionality.

• HMC Specification 1.1

The *Power-On and Initialization* section of the HMC specification describes the initialization sequence requirements.

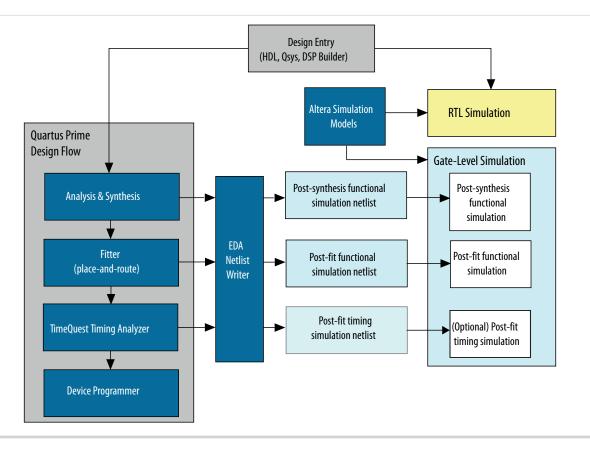

## **Simulating Altera IP Cores**

The Quartus Prime software supports RTL and gate-level design simulation of Altera IP cores in supported EDA simulators. Simulation involves setting up your simulator working environment, compiling simulation model libraries, and running your simulation.

You can use the functional simulation model and the testbench or design example available with your IP core for simulation. When you click the **Generate Example Design** button, the functional simulation model and testbench files are generated in a location you specify. By default, if you do not modify the target location, they are generated in a project subdirectory. This directory includes scripts to compile and run the testbench. For a complete list of models or libraries required to simulate your IP core, refer to the scripts generated with the testbench.

## Figure 2-8: Simulation in Quartus Prime Design Flow

**Note:** Post-fit timing simulation is not supported for 28nm and later device architectures. Therefore, the HMC Controller IP core does not support post-fit timing simulation.

Altera IP supports a variety of simulation models, including simulation-specific IP functional simulation models and encrypted RTL models, and plain text RTL models. These are all cycle-accurate models. The models support fast functional simulation of your IP core instance using industry-standard VHDL or Verilog HDL simulators. For some cores, only the plain text RTL model is generated, and you can simulate that model.

**Note:** Use the simulation models only for simulation and not for synthesis or any other purposes. Using these models for synthesis creates a nonfunctional design.

If you use an HMC BFM to simulate your HMC Controller IP core, ensure that you set the BFM parameters to match the features of your HMC Controller IP core and design. For example, confirm that you set the BFM memory size (2G or 4G) to match the address space that you expect your design to access, and that you set the BFM to communicate correctly with the HMC Controller IP core in Response Open Loop Mode. You must also set the BFM to send Write response packets for non-posted Write transactions received, because the HMC Controller IP core does not support the TGA field.

## Related Information Simulating Altera Designs

# Functional Description

| 2016.05.02 |                         |  |

|------------|-------------------------|--|

| UG-01152   | Subscribe Send Feedback |  |

The Altera HMC Controller MegaCore IP core enables easy access to external HMC devices.

## **High Level Block Diagram**

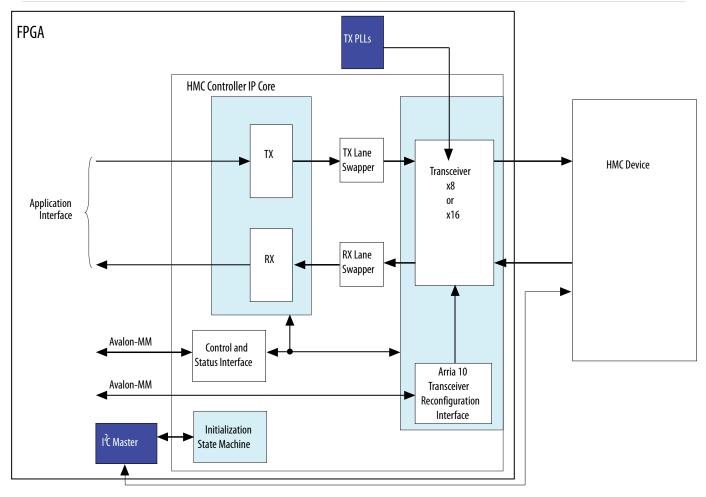

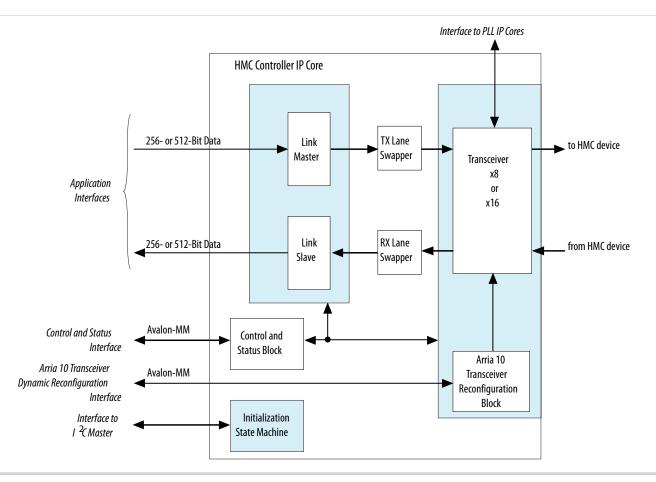

## Figure 3-1: HMC Controller IP Core Block Diagram

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

now part of Intel

#### 3-2 Interfaces Overview

The HMC Controller IP core includes the following components:

- Two data paths, an HMC TX path and an HMC RX path. Each path includes a link layer module, a lane swapper, and high-speed transceivers on the HMC link.

- An initialization state machine.

- A register control block.

- An Arria 10 Native PHY dynamic reconfiguration block.

The TX lane swapper remaps the HMC TX lanes to transceiver channels according to the **TX mapping** parameter. The RX lane swapper remaps the HMC RX lanes from transceiver channels according to the **RX mapping** parameter.

## **Interfaces Overview**

The Altera HMC Controller IP core supports multiple external interfaces.

## **Application Interfaces**

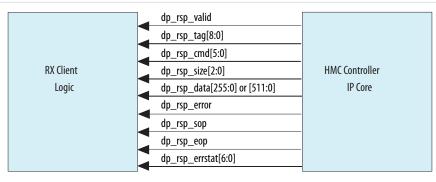

The data path request and response interfaces, also called the application request interface and the application response interface, provide a 256-bit or 512-bit data bus and dedicated signals for the application to provide HMC request packet field values and to read HMC response packet field values. Full-width variations support 1, 2, 3, or 4 pairs of data path request and response interfaces. Half-width variations support 1 pair of data path request and response interfaces.

## Table 3-1: Application Data Width in Full- and Half-Width IP Core Variations

| IP Core Variation              | Full-width   | Half-width  |

|--------------------------------|--------------|-------------|

| Memory Interface to HMC Device | 16-lane link | 8-lane link |

| Client Data Interface Width    | 512 bit      | 256 bit     |

## **Related Information**

Application Interface Signals on page 4-1

## **HMC Interface**

The HMC interface connects to the external HMC device, and complies with the HMC specification. The interface provides a single 8-lane or 16-lane link, configured in an Altera device in 8 or 16 adjacent transceiver channels.

The HMC Controller IP core operates in Response Open Loop Mode.

### **Related Information**

HMC Interface Signals on page 4-10

The HMC Controller IP core's HMC interface connects to the external HMC device's link interface and main reset signal.

• HMC Controller IP Core Supported HMC Transaction Types on page 1-3

**Functional Description**

Altera Corporation

## Interface to External I<sup>2</sup>C Master

The HMC Controller IP core requires that you instantiate an external I<sup>2</sup>C master module in your design. This external I<sup>2</sup>C master module must coordinate link initialization on the link between the HMC and the HMC Controller. The I<sup>2</sup>C master coordinates with the HMC Controller internal initialization state machine and programs configuration registers in the HMC device to which your IP core connects.

Separating the HMC Controller IP core from the I<sup>2</sup>C master module provides design flexibility. Because the IP core does not include the I<sup>2</sup>C master module, you can instantiate a single I<sup>2</sup>C master to control link initialization for multiple HMC Controller IP cores. A single I<sup>2</sup>C master module can also control other I<sup>2</sup>C slaves.

## **Related Information**

- Adding the External I2C Master Module on page 2-16 Information about how to connect the HMC Controller IP core to the external I2C master module.

- Signals on the Interface to the I2C Master on page 4-11

Describes the signals on this interface and the four-way handshaking protocol that the HMC

Controller IP core implements and that the I<sup>2</sup>C master must implement for correct IP core function ality.

## **Control and Status Register Interface**

The control and status register interface provides access to the HMC Controller IP core internal control and status registers. This interface does not provide access to the transceiver registers.

The control and status interface complies with the Avalon Memory-Mapped (Avalon-MM) specification defined in the *Avalon Interface Specifications*.

The control and status interface provides a 32-bit wide data bus for register content. All HMC Controller control and status registers are 32 bits wide and all register accesses through the control and status interface read or write the full 32 bits of register content.

### **Related Information**

- Control and Status Interface Signals on page 4-12

- HMC Controller IP Core Register Map on page 5-1

- Avalon Interface Specifications

## **Status and Debug Interface**

The status and debug interface provides signals to communicate successful link initalization and to support debugging of your HMC system.

Related Information Status and Debug Signals on page 4-13

## **Transceiver Control Interfaces**

The HMC Controller IP core supports the following transceiver control interfaces:

External PLL Interface on page 3-4

Transceiver Reconfiguration Interface on page 3-4

**Functional Description**

#### 3-4 External PLL Interface

## **External PLL Interface**

The HMC Controller IP core requires that you generate an external transceiver PLL IP core and connect it to each HMC Controller IP core lane.

If you do not generate and connect the transceiver PLL IP core, the HMC Controller IP core does not function correctly in hardware.

#### **Related Information**

- Adding the External PLL on page 2-13 Describes how to generate an external transceiver PLL IP core, including parameter requirements.

- Signals on the Interface to the External PLL on page 4-17

- HMC Controller IP Core Design Example on page 6-1 The HMC Controller design example provides an example of how to connect an external PLL to your HMC Controller IP core.

- Arria 10 Transceiver PHY User Guide Information about the Arria 10 transceiver PLLs and clock network.

## **Transceiver Reconfiguration Interface**

The transceiver reconfiguration interface provides access to the registers in the embedded Native PHY IP core. This interface provides direct access to the hard PCS registers on the device.

The transceiver reconfiguration interface complies with the Avalon Memory-Mapped (Avalon-MM) specification defined in the *Avalon Interface Specifications*.

#### **Related Information**

- Transceiver Reconfiguration Signals on page 4-15

- Avalon Interface Specifications Defines the Avalon Memory-Mapped (Avalon-MM) specification.

- Arria 10 Transceiver PHY User Guide Information about the Arria 10 transceiver reconfiguration interface.

- Arria 10 Transceiver Registers Detailed information about the Arria 10 transceiver registers.

## **Clocking and Reset Structure**

The HMC Controller IP core has a single core clock domain and multiple transceiver-related clock domains.

Your design must derive the external transceiver TX PLL reference clock, the RX CDR reference clock, and the REFCLKP and REFCLKN input signals of the external HMC device from the same clock reference source. This requirement ensures a 0 PPM difference between the receive and transmit clocks, as required by the HMC specification.

**Functional Description**

## Figure 3-2: HMC Controller IP Core Clocking Diagram

## **Related Information**

Clock and Reset Signals on page 4-14

Lists the clock and reset signals and the relationships between them.

## **Initialization and Reset**

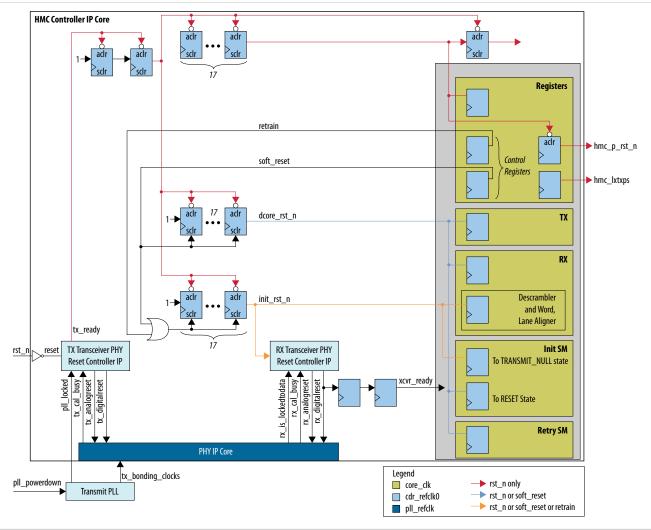

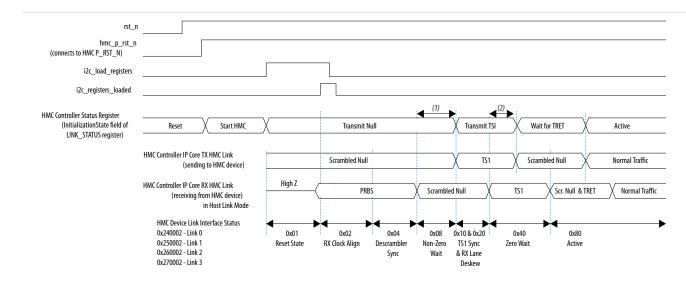

When you assert the active low rst\_n signal, you trigger initialization of the HMC Controller IP core, the HMC device, and the HMC link that connects them. To ensure the correct sequence, you must connect the HMC Controller IP core, the I<sup>2</sup>C master module, and the HMC device correctly. The IP core provides register fields to support link reinitialization, soft reset, fatal error recovery, and power management sleep and down modes.

**Functional Description**

## Figure 3-3: Initialization and Reset Options in the Full-Width HMC Controller IP Core

The HMC Controller IP core provides several mechanisms to reset various parts of the IP core, including the <code>rst\_n</code> input signal and the <code>SoftReset</code> and <code>Retrain</code> fields of the HMC Controller IP core <code>CONTROL</code> register. The <code>SoftReset</code> and <code>Retrain</code> fields of the <code>CONTROL</code> register are available only in full-width IP cores.

**Altera Corporation**

**Functional Description**

#### 3-7

#### Initialization

The following signals control HMC Controller IP core, HMC link, and HMC device initialization:

- rst\_n: Active low HMC Controller IP core input signal that triggers IP core initialization

- hmc\_p\_rst\_n: HMC Controller IP core output signal.

- Signal control: While rst\_n is asserted, and immediately after it is deasserted, the IP core controls this output signal. However, after the IP core raises this signal when rst\_n is deasserted, the P\_RST\_N field in bit [17] of the CONTROL register drives this signal. Software can modify this bit to force the HMC device to reset.

- Signal connection: You should connect this signal to the active low HMC device P\_RST\_N input signal. P\_RST\_N triggers HMC device initialization.

- i2c\_load\_registers: HMC Controller IP core output signal. You should connect this signal to the I<sup>2</sup>C master module input signal that tells the I<sup>2</sup>C master module to load the configuration registers of the HMC device.

- i2c\_registers\_loaded: HMC Controller IP core input signal that indicates the I<sup>2</sup>C master module has completed its part in the initialization of the HMC device. You should connect this signal to the I<sup>2</sup>C master module output signal that indicates successful completion of the HMC configuration register load sequence.

The IP core reports link initialization status in the InitializationState field of the LINK\_STATUS register at offset 0x10. The HMC device reports its own link initialization status in its own link interface status registers.

When you initialize the HMC link, recall the following HMC Controller IP core requirements:

- The HMC Controller IP core operates in Response Open Loop Mode, and you must configure the HMC device to communicate correctly with the IP core in this mode.

- The IP core does not support the TGA field, so you must configure the HMC device to acknowledge every non-posted Write request with a Write response packet.

## Figure 3-4: HMC Link Initialization Sequence

Notes:

1. HMC Controller IP core acquires descrambler sync. The Descrambler Sync field of the Lane Status register goes to all ones.

2. HMC Controller IP core does word and lane alignment. The Lanes Aligned bit pf the Link Status register goes to 1 and the Word Lock field of the Lane Status register goes to all ones.

#### 3-8 Initialization and Reset

#### **Fatal Error Recovery**

If the HMC device declares a fatal error, you must perform a warm reset of the HMC device and a reset of the HMC Controller IP core. To perform the HMC device warm reset, set the appropriate field in the HMC Global Configuration register.

You can perform a soft reset or a hard reset of the HMC Controller IP core. To perform the HMC Controller IP core soft reset, set the SoftReset field in bit [2] of the HMC Controller IP core CONTROL register To perform the hard reset, assert the rst\_n input signal.

If the HMC Controller IP core declares a fatal error, set the ClearFatalError field in bit [1] of the CONTROL register. In some cases, this action is sufficient to force the IP core to resume normal operation. If this action is not sufficient, you must perform a full reinitialization of the IP core.

#### **Power Management**

To save power during a period of inactivity on the link, you can put the HMC link in sleep mode. After a certain amount of time in sleep mode, the HMC device automatically moves to down mode.

To put the link to sleep:

- 1. Stop sending requests on the data path request interfaces, to force the IP core to stop sending requests on the HMC link.

- 2. Wait for all responses to arrive and tokens to return.

- **3.** Write the value of 0 to the TXPS field in bit [16] of the CONTROL register.

- **4.** Wait for the IP core to set the RXPS field in bit [16] of the LINK\_STATUS register to the value of 0.

To wake the link up from sleep mode or from down mode:

- 1. Write the value of 1 to the Retrain field in bit [0] of the CONTROL register.

- **2.** Write the value of 1 to the TXPS field in bit [16] of the CONTROL register.

- 3. Wait for the IP core to set the RXPS field in bit [16] of the LINK\_STATUS register to the value of 0.

### **Link Reinitialization**

To recover from a fatal error, to wake up the link from sleep mode, or to retrain a link exhibiting a high bit error rate, you must reinitalize the HMC link.

After the HMC device exits sleep mode, you must reinitialize the link to resynchronize descramblers and perform word and lane alignment.

To reinitialize the link, write a 1 to the Retrain field in bit [0] of the CONTROL register.

#### **Related Information**

• Adding the External I2C Master Module on page 2-16

Describes the I<sup>2</sup>C master module requirements and the module's connections to the HMC Controller IP core.

- Signals on the Interface to the I2C Master on page 4-11 Describes the detailed behavior of the I<sup>2</sup>C master module during initialization.

- HMC Interface Signals on page 4-10

- This interface includes the hmc\_p\_rst\_n signal.

- Clock and Reset Signals on page 4-14

- LINK\_STATUS Register on page 5-4

- **CONTROL Register** on page 5-2

**Functional Description**

## M20K ECC Support

If you turn on **Enable M20K ECC support** in your HMC Controller IP core variation, the IP core takes advantage of the built-in device support for ECC checking in all M20K blocks configured in the IP core on the device. The feature performs single-error correct, double-adjacent-error correct, and triple-adjacent-error detect ECC functionality in the M20K memory blocks configured in your IP core.

The HMC Controller IP core reports ECC error statistics in the registers RETRY\_ECC\_COUNT at offset 0x38 and RESPONSE\_ECC\_COUNT at offset 0x3C.

This feature enhances data reliability but increases request-to-response latency and resource utilization. Enabling this feature might reduce the maximum operating frequency ( $f_{MAX}$ ) and might increase the difficulty of closing timing in full-width variations.

#### **Related Information**

- Error and Retry Statistics Registers on page 5-10 Describes the RETRY\_ECC\_COUNT and RESPONSE\_ECC\_COUNT registers.

- Embedded Memory Blocks in Arria 10 Devices Information about the built-in ECC feature in Arria 10 devices.

## **Flow Control**

The HMC specification describes two possible flow control schemes for host-to-HMC traffic, token based flow control and Response Open Loop Mode.

In token-passing mode, the device sends information about its buffering capacity to the HMC link partner during transaction layer initialization. In Response Open Loop Mode, the device does not send information about its buffering capacity to the HMC link partner. Instead, it only sends a request packet when it has room to receive the response at any time.

The HMC Controller IP core operates in Response Open Loop Mode. The IP core is designed to have the capacity to accept all response packets from the HMC device.

When user requests come in faster than the HMC Controller IP core can send them out on the HMC link, the HMC Controller IP core backpressures the application by deasserting the dp\_req\_ready signal.

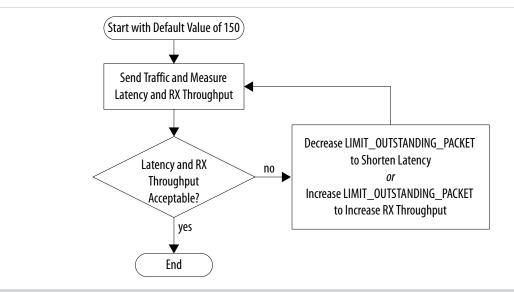

In addition, the IP core supports the Limit Outstanding FLITs feature. The client can turn on this feature to ensure that the IP core limits the number of outstanding FLITs in expected read responses. The IP core delays sending a request to the HMC if sending it would increase the number of pending response FLITs from the HMC above a user-specified threshold.

Note: The IP core only supports the Limit Outstanding FLITs feature for full-width variants.

The Limit Outstanding FLITs feature limit the worst-case round-trip latency of packets in the system by avoiding the congestion that can occur when response packets have large payloads. A sequence of RD128 requests, for example, causes congestion in the response path. Designers building read-intensive, latency-sensitive applications can use the Limit Outstanding FLITs feature to improve latency and throughput.

**Functional Description**

**Altera Corporation**

#### Figure 3-5: Improving Latency and Throughput Flow Chart

Related Information LIMIT\_OUTSTANDING\_PACKET Register on page 5-6

### **Error Detection and Management**

The HMC specification defines error detection and recovery processes. The HMC Controller IP core complies with these requirements, and implements the following additional features to support error management:

- Error Response queues to support software handling without dropping Error Responses that arrive in quick succession

- Statistics registers that count the number of packets in various error categories

#### Table 3-2: HMC Response Packet Field Checking

The HMC Controller checks these HMC packet fields for error indications, and handles errors by entering Error Abort mode to force the HMC device to retransmit the packet. In this mode, the IP core completes transmission of any partially transmitted packet and then submits IRTRY packets, per the HMC specification. The IP core also sets the indicated bit in the INTERRUPT\_STATUS register and increments the Local Count field of the LOCAL\_ERROR\_COUNT register.

| Received Packet Field | Error Indication                                          | INTERRUPT_STATUS Register Bit |

|-----------------------|-----------------------------------------------------------|-------------------------------|

| lng and dln           | The two fields have different values, or an invalid value | LNG/DLN Error                 |

| CRC                   | Incorrect CRC                                             | CRC Error                     |

| SEQ                   | Unexpected value                                          | SEQ Error                     |

**Functional Description**

The HMC Controller IP core also checks the ERRSTAT field value and treats the response according to the following rules: